(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6803168号

(P6803168)

(45) 発行日 令和2年12月23日(2020.12.23)

(24) 登録日 令和2年12月2日(2020.12.2)

|              |                 |

|--------------|-----------------|

| (51) Int.Cl. | F 1             |

| H05K 1/18    | (2006.01)       |

| H05K 3/34    | (2006.01)       |

| H05K 3/28    | (2006.01)       |

| H01L 21/60   | (2006.01)       |

|              | HO5K 1/18 P     |

|              | HO5K 3/34 510   |

|              | HO5K 3/28 G     |

|              | HO1L 21/60 321E |

請求項の数 5 (全 12 頁)

|                    |                              |

|--------------------|------------------------------|

| (21) 出願番号          | 特願2016-149036 (P2016-149036) |

| (22) 出願日           | 平成28年7月28日 (2016.7.28)       |

| (65) 公開番号          | 特開2017-38046 (P2017-38046A)  |

| (43) 公開日           | 平成29年2月16日 (2017.2.16)       |

| 審査請求日              | 令和1年7月29日 (2019.7.29)        |

| (31) 優先権主張番号       | 62/204,706                   |

| (32) 優先日           | 平成27年8月13日 (2015.8.13)       |

| (33) 優先権主張国・地域又は機関 | 米国(US)                       |

| (31) 優先権主張番号       | 14/964,964                   |

| (32) 優先日           | 平成27年12月10日 (2015.12.10)     |

| (33) 優先権主張国・地域又は機関 | 米国(US)                       |

|           |                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504407000<br>パロ アルト リサーチ センター イン<br>コーポレイテッド<br>アメリカ合衆国 カリフォルニア州 94<br>304 パロ アルト カイオーテ ヒル<br>ロード 3333 |

| (74) 代理人  | 100094569<br>弁理士 田中 伸一郎                                                                                |

| (74) 代理人  | 100109070<br>弁理士 須田 洋之                                                                                 |

| (74) 代理人  | 100067013<br>弁理士 大塚 文昭                                                                                 |

| (74) 代理人  | 100086771<br>弁理士 西島 幸喜                                                                                 |

早期審査対象出願

最終頁に続く

(54) 【発明の名称】可撓性基板の上にある印刷された構成要素とのペアダイの集積化

## (57) 【特許請求の範囲】

## 【請求項 1】

ハイブリッド電子アセンブリであって、

第1の表面と、前記第1の表面と反対側の第2の表面とを有する基板を有し、これらが前記基板の高さを規定し、前記第1の表面が、導電性回路トレースを含み、前記基板が、さらに、前記基板の長さおよび幅の中に規定される少なくとも1つの開口部を含み、前記少なくとも1つの開口部が、前記第1の表面および前記第2の表面を貫通して延びており、前記第1の表面と前記導電性回路トレースの表面が実質的に平らで平坦な関係にある、基板と、

第1の表面と第2の表面を有し、前記第1の表面が、導電性回路トレースを含み、電子回路要素が、前記基板の前記少なくとも1つの開口部の中に配置され、前記基板の中の前記少なくとも1つの開口部の中で、または前記少なくとも1つの開口部を貫通して適合するのに十分な高さ、幅および長さの寸法を有する、電子回路要素であって、該電子回路要素と前記基板の前記少なくとも1つの開口部の端部との間にギャップが存在し、前記第1の表面と前記導電性回路トレースの表面が実質的に平らで平坦な関係にある、電子回路要素と、

前記基板の前記第1の表面と前記電子回路要素の前記第1の表面が、前記基板の前記少なくとも1つの開口部の中に配置される前記電子回路要素と実質的に平らで平坦な関係で整列する整列領域と、

前記基板の前記第2の表面と前記電子回路要素の前記第2の表面が、整列していない関

10

20

係にあり、前記電子回路要素の高さは、前記基板の高さより大きく、前記電子回路要素は、前記少なくとも1つの開口部の中に配置され、前記電子回路要素の前記第2の表面は、前記基板の前記第2の表面を通過して延びる、非整列領域と、

前記基板の前記第2の表面の少なくとも一部および前記電子回路要素の少なくとも一部の上に作られ、前記基板と前記電子回路要素が物理的に密に接続する状態を維持するために十分な前記基板および前記電子回路要素の部分を包含する、結合材料と、

前記基板の前記第1の表面の前記導電性回路トレースと前記電子回路要素の前記第1の表面の前記導電性回路トレースの間に作られ、前記基板と前記電子回路要素の間の電気接続を与える導電性トレースとを含む、ハイブリッド電子アセンブリ。

【請求項2】

前記導電性トレースが、斜面のない構造での上に作られる、請求項1に記載のアセンブリ。

【請求項3】

前記電子回路要素の前記第1の表面および前記基板の前記第1の表面が、前記導電性トレースを作るのに十分なほど、同じ高さであることを含む、請求項1に記載のアセンブリ。

【請求項4】

前記基板は、あらかじめ製造された回路板であり、前記アセンブリは、前記あらかじめ製造された回路基板にさらなる電子回路要素を含む改良アセンブリである、請求項1に記載のアセンブリ。

【請求項5】

ハイブリッド電子アセンブリであって、

第1の表面と、前記第1の表面と反対側の第2の表面とを有する基板を有し、これらが前記基板の高さを規定し、前記第1の表面が、導電性回路トレースを含み、前記基板が、さらに、前記基板の長さおよび幅の中に規定される少なくとも1つの開口部を含み、前記少なくとも1つの開口部が、前記第1の表面および前記第2の表面を貫通して延びており、前記第1の表面と前記導電性回路トレースの表面が実質的に平らで平坦な関係にある、基板と、

第1の表面と第2の表面を有し、前記第1の表面が、導電性回路トレースを含み、電子回路要素が、前記基板の前記少なくとも1つの開口部の中に配置され、前記基板の中の前記少なくとも1つの開口部の中で、または前記少なくとも1つの開口部を貫通して適合するのに十分な高さ、幅および長さの寸法を有する、電子回路要素であって、該電子回路要素と前記基板の前記少なくとも1つの開口部の端部との間にギャップが存在し、前記第1の表面と前記導電性回路トレースの表面が実質的に平らで平坦な関係にある、電子回路要素と、

前記基板の前記第1の表面と前記電子回路要素の前記第1の表面が、前記基板の前記少なくとも1つの開口部の中に配置される前記電子回路要素と実質的に平らで平坦な関係で整列する整列領域と、

前記基板の前記第2の表面と前記電子回路要素の前記第2の表面が、整列していない関係にあり、前記電子回路要素の高さは、前記基板の高さより大きく、前記電子回路要素は、前記少なくとも1つの開口部の中に配置され、前記電子回路要素の前記第2の表面は、前記基板の前記第2の表面を通過して延びる、非整列領域と、

前記基板の前記第2の表面の少なくとも一部および前記電子回路要素の少なくとも一部の上に作られ、前記基板と前記電子回路要素が物理的に密に接続する状態を維持するために十分な前記基板および前記電子回路要素の部分を包含する、結合材料と、

前記基板の前記第1の表面の前記導電性回路トレースと前記電子回路要素の前記第1の表面の前記導電性回路トレースの間に作られ、前記基板と前記電子回路要素の間の電気接続を与える導電性トレースとを含み、

前記導電性トレースは、インクジェット印刷導電性トレース、フォトリソグラフィー導電性トレースおよび三次元印刷導電性トレースの少なくとも1つである、ハイブリッド電

10

20

30

40

50

子アセンブリ。

【発明の詳細な説明】

【背景技術】

【0001】

本出願は、電子機器の製造に関し、さらに具体的には、共通の基板の上に配置された異なる種類の要素（例えば、集積回路）および別個の要素で構成されるハイブリッド電子プラットフォームの製造に関する。ハイブリッド電子プラットフォームは、同じ複雑な機能性を維持し、ケイ素に由来する系としての処理能力を維持しつつ、費用対効果が高い大きな領域を製造する技術を使用する。温度および機械的な理由のために、従来のケイ素の集積化法（例えば、ソルダ結合およびワイヤボンディング）は、可撓性の印刷された電子機器を含み得るハイブリッドプラットフォームに適していない場合がある。可撓性基板の上にチップを集積化するために種々のパッケージ化技術が開発されている。例えば、異方性導電性膜（A C F）を適用し、プラスチック基板上でチップを回路に結合し、接続することができる。しかし、この方法の不都合な点は、接着剤で結合し得るチップ上の接触パッドの最小サイズに制限があることである。

【発明の概要】

【発明が解決しようとする課題】

【0002】

上述の制限などを克服する技術を提供することが有用であると考えられる。

【課題を解決するための手段】

【0003】

電子回路要素（例えば、特に、ペアダイおよびパッケージに入れられた集積化されたチップ）のための製造プロセスが提供され、電子回路要素の表面が、接続した基板と同じ高さにある。電子回路要素の表面が、接続パッドを含む電子要素を保持している。電子回路要素と、基板の中の開口部の端部との間にギャップが存在する。このギャップは、フィラー材料（例えば、結合材料）が充填される。基板と電子回路要素同士を包み込むか、または結合するためにも結合材料を使用する。製造プロセス中、電子回路要素の前側表面（接続パッドを含む電子要素を保持する）と、基板の前側表面（これも種々の電子要素を保持する）は、接着性または粘着性の材料（例えば、P D M S）を含む上側表面を有する平らな材料によって、接着した関係に保持される。平坦な材料が分離し、除去されると、平らで平坦であるか、または高さが同じ上側表面が、インクジェット印刷または他の技術による導電性トレースの生成を容易に受け入れることができる。

【図面の簡単な説明】

【0004】

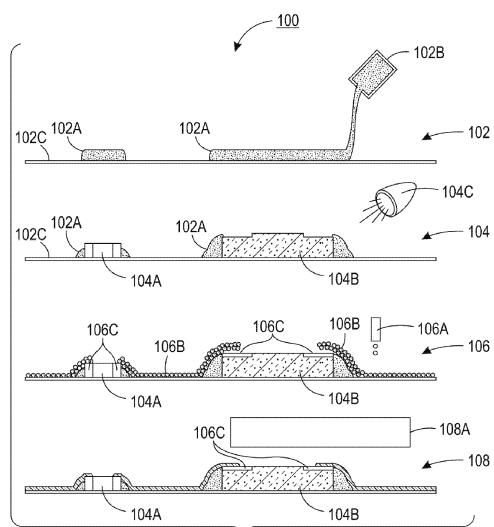

【図1】図1は、関連する構成要素の周囲に斜面が作られる相互接続を与えるためのプロセスを示す。

【図2】図2は、本出願の概念を実施し得るチップを示す。

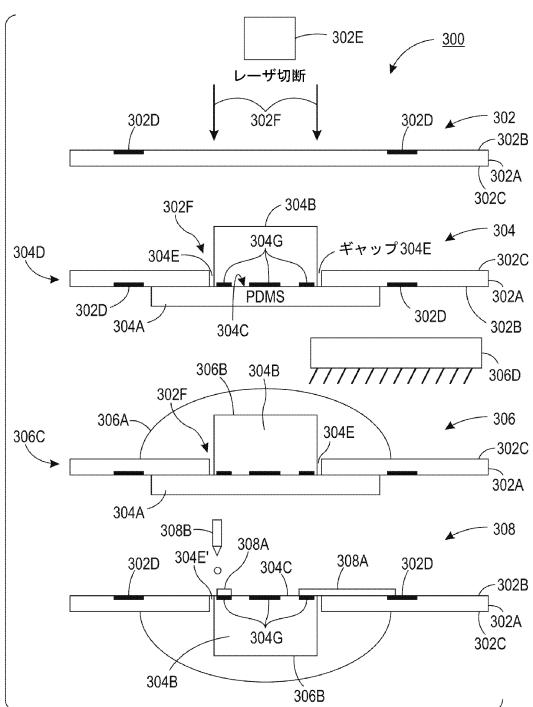

【図3】図3は、斜面を必要としないシステム中に相互接続が作られる本出願のプロセスを示す。

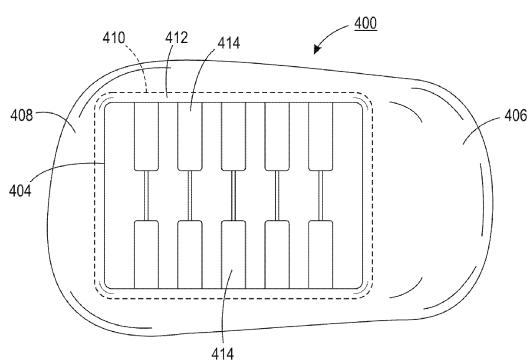

【図4 A】図4 Aは、組み立てられたシリコーン（S I）試験ダイアセンブリの試作品の上面図を示す。

【図4 B】図4 Bは、組み立てられたシリコーン（S I）試験ダイアセンブリの試作品の斜視図を示す。

【図5】図5は、図3の教示に従って作られた構造の代替的な実施形態を示す。

【図6 A】図6 Aは、本教示と組み合わせて使用可能な基板を示す。

【図6 B】図6 Bは、本教示と組み合わせて使用可能な電子回路要素を示す。

【発明を実施するための形態】

【0005】

以下の議論において、「電子回路要素」という用語の使用は、限定されないが、特に、ペアダイ、電子回路パッケージに入れられた電子チップを含む任意の多くの電子回路構造

10

20

30

40

50

を含むものと理解すべきである。

【0006】

可撓性基板の上で電子回路要素を集積化するための製造プロセスを提供するために、本議論は、印刷プロセスと組み合わせた、高解像度を容易にするための方法および構造を開示する。この実施形態において、開示される構造に対し、電子回路要素の表面（接触パッドおよび他の電子回路を含む電子要素を保持する）は、基板と同じ高さである。電子回路要素の側壁の周囲に、この要素と基板とを架橋するために用いられるフィラー材料が存在する。フィラーの上部表面も、基板表面および電子回路要素の上部表面（接触パッドおよび他の電子回路を保持する）と直線状であるか、または基板表面および電子回路要素の上部表面と実質的に同じ高さである。この配置によって、この要素の上の回路と、基板の上の回路との間に導電性トレースまたは接続を構築するか、または設置することが容易に行われる高解像度のパターン形成が可能になる。10

【0007】

パッケージ化の複雑さの課題を満足するために、一実施形態は、ジェット系の印刷技術、例えば、高密度および低い抵抗の相互接続を可能にする能力を与えるインクジェット印刷と一般的に呼ばれるものを使用し、ある実施形態において、三次元（3D）型印刷であってもよい。インクジェット型技術を使用すると、相互接続が、平坦な、平らな、高さが同じ領域の上の印刷された導電性（例えば、金属の）線から作られるとき、標準的なワイヤボンディングプロセスを置き換えることができる。従って、印刷される材料は、印刷可能な導電性材料であると理解されたい。20

【0008】

図1を見ると、一連の模式図102～108によって表され、インクジェット印刷を使用する既知の組立プロセス100が示されている。プロセス100は、以下を含む。

【0009】

模式図102によって示される第1の工程に示されるように、非導電性接着剤102Aは、分注デバイス102Bによって基板102Cの上側表面に分注される。非導電性接着剤は、準軟質の状態である。

【0010】

次に、模式図104によって示される第2の工程において、電子要素104Aおよび104Bは、これらが非導電性接着剤102Aと接触した状態になるように、基板102Cの表面の適切な位置に配置され、非導電性材料が、構成要素104A、104Bの周囲に盛り上がるよう、非導電性材料へと押さえつけられてもよい。構成要素は、上側の位置でこれらの接触接続を有するように配置される（すなわち、構成要素104A、104Bの接続部分は、非導電性接着剤と接触した状態ではない）。この時点で、硬化操作が行われ、非導電性接着剤を硬化させる。硬化は、例えば、限定されないが、硬化ランプ104Cのような多くの既知の様式で達成することができる。30

【0011】

模式図106によって示される第3の工程に移り、インクジェット型プリンタ106Aを使用し、回路パターンおよび相互接続106Bをインクジェット印刷し、これらを構成要素104A、104Bの接触領域（例えば、パッド）106Cに接続する。40

【0012】

最後に、模式図108によって示される第4の工程において、焼結要素108Aが提供され、これを使用し、印刷された導電性材料を焼結する。

【0013】

模式図104および106によって示される工程の具体的な概念は、非導電性接着剤を利用し、構成要素104A、104B（レジスタ、ベアダイなどであってもよい）の側壁を密封するために斜面を形成し、印刷された導電性トレースのための支持表面を提供し、基板102Cの上に印刷される回路の構成要素の上にある接触パッドに接続することである。

【0014】

10

20

30

40

50

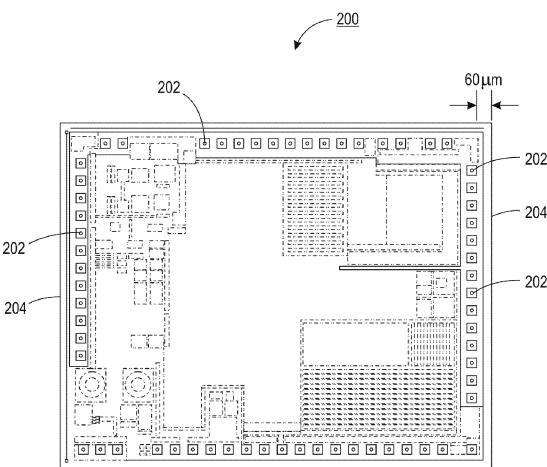

図2は、例示的なペアダイ200を示し、ペアダイ200は、36個の接触パッド202を有し(すべてのパッドの番号が付けられているわけではない)、接触パッド202は、最も小さなピッチが約120μmであり、ペアダイの縁204に対するパッド間の空間は、約60μmである。実際には、チップまたはダイの接触パッドを覆わずに、図1の斜面を構築し、ダイの側壁を密封することは困難である。

#### 【0015】

可撓性基板の上での電子回路要素の集積化(ペアダイ、パッケージに入れられたチップなどを含む)のための製造プロセスを提供するために、本願発明者らは、適切な印刷プロセスを用い、高い解像度の接続を容易にする方法および構造を開発した。開示された構造において、電子回路要素の表面は、基板と実質的に同じ高さにある。電子回路要素の側壁の周囲に、電子回路要素と基板とのギャップを架橋するためのフィラーが存在する。フィラーの上部表面も、基板表面と直線状であるか、または基板表面と実質的に同じ高さまたは平面である。従って、図1のプロセスで使用されるような斜面を必要とすることなく、基板の上の電子回路要素と回路との間の導電性接続を構築するための高解像度のパターン形成を簡単に行うことができる(すなわち、以下、斜面を用いない解決策を記載する)。

#### 【0016】

図3を見ると、本出願に従って、ハイブリッド電子機器のプラットフォームアセンブリを構築するための処理工程300が示され、これは図3(すなわち、模式図308)にも示される。

#### 【0017】

模式図302に示されるように、基板302Aが提供される(ある実施形態において、基板は、可撓性基板、例えば、プラスチック基板である)。基板302Aは、第1の表面302Bと、第1の表面と反対側の第2の表面302Cを有する。これらの表面は、基板302Aの高さを規定する。第1の表面302Bは、電子回路302D、例えば、限定されないが、導電性回路追跡器を含んでいてもよい。また、側面図に示されているが、基板302Aは、もちろん、幅と長さの寸法を有することも理解されたい。

#### 【0018】

材料除去デバイス302Eは、基板302Aのあらかじめ特定した位置の中に開口部302Fを形成する(開口部302Fは、平行に下向きに向かう複数の矢印によって規定される)。さらに具体的には、基板を貫通する開口部を形成するのに適した、基板302Aの第1の表面302Bの上の少なくとも1つの位置が特定される。その後、材料除去デバイス302Eは、材料除去操作を行い、基板302Aに開口部302Fを作成し、開口部302Fは、基板302Aの長さおよび幅の境界の範囲内に位置し、開口部は、第1の表面302Bと第2の表面302Cを貫通して延びる。

#### 【0019】

材料除去デバイス302Eは、一実施形態において、レーザ配置であり、一方、別の実施形態において、物理的に接触して切断するデバイスである。さらなる実施形態において、材料を正確に除去し、開口部302Fを形成することができる他のデバイスを使用してもよい。1つの基板に複数の開口部が作られてもよく、同じ基板に図3の組立プロセスを複数回繰り返し、複数の開口部を形成してもよいことも理解されたい。

#### 【0020】

開口部302Fは、組み込まれる特定の電子回路要素(例えば、ペアダイ)の形状および寸法に合わせて作られる。しかし、電子回路要素304Bを確実に受け入れができるように、特定量のクリアランス(例えば、5~25μm)が与えられる。電子回路要素304Bは、ペアダイまたはあらかじめパッケージに入れられた電子回路要素のうち、少なくとも1つである。

#### 【0021】

模式図304によって示される次の工程において、開口部302Fは、もっと明確に示される。ここで、模式図304は、改变された側面図であり、理解を容易にするために、例えば、電子回路要素304Bの前にある基板材料は示されていないことを述べておく。

10

20

30

40

50

しかし、電子回路要素 304B の位置は、基板 302A の境界の範囲内にあるため、電子回路要素 304B の前側の基板の一部が存在していてもよく（ギャップ 304E が見えないように妨害するだろう）、また、電子回路要素 304B の下側部分に基板の一部が存在していてもよい。

#### 【0022】

模式図 304において、基板 302A は、第 1 の表面 302B が（回路 / トレース 302D と共に）下側を向くようにひっくり返されている。さらに、粘着性の上側表面（例えば、ポリジメチルシロキサン（PDMS）材料、または要素を保持するが、要素同士を永久的に結合しない他のエラストマー・ポリマー）304A を有する平坦な物品は、開口部 302F と、基板 302A の第 1 の表面 302B の少なくとも一部の上に配置される。次いで、前側表面 304C が下側を向いた状態で電子回路要素 304B が、開口部 302F の中に配置される。前側表面 304C が、導電性回路トレース（接触パッドを含む）304G を含むことを述べておく。

10

#### 【0023】

粘着性表面 304A を有する平坦な部品の上側面は、整列領域 304D と考えられてもよく、ここで、基板 302A の第 1 の表面 302B と、電子回路要素 304B の第 1 の表面 304C とが、平坦な部品 304A に起因して、実質的に平らまたは平坦に、または同じ高さの関係で整列する。

#### 【0024】

模式図 304には、開口部 302F の端部と、電子回路要素 304B との間に存在するギャップ 304E も示される。ギャップ 304E は、過度に大きくなりが、電子回路要素 304B の配置を妨害しない程度に十分な大きさであることが好ましい（例えば、約 5 ~ 25 μm）。

20

#### 【0025】

図 3 の模式図 306を見ると、結合材料 306A は、電子回路要素 304B の第 2 の表面（裏側）306B の表面および上側と、基板 302A の第 2 の表面 302C の少なくとも一部の表面および上側に提供される。この裏側の領域は、非整列領域 306C であると理解されてもよく、ここで、基板 302A の第 2 の表面 302C と、電子回路要素 304B の第 2 の表面 306B は、整列していない。言い換えると、電子回路要素 304B の高さは、基板の高さより大きい。

30

#### 【0026】

一実施形態において、結合材料 306A は、この整列の裏側に分注された UV 硬化性ポリマーであり、この結合材料は、ギャップ 304E を密封するように作用する。UV 硬化性ポリマーの硬化を行うために、硬化整列（硬化ランプ、加熱部および / または他の適切な構成要素を含んでいてもよい）306D が提供される。UV 硬化後、UV 硬化したポリマーは、このアセンブリのための結合構造を与える。もちろん、当該技術分野で既知の他の結合材料も、UV 結合材料の代わりに使用してもよい。

#### 【0027】

図 3 の模式図 308において、このアセンブリは、ひっくり返され、平坦な物品（例えば、PDMS 材料）304A は分離され、除去され、実質的に平らまたは平らであるか、または高さが同じ表面が、充填されたギャップ 304E'（すなわち、結合材料 306A が充填され、平坦または平らな表面を形成する）を横切って、さらに、第 1 の表面 304D を横切って、第 1 の表面 302B から露出する。選択される接着材料は、上述の構成要素を保持するが、分離するときには、他の方法ではさらなる組立プロセスを妨害し得るような望ましくない量の残渣を残さないという特徴を有する。また、任意の工程として、構成要素および基板表面の洗浄は、分離および除去の後に行われてもよい。ここに示した操作によって、図 1 のプロセスによって作られる斜面は除外される。

40

#### 【0028】

最後に、導電性トレース 308A は、基板 302A の第 1 の表面 302B と、第 1 の表面 304D の間に延び、電子回路要素 304B が形成されるか、または設置される（例え

50

ば、設置は、斜面のない構造で達成される）。一実施形態において、トレース 308A は、インクジェット型プリンタデバイス 308B を用いることによって（導電性の流体を用いて）作られる。代替的な実施形態において、トレースは、フォトリソグラフィーを用いることによって作られてもよく、導電性トレースを作成するために、平坦または平らであるか、または高さが同じ表面が必要である。

#### 【0029】

図 3 の処理工程 302～308 に引き続き注目し、レーザによる切断（302F）が、あらかじめ製造された回路板（例えば、基板 302A）に対して行われることを示す実施形態が記載され、この処理順序は変更することができる。例えば、レーザによる切断をプランク基板に対して行い、電子回路要素 304B を結合させ、次いで、さらに、接続経路を有する回路を印刷してもよい。10

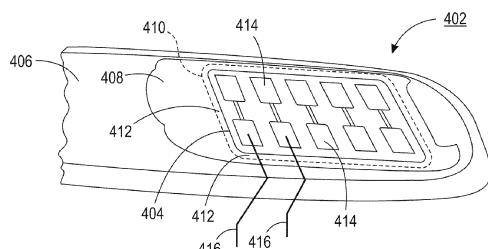

#### 【0030】

図 4A および 4B を見ると、シリコーン（Si）ベアダイアセンブリの試作品の上面図 400 および斜視図 402 が示されている。本出願の教示によれば、試験ダイ 404 の大きさは、おおよそ  $4 \times 6 \text{ mm}$  である。基板 406 は、厚みがおおよそ  $120 \mu\text{m}$  のポリエチレンナフタレン（PEN）シートである。この試作品について、結合材料（Norland Products Inc. 83H 接着剤）408 を使用した。

#### 【0031】

切断輪郭 410 は、ベアダイ 404 の外側領域に沿って与えられる。ギャップ 412 は、ベアダイ 404 と基板切断輪郭 410 との間の領域を規定する。この図には、Si ベアダイ 404 の上に配置される接触パッド 414 も示されている（図面の明確性のために、特定の接触パッド 414 のみが、番号を付けられている）。これに加え、印刷された接続トレース 416 は、このアセンブリから外側に延びるように示されており、接続トレース 416 が、接触パッド 414 とギャップ 412 の上を通過する（図面の明確性のために、ほんの限定された数の印刷された接続トレース 416 が示されており、番号を付けられている）。

#### 【0032】

結合材料 408 は、基板 406 の反対側表面にあり、この試作品では、基板 406 が透明であるため、基板 406 を通して見ることができることが理解されるべきである。

#### 【0033】

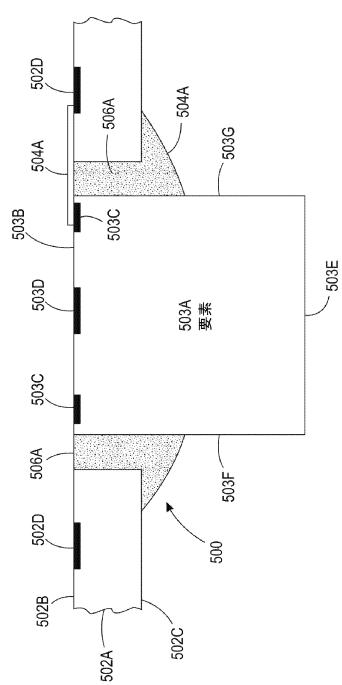

図 5 は、図 3 の一般的な教示を遵守して作られた構造の代替的な実施形態を示す。30

#### 【0034】

図 5 の側面図 500 は、基板 502A を含み、上側基板表面 502B と、下側基板表面 502C とを有する。電子回路 502D、例えば、限定されないが、導電性回路追跡器は、上側表面 502B に保持される。この実施形態において、電子回路要素 503A は、上側表面 503B を有し、電子回路 503C（限定されないが、接触パッドを含む）を保持する。電子回路要素 503A は、さらに、裏側表面 503E と、側壁 503F および 503G とを有する。導電性トレース 508A は、充填されたギャップ 506A を交差しつつ、電子回路要素 503A と基板 502A の間に延びる。導電性トレース 508A は、インクジェット型印刷（導電性材料を用いて）、フォトリソグラフィーまたは他の既知の技術のような印刷技術によって作られる。40

#### 【0035】

図 5 のこの実施形態において、具体的な違いは、結合材料 504A が、以前の実施形態よりも自由度が低い様式で適用されることである（すなわち、図 3 の模式図 306 および結合材料 306A を参照）。具体的には、結合材料（この観点では、硬化している）504A が、ギャップ 506A を充填するために適用され、電子回路 503A の側壁 503F および 503G に沿ってギャップ 506A を通って延び、また、基板 502A の側壁に沿った部分および基板 502A の裏側表面 502C の小さな部分に向かって延びる。従って、この実施形態は、さらに小型の材料集約的なアセンブリを与える。

#### 【0036】

10

20

30

40

50

別の実施形態において、図3（および図5）に関連して開示されるプロセスを、改良した操作に適用してもよい。例えば、これらの状況において、基板は、回路と電子回路要素（例えば、304B、503A）とを有する、あらかじめ製造された回路板である。この状況において、このプロセスは、さらに、回路板にさらなる電子回路要素を少なくとも加えることによって、および／またはあらかじめ製造された回路板の上にすでに存在する電子回路要素を置き換えることによって、あらかじめ製造された回路板を改良することを含む。それぞれの場合に、図3および図5の教示に従って、このような改良を行う。

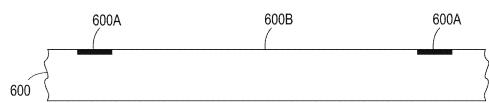

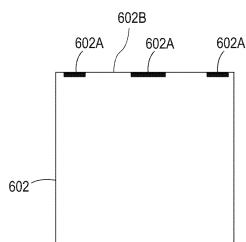

#### 【0037】

ここで、図6Aおよび6Bを見ると、上の実施形態において、それぞれの電子回路は、それぞれの基板表面と実質的に高さが同じである。しかし、本発明の概念は、電子回路と基板が同一平面上にないときにも有用であることを理解すべきである。例えば、図6Aおよび6Bにおいて、基板600と電子回路要素602が示されている。ここから理解することができるよう、基板600の上の電子回路またはトレース600A、および電子要素602の上の電子回路またはトレース602Aは、外形で、それぞれの表面600B、602Bよりも上にある。特定の実施形態において、この外形は、実質的に1～20ミクロンであり、さらに具体的には、その表面よりも10～20ミクロン上である。従って、レーザ切断型センサについての上の図に記載されるプロセスは、図6Aおよび6Bに示されるような項目および上の図に示されるような項目に適しており、同じ種類のプロセスが使用されるだろう。例えば、電子回路要素が、十分にやわらかい材料（例えば、PDMaterial）と接触した状態で配置されると、電子回路要素がPDMaterialに押しつけられ、まだ受けていない残りのプロセスのために適切な位置決めを与える。

#### 【0038】

同様に、基板の上の導電性トレースが、600および602のような要素に適用されるとき、前の図に示されるような実質的に平坦な回路線を作成するために、十分な堆積高さを有する。

#### 【0039】

前の議論は、ハイブリッド電子センサを作成する方法を記載している。この方法は、第1の表面と、第1の表面と反対側の第2の表面とを有し、第1の表面が、導電性回路追跡器を含み、高さ、幅および長さの寸法を有する基板を提供する工程を含むことを述べておく。少なくとも1つの位置が、基板の第1の表面で特定され、基板を貫通する少なくとも1つの開口部を形成する。材料除去操作は、特定された少なくとも1つの位置で行われ、少なくとも1つの特定された位置で、基板に少なくとも1つの開口部を作成する。接着性表面を有する物品が、少なくとも1つの開口部の上の第1の平坦または平らな側と、基板の第1の表面の側にある基板の少なくとも一部に接続する。電子回路要素は、電子回路要素の第1の表面が、エラストマー材料と係合し、基板の実質的に第2の表面で開口部を覆うまで、電子回路要素の第1の表面が、開口部の中を通過する向きで、少なくとも1つの開口部の中に配置され、電子回路要素の第1の表面と、基板の第1の表面は、両方とも、実質的に平らまたは平坦、または高さが同じ関係で配置される。結合材料は、電子回路要素の少なくとも一部と、基板の第2の表面の少なくとも一部とを物理的に結合させるために適用される。硬化操作は、結合材料を硬化させるために行われ、それによって、基板と電子回路要素との間に頑丈な物理的接続を与える。第1の平坦または平らな側に粘着性表面を有する物品は、電子回路要素の第1の表面および基板の第1の表面から分離する。その後、導電性トレースは、基板と電子回路要素の間に設置され、それによって、電気接続を与える。

#### 【0040】

上に記載した方法のいくつかの態様を以下に記載する。

#### 【0041】

設置は、斜面のない構造で達成される。

#### 【0042】

電子回路要素の第1の表面および基板の第1の表面は、導電性トレースを作るのに十分

10

20

30

40

50

なほど、同じ高さであることを含む。

【0043】

基板は、あらかじめ製造された回路板であり、記載した方法は、さらに、さらなる電子回路要素を少なくとも加えること、あらかじめ製造された回路板の上にすでに存在する電子回路要素を置き換えることの少なくとも1つによって、あらかじめ製造された回路板を改良することを含む。

【0044】

電子回路要素は、ベアダイ、およびあらかじめパッケージに入れられた電子回路要素の少なくとも1つである。

【0045】

導電性トレースの設置は、インクジェット印刷、フォトリソグラフィーおよび三次元印刷を少なくとも行うことを含む。

【0046】

材料除去操作は、レーザによる切断、溶融操作および物理的に接触する切断操作のいずれかによって行われる。

【0047】

結合材料は、一実施形態において、UV硬化性ポリマー材料である。

【0048】

基板は、プラスチック基板である。

【0049】

基板は、可撓性基板である。

【0050】

粘着性表面を有する物品は、平坦なPDSM材料またはエラストマー材料である。

【0051】

記載される工程は、第1の表面と、第1の表面と反対側の第2の表面とを有する基板を含む電子ハイブリッドアセンブリを形成し、これらが基板の高さを規定し、第1の表面が、導電性回路追跡器を含み、基板が、基板の長さおよび幅の中に規定される少なくとも1つの開口部を含み、この開口部が、第1の表面および第2の表面を貫通して延びており、電子回路要素は、第1の表面と第2の表面を有し、第1の表面が、導電性回路追跡器を含み、電子回路要素が、基板の少なくとも1つの開口部の中に配置され、基板の中の少なくとも1つの開口部の中で、または少なくとも1つの開口部を貫通して適合するのに十分な高さ、幅および長さの寸法を有する。整列領域は、基板の第1の表面と電子回路要素の第1の表面が、基板の少なくとも1つの開口部の中に配置される電子回路要素と実質的に平らで平坦な関係で整列するように提供される。非整列領域は、基板の第2の表面と電子回路要素の第2の表面が、整列していない関係にあるように提供され、電子回路要素の高さは、基板の高さより大きく、電子回路要素は、少なくとも1つの開口部の中に配置され、電子回路要素の第2の表面は、基板の第2の表面を通過して延びる。結合材料は、基板の第2の表面の少なくとも一部および電子回路要素の少なくとも一部の上に作られ、結合材料は、基板と電子回路要素が物理的に密に接続する状態を維持するために十分な基板および電子回路要素の部分を包含する。導電性トレースは、基板の第1の表面と電子回路要素の第1の表面の間に作られ、基板と電子回路要素の間の電気接続を与える。

10

20

30

40

【図1】

図1

【図2】

図2

【図3】

図3

【図4 A】

図4 A

【図4 B】

図4 B

【図5】

図5

【図6 A】

図6 A

【図6 B】

図6 B

---

フロントページの続き

前置審査

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100120525

弁理士 近藤 直樹

(74)代理人 100139712

弁理士 那須 威夫

(72)発明者 ピン・メイ

アメリカ合衆国 カリフォルニア州 95128 サン・ノゼ ヴィラ・センター・ウェイ 56

8

(72)発明者 グレゴリー・エル・ホワイティング

アメリカ合衆国 カリフォルニア州 94025 メンロー・パーク ミドル・アヴェニュー 6

17

(72)発明者 ブレント・エス・クルーサー

アメリカ合衆国 カリフォルニア州 94536-2412 フレモント コーニッシュ・ドライブ

35215

審査官 原田 貴志

(56)参考文献 特開昭64-011357(JP,A)

特表2013-531378(JP,A)

特開平11-238956(JP,A)

特開2006-165506(JP,A)

特開2010-251376(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05K 1/18

H05K 3/28

H05K 3/34

H01L 21/60