(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년07월08일

(11) 등록번호 10-1417232

(24) 등록일자 2014년06월30일

- (51) 국제특허분류(Int. Cl.)

**H01L 27/146** (2006.01)

- (21) 출원번호 10-2011-7002504

- (22) 출원일자(국제) 2009년07월13일

심사청구일자 2012년04월09일

- (85) 번역문제출일자 2011년01월31일

- (65) 공개번호 10-2011-0036823

- (43) 공개일자 2011년04월11일

- (86) 국제출원번호 PCT/US2009/004051

- (87) 국제공개번호 WO 2010/014138

국제공개일자 2010년02월04일

- (30) 우선권주장

12/184,314 2008년08월01일 미국(US)

- (56) 선행기술조사문현

JP01151262 A

JP10284714 A

JP20011339057 A

JP2006120921 A

전체 청구항 수 : 총 15 항

심사관 : 오순영

(54) 발명의 명칭 복수의 감지층들을 구비한 이미지 센서

**(57) 요 약**

이미지 센서는 픽셀들의 제1 배열을 구비한 제1 센서층(101) 및 픽셀들의 제2 배열을 구비한 제2 센서층(102)을 포함한다. 제1 및 제2 배열들의 각 픽셀은 입사광에 반응하여 전하를 수집하기 위한 광검출기(140), 전하-전압 변환 메커니즘(144), 그리고 광검출기에서 전하-전압 메커니즘으로 전하를 선택적으로 전송하기 위한 전송 게이트(142)를 구비한다. 제1 및 제2 센서층들은 각각 제1 및 제2의 미리 선택된 과정의 범위에서 빛을 수집하기 위한 두께를 갖는다. 회로층(120)은 제1 센서층 아래에 위치되며, 제1 및 제2 센서 층들의 픽셀들을 위한 지원 회로 조합체(122)를 구비하고, 층간 커넥터들(130)은 제1 및 제2 층들의 픽셀들 그리고 지원 회로 조합체 사이에 위치한다.

**대 표 도**

## 특허청구의 범위

### 청구항 1

이미지 센서로서,

각각 입사광에 반응하여 전하를 수집하기 위한 광검출기를 포함하는 픽셀들의 제1 배열, 플로팅 확산, 및 상기 광검출기에서 상기 플로팅 확산으로 전하를 선택적으로 전송하기 위한 전송 게이트를 구비하며, 제1의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖는, 제1 센서층;

상기 제1 센서층 위에 위치하며, 각각 입사광에 반응하여 전하를 수집하기 위한 광검출기를 포함하는 픽셀들의 제2 배열, 플로팅 확산, 및 상기 광검출기에서 상기 플로팅 확산으로 전하를 선택적으로 전송하기 위한 전송 게이트를 구비하고, 제2의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖는, 제2 센서층;

상기 제1 센서층 아래에 위치하며, 상기 제1 및 제2 센서층들의 픽셀들을 위한 지원 회로 조합체(support circuitry)를 구비한 회로층;

상기 제1 및 제2 층들의 픽셀들과 상기 지원 회로 조합체 사이의 층간 커넥터들(interlayer connectors); 및 상기 제2 센서층 위에 위치한 컬러 필터 배열 필터(color filter array filter)

를 포함하는, 이미지 센서.

### 청구항 2

제1항에 있어서,

상기 회로층은 상기 제1 및 제2 센서층의 상기 플로팅 확산들에 결합된 플로팅 확산을 포함하는, 이미지 센서.

### 청구항 3

제1항에 있어서,

상기 회로층은 각각 입사광에 반응하여 전하를 수집하기 위한 광검출기를 포함하는 픽셀들의 배열, 플로팅 확산, 및 상기 광검출기에서 상기 플로팅 확산으로 전하를 선택적으로 전송하기 위한 전송 게이트를 더 포함하는, 이미지 센서.

### 청구항 4

제1항에 있어서,

복수 개의 포토다이오드들이 공통 플로팅 확산에 연결된, 이미지 센서.

### 청구항 5

제1항에 있어서,

상기 회로층은 플로팅 확산을 포함하며, 상기 층간 연결들은 상기 제1 및 제2 센서층들의 플로팅 확산들과 상기 회로층 사이에 연결된, 이미지 센서.

### 청구항 6

제1항에 있어서,

상기 층간 연결들을 제공하는 행 및 열 선택 회로 조합체(row and column select circuitry)를 더 포함하는, 이미지 센서.

### 청구항 7

삭제

### 청구항 8

제1항에 있어서,

상기 제2 센서층 위에 위치한 제3 센서층을 더 포함하며,

상기 제3 센서층은 각각 입사광에 반응하여 전하를 수집하기 위한 광검출기를 포함하는 픽셀들의 제3 배열, 플로팅 확산, 및 상기 광검출기에서 상기 플로팅 확산으로 전하를 선택적으로 전송하기 위한 전송 게이트를 구비하고, 상기 제3 센서층은 제3의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖는, 이미지 센서.

#### 청구항 9

제8항에 있어서,

상기 제3 센서층 위에 위치한 제4 센서층을 더 포함하며,

상기 제3 센서층은 제4의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖고, 상기 제1, 제2, 제3 및 제4의 미리 선택된 파장의 범위의 최소한 하나는 가시 주파수 범위(visible frequency range)의 밖에 있는, 이미지 센서.

#### 청구항 10

제1항에 있어서,

상기 제1 센서층 및 회로층은 상기 픽셀들의 제1 배열 및 상기 지원 회로 조합체를 구비한 단일 층으로 결합되는, 이미지 센서.

#### 청구항 11

이미지 센서로서,

각각 입사광에 반응하여 전하를 수집하기 위한 광검출기를 포함하는 픽셀들의 제1 배열, 플로팅 확산, 및 상기 광검출기에서 상기 플로팅 확산으로 전하를 선택적으로 전송하기 위한 전송 게이트를 구비하며, 제1의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖는, 제1 센서층;

상기 제1 센서층 아래에 위치하며, 각각 입사광에 반응하여 전하를 수집하기 위한 광검출기를 포함하는 픽셀들의 제2 배열, 플로팅 확산, 상기 광검출기에서 상기 플로팅 확산으로 전하를 선택적으로 전송하기 위한 전송 게이트, 및 상기 픽셀들의 제1 및 제2 배열을 위한 지원 회로 조합체를 구비하며, 제2의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖는 회로층;

상기 제1 및 제2 층들의 픽셀들과 상기 지원 회로 조합체 사이의 층간 커넥터들; 및

상기 제1 센서층 위에 위치한 컬러 필터 배열

을 포함하는, 이미지 센서.

#### 청구항 12

제11항에 있어서,

상기 층간 연결들은 상기 제1 센서층 및 상기 회로층의 상기 플로팅 확산들 사이에 연결되는, 이미지 센서.

#### 청구항 13

제11항에 있어서,

상기 층간 연결들을 제공하는 행 및 열 선택 회로 조합체를 더 포함하는, 이미지 센서.

#### 청구항 14

이미지 센서의 픽셀들을 비닝(binning)하는 방법에 있어서, 상기 방법은,

제1 층에 위치한 제1 픽셀 커널을 제공하는 단계;

상기 제1층 위의 제2 층에 위치한 제2 픽셀 커널을 제공하는 단계;

상기 제1 픽셀 커널의 픽셀에서 제1 플로팅 확산으로 제1 전하를 전송하는 단계;

상기 제2 픽셀 커널의 픽셀에서 제2 플로팅 확산으로 제2 전하를 전송하는 단계; 및

상기 제1 및 제2 전하들을 공통 플로팅 확산으로 전송하는 단계

를 포함하는, 방법.

### 청구항 15

제14항에 있어서,

상기 제2 층의 위의 제3 층에 위치한 제3 픽셀 커널을 제공하는 단계;

상기 제3 픽셀 커널의 픽셀에서 제3 플로팅 확산으로 제3 전하를 전송하는 단계; 및

상기 제1, 제2 및 제3 전하들을 상기 공통 플로팅 확산으로 전송하는 단계

를 더 포함하는, 방법.

### 청구항 16

제14항에 있어서,

상기 제1 전하를 전송하는 단계는,

복수의 픽셀들에서 상기 제1 플로팅 확산으로 복수의 전하들을 전송하는 단계를 포함하는, 방법.

## 명세서

### 기술 분야

[0001] 본 발명은 일반적으로 이미지 센서 분야에 관한 것으로서, 더욱 상세하게는 적층된 이미지 센서 구조에 관한 것이다.

### 배경 기술

[0002] 일반적인 상보성 금속 산화막 반도체(complementary metal oxide semiconductor; CMOS) 이미지 센서는 입사광(incident light)에 응답하여 전하 수집을 위한 포토다이오드(photodiode) 그리고 포토다이오드로부터 플로팅 확산(floating diffusion)과 같은 전하-전압 변환 메커니즘으로 전하를 전송하기 위한 전송 게이트를 포함하는 이미지 감지부(image sensing portion)를 구비한다. 보통, 감지부는 이미지 센서를 위한 제어 회로와 유사한 공정을 사용하여 동일한 재료층에서 제조된다. 이미지 센서에서 제공된 픽셀들의 수를 증가시키기 위한 노력에 의해, 픽셀 크기는 감소되어 왔다.

[0003] 그러나, 픽셀 크기가 감소함에 따라, 광검출기(photodetector)의 조사된 영역(illuminated area) 또한 일반적으로 감소되었으며, 이어서 캡처된 신호 수준이 감소되고 성능이 저하되었다.

[0004] 따라서, 향상된 이미지 센서 구조에 대한 필요성이 존재한다.

### 발명의 내용

[0005] 이미지 센서는 픽셀들의 제1 배열을 구비한 제1 센서층을 포함한다. 제1 배열의 각 픽셀은 입사광에 응답하여 전하를 수집하기 위한 광검출기, 전하-전압 변환 메커니즘, 그리고 광검출기에서 전하-전압 메커니즘으로 전하를 선택적으로 전송하기 위한 전송 게이트를 구비한다. 제1 센서층은 제1의 미리 선택된 파장의 범위(a first preselected range of wavelengths)에서 빛을 수집하기 위한 두께를 갖는다. 제2 센서는 제1 센서층 위에 위치한 층으로, 픽셀들의 제2 배열을 구비한다. 각 픽셀은 입사광에 응답하여 전하를 수집하기 위한 광검출기, 전하-전압 변환, 그리고 광검출기에서 전하-전압 메커니즘으로 전하를 선택적으로 전송하기 위한 전송 게이트를 포함한다. 제2 센서층은 제2의 미리 선택된 파장의 범위에서 빛을 수집하기 위한 두께를 갖는다. 회로층은 제1 센서층 아래에 위치되며, 제1 및 제2 센서층들의 픽셀들을 위한 지원 회로 조합체(support circuitry)를 구비하며 층간 커넥터들(interlayer connectors)은 제1 및 제2 층들의 픽셀들 그리고 지원 회로 조합체 사이에 위치한다.

[0006] 본 발명은 향상된 이미지 센서 구조를 제공하는 이점이 있다.

### 도면의 간단한 설명

[0007] 본 발명의 실시예들은 이하의 도면들을 참조하여 더 잘 이해된다. 도면들의 요소들은 반드시 서로에게 상대적인 축척대로 도시된 것은 아니다. 유사한 참조 번호들은 대응되는 유사한 부분들 가리킨다.

도 1은 디지털 카메라의 일 실시예의 특징을 도시한 블록도.

도 2는 이미지 센서의 일 실시예를 개념적으로 도시한 블록도.

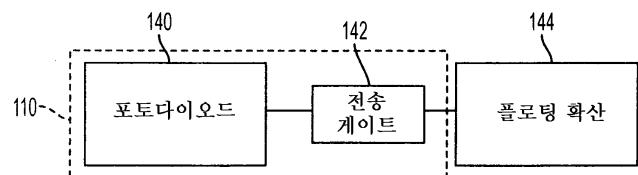

도 3은 픽셀의 부분들을 도시한 블록도.

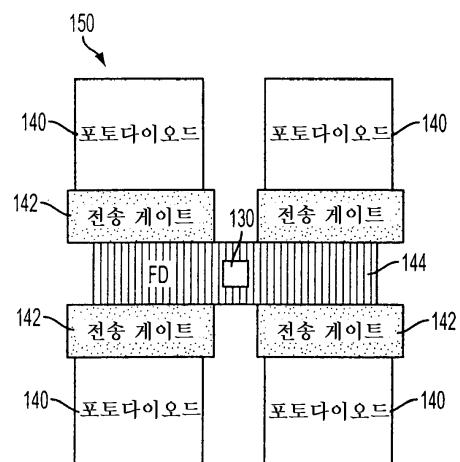

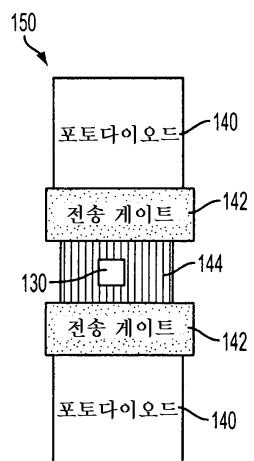

도 4a 및 4b는 픽셀 커널 구성들의 실시예들의 예를 도시한 도면.

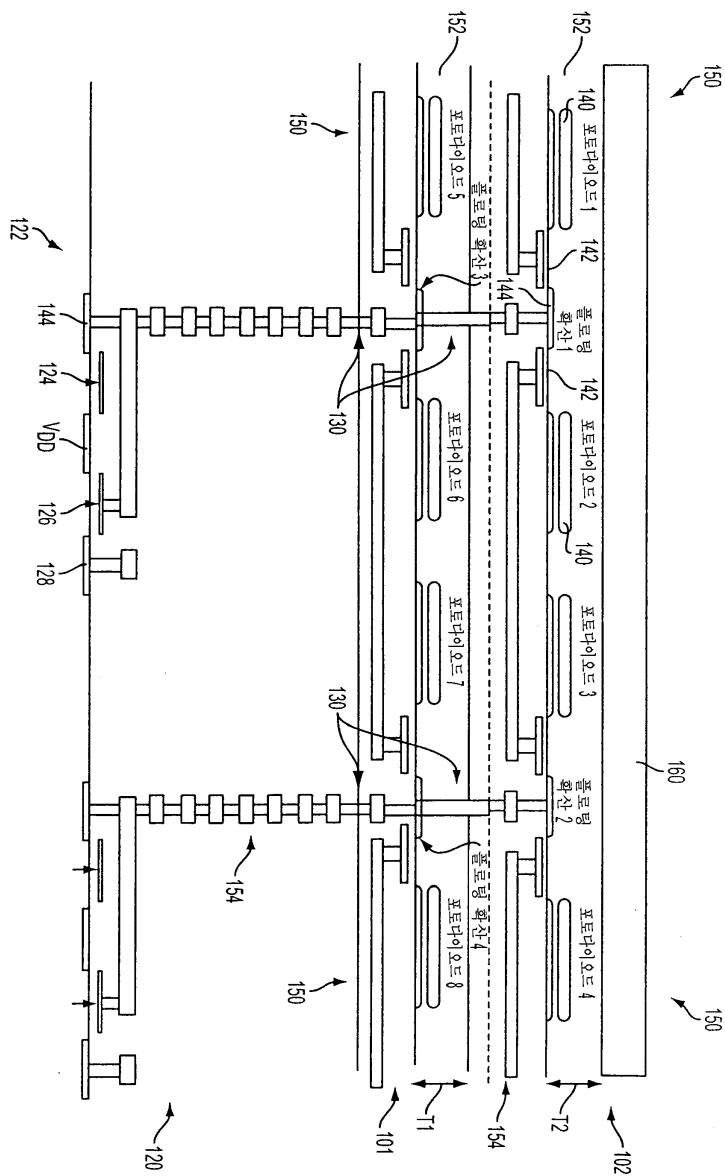

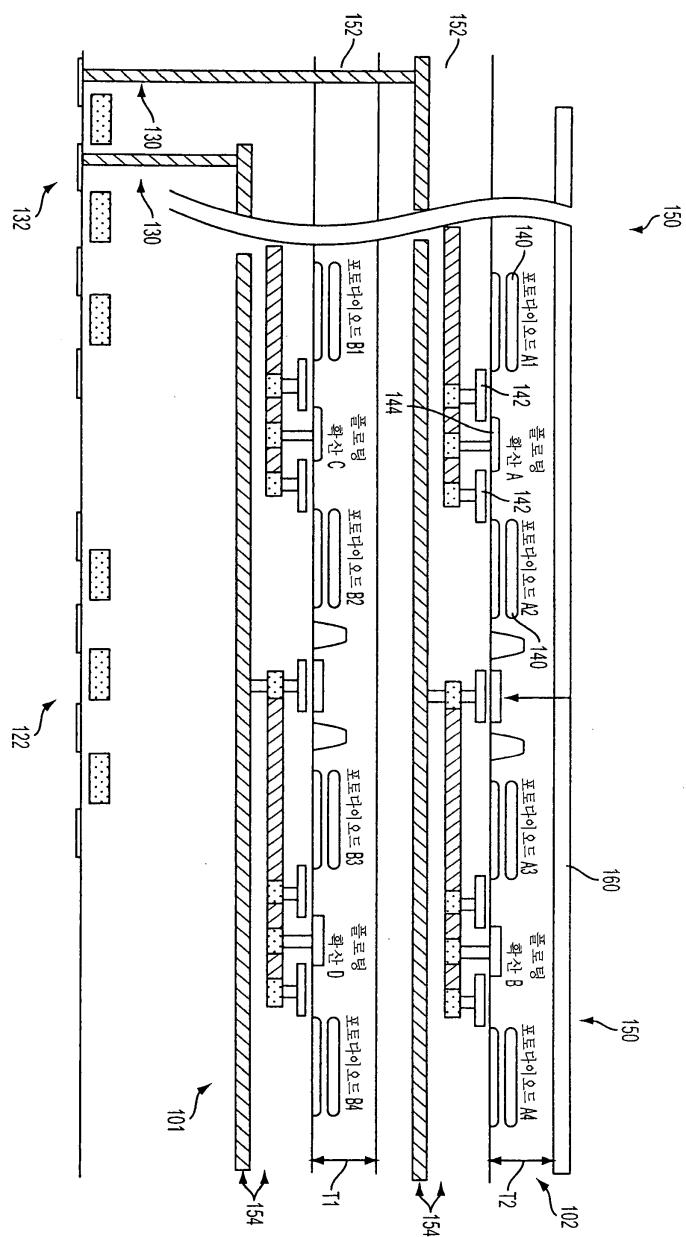

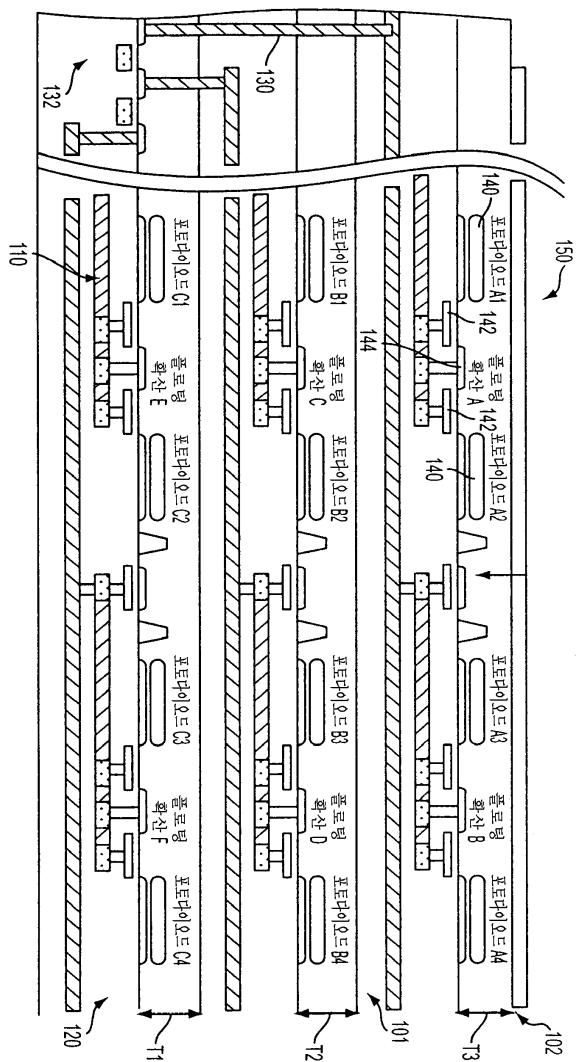

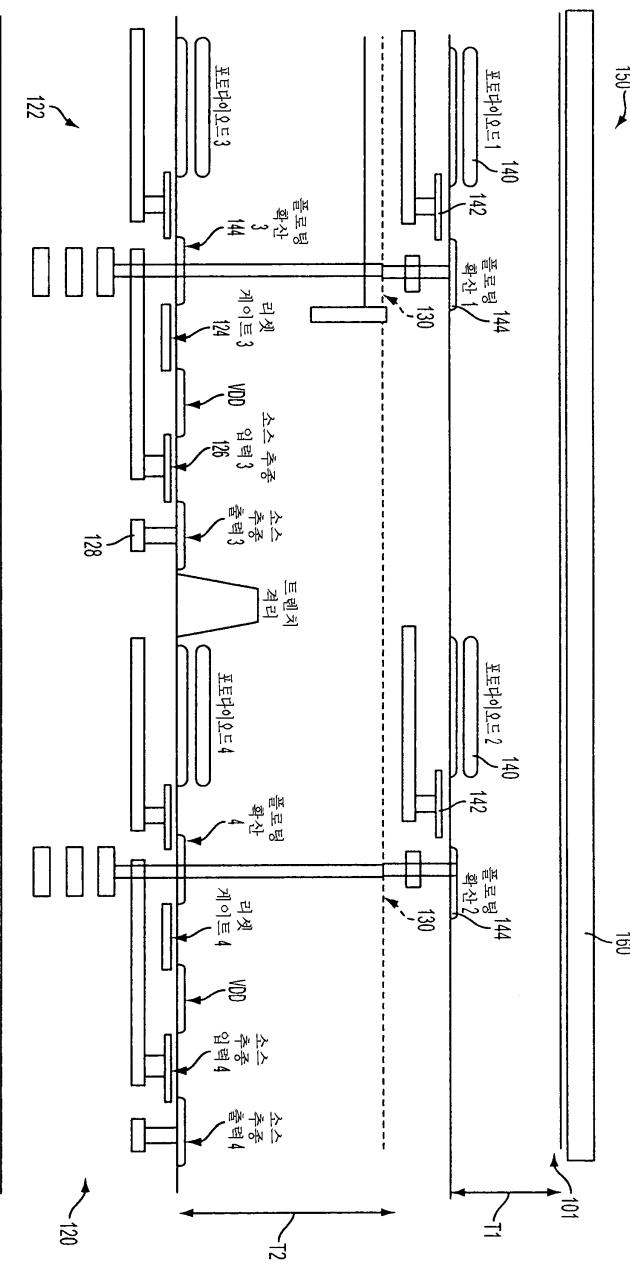

도 5는 이미지 센서의 일 실시예를 도시한 단면도.

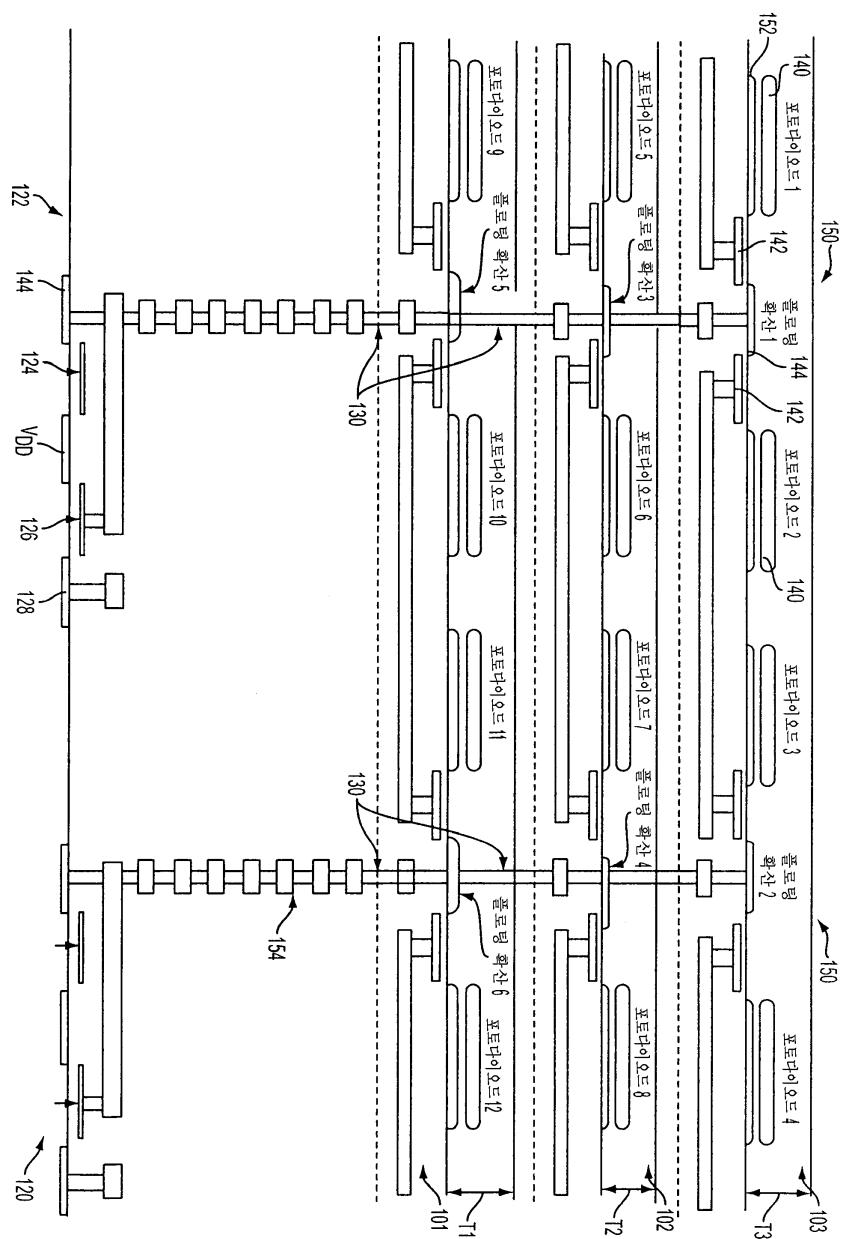

도 6은 이미지 센서의 또 다른 실시예를 도시한 단면도.

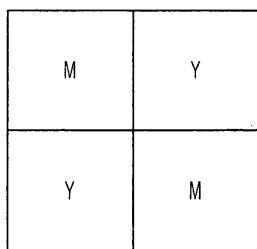

도 7 및 도 8은 컬러 필터 배열들의 예들을 도시한 도면.

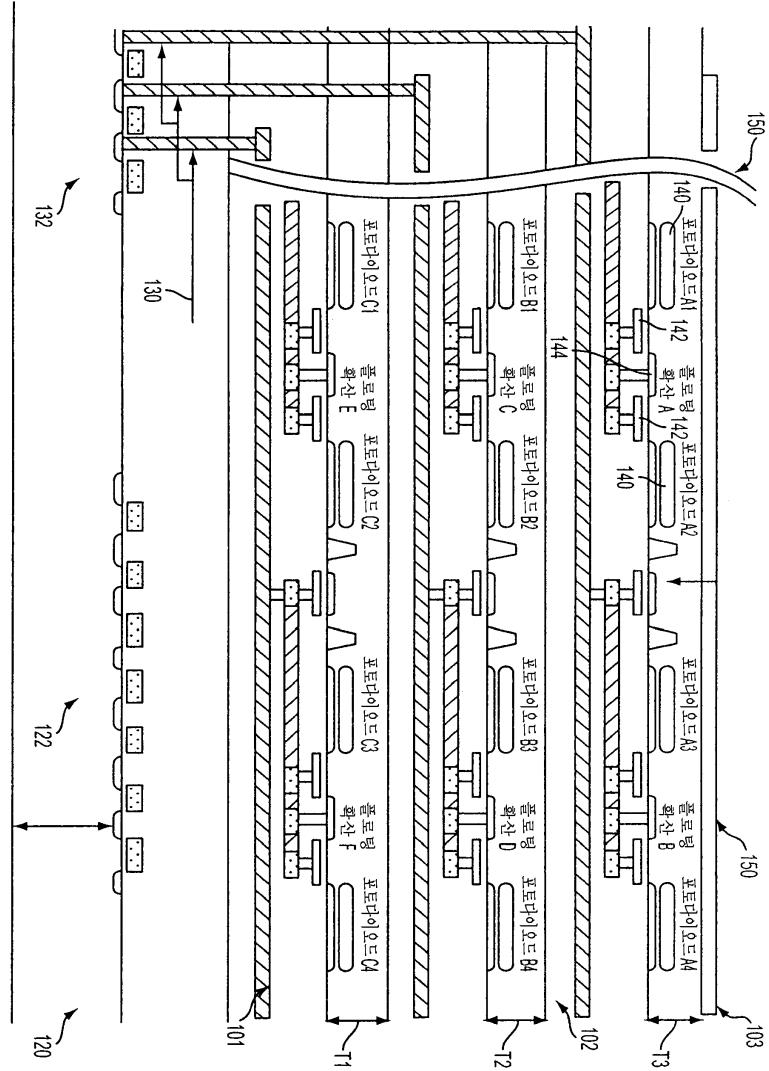

도 9는 이미지 센서의 또 다른 실시예를 도시한 단면도.

도 10은 이미지 센서의 또 다른 실시예를 도시한 단면도.

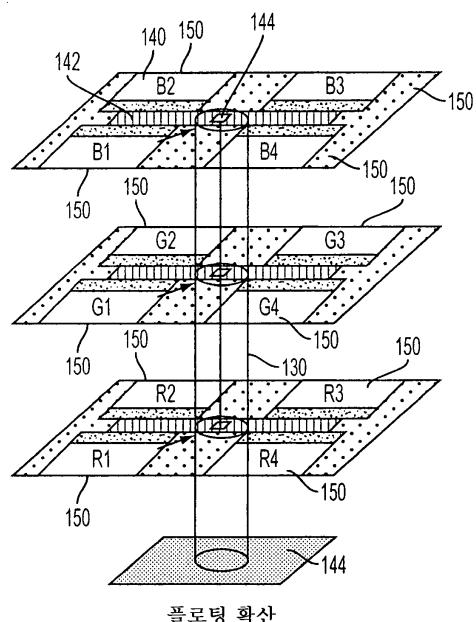

도 11은 이미지 센서의 실시예들에서 픽셀들을 비닝(binning)하는 예를 개념적으로 도시한 도면.

도 12는 이미지 센서의 또 다른 실시예를 도시한 단면도.

도 13은 이미지 센서의 또 다른 실시예를 도시한 단면도.

도 14는 이미지 센서의 또 다른 실시예를 개념적으로 도시한 블록도.

### 발명을 실시하기 위한 구체적인 내용

[0008] 이하의 상세한 설명에서, 본 명세서의 일부를 구성하며, 본 발명이 실시될 수 있는 특정 실시예들을 도시함에 의해 제시하는 첨부된 도면을 참조한다. 이러한 점에서, 다음과 같은 방향성 용어들, "상부(top)", "하부(bottom)", "전면(front)", "후면(back)", "선단(leading)", "후단(trailing)" 등은 설명되는 도면(들)의 방향을 참조하여 사용되었다. 본 발명의 실시예들의 구성요소들이 다수의 상이한 배향들(different orientations)로 위치할 수 있으므로, 방향성 용어는 설명의 목적으로 사용되었으며 본 발명의 범위를 제한하지 않는다. 다른 실시예들이 활용되고 구조적 또는 논리적 변경들이 본 발명의 범위에서 벗어나지 않은 범주에서 가능함은 당연하다. 이하의 상세한 설명은, 따라서, 제한하는 의미로 받아져서는 안되며, 본 발명의 범위는 첨부된 청구항들에 의해 정의된다.

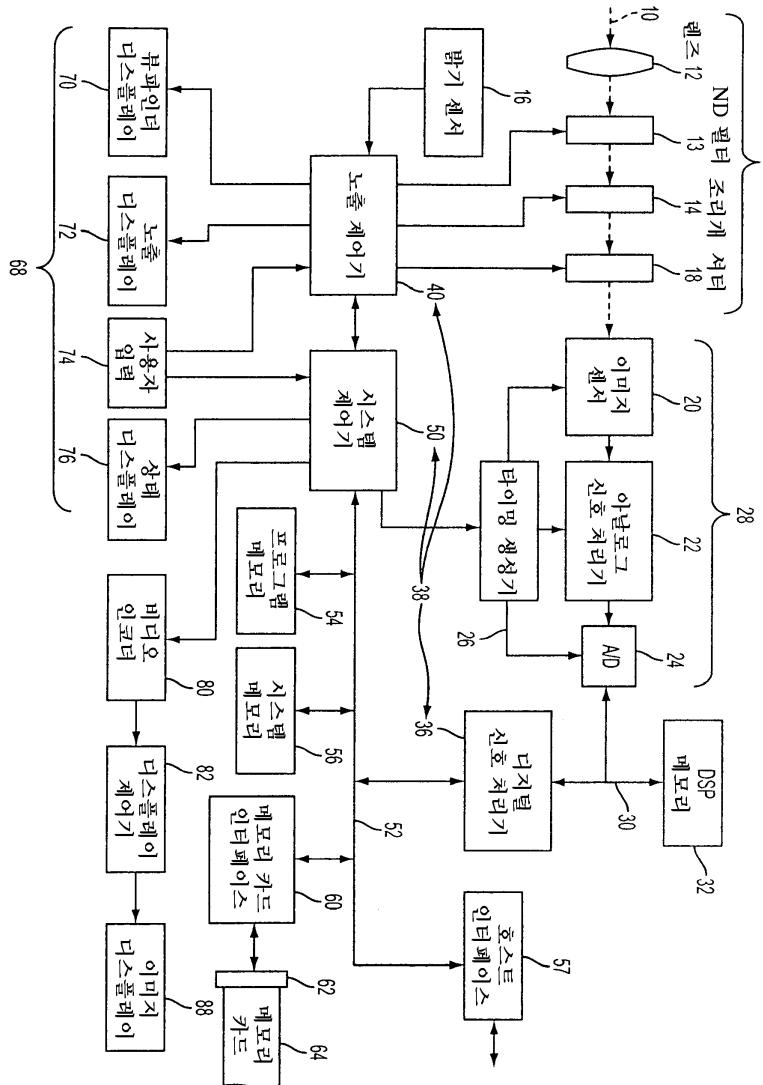

[0009] 도 1로 돌아가면, 본 명세서의 특징들을 사용한 디지털 카메라로 도시된 이미지 캡처 장치의 블록도가 도시되었다. 비록 디지털 카메라가 도시되고 설명되었지만, 본 발명은 명백히 다른 형태의 이미지 캡처 장치들에 적용 가능하다. 개시된 카메라에서, 대상 장면(subject scene)으로부터의 빛(10)은 이미지 스테이지(11)로의 입력이며, 빛은 이미지 센서(20)에서 이미지를 형성하기 위해 렌즈(12)에 의해 초점이 맞춰진다. 이미지 센서(20)는 각 화소(픽셀)를 위해 입사광을 전기 신호로 변환한다. 일부 실시예들에서, 이미지 센서(20)는 능동 화소 센서(active pixel sensor; APS) 타입이다{APS 장치들은 상보성 금속 산화막 반도체(CMOS) 프로세스에서 그들을 제조할 수 있기 때문에 때로는 CMOS 센서들로 언급된다}.

[0010] 센서(20)에 도달하는 빛의 양은 개구(aperture)를 변화시키는 조리개 블록(iris block; 14) 및 광 경로(optical path)에 개재된(interposed) 하나 이상의 ND 필터들(neutral density filters)을 포함하는 ND 필터 블록(13)에 의해 조정된다. 또한 전체적인 빛 수준을 조정하는 것은 셔터 블록(18)이 개방된 시간이다. 노출 제어기 블록(exposure controller block; 40)은 밝기 센서 블록(16)에 의해 계측된 것에 따라 장면에서 이용 가능한 빛의 양에 응답하고 이러한 모든 세 가지의 조정 기능들을 제어한다.

[0011] 특정 카메라 구성의 이러한 설명은 당업자에게 익숙할 것이고, 많은 변경들과 추가적인 특징들이 혼존함이 그러한 당업자에게 자명할 것이다. 예를 들어, 자동 초점 시스템(autofocus system)이 추가되거나, 또는 렌즈가 착탈 가능하고 교체 가능할 수 있다. 대안적인 구성요소들에 의해 유사한 기능이 제공되어, 다양한 유형의 디지

털 카메라들에 본 발명이 적용될 수 있음은 당연하다. 예를 들어, 셔터(18)는 더 복잡한 초점면 장치(focal plane arrangement) 대신에 상대적으로 단순한 이동가능 블레이드 셔터(movable blade shutter)이거나, 또는 그와 유사한 것으로, 디지털 카메라는 상대적으로 단순한 보고 찍는(point and shoot) 디지털 카메라이다. 본 발명의 특징들은 또한 무선 전화기 및 자동차와 같은 비-카메라 장치들에 포함되는 화상 형성 구성요소(imaging components) 상에서 실시될 수 있다.

[0012] 이미지 센서(20)로부터의 아날로그 신호는 아날로그 신호 처리기(22)에 의해 처리되고 A/D 컨버터(analog-to-digital converter; 24)에 적용된다. 타이밍 생성기(timing generator; 26)는 아날로그 신호 처리기(22) 및 A/D 컨버터(24)의 동작을 동기화하고 행들(rows)과 픽셀들을 선택하기 위하여 다양한 클록 신호들(clocking signals)을 생성한다. 이미지 센서 스테이지(28)는 이미지 센서(20), 아날로그 신호 처리기(22), A/D 컨버터(24) 및 타이밍 생성기(26)를 포함한다. 이미지 센서 스테이지(28)의 구성요소들은 분리하여 제조된 접적 회로 들일 수 있고, 또는 CMOS 이미지 센서에서 통상적으로 행해지는 바와 같이 단일 접적 회로로 제조될 수 있다. A/D 컨버터(24)로부터의 디지털 픽셀 값들의 결과적인 스트림은 DSP(digital signal processor; 36)와 연관된 메모리(32)에 저장된다.

[0013] DSP(36)는, 시스템 제어기(50) 및 노출 제어기(40)에 추가하여 도시된 실시예에서 세 개의 처리기들 또는 제어기들 중 하나이다. 비록 이러한 복수의 제어기들 또는 처리기들 사이의 카메라 기능적 제어의 분리는 일반적이지만, 이러한 제어기들 또는 처리기들은 본 발명의 적용과 카메라의 기능적 작동에 영향을 주지 않으며 다양한 방법으로 결합될 수 있다. 이러한 제어기들 또는 처리기들은 하나 이상의 디지털 신호 처리기 장치들, 마이크로제어기들, 프로그램가능 논리 장치들 또는 다른 디지털 논리 회로들을 포함할 수 있다. 비록 그러한 제어기들 또는 처리기들의 조합이 설명되었으나, 모든 필요한 기능들을 수행하기 위하여 하나의 제어기 또는 처리기가 지명될 수 있음을 자명하다. 모든 이러한 변경들은 동일한 기능을 수행할 수 있고 본 발명의 범위 내에서 속하며, 용어 "처리 스테이지(processing stage)"는, 예를 들어, 도 1의 처리 스테이지(38)와 같이, 한 구절(one phrase) 내에서 모든 이러한 기능을 포함하도록 필요에 의해 사용될 것이다.

[0014] 도시된 실시예에서, DSP(36)는 프로그램 메모리(54)에 영구히 저장되고 이미지 캡처 동안 실행을 위해 메모리(32)로 복사되는 소프트웨어 프로그램에 따라 메모리(32)의 디지털 이미지 데이터를 조작한다. DSP(36)는 이미지 처리를 실시하기 위해 필요한 소프트웨어를 실행한다. 메모리(32)는 SDRAM과 같은, 임의의 유형의 RAM을 포함한다. 주소와 데이터 신호를 위한 경로를 포함하는 버스(30)는 DSP(36)를 그것의 연관된 메모리(32), A/D 컨버터(24) 및 다른 연관된 장치들에 연결한다.

[0015] 시스템 제어기(50)는 플래시 EEPROM 또는 다른 비휘발성 메모리를 포함할 수 있는 프로그램 메모리(54)에 저장된 소프트웨어 프로그램에 기초하여 카메라의 전체적인 동작을 제어한다. 이 메모리는 또한 이미지 센서 보정 데이터, 사용자 설정 선택들 및 카메라가 턴-오프(turn-off) 되었을 때 보존되어야 하는 다른 데이터를 저장하는데 사용될 수 있다. 시스템 제어기(50)는 이전에 설명된 바와 같이 렌즈(12), ND 필터(13), 조리개(14) 및 셔터(18)를 동작시키도록 노출 제어기(40)를 지시하고, 이미지 센서(20) 및 연관된 요소들을 동작시키도록 타이밍 생성기(26)를 지시하며, 캡처된 이미지 데이터를 처리하도록 DSP(36)를 지시함에 의해 이미지 캡처 시퀀스를 제어한다. 이미지가 캡처되고 처리된 이후에, 메모리(32)에 저장된 최종 이미지 파일은 인터페이스(57)를 통해 호스트 컴퓨터로 전송되고, 착탈 가능한 메모리 카드(64) 또는 다른 저장 장치에 저장되며, 이미지 디스플레이(88) 상에 사용자를 위해 디스플레이된다.

[0016] 버스(52)는 어드레스, 데이터 및 제어 신호들을 위한 경로를 포함하고, 시스템 제어기(50)를 DSP(36), 프로그램 메모리(54), 시스템 메모리(56), 호스트 인터페이스(57), 메모리 카드 인터페이스(60) 및 다른 연관된 장치들에 연결한다. 호스트 인터페이스(57)는 개인용 컴퓨터(PC) 또는 디스플레이, 저장, 조작 또는 인쇄를 위한 이미지 데이터의 전송을 위한 다른 호스트 컴퓨터로 고속 연결을 제공한다. 이러한 인터페이스는 IEEE1394 또는 USB2.0 직렬 인터페이스 또는 임의의 다른 적합한 디지털 인터페이스이다. 메모리 카드(64)는 일반적으로 소켓(62)에 삽입되고 메모리 카드 인터페이스(60)를 통해 시스템 제어기(50)로 연결되는 CF(compact flash) 카드이다. 사용되는 다른 유형들의 저장소는, 예를 들어, PC-카드, MMC(multimedia card) 또는 SD(secure digital) 카드이다.

[0017] 처리된 이미지들은 시스템 메모리(56) 내의 디스플레이 버퍼로 복사되고 비디오 신호를 생성하도록 비디오 인코더(80)를 통해 연속적으로 판독된다. 이러한 신호는 외부 모니터 상에서 디스플레이되기 위해 직접 카메라로부터 출력되거나, 또는 디스플레이 제어기(82)에 의해 처리되고 이미지 디스플레이(88) 상에 표시된다. 이러한 디스플레이이는 일반적으로 능동 행렬 컬러 액정 디스플레이(active matrix color liquid crystal display)이지

만, 다른 유형의 디스플레이들 또한 사용될 수 있다.

[0018] 뷰파인더 디스플레이(viewfinder display; 70), 노출 디스플레이(72), 상태 디스플레이(76), 이미지 디스플레이(88), 그리고 사용자 입력(74)의 어떠한 조합 또는 모두를 포함하는 사용자 인터페이스는 노출 제어기(40) 및 시스템 제어기(50) 상에서 실행되는 소프트웨어 프로그램의 조합에 의해 제어된다. 사용자 입력(74)은 일반적으로 버튼, 로커 스위치(rocker switch), 조이스틱, 회전 다이얼(rotary dial) 또는 터치스크린의 소정의 조합을 포함한다. 노출 제어기(40)는 빛 계측, 노출 모드, 자동 초점 및 다른 노출 기능들을 동작한다. 시스템 제어기(50)는 하나 이상의 디스플레이들 상에서, 예를 들어, 이미지 디스플레이(88) 상에서 표시되는 GUI(graphical user interface)를 관리한다. GUI는 일반적으로 다양한 옵션을 선택하기 위한 메뉴와 캡처된 이미지 검토를 위한 검토 모드(review mode)를 포함한다.

[0019] 노출 제어기(40)는 노출 모드, 렌즈 개구, 노출 시간(셔터 스피드) 그리고 노출 인덱스(exposure index) 또는 ISO 속도 평가(ISO speed rating)를 선택하는 사용자 입력을 받아들이고 그에 따라서 후속 캡처들을 위해 렌즈 및 셔터를 지시한다. 밝기 센서(16)는 장면의 밝기를 측정하고, ISO 속도 평가, 개구 및 셔터 스피드 설정이 수동인 때 사용자가 참조하도록 노출 계측 기능을 제공한다. 이러한 경우에, 사용자가 하나 이상의 설정을 변경함에 따라, 뷰파인더 디스플레이(70) 상에 표시된 빛 계측 지시자는 어느 정도로 이미지가 노출을 초과하거나 미달할지를 사용자에게 알린다. 자동 노출 모드에서, 사용자는 하나의 설정을 바꾸고 노출 제어기(40)는 정확한 노출을 유지하기 위하여 다른 설정을 자동으로 변경한다. 예를 들어, 임의의 주어진 ISO 속도 평가에 대해 사용자가 렌즈 개구를 감소시킬 때, 노출 제어기(40)는 자동으로 동일한 전체적인 노출을 유지하기 위해 노출 시간을 증가시킨다.

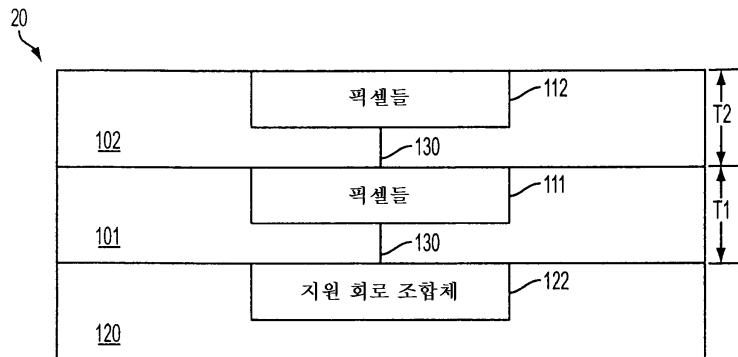

[0020] 도 1에 도시된 이미지 센서(20)는 일반적으로, 각 픽셀에서 들어온 빛을 측정된대로 전기적 신호로 변환하는 방식을 제공하는, 실리콘 기판상에 제조된 빛에 민감한 픽셀들(light sensitive pixels)의 2차원 배열을 포함한다. 도 2를 참조하면, 이미지 센서(20)의 일 실시예의 부분들이 개념적으로 도시되었다.

[0021] 도 2에서, 이미지 센서(20)는 픽셀들의 제1 배열(111)을 구비한 제1 센서층(101)을 포함하는 CMOS 이미지 센서이다. 제2 센서층(102)은 제1 센서층(101) 위에 위치하며, 픽셀들의 제2 배열(112)을 구비한다. 회로층(120)은 제1 및 제2 센서층들(101, 102)의 픽셀 배열들(111, 112)을 위한 지원 회로 조합체(122)와 함께 제1 센서층(101) 아래에 위치한다. 제1 및 제2 층들(101, 102)의 픽셀들(111, 112) 사이의 층간 커넥터들(130) 및 지원 회로 조합체(122)는 각 층 사이에 전기적 연결들을 제공한다. 제1 센서층(101)은 제1의 미리 선택된 파장의 범위에서 빛을 수집하기 위해 두께 T1을 갖고, 제2 센서층은 제2의 미리 선택된 파장의 범위에서 빛을 수집하기 위해 두께 T2를 갖는다. 정규 실리콘 웨이퍼, SOI(silicon on insulator) 웨이퍼 또는 SOS(silicon on sapphire) 웨이퍼들 모두 센서층들(101, 102)을 제조하기에 적합한 물질이다.

[0022] 도 3은 픽셀 배열들(111, 112)의 픽셀(110)의 개념적 부분 블록도이다. 픽셀(110)은 포토다이오드(140)와 같은 광검출기, 그리고 전송 게이트(142)와 같은 전송 메커니즘을 포함한다. 광검출기(140)는 입사광에 반응하여 전하를 수집하고, 전송 게이트(142)는, 광검출기(140)로부터 전하를 받고 전하를 전압 신호로 변환하는 플로팅 확산 감지 노드(floating diffusion sense node; 144)와 같은 전하-전압 메커니즘에 광검출기(140)에서 전하를 전송하도록 기능한다. 앞서 언급된 바와 같이, 픽셀들(110)은 일반적으로 행과 열의 배열로 구성된다. 행 선택 트랜지스터(row select transistor)는 열 버스(column bus)에 결합되며, 픽셀들(110)에서 전하의 판독은 적합한 행 선택 트랜지스터를 활성화함에 의해 원하는 배열의 행을 선택함에 의해 달성되고, 정보는 선택된 행의 열들에서 판독된다.

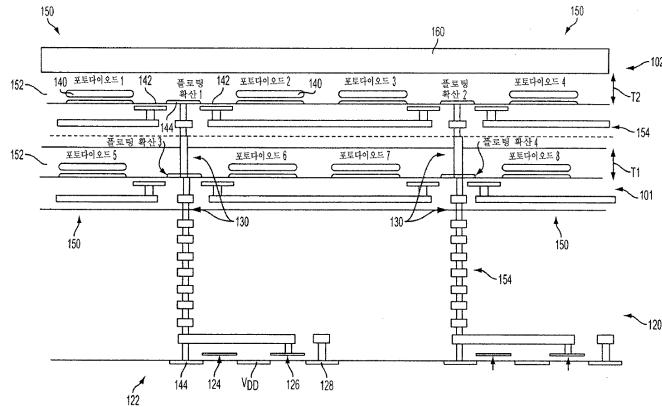

[0023] 일부 실시예들에서, 제1 및 제2 픽셀 배열들(111, 112)의 픽셀들(110)은 픽셀 커널들(pixel kernels; 150)로 조직된다. 도 4a 및 4b는 일부 픽셀 커널 구성들의 예를 도시한다. 도 4a에서, 네 개의 포토다이오드들(140)은 각각 전송 게이트들(142)을 통해 공통 플로팅 확산(common floating diffusion; 144)을 공유하고, 도 4b에서는, 두 개의 포토다이오드들(140)이 공통 플로팅 확산(144)을 공유한다. 도 4a 및 4b에서 도시된 실시예들에서, 층간 커넥터들(130)은 픽셀 커널들(150)의 플로팅 확산들(144)로 결합된다.

[0024] 도 5는 두 센서층(101, 102) 및 회로층(120)을 구비한 이미지 센서의 일 실시예의 특징을 더 도시하는 단면도이다. 각 센서층(101, 102) 및 회로층(120)은 실리콘부(152) 및 하나 이상의 금속층들(154)을 포함한다. 회로층(120)의 지원 회로 조합체(122)는 층간 커넥터들(130)에 의해 대응하는 픽셀 커널에 결합되고 각 픽셀 커널(150)에 대응하는 플로팅 확산(144)을 포함한다. 도 5에 도시된 구조는 추가 금속층(154){전송 게이트(142)에 대응하는 금속층}을 구비하며 웨이퍼 상호접속(wafer interconnection; 130)은 플로팅 확산들(144)을 통해 수행된다. 이러한 것은 동일한 플로팅 확산(144) 상에 픽셀들을 비닝(binning)하는 것을 가능케 한다.

- [0025] 다른 것들 중에서, 지원 회로 조합체(122)는 또한 각 픽셀 커널(150)을 위한 리셋 게이트(reset gate; 124), 전원 공급 VDD, 소스 추종 입력 및 출력(source follower input and output; 126, 128)을 포함한다. 도 5에 도시된 실시예에서, 층간 커넥터들(130)은 집합적인(collective) 플로팅 확산(144)을 형성하기 위하여 회로 웨이퍼, 감지층 T1, 감지층 T2 상의 각 플로팅 확산 노드들(144)을 전기적으로 연결한다.

- [0026] 일반적으로, 실리콘부(152)의 두께를 감소시키는 것은 광학적 간섭(optical interference)을 야기할 수 있으며, 이것은 이어서 양자 효율(quantum efficiency)을 저하시킬 수 있다. 이러한 영향을 완화시키고 양자 효율을 향상시키기 위해, 일부 실시예들에서 반사 방지 막들(antireflection coatings)이 회로층 상부 및 각 감지층들의 양면에 사용되었다. 그러한 반사 방지 막들은 공지되었고, 예를 들어, ONO(silicon oxide - silicon nitride - silicon oxide) 스택들 또는 하프늄 산화물 - 마그네슘 산화물(hafnium oxide - magnesium oxide) 스택들과 같은 단일 층 구조들(single layer structures)에 대해 사용된다. 다른 적합한 반사 방지 막들 또한 사용될 수 있다. 이러한 반사 방지 막들은 감지 및 회로층들이 서로 결합되기 전에 어떠한 일반적인 퇴적 기술을 사용하여 퇴적될 수 있다.

- [0027] 도 6은 층간 연결들(130)이 행 및 열 상호연결들(row and column interconnects)에 의해 구현되어, 행 및 열 회로 조합체(132)를 통해 회로층(120)으로 픽셀들(111)을 연결하는 또 다른 실시예를 도시한다. 추가적인 두 개의 금속층들(154)이 포함되고 웨이퍼 상호연결들(130)은 이미지 영역(imager area)의 외주(periphery)에 위치한 행 및 열 상호연결들을 통해 수행된다. 따라서, 센서층들 상의 각 출력 신호 및 타이밍 라인(timing line)은 회로층(120) 상의 열 또는 행 회로 조합체(132)로 상호연결들(130)과 전기적으로 결합한다. 도시된 실시예들에서, 표준 CMOS 디지털 및 아날로그 회로 조합체는 센서층들(101, 102) 및/또는 회로 웨이퍼(120)의 이미지 영역 외부에 위치한다.

- [0028] 도 5 및 도 6에 도시된 실시예들에서, 컬러 필터 배열(color filter array; CFA; 160)은 센서층(102) 상부에 위치한다. 실리콘부들(silicon portions; 152) 또는 제1 및 제2 센서층들(101, 102)은 상이한 두께들 T1, T2를 구비하여, 각 층이 미리 결정된 파장의 범위에서 빛을 수집하도록 한다. 예를 들어, 센서층들의 두께는 주로 청색광(blue light)을 수집하기 위하여 약  $0.5 \mu\text{m}$ , 주로 녹색광(green light)을 수집하기 위하여 약  $1.3 \mu\text{m}$  및/또는 주로 적색광(red light)을 수집하기 위하여 약  $3.0 \mu\text{m}$  일 수 있다. 두 개의 미리 결정된 색들을 수집하도록 설정된 제1 및 제2 두께들 T1, T2를 이용하여, CFA(160)의 몇몇 층들에 대한 필요성이 제거되었다.

- [0029] 더욱 상세하게, 층 두께들 T1, T2를 갖는 두 개의 센서층들(101, 102)을 구비한 도 5 및 도 6에 도시된 실시예들은 CFA(160)의 두 개의 층들에 대한 필요성을 제거한다. 도 7 및 도 8은 두 상보적 CFA들(160)의 예들을 도시하며, Y는 노란색(yellow), M는 자홍색(magenta), P는 전색(panchromatic)을 나타낸다. 상부 센서층(102)의 실리콘 두께 T2는 도시된 실시예에서 약  $2 \mu\text{m}$ 이다.

- [0030] 도 9 및 도 10에 도시된 실시예들은 각각 추가적 센서층(103)을 포함한다. 도 9에서, 층간 연결들(130)은 플로팅 확산들(144)을 연결하고, 도 10에서, 층간 연결들(130)은 행 및 열 회로 조합체(132)를 이용하여 만들어진다. 도 9 및 도 10에서, 제3 센서층의 실리콘 두께 T3는 주로 청색광을 수집하기 위해 약  $0.5 \mu\text{m}$ 이고, 제2 센서층(102)의 실리콘 두께 T2는 주로 녹색광을 수집하기 위해 약  $1.3 \mu\text{m}$ 이며, 제1 센서층의 실리콘 두께 T1은 주로 적색광을 수집하기 위해 약  $3 \mu\text{m}$ 이다. 그러한 센서는 양자 효율을 감소시키는 것으로 알려진, 색을 검출하기 위한 파장 선택적 필터들(wavelength selective filters)을 요구하지 않는다.

- [0031] 이러한 구조는 또한 공통 플로팅 확산 상에 픽셀들을 비닝하는 복수의 방법들을 가능케 한다. 각 픽셀 커널(150) 내의 포토다이오드들(140)의 수에 기초하여, 셋 또는 그 이상의 포토다이오드들(140)은 동일한 전기적 상호연결(130)로 연결될 수 있다. 이것은 픽셀들(110)의 비닝의 복수의 방법들을 가능케 한다. 예를 들어, 도 11에 도시된 바와 같이, 포토다이오드들 B1, G1 및 R1을 위한 전송 게이트들(142)은 공통 플로팅 확산(142) 상으로 전하를 전송하고 비닝 전색 신호(binned panchromatic signal)를 생성하도록 활성화될 수 있다. 유사하게, 단일 색 층(single color layer)에서, 픽셀 커널(150) 내의 각 포토다이오드(110)를 위한 전송 게이트들(142)은 모든 색 신호들을 비닝하고 더 낮은 공간 해상도에서 더 높은 감응도 출력을 생성하도록 활성화될 수 있다. 예를 들어, 모든 네 개의 적색 픽셀들(R1+R2+R3+R4)을 비닝하는 것은 단일의 큰 (높은 감응도) 적색 픽셀{single large (high sensitivity) red pixel}처럼 기능한다. 다른 것들은 제외한 하나의 색 중심면(color plane)에서 색 응답(color response)을 위해 공간 해상도를 희생하는 선택 또한 존재한다. 예를 들어, 네 개의 적색 픽셀들은 함께 비닝될 수 있으나, 개별 포토다이오드 데이터는 녹색 채널에 보존된다(preserved). 또 다른 선택은 모든 포토다이오드들{예를 들어, 도 11의 모든 12개의 포토다이오드들(네 개의 청색 픽셀들 B1-B4, 네 개의 녹색 픽셀들 G1-G4, 네 개의 적색 픽셀들 R1-R4)}을 공유된 플로팅 확산(144) 상으로 비닝하는 것일 수

있다. 이것은 적층된 커널(stacked kernel)을 위한 높은 감응성, 낮은 공간 해상도 전색 신호를 생성할 수 있다. 이러한 경우에 색 분리(color separation)는 근처의 커널들에서 색 분리를 보존하는 것에 의해 달성될 수 있다.

[0032] 도 12는 두 개의 센서층들(101, 102) 및 감지 요소들을 포함하는 회로층(120)을 포함하는 또 다른 실시예를 도시한다. 이러한 구조는 도 9 및 도 10에 도시된 실시예들과 비교하여 여전히 세 개의 센서층들을 제공하면서도 하나 적은 웨이퍼를 요구한다. 따라서, 회로층(120)은 지원 회로 조합체에 추가하여 픽셀들(110)을 포함한다. 회로층(120) 및 두 센서층(101, 102)의 실리콘 두께 T1, T2, T3는 각 층이 미리 결정된 파장의 범위에서 빛을 수집하도록 한다. 비록 유사한 실시예들에서 연결들은 플로팅 확산(144)을 통해 만들어졌으나, 도 12에서, 층간 연결들(130)은 행 및 열 회로 조합체(132)를 통해 만들어진다.

[0033] 도 13은 한 개의 센서층(101) 및 감지 요소들을 포함하는 회로층(120)을 구비한 일 실시예를 도시한다. 비록 본 명세서의 다른 실시예들에서 개시된 바와 같이 연결들은 대안적으로 행 및 열 회로 조합체를 통해 만들어질 수 있지만, 도 13에 도시된 실시예는 플로팅 확산들(144)을 통한 층간 연결들(130)을 구비한다. 센서층(101) 및 회로층(120)은 층이 미리 결정된 파장의 범위에서 빛을 수집하도록 각각 실리콘 두께 T1, T2를 구비한다. 도 5 및 도 6에 도시된 실시예들과 같이, 도 7 및 도 8에 도시된 것과 같은 상보적 CFA(160)가 제3 색을 필터링 하기 위하여 제공된다.

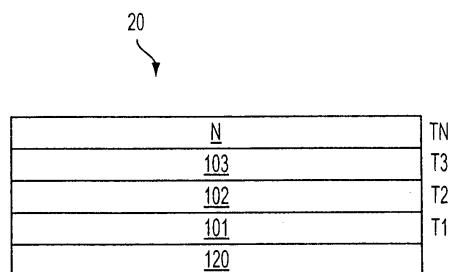

[0034] 도 14는 네 개 이상의 감지층들(101-N)을 구비한 또 다른 실시예를 개념적으로 도시하며, 대응되는 파장의 범위를 갖는 빛을 수집하기 위하여 각 층은 미리 결정된 두께를 갖는다. 이러한 구조는 가시 스펙트럼(visible spectrum)을 넘어 감응도의 확장을 가능케 한다. 상부 세 개의 층은, 예를 들어, 도 9 및 도 10에 도시된 실시예들에 기술된 바와 같이, 가시 주파수 범위(visible frequency range)의 빛을 캡처할 책임을 질 것이며, 추가 층들(N)은 적외선 광을 캡처하는데 사용될 수 있다.

[0035] 본 발명은 임의의 바람직한 실시예들에 대한 특정 참조와 함께 상세하게 설명되었으나, 본 발명의 범위 내에서 변형 및 변경이 행해질 수 있음을 당연하다.

## 부호의 설명

[0036] 10 : 빛

11 : 이미징 스테이지

12 : 렌즈

13 : ND 필터 블록

14 : 조리개 블록

16 : 밝기 센서 블록

18 : 셔터 블록

20 : 이미지 센서

22 : 아날로그 신호 처리기

24 : A/D 컨버터

26 : 타이밍 생성기

28 : 이미지 센서 스테이지

30 : 버스

32 : 메모리

36 : 디지털 신호 처리기 (DSP)

38 : 처리 스테이지

40 : 노출 제어기

- 50 : 시스템 제어기

52 : 버스

54 : 프로그램 메모리

56 : 시스템 메모리

57 : 호스트 인터페이스

60 : 메모리 카드 인터페이스

62 : 소켓

64 : 메모리 카드

70 : 뷰파인더 디스플레이

72 : 노출 디스플레이

74 : 사용자 입력

76 : 상태 디스플레이

80 : 비디오 인코더

82 : 디스플레이 제어기

88 : 이미지 디스플레이

101 : 제1 센서층

102 : 제2 센서층

103 : 제3 센서층

110 : 픽셀

111 : 제1 픽셀 배열

112 : 제2 픽셀 배열

120 : 회로층

122 : 지원 회로 조합체

124 : 리셋 게이트

126 : 소스 추종 입력

128 : 소스 추종 출력

130 : 층간 커넥터들

132 : 행 및 열 회로 조합체

140 : 포토다이오드

142 : 전송 게이트

144 : 플로팅 확산

150 : 픽셀 커널

152 : 실리콘층

154 : 금속층

160 : 컬러 필터 배열 (CFA)

T1 : 제1 두께

T2 : 제2 두께

T3 : 제3 두께

V<sub>DD</sub> : 전원 공급

도면

도면1

## 도면2

## 도면3

## 도면4a

도면4b

도면5

도면6

도면7

|   |   |

|---|---|

| P | Y |

| M | P |

도면8

도면9

도면10

도면11

플로팅 화산

도면12

도면13

도면14