(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5303669号 (P5303669)

(45) 発行日 平成25年10月2日(2013.10.2)

(24) 登録日 平成25年6月28日 (2013.6.28)

(51) Int.Cl. F L

**GO9F 9/30 (2006.01)** GO9F 9/30 338 **HO1L 51/50 (2006.01)** HO5B 33/14 A

請求項の数 5 (全 23 頁)

最終頁に続く

特願2012-112328 (P2012-112328) ||(73)特許権者 000153878 (21) 出願番号 (22) 出願日 平成24年5月16日 (2012.5.16) 株式会社半導体エネルギー研究所 (62) 分割の表示 特願2010-61796 (P2010-61796) 神奈川県厚木市長谷398番地 (72) 発明者 の分割 山崎 舜平 平成15年5月19日 (2003.5.19) 神奈川県厚木市長谷398番地 株式会社 原出願日 特開2012-185514 (P2012-185514A) 半導体エネルギー研究所内 (65) 公開番号 (43) 公開日 平成24年9月27日 (2012.9.27) (72) 発明者 高山 徹 平成24年6月12日 (2012.6.12) 神奈川県厚木市長谷398番地 株式会社 審査請求日 (31) 優先権主張番号 特願2002-143711 (P2002-143711) 半導体エネルギー研究所内 (32) 優先日 平成14年5月17日 (2002.5.17) ||(72)発明者 村上 智史 (33) 優先権主張国 日本国(JP) 神奈川県厚木市長谷398番地 株式会社 半導体エネルギー研究所内 |(72)発明者 木村 肇 神奈川県厚木市長谷398番地 株式会社 半導体エネルギー研究所内

(54) 【発明の名称】表示装置

### (57)【特許請求の範囲】

### 【請求項1】

半導体を有し、

前記半導体の上方に絶縁膜を有し、

前記絶縁膜の上方に第1の導電膜を有し、

前記第1の導電膜の上方に第1の窒化シリコン膜を有し、

前記第1の窒化シリコン膜の上方に有機樹脂膜を有し、

前記有機樹脂膜の上方に第2の窒化シリコン膜を有し、

前記第2の窒化シリコン膜の上方に第2の導電膜を有し、

前記第1の窒化シリコン膜は第1の開口部を有し、

前記有機樹脂膜は第2の開口部を有し、

前記第2の窒化シリコン膜は第3の開口部を有し、

前記半導体は、第1の領域と第2の領域と第3の領域とを有し、

<u>前記第1の領域は、トランジスタの第1のチャネル形成領域として機能することができ</u>る領域であり、

前記第2の領域は、前記トランジスタの第2のチャネル形成領域として機能することができる領域であり、

前記第3の領域は、前記トランジスタのソース領域又は前記トランジスタのドレイン領域の一方として機能することができる領域であり、

前記第1の導電膜は、前記第1の領域と重なる領域を有し、

前記第1の導電膜は、前記第2の領域と重なる領域を有し、

前記第2の導電膜は、前記第1の開口部と前記第2の開口部と前記第3の開口部とを介して前記第3の領域と電気的に接続されており、

前記第2の窒化シリコン膜は、前記第2の開口部の内側に、前記第1の窒化シリコン膜と重なる領域を有することを特徴とする表示装置。

## 【請求項2】

半導体を有し、

前記半導体の上方に絶縁膜を有し、

前記絶縁膜の上方に第1の導電膜を有し、

前記絶縁膜の上方に第3の導電膜を有し、

前記第1の導電膜の上方と前記第3の導電膜の上方とに第1の窒化シリコン膜を有し、

前記第1の窒化シリコン膜の上方に第4の導電膜を有し、

前記第1の窒化シリコン膜の上方に第5の導電膜を有し、

前記第4の導電膜の上方と前記第5の導電膜の上方とに有機樹脂膜を有し、

前記有機樹脂膜の上方に第2の窒化シリコン膜を有し、

前記第2の窒化シリコン膜の上方に第2の導電膜を有し、

前記第1の窒化シリコン膜は第1の開口部を有し、

前記有機樹脂膜は第2の開口部を有し、

前記第2の窒化シリコン膜は第3の開口部を有し、

前記半導体は、第1の領域と第2の領域と第3の領域と第4の領域とを有し、

前記第1の領域は、トランジスタの第1のチャネル形成領域として機能することができる領域であり、

<u>前記第2の領域は、前記トランジスタの第2のチャネル形成領域として機能することが</u>できる領域であり、

前記第3の領域は、前記トランジスタのソース領域又は前記トランジスタのドレイン領域の一方として機能することができる領域であり、

<u>前記第4の領域は、前記トランジスタのソース領域又は前記トランジスタのドレイン領域の他方として機能することができる領域であり、</u>

前記第1の導電膜は、前記第1の領域と重なる領域を有し、

前記第1の導電膜は、前記第2の領域と重なる領域を有し、

前記第2の導電膜は、前記第1の開口部と前記第2の開口部と前記第3の開口部とを介して前記第3の領域と電気的に接続されており、

前記第3の導電膜は、容量素子の一方の電極として機能することができる領域を有し、 前記第4の導電膜は、前記容量素子の他方の電極として機能することができる領域を有 し、

前記第5の導電膜は、前記第4の領域と電気的に接続されており、

前記第2の窒化シリコン膜は、前記第2の開口部の内側に、前記第1の窒化シリコン膜と重なる領域を有することを特徴とする表示装置。

### 【請求項3】

半導体を有し、

前記半導体の上方に絶縁膜を有し、

前記絶縁膜の上方に第1の導電膜を有し、

前記第1の導電膜の上方にパッシベーション膜を有し、

前記パッシベーション膜の上方に平坦化膜を有し、

前記平坦化膜の上方にバリア膜を有し、

前記バリア膜の上方に第2の導電膜を有し、

前記パッシベーション膜は第1の開口部を有し、

前記平坦化膜は第2の開口部を有し、

前記バリア膜は第3の開口部を有し、

前記半導体は、第1の領域と第2の領域と第3の領域とを有し、

10

20

30

40

<u>前記第1の領域は、トランジスタの第1のチャネル形成領域として機能することができ</u>る領域であり、

<u>前記第2の領域は、前記トランジスタの第2のチャネル形成領域として機能することが</u>できる領域であり、

前記第3の領域は、前記トランジスタのソース領域又は前記トランジスタのドレイン領域の一方として機能することができる領域であり、

前記第1の導電膜は、前記第1の領域と重なる領域を有し、

前記第1の導電膜は、前記第2の領域と重なる領域を有し、

前記第2の導電膜は、前記第1の開口部と前記第2の開口部と前記第3の開口部とを介して前記第3の領域と電気的に接続されており、

前記バリア膜は、前記第2の開口部の内側に、前記パッシベーション膜と重なる領域を有することを特徴とする表示装置。

#### 【請求項4】

半導体を有し、

前記半導体の上方に絶縁膜を有し、

前記絶縁膜の上方に第1の導電膜を有し、

前記絶縁膜の上方に第3の導電膜を有し、

前記第1の導電膜の上方と前記第3の導電膜の上方とにパッシベーション膜を有し、

前記パッシベーション膜の上方に第4の導電膜を有し、

前記パッシベーション膜の上方に第5の導電膜を有し、

前記第4の導電膜の上方と前記第5の導電膜の上方とに平坦化膜を有し、

前記平坦化膜の上方にバリア膜を有し、

前記バリア膜の上方に第2の導電膜を有し、

前記パッシベーション膜は第1の開口部を有し、

前記平坦化膜は第2の開口部を有し、

前記バリア膜は第3の開口部を有し、

前記半導体は、第1の領域と第2の領域と第3の領域と第4の領域とを有し、

前記第1の領域は、トランジスタの第1のチャネル形成領域として機能することができる領域であり、

<u>前記第2の領域は、前記トランジスタの第2のチャネル形成領域として機能することが</u>できる領域であり、

前記第3の領域は、前記トランジスタのソース領域又は前記トランジスタのドレイン領域の一方として機能することができる領域であり、

前記第4の領域は、前記トランジスタのソース領域又は前記トランジスタのドレイン領域の他方として機能することができる領域であり、

前記第1の導電膜は、前記第1の領域と重なる領域を有し、

前記第1の導電膜は、前記第2の領域と重なる領域を有し、

前記第2の導電膜は、前記第1の開口部と前記第2の開口部と前記第3の開口部とを介して前記第3の領域と電気的に接続されており、

前記第3の導電膜は、容量素子の一方の電極として機能することができる領域を有し、 前記第4の導電膜は、前記容量素子の他方の電極として機能することができる領域を有 し、

前記第5の導電膜は、前記第4の領域と電気的に接続されており、

前記バリア膜は、前記第2の開口部の内側に、前記パッシベーション膜と重なる領域を有することを特徴とする表示装置。

## 【請求項5】

請求項1乃至請求項4のいずれか一項において、

前記半導体は、半導体膜又はシリコンウェルであることを特徴とする表示装置。

### 【発明の詳細な説明】

## 【技術分野】

20

10

30

30

40

#### [00001]

本発明は、半導体素子(代表的にはトランジスタ)をデバイスとして用いた表示装置、特にエレクトロルミネセンス表示装置に代表される発光装置に係る技術分野及び該表示装置を画像表示部に備えた電子機器に係る技術分野に属する。

### 【背景技術】

#### [0002]

近年、基板上にトランジスタ(特に薄膜トランジスタ)を集積化してなる液晶表示装置やエレクトロルミネセンス(Electro Luminescence)表示装置の開発が進んでいる。これらの表示装置は、いずれもガラス基板上に薄膜形成技術を用いてトランジスタを作り込み、そのトランジスタをマトリクス配列された各画素に配置し、画像表示を行う表示装置として機能させることを特徴とする。

#### [0003]

表示装置の画像表示を行う領域(以下、画素部という。)に要求される仕様は様々であるが、まずドット数が多くて高精細であること、各画素の有効表示領域の面積が大きく明るい画像表示が可能なこと、そして、画素部の全域に渡って点欠陥や線欠陥を誘因するような不良がないこと、等が挙げられる。これらの仕様を満たすためには、各画素に配置されるトランジスタの性能が良いことだけでなく、安定したプロセスで歩留まり良くトランジスタを形成できる技術が必要である。

#### [0004]

また、エレクトロルミネセンス表示装置の中でも有機エレクトロルミネセンス表示装置は、発光源となる発光素子に有機化合物を用いるため、有機化合物の劣化を抑制するための工夫が信頼性確保にあたって重要課題となる(例えば、特許文献 1 参照。)。即ち、信頼性の高い表示装置を得るためには、作製途中のみならず、完成後の経時劣化までも考慮して信頼性対策を施しておく必要がある。

## 【先行技術文献】

### 【特許文献】

#### [0005]

【特許文献 1 】特開 2 0 0 1 - 2 0 3 0 7 6 号公報

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0006]

本発明は、エレクトロルミネセンス表示装置に代表される発光装置において、発光素子の劣化を極力抑えるための構造を提供すると共に、各画素に必要とされる容量素子(コンデンサ)を十分に確保するための構造を提供することを課題とする。

## 【課題を解決するための手段】

#### [0007]

本発明の要旨は、前掲の課題を解決する手段として、平坦化膜の経時変化による影響を防ぐための手段及び開口率を損なうことなく大きな電荷保持特性を有する手段を備えたことを特徴とする表示装置である。即ち、トランジスタを覆う平坦化膜を窒化シリコン膜等の緻密な絶縁膜で封入することにより、その経時変化(脱ガス等)を防ぎ、さらに多層配線のメリットを活用して積層構造の容量素子を設けることにより、開口率を損なうことなく電荷保持特性の良い容量素子を含む画素を備えたことを特徴とする。

### [0008]

なお、ここで発光素子とは、一対の電極(陽極及び陰極)の間に発光体(発光層、キャリア注入層、キャリア輸送層、キャリア阻止層その他の発光に必要な有機化合物もしくは無機化合物を積層してなる積層体を指す。)を設けた素子をいう。例えば、エレクトロルミネセンス素子は、発光素子に該当する。

#### [0009]

具体的には、本発明は、半導体、該半導体上のゲート絶縁膜、該ゲート絶縁膜上の第1 の金属層、前記半導体の上方に設けられた第1パッシベーション膜、該第1パッシベーシ 10

20

30

40

ョン膜上の第2の金属層、該第2の金属層上の平坦化膜、該平坦化膜上のバリア膜及び該バリア膜上の第3の金属層を有する表示装置であって、 前記平坦化膜に設けられた第1 開口部の側面が前記バリア膜に覆われると共に、前記第1開口部の内側に前記ゲート絶縁膜、前記第1パッシベーション膜及び前記バリア膜を含む積層体に設けられた第2開口部を有し、かつ、前記第3の金属層は、前記第1開口部及び第2開口部を介して前記半導体に接続され、 前記半導体、前記ゲート絶縁膜及び前記第1の金属層で構成される第1容量素子と、前記第1の金属層、前記第1パッシベーション膜及び前記第2の金属層で構成される第2容量素子とを備えたことを特徴とする。

### [0010]

また、上記本発明において、容量素子の構成は、前記半導体、前記ゲート絶縁膜及び前記第1の金属層で構成される第1容量素子と、前記第1の金属層、前記第1パッシベーション膜及び前記第2の金属層で構成される第2容量素子と、前記第2の金属層、前記バリア膜及び前記第3の金属で構成される第3容量素子とを備えたことを特徴とする構成であれば、さらに電荷保持特性を良好なものとすることができる。

#### [0011]

また、上記本発明において、容量素子の構成は、前記半導体、前記ゲート絶縁膜及び前記第1の金属層で構成される第1容量素子と、前記第1の金属層、前記第1パッシベーション膜、前記バリア膜及び前記第3の金属層で構成される第2容量素子とを備えたことを特徴とするものであっても良い。

## [0012]

また、上記本発明において、容量素子の構成は、前記半導体、前記ゲート絶縁膜、前記第 1 パッシベーション膜、前記バリア膜及び前記第 3 の金属層で構成される容量素子を備えたことを特徴とするものであっても良い。

## [ 0 0 1 3 ]

また、上記本発明において、容量素子の構成は、前記半導体、前記ゲート絶縁膜、前記第 1 パッシベーション膜及び前記第 2 の金属層で構成される容量素子を備えたことを特徴とするものであっても良い。

#### [0014]

また、上記本発明において、容量素子の構成は、前記第1の金属層、前記第1パッシベーション膜及び前記第2の金属層で構成される容量素子を備えたことを特徴とするものであっても良い。

## [0015]

以下、本発明の表示装置に係る実施の形態について、図面等を参照しながら詳細な説明を行う。

## 【発明の効果】

### [0016]

本発明により、第1に、平坦化膜が第1パッシベーション膜及びバリア膜により封入されているため、平坦化膜からの脱ガス等による経時劣化の問題がなく、信頼性の高い表示装置を得ることができる。また、第2に、容量素子を積層形成することにより少ない面積で大きな容量値を確保できる。また、第3に、図2(B)に示した特殊な構造の画素電極を発光素子の陽極として用いることにより光取り出し効率を高め、輝度が高く明るいエレクトロルミネセンス表示装置とすることができると共に、低消費電力化することにより発光素子の劣化の進行度を抑え、信頼性を高くすることができる。

## [0017]

以上のように、本発明の表示装置は、多層配線を活用することにより各画素に必要とされる容量値(電荷保持用の容量値)を十分な大きさで確保し、かつ、発光素子の劣化を極力抑えるための構造とすることで信頼性が高く輝度の高い表示装置となる。

## 【図面の簡単な説明】

#### [ 0 0 1 8 ]

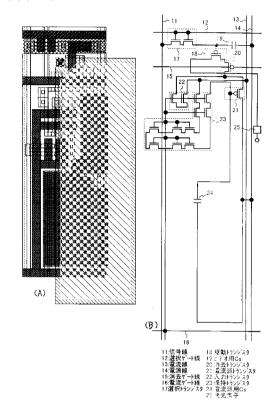

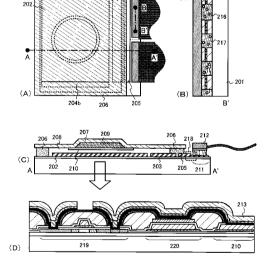

【図1】表示装置の画素構成を示す上面図及び回路図。

10

30

20

40

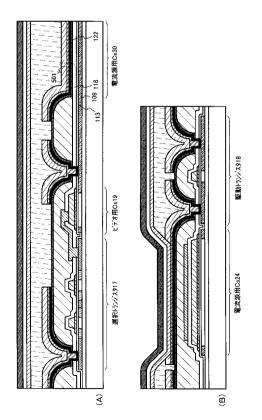

- 【図2】表示装置のデバイス構成を示す断面図。

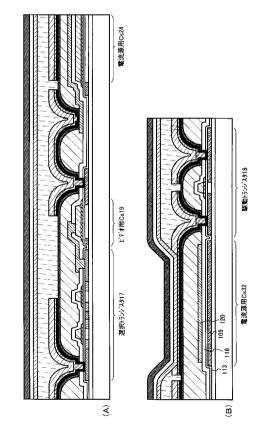

- 【図3】表示装置のデバイス構成を示す断面図。

- 【図4】表示装置のデバイス構成を示す断面図。

- 【図5】表示装置のデバイス構成を示す断面図。

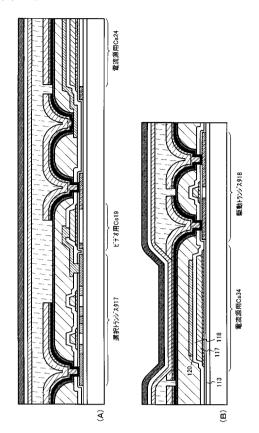

- 【図6】表示装置のデバイス構成を示す断面図。

- 【図7】表示装置のデバイス構成を示す断面図。

- 【図8】表示装置の画素構成を示す上面図及び回路図。

- 【図9】表示装置の外観を示す上面図及び断面図。

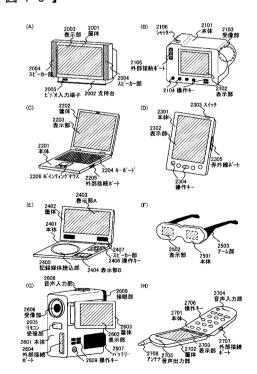

- 【図10】電子機器の一例を示す図。

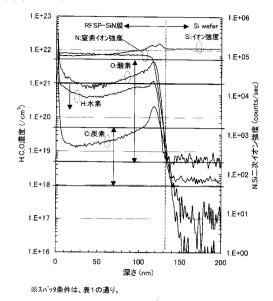

- 【図11】窒化シリコン膜中の不純物分布を示す図。

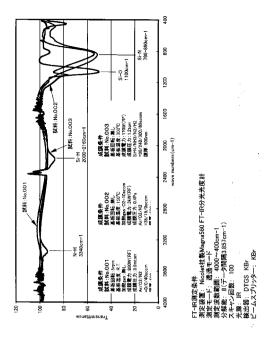

- 【図12】窒化シリコン膜のFT-IR測定結果を示す図。

- 【図13】窒化シリコン膜の透過率を示す図。

- 【図14】窒化シリコン膜のC-V特性を示す図。

- 【図15】窒化シリコン膜のC-V特性を示す図。

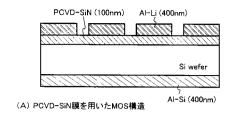

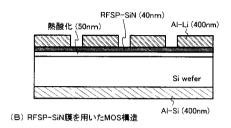

- 【図16】窒化シリコン膜を用いたMOS構造の断面図。

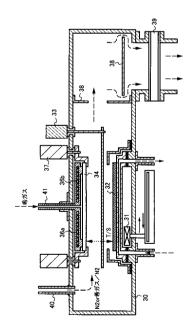

- 【図17】窒化シリコン膜の成膜に用いるスパッタ装置を示す図。

【発明を実施するための形態】

## [0019]

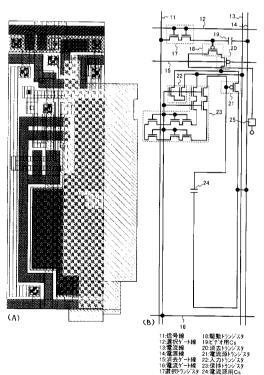

[実施の形態1] 本実施の形態は、本発明のエレクトロルミネセンス表示装置の一例である。図1において、図1(A)は、エレクトロルミネセンス表示装置の一画素における上面回路図(CAD図面)であり、図1(B)はその回路構成を模式的に現した回路図である。図1(B)に示すエレクトロルミネセンス表示装置の各画素は、信号線11、選択ゲート配線12、電流線13、電源線(定電圧もしくは定電流を供給する配線)14、消去ゲート線15及び電流ゲート線16を有し、各画素には選択トランジスタ17、駆動トランジスタ18、ビデオ用Cs(ビデオ用の容量素子)19、消去トランジスタ20、電流源トランジスタ21、入力トランジスタ22、保持トランジスタ23、電流源用Cs(電流源用の容量素子)24及び発光素子25が設けられている。なお、本実施の形態に示す画素の回路構成については、本出願人による特願2001-289983号明細書に記載されており、本出願人の発明による新規な構成である。

## [0020]

本実施の形態のエレクトロルミネセンス表示装置の特徴として、光取り出しがトランジスタを形成した基板とは逆向きに行われるため、画素電極(陽極もしくは陰極)の下に如何なる回路を組み込んでも開口率((画素面積に対して実効的な表示領域の占める割合))の面積を低下させることがないという点である。勿論、本発明の適用は、図1(A)、(B)に示した構成に限定されるものではなく、他の回路構成への適用は当業者が適宜行えば良い。

## [0021]

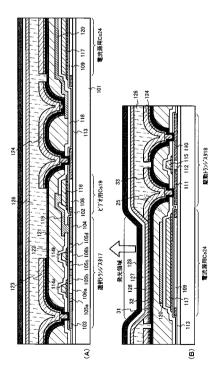

次に、図1(A)、(B)に示したエレクトロルミネセンス表示装置の一画素における代表的な断面構造を図2(A)、(B)に示す。図2(A)の断面図は、選択トランジスタ17及び電流源用Cs(電流源用容量素子)14の断面図、図2(B)は、電流源用Cs24及び駆動トランジスタ18の断面図である。

#### [0022]

図2(A)において、101は基板であり、ガラス基板、セラミック基板、石英基板、シリコン基板もしくはプラスチック基板(プラスチックフィルムを含む。)を用いることができる。また、102は窒化酸化シリコン膜、酸化窒化シリコン膜もしくはこれらの積層膜からなる下地膜である。さらに、下地膜102の上には、選択トランジスタ17の活性層となる半導体が設けられ、該活性層は、ソース領域103、ドレイン領域104、LDD領域105a~105d及びチャネル形成領域106a、106bを有し、ソース領域103とドレイン領域104の間に、二つのチャネル形成領域及び四つのLDD領域を有している。このとき同時に、ビデオ用Cs19の下方電極108、電流源用Cs24の

10

20

30

40

下方電極 1 0 9、駆動トランジスタ 1 8 の活性層を構成するソース領域 1 1 0 、ドレイン 領域 1 1 1 及びチャネル形成領域 1 1 2 が形成される。

#### [0023]

なお、選択トランジスタ 1 7 のソース領域 1 0 3 、ドレイン領域 1 0 4 及び L D D 領域 1 0 5 a ~ 1 0 5 d は n 型不純物領域であり、駆動トランジスタ 1 8 のソース領域 1 1 0 及びドレイン領域 1 1 1 は p 型不純物領域である。また、選択トランジスタ 1 7 のチャネル形成領域 1 0 6 a 及び 1 0 6 b 、駆動トランジスタ 1 8 のチャネル形成領域 1 1 2 、ビデオ用 C s 1 9 の第 1 電極(下方側電極) 1 0 8 並びに電流源用 C s 2 4 の第 1 電極(下方側電極) 1 0 9 は真性(いわゆる i 型)の半導体である。

#### [0024]

これら半導体上には、酸化シリコン膜、酸化窒化シリコン膜(Siが25~35原子%、酸素が55~65原子%、窒素が1~20原子%、水素が0.1~10原子%で含まれるシリコン化合物膜をいう。以下、同じ。)、窒化アルミニウム膜、酸化アルミニウム膜、酸化窒化アルミニウム膜もしくはこれらの絶縁膜と窒化シリコン膜との積層膜を用いたゲート絶縁膜113が設けられる。ゲート絶縁膜113は、選択トランジスタ17及び駆動トランジスタ18のゲート絶縁膜として機能すると共に、ビデオ用Cs19の誘電体及び電流源用Cs24の第1誘電体(下方側誘電体)を兼ねる。

## [0025]

ゲート絶縁膜113上には、第1の金属層をパターン加工して、選択トランジスタ17のゲート電極114a及び114b、駆動トランジスタ18のゲート電極115が設けられる。なお、各ゲート電極は、一層目の電極(窒化タンタル膜)と二層目の電極(タングステン膜)の形状が異なり、一層目の電極の方が二層目の電極よりも線幅が広くなっている。この特徴の形成方法並びにこのような構造のゲート電極とした理由及び利点等については、本出願人による特開2002-57162号公報を参照すれば良い。また、ゲート電極の形成と同時に、ビデオ用Cs19の第2電極(上方側電極)116及び電流源用Cs24の第2電極(中間電極)117が設けられる。

#### [0026]

これらゲート電極及び C s 用電極上には、第 1 パッシベーション膜 1 1 8 として、窒化酸化シリコン膜 ( S i が 2 5 ~ 3 5 原子%、酸素が 1 5 ~ 3 0 原子%、窒素が 2 0 ~ 3 5 原子%、水素が 1 5 ~ 2 5 原子%で含まれるシリコン化合物膜をいう。以下、同じ。)もしくはプラズマ C V D 法で形成された窒化シリコン膜を O . 1 ~ 1  $\mu$  m (好ましくは、 O . 2 ~ O . 5  $\mu$  m) で設ける。この第 1 パッシベーション膜 1 1 8 は、水素を 1 5 ~ 2 5 原子%の濃度で含むため、加熱による水素供給源として機能させ、活性層となる半導体の水素終端を行うことができる。また、同時に、電流源用 C s 2 4 において、第 2 誘電体(上方側誘電体)として機能する。

### [0027]

第1パッシベーション膜118上には、第2の金属層をパターン加工して、選択トランジスタ17のドレイン配線119及び電流源用Cs24の第3電極(上方側電極)120が設けられる。ドレイン配線119は、選択トランジスタ17のドレイン領域104とビデオ用Cs19の第2電極116とを電気的に接続する。なお、第2の金属層としては、如何なる金属膜を用いても良いが、低抵抗なアルミニウム膜もしくは銅薄膜(銅合金膜を含む。)を用いることが望ましい。

また、その上に形成される平坦化層119との密着性を考慮することが望ましい。

## [0028]

これらドレイン配線 1 1 9 及び第 3 電極 1 2 0 上には、平坦化膜 1 2 1 が 0 . 5 ~ 3 µm (好ましくは、1 ~ 2 µm)で設けられる。平坦化膜 1 2 1 としては、スピンコーティング法(塗布法)で形成可能な有機樹脂膜もしくは無機絶縁膜を用いることができる。勿論、CVD法もしくはスパッタ法その他の気相法で形成された無機絶縁膜を研磨(機械的研磨、化学的研磨もしくはこれらを併用したものを含む。)したものであっても良い。本発明の実施にあたっては、プラズマ処理を行わずに済む感光性有機樹脂膜(好ましくはポ

10

20

30

40

10

20

30

40

50

ジ型)を用いると良い。感光性有機樹脂膜(代表的には感光性アクリル膜)は、現像液によるエッチングのみでパターン加工が可能であるため、膜中にプラズマダメージを残すことなく形成できる。

### [0029]

平坦化膜121は、露光及び現像工程を経て、選択トランジスタ17のソース領域103、駆動トランジスタ18のソース領域110及び111、ビデオ用Cs19の第1電極108(厳密には、第1電極108に隣接して設けられたp型不純物領域)並びに電流源用Cs24の第3電極120の上方に開口部(平坦化膜121に設けられた開口部を、第1開口部という。以下、同じ。)が設けられる。そして、第1開口部の設けられた平坦化膜121を覆うようにバリア膜122が30~100mm(好ましくは40~60mm)で設けられ、前掲の第1開口部の内側においては、該バリア膜122、第1パッシベーション膜118及びゲート絶縁膜113に開口部(これらの絶縁膜に設けられた開口部を、第2開口部という。以下、同じ。)が設けられる。

## [0030]

ここで特徴的な点は、バリア膜122として、極めて緻密な膜質の窒化シリコン膜を用いる点である。この点については、後述する。

### [0031]

また、第1開口部においては、バリア膜122と第1パッシベーション膜118が1~5 μm(典型的には2~3 μm)の範囲で接しており、そのため、平坦化膜121はバリア膜122と第1パッシベーション膜118によって完全に閉じ込められた状態となっている。その結果、平坦化膜121として有機樹脂膜やスピンオングラス(SOG)膜を用いたとしても、経時変化による脱ガスの発生を効果的に抑えることができるため、それに起因するトランジスタ特性や発光素子の経時劣化を抑えることができる。

#### [0032]

バリア膜122上には、選択トランジスタ17のソース配線123(図1(B)の信号線11に相当する。)、ビデオ用Cs19の第1電極108と電流源用Cs24の第3電極120とを接続する接続配線124(駆動トランジスタ18のソース配線を兼ねると共に、図1(B)の電源線14に相当する。)及び画素電極125が設けられる。これらの電極は、第1開口部もしくは第2開口部を介してそれぞれ対応する電極へ電気的に接続される。本実施の形態では、これらの電極を下から順にチタン膜31、窒化チタン膜32、アルミニウム膜(アルミニウム合金膜及び他の元素が添加されたアルミニウム膜を含む。以下、同じ。)33の三層構造としている。その理由として、(1)シリコン膜とのオーミック接触を良好なものとするために最下層はチタン膜が好ましいこと、(2)チタン膜とアルミニウムとの接触抵抗を低減するために窒化チタン膜が好ましいこと、(3)画素電極(発光素子の陽極)として窒化チタン膜を用いることができること、(4)アルミニウム膜の断面を利用して光取り出し効率の向上が期待できること、が挙げられる。

## [0033]

本実施の形態では、画素電極125となる電極をチタン膜31、窒化チタン膜32及びアルミニウム膜33で構成しており、発光領域(実効表示領域)において、アルミニウム膜33を選択的に除去して窒化チタン膜32を露出させている。その結果、窒化チタン膜32の表面を発光素子25の陽極として用いることが可能となる。さらに、有機樹脂膜126を用いてアルミニウム膜33をエッチングする際、図2(B)に示すように、アルミニウム膜33の断面形状がテーパー形状となるように調節することで、発光体126を横方向に伝播した光を上方へ反射させ、全体として光の取り出し効率の向上を期待することができる。この反射効果は、画素電極の全周囲で、即ち画素電極の輪郭に沿って効果が得られる。

#### [0034]

なお、発光体(キャリア注入層、キャリア輸送層、キャリア阻止層、発光層その他のキャリアの再結合に寄与する有機化合物もしくは無機化合物またはこれらの積層体を指す。 以下、同じ。)126は、陽極(窒化チタン膜)32及び陰極(周期表の1族もしくは2 族に属する元素を含む電極を指す。以下、同じ。)127との間に設けられて発光素子25を構成し、発光素子25は第2パッシベーション膜128で保護される。第2パッシベーション膜128は、第1パッシベーション膜118と同一材料でも良いが、バリア膜122と同一である方がより保護機能が高く好ましい。また、発光体126は公知の如何なる材料を用いても良い。

## [0035]

以上の構成を含む本発明のエレクトロルミネセンス表示装置の画素構成(図1(A))の特徴は、選択ゲート線12、消去ゲート線15及び電流ゲート線16がいずれも同じ層の金属層(第1の金属層)で形成され、信号線11、電流線13及び電源線14がいずれも同じ層の金属層(第2の金属層)で形成されると共に、第1の金属層と第2の金属層が交差する部分については、第2の金属層よりもさらに上層にある第3の金属層を用いて橋渡しする構成にある。

#### [0036]

即ち、第1の金属層と第2の金属層が交差する場合は、その間に $0.1 \sim 0.5 \mu m$ 程度の比較的薄い第1パッシベーション膜1.1.8 しか存在せず寄生容量が形成されてしまうが、第1の金属層と第3の金属層を交差させる場合は、その間に $0.5 \sim 3 \mu m$ の厚い平坦化膜1.2.1 が存在するため寄生容量を殆ど無視することができる。

#### [0037]

また、デバイス構成としての特徴は、まず第1に、平坦化膜121が第1パッシベーション膜118及びバリア膜122により封入されているため、平坦化膜121からの脱ガス等による経時劣化の問題がなく、信頼性の高い表示装置を得ることができる。

#### [0038]

また、第2に、容量素子を積層形成することにより少ない面積で大きな容量値を確保できる。例えば、電流源用Cs24は、第1電極109、第2電極117及び誘電体(ゲート絶縁膜)113で第1容量素子を構成し、第2電極117、第3電極120及び誘電体(第1パッシベーション膜)118で第2容量素子を構成しており、これらが並列に接続された構成となっている。なお、図示しないが、第1電極109及び第3電極120は固定電位(同電位でも良い。)である。このように、半導体/ゲート絶縁膜/第1の金属層で構成する第1容量素子と第1の金属層/第1パッシベーション膜/第2の金属層で構成する第2容量素子との積層構造の容量素子とすることで、少ない面積で大きな容量値を確保することができる。

## [0039]

なお、ビデオ用 C s 1 9 は、第 1 電極 1 0 8 、第 2 電極 1 1 6 及び誘電体 (ゲート絶縁膜) 1 1 3 で容量素子を構成している。このように、積層構造としなくても十分な場合は、二つの電極を用いる容量素子を形成することも可能である。

### [0040]

また、第3に、図2(B)に示した特殊な構造の画素電極125を発光素子25の陽極として用いることにより光取り出し効率を高め、輝度が高く明るいエレクトロルミネセンス表示装置とすることができる。なお、輝度が高いということは少ない消費電力で明るい画像が得られるということであり、低消費電力化を図ることができ、さらに、低消費電力化することにより発光素子25の劣化の進行度を抑え、信頼性を高くすることも可能である。

### [0041]

以上のように、本実施の形態のエレクトロルミネセンス表示装置は、多層配線を活用することにより各画素に必要とされる容量値(電荷保持用の容量値)を十分な大きさで確保し、かつ、信頼性が高く輝度の高い表示装置となる。

#### [0042]

(本発明で用いる窒化シリコン膜について)

本発明で用いる窒化シリコン膜は、高周波スパッタ法により形成される極めて緻密な膜質の窒化シリコン膜であり、以下の表 1 に示すプロセス条件で形成される(代表的な例に

10

20

30

40

ついても併記した。)。なお、ここで述べる窒化シリコン膜は、本発明において、窒化シ リコン膜が用いられる部分すべてに適用可能である。

また、表中の「RFSP-SiN」とは、高周波スパッタ法により形成された窒化シリコン膜を指す。また、「T/S」とは、ターゲットと基板との距離である。

## [0043]

### 【表1】

RFSP-SiNのプロセス条件

|                         | プロセス条件                                    | 代表的例                           | 備考                                |

|-------------------------|-------------------------------------------|--------------------------------|-----------------------------------|

| ガス                      | $N_2$ または希ガス $/N_2$                       | Ar/N <sub>2</sub>              | いずれも純度4N以<br>上                    |

| ガス流量比                   | N2:30~100%、希ガス:0~70%                      | Ar:N <sub>2</sub> =20:20(sccm) | 希ガスは加熱ガスと<br>して基板裏面から導<br>入しても良い。 |

| 圧力 (Pa)                 | 0.1~1.5                                   | 0.8                            |                                   |

| 周波数(MHz)                | 13~40                                     | 13.56                          |                                   |

| 電力 (W/cm <sup>2</sup> ) | 5~20                                      | 16.5                           |                                   |

| 基板温度(℃)                 | RT(室温)~350                                | 200                            |                                   |

| ターゲット材料                 | ーゲット材料 単結晶Siインゴットより切り出した材料 Si(1~1         |                                |                                   |

| T/S (mm)                | 40~200                                    | 60                             |                                   |

| 背圧(Pa)                  | 1×10 <sup>-3</sup> 以下(好ましくは、3×10-5以<br>下) | 3×10 <sup>-5</sup>             | ターボ分子ポンプまたはクライオポンプ使用              |

20

10

#### [0044]

スパッタガスとして用いるArは、基板を加熱するためのガスとして基板裏面側に吹き付けるように導入され、最終的に $N_2$ と混合されてスパッタに寄与する。また、表 1 に示す成膜条件は、代表的な条件であってここに示す数値に限定されるものではなく、成膜された SiN膜の物性パラメータが後に表 4 において示す物性パラメータの範囲内に入る限り、実施者が適宜変更しても良い。

### [0045]

ここで上記高周波スパッタ法により窒化シリコン膜を成膜するにあたって使用するスパッタ装置の概略図を図17に示す。図17において、30はチャンバー壁、31は磁場を形成するための可動式マグネット、32は単結晶シリコンターゲット、33は防護シャッター、34は被処理基板、36a及び36bはヒーター、37は基板チャック機構、38は防着板、39はバルブ(コンダクタンスバルブもしくはメインバルブ)である。また、チャンバー壁30には、ガス導入管40、41は、それぞれ $N_2$ (もしくは $N_2$ と希ガスの混合ガス)及び希ガスの導入管である。

### [0046]

また、比較例として従来のプラズマCVD法により形成される窒化シリコン膜の成膜条件を表 2 に示す。なお、表中の「PCVD-SiN」とは、プラズマCVD法により形成された窒化シリコン膜を指す。

[0047]

40

### 【表2】

プラズマCVD条件

| <u> </u>   |                                                                   |  |  |  |

|------------|-------------------------------------------------------------------|--|--|--|

|            | PCVD-SiN                                                          |  |  |  |

| ガス         | SiH <sub>4</sub> /NH <sub>3</sub> /N <sub>2</sub> /H <sub>2</sub> |  |  |  |

| ガス流量(sccm) | SiH4:NH3:N2:H2=30:240:300:60                                      |  |  |  |

| 圧力 (Pa)    | 159                                                               |  |  |  |

| 周波数(MHz)   | 13.56                                                             |  |  |  |

| 電力 (W/cm²) | 0.35                                                              |  |  |  |

| 基板温度(℃)    | 325                                                               |  |  |  |

|            | 325                                                               |  |  |  |

10

### [0048]

次に、表1の成膜条件で成膜された窒化シリコン膜と表2の成膜条件で成膜された窒化シリコン膜の代表的な物性値(物性パラメータ)について、比較した結果を表3にまとめる。なお、「RFSP-SiN(No.1)」と「RFSP-SiN(No.2)」との違いは、成膜装置による違いであり、本発明のバリア膜として用いる窒化シリコン膜としての機能を損なうものではない。また、内部応力は、圧縮応力か引っ張り応力かで数値の正負の符号が変わるが、ここでは絶対値のみを取り扱う。

### [0049]

### 【表3】

代表的かSiN物性パラメータの比較

| パラメータ             | 表1の成膜条件によるSiN膜       |                 | 表2の成膜条件によるSiN膜       | tite de     |

|-------------------|----------------------|-----------------|----------------------|-------------|

| /\/ <i>/</i> //   | RFSP-SiN (No.1)      | RFSP-SiN (No.2) | PCVD-SiN膜            | 備考          |

| 比誘電率              | 7.02~9.30            | <b>←</b>        | ~7                   |             |

| 屈折率               | 1.91~2.13            | ←               | 2.0~2.1              | 波長632.8nm   |

| 内部応力 (dyn/cm²)    | 4.17X10 <sup>8</sup> | <b>←</b>        | 9.11X10 <sup>8</sup> |             |

| エッチンク・速度 (nm/min) | $0.77 \sim 1.31$     | 1~8.6           | ~30 .                | LAL500, 20℃ |

| Si濃度 (atomic%)    | 37.3                 | 51.5            | 35.0                 | RBS         |

| N濃度 (atomic%)     | 55.9                 | 48.5            | 45.0                 | RBS         |

| H濃度 (atoms/cc)    | 4X10 <sup>20</sup>   | _               | 1X10 <sup>22</sup>   | SIMS        |

| O濃度 (stoms/cc)    | 8X10 <sup>20</sup>   | _               | 3X10 <sup>18</sup>   | SIMS        |

| C濃度 (atoms/cc)    | 1X10 <sup>19</sup>   | _               | 4X10 <sup>17</sup>   | SIMS        |

30

20

## [0050]

表 3 に示すように、これら R F S P - S i N ( N o . 1 ) 及び R F S P - S i N ( N o . 2 ) に共通の特徴点は、 P C V D - S i N 膜と比較して、 エッチング速度( L A L 5 0 0 を用いて 2 0 でエッチングした際のエッチング速度をいう。以下、同じ。)が遅く、水素濃度が低い点が挙げられる。なお、「 L A L 5 0 0 」とは、橋本化成株式会社製「 L A L 5 0 0 S A バッファードフッ酸」であり、 N H  $_4$  H F  $_2$  ( 7 . 1 3 % ) と N H  $_4$  F ( 1 5 . 4 % ) の水溶液である。また、 内部応力は、 プラズマ C V D 法で成膜された窒化シリコン膜よりも絶対値で比較して小さい値となっている。

40

#### [0051]

ここで本発明者らが表 1 の成膜条件によって成膜した窒化シリコン膜の諸物性のパラメータを表 4 にまとめる。

## [0052]

### 【表4】

本発明に用いるSiNの物性パラメータ

| パラメータ            | 本発明に用いるSiN膜                                                                            | 備考          |

|------------------|----------------------------------------------------------------------------------------|-------------|

| 比誘電率             | 7.0~9.5(好ましくは、7.3~7.7)                                                                 |             |

| 屈折率              | 1.85~2.20(好ましくは、1.90~2.15)                                                             | 波長632.8nm   |

| 内部応力 (dyn/cm²)   | 2X10 <sup>10</sup> 以下(好ましくは、5X10 <sup>8</sup> 以下)                                      |             |

| エッチング速度 (nm/min) | 9以下(好ましくは、0.5~3.5)                                                                     | LAL500, 20℃ |

| Si濃度 (atomic%)   | 35~55(好ましくは、37~52)                                                                     | RBS         |

| N濃度 (atomic%)    | 45~60(好ましくは、48~56)                                                                     | RBS         |

| H濃度 (atoms/cc)   | 1X10 <sup>21</sup> 以下(好ましくは、5X10 <sup>20</sup> 以下)                                     | SIMS        |

| O濃度 (atoms/cc)   | 5X10 <sup>18</sup> ~5X10 <sup>21</sup> (好ましくは、1X10 <sup>19</sup> ~1X10 <sup>21</sup> ) | SIMS        |

| C濃度 (atoms/cc)   | 1X10 <sup>18</sup> ~5X10 <sup>19</sup> (好ましくは、1X10 <sup>18</sup> ~2X10 <sup>19</sup> ) | SIMS        |

### [0053]

また、当該窒化シリコン膜をSIMS(質量二次イオン分析)により調べた結果を図11に、そのFT-IRの結果を図12に、その透過率を図13に示す。

なお、図13には表2の成膜条件で成膜した窒化シリコン膜についても併せて表記する。 透過率については、従来のPCVD-SiN膜と比べて遜色はない。

#### [0054]

本発明で用いる窒化シリコン膜においては、表 4 に示すパラメータを満たす窒化シリコン膜が望ましい。即ち、窒化シリコン膜として、(1)エッチング速度が 9 n m 以下(好ましくは、0 . 5 ~ 3 . 5 n m 以下)である窒化シリコン膜を用いること、(2)水素濃度が 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  以下(好ましくは、5 × 1 0  $^{20}$  atoms / c m  $^{-3}$  以下)であること、(3)水素濃度が 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  以下(好ましくは、5 × 1 0  $^{20}$  atoms / c m  $^{-3}$  以下)で、かつ、酸素濃度が 5 × 1 0  $^{18}$  ~ 5 × 1 0  $^{21}$  atoms / c m  $^{-3}$  (好ましくは、1 × 1 0  $^{19}$  ~ 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  )であること、(4)エッチング速度が 9 n m 以下(好ましくは、0 . 5 ~ 3 . 5 n m 以下)で、かつ、水素濃度が 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  以下(好ましくは、5 × 1 0  $^{20}$  atoms / c m  $^{-3}$  以下)で、かつ、水素濃度が 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  以下(好ましくは、0 . 5 ~ 3 . 5 n m 以下)で、かつ、水素濃度が 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  以下(好ましくは、0 . 5 ~ 3 . 5 n m 以下)で、かつ、酸素濃度が 5 × 1 0  $^{18}$  ~ 5 × 1 0  $^{21}$  atoms / c m  $^{-3}$  (好ましくは、1 × 1 0  $^{19}$  ~ 1 × 1 0  $^{21}$  atoms / c m  $^{-3}$  )であること、のいずれかを満たすことが望ましい。

#### [0055]

また、内部応力の絶対値は、  $2 \times 10^{10}$  d y n / c m  $^2$ 以下、好ましくは  $5 \times 10^9$  d y n / c m  $^2$ 以下、さらに好ましくは  $5 \times 10^8$  d y n / c m  $^2$ 以下とすると良い。内部応力を小さくすれば、他の膜との界面における準位の発生を低減できる。さらに、内部応力による膜はがれを防止できる。

## [0056]

また、表1の成膜条件による窒化シリコン膜は、Na、Liその他の周期表の1族もしくは2族に属する元素に対するプロッキング効果が極めて強く、これらの可動イオン等の拡散を効果的に抑制することができる。例えば、本発明に用いる陰極としては、アルミニウムに0.2~1.5 w t %(好ましくは0.5~1.0 w t %)のリチウムを添加した金属膜が電荷注入性その他の点で好適であるが、この場合において、リチウムの拡散によってトランジスタの動作に害を及ぼすことが懸念される。しかしながら、本発明では、バリア膜で完全に保護されることとなるため、リチウムのトランジスタ方向への拡散は気にする必要がない。

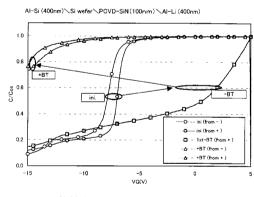

## [0057]

この事実を示すデータを図14~16に示す。図14は、表2の成膜条件で成膜した窒化シリコン膜(PCVD-SiN膜)を誘電体としたMOS構造のBTストレス試験前後におけるC-V特性の変化を示す図である。試料の構造は、図16(A)に示す通りであり、表面電極にA1-Li(リチウムを添加したアルミニウム)電極を用いることによりリチウム拡散による影響の有無を確かめることができる。図14によれば、BTストレス試験によりC-V特性が大きくシフトし、表面電極からのリチウムの拡散による影響が顕

10

20

30

40

著に現れていることが確認できる。

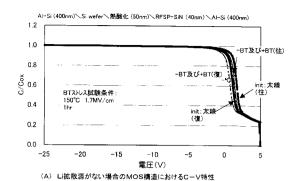

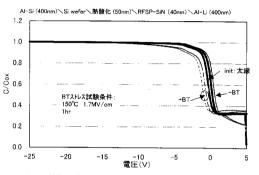

## [0058]

次に、図15(A)、(B)は、表1の成膜条件で成膜した窒化シリコン膜を誘電体としたMOS構造のBTストレス試験前後におけるC-V特性である。図15(A)、(B)の違いは、図15(A)が表面電極にA1-Si(シリコンを添加したアルミニウム膜)電極を用いるのに対し、図15(B)が表面電極にA1-Li(リチウムを添加したアルミニウム膜)電極を用いる点である。なお、図15(B)の結果は、図16(B)に示すMOS構造の測定結果である。ここで熱酸化膜との積層構造としたのは、窒化シリコン膜とシリコン基板との間の界面準位の影響を低減するためである。

#### [0059]

図15(A)、(B)の両グラフを比較すると、両グラフともにBTストレス試験前後におけるC-V特性のシフトは殆ど差がなく、リチウム拡散の影響が現れていないこと、即ち、表1の成膜条件で成膜した窒化シリコン膜が効果的にプロッキング膜として機能していることが確認できる。

#### [0060]

このように、本発明に用いる窒化シリコン膜は、非常に緻密でNaやLiといった可動元素に対するブロッキング効果が高いため、平坦化膜からの脱ガス成分の拡散を抑制すると共に、Al-Li電極等からのLi拡散を効果的に抑制することで信頼性の高い表示装置を実現することができる。緻密である理由として、本発明者らは、単結晶シリコンターゲットの表面で薄い窒化シリコン膜が形成され、その窒化シリコン膜が基板へ積層されて成膜されるため、膜中にシリコンクラスタが混入されにくくなった結果として緻密になるのではないかと推測している。

### [0061]

また、室温から200 程度の低温下のスパッタ法で成膜されるため、本発明のバリア膜として用いる場合のように、樹脂膜の上に成膜できる点においてプラズマCVD法よりも有利である。

## [0062]

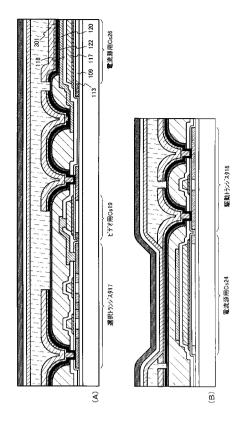

〔実施の形態 2 〕 本実施の形態は、実施の形態 1 とは異なる構成で電流源用 C s を形成した例であり、第 3 の金属層を電極として用いている。なお、その他の構成は、実施の形態 1 と同じであるから、実施の形態 1 の説明を参照すれば良い。従って、本実施の形態では、実施の形態 1 と異なる点のみに着目して説明する。

## [0063]

図3(A)、(B)は、実施の形態1における図2(A)、(B)に相当する図面であり、実施の形態1と同じ符号を付してある部分は、実施の形態1で説明したものと同じ構成を有している。本実施の形態の場合、電流源用Cs26の構成に特徴があり、図2(A)において、平坦化層121を除去してある。即ち、第1電極109、誘電体(ゲート絶縁膜113)及び第2電極117で構成される第1の容量素子、第2電極117、誘電体(第1パッシベーション膜118)

及び第3電極120で構成される第2の容量素子並びに第3電極120、バリア膜122 及び第4電極301で構成される第3の容量素子の三つの容量素子を積層形成した構成となっている。

#### [0064]

本実施の形態では、容量素子を三つ形成するために第1電極109及び第3電極120 を固定電位としている。勿論、第2電極117及び第4電極301を固定電位としても同様である。即ち、交互に固定電位の電極を重ねておくことで最大限に容量を形成することができる。ただし、どの電極を固定電位とするかは回路設計において自由に設定可能であり、前掲の構成に限定する必要はない。

#### [0065]

以上の構成を採用すると、三つの容量素子を小さい面積で形成することが可能となるため、開口率を損失を最小限に抑えつつ大容量を確保することができる。

10

20

30

40

なお、本実施の形態に示す容量素子の構成は、電流源用 C s への適用に限られるものではなく、ビデオ用 C s 1 9 その他の画素内に必要とされる容量素子 ( C s ) として用いることができる。

#### [0066]

〔実施の形態3〕 本実施の形態は、実施の形態1とは異なる構成で電流源用Csを形成した例であり、第3の金属層を電極として用いている。なお、その他の構成は、実施の形態1と同じであるから、実施の形態1の説明を参照すれば良い。従って、本実施の形態では、実施の形態1と異なる点のみに着目して説明する。

#### [0067]

図4(A)、(B)は、実施の形態1における図2(A)、(B)に相当する図面であり、実施の形態1と同じ符号を付してある部分は、実施の形態1で説明したものと同じ構成を有している。本実施の形態の場合、電流源用Cs28の構成に特徴があり、図2(A)において、平坦化層121及び第3電極120を除去してある。即ち、第1電極109、ゲート絶縁膜113及び第2電極117で構成される第1の容量素子並びに第2電極117、誘電体(第1パッシベーション膜118及びバリア膜122の積層体)及び第4電極401で構成される第2の容量素子の二つの容量素子を積層形成した構成となっている。この場合、誘電体が積層形成されているので、ピンホール等による不良の発生確率が大幅に低減するという利点がある。

### [0068]

本実施の形態では、容量素子を二つ形成するために第1電極109及び第4電極401 を固定電位としている。ただし、どの電極を固定電位とするかは回路設計において自由に 設定可能であり、前掲の構成に限定する必要はない。

#### [0069]

以上の構成を採用すると、二つの容量素子を小さい面積で形成することが可能となるため、開口率を損失を抑えつつ大容量を確保することができる。なお、本実施の形態に示す容量素子の構成は、電流源用Csへの適用に限られるものではなく、ビデオ用Cs19その他の画素内に必要とされる容量素子(Cs)として用いることができる。

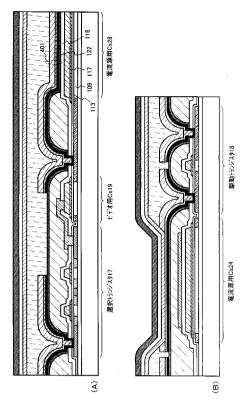

#### [0070]

[実施の形態4] 本実施の形態は、実施の形態1とは異なる構成で電流源用Csを形成した例であり、第3の金属層を電極として用いている。なお、その他の構成は、実施の形態1と同じであるから、実施の形態1の説明を参照すれば良い。従って、本実施の形態では、実施の形態1と異なる点のみに着目して説明する。

## [0071]

図5(A)、(B)は、実施の形態1における図2(A)、(B)に相当する図面であり、実施の形態1と同じ符号を付してある部分は、実施の形態1で説明したものと同じ構成を有している。本実施の形態の場合、電流源用Cs30の構成に特徴があり、図5(A)において、平坦化層121、第3電極120及び第2電極117を除去してある。即ち、第1電極109、誘電体(ゲート絶縁膜113、第1パッシベーション膜118及びバリア膜122の積層体)及び第4電極501で構成される容量素子となっている。本実施の形態では、第1電極109を固定電位としているが、どの電極を固定電位とするかは回路設計において自由に設定可能であり、前掲の構成に限定する必要はない。また、この場合、誘電体が三層の絶縁膜で積層形成されているので、ピンホール等による不良の発生確率を最小限に抑えることができるという利点がある。

## [0072]

また、本実施の形態とした場合、第2電極117が存在しないため第1電極109、即ち半導体には導電型を付与する不純物が添加される。即ち、図1~図4の構成とした場合は、第2電極117に定電圧を印加しないと第1電極109を電極として機能させることができないが、本実施の形態の構成とすると、第4電極501に定電圧を与えなくても常に容量として機能させることができる。この効果は表示装置の消費電力の低減に寄与する

10

20

30

#### [0073]

なお、以上の構成は、電流源用 C s への適用に限られるものではなく、ビデオ用 C s 1 9 その他の画素内に必要とされる容量素子 ( C s ) として用いることもできる。

### [0074]

〔実施の形態 5 〕 本実施の形態は、実施の形態 1 とは異なる構成で電流源用 C s を形成した例であり、第 3 の金属層を電極として用いている。なお、その他の構成は、実施の形態 1 と同じであるから、実施の形態 1 の説明を参照すれば良い。従って、本実施の形態では、実施の形態 1 と異なる点のみに着目して説明する。

### [0075]

図6(A)、(B)は、実施の形態1における図2(A)、(B)に相当する図面であり、実施の形態1と同じ符号を付してある部分は、実施の形態1で説明したものと同じ構成を有している。本実施の形態の場合、電流源用Cs32の構成に特徴があり、図2(A)において、第2電極117を除去してある。即ち、第1電極109が不純物の添加によって電極化しているため、第3電極120に定電圧を印加しておかなくても常に電極として機能させることができ、低消費電力化に寄与する。

#### [0076]

また、電流源用 C s 3 2 の構成は、第 1 電極 1 0 9、誘電体(ゲート絶縁膜 1 1 3 及び第 1 パッシベーション膜 1 1 8 の積層体)及び第 3 電極 1 2 0 で構成される。この場合、誘電体が積層形成されているので、ピンホール等による不良の発生確率が大幅に低減するという利点がある。また、本実施の形態では、第 1 電極 1 0 9 を固定電位としているが、どの電極を固定電位とするかは回路設計において自由に設定可能であり、前掲の構成に限定する必要はない。

### [0077]

なお、以上の構成は、電流源用 C s への適用に限られるものではなく、ビデオ用 C s 1 9 その他の画素内に必要とされる容量素子 ( C s ) として用いることもできる。また、実施の形態 1 ~ 4 のいずれの構成とも組み合わせて実施することが可能である。

#### [0078]

〔実施の形態 6 〕 本実施の形態は、実施の形態 1 とは異なる構成で電流源用 C s を形成した例であり、第 3 の金属層を電極として用いている。なお、その他の構成は、実施の形態 1 と同じであるから、実施の形態 1 の説明を参照すれば良い。従って、本実施の形態では、実施の形態 1 と異なる点のみに着目して説明する。

## [0079]

図7(A)、(B)は、実施の形態1における図2(A)、(B)に相当する図面であり、実施の形態1と同じ符号を付してある部分は、実施の形態1で説明したものと同じ構成を有している。本実施の形態の場合、電流源用Cs34の構成に特徴があり、図2(A)において、第1電極109を除去してある。

## [0080]

また、電流源用 C s 3 4 の構成は、第 2 電極 1 1 7 、誘電体(第 1 パッシベーション膜 1 1 8 ) 及び第 3 電極 1 2 0 で構成される。なお、本実施の形態では、第 3 電極 1 2 0 を 固定電位としているが、どの電極を固定電位とするかは回路設計において自由に設定可能 であり、前掲の構成に限定する必要はない。

#### [0081]

なお、以上の構成は、電流源用 C s への適用に限られるものではなく、ビデオ用 C s 1 9 その他の画素内に必要とされる容量素子 ( C s ) として用いることもできる。また、実施の形態 1 ~ 4 のいずれの構成とも組み合わせて実施することが可能である。

## [0082]

[実施の形態7] 本実施の形態は、画素の構成を実施の形態1とは異なる構成とした例について、図8を用いて説明する。図8(A)に示す画素構成の特徴は、選択ゲート線12、消去ゲート線15及び電流ゲート線16がいずれも同じ層の金属層(第1の金属層)で形成され、信号線11、電流線13及び電源線14がいずれも同じ層の金属層(第2

10

20

30

40

10

20

30

40

50

の金属層)で形成されると共に、第1の金属層と第2の金属層が交差する構成となっている点にある。この場合、その間に0.1~0.5  $\mu$  m程度の比較的薄い第1パッシベーション膜118 しか存在せず寄生容量が形成されてしまうが、実施の形態1の構成よりもコンタクト数が減少するため、開口率が向上するという利点がある。

### [0083]

なお、本実施の形態の画素構成において、画素内には実施の形態 1 ~ 6 に示したいずれの構成の容量素子を形成しても良い。

### [0084]

[実施の形態 8] 実施の形態 1~7に示した薄膜トランジスタの構成はいずれもトップゲート構造(具体的にはプレーナ構造)であるが、各実施の形態では、ボトムゲート構造(具体的には逆スタガ構造)とすることも可能である。その場合、活性層等の半導体層とゲート電極等の第1の金属層の位置が逆向きになるだけである。また当然のことながら、薄膜トランジスタに限らず、シリコンウェルを用いて形成されたMOS構造のトランジスタに適用しても良い。

#### [0085]

[実施の形態9] 実施の形態1~8に示した表示装置は、いずれもエレクトロルミネセンス表示装置を例示しているが、デバイス構成自体は、液晶表示装置に適用する場合についても共通であり、画素電極の構造を変更すれば、液晶表示装置、フィールドエミッション表示装置その他の複数の画素を有する表示装置に適用しても良い。

### [0086]

[実施の形態10] 本実施の形態では、本発明を適用しうるエレクトロルミネセンス表示装置の全体の構成について、図9を用いて説明する。図9は、薄膜トランジスタが形成された素子基板をシーリング材によって封止することによって形成されたエレクトロルミネセンス表示装置の上面図であり、図9(B)は、図9(A)のB-B'における断面図、図9(C)は、図9(A)のA-A'における断面図である。

### [0087]

基板 2 0 1 上には、画素部(表示部) 2 0 2 、該画素部 2 0 2 を囲むように設けられたデータ線駆動回路 2 0 3 、ゲート線駆動回路 2 0 4 a 、 2 0 4 b 及び保護回路 2 0 5 が配置され、これらを囲むようにしてシール材 2 0 6 が設けられている。画素部 2 0 2 の構造については、実施の形態 1 ~ 8 及びその説明を参照すれば良い。シーリング材 2 0 6 としては、ガラス材、金属材(代表的にはステンレス材)、セラミックス材、プラスチック材(プラスチックフィルムも含む)を用いることができるが、実施の形態 1 ~ 8 に示したように絶縁膜のみで封止することも可能である。

## [0088]

このシール材206は、データ線駆動回路203、ゲート線駆動回路204a、204b及び保護回路205の一部に重畳させて設けても良い。そして、該シール材206を用いてシーリング材207が設けられ、基板201、シール材206及びシーリング材207によって密閉空間208が形成される。シーリング材207には予め凹部の中に吸湿剤(酸化バリウムもしくは酸化カルシウム等)

209が設けられ、上記密閉空間208の内部において、水分や酸素等を吸着して清浄な雰囲気に保ち、発光体の劣化を抑制する役割を果たす。この凹部は目の細かいメッシュ状のカバー材210で覆われており、該カバー材210は、空気や水分は通し、吸湿剤209は通さない。なお、密閉空間208は、窒素もしくはアルゴン等の希ガスで充填しておけばよく、不活性であれば樹脂もしくは液体で充填することも可能である。

#### [0089]

また、基板201上には、データ線駆動回路203及びゲート線駆動回路204a、204bに信号を伝達するための入力端子部211が設けられ、該入力端子部211へはFPC(フレキシブルプリントサーキット)212を介してビデオ信号等のデータ信号が伝達される。入力端子部211の断面は、図9(B)の通りであり、ゲート配線もしくはデータ配線と同時に形成された配線からなる入力配線213とFPC212側に設けられた

配線215とを、導電体216を分散させた樹脂217を用いて電気的に接続してある。 なお、導電体216としては、球状の高分子化合物に金もしくは銀といったメッキ処理を 施したものを用いれば良い。

#### [0090]

また、図9(C)において、点線で囲まれた領域218の拡大図を図9(D)に示す。保護回路205は、薄膜トランジスタ219やコンデンサ220を組み合わせて構成すれば良く、コンデンサ220として実施の形態1~7に示した構成の容量素子を用いれば良い。

## [0091]

本実施の形態において、保護回路 2 0 5 は入力端子部 2 1 1 とデータ線駆動回路 2 0 3 との間に設けられ、両者の間に突発的なパルス信号等の静電気が入った際に、該パルス信号を外部へ逃がす役割を果たす。その際、まず瞬間的に入る高電圧の信号をコンデンサ 2 2 0 によって鈍らせ、その他の高電圧を薄膜トランジスタや薄膜ダイオードを用いて構成した回路によって外部へと逃がすことができる。勿論、保護回路は、他の場所、例えば画素部 2 0 2 とデータ線駆動回路 2 0 4 a 2 0 4 b の間などに設けても構わない。

### [0092]

以上のように、本実施の形態では、本発明を実施するにあたって、入力端子部に設けられた静電気対策等の保護回路に用いられるコンデンサを同時形成する例を示しており、実施の形態 1~9 のいずれの構成とも組み合わせて実施することが可能である。

#### [0093]

[実施の形態 1 1 ] 本発明の表示装置を表示部に用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を図 1 0 に示す。

### [0094]

図10(A)はテレビであり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。本発明は表示部2003に適用することができる。なお、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用のテレビが含まれる。

## [0095]

図 1 0 ( B ) はデジタルカメラであり、本体 2 1 0 1、表示部 2 1 0 2、受像部 2 1 0 3、操作キー 2 1 0 4、外部接続ポート 2 1 0 5、シャッター 2 1 0 6 等を含む。本発明は、表示部 2 1 0 2 に適用することができる。

### [0096]

図10(C)はノート型パーソナルコンピュータであり、本体2201、筐体2202 、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウ ス2206等を含む。本発明は、表示部2203に適用することができる。

#### [0097]

図 1 0 ( D ) はモバイルコンピュータであり、本体 2 3 0 1 、表示部 2 3 0 2 、スイッチ 2 3 0 3 、操作キー 2 3 0 4 、赤外線ポート 2 3 0 5 等を含む。本発明は、表示部 2 3 0 2 に適用することができる。

## [0098]

図10(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(DVD等)読み込み部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を

10

20

30

40

10

20

表示するが、本発明は表示部A、B2403、2404に適用することができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

#### [0099]

図10(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2501、表示部2502、アーム部2503を含む。本発明は、表示部2502に適用することができる。

### [ 0 1 0 0 ]

図 1 0 (G)はビデオカメラであり、本体 2 6 0 1、表示部 2 6 0 2、筐体 2 6 0 3、外部接続ポート 2 6 0 4、リモコン受信部 2 6 0 5、受像部 2 6 0 6、バッテリー 2 6 0 7、音声入力部 2 6 0 8、操作キー 2 6 0 9、接眼部 2 6 1 0 等を含む。本発明は、表示部 2 6 0 2 に適用することができる。

#### [0101]

図10(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。本発明は、表示部2703に適用することができる。なお、表示部2703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。

## [0102]

以上の様に、本発明を実施して得た表示装置は、あらゆる電子機器の表示部として用いても良い。なお、本実施の形態の電子機器には、実施の形態 1 ~ 9 に示したいずれの構成を有した表示装置を用いても良い。

【図1】

【図2】

【図3】 【図4】

【図5】 【図6】

【図7】

【図8】

【図9】

【図10】

## 【図11】

## 【図12】

## 【図13】

## 【図14】

#### -Li拡散源がある場合のMOS構造におけるC-V特性

BTストレス試験条件: 150℃、1.7MV/cm 1hr

## 【図15】

(B) Li拡散源がある場合のMOS構造におけるC-V特性

## 【図16】

## 【図17】

## フロントページの続き

## 審査官 請園 信博

(56)参考文献 特開2002-006777(JP,A)

特開2001-013893(JP,A)

特開平10-041519(JP,A)

特開平10-068970(JP,A)

特開2001-282137(JP,A)

特開平04-139828(JP,A)

(58)調査した分野(Int.CI., DB名)

G09F 9/00 - 9/30

9/307 - 9/46

H01L 27/32

H01L 51/50

H05B 33/00 - 33/28