US 20070087522A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2007/0087522 A1

## (10) Pub. No.: US 2007/0087522 A1 (43) Pub. Date: Apr. 19, 2007

### Nemani et al.

#### (54) DIELECTRIC GAP FILL WITH OXIDE SELECTIVELY DEPOSITED OVER SILICON LINER

(75) Inventors: Srinivas Nemani, Sunnyvale, CA (US); Shankar Venkataraman, Santa Clara, CA (US)

> Correspondence Address: TOWNSEND AND TOWNSEND AND CREW LLP / AMAT TWO EMBARCADERO CENTER EIGHTH FLOOR SAN FRANCISCO, CA 94111-3834 (US)

- (73) Assignee: Applied Materials, Inc., Santa Clara, CA

- (21) Appl. No.: 11/565,726

- (22) Filed: Dec. 1, 2006

#### **Related U.S. Application Data**

(63) Continuation of application No. 10/858,135, filed on Jun. 1, 2004, now Pat. No. 7,176,105.

- **Publication Classification**

- (51) Int. Cl. *H01L* 21/76 (2006.01)

- (52) U.S. Cl. ..... 438/424; 438/435

#### (57) ABSTRACT

A thin layer of silicon is deposited within a high aspect ratio feature to provide a template for selective deposition of oxide therein. In accordance with one embodiment, amorphous silicon is deposited within a shallow trench feature overlying an oxide liner grown therein. After exposure to sputtering to remove the amorphous silicon from outside of the trench, oxide is selectively deposited over the amorphous silicon to fill the trench from the bottom up without voids, thereby creating a shallow trench isolation (STI) structure. Deposition of the amorphous silicon or other silicon containing layers allows the selective oxide deposition step to be integrated with a thermally-grown oxide trench liner.

#### DIELECTRIC GAP FILL WITH OXIDE SELECTIVELY DEPOSITED OVER SILICON LINER

#### CROSS REFERENCE TO RELATED APPLICATION

**[0001]** This application is a continuation of U.S. patent application Ser. No. 10/858,135, entitled "DIELECTRIC GAP FILL WITH OXIDE SELECTIVELY DEPOSITED OVER SILICON LINER," filed Jun. 1, 2004, the entire disclosure of which is incorporated herein by reference for all purposes.

#### BACKGROUND OF THE INVENTION

**[0002]** The present invention relates generally to the fabrication of integrated circuits. More particularly, the present invention is directed toward a method of performing gap-fill in integrated circuit devices. Merely by way of example, the invention has been applied to a method for providing self-planarized deposition of high quality dielectric layers for shallow trench isolation. The method can be applied to other applications as well such as inter-metal dielectric and pre-metal dielectric deposition.

[0003] Semiconductor device geometries continue to decrease in size, providing more devices per unit area on a fabricated wafer. These devices are typically initially isolated from each other as they are built into the wafer, and they are subsequently interconnected to create the specific circuit configurations desired. Currently, some devices are fabricated with feature dimensions as small as 0.18  $\mu$ m. For example, spacing between devices such as conductive lines or traces on a patterned wafer may be separated by 0.18  $\mu$ m, leaving recesses or gaps of a comparable size. A nonconductive layer of dielectric material, such as silicon dioxide (SiO<sub>2</sub>), is typically deposited over the features to fill the aforementioned gaps (gap-fill) and insulate the features from other features of the integrated circuit in adjacent layers or from adjacent features in the same layer.

[0004] Dielectric layers are used in various applications including shallow trench isolation (STI) dielectric for isolating devices and interlayer dielectric (ILD) formed between metal wiring layers or prior to a metallization process. In some cases, STI is used for isolating devices having feature dimensions as small as under about 0.5  $\mu$ m. In some of these cases, the aspect ratio of the depth to width of the trench to be filled exceeds 6:1. Planarization of dielectric layers has become increasingly important as the packing densities of semiconductor devices continue to grow.

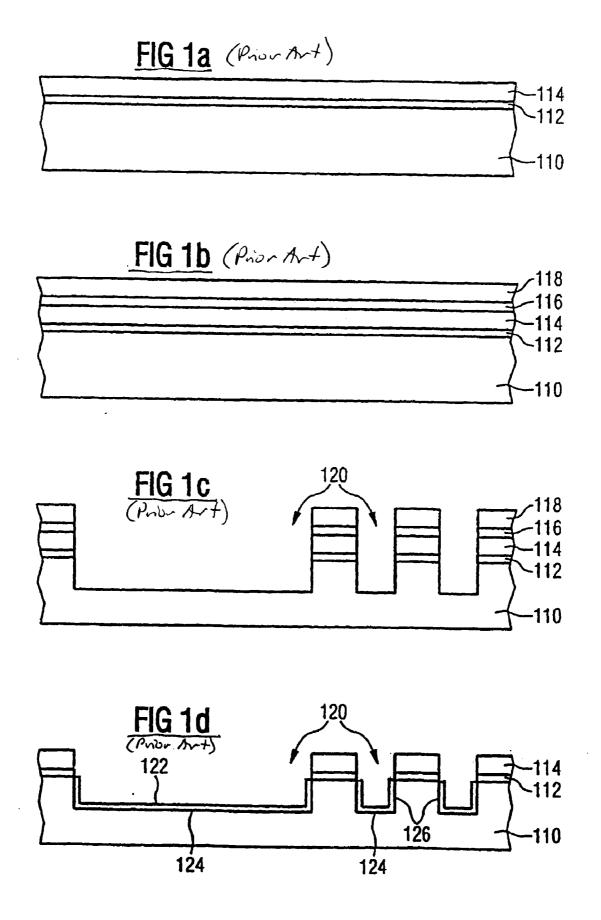

**[0005]** The planarization issue is described using an example of a typical process for forming an STI dielectric, commonly referred to as STI integration, as illustrated in FIGS. 1*a*-1*h*. In FIG. 1*a*, a silicon substrate 110 has deposited thereon a pad oxide layer 112 and a nitride layer 114 such as silicon nitride. The nitride layer 114 is typically deposited by low pressure chemical vapor deposition (LPCVD), and serves as an etch stop for chemical mechanical polishing (CMP).

[0006] Referring to FIG. 1b, a bottom anti-reflective coating (BARC) 116 is formed above the nitride layer 114 for absorbing light reflected from the substrate 110 during

photolithography. Typically an organic spin-on glass (SOG), the BARC **116** is needed typically for light having wavelengths of below about 248 nm, including deep ultraviolet (DUV) and far ultraviolet (FUV) light. A photoresist **118** is formed over the BARC **116** and exposed using a mask (not shown) which defines the location of the trenches.

[0007] The exposed photoresist is then stripped to leave open areas for forming the trenches. Typically, a plasma etch is performed to etch the open areas through the BARC 116, the nitride 114, pad oxide 112, and silicon substrate 110 to form the trenches 120, as shown in FIG. 1*c*.

[0008] After the remaining photoresist 118 and BARC 116 are removed, a thermal oxide 122 is typically grown on the surfaces of the trenches 120 (trench bottom 124 and trench wall 126) to repair the plasma damage to the silicon substrate 110, as illustrated in FIG. 1*d*.

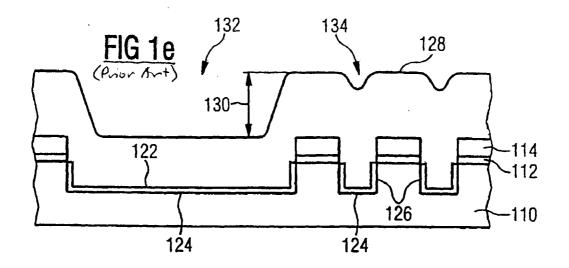

[0009] A dielectric layer 128 is then deposited over the thermal oxide 122 to fill the trenches 120 and cover the nitride layer 114. This dielectric layer 128 is often referred to as a trench oxide filling layer. Typical dielectric layers are formed from oxide materials such as silicon dioxide or silicate glass. As shown in FIG. 1e, the surface profile of the deposited dielectric layer 128 is stepped and generally resembles the shape of the trenched substrate 110. The surface profile is more uniform in dense fields with closely space narrow trenches than in open fields with wide trenches. As seen in FIG. 1e, a step height 130 is formed in the dielectric profile between the dense field 134 and the open field 132.

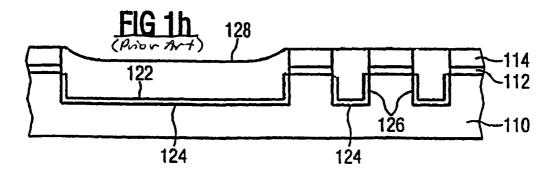

[0010] Because of the step height 130, it is not practicable to apply CMP directly after the dielectric layer deposition step to planarize the dielectric layer 128 because otherwise a dishing effect in the open field 132 will result with CMP, as seen in FIG. 1*h*. Instead, a reverse mask and etch procedure is used to etch the extra oxide to obtain a more planar surface profile as illustrated in FIG. 1*f*. This procedure typically involves the steps of photoresist deposition, reverse masking, cure, etched photoresist removal, etchback, and removal of remaining photoresist.

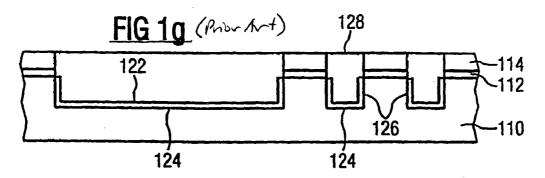

**[0011]** A CMP procedure is then applied to the structure of FIG. **1***f* to globally planarize the surface of the filled substrate **110** as shown in FIG. **1***g*. The reverse mask and etch procedure necessitated by the step height effect adds significant cost and complexity to the planarization procedure, for example, due to the added lithography steps involved.

**[0012]** From the discussion above, it is seen that multiple steps, including additional photolithography steps (which require expensive equipment), are needed to provide STI as described in relation to FIGS. **1***a***-1***h*. However, it is desirable to reduce the number of steps (and related equipment, especially photolithography equipment which requires expensive lenses, light sources, etc.) and to obtain improved results in order to provide a more economic and efficient manufacturing process. For example, one way to obtain improved results is to provide a self-planarized, high quality trench oxide filling layer at a reduced cost.

**[0013]** A number of procedures are known for depositing dielectric layers such as the gap-fill dielectric **128** for the trench oxide filling layer in the example shown in FIG. 1*e*. One type of process employs  $O_3$  (ozone) and TEOS (tetra-ethylorthosilicate) for depositing a dielectric film such as

silicate glass. Such deposited films are commonly referred to as " $O_3$ /TEOS films." Such  $O_3$ /TEOS processes have a surface sensitivity which increases as the  $O_3$ /TEOS ratio increases. Due to the surface sensitivity, the dielectric deposition rate varies in accordance with the properties of the material of the underlying layer.

**[0014]** It is known to minimize the surface sensitivity by depositing a surface insensitive barrier layer prior to the  $O_3$ /TEOS film deposition. For instance, one known process involves a plasma-enhanced TEOS (PETEOS) deposition, followed by a surface treatment and then a thin cap TEOS layer. This process undesirably requires additional process steps.

**[0015]** Another known method is to lower the surface sensitivity by decreasing the  $O_3$ /TEOS ratio. However, lowering the  $O_3$ /TEOS ratio tends to undesirably result in a more porous dielectric film. This is particularly problematic when the dielectric film is used for isolation purposes. One way to address this concern has been to raise the process temperature to above about 500° C., but raising the process temperature is often undesirable. Alternatively, an additional anneal process after the deposition of the trench oxide filling layer and sandwiching PETEOS layers has been used to densify the trench oxide filling layer. This method, however, suffers from the need to perform an extra step.

[0016] Instead of minimizing the surface sensitivity, some have utilized the deposition rate dependence of  $O_3/TEOS$  films to perform gap fill for a trenched silicon substrate wherein the side walls of the trench are covered with thermal oxide spacers. Using an atmospheric pressure chemical vapor deposition (APCVD)  $O_3/TEOS$  deposition and an ozone concentration of 5%, it was reported that faster film growth on the bottom silicon than on the side wall spacers precluded void formation to achieve void-free gap fill.

[0017] Others have investigated the feasibility of forming a planarized inter-metal dielectric (IMD) by taking advantage of the surface sensitivity of  $O_3$ /TEOS and similar materials such as  $O_3$ -octamethylcyclotetrasiloxane (OMTC). Researchers have reported difficulties in controlling the different deposition rates to achieve planarity. For instance, significant elevations have been observed at the edges of aluminum metal lines caused by the different deposition rates of the  $O_3$ /TEOS on a TiN anti-reflective coating (ARC) layer on top of the aluminum and the aluminum side walls. Some of these same researchers have reported more satisfactory planarization results for depositing SiO<sub>2</sub> layers on an aluminum interconnect built upon a phosphorus glass (PSG) level using  $O_3$ -OMTC.

**[0018]** In light of the above, attempts to obtain planarity by depositing surface sensitive dielectric layers have not always been successful. In addition, the inventors have discovered that these methods may produce dielectric layers that do not have the desired quality. What is needed are more efficient and economic methods for self-planarized deposition of a high quality trench oxide filling layer for STI integration.

#### SUMMARY OF THE INVENTION

**[0019]** According to embodiments of the present invention, a method for fabricating integrated circuits is provided. More particularly, the present invention is directed toward a

method of performing gap-fill in integrated circuit devices. Merely by way of example, the invention has been applied to a method for providing self-planarized deposition of high quality dielectric layers for shallow trench isolation. The method can be applied to other applications as well, for example to deposition of pre-metal dielectric (PMD) between raised features present on the surface of a workpiece.

**[0020]** An embodiment of a method in accordance with the present invention for depositing a fill layer in a recess, comprises, disposing in a substrate processing chamber a substrate having a recess, and forming a first insulating layer within the recess. A silicon containing layer is deposited on the substrate, and an upper portion of the silicon containing layer is removed while maintaining a portion of the silicon containing layer is selectively deposited within the recess and then etched, and a third insulating layer is deposited on the substrate and over the second insulating layer.

**[0021]** An embodiment of a method of performing gap-fill in a high aspect ratio recess, comprises, forming an oxide liner within a high aspect ratio recess on a semiconductor workpiece, and depositing a silicon containing liner on the workpiece and within the recess over the oxide liner. The silicon containing liner is etched to remove a portion of the silicon containing liner from outside of the recess and from an upper portion of the recess. A first insulating layer is selectively deposited within the trench overlying the silicon containing liner. The first insulating layer is etched, and then a second insulating layer is deposited.

**[0022]** A further understanding of embodiments in accordance with the present invention can be made by way of reference to the ensuing detailed description taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0023]** FIGS. 1*a*-1*h* are simplified schematic vertical cross-sectional views of a substrate, demonstrating trench formation and trench fill by a dielectric material employing prior art deposition methods.

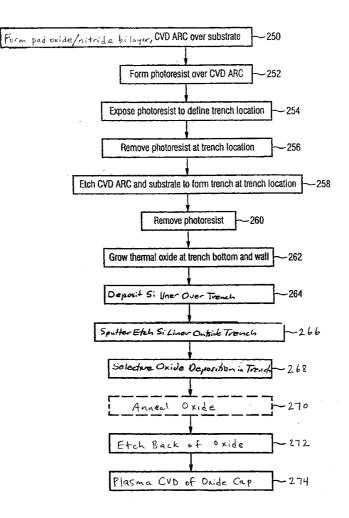

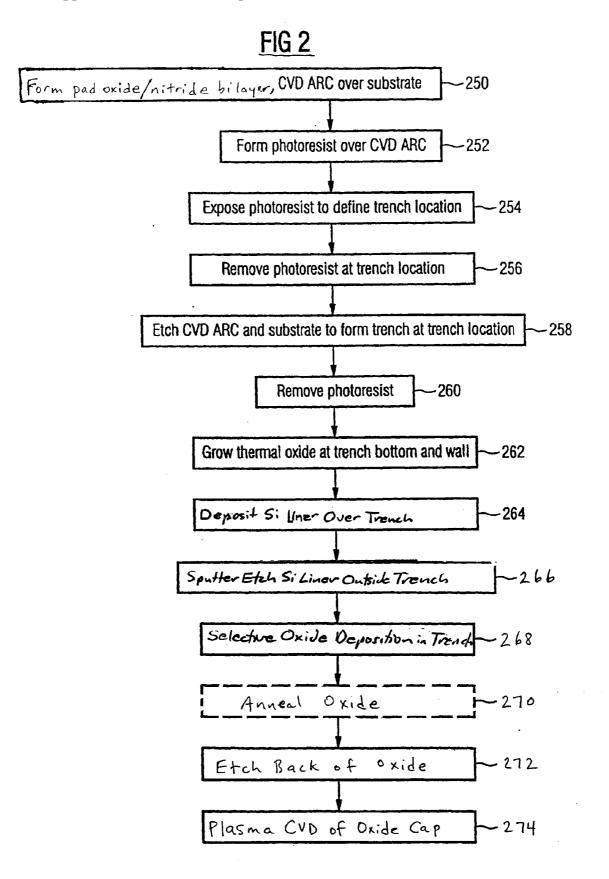

**[0024]** FIG. **2** is a flow diagram of an embodiment of a method of filling a trench in accordance with the present invention.

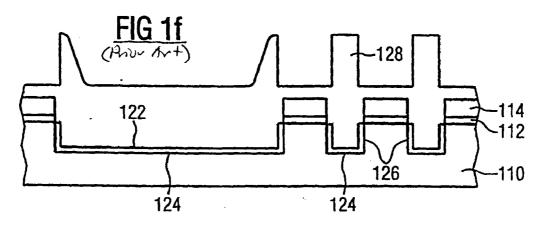

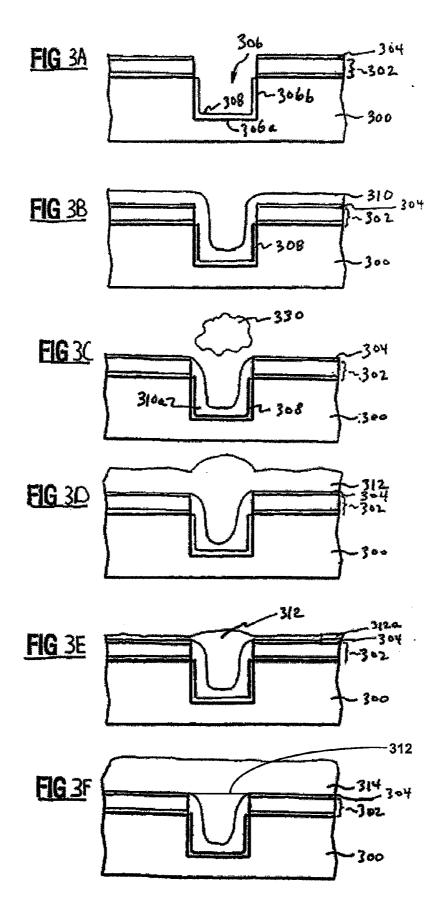

**[0025]** FIGS. **3A-3**F are simplified schematic vertical cross-sectional views of an embodiment of a method of filling a trenched substrate in accordance with the present invention.

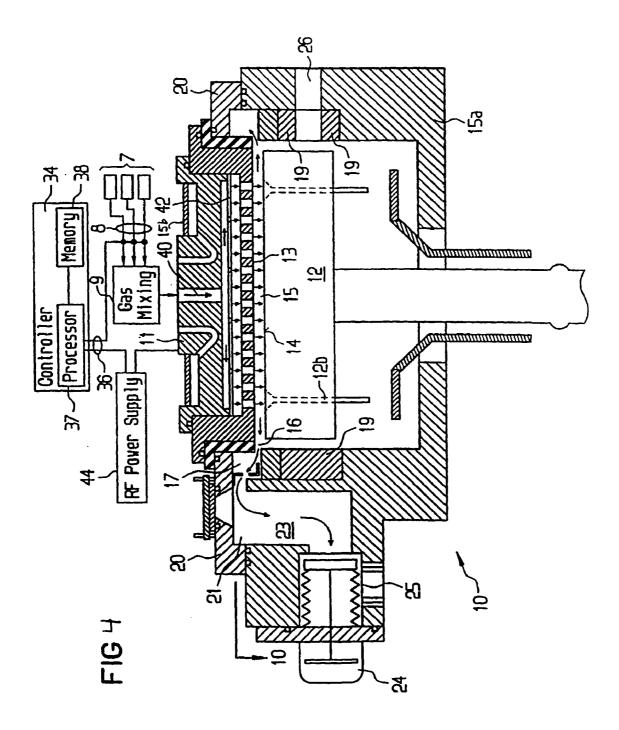

**[0026]** FIG. **4** is a simplified schematic vertical crosssectional view of one embodiment of a chemical vapor deposition (CVD) apparatus according to the present invention.

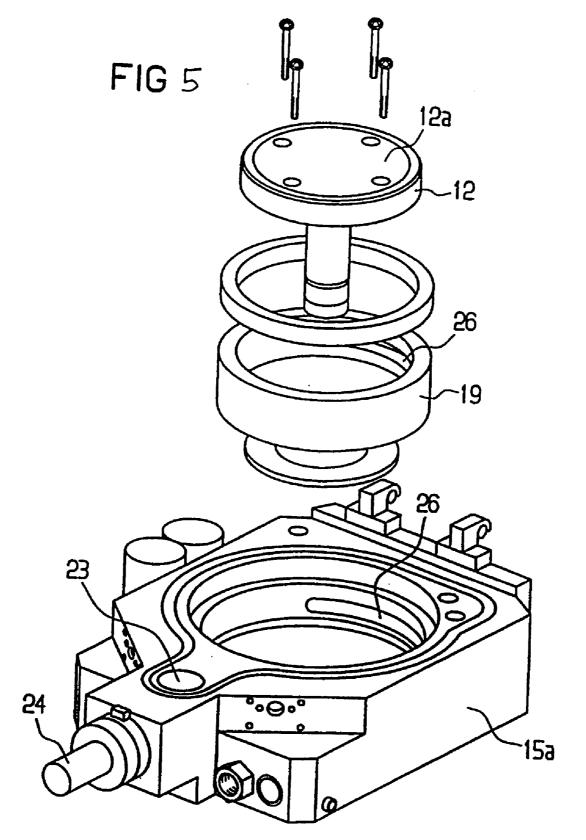

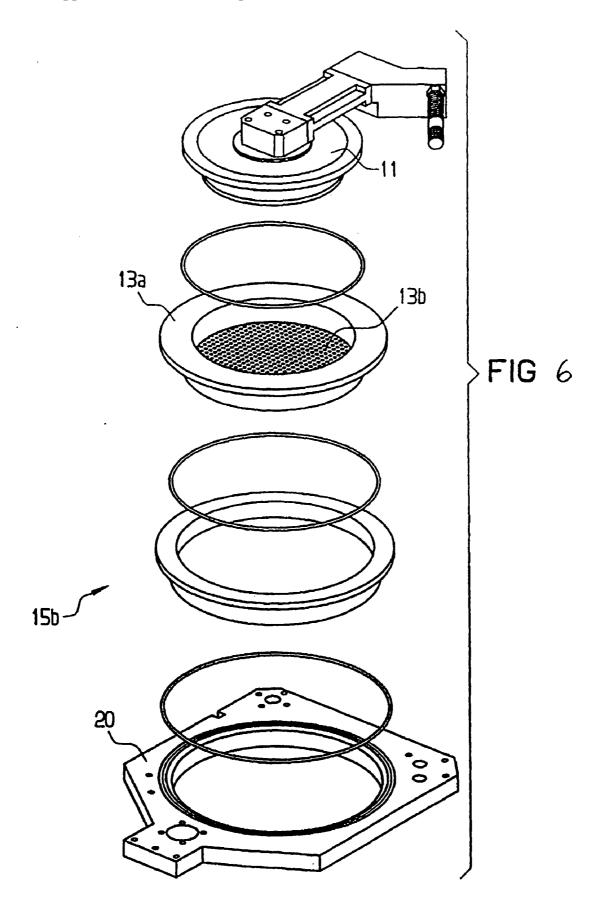

**[0027]** FIGS. **5** and **6** are simplified exploded perspective views of parts of the CVD apparatus depicted in FIG. **4**.

#### DESCRIPTION OF THE SPECIFIC EMBODIMENTS

**[0028]** According to the present invention, a method of fabricating integrated circuits is provided. More particularly, the present invention is directed toward a method of performing gap-fill in integrated circuit devices. Merely by way

of example, the invention has been applied to a method for providing self-planarized deposition of high quality dielectric layers for STI. The method can be applied to other applications as well, for example deposition of pre-metal dielectric (PMD) between raised features present on the surface of a semiconductor workpiece.

[0029] FIG. 2 shows a flow diagram of an embodiment of a method of filling a trench in accordance with the present invention. First, a pad oxide/nitride bilayer (reference 302 in FIG. 3A) is formed over a substrate. An anti-reflective coating (ARC) is deposited by chemical vapor deposition (CVD) on top of the substrate over the pad oxide/nitride bilayer (step 250). Photoresist is formed over the CVD ARC (step 252). The photoresist is developed and removed at the trench (254). Photoresist is developed and removed at the trench location (256).

**[0030]** Next, the CVD ARC and the underlying nitride/pad oxide layers are etched to form the trench at the trench location (step **258**). Often, a plasma etching step is utilized to form the trench. In embodiments according to the present invention, the trench is a high aspect ratio trench. In a specific embodiment, the aspect ratio of the depth to width of the high aspect ratio trench is greater than 6:1. Photoresist is then removed by stripping (step **260**).

[0031] In the next step (262) of this embodiment as illustrated in FIG. 2 and also shown in simplified crosssection in FIG. 3A, substrate 300 (with pad oxide/nitride bilayer 302 and CVD ARC layer 304) bearing the etched trench 306 is exposed to an oxidizing ambient, such that thermal oxide 308 is grown from the silicon at the bottom 306*a* and walls 306*b* of the trench 306. This thermal oxide 308 may be referred to as an oxide liner. As previously described, the thermal oxidation serves to repair damage to the substrate caused by the previous plasma etching step (258). Moreover, a thermal oxide typically provides a higher density oxide layer than those produced using CVD processes.

**[0032]** In embodiments according to the present invention, the oxide liner may be grown using predetermined growth parameters, including, but not limited to temperature, time, and ambient composition. The thermal oxide liner is typically grown according to techniques known to those of skill in the art. In a particular embodiment, an in situ steam generation (ISSG) process is utilized with a chamber pressure in the range of 5-20 Torr, an ambient containing H<sub>2</sub> and O<sub>2</sub> in a predetermined ratio and a substrate temperature in the range from about 500° C.-about 900° C. In a specific embodiment, the ratio of H<sub>2</sub> to O<sub>2</sub> is 1:2. Alternative embodiments utilize different growth parameters including parameters that change as a function of time to achieve the growth of the oxide liner.

[0033] In the next step (264) shown in simplified crosssection in FIG. 3B, a conformal silicon-containing material 310 is deposited within and outside of the trench. This material 310 may be referred to as a silicon liner. Siliconcontaining material 310 can comprise, for example, amorphous silicon (a:Si), Si-rich silicon oxide, silicon oxynitride (SiON), or polysilicon, each of which may be deposited by CVD or other techniques. In an alternative embodiment, the silicon-containing material may comprise a multi-layer film comprising a combination of silicon nitride (SiN) with one or more of the aforementioned materials. In such an alternative embodiment, the top layer of the multi-layer film may comprise one the aforementioned materials other than SiN.

**[0034]** In embodiments according to the present invention, the thickness of the silicon liner is a predetermined thickness. In a specific embodiment, the thickness of the layer is less than 500 Å, although this specific thickness is not required by the present invention. In alternative embodiments, the thickness of the layer is up to 1000 Å. In one embodiment, an a:Si layer is deposited using an Applied Centura Ultima HDP-CVD® chamber available from Applied Materials, Inc. of Santa Clara, Calif. In a specific embodiment according to the present invention, a Si-rich silicon oxide (Si<sub>x</sub>O<sub>y</sub>) is deposited with a predetermined ratio of silicon to oxygen (x:y). In a particular embodiment, the Si-rich silicon oxide is a non-stoichiometric oxide with the ratio of x:y greater than 0.63. In an alternative embodiment, the ratio of x:y is 1:0.

[0035] Continuing through the flow chart shown in FIG. 2, in the next step (266) also shown in cross-section in FIG. 3C, the silicon-containing material deposited in the previous step is removed from outside of the trench and from upper regions of the trench, through the use of a directional or anisotropic etch process. In one embodiment, exposure of the substrate to energized sputtering gases such as Ar, He, Xe, H<sub>2</sub>, or other gases 330 is utilized. Other directional etch processes are utilized in alternative embodiments. In an embodiment according to the present invention, the directional etch process is terminated when the ARC layer 304 is reached. Thus, in this embodiment, the silicon-containing material is only present in the trench. Removal of a portion of the silicon-containing material in this manner leaves a silicon-containing liner 310a overlying the thermal oxide 308 within the trench 306 as illustrated in FIG. 3C.

[0036] Silicon liner 310a in turn serves as a template for the selective deposition of oxide 312 in the subsequent step (268), shown in simplified cross-section in FIG. 3D. This selective oxide deposition process is described in detail in published European Patent Application EP 0 959 496 A2, incorporated by reference herein for all purposes. In some embodiments according to the present invention, the selective deposition of oxide is performed in a Producer SE SACVD® process chamber available from Applied Materials, Inc. of Santa Clara, Calif. The presence of the silicon liner in the embodiment illustrated in FIGS. 2 and 3 allows the selective oxide deposition step to be integrated with a thermally grown oxide liner.

**[0037]** Specifically, typically an inert gas is flowed into the chamber to stabilize the pressure in the chamber before reactive process gases are introduced. Next, a precursor having a surface sensitivity and growth rate dependence on differently constituted surfaces is introduced into the chamber. An example of a suitable precursor is TEOS. Because TEOS is a liquid precursor, a suitable apparatus directs the bubbling of a delivery gas, such as helium, through the TEOS in a bubbler assembly, or introducing of a carrier gas, such as helium or nitrogen, to a liquid injection system to vaporize the TEOS and form a process gas having the desired flow rates.

[0038] An ozone gas is flowed into the chamber to react with the TEOS and deposit an  $O_3$ /TEOS trench fill layer over the substrate. The deposition rate of the  $O_3$ /TEOS layer is faster on the lower trench bottom in the trench (which is

lined with the silicon-containing material) than on the higher surfaces of the upper portions of the substrate that include the etch stop layer (including but not limited to, a CVD ARC or an LPCVD nitride in accordance with various embodiments of the present invention).

[0039] The relative deposition rates of the  $O_3/TEOS$  layer on the upper and lower surfaces within the recess may be regulated by adjusting the  $O_3/TEOS$  ratio until the  $O_3/TEOS$  layer develops a substantially self-planarized dielectric surface.

**[0040]** The O<sub>3</sub>/TEOS ratio can be adjusted by adjusting the flow rates of the O<sub>3</sub>, the TEOS, or both the O<sub>3</sub> and TEOS. For instance, in one embodiment, a predetermined O<sub>3</sub>/TEOS ratio is selected and the relative flow rates are adjusted to achieve the predetermined ratio. In a particular embodiment, it is advantageous to maximize the O<sub>3</sub>/TEOS ratio to accelerate the deposition in the trench to achieve planarity. In this particular embodiment, the predetermined O<sub>3</sub>/TEOS ratio is higher than about 10:1. In alternative embodiments, the O<sub>3</sub>/TEOS ratio is in the range of about 10:1 to 20:1. In a specific embodiment, the O<sub>3</sub>/TEOS ratio is about 13:1.

[0041] The deposition of the trench fill layer can take place at a relatively low temperature of less than about 500° C. This advantageously avoids the undesirable aluminum fluoride formation which may occur when deposition occurs at high temperatures exceeding about 500° C. in processing chambers that include aluminum materials. This low temperature deposition process also avoids the longer cleaning time required to remove the resulting aluminum fluoride. Other process parameters such as pressure and flow rates can be adjusted to optimize the deposition process for a selected O<sub>3</sub>/TEOS ratio. A pressure ranging from about 200 to 700 Torr is preferable for use with O<sub>3</sub>/TEOS ratios of 10:1 to 20:1.

**[0042]** In some embodiments of the present invention, the selectively deposited oxide may be annealed after deposition in order to further densify and improve the quality of the trench fill layer (optional step **270**). Embodiments in accordance with the present invention utilizing this optional annealing step, perform the annealing step in a nitrogen environment at a temperature in the range of about 900-1050° C., for about 30-90 minutes. In a specific embodiment, a 30 minute nitrogen anneal at 1,000° C. is performed. A dense layer of deposited oxide is advantageous, particularly for isolation purposes.

[0043] Referring again back to the flow chart of FIG. 2, in the next step (272) shown in simplified cross-section in FIG. 3E, selectively deposited oxide 312 is etched back by exposure to an etch process. In one embodiment according to the present invention, the etch process is a plasma etch containing fluorine radicals. In one embodiment, this etchback process is halted upon exposure to the underlying ARC layer 304. For example, if the sensitivity to the ARC layer 304 results in a poor quality film, the layer 312a is completely removed. In a second embodiment, such as the one illustrated in FIG. 3E, the etchback process is halted just above the ARC layer 304, leaving some oxide layer 312a remaining on top of the ARC layer. The etch process selected will typically depend on the particular device integration scheme utilized.

**[0044]** In some embodiments of the present invention, a CMP process may be performed after the etchback step to

further planarize the surface of the substrate. This CMP process can be performed without the use of a reverse mask and etch procedure because of the substantially planar surface already present as illustrated in FIG. **3**E. Thus the CMP process can be completed more quickly than in the conventional case where the dielectric profile is stepped, such as that shown in FIG. **1***f*, further decreasing process time and increasing throughput.

**[0045]** In the final step (274) shown in simplified crosssection in FIG. **3**F, a capping layer of oxide **314** is deposited over the oxide-filled trench feature. In one embodiment according to the present invention, the oxide cap is deposited utilizing a CVD process. This CVD process produces a substantially planarized cap layer as illustrated in FIG. **3**F.

[0046] In contrast with the prior selective deposition of oxide material within the trench in step 268, the CVD cap layer 314 is deposited on top of the oxide layer 312, continuously present on the wafer surface. Thus, no selection of predetermined growth ratios is made in this embodiment.

**[0047]** While the above-referenced figures and accompanying description relate to embodiments in accordance with the present invention which form an STI structure in a substrate, this is not required by the present invention. Alternative embodiments in accordance with the present invention could deposit a silicon liner layer prior to selective oxide deposition within other types of features, for example between raised features present on the surface of a semiconductor workpiece, as are present during the pre-metal dielectric (PMD) deposition step.

**[0048]** Numerous benefits are achieved using the present invention over conventional techniques. For example, a thermal oxide layer can be grown in the trench, reducing the damage resulting from the process of etching the trench. Selective deposition of oxide as a trench fill material is performed after deposition of a silicon liner. Thus, this process allows for a selective deposition of oxide to be integrated with a thermal oxide liner. The substantially self-planarized dielectric surface produced by the selective deposition step reduces the need for CMP and other planarization processes. Depending upon the embodiment, one or more of these benefits may exist. These and other benefits have been described throughout the present specification and more particularly below.

[0049] One suitable CVD apparatus in which the method of the present invention can be carried out is shown in FIG. 4, which is a vertical, cross-sectional view of a CVD system 10, having a vacuum or processing chamber 15 that includes a chamber wall 15a and chamber lid assembly 15b. Chamber wall 15a and chamber lid assembly 15b are shown in exploded, perspective views in FIGS. 5 and 6.

[0050] CVD system 10 contains a gas distribution manifold 11 for dispersing process gases to a substrate (not shown) that rests on a heated pedestal 12 centered within the process chamber. During processing, the substrate (e.g. a semiconductor wafer) is positioned on a flat (or slightly convex) surface 12a of pedestal 12. The pedestal can be moved controllably between a lower loading/off-loading position (not shown) and an upper processing position (shown in FIG. 4), which is closely adjacent to manifold 11. A centerboard (not shown) includes sensors for providing information on the position of the wafers.

[0051] Deposition and carrier gases are introduced into chamber 15 through perforated holes 13b (FIG. 6) of a conventional flat, circular gas distribution or face-plate 13a. More specifically, deposition process gases flow into the chamber through the inlet manifold 11 (indicated by arrow 40 in FIG. 4), through a conventional perforated blocker plate 42 and then through holes 13b in gas distribution faceplate 13a.

[0052] Before reaching the manifold, deposition and carrier gases are input from gas sources 7 through gas supply lines 8 (FIG. 4) into a mixing system 9 where they are combined and then sent to manifold 11. Generally, the supply line for each process gas includes (i) several safety shut-off valves (not shown) that can be used to automatically or manually shut-off the flow of process gas into the chamber, and (ii) mass flow controllers (also not shown) that measure the flow of gas through the supply line. When toxic gases (for example, ozone or halogenated gas) are used in the process, the several safety shut-off valves are positioned on each gas supply line in conventional configurations.

[0053] The deposition process performed in CVD system 10 can be either a thermal process or a plasma-enhanced process. In a plasma-enhanced process, an RF power supply 44 applies electrical power between the gas distribution faceplate 13a and the pedestal so as to excite the process gas mixture to form a plasma within the cylindrical region between the faceplate 13a and the pedestal. (This region will be referred to herein as the "reaction region"). Constituents of the plasma react to deposit a desired film on the surface of the semiconductor wafer supported on pedestal 12. RF power supply 44 is a mixed frequency RF power supply that typically supplies power at a high RF frequency (RF1) of 13.56 MHz and at a low RF frequency (RF2) of 360 KHz to enhance the decomposition of reactive species introduced into the vacuum chamber 15. In a thermal process, RF power supply 44 would not be utilized, and the process gas mixture thermally reacts to deposit the desired films on the surface of the semiconductor wafer supported on pedestal 12, which is resistively heated to provide thermal energy for the reaction.

[0054] During a plasma-enhanced deposition process, the plasma heats the entire process chamber 10, including the walls of the chamber body 15a surrounding the exhaust passageway 23 and the shut-off valve 24. When the plasma is not turned on or during a thermal deposition process, a hot liquid is circulated through the walls 15a of the process chamber to maintain the chamber at an elevated temperature. Fluids used to heat the chamber walls 15a include the typical fluid types, i.e., water-based ethylene glycol or oil-based thermal transfer fluids. This heating beneficially reduces or eliminates condensation of undesirable reactant products and improves the elimination of volatile products of the process gases and other contaminants that might contaminate the process if they were to condense on the walls of cool vacuum passages and migrate back into the processing chamber during periods of no gas flow.

**[0055]** The remainder of the gas mixture that is not deposited in a layer, including reaction products, is evacuated from the chamber by a vacuum pump (not shown). Specifically, the gases are exhausted through an annular, slot-shaped orifice **16** surrounding the reaction region and into an annular exhaust plenum **17**. The annular slot **16** and

the plenum 17 are defined by the gap between the top of the chamber's cylindrical side wall 15a (including the upper dielectric lining 19 on the wall) and the bottom of the circular chamber lid 20. The  $360^{\circ}$  circular symmetry and uniformity of the slot orifice 16 and the plenum 17 are important to achieving a uniform flow of process gases over the wafer so as to deposit a uniform film on the wafer.

[0056] From the exhaust plenum 17, the gases flow underneath a lateral extension portion 21 of the exhaust plenum 17, past a viewing port (not shown), through a downward-extending gas passage 23, past a vacuum shut-off valve 24 (whose body is integrated with the lower chamber wall 15a), and into the exhaust outlet 25 that connects to the external vacuum pump (not shown) through a foreline (also not shown).

**[0057]** The wafer support platter of the pedestal **12** (preferably aluminum, ceramic, or a combination thereof) is resistively-heated using an embedded single-loop embedded heater element configured to make two full turns in the form of parallel concentric circles. An outer portion of the heater element runs adjacent to a perimeter of the support platter, while an inner portion runs on the path of a concentric circle having a smaller radius. The wiring to the heater element passes through the stem of the pedestal **12**.

**[0058]** Typically, any or all of the chamber lining, gas inlet manifold faceplate, and various other reactor hardware are made out of material such as aluminum, anodized aluminum, or ceramic. An example of such a CVD apparatus is described in U.S. Pat. No. 5,558,717 entitled "CVD Processing Chamber," issued to Zhao et al. The U.S. Pat. No. 5,558,717 patent is assigned to Applied Materials, Inc., the assignee of the present invention, and is hereby incorporated by reference.

[0059] A lift mechanism and motor (not shown) raises and lowers the heated pedestal assembly 12 and its wafer lift pins 12b as wafers are transferred into and out of the body of the chamber by a robot blade (not shown) through an insertion/ removal opening 26 in the side of the chamber 10. The motor raises and lowers pedestal 12 between a processing position 14 and a lower, wafer-loading position (not shown). The motor, valves or flow controllers connected to the supply lines 8, gas delivery system, throttle valve, RF power supply 44, and chamber and substrate heating systems are all controlled by a system controller 34 (FIG. 4) over control lines 36, of which only some are shown. Controller 34 relies on feedback from optical sensors to determine the position of movable mechanical assemblies such as the throttle valve and susceptor which are moved by appropriate motors under the control of controller 34.

[0060] In a preferred embodiment, the system controller includes a hard disk drive (memory 38), a floppy disk drive and a processor 37. The processor contains a single-board computer (SBC), analog and digital input/output boards, interface boards and stepper motor controller boards. Various parts of CVD system 10 conform to the Versa Modular European (VME) standard 45 which defines board, card cage, and connector dimensions and types. The VME standard also defines the bus structure as having a 16-bit data bus and a 24-bit address bus.

[0061] It should be understood that the inventions described herein can be employed in various integrated

shallow trench isolation, to name just a few examples. Although various embodiments which incorporate teachings of the present invention have been shown and described in detail herein, those skilled in the art can readily devise many other varied embodiments that still incorporate these teachings.

What is claimed is:

**1**. A method of depositing a fill layer in a recess, comprising:

providing a substrate having a recess;

forming a first insulating layer within the recess;

depositing a silicon containing layer on the substrate;

- removing an upper portion of the silicon containing layer while maintaining a portion of the silicon containing layer within the recess;

- selectively depositing a second insulating layer within the recess;

etching the second insulating layer; and

depositing a third insulating layer on the substrate and over the second insulating layer to form a capping layer.

**2**. The method of claim 1 wherein the recess comprises a trench in the substrate.

**3**. The method of claim 1 wherein the recess comprises a gap between raised features present on a surface of the substrate.

**4**. The method of claim 1 wherein forming the first insulating layer comprises forming a silicon oxide layer.

**5**. The method of claim 4 wherein the silicon oxide layer is thermally grown.

**6**. The method of claim 1 wherein forming the silicon containing layer comprises performing chemical vapor deposition of the group consisting of amorphous silicon, polysilicon, silicon oxide, and silicon nitride.

7. The method of claim 1 wherein forming the silicon containing layer comprises forming a non-stoichiometric silicon-rich silicon oxide layer with a Si:O ratio of greater than 0.63.

**8**. The method of claim 1 wherein the step of removing an upper portion of the silicon containing layer further comprises a step of sputtering the substrate with a gas.

**9**. The method of claim 8 wherein the gas is selected from the group consisting of hydrogen, helium, xenon, and argon.

10. The method of claim 1 wherein the step of etching the second insulating layer further comprises etching the second insulating layer in an environment containing fluorine radicals.

**11**. The method of claim 10 wherein the step of etching the second insulating layer is terminated prior to complete removal of the second insulating layer.

**12**. The method of claim 1 wherein the step of selectively depositing the second insulating layer comprises introducing

TEOS and ozone to the substrate, wherein the TEOS and ozone react to deposit the second insulating layer.

**13**. The method of claim 1 further comprising the step of annealing the substrate after the step of selectively depositing the second insulating layer within in the recess.

14. The method of claim 13 wherein the annealing step is carried out at between about 900-1050° C. for between about 30-90 minutes.

15. The method of claim 1 wherein the second insulating layer is selectively deposited at a temperature of less than about  $500^{\circ}$  C.

**16**. A method of performing gap-fill in a high aspect ratio recess, the method comprising:

- forming an oxide liner within a high aspect ratio recess on a semiconductor workpiece;

- depositing a silicon containing liner on the workpiece and within the recess over the oxide liner;

- etching the silicon containing liner to remove a portion of the silicon containing liner from outside of the recess and from an upper portion of the recess;

- selectively depositing a first insulating layer within the trench overlying the silicon containing liner;

etching the first insulating layer; and

depositing a second insulating layer.

**17**. The method of claim 16 wherein the high aspect ratio recess comprises a trench formed in the workpiece.

**18**. The method of claim 16 wherein the high aspect ratio recess comprises a gap between raised features present in a surface of the workpiece.

**19**. The method of claim 16 wherein an aspect ratio of the recess is 6:1 or greater.

**20**. The method of claim 16 wherein depositing the silicon containing liner comprises performing chemical vapor deposition of a material selected from the group consisting of amorphous silicon, polysilicon, silicon oxide, and silicon nitride.

**21**. The method of claim 16 wherein forming the silicon containing liner comprises forming a non-stoichiometric silicon-rich oxide layer with a Si:O ratio of greater than 0.63.

**22**. The method of claim 16 wherein the step of etching the silicon containing liner comprises performing an anisotropic etch.

**23**. The method of claim 22 wherein the anisotropic etch is a sputter etch utilizing species selected from the group consisting of hydrogen, helium, argon, and xenon.

**24**. The method of claim 16 wherein the step of selectively depositing a first insulating layer to fill the trench comprises introducing TEOS and ozone to the workpiece, wherein the TEOS and ozone react to deposit the second insulating layer.

25. The method of claim 16 wherein the first insulating layer is selectively deposited at a temperature of less than about  $500^{\circ}$  C.

\* \* \* \* \*