(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6374492号

(P6374492)

(45) 発行日 平成30年8月15日(2018.8.15)

(24) 登録日 平成30年7月27日(2018.7.27)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652G |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652H |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 652D |

|             |           | HO1L 29/78 | 652F |

|             |           | HO1L 29/78 | 652N |

請求項の数 9 (全 14 頁) 最終頁に続く

(21) 出願番号 特願2016-520007 (P2016-520007)

(86) (22) 出願日 平成26年9月26日 (2014.9.26)

(65) 公表番号 特表2016-536782 (P2016-536782A)

(43) 公表日 平成28年11月24日 (2016.11.24)

(86) 國際出願番号 PCT/US2014/057790

(87) 國際公開番号 WO2015/050790

(87) 國際公開日 平成27年4月9日 (2015.4.9)

審査請求日 平成29年9月15日 (2017.9.15)

(31) 優先権主張番号 14/044,909

(32) 優先日 平成25年10月3日 (2013.10.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】トレンチゲートトレンチフィールドプレート半垂直半横方向MOSFET

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板と、

前記半導体基板の表面に形成され、側壁と底部を有するゲートトレンチであって、前記側壁と前記底部の上にゲート誘電層が形成され、前記ゲート誘電層の上にゲートが形成される、前記ゲートトレンチと、

前記基板の前記表面に形成され、前記ゲートトレンチの前記側壁に隣接する第一の導電型のソース領域と、

前記基板の中で前記ソース領域の下に形成され、前記ゲートトレンチの前記側壁に隣接する第二の導電型のボディ領域と、

前記基板の中で前記ボディ領域の下に形成される前記第一の導電型のドリフト領域と、

前記基板の前記表面に形成される第一の閉ループ構成のトレンチであって、前記第一の閉ループ構成のトレンチは側壁と底部を有し、さらに、前記第一の閉ループ構成のトレンチの前記側壁と前記底部の上に形成される第一の誘電体ライナーと、前記第一の誘電体ライナーの上に形成され、かつ、前記ソース領域に電気的に接続される第一の導電性部材とを有する、前記第一の閉ループ構成のトレンチと、

前記基板の前記表面に形成される第二の閉ループ構成のトレンチであって、前記第二の閉ループ構成のトレンチは側壁と底部を有し、さらに、前記第二の閉ループ構成のトレンチの前記側壁と前記底部の上に形成された第二の誘電体ライナーと、前記第二の誘電体ライナーの上に形成され、かつ、前記ソース領域に電気的に接続される第二の導電性部材と

10

20

を有する、前記第二の閉ループ構成のトレンチと、

を含む、縦型MOSトランジスタであって、

前記ゲートトレンチは前記第一の閉ループ構成のトレンチと前記第二の閉ループ構成のトレンチの間に配置され、

前記ソース領域の第一の部分は前記ゲートトレンチの前記側壁と前記第一の閉ループ構成のトレンチの前記側壁の間の全体に延在し、

前記ソース領域の第二の部分は前記ゲートトレンチの前記側壁と前記第二の閉ループ構成のトレンチの前記側壁の間の全体に延在する、縦型MOSトランジスタ。

## 【請求項2】

請求項1に記載された縦型MOSトランジスタであって、

前記二つの閉ループ構成のトレンチの内部領域が、前記第一の導電型を有し、ドレインコンタクトを形成する、縦型MOSトランジスタ。

## 【請求項3】

請求項1に記載された縦型MOSトランジスタであって、

前記第一の閉ループ構成のトレンチと前記第二の閉ループ構成のトレンチの深さが、1 $\mu\text{m}$ から5 $\mu\text{m}$ の間の値をとる、縦型MOSトランジスタ。

## 【請求項4】

請求項1に記載された縦型MOSトランジスタであって、

前記第一の閉ループ構成のトレンチと前記第二の閉ループ構成のトレンチの幅が、0.5 $\mu\text{m}$ から1.5 $\mu\text{m}$ の間の値をとる、縦型MOSトランジスタ。

## 【請求項5】

請求項1に記載された縦型MOSトランジスタであって、

前記第一の誘電体ライナーと第二の誘電体ライナーがシリコン窒化物を含む、縦型MOSトランジスタ。

## 【請求項6】

請求項1に記載された縦型MOSトランジスタであって、

前記第一の誘電体ライナーと第二の誘電体ライナーがシリコンオキシナイトライドを含む、縦型MOSトランジスタ。

## 【請求項7】

請求項1に記載された縦型MOSトランジスタであって、

前記半導体基板の前記表面に形成され、側壁と底部を有する第二のゲートトレンチであって、前記第二のゲートトレンチの前記側壁と前記底部の上に第二のゲート誘電層が形成され、前記第二のゲート誘電層の上に第二のゲートが形成される、前記第二のゲートトレンチをさらに含み、

前記第二のゲートトレンチは前記第一の閉ループ構成のトレンチと前記第二の閉ループ構成のトレンチの間に配置され、

前記ソース領域の第三の部分は前記第二のゲートトレンチの前記側壁と前記第一の閉ループ構成のトレンチの前記側壁の間の全体に延在し、

前記ソース領域の第四の部分は前記第二のゲートトレンチの前記側壁と前記第二の閉ループ構成のトレンチの前記側壁の間の全体に延在する、縦型MOSトランジスタ。

## 【請求項8】

請求項1に記載された縦型MOSトランジスタであって、

前記基板の前記表面に形成される第三の閉ループ構成のトレンチであって、前記第三の閉ループ構成のトレンチは側壁と底部を有し、さらに、前記第三の閉ループ構成のトレンチの前記側壁と前記底部の上に形成される第三の誘電体ライナーと、前記第三の誘電体ライナーの上に形成され、かつ、前記ソース領域に電気的に接続される第三の導電性部材とを有する、前記第三の閉ループ構成のトレンチと、

前記半導体基板の前記表面に形成され、側壁と底部を有する第二のゲートトレンチであって、前記第二のゲートトレンチの前記側壁と前記底部の上に第二のゲート誘電層が形成され、前記第二のゲート誘電層の上に第二のゲートが形成される、前記第二のゲートトレンチ

10

20

30

40

50

ンチと、

をさらに含み、

前記第二のゲートトレンチは前記第二の閉ループ構成のトレンチと前記第三の閉ループ構成のトレンチの間に配置され、

前記ソース領域の第三の部分は前記第二のゲートトレンチの前記側壁と前記第二の閉ループ構成のトレンチの前記側壁の間の全体に延在し、

前記ソース領域の第四の部分は前記第二のゲートトレンチの前記側壁と前記第三の閉ループ構成のトレンチの前記側壁の間の全体に延在する、縦型MOSトランジスタ。

【請求項9】

請求項8に記載された縦型MOSトランジスタであって、

10

前記半導体基板の前記表面に形成され、側壁と底部を有する第三のゲートトレンチであって、前記第三のゲートトレンチの前記側壁と前記底部の上に第三のゲート誘電層が形成され、前記第三のゲート誘電層の上に第三のゲートが形成される、前記第三のゲートトレンチと、

前記半導体基板の前記表面に形成され、側壁と底部を有する第四のゲートトレンチであって、前記第四のゲートトレンチの前記側壁と前記底部の上に第四のゲート誘電層が形成され、前記第四のゲート誘電層の上に第四のゲートが形成される、前記第四のゲートトレンチと、

をさらに含み、

20

前記第三のゲートトレンチは前記第一の閉ループ構成のトレンチと前記第二の閉ループ構成のトレンチの間に配置され、

前記第四のゲートトレンチは前記第二の閉ループ構成のトレンチと前記第三の閉ループ構成のトレンチの間に配置され、

前記ソース領域の第五の部分は前記第三のゲートトレンチの前記側壁と前記第一の閉ループ構成のトレンチの前記側壁の間の全体に延在し、

前記ソース領域の第六の部分は前記第三のゲートトレンチの前記側壁と前記第二の閉ループ構成のトレンチの前記側壁の間の全体に延在し、

前記ソース領域の第七の部分は前記第四のゲートトレンチの前記側壁と前記第二の閉ループ構成のトレンチの前記側壁の間の全体に延在し、

前記ソース領域の第八の部分は前記第四のゲートトレンチの前記側壁と前記第三の閉ループ構成のトレンチの前記側壁の間の全体に延在する、縦型MOSトランジスタ。

30

【発明の詳細な説明】

【技術分野】

【0001】

本願は、概して半導体デバイスに関し、特に、半導体デバイスにおけるドレイン拡張されたトランジスタに関する。

【背景技術】

【0002】

拡張されたドレイン金属酸化物半導体(MOS)トランジスタは、オン状態でのトランジスタの抵抗と、トランジスタを含む基板の頂部表面においてトランジスタが占める横方向のエリアと、トランジスタの最大動作電位を制限する、トランジスタのドレインノードとソースノードとの間のブレークダウン電位とにより特徴付けられ得る。オン状態抵抗及びブレークダウン電位の所与の値のためトランジスタのエリアを低減することが望ましい場合がある。そのエリアを低減するための一つの手法は、ドリフト領域におけるドレイン電流が基板の頂部表面へ垂直に流れるように、拡張されたドレインにおいて垂直の方位にドリフト領域を構成することである。プレーナープロセスを用いて半導体デバイスにおいて垂直に向けられるドリフト領域をインテグレートする一方で、製造コスト及び複雑度を所望のレベルまで制限することが課題となり得る。

40

【発明の概要】

【0003】

50

記載される例において、垂直のドレイン拡張されたMOSトランジスタを有する半導体デバイスが、トランジスタの垂直ドリフト領域を画定するように、及びディープトレンチ構造の少なくとも一つのインスタンスだけ垂直ドリフト領域から分離される、ドリフト領域に近接する少なくとも一つの垂直ドレインコンタクト領域を画定するようにディープトレンチ構造を形成することによって形成され得る。垂直ドレインコンタクト領域にドーパントが注入され、注入されたドーパントが、ディープトレンチ構造の底部に近接して拡散するように半導体デバイスがアニーリングされる。垂直ドレインコンタクト領域は、介在するディープトレンチ構造の底部において近接する垂直ドリフト領域に対する電気的コンタクトを成す。少なくとも一つのゲート、ボディ領域、及びソース領域が、半導体デバイスの基板の頂部表面において又はそこに近接して、ドリフト領域上方に形成される。ディープトレンチ構造は、ドリフト領域のためのRESURF領域を形成するため間隔が空けられる。

【図面の簡単な説明】

【0004】

【図1】垂直のドレイン拡張されたMOSトランジスタを有する半導体デバイスの断面図である。

【0005】

【図2】垂直のドレイン拡張されたMOSトランジスタを有する別の半導体デバイスの断面図である。

【0006】

【図3】垂直のドレイン拡張されたMOSトランジスタを有する更なる半導体デバイスの断面図である。

【0007】

【図4】垂直のドレイン拡張されたMOSトランジスタを有する別の半導体デバイスの断面図である。

【0008】

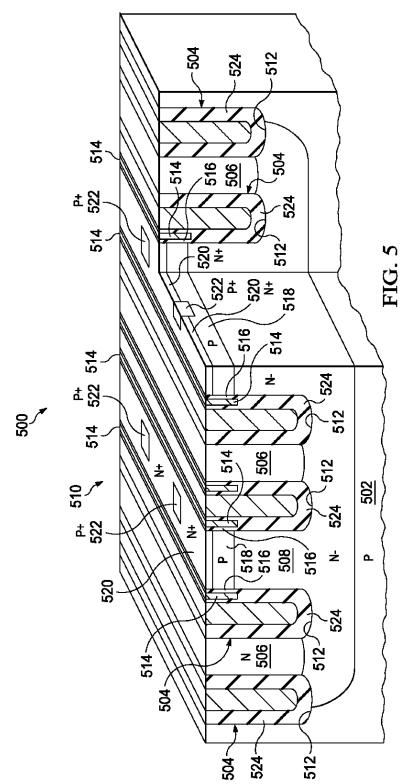

【図5】垂直のドレイン拡張されたMOSトランジスタを有する更なる半導体デバイスの断面図である。

【0009】

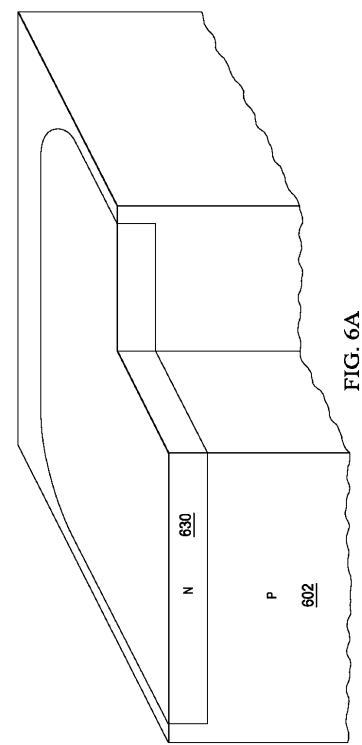

【図6A】製造の継続的段階における半導体デバイスの断面図である。

30

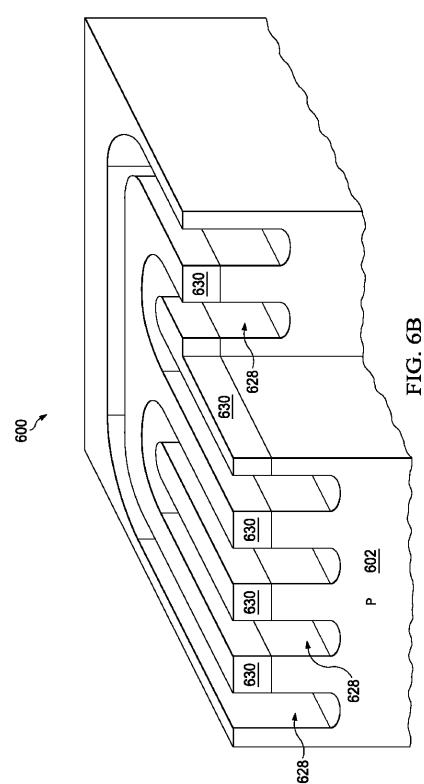

【図6B】製造の継続的段階における半導体デバイスの断面図である。

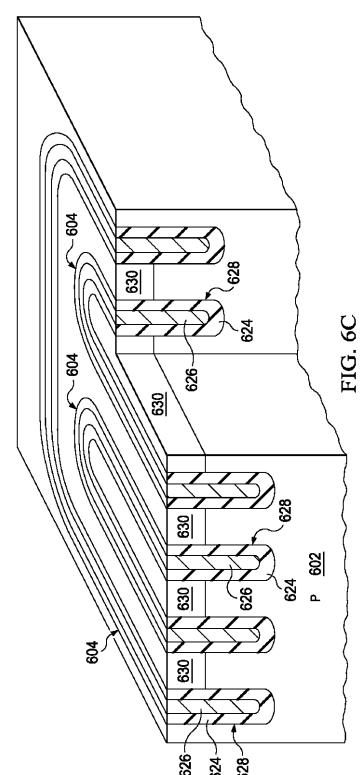

【図6C】製造の継続的段階における半導体デバイスの断面図である。

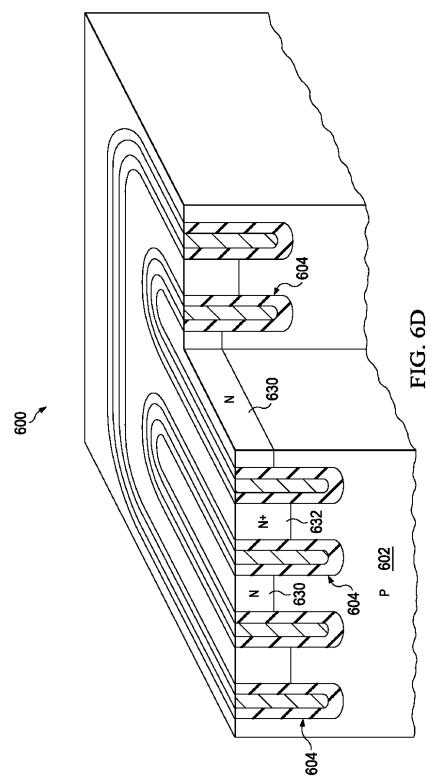

【図6D】製造の継続的段階における半導体デバイスの断面図である。

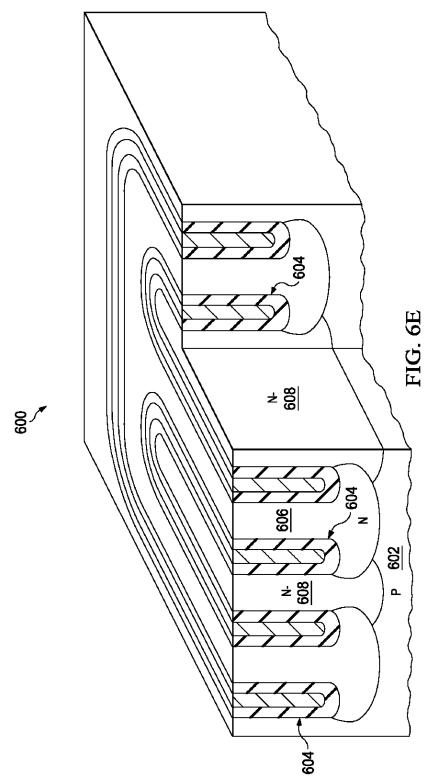

【図6E】製造の継続的段階における半導体デバイスの断面図である。

【0010】

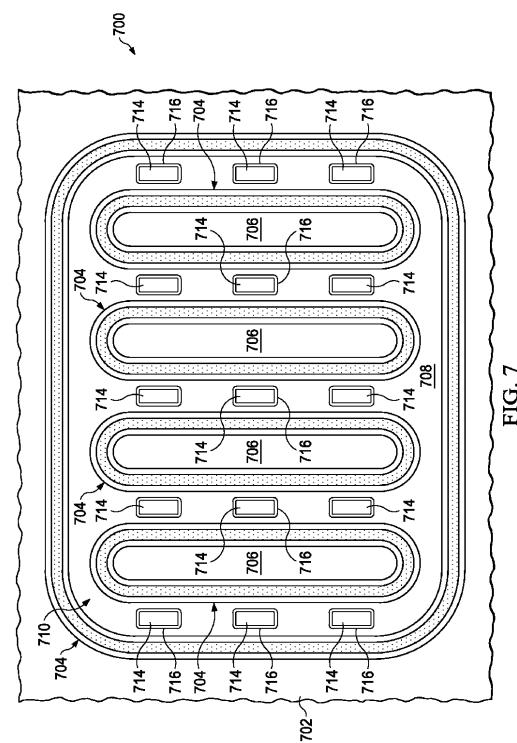

【図7】垂直のドレイン拡張されたMOSトランジスタを有する半導体デバイスの上面図である。

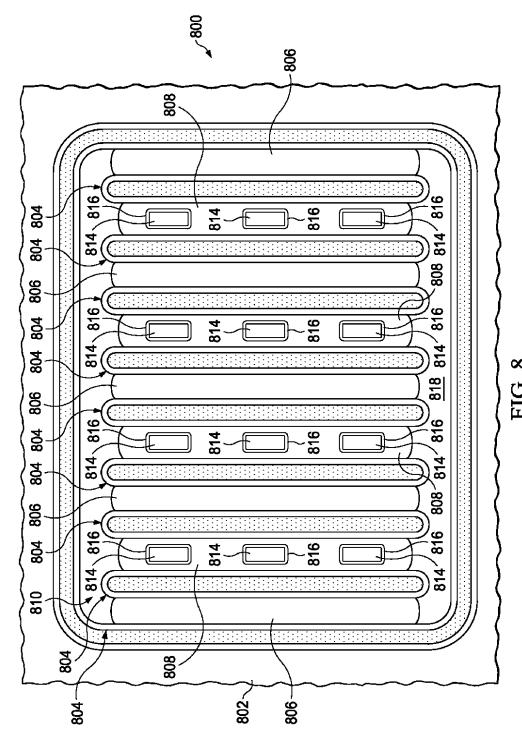

【図8】垂直のドレイン拡張されたMOSトランジスタを有する半導体デバイスの上面図である。

【発明を実施するための形態】

【0011】

下記の同時係属中の特許出願が参照により本願に組み込まれる。

【特許文献1】米国特許出願番号U.S.14/044,915

【特許文献2】米国特許出願番号U.S.14/044,926

【0012】

少なくとも一つの例において、半導体デバイスが、垂直のドレイン拡張されたMOSトランジスタと少なくとも一つの他のトランジスタとを含む集積回路であり得る。半導体デバイスは、別の例において、垂直のドレイン拡張されたMOSトランジスタが唯一のトランジスタであるディスクリートデバイスであり得る。

【0013】

10

20

30

40

50

この説明の目的のため、トランジスタに対する「特定の抵抗率」という用語は、そのトランジスタが形成される基板の頂部表面においてトランジスタが占めるエリアを、そのトランジスタがフルにオンになるときのトランジスタの抵抗で乗じた積である。

【0014】

この説明の目的のため、「RESURF」という用語は、近傍の半導体領域における電界を低減する材料を指す。例えば、RESURF領域は、近傍の半導体領域とは反対の導電型の半導体領域であり得る。RESURF構造は、アペルラの「薄層高電圧デバイス」Philips J, Res. 35 1-13, 1980に記載されている。

【非特許文献1】Appels, et al, "Thin Layer High Voltage Devices" Philips J, Res. 35 1-13, 1980

10

【0015】

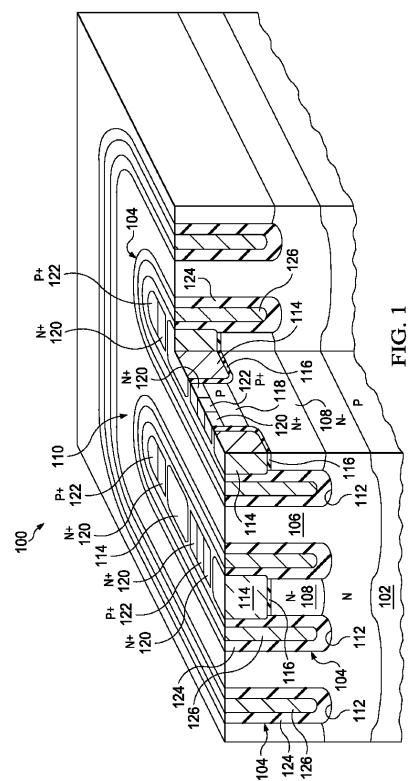

本開示に記載される例は、nチャネルデバイスを説明する。対応するpチャネルデバイスが、ドーピング極性の適切な変更により形成され得る。図1は、垂直のドレイン拡張されたMOSトランジスタを有する半導体デバイスの断面図である。半導体デバイス100が、p型半導体基板102内及び上に形成される。ディープトレンチ構造104が、垂直のドレイン拡張されたMOSトランジスタ110の、少なくとも一つのn型の垂直ドレインコンタクト領域106及び少なくとも一つのn型の垂直に向けられるドリフト領域108を画定するように基板102に配置される。垂直ドレインコンタクト領域106は、ディープトレンチ構造104により少なくとも2つの対向する側部で区分される。垂直ドレインコンタクト領域106は、n型であり、この例ではディープトレンチ構造104の底部112より下に延在する。垂直ドレインコンタクト領域106は、図1に示すように、垂直に向けられるドリフト領域108を基板102のp型底部領域から分離するように、ディープトレンチ構造104の底部112の下で横方向に延在し得る。他の例において、垂直ドレインコンタクト領域106は、一層制限された横方向範囲を有し得る。垂直に向けられるドリフト領域108は、n型であり、ディープトレンチ構造104の底部に近接する垂直ドレインコンタクト領域106への電気的接続を成す。この例では、垂直ドレインコンタクト領域106への電気的接続は、基板102の頂部表面において成される。

20

【0016】

少なくとも一つのゲート114及び対応するゲート誘電体層116が、垂直に向けられるドリフト領域108の上に配置される。この例では、ゲート114は、基板102内のトレンチに配置され、ディープトレンチ構造104の隣り合うインスタンス間に延在する。少なくとも一つのp型ボディ領域118が、ゲート114及び垂直に向けられるドリフト領域108の近傍で基板102に配置される。少なくとも一つのn型ソース領域120が、ゲート114の近傍で基板に配置される。一つ又はそれ以上の任意選択のp型ボディコンタクト領域122が、ボディ領域118に隣接して基板102に配置され得る。この例では、ソース領域120及びボディコンタクト領域122への電気的接続は、基板102の頂部表面において成される。ゲート他の構成を、図1に示す、ディープトレンチ構造104、垂直ドレインコンタクト領域106、及び垂直に向けられるドリフト領域108の構成を備えた、垂直のドレイン拡張されたMOSトランジスタ110に用いることができる。

30

【0017】

ディープトレンチ構造104は、1~5ミクロンの深さ及び0.5~1.5ミクロン幅であり得る。例えば、2.5ミクロンの深さのディープトレンチ構造104は、垂直のドレイン拡張されたMOSトランジスタ110に対し30ボルトオペレーションを提供し得る。4ミクロンの深さのディープトレンチ構造104は、垂直のドレイン拡張されたMOSトランジスタ110のための50ボルトオペレーションを提供し得る。ディープトレンチ構造104は、誘電体ライナー124を有し、導電性中央部材126を任意選択で有し得る。垂直に向けられるドリフト領域108に隣接するディープトレンチ構造104のインスタンスが、垂直に向けられるドリフト領域108のためのRESURF領域を提供するため0.5~2ミクロン離れて配置され得る。垂直ドレインコンタクト領域106に

40

50

隣接するディープトレンチ構造 104 のインスタンスが、0.5 ~ 2.5 ミクロン離れて配置され得る。垂直のドレイン拡張されたMOSトランジスタ 110 のオペレーションの間、存在する場合、導電性中央部材 126 が、垂直に向けられるドリフト領域 108 におけるピーク電界を低減するように電気的にバイアスされ得る。例えば、導電性中央部材 126 は、ソース領域 120 に、ゲート 114 に、又は所望の電位を有するバイアスソースに接続され得る。

【0018】

垂直に向けられるドリフト領域 108 のインスタンスが、垂直ドレインコンタクト領域 106 近傍に配置される。例えば、垂直に向けられるドリフト領域 108 のインスタンスは、図 1 に示すように、垂直ドレインコンタクト領域 106 と互い違いにされ得る。ディープトレンチ構造 104 は、図 1 に示すように、垂直に向けられるドリフト領域 108 を囲み得る。図 1 に示すように、垂直ドレインコンタクト領域 106 は連続的であり得る。ディープトレンチ構造 104 の互い違いの構成をこれ以降に説明する。ディープトレンチ構造 104 が、垂直に向けられるドリフト領域 108 のための RESURF 領域を提供するように、垂直のドレイン拡張されたMOSトランジスタ 110 を形成することが、垂直のドレイン拡張されたMOSトランジスタ 110 の動作電圧と特定の抵抗率との間の所望のバランスを提供し得る。垂直に向けられるドリフト領域 108 を基板 102 の底部領域から隔離するように垂直ドレインコンタクト領域 106 を形成することが、垂直のドレイン拡張されたMOSトランジスタ 110 の抵抗を望ましく低減し得る。

【0019】

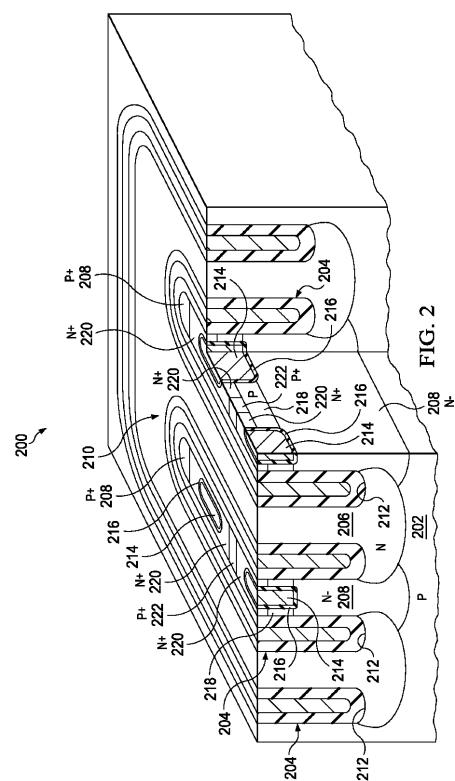

図 2 は、垂直のドレイン拡張されたMOSトランジスタを有する別の半導体デバイスの断面図である。半導体デバイス 200 が、p 型半導体基板 202 内及び上に形成される。図 1 を参照して説明したように、垂直のドレイン拡張されたMOSトランジスタ 210 の、少なくとも一つの n 型垂直ドレインコンタクト領域 206 及び少なくとも一つの n 型の垂直に向けられるドリフト領域 208 を画定するように、ディープトレンチ構造 204 が基板 202 に配置され得る。垂直ドレインコンタクト領域 206 は、ディープトレンチ構造 204 により少なくとも 2 つの対向する側部で区分される。垂直ドレインコンタクト領域 206 は、n 型であり、この例ではディープトレンチ構造 204 の底部 212 より下に延在する。垂直ドレインコンタクト領域 206 は、ディープトレンチ構造 204 の底部 212 を超えて横方向に延在し得るが、図 2 に示すように、垂直に向けられるドリフト領域 208 を基板 202 の底部領域から隔離するほど充分に延在しない。他の例において、垂直ドレインコンタクト領域 206 は、一層制限された垂直及び / 又は横方向範囲を有し得る。垂直に向けられるドリフト領域 208 は、n 型であり、ディープトレンチ構造 204 の底部に近接する垂直ドレインコンタクト領域 206 への電気的接続を成す。この例では、垂直ドレインコンタクト領域 206 への電気的接続は、基板 202 の頂部表面において成される。

【0020】

少なくとも一つのゲート 214 及び対応するゲート誘電体層 216 が、垂直に向けられるドリフト領域 208 の上に配置される。この例では、ゲート 214 は、基板 202 内のトレンチに配置され、ディープトレンチ構造 204 の隣り合うインスタンスに隣接しない。少なくとも一つの p 型ボディ領域 218 が、ゲート 214 及び垂直に向けられるドリフト領域 208 近傍で基板 202 に配置される。少なくとも一つの n 型ソース領域 220 が、ゲート 214 近傍の基板に配置される。一つ又はそれ以上の任意選択の p 型ボディコンタクト領域 222 が、ボディ領域 218 に隣接して基板 202 に配置され得る。この例では、ソース領域 220 及びボディコンタクト領域 222 への電気的接続は、基板 202 の頂部表面において成される。ゲートの他の構成を、図 2 に示す、ディープトレンチ構造 204、垂直ドレインコンタクト領域 206、及び垂直に向けられるドリフト領域 208 の構成を備えた、垂直のドレイン拡張されたMOSトランジスタ 210 に用いることができる。

【0021】

10

20

30

40

50

垂直に向けられるドリフト領域 208 のインスタンスが、垂直ドレインコンタクト領域 206 近傍に配置される。例えば、垂直に向けられるドリフト領域 208 のインスタンスは、図 2 に示すように、垂直ドレインコンタクト領域 206 と互い違いにされ得る。ディープトレンチ構造 204 は、図 2 に示すように、垂直に向けられるドリフト領域 108 を囲み得る。図 2 に示すように、垂直ドレインコンタクト領域 106 は連続的であり得る。ディープトレンチ構造 204 が、垂直に向けられるドリフト領域 208 のための R E S U R F 領域を提供するように、垂直のドレイン拡張された M O S トランジスタ 210 を形成することが、垂直のドレイン拡張された M O S トランジスタ 210 のための動作電圧及び特定の抵抗率との間の所望のバランスを提供し得る。ディープトレンチ構造 204 の底部 212 を超えて横方向に延在するように、ただし、垂直に向けられるドリフト領域 208 を基板 202 の底部領域から隔離するほど充分に延在しないように、垂直ドレインコンタクト領域 206 を形成することが、一層大きな垂直距離に沿った垂直に向けられるドリフト領域 208 のデブリーションを可能にし得、一層高い電圧でのオペレーションを所望に可能にし得る。

10

#### 【 0 0 2 2 】

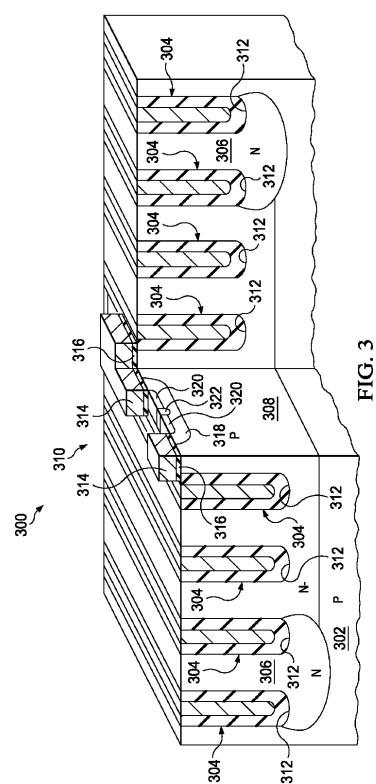

図 3 は、垂直のドレイン拡張された M O S トランジスタを有する更なる半導体デバイスの断面図である。半導体デバイス 300 が、p 型半導体基板 302 内及び上に形成される。ディープトレンチ構造 304 が、図 1 を参照して説明したように、垂直のドレイン拡張された M O S トランジスタ 310 の、少なくとも一つの n 型垂直ドレインコンタクト領域 306 及び少なくとも一つの n 型の垂直に向けられるドリフト領域 308 を画定するように、基板 302 に配置され得る。垂直ドレインコンタクト領域 306 は、ディープトレンチ構造 304 により少なくとも 2 つの対向する側部で区分される。垂直ドレインコンタクト領域 306 は、n 型であり、図 3 に示すようにディープトレンチ構造 304 の底部 312 より下に延在し得る。この例では、垂直に向けられるドリフト領域 308 は、ディープトレンチ構造 304 の少なくとも 2 つのインスタンスだけ垂直ドレインコンタクト領域 306 から横方向にずらされて、垂直のドレイン拡張された M O S トランジスタ 310 の拡張されたドレインに水平ドリフト構成要素を提供する。この例では、垂直ドレインコンタクト領域 306 への電気的接続は、基板 302 の頂部表面において成される。

20

#### 【 0 0 2 3 】

少なくとも一つのゲート 314 及び対応するゲート誘電体層 316 が、垂直に向けられるドリフト領域 308 の上に配置される。この例では、ゲート 314 は、p 型ボディ領域 318 及び n 型ソース領域 320 の上の基板 302 上方に配置される。一つ又はそれ以上の任意選択の p 型ボディコンタクト領域 322 が、ボディ領域 318 に隣接して基板 302 に配置され得る。この例では、ソース領域 320 及びボディコンタクト領域 322 への電気的接続が、基板 302 の頂部表面において成される。ゲートの他の構成が、図 3 に示す、ディープトレンチ構造 304、垂直ドレインコンタクト領域 306、及び横方向にずらされた垂直に向けられるドリフト領域 308 の構成を備えた、垂直のドレイン拡張された M O S トランジスタ 310 に用いられ得る。垂直に向けられるドリフト領域 308 を、垂直ドレインコンタクト領域 306 から横方向にずらして形成することにより、垂直に向けられるドリフト領域 308 の横方向デブリーションが可能となり得、また、ディープトレンチ構造 304 の一層深いインスタンスを必要とすることなく垂直のドレイン拡張された M O S トランジスタ 310 の動作電圧が有利に増大され得る。

30

40

#### 【 0 0 2 4 】

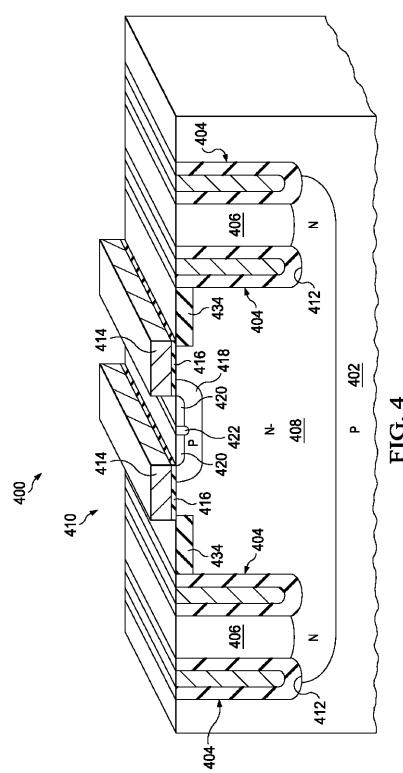

図 4 は、垂直のドレイン拡張された M O S トランジスタを有する別の半導体デバイスの断面図である。半導体デバイス 400 が、p 型半導体基板 402 内及び上に形成される。ディープトレンチ構造 404 が、垂直のドレイン拡張された M O S トランジスタ 410 の、少なくとも一つの垂直ドレインコンタクト領域 406 及び少なくとも一つの垂直に向けられるドリフト領域 408 を画定するように、図 1 を参照して説明したように基板 402 に配置される。垂直ドレインコンタクト領域 406 は、ディープトレンチ構造 404 により少なくとも 2 つの対向する側部で区分される。垂直ドレインコンタクト領域 406 は、

50

n型であり、この例ではディープトレンチ構造404の底部412に近接して延在するが、底部412より下には延在しない。垂直に向けられるドリフト領域408は、n型であり、ディープトレンチ構造404の底部412に近接する垂直ドレインコンタクト領域406への電気的接続を成す。

【0025】

少なくとも一つのゲート414及び対応するゲート誘電体層416が、垂直に向けられるドリフト領域408の上に配置される。この例では、ゲート414は、p型ボディ領域418及びn型ソース領域420の上の基板402上方に配置される。一つ又はそれ以上の任意選択のp型ボディコンタクト領域422が、ボディ領域418に隣接して基板402に配置され得る。この例では、ゲート414の直下の垂直に向けられるドリフト領域408の一部が、フィールド酸化物434などの誘電性材料434により、ディープトレンチ構造404の最も近いインスタンスから横方向に分離される。このような構成が、垂直のドレイン拡張されたMOSトランジスタ410に水平ドリフト構成要素を付加し得、また、垂直のドレイン拡張されたMOSトランジスタ410の動作電圧を有利に増大させ得る。ゲート414の直下の垂直に向けられるドリフト領域408の一部はまた、場合によつては、図3に示すように、ディープトレンチ構造404の少なくとも2つのインスタンスにより垂直ドレインコンタクト領域406の最も近いインスタンスから横方向に分離され得る。ゲートの他の構成が、図4に示す、ディープトレンチ構造404、垂直ドレインコンタクト領域406、及び垂直に向けられるドリフト領域408の構成を備えた、垂直のドレイン拡張されたMOSトランジスタ410に用いられ得る。垂直に向けられるドリフト領域408を垂直ドレインコンタクト領域406から横方向にずらして形成することにより、垂直に向けられるドリフト領域408の横方向のデブリーションが可能となり得、また、一層深いインスタンス又はディープトレンチ構造404の付加的なインスタンスを必要とすることなく垂直のドレイン拡張されたMOSトランジスタ410の動作電圧を有利に増大させ得る。

【0026】

図5は、垂直のドレイン拡張されたMOSトランジスタを有する更なる半導体デバイスの断面図である。半導体デバイス500が、図1を参照して説明したようにp型半導体基板502内及び上に形成される。ディープトレンチ構造504が、垂直のドレイン拡張されたMOSトランジスタ510の、少なくとも一つの垂直ドレインコンタクト領域506及び少なくとも一つの垂直に向けられるドリフト領域508の垂直の部分を画定するように、図1を参照して説明したように基板502に配置される。垂直ドレインコンタクト領域506は、ディープトレンチ構造504により少なくとも2つの対向する側部で区分される。垂直ドレインコンタクト領域506は、n型であり、この例では、ディープトレンチ構造504の底部512に近接して延在し、及び場合によつては底部512より下に延在する。この例では、垂直に向けられるドリフト領域508は、ディープトレンチ構造504の底部512より下に延在し、連続的なn型領域を形成するために横方向に延在する。垂直に向けられるドリフト領域508は、n型であり、垂直ドレインコンタクト領域506への電気的接続を成す。このような構成が、垂直のドレイン拡張されたMOSトランジスタ510のオン状態抵抗を有利に低減する。

【0027】

少なくとも一つのゲート514及び対応するゲート誘電体層516が、垂直に向けられるドリフト領域508上方に配置される。この例では、ゲート514は、p型ボディ領域518及びn型ソース領域520近傍で、ディープトレンチ構造504の誘電体ライナー524に配置される。一つ又はそれ以上の任意選択のp型ボディコンタクト領域522が、ボディ領域518に隣接して基板502に配置され得る。ゲートの他の構成を、図5に示す、ディープトレンチ構造504、垂直ドレインコンタクト領域506、及び垂直に向けられるドリフト領域508の構成を備えた、垂直のドレイン拡張されたMOSトランジスタ510に用いることができる。

【0028】

10

20

30

40

50

図 6 A ~ 図 6 E は、製造の継続的段階における半導体デバイスの断面図である。図 6 A を参照すると、半導体デバイス 600 が、単結晶シリコンウェハなどの p 型半導体基板 602 内及び上に形成される。ドリフト領域イオン注入プロセスが実施され、このプロセスは、ドリフト注入された領域 630 を形成するために、垂直に向けられるドリフト領域のために画定されたエリアにおける基板 602 にリンなどの n 型ドーパントを注入する。例えば、ドリフト領域イオン注入プロセスのドーズ量が  $1 \times 10^{12} \text{ cm}^{-2} \sim 1 \times 10^{13} \text{ cm}^{-2}$  あり得る。この実施例の少なくとも一つのバージョンにおいて、図 6 A に示すように、ドリフト注入された領域 630 は、垂直ドレインコンタクト領域のために画定されたエリアにわたって延在し得る。代替のバージョンにおいて、ドリフト注入された領域 630 は、垂直に向けられるドリフト領域のために画定された基板の或るエリアに限定され得る。

#### 【 0029 】

図 6 B を参照すると、基板 602 の頂部表面の上にハードマスク材料の層を形成することで始まるプロセスなどによって、ディープ隔離トレンチ 628 が基板 602 に形成される。フォトリソグラフィによりエッチングマスクを形成することによりハードマスクが形成され得、その後、反応性イオンエッチング (RIE) プロセスを用いてディープ隔離トレンチ 628 のために画定された領域の上のハードマスク材料を取り除くことが続く。ハードマスクをパターニングした後、Bosch ディープ RIE プロセス又は連続的ディープ RIE プロセスなどの異方性エッチプロセスを用いて、ディープ隔離トレンチ 628 における基板 602 から材料が取り除かれる。

#### 【 0030 】

図 6 C を参照すると、誘電体ライナー 624 が基板 602 に隣接するように、ディープ隔離トレンチ 628 に誘電体ライナー 624 が形成される。例えば、誘電体ライナー 624 は、熱成長された二酸化シリコンを含み得る。誘電体ライナー 624 はまた、化学気相成長 (CVD) プロセスによって形成される、二酸化シリコン、シリコン窒化物、及び / 又はシリコンオキシナイトライドなどの誘電性材料の一つ又はそれ以上の層を含み得る。

#### 【 0031 】

任意選択の導電性中央部材 626 が、誘電体ライナー 624 上に形成され得る。例えば、導電性中央部材 626 は、SiH<sub>4</sub> ガスを 580 ~ 650 の温度で低圧力アクラー内で熱分解させることによって形成される、通常はポリシリコンと称される、多結晶シリコンを含み得る。ポリシリコンは、所望の電気伝導率を提供するために形成の間ドープされ得る。誘電体ライナー 624 で及び存在する場合には導電性中央部材 626 で充填されるディープ隔離トレンチ 628 は、ディープトレンチ構造 604 を形成する。誘電体ライナー 624 の形成からの基板 602 の頂部表面の上の不要な誘電体材料、及び導電性中央部材 626 の形成からの基板 602 の頂部表面の上の不要な導電性材料は、エッチバック及び / 又は化学機械研磨 (CMP) プロセスなどを用いることによって取り除かれ得る。

#### 【 0032 】

図 6 D を参照すると、ドレインコンタクトイオン注入プロセスが実施され、このプロセスは、ドレインコンタクト注入された領域 632 を形成するために、垂直ドレインコンタクト領域のために画定されたエリアにおける基板 602 にリンなどの n 型ドーパントを注入する。ドリフト領域イオン注入プロセスのドーズ量は、ドリフト領域イオン注入ドーズ量より少なくとも 10 倍高く、例えば  $1 \times 10^{16} \text{ cm}^{-2} \sim 3 \times 10^{16} \text{ cm}^{-2}$  あり得る。ドレインコンタクトイオン注入プロセスは、所望の電気伝導率を得るために、導電性中央部材 626 のポリシリコンバージョンにドーパントを提供し得る。

#### 【 0033 】

図 6 E を参照すると、熱駆動オペレーションが実施される。このオペレーションは、ドリフト注入された領域 630 及びドレインコンタクト注入された領域 632 における注入されたドーパントを活性化及び拡散するように、及びそれにより、それぞれ、垂直に向けられるドリフト領域 608 及び垂直ドレインコンタクト領域 606 を形成するように、基

10

20

30

40

50

板 602 を加熱する。熱駆動オペレーションの条件は、ディープトレンチ構造 604 の深さ、及びディープトレンチ構造 604 の底部における垂直ドレインコンタクト領域 606 の所望の横方向範囲に依存する。例えば、2.5 ミクロンの深さのディープトレンチ構造 604 を備えた垂直のドレイン拡張されたMOSトランジスタは、1100 で 3.5 ~ 4 時間、或いは、1125 で 2 時間又は 1050 で 1.2 時間などの同等のアニール条件で基板 602 を加熱する熱駆動オペレーションを有し得る。

【0034】

図 7 及び図 8 は、垂直のドレイン拡張されたMOSトランジスタを有する半導体デバイスの上面図である。図 7 及び図 8 に示すゲートは、図 2 を参照して説明したようにトレンチに配置されるが、これらの例においてゲートの他の構成も用いられ得る。図 7 を参照すると、半導体デバイス 700 が、図 6 A を参照して説明したように半導体基板 702 内及び上に形成される。閉ループ構成を備えたディープトレンチ構造 704 が基板 702 に配置され得る。ディープトレンチ構造 704 のインスタンスが、垂直ドレインコンタクト領域 706 を横方向に囲む。垂直のドレイン拡張されたMOSトランジスタ 710 のゲート 714 及びゲート誘電体層 716 が、垂直ドレインコンタクト領域 706 を横方向に囲むディープトレンチ構造 704 間に配置される。垂直ドリフト領域 708 が、垂直ドレインコンタクト領域 706 を囲むディープトレンチ構造 704 間に配置される。垂直のドレイン拡張されたMOSトランジスタ 710 のボディ領域、ソース領域、及びボディコンタクト領域は、垂直ドリフト領域 708 及び垂直ドレインコンタクト領域 706 の配置をよりはっきりと示すために図 7 には示していない。ディープトレンチ構造 704 のインスタンスが、垂直のドレイン拡張されたMOSトランジスタ 710 を横方向に囲む。垂直ドレインコンタクト領域 706 への電気的接続は、基板 702 の頂部表面において成される。垂直ドレインコンタクト領域 706 をディープトレンチ構造 704 で囲むことが、垂直のドレイン拡張されたMOSトランジスタ 710 のドレインコンタクトとボディ領域との間のブレークダウン電界を防止し得、また、垂直のドレイン拡張されたMOSトランジスタ 710 を、その他の方式よりも高い電圧で有利に動作させ得る。

【0035】

図 8 を参照すると、半導体デバイス 800 が、図 6 A を参照して説明したように半導体基板 802 内及び上に形成される。線形構成を備えたディープトレンチ構造 804 が基板 802 に配置され得る。垂直ドレインコンタクト領域 806 が、線形ディープトレンチ構造 804 の隣り合う対の間に配置される。ゲート 814 及びゲート誘電体層 816 が、垂直ドレインコンタクト領域 806 と互い違いに、ディープトレンチ構造 804 の隣り合う対の間に配置される。垂直ドリフト領域 808 が、ゲート 814 を備えたディープトレンチ構造 804 の互い違いの対の間に配置される。ボディ領域 818 が、線形ディープトレンチ構造 804 の周りに配置され、ゲート 814 に隣接するように垂直ドリフト領域 808 の上に延在する。この場合、垂直ドリフト領域 808 の上に延在するボディ領域 818 の一部と、垂直のドレイン拡張されたMOSトランジスタ 810 のソース領域及びボディコンタクト領域は、垂直ドリフト領域 808 及び垂直ドレインコンタクト領域 806 の配置をよりはっきりと示すために図 8 には示していない。ディープトレンチ構造 804 のインスタンスが、垂直のドレイン拡張されたMOSトランジスタ 810 を横方向に囲む。垂直ドレインコンタクト領域 806 への電気的接続は、基板 802 の頂部表面において成される。線形ディープトレンチ構造 804 間に垂直ドレインコンタクト領域 806 を配置することが、垂直のドレイン拡張されたMOSトランジスタ 810 のために必要とされるエリアを有利に低減し得、それにより、半導体デバイス 800 の製造コストを低減する。

【0036】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、多くの他の実施例が可能である。

【 四 1 】

【図2】

【図3】

【 図 4 】

【図5】

【図 6 A】

【図 6 B】

【図6C】

【図 6 D】

【 図 6 E 】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 K |

| H 01 L | 29/78 | 6 5 2 Z |

| H 01 L | 29/78 | 6 5 3 A |

| H 01 L | 29/06 | 3 0 1 D |

| H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 29/78 | 6 5 8 A |

(72)発明者 マリー デニソン

アメリカ合衆国 75025 テキサス州 プラノ, ソタ グランデ ドライブ 9817

(72)発明者 サミール ペンハルカル

アメリカ合衆国 75013 テキサス州 アレン, バーンサイド ドライブ 2032

(72)発明者 グル マートゥル

アメリカ合衆国 75025 テキサス州 プラノ, オクサデンタル ロード 7117

審査官 棚田 一也

(56)参考文献 特表2005-525703(JP, A)

特開平4-171765(JP, A)

特開2007-220711(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 29 / 06