## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) Int. Cl.

*G11C 7/22* (2006.01)*G11C 7/20* (2006.01)*G11C 8/18* (2006.01)

(45) 공고일자 2006년03월28일

(11) 등록번호 10-0564635

(24) 등록일자 2006년03월21일

(21) 출원번호 10-2004-0085381

(22) 출원일자 2004년10월25일

(65) 공개번호

(43) 공개일자

(73) 특허권자 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 최희주

경기 수원시 영통구 영통동 1047-1 청명마을4단지 건영아파트 423동

701호

이준희

경기 용인시 풍덕천2동 삼성5차아파트 521동 103호

김동준

경기 용인시 기흥읍 농서리 7-1 월계수동 918호

(74) 대리인 리앤목특허법인

이해영

**심사관 : 윤난영**

### (54) 메모리 모듈 내에서의 인터페이스 타이밍을 제어하는 메모리 시스템 및 그 방법

#### 요약

메모리 모듈 내에서의 인터페이스 타이밍을 조절하는 메모리 시스템 및 그 방법이 개시된다. 본 발명에 따른 메모리 시스템은 메모리 모듈, 인터페이스 제어부, 메모리 제어부를 구비한다. 메모리 모듈은 메모리 정보를 저장하며, 상기 메모리 정보에 따라 데이터를 저장한다. 인터페이스 제어부는 복수의 입출력 장치와의 연결을 제어하며, 상기 메모리 모듈로부터 상기 메모리 정보를 독출하여 전송한다. 메모리 제어부는 상기 인터페이스 제어부로부터 전송된 상기 메모리 정보를 수신하여 메모리 신호 정보와 함께 상기 메모리 모듈로 전송한다. 상기 메모리 정보는 메모리 초기화 정보 및 상기 메모리 모듈에 장착되는 복수의 메모리 장치들의 인터페이스 타이밍 정보를 구비한다. 본 발명에 따른 메모리 시스템, 메모리 모듈 및 타이밍 제어 방법은 메모리 인터페이스 타이밍 정보를 이용하여 메모리 신호의 타이밍을 조절하고 메모리 장치의 인터페이스 타이밍을 조절함으로써 서로 다른 인터페이스 타이밍 특성을 갖는 메모리 장치에 대해서도 메모리의 양산을 가능하게 하는 장점이 있다.

#### 내포도

도 2

## 색인어

메모리 모듈, 인터페이스 타이밍

## 명세서

### 도면의 간단한 설명

도 1은 메모리 모듈을 구비하는 일반적인 메모리 시스템을 나타내는 블록도이다.

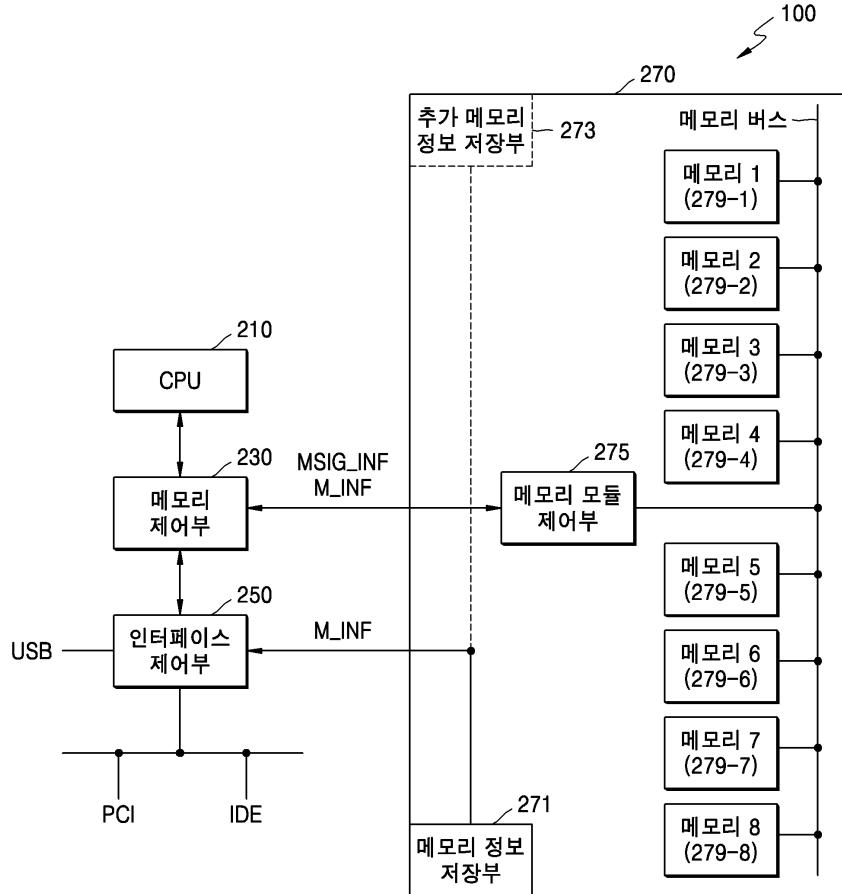

도 2는 본 발명의 실시예에 따른 메모리 시스템을 나타내는 블록도이다.

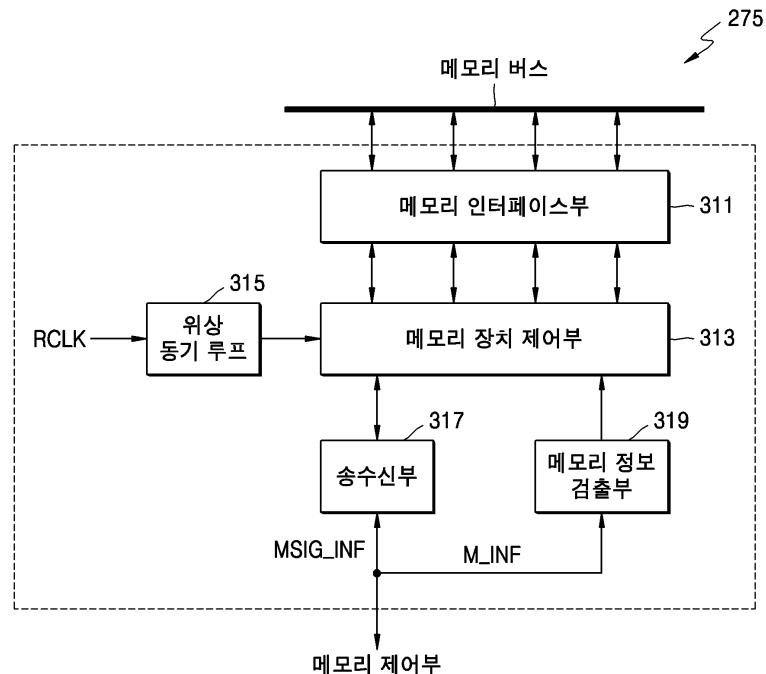

도 3은 도 2의 메모리 모듈 제어부를 나타내는 블록도이다.

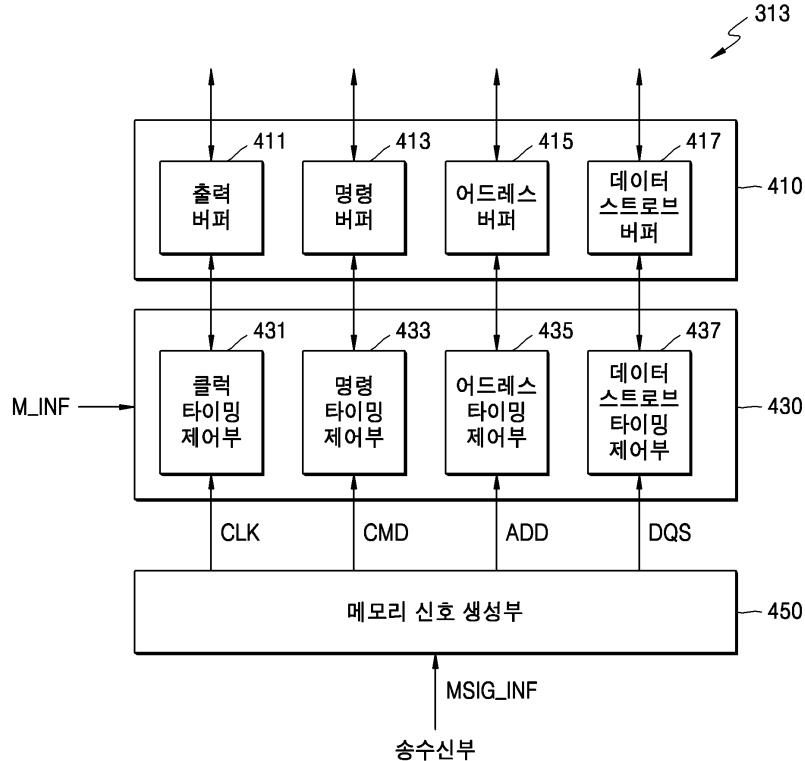

도 4는 도 3의 메모리 장치 제어부를 나타내는 블록도이다.

도 5는 인터페이스 타이밍 정보의 일 예를 나타내는 도면이다.

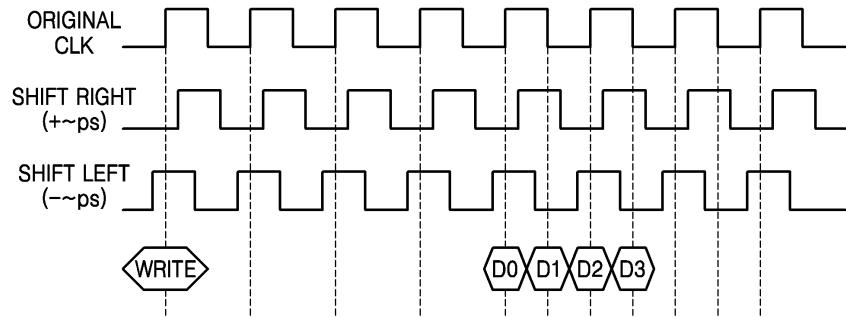

도 6은 도 5의 인터페이스 타이밍 정보에 따라 제어되는 클럭신호의 타이밍 다이어그램이다.

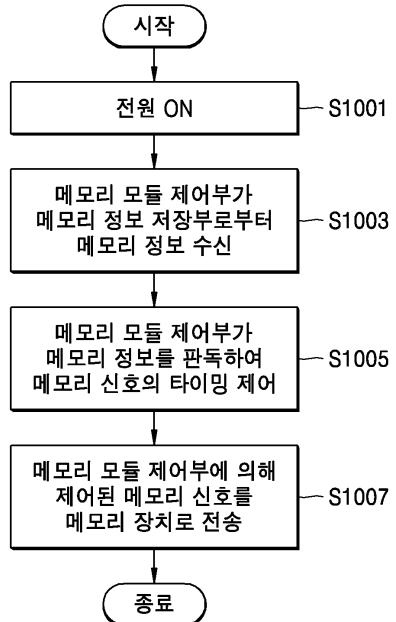

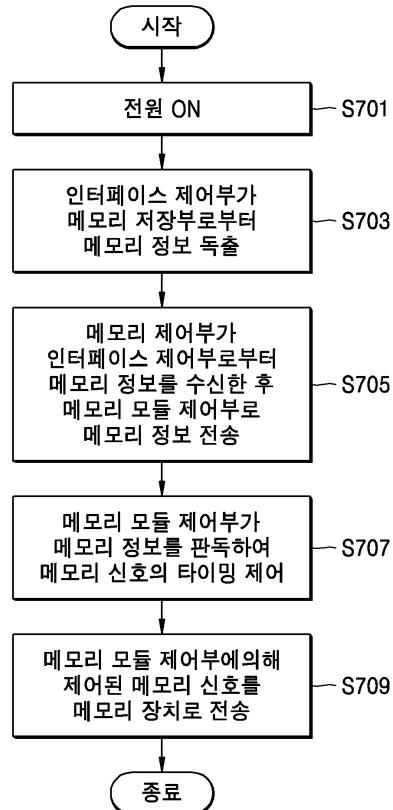

도 7은 본 발명의 다른 실시예에 따른 메모리 모듈 내에서의 인터페이스 타이밍 제어 방법을 나타내는 흐름도이다.

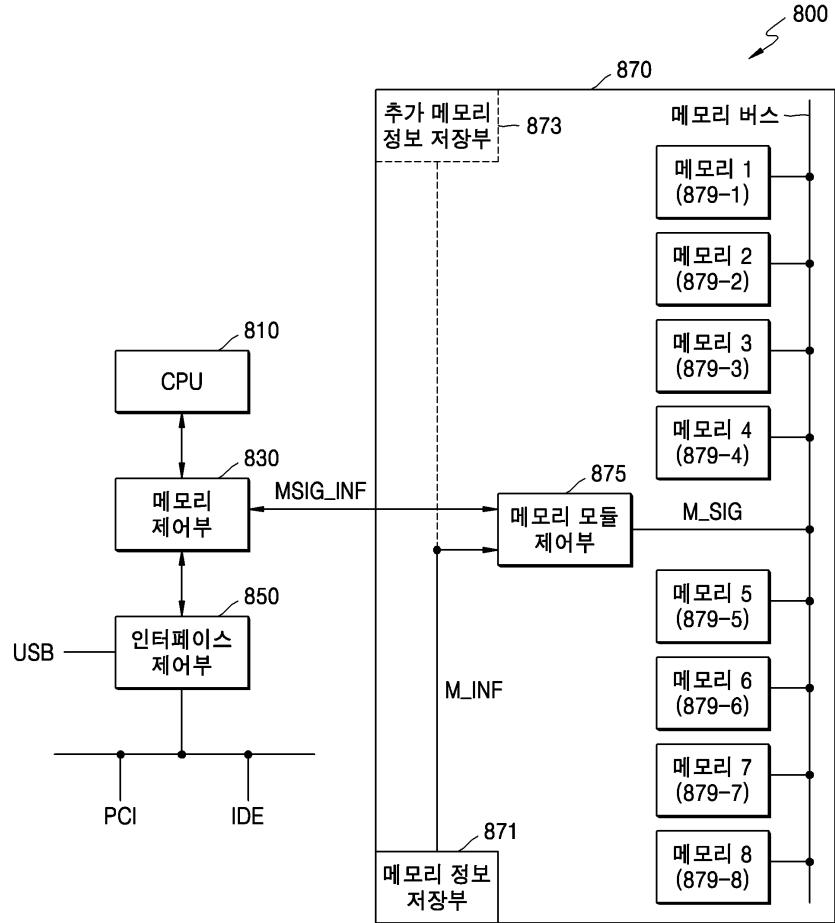

도 8은 본 발명의 또 다른 실시예에 따른 메모리 시스템을 나타내는 블록도이다.

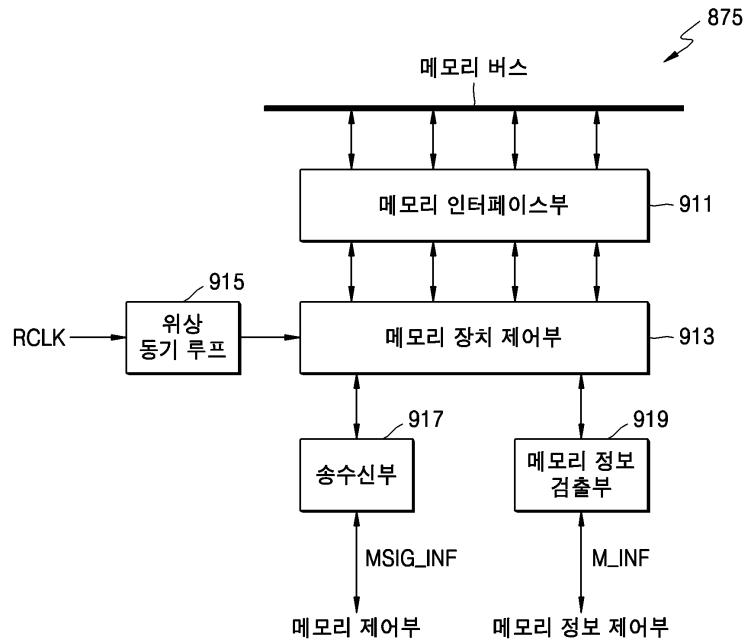

도 9는 도 8의 메모리 모듈 제어부를 나타내는 블록도이다.

도 10은 본 발명의 또 다른 실시예에 따른 메모리 장치 내에서의 인터페이스 타이밍 제어 방법을 나타내는 흐름도이다.

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 복수의 메모리 장치가 장착된 메모리 모듈을 구비하는 메모리 시스템에 관한 것으로, 보다 상세하게는 메모리 정보 저장부에 메모리 모듈에 대한 정보뿐만 아니라 메모리 장치의 타이밍 조절 정보도 저장함으로써 메모리 모듈의 초기화 시 메모리 장치의 인터페이스 타이밍도 조절할 수 있는 메모리 시스템에 관한 것이다.

컴퓨터 시스템의 성능 향상에 따라 현재 대부분의 메모리 시스템에서는 복수의 메모리 장치가 연결되어 사용되는 메모리 모듈이 사용되고 있다. 이러한 메모리 모듈로는 SIMM(single in-line memory module), DIMM(dual in-line memory module), FBDIMM(Fully Buffered DIMM) 등이 있다.

SIMM은 하나 이상의 RAM(DRAM 또는 SDRAM) 칩이 장착되어 있는 작은 회로기판으로서 컴퓨터 마더보드와 연결되는 핀들이 달려 있다. DIMM은 SIMM이 2개인 경우라고 볼 수 있다. SIMM과 마찬가지로, DIMM도 컴퓨터 마더보드에 접속하기 위해 핀이 달린 작은 회로기판 상에 복수의 램 칩들이 부착되어 있다.

SIMM은 보통 72 핀 커넥터가 요구되는 컴퓨터에 사용되며, 32 비트 폭의 데이터가 기입되거나 독출된다. 한편 SDRAM에서는 64 비트 폭의 데이터가 사용되기 때문에, SDRAM을 사용하는 경우에는 적어도 2 개의 SIMM 또는 한 개의 DIMM이 필요하다. DIMM은 168핀 커넥터가 요구되는 컴퓨터에 사용되며, 64 비트 폭의 데이터가 기입되거나 독출된다.

한편, DIMM의 동작은 DIMM 외부의 메모리 제어부에 의해 이루어지며, 컴퓨터 시스템에서는 CPU와 연결되는 North Bridge가 메모리 제어부의 역할을 수행할 수 있다. 그러나, 메모리 모듈 외부의 장치에 의해 제어되는데 따른 지연 등의 문제 때문에 DIMM의 동작속도 및 성능이 저하되는 문제점이 있다.

이러한 문제점을 해결하기 위한 메모리 모듈이 FBDIMM이다. FBDIMM은 메모리 모듈 내에 메모리 모듈의 동작을 제어하는 제어부로서 AMB(Advanced Memory Buffer)를 구비하고 있다.

상술한 바와 같이, 메모리 모듈(특히, DIMM/FBDIMM)에는 RAM 등의 복수의 메모리 장치가 사용되고 또한 메모리 시스템에는 복수의 메모리 모듈이 사용되므로, 메모리 모듈에 데이터를 기입하고 독출하는 동작을 수행하기 위해서는 메모리 모듈 및 메모리 모듈 내의 메모리 장치에 대한 초기화 및 타이밍 설정이 필요하다.

종래에는, 메모리 모듈 내의 SPD(Serial Presence Detect)와 같은 메모리 정보 저장장치에 메모리 초기화 및 타이밍 정보 등을 포함하는 메모리 정보를 저장하였으며, 메모리 제어부는 이러한 메모리 정보를 이용하여 메모리 모듈의 초기화 및 타이밍을 설정하였다. 즉, 메모리 제어부는 SPD에 저장된 메모리 정보를 수집하였다가, 메모리를 초기화하는 경우나 메모리를 테스트하는 경우에 수집된 메모리 정보를 이용하여 메모리를 초기화하거나 메모리 타이밍을 설정하였다.

여기서, SPD는 메모리 모듈 및/또는 메모리 장치의 정보를 저장하고 있는 장치로서, 메모리 모듈 내에 위치한다. SPD에 저장된 정보는 메모리 모듈 및/또는 메모리 장치의 속도, 전압, 로우/컬럼 주소, 리프레쉬 레이트, AC 파라미터(클럭 사이클 시간(tCC), CAS 지연 시간(tCL), RAS-CAS 지연 시간(tRCD), 로우 프리차지 시간(tRP)), 제작자 등으로 메모리 모듈에 대한 전반적인 정보를 포함한다.

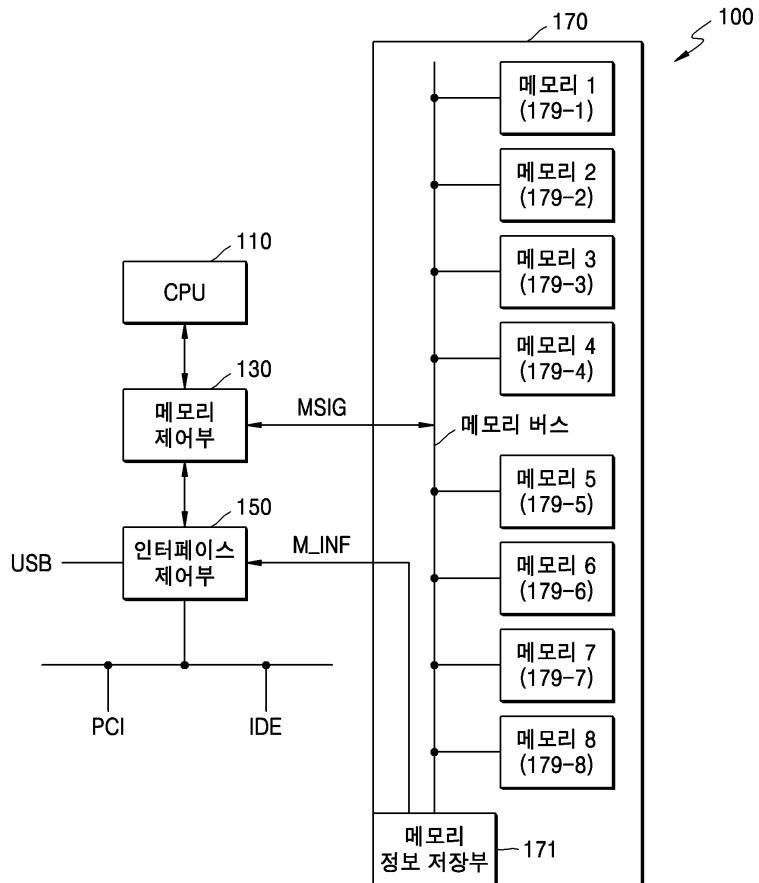

도 1은 메모리 모듈을 구비하는 일반적인 메모리 시스템을 나타내는 블록도이다.

도 1에 도시된 메모리 시스템(100)은 중앙처리장치(110), 메모리 제어부(130), 메모리 인터페이스 제어부(150), 및 메모리 모듈(170)을 구비한다. 메모리 인터페이스 제어부(150)는 메모리 모듈(170) 내의 메모리 정보 저장부(171)에 저장된 메모리 정보(M\_INF)를 독출한 후 이를 메모리 제어부(130)로 전송한다. 메모리 제어부(130)는 메모리 인터페이스 제어부(150)로부터 전송된 메모리 정보(M\_INF)를 내부의 메모리 타이밍 레지스터에 저장하였다가, 이를 이용하여 메모리 모듈(170)을 초기화하고 메모리 모듈의 타이밍을 설정한다. 그 후, 메모리 제어부(130)는 클럭 신호(CLK), 명령 신호(CMD), 어드레스 신호(ADD), 데이터 스트로브 신호(DQS) 등을 구비하는 메모리 신호(M\_SIG)를 복수의 메모리 장치들(179-1 내지 179-8)로 전송한다.

한편 컴퓨터 시스템에서, 메모리 제어부(130)는 CPU를 메모리 모듈과 AGP(Accelerated Graphics Port) 및 PCI (Peripheral Component Interconnect) 버스들에 연결하는 노스 브릿지(NorthBridge: NB) 내에 구현될 수 있으며, 메모리 인터페이스 제어부(150)는 IDE (Integrated Drive Electronics) 버스, USB(Universal Serial BUS), 플러그앤플레이 지원, 키보드/마우스 콘트롤러, 전원관리 등의 기능들을 제어하는 사우스 브릿지(SouthBridge: SB) 내에 구현될 수도 있다.

컴퓨터 시스템에서 구현되는 경우에는, 사우스 브릿지가 메모리 정보 저장부(171)로부터 메모리 정보(M\_INF)를 독출한 후 노스 브릿지에 인터럽트를 요청하면, 노스 브릿지는 인터럽트 요청에 응답하여 현재 수행 중이던 동작을 잠시 중단하고 사우스 브릿지로부터 메모리 정보(M\_INF)를 수신하여 이를 내부의 메모리 타이밍 레지스터에 저장한 후 중단되었던 동작을 다시 수행한다.

그러나, 종래의 메모리 시스템(100)에서의 초기화 및 메모리 타이밍 제어방법은 메모리 모듈 외부의 메모리 제어부에 저장된 메모리 타이밍 정보를 이용하여 메모리 모듈의 초기화 및 메모리 타이밍 설정이 이루어지기 때문에, 메모리 모듈의 초기화에 걸리는 시간이 길어지며, 메모리 장치의 인터페이스 타이밍을 조절하기 어려운 문제점이 있다.

한편, 종래의 메모리 모듈은 메모리 모듈 및 메모리 장치의 발전에 따라 다양한 종류의 메모리 장치가 개발되어 사용되고 있으나, 다양한 종류의 메모리 장치들은 셋-업타임 또는 홀드타임 등의 인터페이스 타이밍이 서로 다르다. 따라서, 서로 다른 인터페이스 타이밍을 적절히 조절하여 메모리의 오동작을 방지할 필요성이 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명이 이루고자 하는 기술적 과제는 메모리 장치의 인터페이스 타이밍 정보를 더 저장함으로써 메모리 모듈의 초기화시 메모리 장치의 인터페이스 타이밍을 조절할 수 있는 메모리 시스템을 제공하는데 있다.

한편, 본 발명이 이루고자 하는 다른 기술적 과제는 메모리 모듈에 장착된 메모리 장치의 인터페이스 타이밍 정보를 이용하여 메모리 모듈의 초기화시 메모리 장치의 인터페이스 타이밍을 조절할 수 있는 메모리 장치의 타이밍 제어 방법을 제공하는데 있다.

### 발명의 구성 및 작용

상기 기술적 과제를 달성하기 위한 본 발명의 일실시예에 따른 메모리 시스템은 메모리 모듈, 인터페이스 제어부, 메모리 제어부를 구비한다. 메모리 모듈은 메모리 정보를 저장하며, 상기 메모리 정보에 따라 데이터를 저장한다. 인터페이스 제어부는 복수의 입출력 장치와의 연결을 제어하며, 상기 메모리 모듈로부터 상기 메모리 정보를 독출하여 전송한다. 메모리 제어부는 상기 인터페이스 제어부로부터 전송된 상기 메모리 정보를 수신하여 메모리 신호 정보와 함께 상기 메모리 모듈로 전송한다. 상기 메모리 정보는 메모리 초기화 정보 및 상기 메모리 모듈에 장착되는 복수의 메모리 장치들의 인터페이스 타이밍 정보를 구비한다.

상기 메모리 모듈은 복수의 메모리 장치들, 메모리 정보 저장부, 메모리 모듈 제어부를 구비한다. 복수의 메모리 장치들은 상기 데이터를 저장한다. 메모리 정보 저장부는 상기 메모리 정보를 저장한다. 메모리 모듈 제어부는 상기 메모리 제어부로부터 전송된 상기 메모리 신호 정보 및 상기 메모리 정보에 응답하여 상기 복수의 메모리 장치들을 제어한다.

상기 메모리 모듈은 상기 메모리 정보 중 상기 인터페이스 타이밍 정보를 저장하는 추가 메모리 정보 저장부를 더 구비할 수 있다.

상기 인터페이스 타이밍 정보는 클럭신호 타이밍 정보, 명령신호 타이밍 정보, 어드레스 타이밍 정보, 및 데이터 스트로브 타이밍 정보를 구비한다.

상기 메모리 모듈 제어부는 송수신부, 메모리 정보 검출부, 메모리 장치 제어부, 및 인터페이스부를 구비한다. 송수신부는 상기 메모리 제어부와 상기 메모리 신호 정보와 상기 메모리 정보를 송수신한다. 메모리 정보 검출부는 상기 메모리 제어부로부터 전송된 상기 메모리 정보를 검출한다. 메모리 장치 제어부는 상기 송수신부에서 수신된 상기 메모리 신호 정보와 상기 검출된 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어한다. 인터페이스부는 상기 복수의 메모리 장치들과 상기 메모리 모듈 제어부 간의 인터페이스를 수행한다.

상기 메모리 장치 제어부는 메모리 신호 생성부, 메모리 신호 타이밍 제어부, 메모리 신호 베퍼부를 구비한다. 메모리 신호 생성부는 상기 메모리 신호 정보를 이용하여 상기 메모리 신호를 생성한다. 메모리 신호 타이밍 제어부는 상기 메모리 정보에 기초하여 상기 메모리 신호의 타이밍을 제어한다. 메모리 신호 베퍼부는 상기 메모리 신호 타이밍 제어부에 의해 제어된 타이밍에 따라 타이밍이 제어된 메모리 신호를 상기 인터페이스부로 베퍼링한다.

상기 기술적 과제를 달성하기 위한 본 발명에 다른 실시예에 따른 메모리 모듈은 복수의 메모리 장치들, 메모리 정보 저장부, 메모리 모듈 제어부를 구비한다. 복수의 메모리 장치들은 데이터를 저장한다. 메모리 정보 저장부는 메모리 정보를 저장한다. 메모리 모듈 제어부는 메모리 신호 정보 및 상기 메모리 정보에 응답하여 상기 복수의 메모리 장치들을 제어한다. 상기 메모리 정보는 메모리 초기화 정보 및 상기 복수의 메모리 장치의 인터페이스 타이밍 정보를 구비한다.

상기 메모리 모듈은 상기 메모리 정보 중 상기 인터페이스 타이밍 정보를 저장하는 추가 메모리 정보 저장부를 더 구비할 수 있다.

상기 메모리 모듈 제어부는 송수신부, 메모리 정보 검출부, 메모리 장치 제어부, 및 인터페이스부를 구비한다. 송수신부는 상기 메모리 모듈 외부와 상기 메모리 신호 정보를 송수신한다. 메모리 정보 검출부는 상기 메모리 정보 저장부로부터의 상기 메모리 정보를 검출한다. 메모리 장치 제어부는 상기 송수신부에서 수신된 상기 메모리 신호 정보와 상기 검출된 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어한다. 인터페이스부는 상기 복수의 메모리 장치들과 상기 메모리 모듈 제어부 간의 인터페이스를 수행한다.

상기 다른 기술적 과제를 달성하기 위한 본 발명의 일실시예에 따른 메모리 장치의 타이밍 제어방법은, 메모리 정보 저장부 및 메모리 모듈 제어부를 구비하는 메모리 모듈에 장착된 복수의 메모리 장치들의 타이밍을 제어하는 방법에 있어서, 상기 메모리 정보 저장부에 저장된 메모리 정보를 독출하는 단계, 메모리 신호 정보와 상기 메모리 정보를 상기 메모리 모

들 제어부로 전송하는 단계, 및 상기 전송된 메모리 신호 정보와 상기 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어하여 상기 복수의 메모리 장치들로 전송하는 단계를 구비한다. 상기 메모리 정보는 메모리 초기화 정보 및 상기 복수의 메모리 장치들의 인터페이스 타이밍 정보를 구비한다.

상기 메모리 신호의 타이밍을 제어하는 단계는, 상기 메모리 신호 정보에 응답하여 상기 메모리 신호를 생성하는 단계, 및 상기 메모리 정보에 응답하여 상기 메모리 신호의 타이밍을 제어하는 단계를 구비한다.

상기 인터페이스 타이밍 정보는 클럭신호 타이밍 정보, 명령신호 타이밍 정보, 어드레스 타이밍 정보, 및 데이터 스트로브 타이밍 정보를 구비한다.

상기 다른 기술적 과제를 달성하기 위한 본 발명에 따른 실시예에 따른 메모리 장치의 타이밍 제어방법은, 메모리 정보 저장부 및 메모리 모듈 제어부를 구비하는 메모리 모듈에 장착된 복수의 메모리 장치들의 타이밍을 제어하는 방법에 있어서, 상기 메모리 정보 저장부에 저장된 메모리 정보를 독출하는 단계, 메모리 신호 정보 및 상기 메모리 정보를 상기 메모리 모듈 제어부로 전송하는 단계, 및 상기 전송된 메모리 신호 정보와 상기 메모리 정보에 응답하여 메모리 신호의 타이밍을 제어하여 상기 복수의 메모리 장치들로 전송하는 단계한다. 상기 메모리 정보는 메모리 초기화 정보 및 메모리 장치의 인터페이스 타이밍 정보를 구비한다.

상기 메모리 신호의 타이밍을 제어하는 단계는, 상기 메모리 신호 정보를 이용하여 상기 메모리 신호를 생성하는 단계, 및 상기 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어하는 단계를 구비한다.

이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 설명함으로써, 본 발명을 상세히 설명한다. 각 도면에 제시된 동일한 참조부호는 동일한 부재를 나타낸다.

도 2는 본 발명의 실시예에 따른 메모리 시스템을 나타내는 블록도이다.

본 발명에 따른 메모리 시스템(200)은 메모리 모듈(270), 메모리 제어부(230), 및 인터페이스 제어부(250)를 구비한다. 인터페이스 제어부(250)는 메모리 모듈(270)에 저장된 메모리 정보(M\_INF)를 독출하여 메모리 제어부(230)로 전송한다. 메모리 제어부(230)는 전송된 메모리 정보(M\_INF)를 메모리 신호 정보(MSIG\_INF)와 함께 메모리 모듈(270)로 전송한다. 한편, 메모리 제어부(230)로부터 메모리 모듈(270)로 데이터를 전송하는 방식은 종래의 병렬방식이 아닌 패킷 형태의 시리얼 방식이다.

도 1의 종래기술에서와 같이, 본 발명의 인터페이스 제어부(250) 및 메모리 제어부(230)는 컴퓨터 시스템에서 각각 사우스 브릿지 및 노스 브릿지 내에 구현될 수도 있다. 이 경우, 사우스 브릿지는 메모리 모듈(270)로부터 메모리 정보(M\_INF)를 독출한 후 노스 브릿지로 메모리 정보(M\_INF) 전송을 위한 인터럽트를 요청하고, 노스 브릿지는 사우스 브릿지로부터의 인터럽트 요청에 응답하여 실행 중이던 작업을 중단하고 메모리 신호 정보(MSIG\_INF)와 함께 메모리 정보(M\_INF)를 메모리 모듈(270)로 전송한다.

메모리 모듈(270)은 복수의 메모리 장치(279-1 내지 279-8), 메모리 모듈 제어부(275), 및 메모리 정보 저장부(271)를 구비하며, 추가 메모리 정보 저장부(273)를 더 구비할 수 있다.

메모리 시스템에서, 메모리 모듈(270)은 DIMM(Dual In-line Memory Module), 바람직하게는 FBDIMM(Fully Buffered DIMM)이고, 복수의 메모리 장치(279-1 내지 279-8) 각각은 RAM(Random Access Memory), 바람직하게는 SDRAM (Synchronous Dynamic RAM)이며, 메모리 정보 저장부(271)와 메모리 모듈 제어부(275)는 바람직하게는 SPD(Serial Presence Detect)와 AMB(Advanced Memory Buffer)일 수 있으나, 본 발명은 이에 제한되지 않는다.

메모리 정보 저장부(271)는, 종래의 메모리 정보 저장부에 저장되었던 메모리 정보 이외에, 메모리 장치(279-1 내지 279-8)의 인터페이스 타이밍을 조절할 수 있는 인터페이스 타이밍 정보를 더 저장한다.

인터페이스 타이밍 정보는 메모리 정보 저장부(271)의 영역 중 종래의 메모리 정보가 저장되었던 영역을 제외한 메모리 정보 저장부(271)의 빈 영역에 저장될 수 있으며, 인터페이스 타이밍 정보만을 저장하는 별도의 추가 메모리 정보 저장부(273)에 저장될 수도 있다.

메모리 정보(M\_INF)는 인터페이스 제어부(250)와 메모리 제어부(230)를 통해 메모리 모듈 제어부(275)로 전송된다. 메모리 모듈 제어부(275)는 전송된 메모리 정보(M\_INF)에 따라 내부의 메모리 타이밍 레지스터를 설정하고 메모리 모듈(270)을 초기화한다. 또한, 메모리 모듈 제어부(275)는 전송된 메모리 신호 정보(MSIG\_INF)를 이용하여 메모리 신호(M\_SIG)를 생성한다.

메모리 신호(M\_SIG)가 생성된 후, 메모리 모듈 제어부(275)는 인터페이스 타이밍 정보를 이용하여 메모리 모듈 내부의 신호(메모리 신호(M\_SIG)) 타이밍을 조절한다. 메모리 모듈 제어부(275)에서 생성되고 타이밍이 조절된 메모리 신호(M\_SIG)는 병렬로 각각의 메모리 장치(279-1 내지 279-8)로 전송된다.

도 3은 도 2의 메모리 모듈 제어부를 나타내는 블록도이다.

메모리 모듈 제어부(275)는 메모리 인터페이스부(311), 메모리 장치 제어부(313), 위상동기루프(315), 송수신부(317), 및 메모리 정보 검출부(319)를 구비한다.

송수신부(317)는 메모리 제어부(230)와 메모리 모듈(270) 간에 신호를 송수신한다. 한편, 메모리 제어부(230)와 메모리 모듈(270) 간에 송수신되는 신호는 메모리 정보(M\_INF) 뿐만 아니라, 클럭신호(CLK), 명령신호(CMD), 어드레스 신호(ADD) 및 데이터 스트로브 신호(DQS) 등의 신호를 생성하기 위한 메모리 신호 정보(MSIG\_INF) 등 메모리 기입 판독을 위한 모든 신호를 포함한다.

메모리 정보 검출부(319)는 메모리 제어부(230)로부터 수신된 신호들 중 메모리 정보(M\_INF)를 검출하여 메모리 장치 제어부(313)로 전송한다. 메모리 장치 제어부(313)는 검출된 메모리 정보(M\_INF) 및 메모리 제어부(230)로부터 수신된 메모리 신호 정보(MSIG\_INF)에 응답하여 각각의 메모리 장치(279-1 내지 279-8)로 전송되는 메모리 신호(M\_SIG)를 제어한다.

좀 더 구체적으로, 메모리 장치 제어부(313)는 검출된 메모리 정보(M\_INF)를 이용하여 내부의 메모리 타이밍 레지스터를 설정하고 메모리를 초기화하며, 메모리 신호 정보(MSIG\_INF)에 응답하여 기입동작 또는 판독동작을 위한 메모리 신호(M\_SIG)를 생성한다. 또한, 메모리 장치 제어부(313)는 인터페이스 타이밍 정보를 이용하여 메모리 신호(M\_SIG)의 타이밍을 조절한다.

메모리 인터페이스부(311)는 메모리 버스를 통해 메모리 모듈 제어부(275)와 각각의 메모리 장치(279-1 내지 279-8) 간에 메모리 신호(M\_SIG)를 전달한다. 위상동기루프(315, Phase Locked Loop: PLL)는 전체 시스템 클럭신호(RCLK)를 이용하여 메모리 모듈에서 사용될 클럭신호(CLK)를 생성한다.

도 4는 도 3의 메모리 장치 제어부를 나타내는 블록도이다.

메모리 장치 제어부(313)는 메모리 신호 생성부(450), 메모리 타이밍 제어부(430), 및 메모리 신호 버퍼부(410)를 구비한다. 메모리 신호 생성부(450)는 메모리 신호 정보(MSIG\_INF)를 이용하여 각각의 메모리 장치(279-1 내지 279-8)로 제공될 메모리 신호(M\_SIG)를 생성한다. 메모리 신호(M\_SIG)는 클럭신호(CLK), 명령신호(CMD), 어드레스신호(ADD), 데이터 스트로브 신호(DQS)를 포함한다.

메모리 타이밍 제어부(430)는 메모리 정보(M\_INF)를 이용하여 메모리 신호(M\_SIG)의 타이밍을 제어한다. 메모리 신호 버퍼부(410)는 메모리 타이밍 제어부(430)에 의해 제어된 타이밍에 따라 메모리 신호(M\_SIG)의 타이밍을 조절하여 타이밍이 제어된 메모리 신호(M\_SIG)를 버퍼링한다. 메모리 신호(M\_SIG)의 타이밍을 제어하여 버퍼링하는 과정은 이후 상세히 설명하기로 한다.

메모리 타이밍 제어부(430)는 클럭신호 타이밍 제어부(431), 명령신호 타이밍 제어부(433), 어드레스 타이밍 제어부(435), 및 데이터 스트로브 타이밍 제어부(437)를 구비한다.

클럭신호 타이밍 제어부(431)는 메모리 정보(M\_INF)에 포함된 클럭신호 타이밍 정보를 이용하여 위상동기루프(315)에서 생성된 클럭신호의 타이밍을 제어한다. 명령신호 타이밍 제어부(433)는 메모리 정보(M\_INF)에 포함된 명령신호 타이밍 정보를 이용하여 명령신호의 타이밍을 제어한다. 어드레스 타이밍 제어부(435)는 메모리 정보(M\_INF)에 포함된 어드레스신호 타이밍 정보를 이용하여 어드레스 신호의 타이밍을 제어한다. 데이터 스트로브 타이밍 제어부(437)는 메모리 정보(M\_INF)에 포함된 데이터 스트로브 신호 타이밍 정보를 이용하여 데이터 스트로브 신호(DQS)의 타이밍을 제어한다.

메모리 신호 버퍼부(410)는 클럭신호 버퍼부(411), 명령신호 버퍼부(413), 어드레스 버퍼부(415), 및 데이터 스트로브 버퍼부(417)를 구비한다. 클럭신호 버퍼부(411)는 클럭신호 제어부(431)에 의해 제어된 타이밍에 따라 클럭신호의 타이밍을 조절하여 메모리 인터페이스부(311)로 전송한다.

명령신호 버퍼부(413)는 명령신호 제어부(433)에 의해 제어된 타이밍에 따라 명령신호의 타이밍을 조절하여 메모리 인터페이스부(311)로 전송한다. 어드레스 버퍼부(415)는 어드레스 제어부(435)에 의해 제어된 타이밍에 따라 어드레스신호의 타이밍을 조절하여 메모리 인터페이스부(311)로 전송한다.

데이터 스트로브 버퍼부(411)는 데이터 스트로브 제어부(431)에 의해 제어된 타이밍에 따라 데이터 스트로브 신호(DQS)의 타이밍을 조절하여 메모리 인터페이스부(311)로 전송한다.

도 5는 인터페이스 타이밍 정보의 일 예를 나타내는 도면이다.

도 5에 도시된 인터페이스 타이밍 정보(500)는 메모리 정보 저장부(271)에 저장된다. 인터페이스 타이밍 정보는 클럭신호(CLK), 명령신호(CMD), 어드레스신호(ADD), 및 데이터 스트로브 신호(DQS, 미도시)의 인터페이스 타이밍 정보를 포함한다. 한편, 본 발명의 인터페이스 타이밍 정보는 별도의 전용 저장장치인 추가 메모리 정보 저장부(273)에 저장될 수도 있다.

도 5의 실시예에서, 클럭신호(CLK)의 인터페이스 타이밍 정보는 메모리 정보 저장부(271)의 126번째 바이트에, 명령신호(CMD)의 인터페이스 타이밍 정보는 메모리 정보 저장부(271)의 127번째 바이트에, 그리고 어드레스신호(ADD)의 인터페이스 타이밍 정보는 메모리 정보 저장부(271)의 128번째 바이트에 각각 저장되나, 각각의 인터페이스 타이밍 정보가 저장되는 위치가 이에 한정되는 것은 아니다.

메모리 정보 저장부(271)의 126번째 바이트에 저장된 값이 “0F”인 경우를 디폴트 값으로 하여, 클럭신호(CLK)의 인터페이스 타이밍이 도 5에 도시된 값에 따라 조절된다. 예를 들어 메모리 정보 저장부(271)의 126번째 바이트에 저장된 값이 “0E”인 경우, 클럭신호(CLK)의 인터페이스 타이밍은 + 100ps만큼 조절되어 클럭신호(CLK)가 기준 클럭신호에 비해 100ps만큼 앞서도록 조절된다.

명령신호(CMD)의 인터페이스 타이밍도, 메모리 정보 저장부(271)의 127번째 바이트에 저장되는 값인 “0F”인 경우를 디폴트 값으로 하여, 조절된다. 예를 들어 저장된 값이 “10”인 경우 명령신호(CMD)의 인터페이스 타이밍은 -100ps만큼 조절되어 명령신호(CMD)가 기준 명령신호에 비해 100ps만큼 뒤지도록 조절된다.

도 5에 도시된 바와 같이 어드레스신호(ADD)의 인터페이스 타이밍 조절을 위해 저장된 값이 “0D”인 경우, 어드레스신호(ADD)는 + 200ps만큼 조절되어 어드레스신호(ADD)가 기준 어드레스신호에 비해 200ps만큼 앞서도록 조절된다.

도 6은 도 5의 인터페이스 타이밍 정보에 따라 제어되는 클럭신호의 타이밍 다이어그램이다.

도 6의 타이밍 다이어그램에는 기준클럭신호(ORIGINAL CLK), 오른쪽으로 천이된 클럭신호(SHIFT RIGHT), 왼쪽으로 천이된 클럭신호(SHIFT LEFT), 및 기입명령(WRITE)과 데이터 신호(D0 내지 D3)가 나타나 있다.

메모리 저장 장치(271)에 저장된 저장된 값이 “0F”인 경우를 기준으로(ORIGINAL CLK) 클럭신호(CLK)의 인터페이스 타이밍이 조절된다. 즉, “0F”보다 작은 값이 저장된 경우 클럭신호(CLK)는 양의 천이량을 가지며, 클럭신호(CLK)는 오른쪽으로 천이된다(SHIFT RIGHT). 한편, “0F”보다 큰 값이 저장된 경우 클럭신호(CLK)는 음의 천이량을 가지며, 클럭신호(CLK)는 왼쪽으로 천이된다(SHIFT LEFT).

한편, 도 6에서 명령신호인 기입명령(WRITE)과 데이터 신호(D0 내지 D3)는 기준클럭(ORIGINAL CLK)에 동기되도록 설정되어 있다. 그러나, 명령신호와 데이터 신호(D0 내지 D3)는 메모리 장치(279-1 내지 279-8)의 초기화에 걸리는 시간 및 신호의 지연 등에 의해 기준클럭(ORIGINAL CLK)과의 동기가 어긋나는 경우가 발생할 수 있으며, 이러한 경우 본 발명에 따라 클럭신호(CLK)의 인터페이스 타이밍을 조절함으로써 클럭신호(CLK)와 동기되도록 할 수 있다.

도 7은 본 발명의 다른 실시예에 따른 메모리 모듈 내에서의 인터페이스 타이밍 제어 방법을 나타내는 흐름도이다.

도 7을 참조하여, 본 발명의 실시예에 따른 메모리 장치(279-1 내지 279-8)에 제공되는 메모리 신호(M\_SIG)의 타이밍을 조절하는 방법에 대해 상술한다.

먼저, 전원이 켜지면(S701) 인터페이스 제어부(250)는 메모리 정보 저장부(271)에 저장된 메모리 정보(M\_INF)를 독출한 후(S703), 독출된 메모리 정보(M\_INF)를 메모리 제어부(230)로 전송한다. 한편, 메모리 제어부(230)는 인터페이스 제어부(250)로부터 수신한 메모리 정보(M\_INF)를 메모리 모듈 제어부(275)로 전송한다(S705).

메모리 모듈 제어부(275)는 메모리 제어부(230)로부터 전송된 메모리 정보(M\_INF)를 이용하여 메모리 신호(M\_SIG)를 생성하고 타이밍을 제어한다(S707). 타이밍이 제어된 메모리 신호(M\_SIG)는 메모리 버스를 통해 메모리 장치(279-1 내지 279-8)로 전송된다.

한편, 메모리 정보(M\_INF)는 메모리 초기화 정보와 클럭신호(CLK), 명령신호(CMD), 어드레스 신호(ADD), 및 데이터 스트로브 신호(DQS) 등의 타이밍을 조절하기 위한 메모리 장치의 인터페이스 타이밍 정보를 포함한다. 메모리 모듈 제어부(275)는 인터페이스 타이밍 정보를 이용하여 클럭신호(CLK), 명령신호(CMD), 어드레스 신호(ADD), 및 데이터 스트로브 신호(DQS)의 인터페이스 타이밍을 제어한다.

도 8은 본 발명의 또 다른 실시예에 따른 메모리 시스템을 나타내는 블록도이다.

본 발명의 또 다른 실시예에 따른 메모리 시스템(800)은, 메모리 모듈 제어부(875)는 메모리 정보 저장부(871) 및/또는 추가 메모리 정보 저장부(873)로부터 메모리 정보(M\_INF)를 직접 수신하는 것을 제외하고, 본 발명의 도 2에 도시된 메모리 시스템(200)과 동일한 구성을 갖는다.

즉, 메모리 정보(M\_INF)는, 인터페이스 제어부(850)가 메모리 정보 저장부(871)에 저장된 메모리 정보(M\_INF)를 독출한 후 메모리 제어부(830)로 전송하고 메모리 제어부(830)가 메모리 정보(M\_INF)를 메모리 모듈 제어부(875)로 전송하는 과정 없이, 메모리 모듈 제어부(875)로 직접 전송된다.

도 9는 도 8의 메모리 모듈 제어부를 나타내는 블록도이다.

본 발명의 제 2 실시예의 메모리 모듈 제어부(875)는 메모리 정보 검출부(919)가 메모리 정보(M\_INF)를 메모리 정보 저장부(871)로부터 직접 수신하는 것을 제외하고 본 발명의 제 1 실시예의 메모리 모듈 제어부(275)와 구성이 동일한다.

즉 메모리 정보(M\_INF)는, 메모리 인터페이스 제어부(850)와 메모리 제어부(830)를 거쳐 메모리 모듈로 전송되는 것이 아니라, 메모리 정보 저장부(871)로부터 메모리 모듈 제어부(875)로 직접 전송되며, 메모리 정보 검출부(919)는 메모리 정보 저장부(871)로부터 전송된 메모리 정보(M\_INF)를 검출하여 검출된 메모리 정보(M\_INF)를 메모리 장치 제어부(913)로 전송한다.

한편, 메모리 장치 제어부(913)가 검출된 메모리 정보(M\_INF)를 이용하여 메모리 신호(M\_SIG)의 타이밍을 제어하는 구성은 본 발명의 제 1 실시예에서와 동일하며, 따라서 메모리 장치 제어부(913)의 구성 또한 본 발명의 제 1 실시예의 메모리 장치 제어부(313)의 구성과 동일하다.

도 10은 본 발명의 또 다른 실시예에 따른 메모리 장치 내에서의 인터페이스 타이밍 제어 방법을 나타내는 흐름도이다.

전원이 켜지면(S1001), 메모리 모듈 제어부(875)는 메모리 정보 저장부(871)로부터 메모리 정보(M\_INF)를 수신한다 (S1003). 메모리 모듈 제어부(875)는 수신된 메모리 정보(M\_INF)를 이용하여 메모리 장치(879-1 내지 879-8)로 제공될 메모리 신호(M\_SIG)의 타이밍을 제어하고(S1005), 타이밍이 제어된 메모리 신호(M\_SIG)를 메모리 버스를 통해 메모리 장치(879-1 내지 879-8)로 전송한다(S1007).

한편, 메모리 정보(M\_INF)는 메모리 초기화 정보와 클럭신호(CLK), 명령신호(CMD), 어드레스 신호(ADD), 및 데이터 스트로브 신호(DQS) 등의 메모리 신호 인터페이스 타이밍 정보를 포함한다. 메모리 모듈 제어부(275)는 인터페이스 타이밍 정보를 이용하여 클럭신호(CLK), 명령신호(CMD), 어드레스 신호(ADD), 및 데이터 스트로브 신호(DQS)의 인터페이스 타이밍을 제어하는 점은 본 발명의 제 1 실시예에서와 동일하다.

본 발명은 도면에 도시된 일실시예를 참고로 설명되었으나, 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변경 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

### 발명의 효과

상술한 바와 같이 본 발명의 실시예에 따른 메모리 시스템, 메모리 모듈, 및 메모리 장치의 타이밍 제어 방법은 메모리 인터페이스 타이밍 정보를 이용하여 메모리 신호의 타이밍을 조절하고 메모리 장치의 인터페이스 타이밍을 조절함으로써 서로 다른 인터페이스 타이밍 특성을 갖는 메모리 장치에 대해서도 메모리의 양산이 가능한 장점이 있다.

또한, 본 발명의 실시예에 따른 메모리 시스템, 메모리 모듈, 및 메모리 장치의 타이밍 제어 방법은 메모리 장치의 인터페이스 타이밍을 조절하여 오동작하는 메모리 장치의 타이밍을 조절함으로써 메모리장치의 디버그(debug) 작업 등을 용이하게 할 수 있는 장점이 있다.

### (57) 청구의 범위

#### 청구항 1.

메모리 정보를 저장하며, 상기 메모리 정보에 따라 데이터를 저장하는 메모리 모듈;

복수의 입출력 장치와의 연결을 제어하며, 상기 메모리 모듈로부터 상기 메모리 정보를 독출하여 전송하는 인터페이스 제어부; 및

상기 인터페이스 제어부로부터 전송된 상기 메모리 정보를 수신하여 메모리 신호 정보와 함께 상기 메모리 모듈로 전송하는 메모리 제어부를 구비하며,

상기 메모리 정보는 메모리 초기화 정보 및 상기 메모리 모듈에 장착되는 복수의 메모리 장치들의 인터페이스 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 시스템.

#### 청구항 2.

제 1 항에 있어서, 상기 메모리 모듈은,

상기 데이터를 저장하는 복수의 상기 메모리 장치들;

상기 메모리 정보를 저장하는 메모리 정보 저장부; 및

상기 메모리 제어부로부터 전송된 상기 메모리 신호 정보 및 상기 메모리 정보에 응답하여 상기 복수의 메모리 장치들을 제어하는 메모리 모듈 제어부를 구비하는 것을 특징으로 하는 메모리 시스템.

#### 청구항 3.

제 2 항에 있어서,

상기 메모리 모듈은 상기 메모리 정보 중 상기 인터페이스 타이밍 정보를 저장하는 추가 메모리 정보 저장부를 더 구비하는 것을 특징으로 하는 메모리 시스템.

#### 청구항 4.

제 3 항에 있어서,

상기 인터페이스 타이밍 정보는 클럭신호 타이밍 정보, 명령신호 타이밍 정보, 어드레스 타이밍 정보, 및 데이터 스트로브 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 시스템.

### 청구항 5.

제 2 항에 있어서, 상기 메모리 모듈 제어부는,

상기 메모리 제어부와 상기 메모리 신호 정보와 상기 메모리 정보를 송수신하는 송수신부;

상기 메모리 제어부로부터 전송된 상기 메모리 정보를 검출하는 메모리 정보 검출부;

상기 송수신부에서 수신된 상기 메모리 신호 정보와 상기 검출된 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어하는 메모리 장치 제어부; 및

상기 복수의 메모리 장치들과 상기 메모리 모듈 제어부 간의 인터페이스를 수행하는 인터페이스부를 구비하는 것을 특징으로 하는 메모리 시스템.

### 청구항 6.

제 5 항에 있어서, 상기 메모리 장치 제어부는,

상기 메모리 신호 정보를 이용하여 상기 메모리 신호를 생성하는 메모리 신호 생성부;

상기 메모리 정보에 기초하여 상기 메모리 신호의 타이밍을 제어하는 메모리 신호 타이밍 제어부; 및

상기 메모리 신호 타이밍 제어부에 의해 제어된 타이밍에 따라 타이밍이 제어된 메모리 신호를 상기 인터페이스부로 버퍼링하는 메모리 신호 버퍼부를 구비하는 것을 특징으로 하는 메모리 시스템.

### 청구항 7.

제 6 항에 있어서, 상기 메모리 신호 타이밍 제어부는,

상기 인터페이스 타이밍 정보에 응답하여 클럭신호의 타이밍을 제어하는 클럭신호 타이밍 제어부;

상기 인터페이스 타이밍 정보에 응답하여 명령신호의 타이밍을 제어하는 명령신호 타이밍 제어부;

상기 인터페이스 타이밍 정보에 응답하여 어드레스 신호의 타이밍을 제어하는 어드레스 타이밍 제어부; 및

상기 인터페이스 타이밍 정보에 응답하여 데이터 스트로브신호의 타이밍을 제어하는 데이터 스트로브 타이밍 제어부를 구비하는 것을 특징으로 하는 메모리 시스템.

### 청구항 8.

제 6 항에 있어서, 메모리 신호 버퍼부는,

상기 클럭신호 타이밍 제어부에 의해 타이밍이 제어된 클럭신호를 상기 인터페이스부로 공급하는 클럭신호 버퍼부;

상기 명령신호 타이밍 제어부에 의해 타이밍이 제어된 명령신호를 상기 인터페이스부로 공급하는 명령신호 버퍼부;

상기 어드레스 타이밍 제어부에 의해 타이밍이 제어된 어드레스신호를 상기 인터페이스부로 공급하는 어드레스 버퍼부;

및

상기 데이터 스트로브 타이밍 제어부에 의해 타이밍이 제어된 데이터 스트로브신호를 상기 인터페이스부로 공급하는 데이터 스트로브 버퍼부를 구비하는 것을 특징으로 하는 메모리 시스템.

### 청구항 9.

메모리 정보 저장부 및 메모리 모듈 제어부를 구비하는 메모리 모듈에 장착된 복수의 메모리 장치들의 타이밍을 제어하는 방법에 있어서,

상기 메모리 정보 저장부에 저장된 메모리 정보를 독출하는 단계;

메모리 신호 정보와 상기 메모리 정보를 상기 메모리 모듈 제어부로 전송하는 단계; 및

상기 전송된 메모리 신호 정보와 상기 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어하여 상기 복수의 메모리 장치들로 전송하는 단계를 구비하며,

상기 메모리 정보는 메모리 초기화 정보 및 상기 복수의 메모리 장치들의 인터페이스 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 장치의 타이밍 제어 방법.

### 청구항 10.

제 9 항에 있어서, 상기 메모리 신호의 타이밍을 제어하는 단계는,

상기 메모리 신호 정보에 응답하여 상기 메모리 신호를 생성하는 단계; 및

상기 메모리 정보에 응답하여 상기 메모리 신호의 타이밍을 제어하는 단계를 구비하는 것을 특징으로 하는 메모리 장치의 타이밍 제어 방법.

### 청구항 11.

제 9 항에 있어서,

상기 인터페이스 타이밍 정보는 클럭신호 타이밍 정보, 명령신호 타이밍 정보, 어드레스 타이밍 정보, 및 데이터 스트로브 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 장치의 타이밍 제어 방법.

### 청구항 12.

데이터를 저장하는 복수의 메모리 장치들;

메모리 정보를 저장하는 메모리 정보 저장부; 및

메모리 신호 정보 및 상기 메모리 정보에 응답하여 상기 복수의 메모리 장치들을 제어하는 메모리 모듈 제어부를 구비하며,

상기 메모리 정보는 메모리 초기화 정보 및 상기 복수의 메모리 장치의 인터페이스 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 13.

제 12 항에 있어서,

상기 메모리 모듈은 상기 메모리 정보 중 상기 인터페이스 타이밍 정보를 저장하는 추가 메모리 정보 저장부를 더 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 14.

제 13 항에 있어서,

상기 인터페이스 타이밍 정보는 클럭신호 타이밍 정보, 명령신호 타이밍 정보, 어드레스 타이밍 정보, 및 데이터 스트로브 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 15.

제 12 항에 있어서, 상기 메모리 모듈 제어부는,

상기 메모리 모듈 외부와 상기 메모리 신호 정보를 송수신하는 송수신부;

상기 메모리 정보 저장부로부터의 상기 메모리 정보를 검출하는 메모리 정보 검출부;

상기 송수신부에서 수신된 상기 메모리 신호 정보와 상기 검출된 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어하는 메모리 장치 제어부; 및

상기 복수의 메모리 장치들과 상기 메모리 모듈 제어부 간의 인터페이스를 수행하는 인터페이스부를 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 16.

제 15 항에 있어서, 상기 메모리 장치 제어부는,

상기 메모리 신호 정보에 응답하여 상기 메모리 신호를 생성하는 메모리 신호 생성부;

상기 메모리 정보에 응답하여 상기 메모리 신호의 타이밍을 제어하는 메모리 신호 타이밍 제어부; 및

상기 메모리 신호 타이밍 제어부에 의해 제어된 타이밍에 따라 타이밍이 제어된 메모리 신호를 상기 인터페이스부로 버퍼링하는 메모리 신호 버퍼부를 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 17.

제 16 항에 있어서, 상기 메모리 신호 타이밍 제어부는,

상기 인터페이스 타이밍 정보에 응답하여 클럭신호의 타이밍을 제어하는 클럭신호 타이밍 제어부;

상기 인터페이스 타이밍 정보에 응답하여 명령신호의 타이밍을 제어하는 명령신호 타이밍 제어부;

상기 인터페이스 타이밍 정보에 응답하여 어드레스 신호의 타이밍을 제어하는 어드레스 타이밍 제어부; 및

상기 인터페이스 타이밍 정보에 응답하여 데이터 스트로브신호의 타이밍을 제어하는 데이터 스트로브 타이밍 제어부를 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 18.

제 16 항에 있어서, 메모리 신호 버퍼부는,

상기 클럭신호 타이밍 제어부에 의해 타이밍이 제어된 클럭신호를 상기 인터페이스부로 공급하는 클럭신호 버퍼부;

상기 명령신호 타이밍 제어부에 의해 타이밍이 제어된 명령신호를 상기 인터페이스부로 공급하는 명령신호 버퍼부;

상기 어드레스 타이밍 제어부에 의해 타이밍이 제어된 어드레스신호를 상기 인터페이스부로 공급하는 어드레스 버퍼부; 및

상기 데이터 스트로브 타이밍 제어부에 의해 타이밍이 제어된 데이터 스트로브신호를 상기 인터페이스부로 공급하는 데이터 스트로브 버퍼부를 구비하는 것을 특징으로 하는 메모리 모듈.

### 청구항 19.

메모리 정보 저장부 및 메모리 모듈 제어부를 구비하는 메모리 모듈에 장착된 복수의 메모리 장치들의 타이밍을 제어하는 방법에 있어서,

상기 메모리 정보 저장부에 저장된 메모리 정보를 독출하는 단계;

메모리 신호 정보 및 상기 메모리 정보를 상기 메모리 모듈 제어부로 전송하는 단계; 및

상기 전송된 메모리 신호 정보와 상기 메모리 정보에 응답하여 메모리 신호의 타이밍을 제어하여 상기 복수의 메모리 장치들로 전송하는 단계를 구비하며,

상기 메모리 정보는 메모리 초기화 정보 및 메모리 장치의 인터페이스 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 장치의 타이밍 제어 방법.

### 청구항 20.

제 19 항에 있어서, 상기 메모리 신호의 타이밍을 제어하는 단계는,

상기 메모리 신호 정보를 이용하여 상기 메모리 신호를 생성하는 단계; 및

상기 메모리 정보를 이용하여 메모리 신호의 타이밍을 제어하는 단계를 구비하는 것을 특징으로 하는 메모리 장치의 타이밍 제어 방법.

### 청구항 21.

제 19 항에 있어서,

상기 인터페이스 타이밍 정보는 클럭신호 타이밍 정보, 명령신호 타이밍 정보, 어드레스 타이밍 정보, 및 데이터 스트로브 타이밍 정보를 구비하는 것을 특징으로 하는 메모리 장치의 타이밍 제어 방법.

## 도면

도면1

도면2

도면3

도면4

도면5

도면5는 SPD Byte #와 SPD Value, CLK Adjust를 기준으로 정렬된 테이블입니다. 예제로 126 for CLK, 127 for CMD, 128 for ADD를 각각 살펴보겠습니다.

| SPD Byte #               | SPD Value | CLK Adjust |

|--------------------------|-----------|------------|

| 126 for CLK<br>(Example) | 0C        | +300 ps    |

|                          | 0D        | +200 ps    |

|                          | 0E        | +100 ps    |

|                          | 0F        | Default    |

|                          | 10        | -100 ps    |

|                          | 11        | -200 ps    |

|                          | 12        | -300 ps    |

| 127 for CMD<br>(Example) | 0C        | +300 ps    |

|                          | 0D        | +200 ps    |

|                          | 0E        | +100 ps    |

|                          | 0F        | Default    |

|                          | 10        | -100 ps    |

|                          | 11        | -200 ps    |

|                          | 12        | -300 ps    |

| 128 for ADD<br>(Example) | 0C        | +300 ps    |

|                          | 0D        | +200 ps    |

|                          | 0E        | +100 ps    |

|                          | 0F        | Default    |

|                          | 10        | -100 ps    |

|                          | 11        | -200 ps    |

|                          | 12        | -300 ps    |

도면6

도면7

도면8

도면9

## 도면10