(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5518381号

(P5518381)

(45) 発行日 平成26年6月11日(2014.6.11)

(24) 登録日 平成26年4月11日(2014.4.11)

(51) Int.Cl.

H01L 31/10 (2006.01)

F 1

H01L 31/10

A

H01L 31/10

D

請求項の数 9 (全 54 頁)

(21) 出願番号 特願2009-158854 (P2009-158854)

(22) 出願日 平成21年7月3日 (2009.7.3)

(65) 公開番号 特開2010-41043 (P2010-41043A)

(43) 公開日 平成22年2月18日 (2010.2.18)

審査請求日 平成24年7月2日 (2012.7.2)

(31) 優先権主張番号 特願2008-180776 (P2008-180776)

(32) 優先日 平成20年7月10日 (2008.7.10)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 広瀬 篤志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 堀部 修平

最終頁に続く

(54) 【発明の名称】 カラーセンサ及び当該カラーセンサを具備する電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

インターポーラと、第1の光センサと、第2の光センサと、を有し、

前記第1の光センサは、第1の光電流変換回路部と、第1の光フィルタと、を有し、

前記第2の光センサは、第2の光電流変換回路部と、第2の光フィルタと、を有し、

前記第1の光電流変換回路部及び前記第2の光電流変換回路部は、前記インターポーラ

の表面側に設けられた配線と電気的に接続され、

前記配線は、前記インターポーラに設けられた開口を介して、前記インターポーラの裏

面側に設けられた電極と電気的に接続され、

前記電極は、前記第1の光電流変換回路部及び前記第2の光電流変換回路部と重畳せず

前記電極は、前記第1の光フィルタと重畳する領域、又は、前記第2の光フィルタと重

畳する領域を有することを特徴とするカラーセンサ。

## 【請求項 2】

インターポーラと、第1の光センサと、第2の光センサと、を有し、

前記第1の光センサは、第1の光電流変換回路部と、第1の光フィルタと、を有し、

前記第2の光センサは、第2の光電流変換回路部と、第2の光フィルタと、を有し、

前記第1の光電流変換回路部及び前記第2の光電流変換回路部は、前記インターポーラ

の表面側に設けられた第1の配線と電気的に接続され、

前記第1の光電流変換回路部及び前記第2の光電流変換回路部は、前記インターポーラ

10

20

の表面側に設けられた第2の配線と電気的に接続され、

前記第1の配線は、前記インターポーラーに設けられた第1の開口を介して、前記インターポーラーの裏面側に設けられた第1の電極と電気的に接続され、

前記第2の配線は、前記インターポーラーに設けられた第2の開口を介して、前記インターポーラーの裏面側に設けられた第2の電極と電気的に接続され、

前記第1の電極には、第1の電位が供給され、

前記第2の電極には、第2の電位が供給され、

前記第1の電極は、前記第1の光電流変換回路部及び前記第2の光電流変換回路部と重畳せず、

前記第2の電極は、前記第1の光電流変換回路部及び前記第2の光電流変換回路部と重畳せず、 10

前記第1の電極は、前記第1の光フィルタと重畳する領域、又は、前記第2の光フィルタと重畳する領域を有し、

前記第2の電極は、前記第1の光フィルタと重畳する領域、又は、前記第2の光フィルタと重畳する領域を有することを特徴とするカラーセンサ。

**【請求項3】**

インターポーラーと、光センサと、を有し、

前記光センサは、第1の光電流変換回路部と、第2の光電流変換回路部と、第1の光フィルタと、第2の光フィルタと、を有し、

前記第1の光電流変換回路部及び前記第2の光電流変換回路部は、前記インターポーラーの表面側に設けられた配線と電気的に接続され、 20

前記配線は、前記インターポーラーに設けられた開口を介して、前記インターポーラーの裏面側に設けられた電極と電気的に接続され、

前記電極は、前記第1の光電流変換回路部及び前記第2の光電流変換回路部と重畳せず

前記電極は、前記第1の光フィルタと重畳する領域、又は、前記第2の光フィルタと重畳する領域を有することを特徴とするカラーセンサ。

**【請求項4】**

インターポーラーと、光センサと、を有し、

前記光センサは、第1の光電流変換回路部と、第2の光電流変換回路部と、第1の光フィルタと、第2の光フィルタと、を有し、 30

前記第1の光電流変換回路部及び前記第2の光電流変換回路部は、前記インターポーラーの表面側に設けられた第1の配線と電気的に接続され、

前記第1の光電流変換回路部及び前記第2の光電流変換回路部は、前記インターポーラーの表面側に設けられた第2の配線と電気的に接続され、

前記第1の配線は、前記インターポーラーに設けられた第1の開口を介して、前記インターポーラーの裏面側に設けられた第1の電極と電気的に接続され、

前記第2の配線は、前記インターポーラーに設けられた第2の開口を介して、前記インターポーラーの裏面側に設けられた第2の電極と電気的に接続され、

前記第1の電極には、第1の電位が供給され、

前記第2の電極には、第2の電位が供給され、

前記第1の電極は、前記第1の光電流変換回路部及び前記第2の光電流変換回路部と重畳せず、

前記第2の電極は、前記第1の光電流変換回路部及び前記第2の光電流変換回路部と重畳せず、

前記第1の電極は、前記第1の光フィルタと重畳する領域、又は、前記第2の光フィルタと重畳する領域を有し、

前記第2の電極は、前記第1の光フィルタと重畳する領域、又は、前記第2の光フィルタと重畳する領域を有することを特徴とするカラーセンサ。

**【請求項5】**

10

20

30

40

50

請求項 2 又は 4 において、

前記インターポーラは、前記第 1 の配線及び第 2 の配線と電気的に接続されていない第 3 の配線、又は、前記第 1 の電極及び前記第 2 の電極と電気的に接続されていない第 3 の電極を有することを特徴とするカラーセンサ。

【請求項 6】

請求項 1 乃至 5 のいずれか一項について、

前記第 1 の光フィルタ及び前記第 2 の光フィルタは、透光性を有する樹脂に覆われていることを特徴とするカラーセンサ。

【請求項 7】

請求項 1 乃至 6 のいずれか一項において、

前記第 1 の光電流変換回路部及び前記第 2 の光電流変換回路部は、光電変換素子からの信号を対数圧縮することができる機能を有することを特徴とするカラーセンサ。

【請求項 8】

請求項 1 乃至 6 のいずれか一項において、

前記第 1 の光電流変換回路部及び前記第 2 の光電流変換回路部は、光電変換素子からの信号をデジタル信号に変換することができる機能を有することを特徴とするカラーセンサ。

【請求項 9】

請求項 1 乃至 8 のいずれか一項に記載のカラーセンサを有することを特徴とする電子機器。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、カラーセンサに関する。また、当該カラーセンサを具備する電子機器に関する。

【背景技術】

【0002】

光の強度を電気的な信号に変換して出力する光センサは数多く知られており、紫外線から赤外線にかけて感度を有するものである。光センサは、人間の生活環境に応じて照度調整や、オンまたはオフの制御などが必要な機器類に数多く用いられている。

20

【0003】

表示装置では、表示装置の周囲の明るさを検出し、その表示輝度を調整することが行われているものもある。光センサにより、周囲の明るさを検出して適度な表示輝度を得ることによって、視認性を向上させ、表示装置の無駄な電力を減らすことができるからである。例えば、輝度調整用の光センサを具備する表示装置としては、携帯電話、表示部付きコンピュータが挙げられる。また表示部周囲の明るさだけではなく、表示装置、特に液晶表示装置のバックライトの輝度を光センサにより検出し、表示画面の輝度を調節することも行われている。

30

【0004】

光センサは、光のセンシング部分にフォトダイオードなどの光電変換素子を用い、光電変換素子に流れる電流量に基づいて照度を検出することができる。特許文献 1 には、光センサの照度のダイナミックレンジを取るために、光電変換素子より生じる光電流をダイオード素子に流すことで、対数圧縮された電圧値による出力信号を得る構成について記載されている。なお対数圧縮とは、光電変換素子に入射する光の照度、すなわち光電流の値を変数として、出力される電流値または電圧値を対数の関数として得ることをいう。また、特許文献 1 には、入射光量に応じてフォトダイオードから流れる電流により得られるアナログ値をデジタル値に変換した出力信号とする構成について記載している。

40

【0005】

また特許文献 2 には、複数の光センサを基板上に設け、波長の異なる光を受光するカラーセンサについて記載している。

50

**【先行技術文献】****【特許文献】****【0006】**

【特許文献1】特開2008-124568号公報

【特許文献2】特開2006-135320号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

特許文献2に示す複数の光センサを具備するカラーセンサは、大面積基板を半導体素子層ごとに分断して基板に実装することとなる。基板に実装される複数の光センサは、選択して設けることができるため、それぞれ光透過特性の異なる光センサを組み合わせて実装し、カラーセンサを作製することができる。

10

**【0008】**

しかしながら、特許文献1に示すように光センサの集積化、小型化に伴い、光センサの端子数の増加が進んでいるのが現状である。そのため、カラーセンサを作製する際に組み合わせる光センサの実装数に比例して端子数が増加するため、基板側では外部機器と電気的に接続するための端子電極の数が増加してしまう。

20

**【0009】**

本発明の一態様は上述の課題を解決するために案出されたものであり、外部機器と電気的に接続するための端子電極の減少を図ることができるカラーセンサを提供することを課題の一とする。

**【課題を解決するための手段】****【0010】**

本発明の一態様は、光電変換素子、及び光フィルタが透光性基板上に設けられた複数の光センサと、を有し、複数の前記光センサにおける前記光フィルタは、各々異なる光透過特性を具備しており、複数の前記光センサが、外部機器と電気的に接続するための複数の端子電極を有するインターポーラ上に実装されており、前記インターポーラは、高電源電位を入力するための前記端子電極と複数の前記光センサとの電気的な接続、及び低電源電位を入力するための前記端子電極と複数の前記光センサとの電気的な接続、をとるために、複数の分岐を有する配線を具備するカラーセンサである。

30

**【0011】**

また本発明の一態様は、複数の光電変換素子、及び複数の光フィルタが透光性基板上に設けられた光センサと、を有し、複数の前記光フィルタは、各々異なる光透過特性を具備しており、前記光センサが、外部機器と電気的に接続するための複数の端子電極を有するインターポーラ上に実装されており、前記インターポーラは、高電源電位を入力するための前記端子電極と前記光センサとの電気的な接続、及び低電源電位を入力するための前記端子電極と前記光センサとの電気的な接続、をとるために、複数の分岐を有する配線を具備するカラーセンサである。

**【0012】**

また本発明の一態様は、光電変換素子、光電流変換回路部、及び光フィルタが透光性基板上に設けられた複数の光センサと、を有し、複数の前記光センサにおける前記光フィルタは、各々異なる光透過特性を具備しており、複数の前記光センサが、外部機器と電気的に接続するための複数の端子電極を有するインターポーラ上に実装されており、前記インターポーラは、高電源電位を入力するための前記端子電極と複数の前記光センサとの電気的な接続、及び低電源電位を入力するための前記端子電極と複数の前記光センサとの電気的な接続、をとるために、複数の分岐を有する配線を具備しており、複数の前記端子電極と、前記光電流変換回路部は離間して設けられているカラーセンサである。

40

**【0013】**

また本発明の一態様は、複数の光電変換素子、複数の光電流変換回路部、及び複数の光フィルタが透光性基板上に設けられた光センサと、を有し、複数の前記光フィルタは、各々

50

異なる光透過特性を具備しており、前記光センサが、外部機器と電気的に接続するための複数の端子電極を有するインターポーヴ上に実装されており、前記インターポーヴは、高電源電位を入力するための前記端子電極と前記光センサとの電気的な接続、及び低電源電位を入力するための前記端子電極と前記光センサとの電気的な接続、をとるために、複数の分岐を有する配線を具備しており、複数の前記端子電極と、複数の前記光電流変換回路部は離間して設けられているカラーセンサである。

【発明の効果】

【0014】

本発明の一態様により、外部と接続するための端子電極数の減少を図ることのできるカラーセンサとすることができる。

10

【図面の簡単な説明】

【0015】

【図1】カラーセンサを説明する図。

【図2】カラーセンサを説明する図。

【図3】カラーセンサを説明する図。

【図4】カラーセンサを説明する図。

【図5】カラーセンサを説明する図。

【図6】カラーセンサを説明する図。

【図7】カラーセンサを説明する図。

【図8】カラーセンサを説明する図。

【図9】カラーセンサを説明する図。

【図10】カラーセンサを説明する図。

【図11】カラーセンサを説明する図。

【図12】カラーセンサを構成するトランジスタを説明する図。

【図13】カラーセンサを構成するトランジスタを説明する図。

【図14】カラーセンサを構成するトランジスタを説明する図。

【図15】カラーセンサを構成するトランジスタを説明する図。

【図16】カラーセンサを構成するトランジスタを説明する図。

【図17】カラーセンサを構成するトランジスタを説明する図。

【図18】カラーセンサを具備する電子機器を説明する図。

20

【図19】カラーセンサを具備する電子機器を説明する図。

【図20】カラーセンサを具備する電子機器を説明する図。

【図21】カラーセンサを具備する電子機器を説明する図。

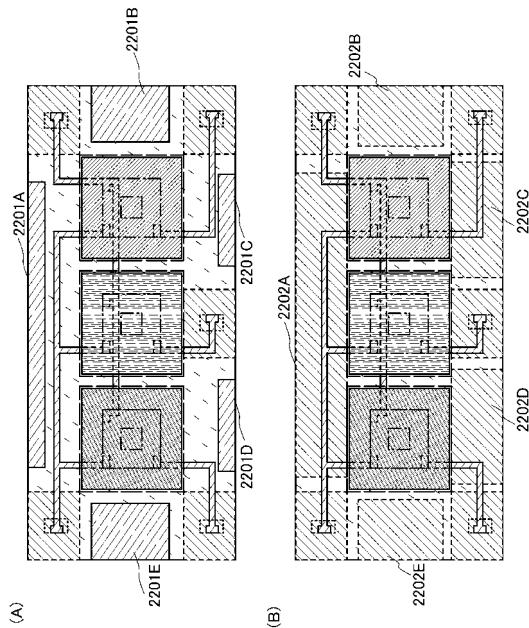

【図22】カラーセンサを説明する図。

【発明を実施するための形態】

【0016】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

40

【0017】

(実施の形態1)

本実施の形態では、外部と接続するための端子数の減少を図ることのできるカラーセンサについて説明していく。なお本実施の形態で説明する光センサは、光電変換素子により得られる入射光量に関する信号を、高電源電位  $V_{dd}$  及び低電源電位  $V_{ss}$  に接続された光電流変換回路部により、電流値または電圧値として外部に出力、若しくはデジタル信号として外部に出力、するものである。

【0018】

50

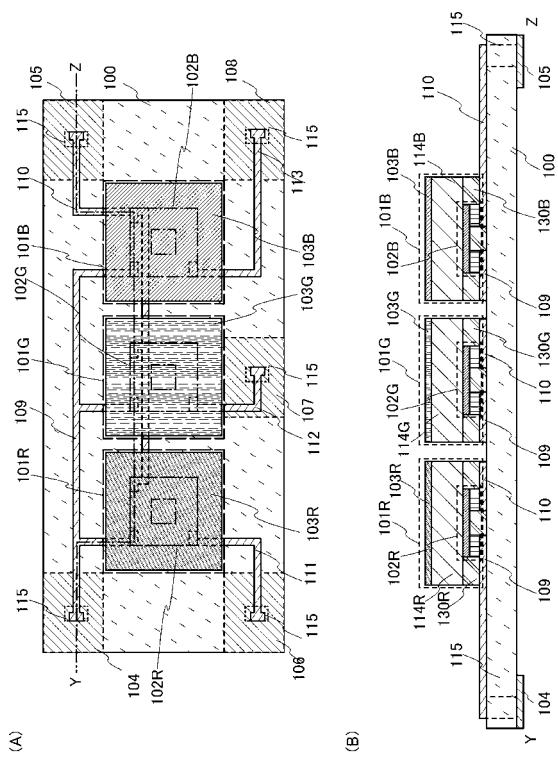

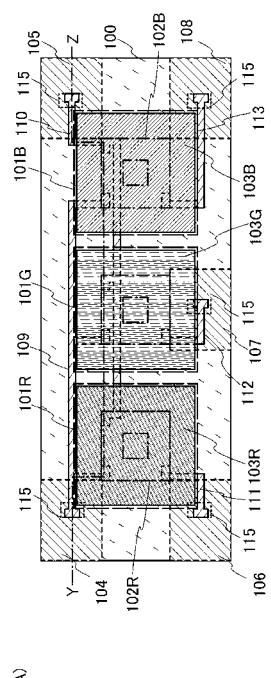

図1( A )、図1( B )に本実施の形態のカラーセンサを示す。図1( A )はカラーセンサの上面図であり、図1( B )は図1( A )の線Y-Zの断面図である。

【 0 0 1 9 】

図1( A )に示す上面図で、カラーセンサは、光センサ101R、光センサ101G、光センサ101Bをインターポーラ100に実装されて有する構造である。光センサ101Rは、光電流変換回路部102Rを有し、光の入射面に光フィルタ103Rを具備する構成である。光センサ101Gは、光電流変換回路部102Gを有し、光の入射面に光フィルタ103Gを具備する構成である。光センサ101Bは、光電流変換回路部102Bを有し、光の入射面に光フィルタ103Bを具備する構成である。また、インターポーラ100には、光センサ101R、光センサ101G、及び光センサ101Bが設けられていない面(以下、裏面という)に、外部との電気的接続を行うための電極である端子電極104(単に、端子ともいう)、端子電極105、端子電極106、端子電極107、端子電極108が設けられている。また、インターポーラ100には、光センサ101R、光センサ101G、及び光センサ101Bと接する面(以下、表面という)に、端子電極104、端子電極105、端子電極106、端子電極107、または端子電極108と、光センサ101R、光センサ101G、及び光センサ101Bとの電気的接続を行うための導電層である配線109、配線110、配線111、配線112、配線113が設けられている。また、インターポーラ100は点線115で示すように、配線109、配線110、配線111、配線112、配線113と、端子電極104、端子電極105、端子電極106、端子電極107、端子電極108とを電気的に接続するための表面と裏面を貫通する開口が複数設けられている。

【 0 0 2 0 】

図1( B )に示す断面図で、光センサ101Rは、光電流変換回路部102Rと光フィルタ103Rとの間に透光性基板114Rを具備する構成である。また光センサ101Gは、光電流変換回路部102Gと光フィルタ103Gとの間に透光性基板114Gを具備する構成である。また光センサ101Bは、光電流変換回路部102Bと光フィルタ103Bとの間に透光性基板114Bを具備する構成である。また、インターポーラ100は図1( B )の点線115で示すように、表面と裏面とを貫通する開口を複数有しており、配線109、配線110、配線111、配線112、配線113により、光センサ101R、光センサ101G、光センサ101Bと、端子電極104、端子電極105、端子電極106、端子電極107、端子電極108とを電気的に接続している。従って、端子電極104、端子電極105、端子電極106、端子電極107、端子電極108は光センサ101R、光センサ101G、光センサ101Bの外部電極として、他の基板に実装することができる。また、光センサ101R、光センサ101G、光センサ101Bとインターポーラ100との間に樹脂130R、樹脂130G、樹脂130B、を設けて固着すると、固着強度が向上するためには嬉しい。

【 0 0 2 1 】

なお、光フィルタ103R、光フィルタ103G、光フィルタ103Bは、有彩色の透光性樹脂層で構成されており、それぞれ異なる光透過特性を有するものである。一例としては、光センサ101Rは赤色を透過する光フィルタ103R、光センサ101Gは緑色を透過する光フィルタ103G、光センサ101Bは青色を透過する光フィルタ103Bをそれぞれ有しており、それぞれの光センサ101R、光センサ101G、光センサ101Bに透過した色の光を検知することができる。よって、光フィルタ103R、光フィルタ103G、光フィルタ103Bを含む本実施の形態のカラーセンサは、3種類の色(赤色、緑色、青色)の光をそれぞれに検知することができるカラーセンサである。

【 0 0 2 2 】

なお有彩色は、黒色、灰色、白色などの無彩色を除く色であり、光フィルタ103R、光フィルタ103G、光フィルタ103Bはカラーフィルタとして機能させるため、その着色された有彩色の光のみを透過する材料で形成される。有彩色としては、赤色、緑色、青色などを用いることができる。また、シアン、マゼンダ、イエロー(黄)などを用いても

よい。

【0023】

なお光センサ101R、光センサ101G、光センサ101Bとインターポーザ100の配線との接続部分の構造としては、インターポーザ100上の配線と光センサ101R、光センサ101G、光センサ101Bの端子に設けられた導電性の突起物であるバンプとを接触させ、インターポーザ100と光センサ101R、光センサ101G、光センサ101Bとを樹脂で固定してもよい。またインターポーザ100の配線と、光センサ101R、光センサ101G、光センサ101Bの各端子との間に導電性の粒子を分散させた樹脂を設け、この導電性の粒子で光センサ101R、光センサ101G、光センサ101Bとインターポーザ100の配線との接続を行い、導電性の粒子を分散させた有機樹脂で接着、固定してもよい。また、接着に使用する樹脂としては光硬化性の樹脂や熱硬化性のものあるいは自然硬化性の樹脂等を用いることができる。10

【0024】

なおインターポーザ100の材料としては、有機ポリマー、無機ポリマー、ガラスエポキシ系やセラミック系、ポリイミド、フッ素樹脂などを用いることができる。

【0025】

また、インターポーザ100の厚さは50μm～300μm（代表的には100μm～200μm）程度である。より厚さの薄いインターポーザを用いると、カラーセンサの薄型化の効果をより高めることができる。20

【0026】

また、図1（A）の上面図、図1（B）の断面図で示すように、インターポーザ100の表面と裏面において、端子電極104、端子電極105、端子電極106、端子電極107、及び端子電極108と、光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bとの配置が重畠しないようにすることが好ましい。その理由は、端子電極104、端子電極105、端子電極106、端子電極107、及び端子電極108と、外部機器との電気的接続を行うためにはんだ等の加熱処理を伴う場合、端子電極104、端子電極105、端子電極106、端子電極107、及び端子電極108から熱の移動による光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bの不良の発生を低減することができるからである。また、熱の放散を促進するために配線109乃至配線113は、インターポーザ100上では光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bから離間して設けることが好ましい。30

【0027】

なお図1（A）、図1（B）では、インターポーザ100の表面と裏面において、光フィルタ103R、光フィルタ103G、光フィルタ103Bと、端子電極104、端子電極105、端子電極106、端子電極107、及び端子電極108とを離間して設ける構成について示した。図9（A）、図9（B）の上面図及び断面図で示すように、インターポーザ100の表面と裏面において、光フィルタ103R、光フィルタ103G、光フィルタ103Bと、端子電極104、端子電極105、端子電極106、端子電極107、及び端子電極108とを重畠して設ける構成としてもよい。図9の構成とすることで、インターポーザ100の小型化を図ることができるために、カラーセンサを小型化することができる。なお、予め配線の幅や形状を変更することで、配線109、配線110、配線111、配線112、配線113を配線の間の余分な面積に延設させて図22（A）と同様の効果を得てもよい。40

【0028】

また、図1（A）に示す上面図では、光フィルタ103R、光フィルタ103G、光フィルタ103Bと、端子電極104、端子電極105、端子電極106、端子電極107、及び端子電極108とを離間して設ける構成であるため、インターポーザ100の表側では、端子電極と各光センサ間を電気的に接続するための配線の間に余分な面積を有することとなる。本実施の形態では、図22（A）に示すように、配線の間に、他の配線と電気50

的に接続のない配線 2201A 乃至 2201E を設けてもよい。配線 2201A 乃至 2201E を設けることにより、曲げ等による強度を向上させることができるため、衝撃に強いカラーセンサとすることができます。なお、予め端子電極の大きさや形状を変更することで、端子電極 104、端子電極 105、端子電極 106、端子電極 107、または端子電極 108 を端子電極間に余分な面積に設けて図 22 (B) と同様の効果を得てもよい。また図 22 (A) の構成と組み合わせて実施してもよい。

#### 【0029】

また、図 22 (A) と同様に、インターポーザ 100 の裏面側では、端子電極間に余分な面積を有することとなる。本実施の形態では、図 22 (B) に示すように、端子電極の間に、他の端子電極と電気的に接続のない電極 2202A 乃至 2202E を設けてもよい。電極 2202A 乃至 2202E を設けることにより、曲げ等による強度を向上させることができるために、衝撃に強いカラーセンサとすることができます。

10

#### 【0030】

インターポーザ 100 に実装される複数の光センサは、自由に選択することができるため、有彩色の光フィルタ 103R、光フィルタ 103G、光フィルタ 103B を備えた光センサをインターポーザ 100 に実装し、カラーセンサを作製することができる。また、インターポーザ 100 に実装する際に、光センサに検査工程を行い、良品のみを選別してインターポーザ 100 に実装することができるため、作製工程においてカラーセンサの歩留まりを向上させることができる。特に、光電流変換回路部に演算回路など複雑な構成を含む構成の場合、チップ状の光センサに不良が生じる恐れがあるため、インターポーザに実装する前に光センサの不良検査が行えることは有効である。

20

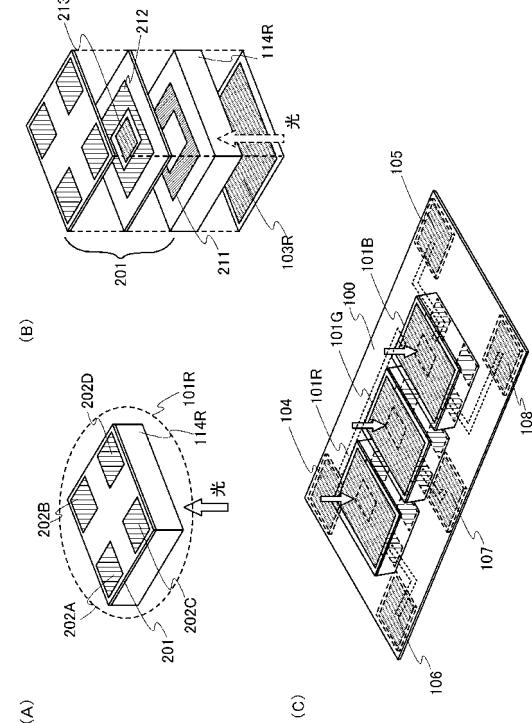

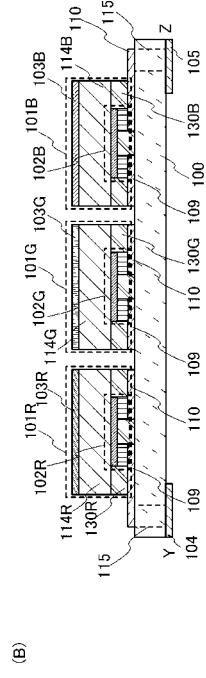

#### 【0031】

次に図 2 (A) 乃至 (C) を用いて、図 1 (A)、(B) で示す光センサ 101R、光センサ 101G、光センサ 101B の構成について説明する。なお、光センサ 101R、光センサ 101G、光センサ 101B の違いは、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B の光透過特性の違いによるものである。図 2 (A)、(B) では、カラーセンサを構成する光センサの一つである光センサ 101R の構成について示す。なお光センサ 101G、光センサ 101B は、光センサ 101R との違いについて大きくは光フィルタが異なる点にあり、その説明を省略する。

#### 【0032】

30

光センサ 101R には、透光性基板 114R 上に光電変換回路部 201 を有する。光電変換回路部 201 上には、外部との信号の入出力を行うための第 1 の端子 202A、第 2 の端子 202B、第 3 の端子 202C、第 4 の端子 202D を有する。光センサ 101R には、透光性基板 114R 側より光が入射され、光電変換回路部 201 で照度に応じた出力信号に変換される。

#### 【0033】

なお本明細書にて用いる第 1、第 2、第 3、乃至第 N (N は自然数) という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

#### 【0034】

40

第 1 の端子 202A、第 2 の端子 202B、第 3 の端子 202C、第 4 の端子 202D は湿式法を用いて導電性樹脂によって形成されてもよいし、乾式法を用いて導電性薄膜によって形成されてもよい。また、導電性樹脂層と導電性薄膜とを積層してもよい。

#### 【0035】

例えば、スクリーン印刷法を用いて端子を形成する場合には、粒径が数 nm から数十  $\mu$ m の導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀 (Ag)、金 (Au)、銅 (Cu)、ニッケル (Ni)、白金 (Pt)、パラジウム (Pd)、タンタル (Ta)、モリブデン (Mo) およびチタン (Ti) 等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子の

50

バインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコン樹脂等の有機樹脂が挙げられる。また、導電層の形成の際は、導電性のペーストを押し出した後に焼成することが好ましい。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよい。

【0036】

なお図2(A)では、一例として、第1の端子202A、第2の端子202B、第3の端子202C、第4の端子202Dの4つの端子を有する光センサについて示している。光センサには、高電源電位及び低電源電位が入力されるとともに、電圧値または電流値のアナログ信号が出力信号として出力される、またはバス規格に応じたデジタル信号が入出力されるものもある。

10

【0037】

なお、図2(A)では、第1の端子202A乃至第4の端子202Dの形状について同様に記したが、異なる形状としてもよい。端子電極の形状をそれぞれ異なる形状とすることにより、光センサをインターポーラに取り付ける際に取り付ける向きを容易に把握することができる。

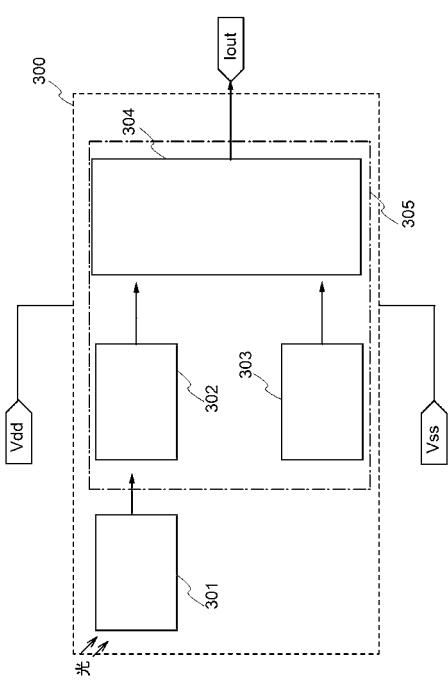

【0038】

次に、図3を用いて、第1の端子202A乃至第4の端子202Dに入出力される信号について説明する。図3は、高電源電位Vdd及び低電源電位Vssが入力され、光電流に応じた出力信号を対数圧縮して出力する回路を具備する光センサの構成の一例を示すブロック図である。なお図3に示す例では、端子数は3つあればよく、図2(A)に示す光センサでは一つの端子が余ることとなる。この場合余った端子を、他の端子と同じ電位または信号を入出力する端子とするか、別の信号を入出力する端子としてもよい。なお対数圧縮とは、光電変換素子に入射する光の照度、すなわち光電流の値を変数として、出力される電流値または電圧値を対数の関数として得ることをいう。

20

【0039】

図3に示す光センサ300は、光電変換素子301、対数圧縮回路302、温度補正電圧生成回路303、温度補正演算回路304を有する。光電変換素子301は外部からの光を受光し、照度に応じた光電流を対数圧縮回路302に出力する。対数圧縮回路302は、光電流をダイオード素子により、対数圧縮した電圧値にして出力する回路である。温度補正電圧生成回路303は、光電流を対数圧縮する際に用いたダイオード素子の温度依存による出力の変化を補正するための温度補正電圧を出力するための回路である。温度補正演算回路304は、対数圧縮回路302から出力される対数圧縮された電圧値、及び温度補正電圧生成回路から出力される温度補正電圧を基に出力信号である電流値Ioutを生成するための回路である。なお、図1で示した光電流変換回路部は、対数圧縮回路302、温度補正電圧生成回路303、及び温度補正演算回路304を有する回路部305に相当する。

30

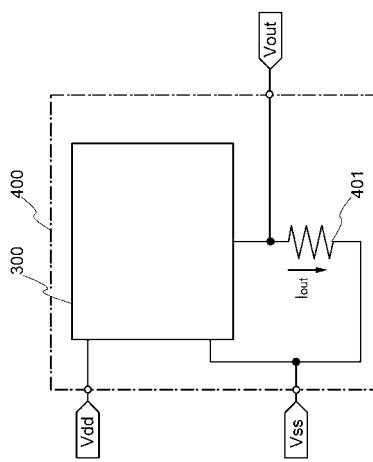

【0040】

また光センサ300は、図3で示した出力信号である電流値Ioutを、外部抵抗を設けることにより、電圧Voutとして出力することもできる。図4に電圧Voutとして出力することのできる光センサ400を示す。図4に示す光センサ400は、図3で示した光センサ300を内包し、内部抵抗401を設け、外部への出力として電圧Voutを得る構成の一例である。

40

【0041】

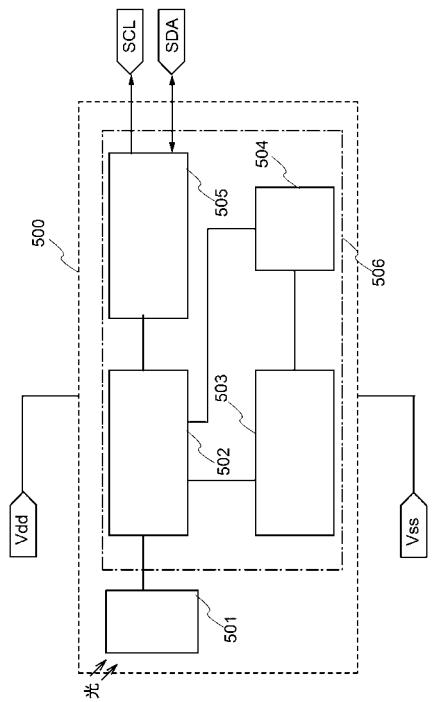

また、第1の端子202A乃至第4の端子202Dに入出力される信号の別の例について説明する。図5は、アナログ信号をデジタル信号に変換して出力する回路を具備する光センサのブロック図である。なお図5に示す例では、高電源電位Vdd及び低電源電位Vssの他に、出力信号を入出力するための端子が2つあればよく、合計の端子数は4つあればよい。図5に示す光センサ500は、光電変換素子501、アナログ/デジタル変換回路502(以下AD変換回路という)、定電圧回路503、発振回路504、I2C(Inter Integrated circuit)インターフェース回路505を有す

50

る。

【0042】

なお、図5に示す光電変換素子501は外部からの光を受光し、照度に応じた光電流をA

D変換回路502に出力する。A D変換回路502は、連続量である光電流の値を量子化

して、デジタル信号に変換してI2Cインターフェース回路505に出力する回路である。

定電圧回路503はA D変換回路502及び発振回路504を動作するための一定の電

圧を生成するための回路である。発振回路504は、A D変換回路502を動作するため

のクロック信号を出力するための回路である。I2Cインターフェース回路505は、他

の装置とのデータ通信のためのシリアルデータライン(SDA)と、他の装置との間のデ

ータ通信を制御及び同期化するためのシリアルクロックライン(SCL)と、からなるI

2Cバスによって外部装置と電気的に接続されるための回路である。SDAとSCLから

なるI2Cバスは、各装置に設けられるアドレスメモリに割り振られた固有のアドレスに

よって、マイクロコンピュータからの制御を行うためのバス規格である。なお他の装置が

液晶表示装置である場合には、ディスプレイドライバー、LEDドライバーがI2Cバス

によって電気的に接続される構成となる。なお、図1(A)、(B)で示した光電流変換

回路部102R、102G、102Bは、A D変換回路502、定電圧回路503、発振

回路504、I2Cインターフェース回路505を有する回路部506に相当する。

10

【0043】

なお、A D変換回路502は、連続量である電圧 $V_{out}$ を量子化して、デジタル信号に

変換するための回路である。A D変換回路502としては、例えば、並列比較方式A D変

換回路、パイプライン方式A D変換回路、逐次比較方式A D変換回路、デルタシグマ方式

A D変換回路、二重積分方式A D変換回路があり、任意で選択すればよい。

20

【0044】

なお図5には、I2Cインターフェースを適用した光センサ500を示したが、I2Cバ

ス以外に、ユニバーサルシリアルバス(Universal Serial Bus)、シリアル周辺インターフェース(Serial Peripheral Interface)等のバス規格を用いることができる。

【0045】

上記図3乃至図5のブロック図に示す光センサを、図1(A)で示す複数の光センサに適

用してカラーセンサを構成する場合には、外部に接続するための複数の端子より、高電源

電位 $V_{dd}$ 及び低電源電位 $V_{ss}$ が入力されることとなる。そのため、複数の光センサを

インターポーラ上に実装するために、高電源電位 $V_{dd}$ 及び低電源電位 $V_{ss}$ の数に応じて、

インターポーラ上に配線を引き回して端子電極との電気的接続を図る必要がある。

30

【0046】

本実施の形態で示す構成では、図1(A)に示すように、端子電極と各光センサより引き

回される配線との電気的な接続を共通化し、高電源電位を供給するため端子電極を共通化

することができる。図1(A)でいえば、高電源電位を供給するために光センサ間で共通化

する端子は端子電極104であり、端子電極104と各光センサより引き回される配線

は配線109である。すなわち配線109は、複数の光センサと、端子電極104との電

気的な接続を図るために複数の分岐を有する配線である。また同様に本実施の形態の構成

では、図1(A)に示すように、端子電極と各光センサより引き回される配線との電気的

な接続を共通化し、低電源電位を供給するため端子電極を共通化することができる。図1

(A)でいえば、低電源電位を供給するために光センサ間で共通化する端子としては端子

電極105であり、端子電極105と各光センサより引き回される配線としては配線11

0である。すなわち配線110は、配線109と同様に、複数の光センサと、端子電極1

05との電気的な接続を図るために複数の分岐を有する配線である。

40

【0047】

なお各光センサより出力される出力信号が図3に示すような $I_{out}$ の場合は、光センサ

毎に端子電極を割り当てて、各光センサより端子電極へ配線を引き回して電気的な接続を

取ることにより、外部に出力することができる。図1(A)でいえば、光センサ101R

50

からの出力信号を外部に出力する端子は端子電極 106 であり、端子電極 106 と光センサ 101R より引き回される配線は配線 111 である。また図 1 (A) でいえば、光センサ 101G からの出力信号を外部に出力する端子は端子電極 107 であり、端子電極 107 と光センサ 101G より引き回される配線は配線 112 である。また図 1 (A) でいえば、光センサ 101B からの出力信号を外部に出力する端子は端子電極 108 であり、端子電極 108 と光センサ 101B より引き回される配線は配線 113 である。

#### 【0048】

なお各光センサより出力される出力信号が図 5 に示すようなシリアルデータライン及びシリアルクロックラインのように複数の場合は、光センサ毎にシリアルデータライン及びシリアルクロックラインの入出力信号のために端子電極を割り当て、各光センサより端子電極へ配線を引き回して電気的な接続を取ることにより、外部に出力信号を出力することができる。

#### 【0049】

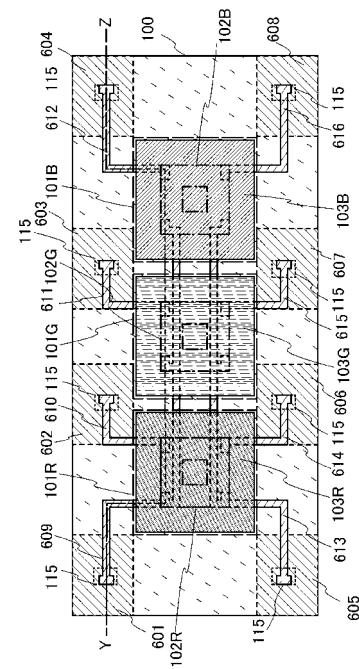

図 6 に、高電源電位 Vdd 及び低電源電位 Vss 以外に、入出力信号が 2 つある際のカラーセンサの上面図を示す。図 1 (A) と同様に、カラーセンサは、光センサ 101R、光センサ 101G、光センサ 101B をインターポーヴ 100 に実装されて有する構造である。光センサ 101R は、光電流変換回路部 102R を有し、光の入射面に光フィルタ 103R を具備する構成である。光センサ 101G は、光電流変換回路部 102G を有し、光の入射面に光フィルタ 103G を具備する構成である。光センサ 101B は、光電流変換回路部 102B を有し、光の入射面に光フィルタ 103B を具備する構成である。また、インターポーヴ 100 には裏面に、外部との電気的接続を行うための電極である端子電極 601、端子電極 602、端子電極 603、端子電極 604、端子電極 605、端子電極 606、端子電極 607、端子電極 608 が設けられている。また、インターポーヴ 100 には表面に、端子電極 601、端子電極 602、端子電極 603、端子電極 604、端子電極 605、端子電極 606、端子電極 607、端子電極 608 と、光センサ 101R、光センサ 101G、及び光センサ 101B との電気的接続を行うための導電層である配線 609、配線 610、配線 611、配線 612、配線 613、配線 614、配線 615、配線 616 が設けられている。また、インターポーヴ 100 は点線 115 で示すように、配線 609 乃至配線 616 と、端子電極 601 乃至端子電極 608 とを電気的に接続するための表面と裏面を貫通する開口が複数設けられている。

#### 【0050】

図 6 で、高電源電位を供給するために光センサ間で共通化する端子としては端子電極 601 であり、端子電極 601 と各光センサより引き回される配線としては配線 609 にあたる。すなわち配線 609 は、複数の光センサと、端子電極 601 との電気的な接続を図るために複数の分岐を有する配線となる。また図 6 で、低電源電位を供給するために光センサ間で共通化する端子としては端子電極 605 であり、端子電極 605 と各光センサより引き回される配線としては配線 613 にあたる。すなわち配線 613 は、配線 609 と同様に、複数の光センサと、端子電極 605 との電気的な接続を図るために複数の分岐を有する配線となる。また図 6 で、光センサ 101R からのシリアルデータラインを外部に出力する端子としては端子電極 602 であり、端子電極 602 と光センサ 101R より引き回される配線としては配線 610 である。また図 6 で、光センサ 101G からのシリアルデータラインを外部に出力する端子としては端子電極 603 であり、端子電極 603 と光センサ 101G より引き回される配線としては配線 611 である。また図 6 で、光センサ 101B からのシリアルデータラインを外部に出力する端子としては端子電極 604 であり、端子電極 604 と光センサ 101B より引き回される配線としては配線 612 である。また図 6 で、光センサ 101R からのシリアルクロックラインを外部に出力する端子としては端子電極 606 であり、端子電極 606 と光センサ 101R より引き回される配線としては配線 614 である。また図 6 で、光センサ 101G からのシリアルクロックラインを外部に出力する端子としては端子電極 607 であり、端子電極 607 と光センサ 101G より引き回される配線としては配線 615 である。また図 6 で、光センサ 101B か

10

20

30

40

50

らのシリアルクロックラインを外部に出力する端子としては端子電極 608 であり、端子電極 608 と光センサ 101B より引き回される配線としては配線 616 である。

#### 【0051】

上述の様に本実施の形態の図 1 及び図 6 で示す複数の光センサを具備するカラーセンサは、図 3 または図 5 の様な光センサを複数具備することで増加してしまう端子数をインターポーヴ上に削減することができる。そのため、端子電極の数を大幅に削減することができる。端子数を削減することにより、外部機器との接続不良の減少を図ることができるため、歩留まりの向上を図ることができる。本実施の形態で示す構成は、特に高電源電位及び低電源電位を入力する端子のように各光センサで共通する端子を具備する複数の光センサを、インターポーヴ上に実装して作製するカラーセンサにおいて有効である。また本実施の形態における構成では、複数の光センサをインターポーヴ上に設けてカラーセンサとする際、ピンコンパチブル（ピン互換）を図ることができる。

10

#### 【0052】

なお、図 6 に示すカラーセンサの上面図は、図 9 (A) と同様に、端子電極 601 乃至端子電極 608 と、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B とを、インターポーヴ 100 の表面と裏面で重畳して設ける構成としてもよい。

#### 【0053】

次に、図 2 (A) で示した光センサ 101R の構成について図 2 (B) を用い、更に詳しく説明する。透光性基板 114R の光が入射される側には、光フィルタ 103R が設けられている。また透光性基板 114R の光フィルタ 103R が設けられている側には、光電変換回路部 201 を構成する光電流変換回路 211、配線層 212、光電変換素子 213 を有する。光電流変換回路 211 は、配線により電気的に接続された半導体層を有し、光電変換素子 213 への照度に応じた出力信号を生成する回路である。配線層 212 は、光電流変換回路 211、光電変換素子 213、及び第 1 の端子 202A 乃至第 4 の端子 202D を電気的に接続するための配線である。光電変換素子 213 は、PIN 型または PIN 型のフォトダイオード、フォトトランジスタ等によって入射される光量に応じた光電流に変換する素子である。また、図 2 (B) に示すように、光電変換回路部の中央付近に配置する構造とすることにより、光フィルタを通過する光のみを受光しやすくでき、好適である。

20

#### 【0054】

30

なお本明細書では、光電変換素子として PIN 型のフォトダイオードを用いた構成について説明を行う。PIN 型のフォトダイオードは、PN 型のフォトダイオードに比べ、光の照射に対する空乏層の応答特性がよいため、好適である。

#### 【0055】

次に図 2 (C) に示すように、光フィルタ 103R を有する光センサ 101R、光フィルタ 103G を有する光センサ 101G、光フィルタ 103B を有する光センサ 101B を、それぞれインターポーヴ 100 上に配置する。そして図 1 (A) で示した配線 109 乃至配線 113 (図 2 (C) 中の点線) により、端子電極 104 乃至端子電極 108 と電気的な接続を取ることができる。

#### 【0056】

40

図 2 (C) に示す構成によると、インターポーヴ 100 に実装する際に、光センサ 101R、光センサ 101G、光センサ 101B は、それぞれに対し検査工程を行い、良品のみを選別してインターポーヴ に実装することができる。そのため、カラーセンサの歩留まりが向上する。特に、光センサが演算回路など複雑な構成を含む光電流変換回路部を有する場合、チップ状の光センサに不良が生じる恐れがある。そのため、インターポーヴ 100 に実装する前に光センサの不良検査が行えることは有効である。さらに、良品の中でも高品質の光センサを選別しインターポーヴ に実装することでより高品質のカラーセンサも作製することもできる。

#### 【0057】

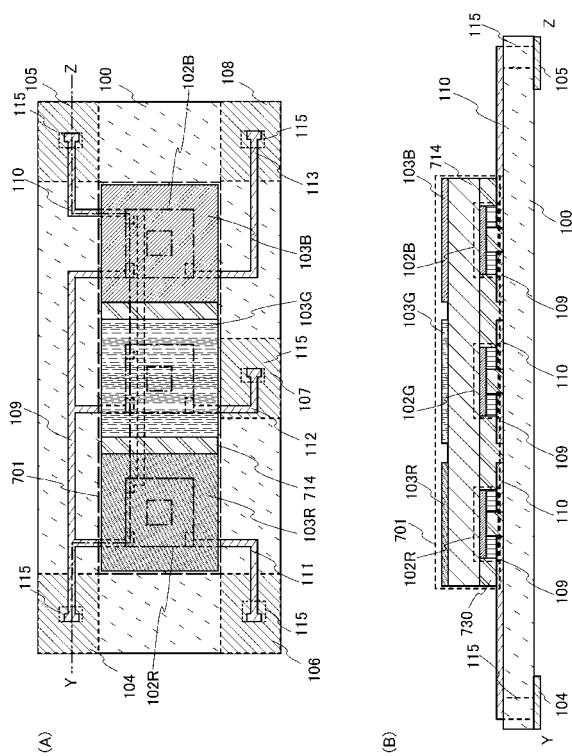

また、図 7 (A)、図 7 (B) に、図 1 (A)、図 1 (B) とは異なるカラーセンサの

50

上面図及び断面図を示す。図7(A)が、図1(A)と異なる点は、カラーセンサが、光センサ701をインターポーラ100に実装する点にあり、光センサ701は、光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bを有し、光の入射面に光フィルタ103R、光フィルタ103G、光フィルタ103Bを具備する構成である。また図7(A)が図1(A)と異なる点は、光フィルタ103R、光フィルタ103G、光フィルタ103Bは、透光性基板714に接して設けられている点にある。

#### 【0058】

なお図7(A)の上面図が図1(A)と同様な点として、インターポーラ100には裏面に、外部との電気的接続を行うための電極である端子電極104、端子電極105、端子電極106、端子電極107、端子電極108が設けられている点にある。また図7(A)の上面図が図1(A)と同様な点として、インターポーラ100には表面に、端子電極104、端子電極105、端子電極106、端子電極107、または端子電極108と、光センサ701との電気的接続を行うための導電層である配線109、配線110、配線111、配線112、配線113が設けられている点にある。また図7(A)の上面図が図1(A)と同様な点として、インターポーラ100には点線115で示すように、配線109、配線110、配線111、配線112、配線113と、端子電極104、端子電極105、端子電極106、端子電極107、端子電極108とを電気的に接続するための表面と裏面を貫通する開口が複数設けられている点がある。

#### 【0059】

図7(B)が、図1(B)と異なる点は、光センサ701は、光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bと、光フィルタ103R、光フィルタ103G、及び光フィルタ103Bとの間に透光性基板714を具備する点にある。また図7(B)が図1(B)と異なる点は、光センサ701とインターポーラ100との間には、固着強度を向上するための樹脂730が光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102B間で隙間なく設けられている点にある。

#### 【0060】

図1(B)とは異なり、図7(A)、図7(B)では樹脂730を隙間なく設ける構成とすることにより、固着強度をより向上することができるため好適である。

#### 【0061】

なお図7(B)の断面図が図1(B)と同様な点として、インターポーラ100は図7(B)の点線115で示すように、表面と裏面とを貫通する開口を複数有しており、配線109、配線110、配線111、配線112、配線113により、光センサ101R、光センサ101G、光センサ101Bと、端子電極104、端子電極105、端子電極106、端子電極107、端子電極108とを電気的に接続している点がある。

#### 【0062】

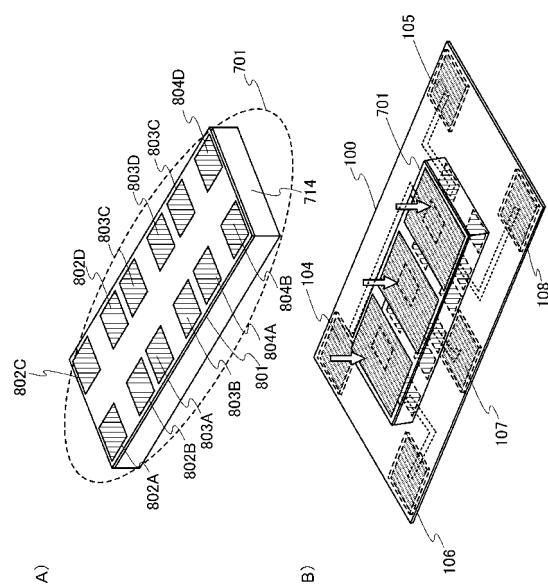

次に図8(A)、図8(B)に、図7(A)、図7(B)で示した光センサ701の構成について説明する。

#### 【0063】

光センサ701には、透光性基板714上に光電変換回路部801を有する。光電変換回路部801上には、光フィルタ103R(図示せず)を通過する光に関する外部との信号の入出力を行うための第1の端子802A、第2の端子802B、第3の端子802C、第4の端子802Dを有する。また光電変換回路部801上には、光フィルタ103G(図示せず)を通過する光に関する外部との信号の入出力を行うための第1の端子803A、第2の端子803B、第3の端子803C、第4の端子803Dを有する。また光電変換回路部801上には、光フィルタ103B(図示せず)を通過する光に関する外部との信号の入出力を行うための第1の端子804A、第2の端子804B、第3の端子804C、第4の端子804Dを有する。光センサ701には、透光性基板714側より光が入射され、光電変換回路部801で照度に応じた出力信号に変換される。

#### 【0064】

なお図8(A)では、一例として、1つの光フィルタに対し、4つの端子を有する光セン

10

20

30

40

50

サ、すなわち 12 個の端子を有する光センサについて示している。光センサには、1 つの光フィルタに応じて高電源電位及び低電源電位が入力される。また光センサからは、電圧値または電流値のアナログ信号が出力信号として出力される、またはバス規格に応じたデジタル信号が入出力される。光センサに入出力される信号の例としては、図 3 乃至図 5 で示した通りである。

#### 【 0 0 6 5 】

次に、図 8 ( A ) で示した光センサ 701 の構成について図 8 ( B ) を用い、更に詳しく説明する。

#### 【 0 0 6 6 】

次に図 8 ( A ) で示した光センサ 701 をインターポーザ 100 上に実装した様子について図 8 ( B ) に示す。光フィルタ 103R、光フィルタ 103G、及び光フィルタ 103B を有する光センサ 701 を、インターポーザ 100 上に配置する。そして図 7 ( A ) で示した配線 109 乃至配線 113 ( 図 8 ( B ) 中の点線 ) により、端子電極 104 乃至端子電極 108 と電気的な接続を取ることができる。

10

#### 【 0 0 6 7 】

図 8 ( B ) に示す構成によると、インターポーザ 100 に実装する際に、光センサ 701 は、異なる光透過性を具備する光フィルタを備えた状態で大面積基板より分断するができるため、分断にかかる工程時間の短縮、及び分断に用いるダイサーなどの加工手段の摩耗を軽減することができる。また複数の光センサを選択してインターポーザ上に実装する際に、選択した光センサの大きさまたは高さのばらつき等の問題をなくすことができるため好適である。

20

#### 【 0 0 6 8 】

また光センサ内の光電流変換回路部を共通化して、センサに演算回路など複雑な構成を含む光電流変換回路部を有する構成の場合、チップ状の光センサに不良が生じる恐れがある。そのため、インターポーザ 100 に実装する前に光センサの不良検査が行えることは有効である。さらに、良品の中でも高品質の光センサを選別しインターポーザに実装することでより高品質のカラーセンサも作製することもできる。

30

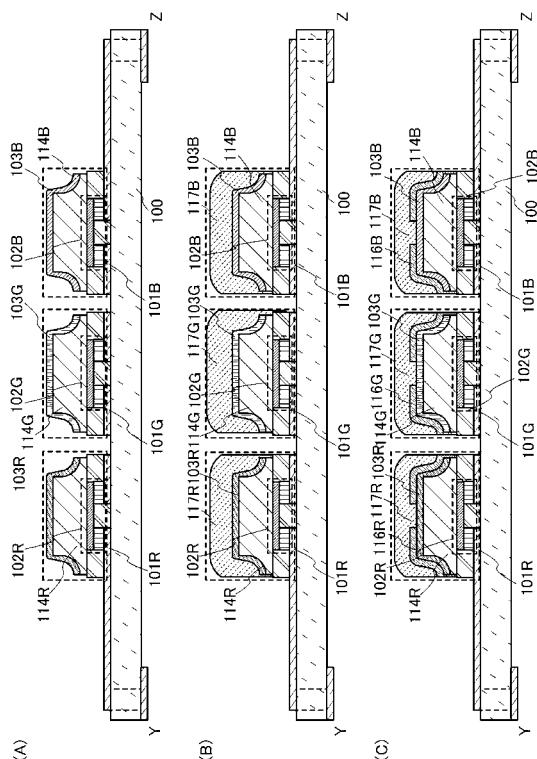

#### 【 0 0 6 9 】

次にカラーセンサの断面図の形態について、図 1 ( B ) で説明した断面図とは異なる形態について、図 10 ( A )、図 10 ( B )、図 10 ( C )、図 11 ( A )、図 11 ( B )、図 11 ( C ) を用いて説明する。

#### 【 0 0 7 0 】

図 10 ( A ) に示すカラーセンサの断面図は、図 1 ( B ) に示した断面図において、光センサ 101R、光センサ 101G、光センサ 101B の光電変換素子が設けられる領域に対応する、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B 上に一部開口部を残して、遮光層 116 で覆って形成する例である。なお遮光層 116 は、スピンドル法などの塗布法によって形成することができ、その他液滴吐出法、印刷法、ディッピング法、ディスペンサ法、刷毛塗り法、スプレー法、フローコート法などによって形成することもできる。

40

#### 【 0 0 7 1 】

遮光層 116 は、光センサ 101R、光センサ 101G、光センサ 101B が有する光電変換素子へ外部からの不適切な光が照射し、誤作動を生じないように光を遮断することができる。よって、遮光層 116 の開口より入射し、光フィルタとして機能する有彩色の光フィルタ 103R、光フィルタ 103G、光フィルタ 103B を透過した光のみを光電変換素子は受光することができるため、カラーセンサの信頼性が向上する。また、光電流変換回路部 102R、光電流変換回路部 102G、光電流変換回路部 102B の半導体素子に光が照射されると特性変動が生じる恐れがあるが、遮光層を設けることでそのような不良を防止することができる。

#### 【 0 0 7 2 】

また、図 10 ( B ) に示すカラーセンサの断面図は、図 10 ( A ) に示した断面図におい

50

て、光センサ101R、光センサ101G、光センサ101Bの光電変換素子が設けられる領域に対応して光フィルタ103R、光フィルタ103G、光フィルタ103Bを形成し、光フィルタ103R、光フィルタ103G、光フィルタ103B上に一部開口部を残して、遮光層116で覆って形成する例である。

【0073】

光フィルタ103R、光フィルタ103G、光フィルタ103Bは、光センサ101R、光センサ101G、光センサ101Bの光電変換素子が設けられる領域に対応して設けられるため、光フィルタの小面積化を図ることができる。そのため、光フィルタ103R、光フィルタ103G、光フィルタ103Bの材料となる透光性樹脂を削減することができ、低コスト化を図ることができる。加えて、光センサ101R、光センサ101G、光センサ101Bが有する光電変換素子へ外部からの不適切な光が照射し、誤作動を生じないように光を遮断することができる。よって、遮光層116の開口より入射し、光フィルタとして機能する有彩色の光フィルタ103R、光フィルタ103G、光フィルタ103Bを透過した光のみを光電変換素子は受光することができるため、カラーセンサの信頼性が向上する。また、光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bの半導体素子に光が照射されると特性変動が生じる恐れがあるが、遮光層を設けることでそのような不良を防止することができる。

【0074】

また、図10(C)に示すカラーセンサの断面図は、図10(A)に示した断面図において、光センサ101R、光センサ101G、光センサ101Bの光電変換素子が設けられる領域に対応して開口部を設けた遮光層116を形成した後に、光フィルタ103R、光フィルタ103G、光フィルタ103Bを形成する例である。

【0075】

光フィルタ103R、光フィルタ103G、光フィルタ103Bは、図10(B)と同様に、光センサ101R、光センサ101G、光センサ101Bの光電変換素子が設けられる領域に対応して設けることができるため、光フィルタの小面積化を図ることができる。そのため、光フィルタ103R、光フィルタ103G、光フィルタ103Bの材料となる透光性樹脂を削減することができ、低コスト化を図ることができる。加えて、光センサ101R、光センサ101G、光センサ101Bが有する光電変換素子へ外部からの不適切な光が照射し、誤作動を生じないように光を遮断することができる。よって、光フィルタとして機能する有彩色の光フィルタ103R、光フィルタ103G、光フィルタ103Bを透過し、遮光層116の開口より入射する光のみを光電変換素子は受光することができるため、カラーセンサの信頼性が向上する。また、光電流変換回路部102R、光電流変換回路部102G、光電流変換回路部102Bの半導体素子に光が照射されると特性変動が生じる恐れがあるが、遮光層を設けることでそのような不良を防止することができる。

【0076】

以上示した図10(A)乃至図10(C)の構成において、光センサ101R、光センサ101G、光センサ101Bの光フィルタが接している透光性基板の側面を、裾広がりの曲面を有する形状としてもよい。

【0077】

図11(A)に示すカラーセンサの断面図は、光センサ101R、光センサ101G、光センサ101Bの光フィルタが接している透光性基板114R、透光性基板114G、透光性基板114Bの側面を、裾広がりの曲面とした例である。

【0078】

図11(A)に示すように、光センサ101R、光センサ101G、光センサ101Bの上部を、光フィルタ103R、光フィルタ103G、光フィルタ103Bが覆って設けられる構成とすることで、光電変換素子へ外部からの不適切な光が照射し、誤作動を生じないように光を遮断することができる。よって、光フィルタとして機能する有彩色の光フィルタ103R、光フィルタ103G、光フィルタ103Bを透過し、遮光層116の開口より入射する光のみを光電変換素子は受光するため、カラーセン

10

20

30

40

50

サの信頼性が向上する。また、光電流変換回路部 102R、光電流変換回路部 102G、光電流変換回路部 102B の半導体素子に光が照射されると特性変動が生じる恐れがあるが、遮光層を設けることでそのような不良を防止することができる。

#### 【0079】

また、図 11 (B) に示すカラーセンサの断面図は、光センサ 101R、光センサ 101G、光センサ 101B の光フィルタが接している透光性基板 114R、透光性基板 114G、透光性基板 114B の側面を、裾広がりの曲面とし、さらに透光性樹脂層 117R、透光性樹脂層 117G、透光性樹脂層 117B で光フィルタを覆った例である。

#### 【0080】

図 11 (B) に示すように、光センサ 101R、光センサ 101G、光センサ 101B の上部を、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B が覆って設ける構成とすることができますため、光電変換素子へ外部からの不適切な光が照射し、誤作動を生じないように光を遮断することができる。よって、光フィルタとして機能する有彩色の光フィルタ 103R、光フィルタ 103G、光フィルタ 103B を透過し、遮光層 116 の開口より入射する光のみを光電変換素子は受光することができるため、カラーセンサの信頼性が向上する。また、光電流変換回路部 102R、光電流変換回路部 102G、光電流変換回路部 102B の半導体素子に光が照射されると特性変動が生じる恐れがあるが、遮光層を設けることでそのような不良を防止することができる。加えて、透光性樹脂層 117R、透光性樹脂層 117G、透光性樹脂層 117B を設けることにより、保護層として機能させることができ、衝撃吸収性も向上させ、有彩色の透光性樹脂層の劣化も防止する効果がある。また、衝撃吸収層として機能する透光性樹脂層の膜厚は、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B より厚くてもよい。そのため、衝撃吸収層として機能する透光性樹脂層の膜厚を厚く形成することができ、衝撃吸収層として耐衝撃性を向上させることができる。

#### 【0081】

また、図 11 (C) に示すカラーセンサの断面図は、光センサ 101R、光センサ 101G、光センサ 101B の光フィルタが接している透光性基板 114R、透光性基板 114G、透光性基板 114B の裾広がりの曲面の側面に、光フィルタを設け、さらに光フィルタ上に光センサ 101R、光センサ 101G、光センサ 101B の光電変換素子が設けられる領域に対応して開口部を設けた遮光層 116R、遮光層 116G、遮光層 116B を形成し、さらに透光性樹脂層 117R、透光性樹脂層 117G、透光性樹脂層 117B で遮光層及び光フィルタを覆った例である。

#### 【0082】

図 11 (C) に示すように、光センサ 101R、光センサ 101G、光センサ 101B の上部を、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B が覆う構成及び光電変換素子が設けられる領域に遮光層を設ける構成とすることができますため、光電変換素子へ外部からの不適切な光が照射し、誤作動を生じないように光を遮断することができる。よって、光フィルタとして機能する有彩色の光フィルタ 103R、光フィルタ 103G、光フィルタ 103B を透過し、遮光層 116 の開口より入射する光のみを光電変換素子は受光することができるため、カラーセンサの信頼性が向上する。また、光電流変換回路部 102R、光電流変換回路部 102G、光電流変換回路部 102B の半導体素子に光が照射されると特性変動が生じる恐れがあるが、遮光層を設けることでそのような不良を防止することができる。加えて、透光性樹脂層 117R、透光性樹脂層 117G、透光性樹脂層 117B を設けることにより、保護層として機能させることができ、衝撃吸収性も向上させ、有彩色の透光性樹脂層の劣化も防止する効果がある。また、衝撃吸収層として機能する透光性樹脂層の膜厚は、光フィルタ 103R、光フィルタ 103G、光フィルタ 103B より厚くてもよい。そのため、衝撃吸収層として機能する透光性樹脂層の膜厚を厚く形成することができ、衝撃吸収層として耐衝撃性を向上させることができる。

#### 【0083】

以上説明したように本実施の形態のカラーセンサは、光センサを複数具備することで增加

10

20

30

40

50

してしまう端子電極数をインターポーヴ上上で削減することができる。具体的には、高電源電位が入力される端子電極、低電源電位が入力される端子電極をインターポーヴ上上で共通化することができる。そのため、端子電極の数を大幅に削減することができる。端子電極数を削減することにより、外部機器との接続不良の減少を図ることができるため、歩留まりの向上を図ることができる。また本実施の形態における構成では、複数の光センサをインターポーヴ上に設けてカラーセンサとする際、ピンコンパチブルを図ることができる。

#### 【0084】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0085】

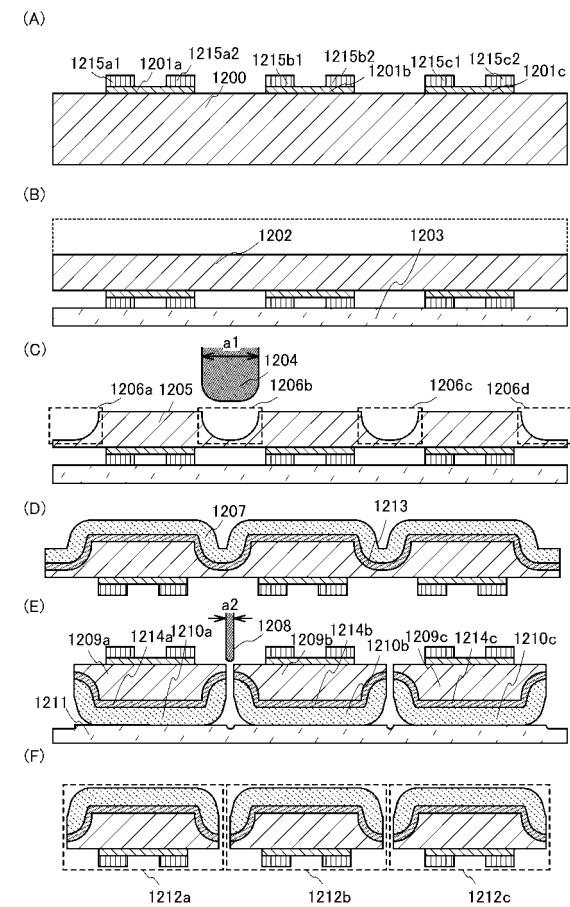

##### (実施の形態2)

本実施の形態では、上記実施の形態1で説明した光センサの作製方法について一例を示し、説明していく。本実施の形態では、一例として、実施の形態1の図11(B)の断面図で説明した光センサについての作製方法について説明するものとする。

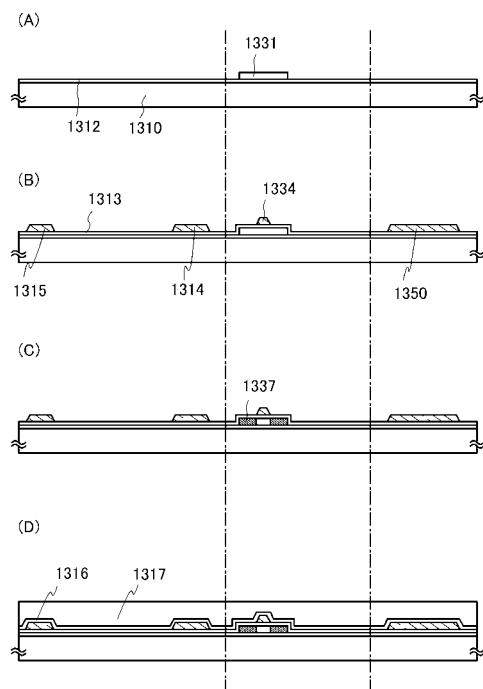

#### 【0086】

図12(A)に透光性基板1200上に設けられた光電変換素子層を有する複数の光電流変換回路部(以下、半導体素子層1201a、1201b、1201cという)を示す。半導体素子層1201a、1201b、1201cはそれぞれ端子電極1215a1、1215a2、1215b1、1215b2、1215c1、1215c2を有している。

#### 【0087】

次に、透光性基板1200の厚さを研削、研磨処理によって薄くする工程を行う。工程時の透光性基板1200を固定する固定テープ1203に半導体素子層1201a、1201b、1201c側を向けて透光性基板1200を固定し、透光性基板1200を加工して、厚さの薄い透光性基板1202とする(図12(B)参照)。透光性基板1200が厚さ0.5mmのガラス基板であるとすれば、透光性基板1202は、0.25~0.3mm程度に薄型化することが好ましい。透光性基板の厚さを薄く加工することで、透光性基板の分断にかかる工程時間の短縮、及び分断に用いるダイサーなど加工手段の摩耗を軽減することができる。研削処理及び研磨処理は好適に組み合わせて用いることができ、本実施の形態では、研削機により研削した後、研磨機により研磨処理で表面を平坦化する。研磨処理として化学的機械研磨を行ってもよい。

#### 【0088】

本実施の形態では、大面積基板である透光性基板を分断することによって、複数の光センサをチップ状で取り出す例について示す。分断工程は、一度に行わず、まず、透光性基板1202に半導体素子層1201a、1201b、1201cを分断するための溝1206a、1206b、1206c、1206dをダイサー1204のダイシングブレードで形成する(図12(C)参照)。透光性基板1205の溝1206a、1206b、1206c、1206dにおいて透光性基板1205は意図的に残存させる。残存させる透光性基板1205の厚さは、30μm~100μm(好ましくは30μm~50μm)程度とすればよい。

#### 【0089】

次に、溝1206a、1206b、1206c、1206dの形成された透光性基板1202上に透光性樹脂層1213及び透光性樹脂層1207の積層を形成する(図12(D)参照)。透光性樹脂層1213、1207の材料は、透光性樹脂層形成後の工程において(例えば、インターポーヴの実装時)加熱処理を用いる場合はその加熱温度に耐えうる樹脂材料を用いる。積層して設けられる透光性樹脂層の一方は、光フィルタとして機能する有彩色の着色層であり、他方は衝撃吸収層として機能する樹脂層とする。本実施の形態では、透光性樹脂層1213を有彩色の着色材料を含む樹脂層で形成する。

#### 【0090】

衝撃吸収層として機能する透光性樹脂層1207を形成すると、光センサ及びカラーセンサに、より耐ストレス性を付与することができる。例えば、本実施の形態で示す透光性樹

10

20

30

40

50

脂層が設けられた光センサは、約 20 N の圧力を加えても破損することなく耐えることができる。

【 0 0 9 1 】

透光性樹脂層としては、ビニル樹脂、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂、シロキサン樹脂等の樹脂材料でなる層を用いることができる。樹脂層の作製方法はスピンコート法などの塗布法を用いることができ、その他液滴吐出法、印刷法、ディッピング法、ディスペンサ法、刷毛塗り法、スプレー法、フローコート法などを用いることもできる。

【 0 0 9 2 】

その後、透光性樹脂層 1213、1207 及び透光性基板 1205 を、溝 1206a、1206b、1206c、1206d で切断して、複数の光センサに分断（分割）する。本実施の形態では、透光性基板 1205 及び透光性樹脂層 1213、1207 を固定テープ 1211 に固定し、透光性基板 1205 側より溝 1206a、1206b、1206c、1206d に残存する透光性基板 1205 及び透光性樹脂層 1213、1207 を、ダイサー 1208 によって切断する。ダイサー 1208 によって、透光性基板 1205 及び透光性樹脂層 1213、1207 は分割され、透光性基板 1209a、1209b、1209c、透光性樹脂層 1214a、1214b、1214c、1210a、1210b、1210c となる（図 12（E）参照。）。本実施の形態では、固定テープ 1203、1211 として、ダイシングテープを用いる。

【 0 0 9 3 】

溝の形成された透光性基板 1205 及び透光性樹脂層 1213、1207 を切断する際は、透光性基板 1205 側でも透光性樹脂層 1213、1207 側からでも切断することができる。透光性基板 1205 にアライメント合わせのマーカーを形成する場合は、透光性基板 1205 側よりダイサー等の切断手段を用いて切断すると、切断箇所の正確性を高くすることができる。

【 0 0 9 4 】

以上の工程で、光センサ 1212a、1212b、1212c を形成することができる（図 12（F）参照。）。透光性樹脂層 1207 及び透光性基板 1202 を切断する切断面の幅を、溝の幅より狭くすることによって、透光性基板側面に、溝に形成された樹脂層を残存させることができる。本実施の形態では、ダイサー 1204 及びダイサー 1208 の幅とは処理領域（ダイサーによって加工される領域）を決定するダイシングブレードの厚さとなる。

【 0 0 9 5 】

切断面の幅 a1 はダイサー 1204 のダイシングブレードの幅 a1 に、溝の幅は、ダイサー 1208 のダイシングブレードの幅 a2 によって制御できるため、ダイサー 1204 のダイシングブレードの幅 a1 よりダイサー 1208 のダイシングブレードの幅 a2 を狭くすればよい。例えば、本実施の形態では、ダイサー 1204 のダイシングブレードの幅 a1 を 0.16 mm、ダイサー 1208 のダイシングブレードの幅 a2 を 0.1 mm とする。

【 0 0 9 6 】

従って、光センサ 1212a、1212b、1212c において、半導体素子層 1201a、1201b、1201c の設けられていない面及び側面の一部は樹脂層 1210a、1210b、1210c で覆われる構造となる。

【 0 0 9 7 】

透光性基板に形成される溝の形状は加工手段に依存する。本実施の形態ではダイサー 1204 のやや丸みを帯びたダイシングブレードの形状が反映され、溝 1206a、1206b、1206c、1206d も図 11（B）の断面において丸み（曲率を有する）を帯びた形状となっている。ダイシングブレードの形状を矩形とすれば、溝の形状も矩形となり、分断後の光センサの透光性基板の端部も矩形を有する形状とすることができる。

【 0 0 9 8 】

10

20

30

40

50

また、基板端部での被覆性を向上させるために、透光性樹脂層を厚くすると好ましい。透光性樹脂層の構造や膜厚、また切断箇所によっても完成する光センサの形状を自由に変化させる（異なる）ことができる。

【0099】

ダイシングブレードの幅の細いダイサーを用いて分断すると、透光性基板の溝の領域を完成した光センサに多く残すこともできる。衝撃吸収材として機能する透光性樹脂層を積層すると、光センサに、より耐ストレス性を付与することができる。

【0100】

また、本実施の形態では、溝を形成し、溝上に透光性樹脂層を形成するので、溝底面に厚く透光性樹脂層を形成することができる。さらに透光性樹脂層を形成後、透光性樹脂層と透光性基板を積層して切断するため、側面において透光性樹脂層の端部と透光性基板の端部とが一致する。側面において透光性基板の上側の端部が露出しないために、透光性基板の端部の破損や欠けを防止することができる。また、透光性樹脂層を積層により厚く形成すると、光センサの側面において透光性基板の端部と透光性樹脂層の端部との距離を長くすることができるため、より透光性基板端部に与えるダメージを軽減することができる。

10

【0101】

図12のように各基板に形成され、分断されて作製された複数の光センサをインターポーラ上に実装し、カラーセンサを作製することができる。

【0102】

光センサにおいて薄く成形された透光性基板は透光性樹脂層で覆われているため工程上取り扱い易く、破損などの不良が生じにくい。よって、より薄型の高性能なカラーセンサを歩留まり良く作製することができる。

20

【0103】

インターポーラに実装される複数の光センサは、自由に選択することができるため、それぞれ含む有彩色の透光性樹脂の色が異なる光センサをインターポーラに実装し、カラーセンサを作製することができる。

【0104】

また、インターポーラに実装する際に、光センサに検査工程を行い、良品のみを選別してインターポーラに実装することができるため、作製工程においてカラーセンサの歩留まりが向上する。特に、光センサに增幅回路など複雑な構成を含む半導体素子層を有する構成の場合、チップ状の光センサに不良が生じる恐れがあるため、インターポーラに実装する前に光センサの不良検査が行えることは有益である。

30

【0105】

さらに、本実施の形態の光センサは、透光性基板の半導体素子層の形成面と反対側の一面及び端部（側面）の一部とを少なくとも有彩色の透光性樹脂層で覆う構成である。従って透光性樹脂層が、作製工程、または検査工程において加わる圧力等の外部ストレスからの衝撃吸収層としても機能するため、光センサのキズ、クラックなどの不良を低減し、信頼性の高いカラーセンサを作製することができる。

【0106】

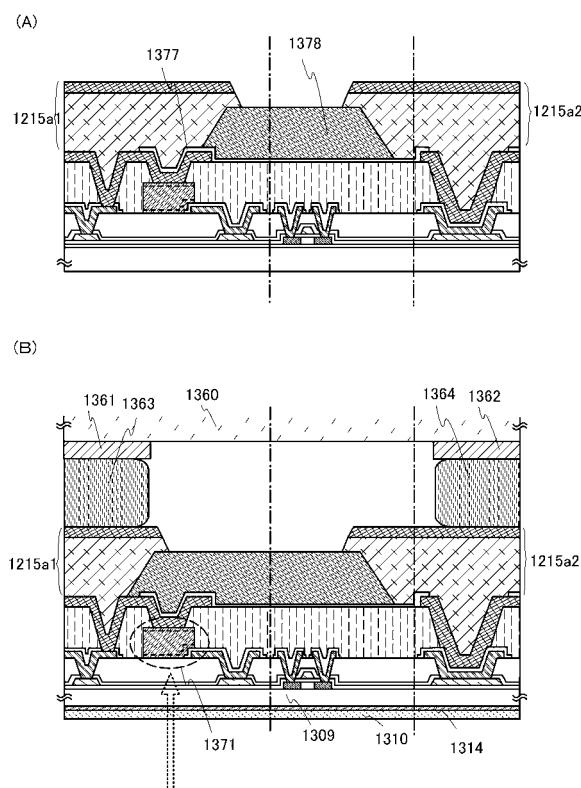

分断される半導体素子層として、基板上に光電変換素子及び電界効果トランジスタを形成する方法を、図13（A）乃至図13（D）、図14（A）乃至図14（C）、図15（A）、図15（B）の、断面図を用いて説明する。

40

【0107】

なお透光性基板1310として、ガラス基板の一つであるAN100を用いる。基板上に形成する電界効果トランジスタとしては、薄膜トランジスタを用いることにより、基板上に、光電変換素子と薄膜トランジスタを同一工程で作製することができるため、光センサの量産化がし易いといった利点がある。なお、本実施の形態で示す光センサは、光フィルタ（以下、カラーフィルタという）として機能する透光性樹脂層及び透光性基板を通過して光電変換素子に光を照射されるものである。

【0108】

50

プラズマCVD法で下地絶縁膜1312となる窒素を含む酸化珪素膜(膜厚100nm)を形成し、さらに大気にふれることなく、半導体膜例えは水素を含む非晶質珪素膜(膜厚54nm)を積層形成する。また、下地絶縁膜1312は酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜を用いた積層してもよい。例えは、下地絶縁膜1312として、酸素を含む窒化珪素膜を50nm、さらに窒素を含む酸化珪素膜を100nm積層した膜を形成してもよい。なお、窒素を含む酸化珪素膜や窒化珪素膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するブロッキング層として機能する。

#### 【0109】

半導体素子が有する半導体層を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製される非晶質(アモルファス、以下「AS」ともいう。)半導体、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた多結晶半導体、或いは微結晶(セミアモルファス若しくはマイクロクリスタルとも呼ばれる。以下「SAS」ともいう。)半導体などを用いることができる。半導体層はスパッタ法、LPCVD法、またはプラズマCVD法等により成膜することができる。

10

#### 【0110】

微結晶半導体膜は、ギブスの自由エネルギーを考慮すれば非晶質と単結晶の中間的な準安定状態に属するものである。すなわち、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する。柱状または針状結晶が基板表面に対して法線方向に成長している。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520cm<sup>-1</sup>よりも低周波数側に、シフトしている。即ち、単結晶シリコンを示す520cm<sup>-1</sup>とアモルファスシリコンを示す480cm<sup>-1</sup>の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手(ダンギングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。

20

#### 【0111】

この微結晶半導体膜は、周波数が数十MHz～数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などの水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。

30

#### 【0112】

アモルファス半導体としては、代表的には水素化アモルファスシリコン、結晶性半導体としては代表的にはポリシリコンなどがあげられる。ポリシリコン(多結晶シリコン)には、800以上の中間温度を経て形成されるポリシリコンを主材料として用いた所謂高温ポリシリコンや、600以下の低温ポリシリコン、また結晶化を促進する元素などを用いて、非晶質シリコンを結晶化させたポリシリコンなどを含んでいる。もちろん、前述したように、微結晶半導体又は半導体層の一部に結晶相を含む半導体を用いることもできる。

40

#### 【0113】

また、半導体の材料としてはシリコン(Si)、ゲルマニウム(Ge)などの単体のほかGaAs、InP、SiC、ZnSe、GaN、SiGeなどのような化合物半導体も用いることができる。また酸化物半導体である酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)なども用いることができ、ZnOを半導体層に用いる場合、ゲート絶縁層をY<sub>2</sub>O<sub>3</sub>、Al<sub>2</sub>O<sub>3</sub>、TiO<sub>2</sub>、それらの積層などを用いるとよく、ゲート電極層、ソース電極層、

50

ドレイン電極層としては、ITO、Au、Tiなどを用いるとよい。また、ZnOにInやGaなどを添加することもできる。

【0114】

半導体層に、結晶性半導体膜を用いる場合、その結晶性半導体膜の作製方法は、種々の方法（レーザ結晶化法、熱結晶化法、またはニッケルなどの結晶化を助長する元素を用いた熱結晶化法等）を用いれば良い。また、SASである微結晶半導体をレーザ照射して結晶化し、結晶性を高めることもできる。結晶化を助長する元素を導入しない場合は、非晶質珪素膜にレーザ光を照射する前に、窒素雰囲気下500で1時間加熱することによって非晶質珪素膜の含有水素濃度を $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下にまで放出させる。これは水素を多く含んだ非晶質珪素膜にレーザ光を照射すると非晶質珪素膜が破壊されてしまうからである。

10

【0115】

非晶質半導体膜への金属元素の導入の仕方としては、当該金属元素を非晶質半導体膜の表面又はその内部に存在させ得る手法であれば特に限定はなく、例えばスパッタ法、CVD法、プラズマ処理法（プラズマCVD法も含む）、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。また、このとき非晶質半導体膜の表面の濡れ性を改善し、非晶質半導体膜の表面全体に水溶液を行き渡らせるため、酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を成膜することが望ましい。

20

【0116】

また、非晶質半導体膜を結晶化し、結晶性半導体膜を形成する結晶化工程で、非晶質半導体膜に結晶化を促進する元素（触媒元素、金属元素とも示す）を添加し、熱処理（550～750で3分～24時間）により結晶化を行ってもよい。結晶化を助長（促進）する元素としては、鉄（Fe）、ニッケル（Ni）、コバルト（Co）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）、銅（Cu）及び金（Au）から選ばれた一種又は複数種類を用いることができる。

【0117】

結晶化を助長する元素を結晶性半導体膜から除去、又は軽減するため、結晶性半導体膜に接して、不純物元素を含む半導体膜を形成し、ゲッタリングシンクとして機能させる。不純物元素としては、n型を付与する不純物元素、p型を付与する不純物元素や希ガス元素などを用いることができ、例えばリン（P）、窒素（N）、ヒ素（As）、アンチモン（Sb）、ビスマス（Bi）、ボロン（B）、ヘリウム（He）、ネオン（Ne）、アルゴン（Ar）、Kr（クリプトン）、Xe（キセノン）から選ばれた一種または複数種を用いることができる。結晶化を促進する元素を含む結晶性半導体膜に、希ガス元素を含む半導体膜を形成し、熱処理（550～750で3分～24時間）を行う。結晶性半導体膜中に含まれる結晶化を促進する元素は、希ガス元素を含む半導体膜中に移動し、結晶性半導体膜中の結晶化を促進する元素は除去、又は軽減される。その後、ゲッタリングシンクとなった希ガス元素を含む半導体膜を除去する。

30

【0118】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、熱処理やレーザ光照射を単独で、複数回行っても良い。

【0119】

また、結晶性半導体膜を、直接基板にプラズマ法により形成しても良い。また、プラズマ法を用いて、結晶性半導体膜を選択的に基板に形成してもよい。

【0120】

本実施の形態では、半導体膜として触媒元素を用いた結晶化方法を用いて多結晶珪素膜を形成する。重量換算で10ppmのニッケルを含む酢酸ニッケル溶液をスピナーで添加する。なお、溶液を添加する方法に代えてスパッタ法でニッケル元素を全面に散布する方法

40

50

を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜（ここでは多結晶珪素膜）を形成する。ここでは熱処理（500、1時間）の後、結晶化のための熱処理（550、4時間）を行って多結晶珪素膜を得る。

【0121】

次いで、多結晶珪素膜表面の酸化膜を希フッ酸等で除去する。その後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザ光（XeCl：波長308nm）の照射を大気中、または酸素雰囲気中で行う。

【0122】

レーザ光には波長400nm以下のエキシマレーザ光や、YAGレーザの第2高調波又は第3高調波を用いる。ここでは、繰り返し周波数10～1000Hz程度のパルスレーザ光を用い、当該レーザ光を光学系にて100～500mJ/cm<sup>2</sup>に集光し、90～95%のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。本実施の形態では、繰り返し周波数30Hz、エネルギー密度470mJ/cm<sup>2</sup>でレーザ光の照射を大気中で行なう。

10

【0123】

なお、大気中、または酸素雰囲気中で行うため、レーザ光の照射により表面に酸化膜が形成される。なお、本実施の形態ではパルスレーザを用いた例を示したが、連続発振のレーザを用いてもよく、半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザを用い、基本波の第2高調波～第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザ（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を適用すればよい。

20

【0124】

連続発振のレーザを用いる場合には、出力10Wの連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または機能形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01～100MW/cm<sup>2</sup>程度（好ましくは0.1～10MW/cm<sup>2</sup>）が必要である。そして、10～2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すればよい。

30

【0125】

次いで、上記レーザ光の照射により形成された酸化膜に加え、オゾン水で表面を120秒処理して合計1～5nmの酸化膜からなるバリア層を形成する。このバリア層は、結晶化させるために添加した触媒元素、例えばニッケル（Ni）を膜中から除去するために形成する。ここではオゾン水を用いてバリア層を形成したが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD法やスパッタ法や蒸着法などで1～10nm程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザ光の照射により形成された酸化膜を除去してもよい。

【0126】

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなるアルゴン元素を含む非晶質珪素膜を10nm～400nm、ここでは膜厚100nmで成膜する。ここでは、アルゴン元素を含む非晶質珪素膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴン元素を含む非晶質珪素膜を形成する場合、成膜条件は、モノシリコンとアルゴンの流量比（SiH<sub>4</sub>:Ar）を1:99とし、成膜圧力を6.665Paとし、RFパワー密度を0.087W/cm<sup>2</sup>とし、成膜温度を350とする。

40

【0127】

その後、650に加熱された炉に入れて3分の熱処理を行い、触媒元素を除去（ゲッタリング）する。これにより結晶構造を有する半導体膜中の触媒元素濃度が低減される。炉に代えてランプアニール装置を用いてもよい。

50

## 【0128】

次いで、バリア層をエッチングストップとして、ゲッタリングサイトであるアルゴン元素を含む非晶質珪素膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

## 【0129】

なお、触媒元素を用いて半導体膜の結晶化を行わない場合には、上述したバリア層の形成、ゲッタリングサイトの形成、ゲッタリングのための熱処理、ゲッタリングサイトの除去、バリア層の除去などの工程は不要である。

## 【0130】

次いで、得られた結晶構造を有する半導体膜（例えば結晶性珪素膜）の表面にオゾン水で薄い酸化膜を形成した後、第1のフォトマスクを用いてレジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層1331を形成する（図13（A）参照。）。半導体層1331を形成した後、レジストからなるマスクを除去する。

## 【0131】

次いで、必要があればトランジスタのしきい値電圧を制御するために微量な不純物元素（ホウ素またはリン）のドーピングを行う。ここでは、ジボラン（ $B_2H_6$ ）を質量分離しないでプラズマ励起したイオンドープ法を用いる。

## 【0132】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時に半導体層1331の表面を洗浄した後、ゲート絶縁膜1313となる絶縁膜を形成する。

## 【0133】

ゲート絶縁膜1313は酸化珪素、若しくは酸化珪素と窒化珪素の積層構造で形成すればよい。ゲート絶縁膜1313は、プラズマCVD法や減圧CVD法により絶縁膜を堆積することで形成しても良いし、プラズマ処理による固相酸化若しくは固相窒化で形成すると良い。半導体層を、プラズマ処理により酸化又は窒化することにより形成するゲート絶縁膜は、緻密で絶縁耐圧が高く信頼性に優れているためである。例えば、亜酸化窒素（ $N_2O$ ）をArで1～3倍（流量比）に希釈して、10～30Paの圧力にて3～5kWのマイクロ波（2.45GHz）電力を印加して半導体層の表面を酸化若しくは窒化させる。この処理により1nm～10nm（好ましくは2nm～6nm）の絶縁膜を形成する。さらに亜酸化窒素（ $N_2O$ ）とシラン（ $SiH_4$ ）を導入し、10～30Paの圧力にて3～5kWのマイクロ波（2.45GHz）電力を印加して気相成長法により酸化窒化シリコン膜を形成してゲート絶縁膜を形成する。固相反応と気相成長法による反応を組み合わせることにより界面準位密度が低く絶縁耐圧の優れたゲート絶縁膜を形成することができる。

## 【0134】

また、ゲート絶縁膜1313として、二酸化ジルコニウム、酸化ハフニウム、二酸化チタン、五酸化タンタルなどの高誘電率材料を用いても良い。ゲート絶縁膜1313に高誘電率材料を用いることにより、ゲートリーク電流を低減することができる。

## 【0135】

本実施の形態では、ゲート絶縁膜1313としてプラズマCVD法により115nmの厚さで窒素を含む酸化珪素膜を形成する。

## 【0136】

次いで、ゲート絶縁膜1313上に金属膜を形成した後、第2のフォトマスクを用いて、ゲート電極1334、配線1314及び1315、端子電極1350を形成する（図13（B）参照）。この金属膜として、例えば窒化タンタル及びタンゲステン（W）をそれぞれ30nm、370nm積層した膜を用いる。

## 【0137】

また、ゲート電極1334、配線1314及び1315、端子電極1350として、上記

10

20

30

40

50

以外にもチタン (Ti)、タングステン (W)、タンタル (Ta)、モリブデン (Mo)、ネオジム (Nd)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、白金 (Pt)、アルミニウム (Al)、金 (Au)、銀 (Ag)、銅 (Cu) から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タングステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。

#### 【0138】

また、ゲート電極 1334、配線 1314 及び 1315、端子電極 1350 に可視光に対して透光性を有する透光性の材料を用いることもできる。透光性の導電材料としては、インジウム錫酸化物 (ITO)、酸化珪素を含むインジウム錫酸化物 (ITSO)、有機インジウム、有機スズ、酸化亜鉛等を用いることができる。また、酸化亜鉛 (ZnO) を含むインジウム亜鉛酸化物 (IZO (Indium Zinc Oxide))、酸化亜鉛 (ZnO)、ZnO にガリウム (Ga) をドープしたものの、酸化スズ (SnO<sub>2</sub>)、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いてもよい。

#### 【0139】

次いで、半導体層 1331 への一導電型を付与する不純物の導入を行って、トランジスタ 1373 のソース領域またはドレイン領域 1337 の形成を行う (図 13 (C) 参照)。本実施の形態では n チャネル型トランジスタを形成するので、n 型を付与する不純物、例えばリン (P)、砒素 (As) など半導体層 1331 に導入する。p チャネル型トランジスタを形成する場合は、p 型を付与する不純物、例えばボロン (B) を半導体層 1331 に導入すればよい。

#### 【0140】

次いで、CVD 法により酸化珪素膜を含む第 1 の層間絶縁膜 (図示しない) を 50 nm 形成した後、それぞれの島状半導体領域に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法 (RTA 法)、或いは YAG レーザまたはエキシマレーザを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方法のうち、いずれかと組み合わせた方法によって行う。

#### 【0141】

次いで、水素及び酸素を含む窒化珪素膜を含む第 2 の層間絶縁膜 1316 を、例えば 10 nm の膜厚で形成する。

#### 【0142】

次いで、第 2 の層間絶縁膜 1316 上に絶縁性材料から成る第 3 の層間絶縁膜 1317 を形成する (図 13 (D) 参照)。第 3 の層間絶縁膜 1317 は CVD 法で得られる絶縁膜を用いることができる。本実施の形態においては密着性を向上させるため、第 3 の層間絶縁膜 1317 として、900 nm の膜厚で形成した窒素を含む酸化珪素膜を形成する。

#### 【0143】

次に、熱処理 (300 ~ 550 °C で 1 ~ 12 時間の熱処理、例えば窒素雰囲気中 410 °C で 1 時間) を行い、半導体層を水素化する。この工程は第 2 の層間絶縁膜 1316 に含まれる水素により半導体層のダングリングボンドを終端させるために行うものである。ゲート絶縁膜 1313 の存在に関係なく半導体層を水素化することができる。

#### 【0144】

また第 3 の層間絶縁膜 1317 として、シロキサンを用いた絶縁膜、及びそれらの積層構造を用いることも可能である。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造で構成される。置換基として、少なくとも水素を含む化合物 (例えばアルキル基、アリール基) が用いられる。置換基として、フッ素を用いてもよい。または置換基として、少なくとも水素を含む化合物と、フッ素とを用いてもよい。

#### 【0145】

10

20

30

40

50

第3の層間絶縁膜1317としてシロキサンを用いた絶縁膜、及びそれらの積層構造を用いた場合は、第2の層間絶縁膜1316を形成後、半導体層を水素化するための熱処理を行い、次に第3の層間絶縁膜1317を形成することもできる。

【0146】

次いで、第3のフォトマスクを用いてレジストからなるマスクを形成し、第1の層間絶縁膜、第2の層間絶縁膜1316及び第3の層間絶縁膜1317またはゲート絶縁膜1313を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。

【0147】

なお、第3の層間絶縁膜1317は必要に応じて形成すればよく、第3の層間絶縁膜1317を形成しない場合は、第2の層間絶縁膜1316を形成後に第1の層間絶縁膜、第2の層間絶縁膜1316及びゲート絶縁膜1313を選択的にエッチングしてコンタクトホールを形成する。

【0148】

次いで、スパッタ法で金属積層膜を成膜した後、第4のフォトマスクを用いてレジストからなるマスクを形成し、選択的に金属膜をエッチングして、配線1319、接続電極1320、端子電極1351、トランジスタ1373のソース電極またはドレイン電極1341を形成する。そして、レジストからなるマスクを除去する。なお、本実施の形態の金属膜は、膜厚100nmのTi膜と、膜厚350nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層を積層したものとする。

【0149】

また配線1319、接続電極1320、端子電極1351、及びトランジスタ1373のソース電極又はドレイン電極1341を単層の導電膜により形成する場合は、耐熱性及び導電率等の点からチタン膜(Ti膜)が好ましい。またチタン膜に変えて、タンゲステン(W)、タンタル(Ta)、モリブデン(Mo)、ネオジム(Nd)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Pl)から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。配線1319、接続電極1320、端子電極1351、及びトランジスタ1373のソース電極又はドレイン電極1341を単層膜にすることにより、作製工程において成膜回数を減少させることが可能となる。

【0150】

以上の工程で、多結晶硅素膜を半導体層として用いたトップゲート型のトランジスタ1373を作製することができる。

【0151】

本実施の形態では、半導体素子層に含まれる半導体素子として、nチャネル型トランジスタを例として示したが、pチャネル型トランジスタを用いてもよい。様々な形態の電界効果トランジスタを用いることができ、用いるトランジスタの種類に限定はない。

【0152】

本実施の形態では、シングルゲート構造のトランジスタを説明したが、ダブルゲート構造などのマルチゲート構造でもよい。この場合、半導体層の上方、下方にゲート電極層を設ける構造でも良く、半導体層の片側(上方又は下方)にのみ複数ゲート電極層を設ける構造でもよい。

【0153】

インクジェットや印刷法を用いて形成したトランジスタなどを用いることができる。これらにより、室温で製造、低真空度で製造、又は大型基板上に製造することができる。また、マスク(レチクル)を用いなくても製造することができるため、トランジスタのレイアウトを容易に変更することができる。さらに、レジストを用いる必要がないので、材料費が安くなり、工程数を削減できる。さらに、必要な部分にのみ膜を付けるため、全面

10

20

30

40

50

に成膜した後でエッティングする、という製法よりも、材料が無駄にならず、低コストにできる。

【0154】

または、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することができる。そのため、衝撃に強くできる。

【0155】

または、半導体層として、単結晶半導体層を用いた透光性のSOI構造を有する基板などを用いてトランジスタを形成してもよい。これらにより、特性やサイズや形状などのバラツキが少なく、電流供給能力が高く、サイズの小さいトランジスタを製造することができる。これらのトランジスタを用いると、回路の低消費電力化、又は回路の高集積化を図ることができる。

10

【0156】

本実施の形態の光センサは、薄膜トランジスタを用いて電界効果トランジスタを構成することにより、ガラス基板等の透光性基板上に形成することができる。そのため、光電変換素子を基板上面に形成しても、基板の裏面から透光性基板を透過した光を光電変換素子で受光することができる。

【0157】

次いで、後に形成される光電変換層（代表的にはアモルファスシリコン）と反応して合金になりにくい導電性の金属膜（チタン（Ti）またはモリブデン（Mo）など）を成膜した後、第5のフォトマスクを用いてレジストからなるマスクを形成し、選択的に導電性の金属膜をエッティングして配線1319を覆う保護電極1318、保護電極1345、保護電極1346、及び保護電極1348を形成する（図14（A））。ここではスパッタ法で得られる膜厚200nmのTi膜を用いる。なお、同様に接続電極1320、端子電極1351、トランジスタ1373のソース電極またはドレイン電極1341も導電性の金属膜で覆われる。従って、導電性の金属膜は、これらの電極における2層目のAl膜が露呈されている側面も覆い、導電性の金属膜は光電変換層へのアルミニウム原子の拡散も防止できる。

20

【0158】

ただし、配線1319、接続電極1320、端子電極1351、及びトランジスタ1373のソース電極またはドレイン電極1341を、単層の導電膜で形成する場合、保護電極1318、保護電極1345、保護電極1346、及び保護電極1348は形成しなくてよい。

30

【0159】

次に第3の層間絶縁膜1317上に、p型半導体層1371p、i型半導体層1371i及びn型半導体層1371nを含む光電変換層1371を形成する。

【0160】

p型半導体層1371pは、周期表第13属の不純物元素、例えばホウ素（B）を含んだセミアモルファス（微結晶、マイクロクリスタルともいう）シリコン膜をプラズマCVD法にて成膜して形成すればよい。

40

【0161】

微結晶シリコン膜を形成する方法の一例は、シランガスと水素及び/又は希ガスを混合してグロー放電プラズマにより成膜する方法が挙げられる。シランは水素及び/又は希ガスで10倍から2000倍に希釈される。そのため多量の水素及び/又は希ガスが必要とされる。基板の加熱温度は100～300、好ましくは120～220で行う。微結晶シリコン膜の成長表面を水素で不活性化し、微結晶シリコンの成長を促進するためには120～220で成膜を行うことが好ましい。成膜処理中、活性種であるSiHラジカル、SiH<sub>2</sub>ラジカル、SiH<sub>3</sub>ラジカルは結晶核を基に結晶成長する。また、シラン等のガス中にGeH<sub>4</sub>、GeF<sub>4</sub>などの水素化ゲルマニウム、フッ化ゲルマニウムを混合する、あるいはシリコンに炭素又はゲルマニウムを加え、エネルギー bandwidth幅を調節し

50

ても良い。シリコンに炭素を加えた場合、エネルギー bandwidth 幅は広がり、またシリコンにゲルマニウムを加えた場合、エネルギー bandwidth 幅は狭まる。

【0162】

また配線 1319 及び保護電極 1318 は光電変換層 1371 の最下層、本実施の形態では p 型半導体層 1371p と接している。

【0163】

p 型半導体層 1371p を形成したら、さらに i 型半導体層 1371i 及び n 型半導体層 1371n を順に形成する。これにより p 型半導体層 1371p 、 i 型半導体層 1371i 及び n 型半導体層 1371n を有する光電変換層 1371 が形成される。

【0164】

i 型半導体層 1371i としては、例えばプラズマ CVD 法で微結晶シリコン膜を形成すればよい。また n 型半導体層 1371n としては、周期表第 15 属の不純物元素、例えばリン (P) を含む微結晶シリコン膜を形成してもよいし、微結晶シリコン膜を形成後、周期表第 15 属の不純物元素を導入してもよい。

10

【0165】

また p 型半導体層 1371p 、 i 型半導体層 1371i 、 n 型半導体層 1371n として、微結晶半導体膜だけではなく、アモルファス半導体膜を用いてもよい。また前記の触媒やレーザ結晶化処理により形成される多結晶半導体膜を用いてもよい。

【0166】

さらには、微結晶シリコン、スマートカット法により形成される単結晶シリコンにて形成される光電変換層は基板面内の特性のばらつきを低減することができる。

20

【0167】

次いで、全面に絶縁性材料（例えば珪素を含む無機絶縁膜）からなる封止層 1324 を厚さ 1 μm ~ 30 μm で形成して図 14 (B) の状態を得る。ここでは絶縁性材料膜として CVD 法により、膜厚 1 μm の窒素を含む酸化珪素膜を形成する。CVD 法による絶縁膜を用いることによって密着性の向上を図っている。

【0168】

次いで、封止層 1324 をエッティングして開口部を設けた後、スパッタ法により配線 1374 及び 1375 を形成する。配線 1374 及び 1375 は、チタン膜 (Ti 膜) (200 nm) はスパッタ法により成膜する。

30

【0169】

次いで露出している面を覆って、保護膜 1377 を形成する（図 15 (A) 参照。）。保護膜 1377 として、本実施の形態では窒化珪素膜を用いる。この保護膜 1377 により、光電変換層 1371 やトランジスタ 1373 に、水分や有機物等の不純物が混入するのを防ぐことができる。

【0170】

次いで保護膜 1377 上に、封止膜 1378 を形成する。封止膜 1378 も外部ストレスから半導体素子層を保護する機能を有する。本実施の形態では、封止膜 1378 として、感光性のエポキシ - フェノール系樹脂を用い 20 μm の厚さで形成する。封止膜 1378 としては、エポキシ - フェノール系樹脂であるオームコートを用いる。

40

【0171】

次いで上層の端子電極が下層の配線 1374 、もしくは配線 1375 と電気的に接続される領域の保護膜をエッティングしてコンタクトホールを形成する。

【0172】

次いで、封止膜 1378 上に、例えばニッケル (Ni) ペーストを用い、さらにスパッタ法にてチタン膜 (Ti 膜) (150 nm) と、ニッケル膜 (Ni 膜) (750 nm) と、金膜 (Au 膜) (50 nm) との積層膜を形成する。こうして得られる端子電極 1215a1 及び端子電極 1215a2 の固着強度は 5 N を超え、端子電極として十分な固着強度を有している。

【0173】

50

以上の工程で、はんだ接続が可能な端子電極 1215a1 及び端子電極 1215a2 が形成され、図 15 (B) に示す構造が得られる。

【0174】

実際には、図 15 (B) の時点で形成された、光電変換素子及びトランジスタ等を含む 1 つの半導体素子層は、大面積基板上にそれぞれ素子材料を形成されることで大量生産が可能である。1枚の大面積基板（例えば 600 cm × 720 cm）からは大量の半導体素子層を含む光センサ（例えば 2 mm × 1.5 mm）を製造することができる。

【0175】

半導体素子層が形成された透光性基板 1309 は、さらに端子電極 1215a1、1215a2 の部分にて、はんだ 1363 及び 1364 でインターポーヴ 1360 へと実装される例である（図 15 (B) 参照。）。なおインターポーヴ 1360 上の電極 1361 は、はんだ 1363 で端子電極 1215a1 に実装されている。またインターポーヴ 1360 の電極 1362 は、はんだ 1364 にて端子電極 1215a2 に実装される。

10

【0176】

図 15 (B) に示す光電変換素子において、光電変換層 1371 に入射する光は、透光性基板 1309 及び透光性樹脂層 1210、1214 を用いることにより、透光性基板 1309 及び透光性樹脂層 1210、透光性樹脂層 1214 側から入ることができる。

【0177】

本実施の形態において、光センサは、光電変換素子へ照射する光の入射領域に開口、又は透光性材料を用いて形成する透光性領域を有する筐体に設けられてもよい。本実施の形態では、有彩色の透光性樹脂層を透過した光を光電変換素子に検知させるので、有彩色の透光性樹脂層の被形成領域を筐体で覆うことで、外部より透光性樹脂層の被形成領域を透過して光電変換素子へ入射する光を遮断することができる。よって、センサとして光センサの精度を高め、誤差を軽減することができる。

20

【0178】

以上の様な作製方法にて、光センサを作製すれば、単価を安く、かつ歩留まりを向上させることができる。

【0179】

透光性基板を分断する前に、透光性基板の厚さを小さくし、分断工程を 2 段階で行うことで、透光性基板を分断加工する際の切削工具の消耗を低減することができる。透光性基板の大型化、分断する光センサの小型化に伴い、切削工具の処理領域は増加するのでさらに切削工具の消耗は大きくなる。よって、切削工具の消耗を低減することができる本実施の形態の構成は、大面積基板、より小型な光センサにおいて、特に有益である。これにより光センサ及びカラーセンサをより安価に製造することができる。透光性基板の厚さが薄いため、光センサ及びカラーセンサのサイズを薄型化することができる。

30

【0180】

よって、薄型であっても取り扱いやすく、信頼性の高いカラーセンサを提供することができる。本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。そのため、カラーセンサは、光センサを複数具備することで増加してしまう端子数をインターポーヴ 上で削減することができる。具体的には、高電源電位が入力される端子、低電源電位が入力される端子をインターポーヴ 上で共通化することができる。そのため、端子電極の数を大幅に削減することができる。端子数を削減することにより、外部機器との接続不良の減少を図ることができるために、歩留まりの向上を図ることができる。また本実施の形態における構成では、複数の光センサをインターポーヴ 上に設けてカラーセンサとする際、ピンコンパチブルを図ることができる。

40

【0181】

(実施の形態 3)

上記実施の形態のカラーセンサにおいて、光センサが有する半導体素子層に含まれる半導体素子として様々な形態の電界効果トランジスタを用いることができる。本実施の形態で

50

は、光センサに適用することができる半導体素子として、単結晶半導体層を有する電界効果トランジスタについて詳細に説明する。

【0182】

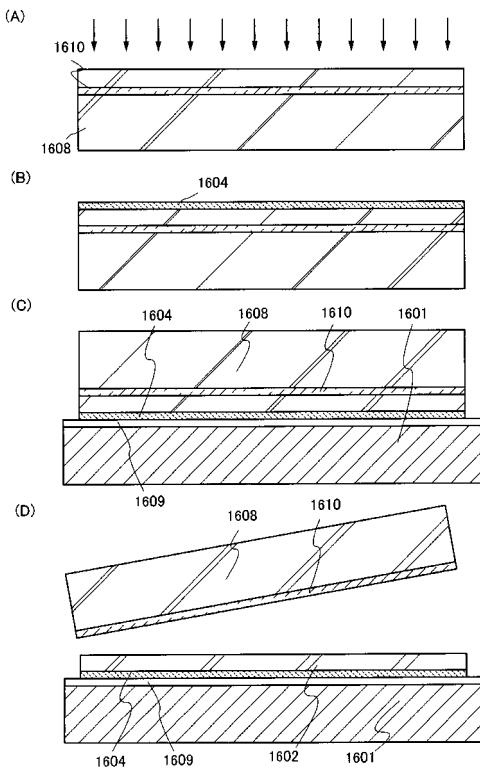

以下、透光性基板上に、単結晶半導体基板より単結晶半導体層を設け、半導体素子層に含まれる半導体素子を形成する方法を図16及び図17を用いて説明する。

【0183】

図16(A)に示す単結晶半導体基板1608は清浄化されており、その表面から電界で加速されたイオンを所定の深さに照射し、脆弱化層1610を形成する。イオンの照射は透光性基板に転置する単結晶半導体層の厚さを考慮して行われる。イオンを照射する際の加速電圧はこのような厚さを考慮して、単結晶半導体基板1608に照射されるようにする。本実施の形態では、単結晶半導体基板へイオンを照射し、イオンにより微小な空洞を有するように脆弱化された領域を脆弱化層という。

10

【0184】

単結晶半導体基板1608には、市販の単結晶半導体基板を用いることができ、例えば、単結晶シリコン基板、単結晶ゲルマニウム基板、単結晶シリコンゲルマニウム基板など、第14族元素でなる単結晶半導体基板を用いることができる。また、ガリウムヒ素やインジウムリン等の化合物半導体基板も用いることができる。半導体基板として多結晶半導体基板を用いてもよい。もちろん、単結晶半導体基板は、円形のウエハに限定されるものではなく、様々な形状の単結晶半導体基板を用いることができる。例えば、円形、長方形、五角形、六角形などの多角形の基板を用いることができる。もちろん、市販の円形状の単結晶半導体ウエハを単結晶半導体基板に用いることも可能である。円形状の単結晶半導体ウエハには、シリコンやゲルマニウムなどの半導体ウエハ、ガリウムヒ素やインジウムリンなどの化合物半導体ウエハなどがある。単結晶半導体ウエハの代表例は、単結晶シリコンウエハであり、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)サイズ、直径400mm、直径450mmの円形のウエハを用いることができる。また、長方形の単結晶半導体基板は、市販の円形状の単結晶半導体ウエハを切断することで形成することができる。基板の切断には、ダイサー或いはワイヤソー等の切断装置、レーザ切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いることができる。また、基板として薄片化する前の半導体基板製造用のインゴットを、その断面が長方形になるように直方体状に加工し、この直方体状のインゴットを薄片化することでも、長方形形状の単結晶半導体基板を製造することができる。また、単結晶半導体基板の厚さは特に限定されないが、単結晶半導体基板を再利用することを考慮すれば、厚い方が1枚の原料ウエハからより多くの単結晶半導体層を形成することができるため、好ましい。市場に流通している単結晶シリコンウエハの厚さは、そのサイズはSEMI規格に準じており、例えば直径6インチのウエハは膜厚625μm、直径8インチのウエハは膜厚725μm、直径12インチのウエハは775μmとされている。なお、SEMI規格のウエハの厚さは公差±25μmを含んでいる。もちろん、原料となる単結晶半導体基板の厚さはSEMI規格に限定されず、インゴットをスライスするときに、その厚さを適宜調節することができる。もちろん、再利用された単結晶半導体基板1608を用いるときには、その厚さは、SEMI規格よりも薄くなる。透光性基板上に得られる単結晶半導体層は母体となる半導体基板を選択することによって決定することができる。

20

【0185】

また、単結晶半導体基板1608は、作製する半導体素子(本実施の形態においては電界効果トランジスタ)によって、結晶面方位を選択すればよい。例えば、結晶面方位として{100}面、{110}面など有する単結晶半導体基板を用いることができる。

【0186】

本実施の形態は、単結晶半導体基板の所定の深さに水素、ヘリウム、又はフッ素をイオン照射して添加し、その後熱処理を行って表層の単結晶半導体層を剥離するイオン照射剥離法で形成するが、ポーラスシリコン上に単結晶シリコンをエピタキシャル成長させた後、

40

50

ポーラスシリコン層をウォータージェットで劈開して剥離する方法を適用しても良い。

【0187】

単結晶半導体基板1608として単結晶シリコン基板を用い、希フッ酸で表面を処理し、自然酸化膜の除去と表面に付着するゴミ等の汚染物も除去して単結晶半導体基板1608表面を清浄化する。

【0188】

脆弱化層1610は、イオンをイオンドーピング法（ID法と略記する）やイオン注入法（II法と略記する）によって照射すればよい。脆弱化層1610は水素、ヘリウム若しくはフッ素に代表されるハロゲンのイオンを照射することで形成される。ハロゲン元素としてフッ素イオンを照射する場合にはソースガスとしてBF<sub>3</sub>を用いれば良い。なお、イオン注入とはイオン化したガスを質量分離して半導体基板に照射する方式をいう。 10

【0189】

例えば、イオン注入法を用いて、イオン化した水素ガスを質量分離し、H<sup>+</sup>のみ、（又はH<sub>2</sub><sup>+</sup>のみ）を選択的に加速して単結晶半導体基板に照射することができる。

【0190】

イオンドープ法は、イオン化したガスを質量分離せずに、プラズマ中で複数種のイオン種を作り、それらを加速して単結晶半導体基板に照射する。例えば、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含む水素では、照射されるイオンは、代表的にH<sub>3</sub><sup>+</sup>イオンが50%以上、例えばH<sub>3</sub><sup>+</sup>イオンが80%、他のイオン（H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオン）が20%、が一般的である。H<sub>3</sub><sup>+</sup>イオンのイオン種のみとして照射することもここではイオンドープとする。 20

【0191】

また、一又は複数の同一の原子から成る質量の異なるイオンを照射してもよい。例えば、水素イオンを照射する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくことが好ましい。水素イオンを照射する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくと照射効率を高めることができ、照射時間を短縮することができる。このような構成とすることで、剥離を容易に行うことができる。

【0192】

以下、イオンドーピング法とイオン注入法について詳細に説明する。イオンドーピング法に用いるイオンドーピング装置（ID装置ともいう）では、プラズマ空間が大きく、大量のイオンを単結晶半導体基板に照射することができる。一方、イオン注入法に用いるイオン注入装置（II装置ともいう）は、プラズマから取り出したイオンを質量分析して特定のイオン種だけを半導体基板に打ち込めるという特徴があり、基本的に点ビームをスキャンさせて処理する。 30

【0193】

プラズマ発生方法としては、どちらの装置も、例えば、フィラメントを熱して出てくる熱電子によりプラズマ状態を作っている。しかし、生成される水素イオン（H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>）が半導体基板に照射される際の水素イオン種の割合は、イオンドーピング法とイオン注入法で大きく異なる。

【0194】

H<sub>3</sub><sup>+</sup>をより多く照射するという観点からすれば、イオン注入装置よりイオンドーピング装置を用いる方が好ましいといえる。 40

【0195】

単結晶シリコン基板に水素イオンやフッ素イオンのようなハロゲンイオンを照射した場合、添加されたフッ素が、シリコン結晶格子内のシリコン原子をノックアウトする（追い出す）ことによって空白部分を効果的に作り出し、脆弱化層に微小な空洞を作る。この場合、比較的低温の熱処理によって脆弱化層に形成された微小な空洞の体積変化が起こり、脆弱化層に沿って分離することにより薄い単結晶半導体層を形成することができる。フッ素イオンを照射した後に、水素イオンを照射して空洞内に水素を含ませるようにも良い。単結晶半導体基板から薄い単結晶半導体層を分離するために形成する脆弱化層は、脆弱 50

化層に形成された微小な空洞の体積変化を利用して分離をするので、このようにフッ素イオンや水素イオンの作用を有効利用することが好ましい。

【0196】

また、単結晶半導体基板と上記単結晶半導体層と接合する絶縁層との間に、保護層を形成してもよい。保護層は、窒化シリコン層、酸化シリコン層、窒化酸化シリコン層、又は酸化窒化シリコン層から選ばれた一層又は複数の層による積層構造により形成することができる。これらの層は、単結晶半導体基板に脆弱化層が形成される前に単結晶半導体基板上に形成することができる。また、単結晶半導体基板に脆弱化層を形成した後に単結晶半導体基板上に形成してもよい。

【0197】

なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法 (RBS: Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS: Hydrogen Forward Scattering) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、Si が 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。

【0198】

脆弱化層の形成に当たってはイオンを高ドーズ条件で照射する必要があり、単結晶半導体基板 1608 の表面が粗くなってしまう場合がある。そのためイオンが照射される表面に窒化シリコン膜、窒化酸化シリコン膜、若しくは酸化シリコン膜などによりイオン照射に対する保護層を 50 nm 乃至 200 nm の厚さで設けておいても良い。

【0199】

例えば、単結晶半導体基板 1608 上に保護層としてプラズマ CVD 法により酸化窒化シリコン膜 (膜厚 5 nm ~ 300 nm、望ましくは 30 nm ~ 150 nm (例えば 50 nm)) と窒化酸化シリコン膜 (膜厚 5 nm ~ 150 nm、望ましくは 10 nm ~ 100 nm (例えば 50 nm)) の積層を形成する。一例としては、単結晶半導体基板 1608 上に酸化窒化シリコン膜を膜厚 50 nm 形成し、該酸化窒化シリコン膜上に窒化酸化シリコン膜を膜厚 50 nm 形成し、積層する。酸化窒化シリコン膜は有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜でもよい。

【0200】

また、単結晶半導体基板 1608 を脱脂洗浄し、表面の酸化膜を除去して熱酸化を行ってもよい。熱酸化としては通常のドライ酸化でも良いが、酸化雰囲気中にハロゲンを添加した酸化を行うことが好ましい。例えば、酸素に対し HCl を 0.5 ~ 1.0 体積% (好ましくは 3 体積%) の割合で含む雰囲気中で、700 以上の温度で熱処理を行う。好適には 950 ~ 1100 の温度で熱酸化を行うと良い。処理時間は 0.1 ~ 6 時間、好ましくは 0.5 ~ 3.5 時間とすれば良い。形成される酸化膜の膜厚としては、10 nm ~ 1000 nm (好ましくは 50 nm ~ 200 nm)、例えば 100 nm の厚さとする。

【0201】

ハロゲンを含むものとしては HCl の他に、HF、NF<sub>3</sub>、HBr、Cl<sub>2</sub>、ClF<sub>3</sub>、BCl<sub>3</sub>、F<sub>2</sub>、Br<sub>2</sub>、ジクロロエチレンなどから選ばれた一種又は複数種を適用することができる。

【0202】

このような温度範囲で熱処理を行うことで、ハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリングとしては、特に金属不純物を除去する効果がある。すなわち、塩素の作用により、金属などの不純物が揮発性の塩化物となって気相中へ離脱して除去

10

20

30

40

50

される。単結晶半導体基板1608の表面を化学的機械研磨(CMP)処理をしたものに對しては有効である。また、水素は単結晶半導体基板1608と形成される絶縁層との界面の欠陥を補償して界面の局在準位密度を低減する作用を奏し、単結晶半導体基板1608と絶縁層との界面が不活性化されて電気的特性が安定化する。

【0203】

この熱処理により形成される酸化膜中にハロゲンを含ませることができる。ハロゲン元素は $1 \times 10^{17} / \text{cm}^3 \sim 5 \times 10^{20} / \text{cm}^3$ の濃度で含まれることにより金属などの不純物を捕獲して単結晶半導体基板1608の汚染を防止する保護層としての機能を発現させることができる。

【0204】

脆弱化層1610を形成する際、加速電圧と全イオン数は、単結晶半導体基板上に堆積した膜の厚さと、目的とする単結晶半導体基板より分離して透光性基板上に転置される単結晶半導体層の膜厚と、照射するイオン種によって調整することができる。

【0205】

例えば、イオンドーピング法で原料として水素ガスを用い、加速電圧を40kV、全イオン数 $2 \times 10^{16} \text{ ions/cm}^2$ でイオンを照射して脆弱化層を形成することができる。保護層の膜厚を厚くすれば、同一条件でイオンを照射し脆弱化層を形成した場合、目的とする単結晶半導体基板より分離して透光性基板上に転置(転載)される単結晶半導体層として、膜厚の薄い単結晶半導体層を形成することができる。例えば、イオン種( $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$ イオン)の割合にもよるが、上記条件で脆弱化層を形成するとし、保護層として単結晶半導体基板上に酸化窒化シリコン膜(膜厚50nm)と窒化酸化シリコン膜(膜厚50nm)を保護層として積層する場合、透光性基板に転置される単結晶半導体層の膜厚は約120nmとなり、単結晶半導体基板上に酸化窒化シリコン膜(膜厚100nm)と窒化酸化シリコン膜(膜厚50nm)を保護層として積層する場合は、透光性基板に転置される単結晶半導体層の膜厚は約70nmとなる。

【0206】

ヘリウム(He)や水素を原料ガスにする場合、加速電圧を10kV～200kVの範囲で、ドーズ量を $1 \times 10^{16} \text{ ions/cm}^2 \sim 6 \times 10^{16} \text{ ions/cm}^2$ の範囲で照射し脆弱化層を形成することができる。ヘリウムを原料ガスにすると、質量分離を行わなくてもHe<sup>+</sup>イオンを主なイオンとして照射することができる。また、水素を原料ガスとするとH<sub>3</sub><sup>+</sup>イオンやH<sub>2</sub><sup>+</sup>イオンを主なイオンとして照射することができる。イオン種は、プラズマの生成方法、圧力、原料ガス供給量、加速電圧によっても変化する。

【0207】

脆弱化層形成の例としては、単結晶半導体基板上に酸化窒化シリコン膜(膜厚50nm)、窒化酸化シリコン膜(膜厚50nm)、及び酸化シリコン膜(膜厚50nm)を保護層として積層し、水素を加速電圧40kV、ドーズ量 $2 \times 10^{16} \text{ ions/cm}^2$ で照射し単結晶半導体基板に脆弱化層を形成する。その後保護層の最上層である該酸化シリコン膜上に接合面を有する絶縁層として酸化シリコン膜(膜厚50nm)を形成する。脆弱化層形成の他の例としては、単結晶半導体基板上に酸化シリコン膜(膜厚100nm)、及び窒化酸化シリコン膜(膜厚50nm)を保護層として積層し、水素を加速電圧40kV、ドーズ量 $2 \times 10^{16} \text{ ions/cm}^2$ で照射し単結晶半導体基板に脆弱化層を形成する。その後保護層の最上層である該窒化酸化シリコン膜上に接合面を有する絶縁層として酸化シリコン膜(膜厚50nm)を形成する。なお、上記酸化窒化シリコン膜及び窒化酸化シリコン膜はプラズマCVD法により形成すればよく、上記酸化シリコン膜は有機シランガスを用いてCVD法により形成すればよい。

【0208】

また、透光性基板と単結晶半導体基板との間に絶縁層を形成してもよい。絶縁層は透光性基板側、あるいは単結晶半導体基板側どちらか一方でもよいし、両方に形成してもよい。接合を形成する面に形成する絶縁層は平滑面を有し親水性表面を形成する。該絶縁層としては、酸化シリコン膜を用いることができる。酸化シリコン膜としては有機シランガスを

10

20

30

40

50

用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。

【0209】

有機シランガスとしては、珪酸エチル (TEOS: 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、トリメチルシラン (TMS:  $(\text{CH}_3)_3\text{SiH}$ )、テトラメチルシラン (化学式  $\text{Si}(\text{CH}_3)_4$ )、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシラン ( $\text{SiH}(\text{OC}_2\text{H}_5)_3$ )、トリスジメチルアミノシラン ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) 等のシリコン含有化合物を用いることができる。なお、原料ガスに有機シランを用いて化学気相成長法により酸化シリコン層を形成する場合、酸素を付与するガスを混合させることが好ましい。酸素を付与するガスとしては、酸素、亜酸化窒素、二酸化窒素等を用いることができる。さらに、アルゴン、ヘリウム、窒素又は水素等の不活性ガスを混合させてもよい。

【0210】

また、接合を形成する面に形成する絶縁層として、モノシラン、ジシラン、又はトリシラン等のシランを原料ガスに用いて化学気相成長法により形成される酸化シリコン膜を適用することもできる。この場合も、酸素を付与するガスや不活性ガス等を混合させることができが好ましい。また、単結晶半導体層と接合する絶縁層となる酸化シリコン膜は、塩素を含んでいてもよい。なお、本明細書において、化学気相成長 (CVD; Chemical Vapour Deposition) 法は、プラズマCVD法、熱CVD法、光CVD法を範疇に含む。

【0211】

その他、接合を形成する面に形成する絶縁層として、酸化性雰囲気下において熱処理することにより形成される酸化シリコン、酸素ラジカルの反応により成長する酸化シリコン、酸化性の薬液により形成されるケミカルオキサイドなどを適用することもできる。絶縁層として、シロキサン ( $\text{Si}-\text{O}-\text{Si}$ ) 結合を含む絶縁層を適用してもよい。また、前記有機シランガスと、酸素ラジカル又は窒素ラジカルとを反応させて絶縁層を形成してもよい。

【0212】

絶縁層において、接合を形成する面の表面は、算術平均粗さ  $R_a$  が  $0.8\text{ nm}$  未満、二乗平均平方根粗さ  $R_{ms}$  が  $0.9\text{ nm}$  未満が望ましく、 $R_a$  が  $0.4\text{ nm}$  以下、 $R_{ms}$  が  $0.5\text{ nm}$  以下がより望ましく、さらには  $R_a$  が  $0.3\text{ nm}$  以下、 $R_{ms}$  が  $0.4\text{ nm}$  以下がより望ましい。例えば、 $R_a$  が  $0.27\text{ nm}$ 、 $R_{ms}$  が  $0.34\text{ nm}$  である。本明細書において  $R_a$  は算術平均粗さであり、 $R_{ms}$  は二乗平均平方根粗さであり、測定範囲は  $2\text{ }\mu\text{m}^2$ 、又は  $10\text{ }\mu\text{m}^2$  である。

【0213】

透光性基板と単結晶半導体基板とを接合するに際し、接合を形成する面の一方若しくは双方に、好ましくは有機シランを原材料として成膜した酸化シリコン膜でなる絶縁層を設けると強固な接合を形成することができる。

【0214】

本実施の形態では、図16 (B) で示すように透光性基板と接合を形成する面に絶縁層 1604 として酸化シリコン膜を形成する。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板に形成した脆弱化層 1610 から脱ガスが起こらない温度として、例えば  $350^\circ\text{C}$  以下 (具体的な例としては  $300^\circ\text{C}$  ) の成膜温度が適用される。また、単結晶半導体基板から単結晶半導体層を剥離する熱処理は、成膜温度よりも高い熱処理温度が適用される。

【0215】

透光性基板には、不純物元素の拡散を防止する窒化シリコン膜又は窒化酸化シリコン膜を

10

20

30

40

50

ブロッキング層（バリア層ともいう）として設けてもよい。さらに応力を緩和する作用のある絶縁膜として酸化窒化シリコン膜を組み合わせても良い。

【0216】

図16（C）は透光性基板1601上に設けられたブロッキング層1609と単結晶半導体基板1608の絶縁層1604が形成された面とを密接させ、この両者を接合させる様子を示す。接合を形成する面は、十分に清浄化しておく。透光性基板1601上に設けられたブロッキング層1609と単結晶半導体基板1608の絶縁層1604が形成された面は、メガソニック洗浄などによって清浄化すればよい。また、メガソニック洗浄後にオゾン水で洗浄し、有機物の除去と表面の親水性向上を行ってもよい。

【0217】

透光性基板1601上のブロッキング層1609と絶縁層1604を対向させて、一箇所を外部から押しつけると、局所的に接合面同士の距離が縮まる事による、ファン・デル・ワールス力の強まりや水素結合の寄与によって、お互いに引きつけ合う。更に、隣接した領域でも対向する透光性基板1601上のブロッキング層1609と絶縁層1604間の距離が縮まるので、ファン・デル・ワールス力が強く作用する領域や水素結合が関与する領域が広がる事によって、接合（ボンディングともいう）が進行し接合面全域に接合が広がる。

10

【0218】

押しつける際に、基板四隅の一ヶ所を100kPa～5000kPaの圧力で抑えると、接合面同士が近づき、ファン・デル・ワールス力から水素結合へ移行することができる。基板内において一ヶ所の接合面が近接すると、隣接する接合面も近接し水素結合へ移行するため、接合面全域が水素結合へ移行することができる。

20

【0219】

良好な接合を形成するために、表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により200乃至400の温度であっても異種材料間の接合を形成することが容易となる。

【0220】

30

また、透光性基板と絶縁層との接合界面の接合強度を向上させるために、加熱処理を行うと好ましい。例えば、オーブンや炉などで70～350（例えば200で2時間）の温度条件で熱処理を行う。

【0221】

図16（D）において、透光性基板1601と単結晶半導体基板1608を貼り合わせた後、加熱処理を行い脆弱化層1610を劈開面として単結晶半導体基板1608を透光性基板1601から剥離する。例えば、400～700の熱処理を行うことにより、脆弱化層1610に形成された微小な空洞の体積変化が起こり、脆弱化層1610に沿って劈開することが可能となる。絶縁層1604はブロッキング層1609を介して透光性基板1601と接合しているので、透光性基板1601上には単結晶半導体基板1608と同じ結晶性の単結晶半導体層1602が残存することとなる。

40

【0222】

400～700の温度域での熱処理は、前述の接合強度を向上させるための熱処理と同じ装置で連続して行ってもよいし、別の装置で行ってもよい。例えば炉で2002時間熱処理した後に、600近傍まで昇温し2時間保持し、400から室温までの温度域に降温した後炉より取り出す。また、熱処理は室温から昇温してもよい。また、炉で2002時間熱処理した後に、瞬間熱アニール（RTA）装置によって600～700の温度域で、1分間～30分間（例えば6007分間、6507分間）熱処理を行ってもよい。

【0223】

50

400～700の温度域での熱処理により、絶縁層と透光性基板との接合は水素結合から共有結合に移行し、脆弱化層に添加された元素が析出し圧力が上昇し、単結晶半導体基板より単結晶半導体層を剥離することができる。熱処理を行った後は透光性基板と単結晶半導体基板は、一方が他方に載っている状態であり、大きな力を加えずに透光性基板と単結晶半導体基板を離すことができる。例えば、上方に載っている基板を真空チャックで持ち上げることにより簡単に離すことができる。この際、下側の基板の真空チャックやメカニカルチャックで固定しておくと水平方向のずれがなく透光性基板及び単結晶半導体基板の両基板を離すことができる。

【0224】

なお、図16、図17においては、単結晶半導体基板1608が透光性基板1601より10小さいサイズの例を示すが、本実施の形態はそれに限定されず、単結晶半導体基板1608と透光性基板1601が同じサイズであってもよいし、単結晶半導体基板1608が透光性基板1601より大きいサイズであってもよい。

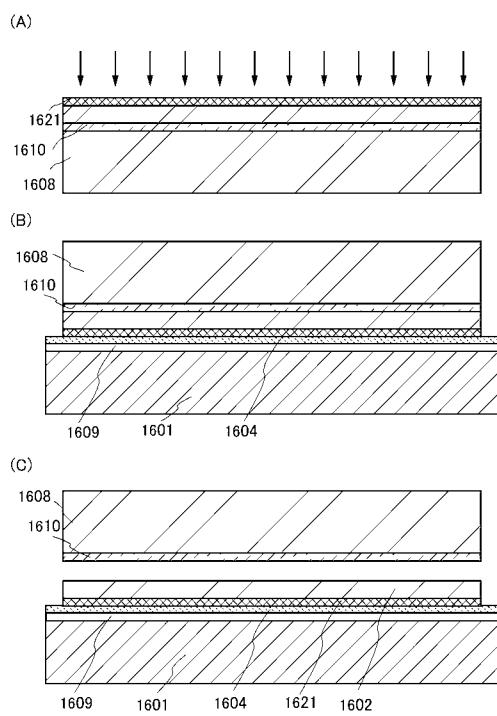

【0225】

図17は透光性基板側に絶縁層を設けて単結晶半導体層を形成する工程を示す。図17(A)は保護層1621として酸化シリコン膜が形成された単結晶半導体基板1608に電界で加速されたイオンを所定の深さに照射し、脆弱化層1610を形成する工程を示している。イオンの照射は図16(A)の場合と同様である。単結晶半導体基板1608の表面に保護層1621を形成しておくことでイオン照射によって表面がダメージを受け、平坦性が損なわれるのを防ぐことができる。また、保護層1621によって、単結晶半導体基板1608から形成される単結晶半導体層1602に対する不純物の拡散防止効果を20発現する。

【0226】

図17(B)は、プロッキング層1609及び絶縁層1604が形成された透光性基板1601と単結晶半導体基板1608の保護層1621が形成された面を密着させて接合を形成する工程を示している。透光性基板1601上の絶縁層1604と単結晶半導体基板1608の保護層1621を密着させることにより接合が形成される。

【0227】

その後、図17(C)で示すように単結晶半導体基板1608を剥離する。単結晶半導体層を剥離する熱処理は図16(D)の場合と同様にして行う。このようにして図17(C)で示す絶縁層を介して単結晶半導体層を有する本実施の形態のSOI構造の半導体基板を得ることができる。

【0228】

また、単結晶半導体基板より分離し、透光性基板に転置された単結晶半導体層は、分離工程およびイオン注入工程によって、結晶欠陥が生じ、また、その表面は平坦性が損なわれ、凹凸が形成されてしまう場合がある。単結晶半導体層を用いて半導体素子としてトランジスタを作製する場合、このような凹凸のある単結晶半導体層の上面に薄く、絶縁耐圧性の高いゲート絶縁層を形成することは困難である。また、単結晶半導体層に結晶欠陥があると、ゲート絶縁層との局在界面準位密度が高くなるなど、トランジスタの性能および信頼性に影響を与える。

【0229】

従って単結晶半導体層にレーザ光のような電磁波を照射し、結晶欠陥を低減させることが好ましい。電磁波を照射することによって、単結晶半導体層の少なくとも一部の領域を溶融させ、単結晶半導体層中の結晶欠陥を低減させることができる。なお、電磁波の照射前に単結晶半導体層表面に形成された酸化膜（自然酸化膜、あるいはケミカル酸化膜）を希フッ酸で除去するとよい。

【0230】

電磁波は単結晶半導体層に高いエネルギーを供給できるものであればよく、好適にはレーザ光を用いることができる。

【0231】

10

20

30

40

50

またエネルギーの供給は、高エネルギーを有する粒子を照射などによって単結晶半導体層に衝突させ、主として熱伝導によって行うこともできる。高エネルギーを有する粒子を提供する熱源としては、プラズマを用いることができ、常圧プラズマ、高圧プラズマ、熱プラズマジェット、ガスバーナーなどの炎を用いることができる、又、他の熱源としては電子ビームなどを用いることができる。

#### 【0232】

電磁波の波長は、単結晶半導体層に吸収される波長とする。その波長は、電磁波の表皮深さ (skin depth)などを考慮して決定することができる。例えば、電磁波の波長は 190 nm ~ 600 nm を用いることができる。また、電磁波のエネルギーは、電磁波の波長、電磁波の表皮深さ、照射する単結晶半導体層の膜厚などを考慮して決定することができる。10

#### 【0233】

レーザ光を発振するレーザは、連続発振レーザ、疑似連続発振レーザ及びパルス発振レーザを用いることができる。部分溶融させるためパルス発振レーザが好ましい。例えば、KrF レーザなどのエキシマレーザ、Ar レーザ、Kr レーザなどの気体レーザがある。その他、固体レーザとして、YAG レーザ、YVO<sub>4</sub> レーザ、YLF レーザ、YAlO<sub>3</sub> レーザ、GdVO<sub>4</sub> レーザ、KGW レーザ、KYW レーザ、アレキサンドライトレーザ、Ti : サファイアレーザ、Y<sub>2</sub>O<sub>3</sub> レーザなどがある。なお、エキシマレーザはパルス発振レーザであるが、YAG レーザなどの固体レーザには、連続発振レーザにも、疑似連続発振レーザにも、パルス発振レーザにもなるものがある。なお、固体レーザにおいては、基本波の第 2 高調波 ~ 第 5 高調波を適用するのが好ましい。また、GaN、GaAs、GaAlAs、InGaAsP 等の半導体レーザも用いることができる。20

#### 【0234】

また、電磁波のエネルギーを単結晶半導体層に照射できるならば、ランプ光を用いてもよい。例えば、紫外線ランプ、ブラックライト、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いてもよい。上記ランプ光を用いたフラッシュアニールを用いてもよい。ハロゲンランプやキセノンランプなどを好適に用いて行うフラッシュアニールは極短時間の処理でよいため、透光性基板の温度上昇を抑えることができる。

#### 【0235】

電磁波の形状や電磁波の進路を調整するため、シャッター、ミラー又はハーフミラー等の反射体、シリンドリカルレンズや凸レンズなどによって構成される光学系が設置されているよい。

#### 【0236】

なお、電磁波の照射方法は、選択的に電磁波を照射してもよいし、光(電磁波)を X-Y 軸方向に走査して光(電磁波)を照射することができる。この場合、光学系にポリゴンミラーやガルバノミラーを用いることが好ましい。

#### 【0237】

電磁波の照射は、大気雰囲気のような酸素を含む雰囲気、または窒素雰囲気のような不活性雰囲気で行うことができる。不活性雰囲気中で電磁波を照射するには、気密性のあるチャンバー内で電磁波を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、電磁波の被照射面に窒素ガスなど不活性ガスを吹き付けることで、窒素雰囲気を形成することもできる。40

#### 【0238】

さらに、電磁波照射などの高エネルギーを供給され、結晶欠陥を低減された単結晶半導体層表面に研磨処理を行ってもよい。研磨処理によって単結晶半導体層表面の平坦性を高めることができる。

#### 【0239】

研磨処理としては、化学的機械研磨 (CMP) 法や液体ジェット研磨法を用いることができる。なお、研磨処理前に単結晶半導体層表面を洗浄し、清浄化する。洗浄は、メガソニ50

ツク洗浄や2流体ジェット洗浄等を用いればよく、洗浄により単結晶半導体層表面のゴミ等を除去する。また、希フッ酸を用いて単結晶半導体層表面上の自然酸化膜等を除去して単結晶半導体層を露出させると好適である。

【0240】

また、電磁波を照射する前にも単結晶半導体層表面に研磨処理（又はエッティング処理）を行ってもよい。

【0241】

また、単結晶半導体基板より単結晶半導体層を転載する際、単結晶半導体基板を選択的にエッティングし、形状を加工された複数の単結晶半導体層を、透光性基板に転載してもよい。

10 透光性基板には、複数の島状の単結晶半導体層を形成することができる。予め、単結晶半導体基板で形状を加工して転載するために、単結晶半導体基板の大きさや形状に制限を受けない。そのために大型の透光性基板への単結晶半導体層の転載がより効率よく行うことができる。

【0242】

さらに、透光性基板上に貼り合わせられた単結晶半導体層に対して、エッティングを行い、単結晶半導体層の形状を加工、修正し精密に制御してもよい。これにより、半導体素子の単結晶半導体層の形状に加工でき、レジストマスク形成時の露光の回り込みなどによるパターンズレや、転載時の貼り合わせ工程による位置ズレなどによる単結晶半導体層の形成位置の誤差や形状不良を修正することができる。

【0243】

従って、透光性基板に所望の形状の複数の単結晶半導体層を、歩留まりよく形成することができる。よって、大面積基板により精密な高性能の半導体素子及び集積回路を有する光センサを高スループットで生産性よく作製することができる。

【0244】

また、単結晶半導体基板より単結晶半導体層を分離してから、透光性基板に貼り合わせてもよい。劈開により露出される単結晶半導体層の表面を透光性基板側に向けて貼り合わせてもよいし、劈開により露出される単結晶半導体層の表面とゲート絶縁膜とが接するように、単結晶半導体層を透光性基板上に貼り合わせてもよい。

【0245】

本実施の形態において、単結晶半導体基板1608として単結晶シリコン基板を適用した場合は、単結晶半導体層1602として単結晶シリコン層を得ることが可能である。また、本実施の形態の光センサの製造方法は、プロセス温度を700以下とすることができるため、透光性基板1601としてガラス基板を適用することができる。すなわち、従来の薄膜トランジスタと同様にガラス基板上に形成することができ、かつ単結晶シリコン層を半導体層に適用することが可能となる。これらのことにより、高速動作が可能で、サブスレッショルド値が低く、電界効果移動度が高く、低消費電圧で駆動可能など高性能、高信頼性のトランジスタをガラス基板等の透光性基板上に作製することができる。

【0246】

本実施の形態は、実施の形態1と適宜組み合わせることができる。

【0247】

（実施の形態4）

本実施の形態では、実施の形態2において、単結晶半導体基板より透光性基板へ単結晶半導体層を接合する工程の異なる例を示す。従って、実施の形態2と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

【0248】

まず、単結晶基板側の処理を説明する。本実施の形態では、単結晶半導体基板を脱脂洗浄し、表面の酸化膜を除去して熱酸化を行う。熱酸化としては、酸化雰囲気中にハロゲンを添加した酸化を行うことが好ましい。例えば、酸素に対しHClを0.5～10体積%（好ましくは3体積%）の割合で含む雰囲気中で、700以上の中温で熱処理を行う。好適には950～1100の温度で熱酸化を行うと良い。処理時間は0.1～6時間、

10

20

30

40

50

好みくは0.5~3.5時間とすれば良い。形成される酸化膜の膜厚としては、10nm~1000nm(好みくは50nm~200nm)、例えば100nmの厚さとする。

【0249】

ハロゲンを含むものとしてはHClの他に、HF、NF<sub>3</sub>、HBr、Cl<sub>2</sub>、ClF<sub>3</sub>、BCl<sub>3</sub>、F<sub>2</sub>、Br<sub>2</sub>などから選ばれた一種又は複数種を適用することができる。

【0250】

このような温度範囲で熱処理を行うことで、ハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリングとしては、特に金属不純物を除去する効果がある。すなわち、塩素の作用により、金属などの不純物が揮発性の塩化物となって気相中へ離脱して除去される。単結晶半導体基板の表面を化学的機械研磨(CMP)処理をしたものに対しては有効である。また、水素は単結晶半導体基板と、透光性基板に形成される絶縁層との界面の欠陥を補償して界面の局在準位密度を低減する作用を奏し、単結晶半導体基板と絶縁層との界面が不活性化されて電気的特性が安定化する。

10

【0251】

この熱処理により形成される酸化膜中にハロゲンを含ませることができる。ハロゲン元素は $1 \times 10^{17} / \text{cm}^3 \sim 5 \times 10^{20} / \text{cm}^3$ の濃度で含まれることにより金属などの不純物を捕獲して単結晶半導体基板の汚染を防止する保護層としての機能を発現させることができる。

20

【0252】

単結晶半導体基板にイオンを導入し、脆弱化層を形成する。脆弱化層が形成される領域の深さは、導入されるイオンの加速エネルギーと入射角によって調節することができる。加速エネルギーは加速電圧、ドーズ量などにより調節できる。

【0253】

イオンの導入の際に用いるガスとしては、水素ガス、希ガス等があるが、本実施の形態では水素ガスを用いることが好みしい。イオンドーピング法で水素ガスを用いた場合、生成するイオン種は、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>及びH<sub>3</sub><sup>+</sup>であるが、H<sub>3</sub><sup>+</sup>が最も多く導入されることが好みしい。H<sub>3</sub><sup>+</sup>はH<sup>+</sup>、H<sub>2</sub><sup>+</sup>よりもイオンの導入効率がよく、導入時間の短縮を図ることができる。また、後の工程において脆弱化層に亀裂が生じやすくなる。

30

【0254】

次に、透光性基板側の処理を説明する。まず透光性基板の表面を洗浄する。洗浄は、塩酸過水(HPM)、硫酸過水(SPM)、アンモニア過水(APM)、希フッ酸(DHF)等を用いて超音波洗浄を行えばよく、本実施の形態では、塩酸過水を用いて超音波洗浄を行う。

【0255】

次に、洗浄によって表面のゴミ等の不純物などを除去された透光性基板にプラズマ処理による平坦化処理を行う。本実施の形態では、プラズマ処理は真空チャンバー内でアルゴン(Ar)ガスなどの不活性ガスを用い、被処理物である透光性基板にバイアス電圧を印加してプラズマ状態として行う。不活性ガスとともに、酸素(O<sub>2</sub>)ガス、窒素(N<sub>2</sub>)ガスを導入してもよい。

40

【0256】

透光性基板を陰極方向とし、プラズマ中のArの陽イオンを陰極方向に加速し、透光性基板に衝突させる。Arの陽イオンの衝突によって透光性基板表面がスパッタエッティングされ、透光性基板表面の凸部をエッティングし、透光性基板の表面を平坦化することができる。反応ガスは、透光性基板表面のスパッタエッティングによって生じる欠陥を補修する効果がある。

【0257】

次に、透光性基板上に絶縁層を形成する。本実施の形態では、シリコン系の絶縁層以外の絶縁層である酸化アルミニウムを主成分とする酸化膜を用いる。酸化アルミニウムを主成分とする酸化膜とは、当該酸化膜に含まれる成分の合計を100重量%とするときに、酸

50

化アルミニウムを10重量%以上含む酸化膜をいう。他にも、絶縁層としては、酸化アルミニウムを主成分とし、酸化マグネシウムと酸化ストロンチウムの一方又は両方が含まれる膜を適用することができる。また、窒素を含む酸化アルミニウムを用いてもよい。

【0258】

絶縁層は、スパッタリング法により形成することができる。スパッタリング法に用いるターゲットとしては、例えば、アルミニウムを含む金属又は酸化アルミニウム等の金属酸化物を用いることができる。なお、ターゲットの材料は、形成する膜に応じて適宜選択すればよい。

【0259】

ターゲットとして金属を用いる場合には、反応ガス（例えば、酸素）を導入しながらスパッタすること（反応性スパッタリング法）により、絶縁層を形成する。金属としては、アルミニウムの他に、マグネシウム（Mg）、アルミニウムとマグネシウムを含む合金、アルミニウムとストロンチウム（Sr）を含む合金、アルミニウムとマグネシウムとストロンチウムを含む合金を用いることができる。この場合、スパッタリングは直流（DC）電源又は高周波（RF）電源を用いて行えばよい。

10

【0260】

ターゲットとして金属酸化物を用いる場合には、高周波（RF）電源を用いてスパッタすること（RFスパッタリング法）により、絶縁層を形成する。金属酸化物としては、酸化アルミニウムの他に、酸化マグネシウム、酸化ストロンチウム、アルミニウムとマグネシウムを含有する酸化物、アルミニウムとストロンチウムを含有する酸化物、アルミニウムとマグネシウムとストロンチウムを含有する酸化物を用いることができる。

20

【0261】

他にも、バイアススパッタリング法を用いて、絶縁層を形成してもよい。バイアススパッタリング法を用いると、膜の堆積と表面の平坦化を両方行うことができる。

【0262】

アルミニウムを主成分とする酸化膜は透光性基板に含まれる可動イオンや水分等の不純物が、後に透光性基板上に形成される単結晶半導体膜に拡散することを防ぐことができる。

【0263】

次に、単結晶半導体基板の表面と透光性基板の表面とを対向させ、単結晶半導体基板と絶縁層とをボンディングする。単結晶半導体基板と透光性基板上に形成された絶縁層の表面とを密着させることにより接合が形成される。

30

【0264】

なお、単結晶半導体基板と透光性基板をボンディングさせる前に、透光性基板上に形成された絶縁層の表面処理を行うことが好ましい。

【0265】

次に、実施の形態2と同様に、加熱処理を行い脆弱化層にて分離（劈開）することにより、透光性基板上に絶縁層を介して単結晶半導体層を形成することができる。

【0266】

透光性基板上に設けられた単結晶半導体層を用いて半導体素子層を形成することができる。

40

【0267】

次に、分離された単結晶半導体基板を繰り返し利用する工程（半導体基板再生処理）について説明する。

【0268】

まず、分離された単結晶半導体基板を取り出す。エッジロールオフの影響により、単結晶半導体基板の端部において透光性基板との貼り合わせが十分に行われない場合がある。その結果、端部において単結晶半導体基板は脆弱化層にて分離されず、絶縁層等が残存する場合がある。

【0269】

単結晶半導体基板の端部における残渣部分を除去する。残渣部分は、ウェットエッティング

50

処理を行うことにより除去することができる。具体的には、フッ化水素酸とフッ化アンモニウムと界面活性剤を含む混合溶液（例えば、ステラケミファ社製、商品名：L A L 5 0 0）をエッチャントとして用いてウェットエッチングを行う。

【 0 2 7 0 】

また、水素イオンが導入された脆弱化層は、T M A H ( T e t r a M e t h y l A m m o n i u m H y d r o x i d e 、 テトラメチルアンモニウムヒドロキシド) に代表される有機アルカリ系水溶液を用いてウェットエッチングすることにより、除去することができる。このような処理を行うことにより、単結晶半導体基板の端部における残渣物による段差が緩和される。

【 0 2 7 1 】

次に、単結晶半導体基板をハロゲン雰囲気中で酸化することにより、酸化膜を形成し、その後当該酸化膜を除去する。ハロゲンとしては塩化水素 ( H C l ) を用いることができる。こうすることでハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリングとしては、特に金属不純物を除去する効果がある。すなわち、塩素の作用により、金属などの不純物が揮発性の塩化物となって気相中へ離脱して除去される。

【 0 2 7 2 】

次に、単結晶半導体基板に研磨処理としてC M P 処理を行う。その結果、単結晶半導体基板の端部における段差を除去し、単結晶半導体基板の表面を平坦にすることができる。その後、得られた単結晶半導体基板を母体ウエハーとして再度利用する。

【 0 2 7 3 】

本実施の形態で示したように、単結晶半導体基板の再生処理工程により単結晶半導体基板を繰り返し利用することによって、低コスト化を図ることができる。また、本実施の形態で示した単結晶半導体基板の再生処理工程を用いることにより、単結晶半導体基板を繰り返し利用した場合であっても、単結晶半導体基板の表面を十分に平坦化することができるため、単結晶半導体基板と透光性基板との密着性を向上させ、貼り合わせ不良を低減することができる。

【 0 2 7 4 】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。そのため、カラーセンサは、光センサを複数具備することで増加してしまう端子数をインターポーラー上で削減することができる。具体的には、高電源電位が入力される端子、低電源電位が入力される端子をインターポーラー上で共通化することができる。そのため、端子電極の数を大幅に削減することができる。端子数を削減することにより、外部機器との接続不良の減少を図るために歩留まりの向上を図ることができる。また本実施の形態における構成では、複数の光センサをインターポーラー上に設けてカラーセンサとする際、ピンコンパチブルを図ることができる。

【 0 2 7 5 】

（実施の形態 5 ）

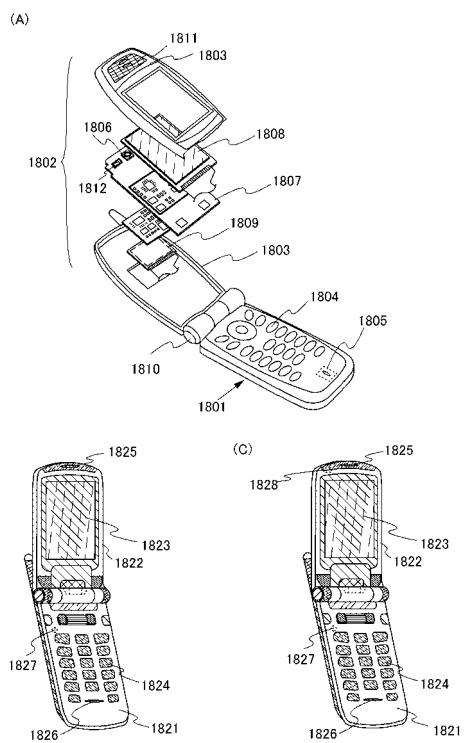

本実施の形態では、上記実施の形態により得られたカラーセンサを含む様々な電子機器の例について説明する。電子機器として、コンピュータ、ディスプレイ、携帯電話、テレビジョン装置などが挙げられる。これらの電子機器の具体例を図 1 8 ( A ) 乃至 ( C ) 、図 1 9 ( A ) ( B ) 、図 2 0 、及び図 2 1 ( A ) ( B ) に示す。

【 0 2 7 6 】

図 1 8 ( A ) 乃至図 1 8 ( C ) は携帯電話であり、図 1 8 ( A ) は、本体 ( A ) 1 8 0 1 、本体 ( B ) 1 8 0 2 、筐体 1 8 0 3 、操作キー 1 8 0 4 、音声出力部 1 8 0 6 、音声入力部 1 8 0 5 、回路基板 1 8 0 7 、表示パネル ( A ) 1 8 0 8 、表示パネル ( B ) 1 8 0 9 、蝶番 1 8 1 0 、透光性材料部 1 8 1 1 、カラーセンサ 1 8 1 2 を有している。

【 0 2 7 7 】

カラーセンサ 1 8 1 2 は透光性材料部 1 8 1 1 を透過した光を色要素毎に検知し、検知した外部光の照度に合わせて表示パネル ( A ) 1 8 0 8 及び表示パネル ( B ) 1 8 0 9 の輝

10

20

30

40

50

度コントロールや、色調節を行う。これにより携帯電話の消費電流を抑え、且つ外部環境の色味に応じて最適化された表示を行うことができる。

【0278】

なお色要素とは、一例としては赤（R）、緑（G）、青（B）であり、光センサが具備する光フィルタの光透過特性を調整すればよい。

【0279】

図18（B）及び図18（C）に携帯電話の別の例を示す。図18（B）において、本体1821、筐体1822、表示パネル1823、操作キー1824、音声出力部1825、音声入力部1826、カラーセンサ1827を示し、図18（C）において、図18（B）での構成に加えてカラーセンサ1828を示している。

10

【0280】

図18（B）に示す携帯電話では、本体1821に設けられたカラーセンサ1827により外部の光を色要素毎に検知することにより表示パネル1823及び操作キー1824の輝度を制御し、外部環境の色味に応じて最適化された表示を行うことが可能である。

【0281】

また図18（C）に示す携帯電話では、図18（A）の構成に加えて、本体1821の内部にカラーセンサ1828を設けている。カラーセンサ1828により、表示パネル1823に設けられているバックライトの輝度を制御し、外部環境の色味に応じて最適化された表示を行うことが可能である。特にバックライトを赤（R）、緑（G）、青（B）の3色のLEDで構成することで表示の色味を調整している場合には、カラーセンサによるバックライトの調光を行うことにより、画質の向上を図ることができる。

20

【0282】

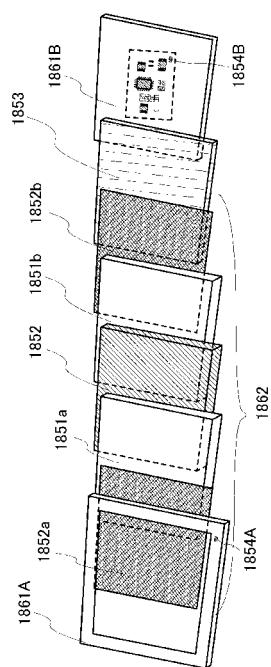

図19に示す液晶パネル1862は、筐体1861A、バックライト1853の間にあり、基板1851a及び基板1851bに挟まれた液晶層1852、偏光フィルタ1852a及び偏光フィルタ1852b等を有している。また筐体1861Aにはカラーセンサ1854Aが付設されている。またバックライトの背後には制御回路基板1861Bが設けられており、制御回路基板1861Bにはカラーセンサ1854Bが付設されている。

【0283】

カラーセンサ1854Aは外部光を色要素毎に検知し、その情報がフィードバックされて液晶パネル1862の輝度補正、及びビデオデータの色度補正が行う。またカラーセンサ1854Bはバックライト1853の光を色要素毎に検知し、検知した外部光の照度に合わせてバックライトの制御を行う。カラーセンサによるバックライトの調光を行うことにより、画質の向上を図ることができる。

30

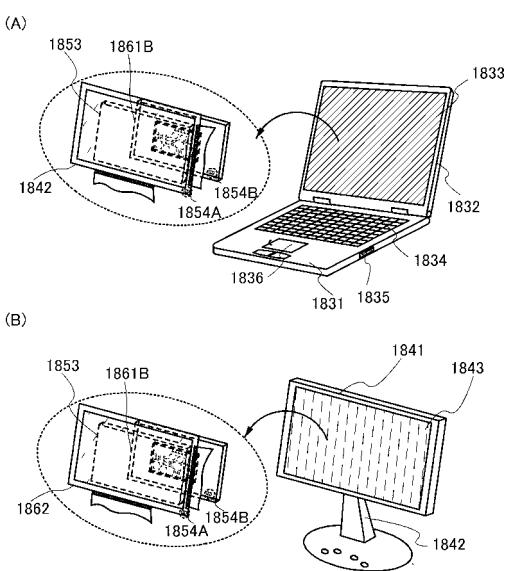

【0284】

図20（A）はコンピュータであり、本体1831、筐体1832、表示部1833、キーボード1834、外部接続ポート1835、ポインティングデバイス1836等を含む。

【0285】

また図20（B）は表示装置の例であるテレビジョン装置であり、筐体1841、支持台1842、表示部1843などによって構成されている。

40

【0286】

図20（A）のコンピュータに設けられる表示部1833、及び図20（B）に示す表示装置の表示部1843は、図19で示すように、内部にカラーセンサ1854Bを具備する制御回路基板1861B、バックライト1853、基板上にカラーセンサ1854Aが設けられた液晶パネル1862を有する。なお、液晶パネルの基板上に設けられるカラーセンサ1854Aには、筐体に設けられた導光部を介して筐体の外部光を検出する構成としてもよい。

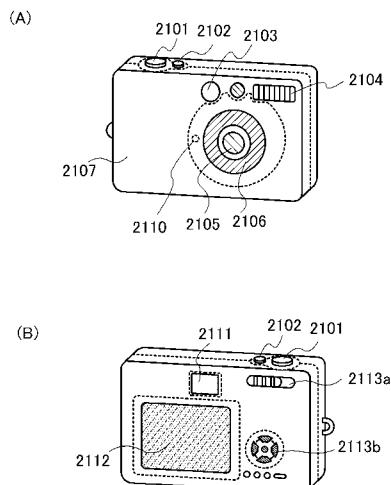

【0287】

図21（A）及び図21（B）は、上記実施の形態によるカラーセンサ2110を含むカメラ、例えばデジタルカメラの例を示す図である。図21（A）は、デジタルカメラの前

50

面方向から見た斜視図、図21(B)は、後面方向から見た斜視図である。図21(A)において、デジタルカメラには、リリースボタン2101、メインスイッチ2102、ファインダ窓2103、フラッシュ2104、レンズ2105、鏡胴2106、筐体2107、カラーセンサ2110が備えられている。

【0288】

また、図21(B)において、ファインダ接眼窓2111、モニタ2112、操作ボタン2113a、2113bが備えられている。

【0289】

リリースボタン2101は、半分の位置まで押下されると、焦点調整機構および露出調整機構が作動し、最下部まで押下されるとシャッターが開く。

10

【0290】

メインスイッチ2102は、押下又は回転によりデジタルカメラの電源のオン、オフを切り替える。

【0291】

ファインダ窓2103は、デジタルカメラの前面のレンズ2105の上部に配置されており、図21(B)に示すファインダ接眼窓2111から撮影する範囲やピントの位置を確認するための装置である。

【0292】

フラッシュ2104は、デジタルカメラの前面上部に配置され、被写体輝度が低いときに、リリースボタンが押下されてシャッターが開くと同時に補助光を照射する。

20

【0293】

レンズ2105は、デジタルカメラの正面に配置されている。レンズは、フォーカシングレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光学系を構成する。また、レンズの後方には、CCD(Charge Coupled Device)等の撮像素子が設けられている。

【0294】

鏡胴2106は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレンズの位置を移動するものであり、撮影時には、鏡胴を繰り出すことにより、レンズ2105を手前に移動させる。また、携帯時は、レンズ2105を沈銅させてコンパクトにする。なお、本実施の形態においては、鏡胴を繰り出すことにより被写体をズーム撮影することができる構造としているが、この構造に限定されるものではなく、筐体2107内の撮影光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでもよい。

30

【0295】

ファインダ接眼窓2111は、デジタルカメラの後面上部に設けられており、撮影する範囲やピントの位置を確認する際に接眼するために設けられた窓である。

【0296】

操作ボタン2113は、デジタルカメラの後面に設けられた各種機能ボタンであり、セットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等により構成されている。

40

【0297】

上記実施の形態で述べたカラーセンサ2110を図21(A)及び図21(B)に示すカメラに組み込むと、カラーセンサ2110が光の有無及び外部光の色要素毎の強度の検知をすることができる、これによりカメラの露出調整及び色調整等を行うことができる。上記実施の形態で述べたカラーセンサは、薄型なため、実装しても装置を小型化することができる。カラーセンサのような部品の小型化は、携帯用電子機器に利用する場合に特に有用である。

【0298】

また上記実施の形態で述べたカラーセンサはその他の電子機器、例えばプロジェクションテレビ、ナビゲーションシステム等に応用することが可能である。すなわち光を検出する

50

必要のあるものであればいかなるものにも用いることが可能である。

【0299】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。そのため、カラーセンサは、光センサを複数具備することで増加してしまう端子数をインターポーラー上で削減することができる。具体的には、高電源電位が入力される端子、低電源電位が入力される端子をインターポーラー上で共通化することができる。そのため、端子電極の数を大幅に削減することができる。端子数を削減することにより、外部機器との接続不良の減少を図ることができるため、歩留まりの向上を図ることができる。また本実施の形態における構成では、複数の光センサをインターポーラー上に設けてカラーセンサとする際、ピンコンパチブルを図ることができる。

10

【符号の説明】

【0300】

|     |               |    |

|-----|---------------|----|

| 100 | インターポーラー      | 20 |

| 101 | 半導体素子層        |    |

| 104 | 端子電極          |    |

| 105 | 端子電極          |    |

| 106 | 端子電極          |    |

| 107 | 端子電極          |    |

| 108 | 端子電極          |    |

| 109 | 配線            |    |

| 110 | 配線            |    |

| 111 | 配線            |    |

| 112 | 配線            |    |

| 113 | 配線            |    |

| 115 | 点線            |    |

| 116 | 遮光層           |    |

| 151 | 素子層           |    |

| 201 | 光電変換回路部       | 30 |

| 211 | 光電流変換回路       |    |

| 212 | 配線層           |    |

| 213 | 光電変換素子        |    |

| 300 | 光センサ          |    |

| 301 | 光電変換素子        |    |

| 302 | 対数圧縮回路        |    |

| 303 | 温度補正電圧生成回路    |    |

| 304 | 温度補正演算回路      |    |

| 305 | 回路部           |    |

| 400 | 光センサ          | 40 |

| 401 | 内部抵抗          |    |

| 500 | 光センサ          |    |

| 501 | 光電変換素子        |    |

| 502 | A/D変換回路       |    |

| 503 | 定電圧回路         |    |

| 504 | 発振回路          |    |

| 505 | I2Cインターフェース回路 |    |

| 506 | 回路部           |    |

| 601 | 端子電極          |    |

| 602 | 端子電極          |    |

| 603 | 端子電極          | 50 |

|         |          |    |

|---------|----------|----|

| 6 0 4   | 端子電極     |    |

| 6 0 5   | 端子電極     |    |

| 6 0 6   | 端子電極     |    |

| 6 0 7   | 端子電極     |    |

| 6 0 8   | 端子電極     |    |

| 6 0 9   | 配線       |    |

| 6 1 0   | 配線       |    |

| 6 1 1   | 配線       |    |

| 6 1 2   | 配線       |    |

| 6 1 3   | 配線       | 10 |

| 6 1 4   | 配線       |    |

| 6 1 5   | 配線       |    |

| 6 1 6   | 配線       |    |

| 7 0 1   | 光センサ     |    |

| 7 1 4   | 透光性基板    |    |

| 7 3 0   | 樹脂       |    |

| 8 0 1   | 光電変換回路部  |    |

| 1 0 1 B | 光センサ     |    |

| 1 0 1 G | 光センサ     |    |

| 1 0 1 R | 光センサ     | 20 |

| 1 0 2 B | 光電流変換回路部 |    |

| 1 0 2 G | 光電流変換回路部 |    |

| 1 0 2 R | 光電流変換回路部 |    |

| 1 0 3 B | 光フィルタ    |    |

| 1 0 3 G | 光フィルタ    |    |

| 1 0 3 R | 光フィルタ    |    |

| 1 1 4 B | 透光性基板    |    |

| 1 1 4 G | 透光性基板    |    |

| 1 1 4 R | 透光性基板    |    |

| 1 1 6 B | 遮光層      | 30 |

| 1 1 6 G | 遮光層      |    |

| 1 1 6 R | 遮光層      |    |

| 1 1 7 B | 透光性樹脂層   |    |

| 1 1 7 G | 透光性樹脂層   |    |

| 1 1 7 R | 透光性樹脂層   |    |

| 1 2 0 0 | 透光性基板    |    |

| 1 2 0 2 | 透光性基板    |    |

| 1 2 0 3 | 固定テープ    |    |

| 1 2 0 4 | ダイサー     |    |

| 1 2 0 5 | 透光性基板    | 40 |