# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl.

H01P 1/203 (2006.01)

H01L 25/00 (2006.01)

(45) 공고일자 2007년05월17일 (11) 등록번호 10-0719422 (24) 등록일자 2007년05월11일

(21) 출원번호10-2005-7017428(22) 출원일자2005년09월16일심사청구일자2005년09월16일번역문 제출일자2005년09월16일

변역군 세물일자 2005년09월10일 (86) 국제출원번호 PCT/US2004/004323 국제출원일자 2004년02월13일

(87) 국제공개번호 WO 2004/095622

국제공개일자

(65) 공개번호

(43) 공개일자

2004년11월04일

10-2005-0109591

2005년11월21일

(30) 우선권주장

10/392,142

2003년03월19일

미국(US)

(73) 특허권자

레이티언 캄파니

미국 02451-1449 매사추세츠주 왈탐 윈터 스트리트 870

(72) 발명자

타이라니, 레자

미국 90292 캘리포니아주 마리나 델 레이 넘버 비42 마리나포인트 드라

이브 13603

달콘조, 래리

미국 90025 로스 앤젤레스 넘버 306 그린필드 애비뉴 1887

드래피우, 데이비드 제이.

미국 90048 캘리포니아주 로스 앤젤레스 와너 드라이브 6425

나카히라, 론 케이.

미국 90620 캘리포니아주 부에나 파크 캔터버리 웨이 8026

(74) 대리인

주성민 장수길

(56) 선행기술조사문헌 EP0532770 A1

KR1020010089316 A

심사관: 김희주

전체 청구항 수 : 총 14 항

#### (54) 초소형 RF 스트립라인 선형위상 필터

(57) 요약

30 내지 100의 범위의 비유전율을 갖는 고유전재료로 제조되는 하부 유전체 기판(30)을 포함하는 RF 필터 회로가 개시된다. 회로 토폴로지를 정의하는 도전체 패턴(26)이 상기 기판의 표면상에 제조된다.

#### 대표도

도 2A

## 특허청구의 범위

### 청구항 1.

스트립라인 RF 필터 회로로서,

30 내지 100의 범위의 비유전율을 갖는 고유전재료로 제조되는 하부 유전체 기판(30);

적어도 30 이상의 비유전율을 갖는 고유전재료로 제조되는 상부 유전체 기판(28);

상기 하부 기판의 상면에 형성된 도전체 패턴(26 및 26') - 상기 도전체 패턴은 필터 회로 패턴, 제1 입출력 포트(16), 및 제2 입출력 포트(18)를 한정하고, 스트립라인 회로를 형성하기 위해 상기 상부 기판 및 상기 하부 기판은 상기 도전체 패턴을 협지(sandwitching)시킴 -; 및

상기 도전체 패턴(26 및 26')을 모두 커버하는 후막 유전체층(60)

을 포함하는 스트립라인 RF 필터 회로.

## 청구항 2.

초소형 고주파 공진회로로서,

공진회로 입력 포트(16) 및 공진회로 출력 포트(18);

적어도 약 30 이상의 비유전율을 갖는 고유전재료로 이루어지는 세라믹 기판(28)상에 후막으로 형성되며, 상기 입력 포트에서 상기 출력 포트까지 상기 공진회로를 통하는 신호 경로를 횡단하도록 위치되고, 제1 접지면과 제2 접지면 사이에 배치되는, 복수의 스트립라인 핑거(12 또는 40); 및

상기 스트립라인 핑거들을 커버하고 분리하는 후막 유전체층(60)

을 포함하는 초소형 고주파 공진회로.

#### 청구항 3.

제1항에 있어서,

상기 기판(28)의 상기 고유전재료는 지르코늄-티타네이트 또는 MgO-CaO-TiO<sub>2</sub>를 포함하는 스트립라인 RF 필터 회로.

#### 청구항 4.

제1항에 있어서,

상기 필터 회로 패턴은 인터디지털 필터회로 토폴로지를 정의하는 스트립라인 RF 필터회로.

### 청구항 5.

제1항에 있어서,

상기 필터는 대역통과 특성을 갖는 스트립라인 RF 필터회로.

#### 청구항 6.

삭제

## 청구항 7.

제2항에 있어서,

상기 스트립라인 핑거 각각은 상기 제1 접지면과 상기 제2 접지면 중 적어도 하나에 전기적으로 접촉하는 초소형 고주파 공진회로.

## 청구항 8.

제2항에 있어서,

상기 스트립라인 핑거 각각은, 상기 세라믹 기판상에 작은 입자의 도전성 금속화 페이스트를 적용하고, 상기 페이스트를 경화시켜 금속화층을 상기 세라믹 기판상에 형성하고, 상기 경화된 페이스트에 의해 형성되는 상기 금속화층의 일부분들을 제거하여 형성되는 초소형 고주파 공진회로.

### 청구항 9.

제2항에 있어서,

상기 유전체층은 후막 저손실 라미네이트층을 형성하는 초소형 고주파 공진회로.

#### 청구항 10.

제7항에 있어서.

상기 제1 접지면과 상기 제2 접지면 중 적어도 하나는 상기 세라믹 기판의 한 표면상의 접지면으로부터 상기 스트립라인 핑거들을 포함하는 반대 표면까지 상기 세라믹 기판의 측벽 주위를 감싸도록 형성되는 랩-어라운드(wrap-around) 부분에 의해 상기 스트립라인 핑거들과 전기적으로 접촉하는 초소형 고주파 공진회로.

## 청구항 11.

초소형 고주파 공진회로를 형성하는 방법으로서,

공진회로 입력 포트(16) 및 공진회로 출력 포트(18)를 형성하는 단계;

적어도 약 30 이상의 비유전율을 가지는 세라믹 기판(28)상의 후막으로 형성되며, 상기 입력 포트에서 상기 출력 포트까지 상기 공진회로를 통하는 신호경로를 횡단하도록 위치되며, 제1 접지면(32)과 제2 접지면(34) 사이에 위치되는 복수의 스트립라인 핑거(12 또는 40)를 형성하는 단계; 및

상기 스트립라인 핑거들을 커버하고 분리하는 후막 유전체층(60)을 형성하는 단계

를 포함하는 초소형 고주파 공진회로 형성방법.

#### 청구항 12.

삭제

## 청구항 13.

제11항에 있어서,

상기 제1 접지면과 상기 제2 접지면 중 적어도 하나와 전기적으로 접촉하도록 상기 스트립라인 핑거 각각을 형성하는 단계를 더 포함하는 초소형 고주파 공진회로 형성방법.

## 청구항 14.

제13항에 있어서,

작은 입자의 도전성 금속화 페이스트를 적용하고, 상기 페이스트를 경화시켜 상기 세라믹 기판상에 금속화층을 형성하고, 상기 경화된 페이스트에 의해 형성되는 금속화층의 일부분들을 제거함으로써 상기 세라믹 기판상에 스트립라인 핑거 각각 을 형성하는 단계를 더 포함하는 초소형 고주파 공진회로 형성방법.

## 청구항 15.

제11항에 있어서.

상기 유전체층은 후막 저손실 라미네이트층을 형성하는 초소형 고주파 공진회로 형성방법.

#### 청구항 16.

제2항에 있어서,

상기 기판(28)의 상기 고유전재료는 지르코늄-티타네이트 또는 MgO-CaO-TiO<sub>2</sub>를 포함하는 초소형 고주파 공진회로.

#### 명세서

#### 배경기술

저렴하고, 저중량이면서도, 고성능인 집적형 필터 뱅크(integrated filter bank)는 예컨대 진보된 채널형 수신기 및 엑시머모듈의 중요 구성성분이다. 이들은 비용을 줄이도록 높은 제조 수율 뿐만 아니라 우수한 성능을 제공하는 소형화된 저가의 필터 기술을 필요로 한다.

현재, 소형의 UHF, RF, 및 마이크로파 회로, 특히 필터의 제조는 집중형(lumped) 커패시터(Cs) 및 인덕터(Ls)를 사용하여 필터를 구축하는 "집중형 소자(lumped element)" 기술에 기초하고 있다. 이러한 필터는 예컨대 각 필터를 튜닝하는데 필요한 튜닝 시간이 길어진다는 점에서 고가이다. 더우기, 이러한 필터는 비교적 큰 회로 궤적(footprint)과 높은 Z-차원의 높이를 필요로 하며, 비교적 중량이 크다.

필터 소형화의 또 다른 접근법으로는, 가상 비유전율  $\epsilon_{\rm r}=24$ 을 갖는 란타넘 알루미네이트(LaAlO $_3$ ) 기판을 활용하는 것이 있다. 이러한 종류의 재료는 과거에는 저온 초전도(LTS: low temperature superconducting)막에만 사용되었다. 이러한 기판들은 고가이며, 높은 변위 밀도를 가지며, 비교적 낮은 유전율(예컨대,  $\epsilon_{\rm r}=<24$ )을 갖는다. 이들은 효율성 측면에서 소형 극저온 냉장 기능이 존재하는 특정한 공간 활용에 제한되었으며, "Compact Forward-Coupled Superconducting Microstrip Filters for Cellular Communication", IEEE Transactions on Applied Superconducting, Volume 5, No. 2, 1995, pages 256-2659에 논의되는 바와 같이, 이러한 분산된 소형 필터들은 상당히 고가임에도 불구하고, 중요한 역할을 하였다.

현재의 멀티칩 마이크로파 모듈(Multi-Chip-Microwave-Modules)은 알루미나(Alumina), 듀로이드(Duroid), 또는 LTCC(Low Temperature Co-fired Ceramics) 재료에 기초한다. 일반적으로, 공지된 후막 금속화의 표면 조직은 도전체 페이스트(conductor paste)의 다소 큰 입자 크기로 인해 그다지 매끄럽지 못하다.

복합형 다층(Complex Multi-layer) 제조기술은 일반적으로 마이크로파/RF 회로 토폴로지의 일부로서, 또는 제어 DC 회로로부터 RF 유전층을 물리적으로 분리하는 수단으로서, 또는 그 모두를 위해, 유전체 라미네이션(lamination)층이라고 하는 유전체 인터포져(interposer)층을 필요로 한다. 또한, 스트립라인 RF/마이크로파 회로는 전기적으로 회로 유전체층의 일부인 라미네이션층을 필요로 하며, 이는 이러한 층이 저손실 탄젠트(높은 Q)와 지속적으로 높은 유전율( $\epsilon_r$ ), 즉 100이상의 유전율를 가져야 한다는 것을 의미한다.

### 발명의 상세한 설명

30 내지 100의 범위의 비유전율을 갖는 고유전체 물질로 제조된 하부 유전체 기판을 포함하는 RF 필터을 설명한다. 회로 토폴로지를 정의하는 유전체 패턴이 기판의 표면에 제조된다.

#### 실시예

본 발명의 일실시예에서, 새로운 종류의 초소형 RF/마이크로파 스트립라인 필터로서, 30 내지 100의 범위의 높은 유전율을 갖는 고유전체 세라믹상에서 구현가능한 복합형 다층 멀티칩 모듈(MCM: Multi-layer Multi-Chip Moudules)을 포함하는 새로운 종류의 초소형 콤팩트형 UHF, RF, 및 마이크로파 회로 및 MIC를 제공한다. 본 발명의 일실시예에서는, 초소형 RF/마이크로파 회로를 달성하기 위하여, 30 내지 100의 범위의 유전율을 갖는 고유전율 세라믹상에 "분산형 소자 (distributed elements)"를 활용한다. 본 발명의 일실시예에서는 고유전율 세라믹상에 이러한 회로를 제조하기 위한 다층후막 공정을 설명한다.

본 발명의 실시예들은 이하의 하나 이상의 특징을 포함한다.

Bessel 및/또는 Gaussian 함수 등의 전달함수를 갖는 종래의 필터와 비교하는 경우 개선된 필터 응답을 나타낼 수 있는, 스트립라인 선형 위상 대역통과(BP) 필터를 위한 새로운 설계;

30 내지 100의 범위의 유전율을 갖는 적합한 고유전체 세라믹 재료의 확인 및 적용;

스트립라인 회로 및 기타의 스트립라인 회로의 제조에 필요로 되는 새로운 후막 저손실 라미네이션층 기술을 제공할 수 있는, 높은 도전성의 새로운 페이스트 또는 잉크, 새로운 레이저 비어(via), 및 새로운 레이저 윈도우 기술을 포함하는 정교한 후막 기술의 개발;

스트립라인 회로 기술에 적합한 랩-어라운드 접지 설계.

높은 유전율 기판을 사용하는 경우에 마이크로스트립라인/스트립라인의 길이 및 폭 모두가 생성되므로, 결과적인 선폭의 감소는 회로의 마이크로파 손실(삽입 손실)을 증가시키게 된다는 것은 일반적으로 잘못된 개념이다. 대부분의 경우, 길이 의 감소는 도전체 폭의 감소와 관련되는 불요한 손실을 보상한다.  $50\ \Omega$  마이크로스트립 라인의 길이 $(1/4N_g)$ ® 6 Ghz)의 성능을 세 개의 다른 기판에서, 약 30 내지 100의 범위인  $\epsilon_r$ 을 갖는 고유전율 재료, 일실시예로 Countis Laboratories의 CD-40이라는 제품인 지르코늄-티타네이트 고유전율 세라믹 복합체로 구성된 세라믹으로 시뮬레이션하였다. 표 1은, 이러한 세라믹(즉,  $\epsilon_r$  =39), 알루미나( $\epsilon_r$  =9.9), 및 듀로이드( $\epsilon_r$  =2.99)를 사용한 필터 소자를 비교하는 시뮬레이션 결과를 나타내는 것으로, 이러한 시뮬레이션 결과를 요약하면, 고유전 재료가 높은 도전 손실(6 Minch)을 갖더라도, 그 총 선로손실(6 입 손실)은 다른 두 선로와 거의 동일하다는 것을 나타낸다. 이는, 적어도 부분적으로는, 예컨대, 듀로이드 선로와 비교할 때 고유전 선로의 길이가 6 3배로 감소하기 때문이다. 표에서는, 스트립라인이 아니라 마이크로스트립 라인에서 수행된 시뮬레이션 결과를 나타낸다. 마이크로스트립 라인에서는 전파 모드가 실제의 TEM이 아니고(비균질(inhomogeneous) 매질, 즉 공기와의 인터페이스), auasi-TEM 일 뿐이므로,  $\epsilon_r$  eff는  $\epsilon_r$  과는 다르다. 그러나, 스트립라인에서는, 매질이 균질(homogeneous)하여 실제 TEM 필드를 지원하므로,  $\epsilon_r$  이 그 특성을 설명할 수 있다. 가장자리 필드 효과(fringing field effect)를 고려한 유효 유전율의 범위에 대한 필요성이 있다.  $\epsilon_r$  과  $\epsilon_r$  eff 의 차이는 소위 "필링 인수(filling factor)"에 의해 결정된다. 듀로이드의 금속 두께는 6 4 mil 로, 다른 두개의 기판에 대해서는 6 2 mil 로 시뮬레이션 하였다.

| 기판 재료          | W<br>mil | W/H  | ε <sub>r eff</sub> | 유전손실<br>dB/inch |        | 총 손실<br>dB/inch | _   | 선로 손실<br>@ 5GHz |

|----------------|----------|------|--------------------|-----------------|--------|-----------------|-----|-----------------|

| ZT-39 50 mil   | 9        | 0.18 | 23.3               | 0.03            | 0.2    | 0.23            | 122 | 0.028 dB        |

| Alumina 25 mil | 23.8     | 0.95 | 6.7                | 0.003           | 0.1    | 0.1             | 228 | 0.022 dB        |

| Duroid 25 mil  | 62       | 2.5  | 2.4                | 0.016           | 0.04** | 0.06            | 378 | 0.022 dB        |

본 발명의 일실시예는, 예컨대 선형위상 대역통과 필터에 사용될 수도 있는 공진자(resonator)의 새로운 설계에 관한 것으로서, 더욱 자세하게는, 고유전 세라믹 기판상에서 이러한 회로 및 필터를 제조하는 것에 관한 것이다. 종래의 필터는, 신호를 변형시킬 수도 있는, 비선형 위상-주파수 특성을 갖는다. 선형 위상 필터, 또는 소위 일정한 군지연 필터(constant group delay filter)는 비교적 선형인 주파수-위상 변화를 가지므로, 신호를 크게 변형시키지는 않는다. 일실시예에서는, Gaussian 또는 Bessel-Thompson 전달함수에 기초로 하는 종래의 접근법 보다 우수한 필터 성능을 제공할 수 있다. 일실시예에서는, 필터의 통과대역내에 매우 선형인 위상 응답을 유지하는 한편 매우 예리한 감쇄 스커트(attenuation skirts)를 갖는 +/- 0.5 도의 선형위상 전달함수의 필터를 제조할 수 있다. 일실시예에서, 필터 토폴로지는 예컨대 7차의 탭핑된 인터디지털 설계일 수도 있다.

일례로서, 본 발명의 일실시예에 따른 선형위상 인터디지털 필터는, 마이크로칩에 집적되는 마이크로파 수신기용으로, 무선 주파수 집적 필터(RFIF: Radio Frequency Integrated Filter) 마이크로파 집적 회로(MIC: Microwave Integrated Circuit)에서 사용될 수 있다. 이 필터는 1400 MHz 주위의 중심 주파수를 가지며, 100 MHz 대역폭에서 +/- 3 도 (degree)의 엄격한 위상 선형성으로 설계되었다. 일례의 필터는 작은 회로 궤적(0.34"x0.34"x0.05")를 가지며, 낮은 제조비용을 갖는다.

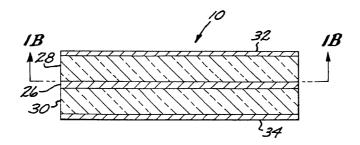

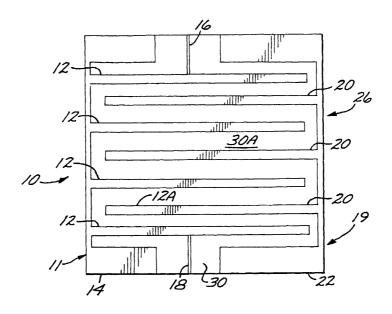

도 1A 및 도 1B를 참조하면, 본 발명의 양태에 따른 스트립라인 필터회로(10)의 바람직한 일실시예가 도시되어 있다. 도 1A는 필터 구조의 도해식의 측단면도로서, 상부 기판 및 하부 기판(28, 30)을 구비하며, 하부 기판(30)의 상부 표면(30A)에는 스트립라인 도전체 패턴(26)이 형성되어 있다. 기판(28, 30)은 30 내지 100의  $\epsilon_r$ 을 갖는 지르코늄-티타네이트 등의 높은 유전율을 갖는 재료로 제조된다. 이러한 목적의 기타의 재료로는,  $MgO-CaO-TiO_2$ 를 포함한다. 바람직한 일실시예에 있어서, 기판(28, 30)은 25 mils 의 공칭 두께를 갖는다.

도 1B는 상부 기판(28)을 도 1A의 1B-1B 라인으로 도시된 바와 같이 제거한, 기판의 개략 평면도이다. 도 1B는 이러한 본 발명의 일실시예의 도전체 패턴(26)을 나타낸다. 패턴(26)은 제1 패턴부(11) 및 제2 패턴부(19)를 포함한다. 필터 회로 (10)는 입출력(I/O) 포트(16) 및 입출력 포트(18)을 갖는다. 제1 패턴부(11)는 랩 어라운드 접지면부(22)에 연결된 복수의 횡단 스트립라인 핑거(12)를 포함한다. 제1 패턴부(11)의 스트립라인 핑거(12)는 제2 패턴부(19)의 스트립라인 핑거(20)에 인터리브(interleave)된다. 도전성 외부층(32, 34)이 기판(28, 30)의 외측표면에 형성되어 필터회로 접지면으로 기능한다.

제1 패턴부(11) 및 제2 패턴부(19)는, 예컨대, DuPont 사의 QG150과 같은, 정밀한 입자의 골드 페이스트를 사용한 공지된 후막 착화(deposition)기법을 활용하여 형성될 수도 있다. 당업계에 공지된 바와 같이, 하부 기판(30)에 페이스트를 적용하고, 페이스트를 셋팅하도록 가열한 후, 예컨대, 포토리소그래픽 기법을 사용하여 경화된 페이스트를 에칭하여 핑거

(12, 20)와 접지면부(14, 22)를 형성할 수도 있다. 다른 방법으로, 2 단계 공정으로 기판(30)의 양표면에 페이스트를 적용하여 일측에는 핑거를 타측에는 접지면을 형성하고, 또한 비어 연결부(48, 50)를 수용하기 위해 개구를 형성하도록 에칭할 수도 있다.

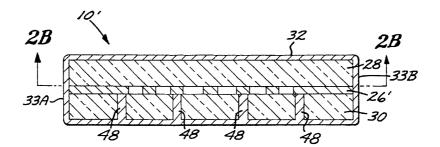

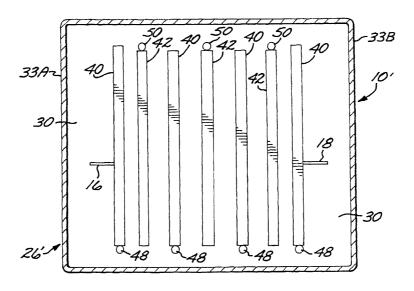

도 2A 및 도 2B를 참조하면, 스트립라인 필터회로(10')의 대체 실시예가 도시되어 있다. 도 1의 실시예와 같이, 회로(10')는 상부 고유전체 기판(28) 및 하부 고유전체 기판(30)을 포함한다. 회로(10')는, 도 2A에 도시된 바와 같이 비어(48)를 통해 접지면(34)에 각각 연결되는 복수의 횡단 스트립라인 핑거(40) 및 비어 연결부(50)를 통해 접지면(34)에 각각 연결되는 복수의 인터리브형 횡단 스트립라인 핑거(42)를 포함하는, 하부 기판(30)의 상부 표면에 형성된 스트립라인 도전체 패턴 (26')을 포함한다. 외측 접지면부, 예컨대, 도전체층(33A, 33B)이 기판 어셈블리의 측면 표면에 형성된다.

도 1A 내지 2B의 실시예에서, 스트립라인 RF 필터 회로를 나타내는 한편, 본 발명의 양태에 따라서 마이크로스트립 RF 필터회로가 또한 제조될 수 있다. 이러한 경우, 상부 기판(28)이 생략된다. 결과의 마이크로스트립 회로는 종래의 마이크로스트립 회로에 비하여 크기에 있어서 장점을 제공하지만, 스트립라인 실시예 만큼 크게 초소형화의 이익을 제공하지는 않게 된다.

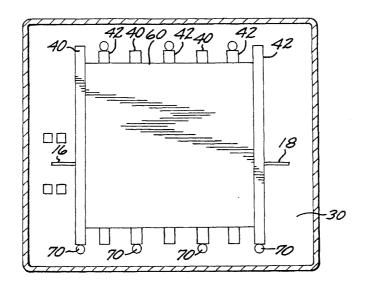

통상, 스트립라인 RF/마이크로파 회로는, 전기적으로 회로 유전층의 일부인 라미네이션층을 활용하는데, 이러한 층은 낮은 손실 탄젠트(high Q), 일정한 유전율을 가져야 함을 의미한다. 유전성 페이스트 또는 잉크는 고유전 세라믹 재료에 적용하기에 적합한 것으로 확인되었다. 도 3을 참조하면, 도 1B 내지 도 2B에 도시된 것과 같은 종류의 기판(30)이 도시되어 있는데, 그 위에는, 표면에 접지면(32)을 포함하는 세라믹 상부 기판층(28)이 유전체층(60) 및 함께 라미네이트된 전체 어 셈블리 상에 위치되는 때에, 예컨대 Dupont QM44 로 이루어지는 높은 Q의 유전성 페이스트의 층(60)이 핑거(40, 42)에 대하여 적용되어 라미네이트층을 형성한다. 도 1A 및 도 1B에 따른 일실시예를 나타내는 도 3에 도시된 바와 같이, 유전 체층(60)은 실질적으로 모든 스트립라인 핑거(40, 42)를 커버해야 하고, 입력(16) 및 출력(18)에 연결된 스트립라인 핑거(40) 사이에 들어가야 한다. 마찬가지로, 스트립라인 핑거(12 및 20)의 동일한 부분들은 실질적으로 유전체 페이스트층 (60)으로 커버되어야 한다.

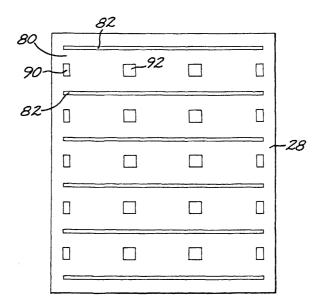

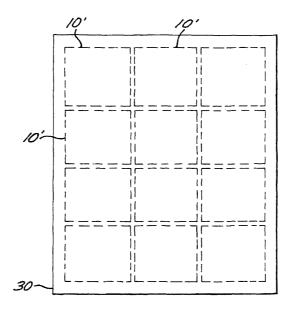

도 4 및 도 5를 참조하면, 본 발명의 뱃치(batch) 제조 실시예의 방법을 볼 수 있다. 도 4에 도시된 바와 같이, 하부 세라믹기판(30)은, 그 위에 복수의 회로 소자들(10'), 예컨대, 에칭 또는 레이저 절삭으로 세라믹 재료의 부서지기 쉬운 성질을 고려한 임의의 적합한 수단에 의해 기판(30)을 통해 절단된 비어를 포함하여, 각각 도 2에 도시된 바와 같은 패턴(26')을 포함하는 복수의 회로 소자들을 형성할 수도 있다. 도 5는 유전체 페이스트(60)를 적용한 후 하부 기판(30) 상에 위치되며, 예컨대 유전체 뿐만 아니라 접착제로서 경화시키는 경우 유전체 페이스트(60)를 활용하여 하부 기판(30)에 라미네이트 되는 상부 기판(28)을 나타낸다. 상부 기판(28)은 관통하여 절단된 복수의 윈도우(90 및 92), 및 전술한 조립 과정중에 상부기판(80)을 하부 기판(30)과 정렬시키기 위한 복수의 정렬 슬릿(82)을 갖는다. 그 후, 상부 기판(28) 및 하부 기판(30)은 적절히 재단되어, 복수의 필터 소자들로 분리되며, 윈도우(90) 및 윈도우(92)의 절반은 각각의 도전체 패턴(26')으로 연결부들이 만들어질 수 있는 입출력 개구들을 정의한다.

본 발명의 일실시예에 따르면, 좀 더 매끄러운 표면을 제공하기 위해서 뿐만 아니라, 결과적으로는 금속 도전성에서 두 배의 개선 요소를 제공하여, RF 회로의 회로 손실을 거의 두 배 줄이도록 도전체 페이스트가 선택되었다. 기타의 관련 처리 단계들로서는, 후막의 퍼니스 온도 프로파일의 최적화를 포함한다. 일례의 프로파일로는, 30분만에 실온에서 875°C까지 변화하며, 30분만에 실온으로 하강하는 선형의 프로파일을 포함할 수도 있다. 이러한 최적화된 온도 프로파일은 도전체 페이스트와 함께 고유전체 세라믹을 활용할 수 있도록 해준다.

바람직하게는, 고유전율 세라믹 기판 및 라미네이션층 양측에 대하여 레이저 가공된 비어 홀 기술이 채용되어, 접지-대접지의 배선을 제공하거나 금속화층 사이의 수직 배선을 제공한다. 레이저 드릴 기법은 고유전체 세라믹 기판에 윈도우 개구를 절단하기 위하여 개발되었으며, 예컨대, 랩-어라운드 접지 스트립라인 필터를 뱃치 모드 방식으로 제조하기 위해 사용된다. 일례의 레이저 드릴 공정은 이하와 같다. 적합한 펄스 전력 및 고유전체 세라믹에 적합한 듀티 사이클을 위하여  $CO_2$  레이저가 프로그래밍 된다. 폴리 비닐 아세테이트(PVA) 또는 기타의 적합한 수용성 코팅으로 기판이 코팅되어 레이저 슬래그(slag)로부터 기판을 보호한다. 코팅된 기판을 10분간  $90^{\circ}$ C에서 베이킹한다. 다음, 기판을 레이저에 탑재하고, 홀 패턴이 레이저 가공된다. 그 후, 기판을 탈이온화수(DI water)에 담그어, PVA를 제거하고, 블로우-드라이(blow-dry)를 행한다.

본 발명의 일실시예에 있어서, 충(60)을 형성하기 위한 처리와 함께 저손실 유전체 페이스트 또는 잉크가 활용된다. 이러한 저손실 유전체 잉크는 고유전체 세라믹 재료에 적용함에 있어 적합하다.

예컨대, L-밴드 대역통과 필터와 같은 초소형 필터를 구현하기 위한 본 발명의 실시예에서는, Countis Laboratory사의 CD-40 및 CD-14와 같은 저가의 후막 처리를 허용하는 일종의 고유전율 세라믹의 사용을 통해 저비용 및 소형의 회로괘적을 제공한다.

본 발명의 일실시예에 따르면, 고유전율 세라믹을 활용함으로써, 스트립라인을 사용하여 필터 소자의 초소형화를 가능하게 한다. 또한, 마이크로스트립 필터 또는 기타의 회로 성분의 제조를 위해 재료들이 선택된다.

따라서, 본 발명의 바람직한 실시예는, 초소형 고주파수 공진 회로; 및 공진회로 입력과 공진회로 출력과 적어도 약 30의유전율을 가지는 세라믹 기판상에 후막으로 형성되며, 입력으로부터 출력까지 공진 회로를 통한 신호 경로를 횡단하도록위치되며, 제1 접지면과 제2 접지면사이에 위치되는 복수의 도전체 핑거를 포함하는 장치를 만드는 방법을 포함한다. 또한, 본 장치는, 스트립라인 핑거 각각이 제1 접지면 및 제2 접지면 중 적어도 하나에 전기적으로 접촉하도록 하면서, 스트립라인 핑거들을 커버하고, 분리시키는 후막 유전체층을 구비할 수도 있다. 스트립라인 핑거의 각각은, 작은 입자의 도전성 금속화 페이스트(metallization paste)를 적용하고, 페이스트를 경화하여 세라믹 기판상에 금속화층을 형성하고, 경화된 페이스트에 의해 형성되는 금속화층의 위치를 제거함으로써 세라믹 기판상에 형성될 수도 있다. 유전체 라이네이션층은 후막 저손실 라미네이트층을 형성할 수도 있다. 제1 접지면 및 제2 접지면 중 적어도 하나가, 세라믹 기판의 한 표면상의 접지면으로부터 스트립라인 핑거를 포함하는 반대 표면으로 세라믹 기판의 측벽 주위를 감싸도록 형성되는 랩-어라운드 부분에 의해 스트립라인 핑거들에 전기적으로 접촉될 수도 있다.

전술한 실시예들은 단지 본 발명의 원리를 나타낼 수도 있는 가능한 특정 실시예들의 예시일 뿐임을 이해할 것이다. 이러한 원리에 따라서, 당업자라면 본 발명의 개념과 범주를 일탈하지 않고서, 기타의 배치들이 용이하게 고안될 수도 있다.

#### 도면의 간단한 설명

본 발명의 기타의 특징 및 장점들은 첨부된 도면에 도시된 바와 같이, 이하의 그 바람직한 실시예의 설명으로부터 더욱 명확해질 것이다.

도 1A는 본 발명에 따른 스트립라인 필터회로의 실시예를 나타낸 개략 단면도.

도 1B는 랩-어라운드 접지 구조를 갖는 일실시예의 인터디지털 회로패턴을 도시하기 위해 상부 기판을 제거하여 나타낸, 도 1A의 회로의 개략 평면도.

도 2A는 본 발명에 따른 스트립라인 필터의 대체실시예를 나타낸 개략 단면도.

도 2B는 상부 기판을 제거하여 나타낸 도 2A의 회로의 개략 평면도로서, 인터디지털 스트립라인 필터의 대체실시예의 일부분을 나타낸 개략 평면도.

도 3B는 도 2B의 실시예에 후막 고유전체 라미네이트층을 적용한 것을 나타낸 도면.

도 4는 도 1A 내지 도 1B의 실시예의 각각에 따른 복수의 인터디지털 스트립라인 회로성분을 포함하는 하부 기판(bottom substrate)을 나타낸 도면.

도 5는 본 발명의 일실시예에 따른 기판을 나타낸 도면.

#### 도면

# 도면1A

도면1B

도면2A

# 도면2B

도면3

# 도면4

# 도면5