(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3611511号

(P3611511)

(45) 発行日 平成17年1月19日(2005.1.19)

(24) 登録日 平成16年10月29日(2004.10.29)

(51) Int.C1.<sup>7</sup>

F 1

|           |                |

|-----------|----------------|

| GO9G 3/36 | GO9G 3/36      |

| GO9G 3/20 | GO9G 3/20 631B |

| GO9G 3/30 | GO9G 3/20 633G |

| GO9G 5/00 | GO9G 3/20 660V |

| GO9G 5/36 | GO9G 3/20 680S |

請求項の数 7 (全 16 頁) 最終頁に続く

(21) 出願番号 特願2000-293760 (P2000-293760)

(22) 出願日 平成12年9月27日 (2000.9.27)

(65) 公開番号 特開2002-108268 (P2002-108268A)

(43) 公開日 平成14年4月10日 (2002.4.10)

審査請求日 平成15年10月16日 (2003.10.16)

早期審査対象出願

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目2番3号

(74) 代理人 100083840

弁理士 前田 実

(72) 発明者 中谷 英彦

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72) 発明者 杉山 和宏

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 濱本 祐広

最終頁に続く

(54) 【発明の名称】マトリクス型表示装置及び画像データ表示方法並びに携帯情報端末装置

## (57) 【特許請求の範囲】

## 【請求項 1】

外部から入力される画像データをフレーム単位で記憶可能なグラフィックスメモリと、前記外部から入力される画像データのフレーム毎の当該グラフィックスメモリへの書き完了時に書き完了信号を出力するメモリデータ書き制御回路と、

前記書き完了信号とフレーム同期信号とに基づいて、読み出開始信号を出力する同期化回路と、

前記読み出開始信号に基づいて、前記グラフィックスメモリに記憶された画像データをフレーム単位で読み出すデータ読み出制御回路と、

前記グラフィックスメモリから読み出された画像データをフレーム単位で記憶するフレームメモリと、

自回路内で発生するクロック信号に基づいて、前記フレームメモリに記憶された画像データを読み出すと共に、複数の信号線を駆動するための制御信号を出力し、かつ、前記フレーム同期信号を出力する信号電極駆動回路と、

前記フレーム同期信号に基づいて、複数の走査線を駆動するための制御信号を出力する走査電極駆動回路と、

前記複数の信号線と、当該信号線と直交する方向に配線された上記複数の走査線との交点に画素部が設けられた表示パネルと

を備えるマトリクス型表示装置。

## 【請求項 2】

10

フレーム同期信号を所定量遅延した読出同期信号を出力する遅延回路を備え、同期化回路は、書込完了信号と当該読出同期信号とに基づいて、読出開始信号を出力することを特徴とする請求項1に記載のマトリクス型表示装置。

【請求項3】

信号電極駆動回路は、自回路内で発生するクロック信号に基づいて、さらにライン同期信号を出力し、

走査電極駆動回路は、当該ライン同期信号とフレーム同期信号とに基づいて、複数の走査線を駆動するための制御信号を出力し、

遅延回路は、前記ライン同期信号に基づいて、前記フレーム同期信号の遅延量を設定することを特徴とする請求項2に記載のマトリクス型表示装置。 10

【請求項4】

同期化回路は、書込完了信号を受信した後、初めてフレーム同期信号、又は読出同期信号が入力された場合に読出開始信号を出力すること

を特徴とする請求項1から3のいずれか1項に記載のマトリクス型表示装置。

【請求項5】

読出同期信号の遅延量は、

書込完了信号出力後において、

初めてフレーム同期信号が入力されるタイミングから、

当該タイミングにおいてフレームメモリに記憶されていたフレームの画像データを、当該フレームメモリから読み出す処理の完了後のタイミングまでの期間であること 20

を特徴とする請求項2から4のいずれか1項に記載のマトリクス型表示装置。

【請求項6】

外部から入力される画像データをフレーム単位で記憶する第1の記憶ステップと、

上記外部から入力される画像データのフレーム毎の書込完了時に書込完了信号を出力する書込完了ステップと、

上記書込完了信号とフレーム同期信号とに基づいて、読出開始信号を出力する読出開始ステップと、

上記読出開始信号に基づいて、第1の記憶ステップで記憶された画像データをフレーム単位で読み出す読み出しステップと、

上記読み出しステップにて読み出された画像データをフレーム単位で記憶する第2の記憶ステップと、 30

クロック信号を発生し、当該クロック信号に基づいて、前記第2の記憶ステップで記憶された画像データを読み出すと共に、複数の信号線を駆動するための制御信号を出力し、かつ、上記フレーム同期信号を出力する信号電極駆動ステップと、

上記フレーム同期信号に基づいて、複数の走査線を駆動するための制御信号を出力する走査電極駆動ステップと、

前記複数の信号線と、当該信号線と直交する方向に配線された上記複数の走査線との交点に画素部が設けられた表示パネルに前記信号電極駆動ステップにて読み出された画像データを表示する表示ステップと

を備える画像データ表示方法。 40

【請求項7】

請求項1から5のいずれか1項に記載のマトリクス型表示装置を備える携帯情報端末装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、マトリクス状に配列された交点に画素部が設けられたマトリクス型液晶パネルやマトリクス型蛍光表示パネル等の表示パネルを用いて画像を表示させる際の表示装置に係わり、特に、動画像を表示する携帯電話装置等の携帯情報端末装置の表示部に用いられるマトリクス型表示装置に関する。 50

**【0002】****【従来の技術】**

従来から、形態電話装置や携帯情報端末装置等の可搬型情報処理装置には、マトリクス型の液晶等を用いた表示装置が使用されている。

例えば、近年の携帯電話では、その基本的な要求事項として、所謂待ち受け画面を表示した状態で数百時間のバッテリー駆動時間を確保することが要求される。そのため、携帯電話に使用されるマトリクス型表示装置には、静止画表示時の画像データ転送を必要無くして電力消費を少なくするために、画像データの入力バッファ的な役割となるグラフィックスメモリとは別に、液晶表示パネルを駆動するための回路にフレームメモリが内蔵されることが多いになっている。つまり、静止画表示時には、液晶表示パネルを駆動するための回路にデータを転送して電力消費してしまうことがないようにしてあり、そのように構成された低消費電力の液晶マトリクス型表示装置が近年の携帯電話に数多く用いられている。10

**【0003】**

従来の携帯電話用の液晶表示パネルとしては、上記したようにフレームメモリを内蔵させ、さらに低消費電力で低コストのSTN液晶パネルが用いられることが多かった。しかし、今後はIMT-2000規格に対応する動画配信のサービスが始まると共に、TV電話機能が付加されると予想される。その場合には、動画表示が必要になり、従来のSTN(超ねじれ復屈折型)液晶パネルでは、応答速度が不足するため、動画表示対応の携帯電話用の表示パネルに切り換えられると予想される。具体的には、応答速度が速く、画質の良いTFT(Thin Film Transistor)液晶パネルやMIM(Metal Insulator Metal)液晶パネルなどのアクティブマトリクス型液晶パネルが主に用いられる予想される。20

**【0004】**

一般的に、今後の使用が予想されるアクティブマトリクス型液晶パネルは、従来から用いられたSTN液晶パネルほど低消費電力ではない。しかし、近年では携帯電話として使用可能レベルまで低消費電力化されたものが開発されている。

**【0005】**

一方、応答速度の比較的遅いとされて今後の使用が微妙となるSTN液晶パネルについても、応答速度を速めて動画表示を可能にする高速応答STN液晶パネルが開発されている。30

また、応答速度が液晶パネルより遙かに速く、画素部分自体を発光させる方式で表示する有機EL表示パネルは、自発光型の表示パネルであるため、バックライトやフロントライト等の照明が不要となって消費電力もそれほど多くならない。従って、有機EL表示パネルは、バックライト等の照明の分の薄型軽量化が可能になるため、携帯電話用の表示パネルとして適していると考えられる。

**【0006】**

上記した各表示パネルの一般的な応答速度としては、携帯電話に従来から用いられているSTN液晶パネルで、300~500msec程度であり、TFT等のアクティブマトリクス型液晶パネルで30~50msec程度であり、高速応答型のSTN液晶パネルで70~80msec程度であり、有機ELパネルは数μsec程度のオーダーである。40

**【0007】**

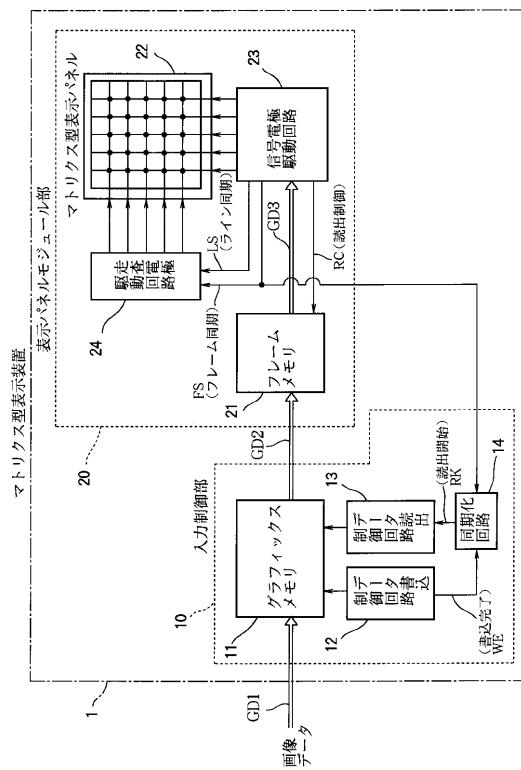

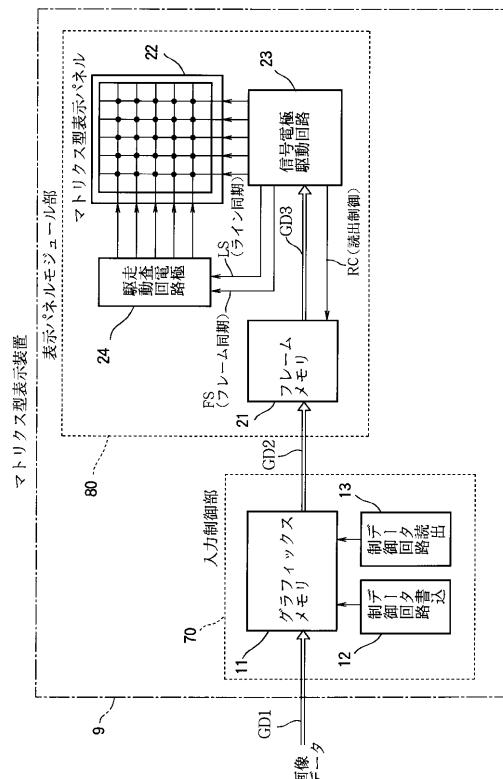

図9は、従来のフレームメモリ内蔵のマトリクス型表示装置の構成を示すブロック図である。

図9のマトリクス型表示装置9では、70は、入力する画像データのタイミング等を制御する入力制御部であり、80は、入力された画像データを表示する表示パネルモジュール部である。

入力制御部70は、入力する画像データを少なくともフレーム単位で一時的に記憶できるグラフィックスメモリ11と、アドレスバス、データバス、および制御線等を備えるマイクロプロセッサ等から構成され、入力した画像データをグラフィックスメモリ11に書き込む際の制御を行うデータ書き込み制御部12と、グラフィックスメモリ11に一時記憶され50

た画像データを読み出して表示パネルモジュール部 80 に転送するデータ読出制御回路 13 を有している。

【0008】

表示パネルモジュール部 80 は、入力制御部 70 から転送されてきた画像データを少なくともフレーム単位で記憶できるフレームメモリ 21 と、複数の信号線が縦列に平行配線され、複数の走査線が横列に平行配線されることによりマトリクス状に配列された交点に画素部が設けられている表示パネル 22 と、表示パネル 22 に画像を表示するための基準となるクロック信号を発生し、そのクロック信号に基づいて、フレームメモリ 21 から画像データを読み出し、表示パネル 22 の信号線を駆動するための制御信号を発生すると共に、表示パネル 22 のフレーム同期信号およびライン同期信号を発生する信号電極駆動回路 23 と、フレーム同期信号およびライン同期信号に基づいて、表示パネル 22 の走査線を駆動するための制御信号を発生する走査電極駆動回路 24 を有している。また、表示パネル 22 は、例えば、液晶表示素子がマトリクス状に配置された液晶表示パネルである。

【0009】

外部からマトリクス型表示装置 9 に入力してグラフィックメモリ 11 に書き込まれる画像データが GD1 であり、グラフィックスメモリ 11 から読み出されてフレームメモリ 21 に転送される画像データが GD2 であり、フレームメモリ 21 から読み出されて信号電極駆動回路 23 に入力する画像データが GD3 である。また、信号電極駆動回路 23 から走査電極駆動回路 24 に出力されるフレーム同期信号が FS であり、同様に信号電極駆動回路 23 から走査電極駆動回路 24 に出力されるライン同期信号が LS であり、同様に信号電極駆動回路 23 からフレームメモリ 21 の記憶内容を読み出すために出力される読出制御信号が RC である。

【0010】

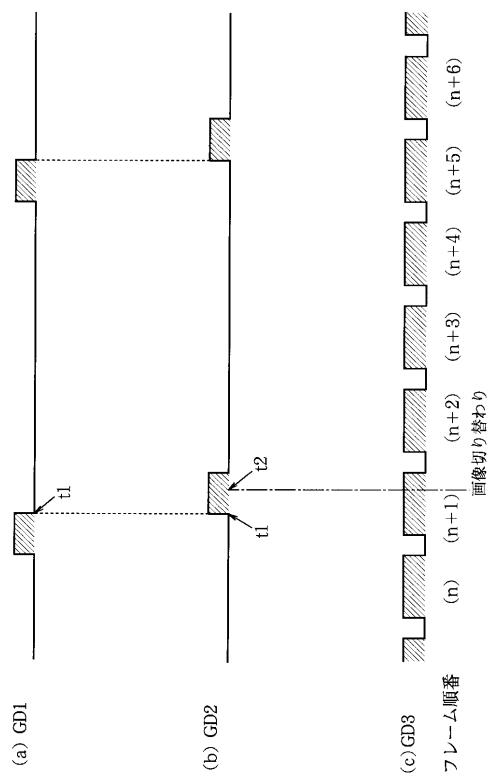

マトリクス型表示装置 9 の動作については、図 9 に加えて、図 10 の画像データのタイミングチャートを参照して以下に説明する。

通信機能等により外部からマトリクス型表示装置 9 の入力制御部 70 に入力した画像データ GD1 は、データ書込制御回路 12 により制御されて一旦グラフィックスメモリ 11 に記憶される。図 10 (a) に示したように、グラフィックスメモリ 11 への画像データ GD1 の記憶処理がタイミング t1 で終了すると、図 10 (b) に示したように、t1 のタイミングですぐにデータ読出制御回路 13 によってその画像データ GD1 は読み出され、画像データ GD2 としてフレームメモリ 21 に転送される。

【0011】

一方、表示パネルモジュール部 80 では、信号電極駆動回路 23 により、図 10 (c) に示したように、独自に発生されたクロック信号に基づくりフレッシュサイクルで、フレームメモリ 21 に記憶された画像データ GD2 が、画像データ GD3 として周期的に読み出されて、信号電極駆動回路 23 に入力される。信号電極駆動回路 23 では、独自のクロックに基づいて、フレームメモリ 21 に向けて読み出し制御信号 RC を生成して送出し、マトリクス型表示パネル 22 の各信号電極に対する制御信号を生成して送出すると共に、フレーム同期信号 FS およびライン同期信号 LS を生成して走査電極駆動回路 24 に送出する。走査電極駆動回路 24 では、フレーム同期信号 FS およびライン同期信号 LS に基づいて、マトリクス型表示パネル 22 の走査電極に対する制御信号を生成して送出する。

【0012】

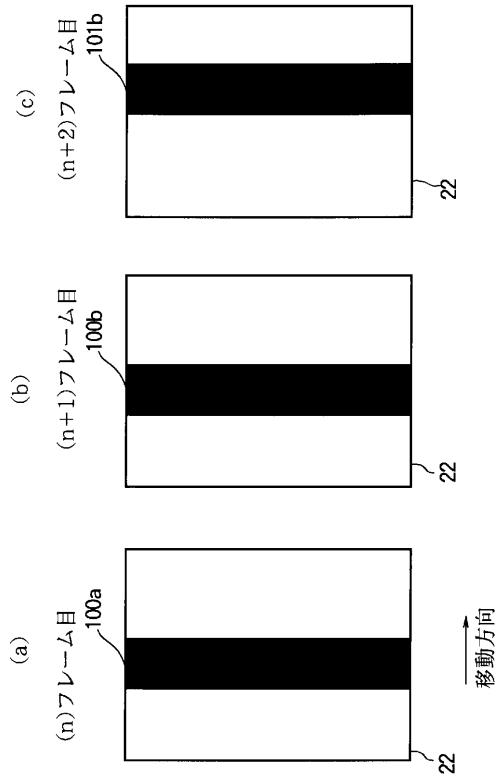

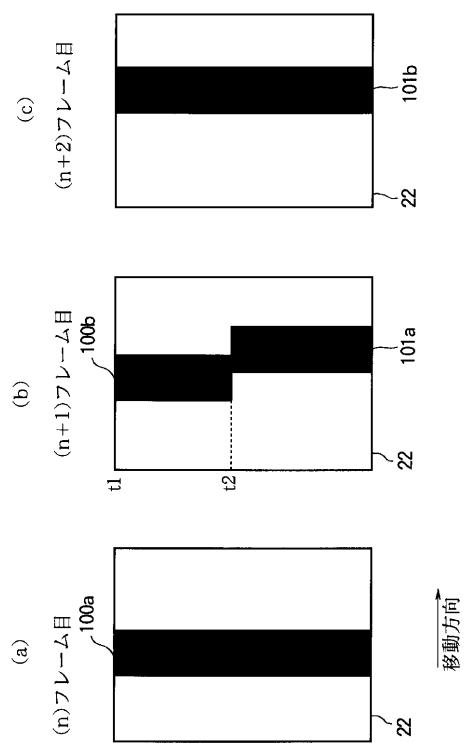

図 11 (a) ~ (c) は、マトリクス型表示装置 9 のマトリクス型表示パネル 22 上で、左端から右端に向かって移動する太い縦線を示した図である。

なお、図 10 (c) に示した表示パネル 22 のフレーム周波数は、一般的には毎秒 60 フレーム程度であり、グラフィックスメモリ 11 からフレームメモリ 21 へのデータ転送の頻度の数倍である。また、画像データ GD2 のデータ転送は、マトリクス型表示パネル 22 へフレームメモリ 21 から読み出す画像データ GD3 とは非同期に行われる。図 10 (c) に示したように、フレームメモリ 21 から読み出された 1 フレーム毎の画像データ GD3 を、早い方から順に (n) フレーム目、(n + 1) フレーム目、(n + 2) フレーム

目とすると、まず、(n)フレーム目の縦線100aの画像は、図11(a)のように縦に連続して表示される。

【0013】

次に、画像データGD2とGD3は同期していないので、図10(c)の(n+1)フレーム目のタイミングt2では、読み出される画像データ信号GD3に、書込む画像データ信号GD2が追いつき、その後で追い越してしまう。すると、図11(b)に示したように、(n+1)フレーム目の縦線100bの画像は、垂直走査方向のタイミングt2から下が、新たに書込みされた縦線101aとなり、縦線が連続しないで段差ができてしまう。この縦線の段差は、図11(c)に示した(n+2)フレーム目では、新たに書込みされた縦線101bのみとなり、段差は無くなる。

10

【0014】

このように、図9に示した従来のマトリクス型表示装置9では、マトリクス型表示パネル22のフレーム周期と非同期に画像データGD2がグラフィックスメモリ11からフレームメモリ21に転送されるため、表示パネル22に表示される画像の1フレームの途中で次の1フレームの画像に切り替わる事態が発生する。

【0015】

このような事態は、マトリクス型表示パネル22として応答速度の遅い従来からのSTN液晶パネルを使用している場合にも発生する。しかし、従来のSTN液晶パネルの場合には、液晶の応答速度が表示パネルにおける1フレームの画像データ転送速度と比較して十分大きいため、動きのある動画像を表示させようとして1フレーム毎の映像データを転送しても液晶側の応答が間に合わず十分な表示ができなくなるという問題があり、そのため、液晶表示パネルの1フレームを表示する途中で次の画像が転送されることにより画像に縦の段差が発生しても、その前に表示できなくなっていることが多かったため、比較的目につきにくく放置されていた。

20

【0016】

【発明が解決しようとする課題】

しかしながら、上記したように動画像を表示させるために、例えば、アクティブマトリクス型液晶パネル、高速応答STNパネル、あるいは、有機ELパネル等の応答速度の比較的速い表示パネルを携帯電話装置へ使用した場合には、図11(b)に示した横方向に動きのある画像データの映像について、応答性の点では問題無くなることから、1フレームの途中で次の画像に切り替わり、画像に縦の段差が発生するという問題が顕在化してしまう。その結果、表示される動画像の品位が著しく損われてしまう。従って、応答速度が比較的速い表示パネルを携帯電話等に使用する場合には、画像に縦の段差が発生するという問題が放置できない問題となる。

30

【0017】

本発明は、以上のような問題点を解決するためになされたものであって、動画像の品位を損なわず、なめらかな動画像を表示できる携帯情報端末装置用のマトリクス型表示装置を提供することを目的とする。

【0018】

【課題を解決するための手段】

40

この発明に係るマトリクス型表示装置は、

外部から入力される画像データをフレーム単位で記憶可能なグラフィックスメモリと、外部から入力される画像データのフレーム毎の当該グラフィックスメモリへの書込完了時に書込完了信号を出力するメモリデータ書込制御回路と、

書込完了信号とフレーム同期信号とに基づいて、読み出開始信号を出力する同期化回路と、読み出開始信号に基づいて、グラフィックスメモリに記憶された画像データをフレーム単位で読み出すデータ読み出制御回路と、

グラフィックスメモリから読み出された画像データをフレーム単位で記憶するフレームメモリと、

自回路内で発生するクロック信号に基づいて、前記フレームメモリに記憶された画像データ

50

タを読み出すと共に、複数の信号線を駆動するための制御信号を出力し、かつ、フレーム同期信号を出力する信号電極駆動回路と、

フレーム同期信号に基づいて、複数の走査線を駆動するための制御信号を出力する走査電極駆動回路と、

複数の信号線と、信号線と直交する方向に配線された複数の走査線との交点に画素部が設けられた表示パネルと

を備えることとしたものである。

【0028】

【発明の実施の形態】

以下、本発明にかかるマトリクス型表示装置を、その実施の一形態を示す図面に基づき具体的に説明する。なお、以下の各図において、図9～図11を用いて上記に説明した従来のマトリクス型表示装置9と同一の機能を有するものには、同一符号を付して示して重複する説明を省略する。

10

【0029】

実施の形態1.

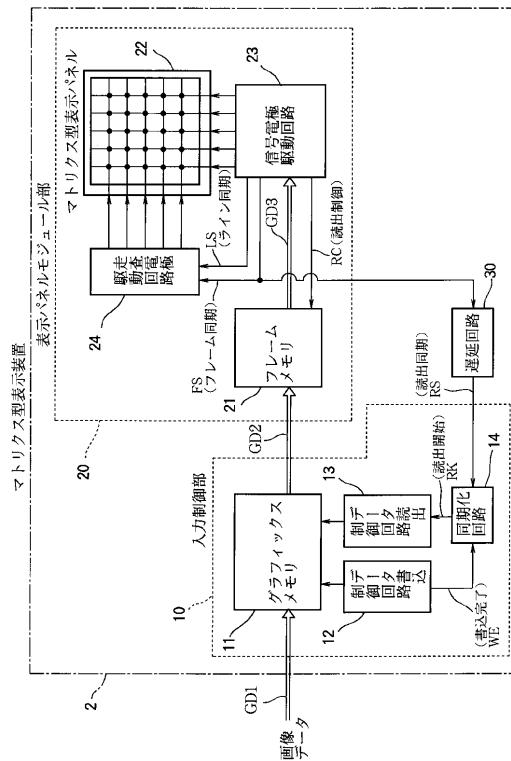

図1は本発明の実施の形態1であるマトリクス型表示装置を示す図である。

図1のマトリクス型表示装置1と図9のマトリクス型表示装置9との主な相違点は、表示パネルモジュール部20内の信号電極駆動回路23から出力されるフレーム同期信号FSに同期させて、読み出し開始信号をデータ読出制御回路13に対して出力する同期化回路14を、入力制御部10内に備える点である。また、上記した同期化回路14の追加に伴い、データ書き込み制御部12は、同期化回路14に書き完了信号WEを出力できるようになっており、信号電極駆動回路23は、フレーム同期信号を走査電極駆動回路24に出力すると共に同期化回路14にも出力できるようになっている。他の構成については、図11に示した従来のマトリクス型表示装置9と同一であるので説明を省略する。

20

【0030】

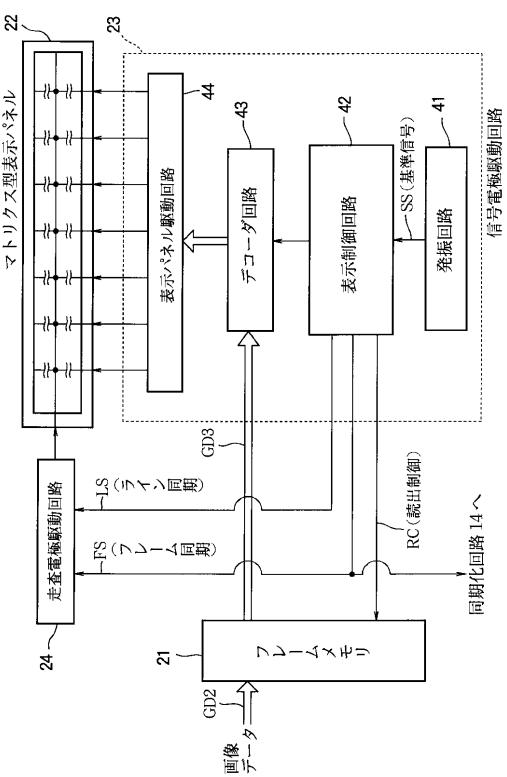

図2は、図1の表示パネルモジュール部20内の信号電極駆動回路23の内部構成を示すプロック図である。

信号電極駆動回路23において、41は、マトリクス表示パネル22に画像を表示させるための基準となるクロック信号(基準信号)SSを発生する発振回路である。42は、基準信号SSに基づいて、フレームメモリ21に読み出し制御信号RCを出力し、操作電極駆動回路24にフレーム同期信号FSおよびライン同期信号LSを出力し、後述するデコーダ回路43に画像データをデコードするための同期信号を出力する表示制御回路である。なお、フレーム同期信号FSについては、表示制御回路42から同期化回路14へも出力される。43は、表示制御回路42からの同期信号および画像データのコーディングルールに基づいてコード化された画像データGD3を画像表示可能な画像データに変換(デコード)するデコーダ回路である。44は、デコードされた画像データGD3に基づいて、マトリクス型表示パネル22の各信号電極に電圧を印加して駆動する表示パネル駆動回路である。

30

【0031】

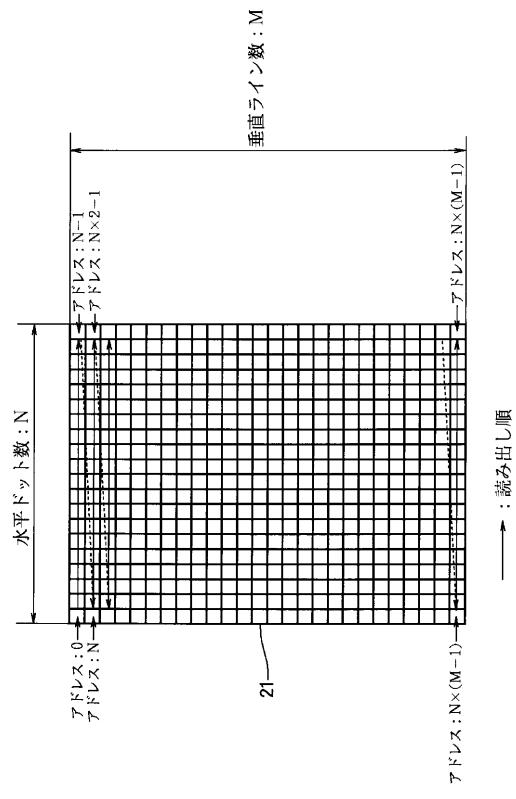

図3は、図1のフレームメモリ21のアドレス構成を示す図である。

40

図3に示すように、マトリクス型表示装置1における水平ドット数N/垂直ライン数Mのフレームメモリ21においては、データ読出制御回路13が、グラフィックスメモリ11から読み出された1画面分の画像データを、フレームメモリ21のアドレス0からアドレスN×M-1まで順次書きこむ。さらに詳しくは、データ読出制御回路13が、最初の1ライン目の画像データをアドレス0からアドレスN-1まで書き込み、次に、2ライン目の画像データをアドレスNからアドレスN×2-1まで書き込む。同様にして各ラインの画像データを書き込み、最終ラインであるMライン目の画像データをアドレスN×(M-1)からアドレスN×M-1まで書き込んで1画面の書き込みを終了する。

【0032】

なお、フレームメモリ21に一旦書き込まれてから読み出されるデータとしては、画像デ

50

ータに限らず、例えば、文字等を構成するデータでも良い。また、フレームメモリ21のデータ転送速度としては、IMT-2000規格対応の動画対応の携帯電話においては、データ通信速度等の制約により当面は毎秒15画面程度までの転送速度が想定されている。しかし、この転送速度に付いては、将来的には毎秒30画面程度まで上がっていくことが予想される。

【0033】

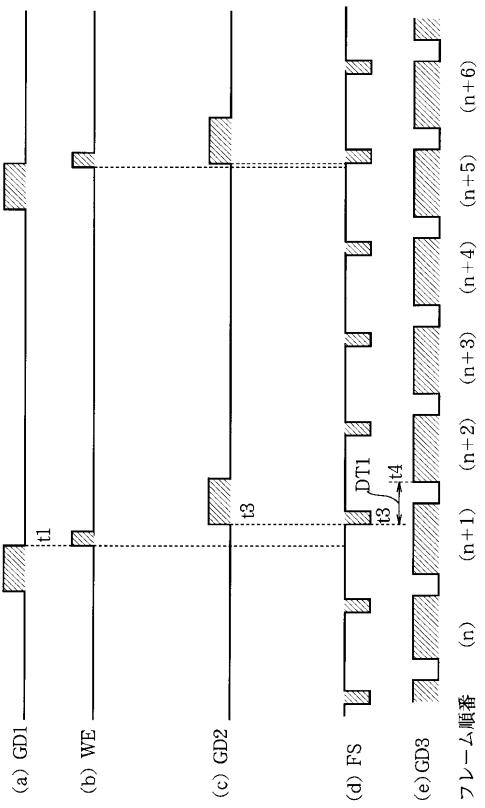

次に、マトリクス型表示装置1の動作について、図1～3に加えて、図4のタイミングチャートを参照して以下に説明する。

通信機能等により外部からマトリクス型表示装置1の入力制御部10に入力した画像データGD1は、データ書込制御回路12により制御されて一旦グラフィックスメモリ11に記憶される。図4(a)に示したように、グラフィックスメモリ11への画像データGD1の記憶処理がタイミングt1で終了すると、図4(b)に示したように、t1のタイミングで、データ書込制御回路12から書込完了信号WEが同期化回路14に送出される。この書込完了信号WEが入力することにより、同期化回路14はリセットされて、以下の動作を実施する。

10

【0034】

同期化回路14では、図4(d)に示したフレーム同期信号FSであって、書込完了信号WEを受信した後の最初のものが入力されるのを待ち、その入力するタイミングt3に同期させて読み出し開始信号RKをデータ読出制御回路13に送出する。すると、データ読出制御回路13によってグラフィックスメモリ11に一時記憶された画像データGD1は、タイミングt3で読み出され、画像データGD2としてフレームメモリ21に転送される。

。

20

【0035】

一方、表示パネルモジュール部20では、信号電極駆動回路23により、図4(e)に示したように、発振回路41によって発生された基準信号41(クロック信号)に基づくりフレッシュサイクルで、フレームメモリ21に記憶された画像データGD2が、画像データGD3として周期的に読み出されて、信号電極駆動回路23に入力される。フレームメモリ21から読み出された1フレーム毎の画像データGD3を、早い方から順に(n)フレーム目、(n+1)フレーム目、(n+2)フレーム目、以後同様に数値nを漸増させた順番とする。なお、nは正の整数である。

30

【0036】

信号電極駆動回路23内の表示制御回路42では、基準信号41に基づいて、フレームメモリ21に向けて読み出し制御信号RCを生成して送出し、デコーダ回路43にデコード用の同期信号を送出すると共に、フレーム同期信号FSおよびライン同期信号LSを生成して走査電極駆動回路24に送出する。デコーダ回路43は、表示制御回路42からの同期信号と画像データのコーディングルールに基づいて、入力した画像データGD3をマトリクス型表示パネル22で画像表示可能な画像データにデコードする。表示パネル駆動回路44は、デコードされた画像データからマトリクス型表示パネル22の各信号電極に対する制御信号を生成して送出する。走査電極駆動回路24では、フレーム同期信号FSおよびライン同期信号LSに基づいて、マトリクス型表示パネル22の走査電極に対する制御信号を生成して送出する。

40

【0037】

図4(c)および図4(e)を参照してわかるように、フレームメモリ21に記憶された(n+2)番目の画像データを読出すためのフレーム同期信号FSの送出タイミングt3に同期させて、データ読出制御回路13によりグラフィックスメモリ11からフレームメモリ21への次の画像データGD2の転送が行われる。また、画像データGD3は、フレーム同期信号FSから遅延時間DT1だけ遅れて出力される。従って、フレームメモリ21に記憶された(n+2)番目の画像データをGD3として読出す時には、新規に転送されて記憶された画像データGD2をGD3として読み出すことになり、画像データ読み出し中に新規に転送された画像データに切り替わることが無くなる。

50

## 【0038】

図5(a)～(c)は、マトリクス型表示装置1のマトリクス型表示パネル22上で、左端から右端に向かって移動する太い縦線を示した図である。

図4(e)に示したように、フレームメモリ21から読み出された1フレーム毎の画像データG D 3を、早い方から順に(n)フレーム目、(n+1)フレーム目、(n+2)フレーム目とすると、まず、(n)フレーム目の縦線100aの画像は、図5(a)のように縦に連続して表示される。

## 【0039】

次に、画像データG D 2はフレーム同期信号F Sと同期し、画像データG D 3の(n+2)番目の画像データはフレーム同期信号F SにD T 1だけ遅延したタイミングt 4に同期して読み出される。また、フレーム同期信号F Sのタイミングt 3は、画像データG D 3の出力が開始されるタイミングt 4よりD T 1だけ先行するだけであるので、図4(e)の(n+1)フレーム目では、転送中の画像データG D 2に切り替わることはない。従つて、図5(b)に示したように、(n+1)フレーム目の縦線100bの画像は、図5(a)に示した(n)フレーム目の縦線100aの画像と同様になり、縦線が連続して段差ができなくなる。次の、図5(c)に示した(n+2)フレーム目は、新たに書き込まれた縦線101bのみが表示され、従来と同様に段差は発生しない。

## 【0040】

このように、本実施の形態1のマトリクス型表示装置1では、マトリクス型表示パネル22のフレーム周期と同期されて画像データG D 2がグラフィックスメモリ11からフレームメモリ21に転送されるため、フレームメモリ21への画像データG D 2の転送処理と、フレームメモリ21から信号電極駆動回路23への画像データG D 3の読み出し処理が同一アドレスに一致しないようになり、マトリクス型表示パネル22に表示される画像の1フレームの途中で次の1フレームの画像に切り替わらなくなるようにデータ転送を制御することから、動画像を表示させたときに、1画面の上部と下部の画像内容が時間的にずれる事態が発生しなくなり、なめらかな映像を表示することができる。

## 【0041】

実施の形態2。

実施の形態1では、グラフィックスメモリ11からフレームメモリ21への画像データG D 2の転送開始タイミングを、フレーム同期信号F Sに同期させることにより、フレームメモリ21から読み出される画像データG D 3の途中で画像が新規書き込まれた画像に切り替わらないようにしたが、信号電極駆動回路23により、フレーム同期信号F Sに基づいてフレームメモリ21から画像データG D 3を読み出す際には遅延時間D T 1が発生する。例えば、その遅延時間D T 1が長くなると、図4(e)の(n+1)フレーム目の画像データG D 3の読み出し終了タイミングと、画像データG D 2の転送終了タイミングが近づき、画像データG D 2の転送終了タイミングが画像データG D 3の読み出し終了タイミングを追い越してしまう場合には、再び、マトリクス型表示パネル22に表示される画像の1フレームの途中で、次の1フレームの画像に切り替わる可能性が出てくる。

そこで、以下に説明する実施の形態2では、マトリクス型表示装置のフレーム同期信号F Sから画像データG D 3の読み出しまでの遅延時間D T 1が長くなりすぎないようにした。

## 【0042】

図6は本発明の実施の形態2のマトリクス型表示装置の構成を示すブロック図である。図6のマトリクス型表示装置2と図1のマトリクス型表示装置1との主な相違点は、信号電極駆動回路23から送出されたフレーム同期信号F Sを、任意の1フレームの画像データG D 3の読み出し終了タイミングt 5に同期するように所定時間だけ遅延させて読み出し同期信号R Sとして出力する遅延回路30を備える点である。他の構成に付いては、図1に示した実施の形態1のマトリクス型表示装置1と同一であるので説明を省略する。

## 【0043】

次に、マトリクス型表示装置2の動作について、図6に加えて、図7のタイミングチャート

10

20

30

40

50

トを参照して以下に説明する。

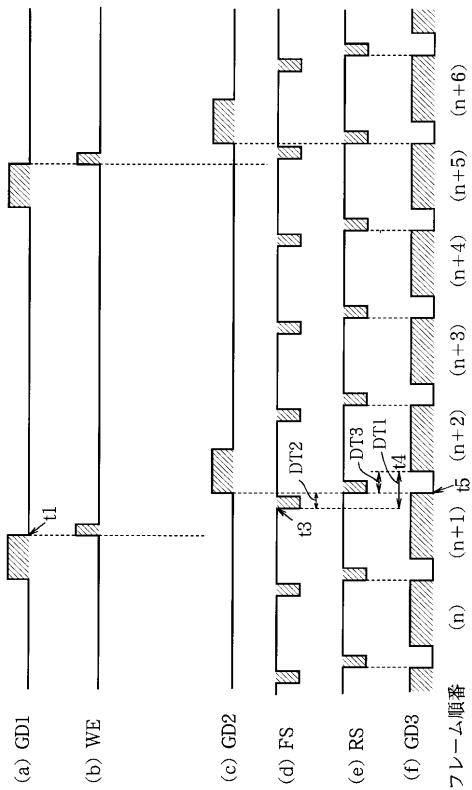

図7( a )、( b )、( d )および( f )は、夫々図4( a )、( b )、( d )および( e )に対応する同信号であるので説明を省略する。図7( e )は、遅延回路30によりフレーム同期信号FSを、( n+1 )フレームの画像データGD3の読み出し終了タイミングt5に同期するように所定時間DT2だけ遅延させた読み出し同期信号RSを示すものである。図7( c )は、読み出し同期信号RSに同期させて転送される画像データGD2を示すものである。

#### 【0044】

フレーム同期信号FSから( n+2 )フレームの画像データGD3の読み出し開始タイミングt4までの遅延時間DT1が長くなりすぎることをなくすために、フレーム同期信号FSを直接に同期化回路14に入力させずに、遅延回路30で遅延させた読み出し同期信号RSを同期化回路14に入力させるようにしたので、遅延時間DT1が遅延回路30の遅延時間DT2分だけ短縮された遅延時間DT3となる。また、読み出し同期信号RSは、( n+1 )フレームの画像データGD3の読み出し終了タイミングt5に同期して発生されるので、マトリクス型表示パネル22に表示される画像の1フレームの途中で次の1フレームの画像に切り替わる事態を無くすことができる。

#### 【0045】

このように本実施の形態2では、フレーム同期信号FSを遅延させた読み出し同期信号RSを出力する遅延回路30を同期化回路14のフレーム同期信号入力部の前段に追加することにより、例えば、30～50msec程度の応答速度であるTFT等のアクティブマトリクス型液晶パネル、70～80msec程度の応答速度である高速応答型のSTN液晶パネル、数μsec程度の応答速度である有機ELパネルの夫々に対するように異なる応答速度を有するマトリクス型表示パネルの夫々に対して、遅延時間が長くなりすぎない最適な遅延量を遅延回路30で設定して読み出し同期信号RSとして出力できるようにしたので、マトリクス型表示パネルの種類を問わず、信号電極駆動回路23からのフレーム同期信号FSが画像データGD2の転送タイミングとして適切でない場合にも、なめらかな動画像を表示させることができる。

#### 【0046】

実施の形態3。

実施の形態2では、フレーム同期信号FSが入力され、その信号FSを画像データGD3の読み出し終了タイミングt5に同期するように最適に遅延させた読み出し同期信号RSとして出力する遅延回路30を、同期化回路14のフレーム同期信号入力部の前段に追加することにより、マトリクス型表示パネル22に表示される画像の1フレームの途中で次の1フレームの画像に切り替わる事態を無くしていたが、遅延回路30で用いられるクロック信号は、信号電極駆動回路23内部のクロック信号(基準信号SS)と同一であるとは限らなかった。

基準信号SSと遅延回路30で用いられるクロック信号とが異なる場合には、夫々の発振回路のばらつきにより、読み出し同期信号RSを最適な遅延量に設定できない場合があった。

そこで、以下に説明する実施の形態3では、読み出し同期信号RSが信号電極駆動回路23内部のクロック信号(基準信号SS)と同期するようにして、発振回路のばらつきの影響を受けないようにした。

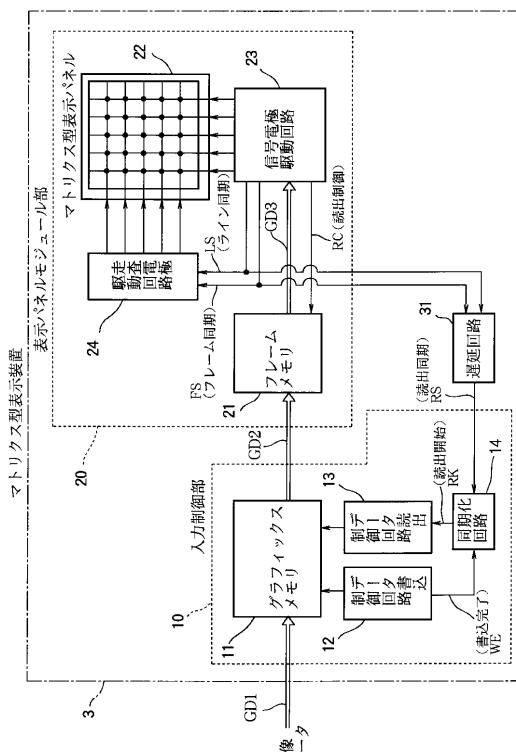

#### 【0047】

図8は、本発明の実施の形態3のマトリクス型表示装置の構成を示すブロック図である。図8のマトリクス型表示装置3と図2のマトリクス型表示装置2との主な相違点は、遅延回路31に信号電極駆動回路23から送出されたフレーム同期信号FSに加えてライン同期信号LSが入力される点である。本実施の形態2では、ライン同期信号LSを遅延回路31のクロック信号として利用するようにした。他の構成に付いては、図6に示した実施の形態2のマトリクス型表示装置2と同一であるので説明を省略する。

#### 【0048】

10

20

30

40

50

次に、マトリクス型表示装置3の動作について、図8に加えて、実施の形態2の図7のタイミングチャートを参照して以下に説明する。

基準信号SSと遅延回路30で用いられるクロック信号とが異なる場合には、例えば、図7(e)の読み出し同期信号RSが、図7(f)の(n+1)フレームの画像データGD3の読み出し終了タイミングt5と一致しなくなる。すると、読み出し同期信号RSに同期させて転送される画像データGD2も画像データGD3の読み出し終了タイミングt5と一致しなくなるので、再び、マトリクス型表示パネル22に表示される画像の1フレームの途中で次の1フレームの画像に切り替わる事態が発生する可能性が出てくる。

#### 【0049】

ところで、信号電極駆動回路23から送出されたフレーム同期信号FSとライン同期信号LSは、図2に示したように同じ発振回路41からの基準信号SSに基づいて生成されるので、発振回路毎にばらつきが発生しても、フレーム同期信号FSとライン同期信号LS間の同期がばらつくことはない。

#### 【0050】

そのため、本実施の形態3では、図8に示したようにライン同期信号LSを遅延回路31のクロック信号として入力するように構成している。こうすることにより、予め設定されたライン同期信号LSのパルス数だけフレーム同期信号FSを遅延させた信号を、読み出し同期信号RSとして遅延回路31から出力できるようになる。この場合には、読み出し同期信号RSがフレーム同期信号FSから遅延する量はばらつかないので、(n+1)フレームの画像データGD3の読み出し終了タイミングt5と、読み出し同期信号RSに同期させて転送される画像データGD2とを確実に同期させることができる。従って、マトリクス型表示パネル22に表示される画像の1フレームの途中で次の1フレームの画像に切り替わる事態を無くすことができる。

#### 【0051】

このように本実施の形態3では、遅延回路31にフレーム同期信号FSに加えてライン同期信号LSを入力させ、ライン同期信号LSをクロックとしてフレーム同期信号FSを遅延させることにより読み出し同期信号RSを出力するようにし、発振回路等のばらつきにより読み出し同期信号RSの発生タイミングがばらつかず、最適な遅延量を有する読み出し同期信号RSを出力することができるようにして、フレーム同期信号FSから一定の位相量だけ遅延させた最適な遅延量の読み出し同期信号RSを設定できるようにしたので、例えば、上記したアクティブマトリクス型液晶パネル、高速応答型のSTN液晶パネル、有機ELパネル等のマトリクス型表示パネルの種類を問わず、発振回路の周波数ドリフト等が発生しやすい状況であっても発振回路のばらつきに影響されず、安定したなめらかな動画像を表示させることができる。

#### 【0052】

また、上記の各実施形態のマトリクス型表示パネルが液晶パネルである場合には、透過型、反射型、あるいは、反射半透過型に分類することができる。透過型の液晶パネルは、画像表示内容を視認するためにバックライト等の内部照明が必要であり、バックライトには電力が必要となるので、低消費電力が要望される携帯電話等の携帯情報端末装置では使用することが難しい。それに対して反射型は、背面側の全面に反射板を設けることにより外部からの光の反射光により画像表示内容を視認できることから、バックライトの電力が不要であるので、低消費電力が要望される携帯電話等の携帯情報端末装置に向いている。また、反射半透過型は、背面側に網点状等の半透過型の反射板を設けることにより外部からの光の反射光と内部照明の双方により画像表示内容を視認できることから、反射型と同様にバックライトの電力が不要であり、さらに、外部が暗い場合のみ内部照明を用いて視認することができるので、低消費電力が要望される携帯電話等の携帯情報端末装置に向いていることに加え、暗い場所での視認性も向上するので使い勝手をよくすることができる。

#### 【0053】

また、マトリクス型表示パネルとしてアクティブマトリクス型の液晶表示パネルを用いた場合、従来の応答速度が遅いSTN型の液晶表示パネルに比べて、応答速度と周囲に対す

10

20

30

40

50

る表示部のコントラストが向上するので、動きの激しい動画像あるいは高速に移動する動画像を表示する場合であっても、安定したなめらかな動画像を表示させることができることに加えて、視認性を向上させることができる。

【0054】

また、マトリクス型表示パネルとして高速応答型STN液晶表示パネルを用いた場合、従来の応答速度が遅いSTN型の液晶表示パネルに比べて、応答速度が向上するので、低消費電力と低コストを維持したままで、動きの激しい動画像あるいは高速に移動する動画像を表示する場合であっても、安定したなめらかな動画像を表示させることができる。

【0055】

また、マトリクス型表示パネルとして有機蛍光表示パネルを用いた場合、アクティブマトリクス型の液晶表示パネルと同様に、従来の応答速度が遅いSTN型の液晶表示パネルに比べて、応答速度が向上する。また、有機蛍光表示パネルの場合には、表示部自体が発光することにより周囲に対する表示部のコントラストが向上するので、安定したなめらかな動画像を表示させることができることに加えて、視認性を液晶よりもさらに向上させることができるので画質をさらに向上させ、バックライトが不要であるので薄型化することができる。

【0056】

また、マトリクス型表示パネルとしてアクティブマトリクス型の有機蛍光表示パネルを用いた場合、動きの激しい動画像あるいは高速に移動する動画像を表示する場合であっても、安定したなめらかな動画像を表示させることができ、視認性を液晶よりもさらに向上させることができるので画質をさらに向上させ、薄型化することができる。

【0057】

【発明の効果】

本発明は、以上説明したように構成されているので、以下に示すような効果を奏する。

すなわち、マトリクス型表示パネルのフレーム周期と同期されて画像データがグラフィックスメモリからフレームメモリに転送されるため、フレームメモリへの画像データの転送処理と、フレームメモリから信号電極駆動回路への画像データの読み出し処理が同一アドレスに一致しないようになり、マトリクス型表示パネルに表示される画像の1フレームの途中で次の1フレームの画像に切り替わらなくなるようにデータ転送を制御するので、動画像を表示させたときに、1画面の上部と下部の画像内容が時間的にずれる事態が発生しなくなり、なめらかな映像を表示することができる。

【図面の簡単な説明】

【図1】本発明の実施の形態1のマトリクス型表示装置の構成を示すブロック図である。

【図2】図1の信号電極駆動回路の内部構成を示すブロック図である。

【図3】図1のフレームメモリのアドレス構成を示す図である。

【図4】(a)～(e)は図1のマトリクス型表示装置のタイミングチャートである。

【図5】(a)～(c)はマトリクス型表示パネル上で左端から右端に向かって移動する太い縦線を示した図である。

【図6】本発明の実施の形態2のマトリクス型表示装置の構成を示すブロック図である。

【図7】(a)～(f)は図6のマトリクス型表示装置のタイミングチャートである。

【図8】本発明の実施の形態3のマトリクス型表示装置の構成を示すブロック図である。

【図9】従来のフレームメモリ内蔵のマトリクス型表示装置の構成を示すブロック図である。

【図10】(a)～(c)は従来のマトリクス型表示装置のタイミングチャートである。

【図11】(a)～(c)は従来のマトリクス型表示パネル上で左端から右端に向かって移動する太い縦線を示した図である。

【符号の説明】

1 マトリクス型表示装置、 10 入力制御部、 11 グラフィックスメモリ、 1

2 データ書込制御回路、 13 データ読出制御回路、 14 同期化回路、 20

表示パネルモジュール、 21 フレームメモリ、 22 マトリクス型表示パネル、 50

23 信号電極駆動回路、24 走査電極駆動回路、GD1、GD2、GD3 画像データ、FS フレーム同期信号、LS ライン同期信号、RC 読み出し制御信号、RK 読み出し開始信号、WE 書込完了信号。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 8 0 T |

| G 0 9 G | 3/30 | H       |

| G 0 9 G | 5/36 | 5 1 0 M |

| G 0 9 G | 5/00 | 5 5 5 T |

(56) 参考文献 特開平11-288256 (JP, A)

特開昭61-175677 (JP, A)

特開平11-167096 (JP, A)

特開平05-197356 (JP, A)

特開昭63-088597 (JP, A)

特開平07-261703 (JP, A)

特開平07-261732 (JP, A)

(58) 調査した分野(Int.Cl.<sup>7</sup>, DB名)

G09G3/00-5/42