(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6148368号

(P6148368)

(45) 発行日 平成29年6月14日(2017.6.14)

(24) 登録日 平成29年5月26日(2017.5.26)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 616T |

| HO1L 21/822  | (2006.01) | HO1L 29/78  | 618B |

| HO1L 27/04   | (2006.01) | HO1L 27/04  | H    |

| HO1L 27/06   | (2006.01) | HO1L 27/06  | 311C |

| HO1L 21/8234 | (2006.01) | HO1L 27/088 | A    |

請求項の数 3 (全 28 頁) 最終頁に続く

|              |                                                                    |

|--------------|--------------------------------------------------------------------|

| (21) 出願番号    | 特願2016-51989 (P2016-51989)                                         |

| (22) 出願日     | 平成28年3月16日 (2016.3.16)                                             |

| (62) 分割の表示   | 特願2014-128133 (P2014-128133)<br>の分割<br>原出願日 平成23年1月21日 (2011.1.21) |

| (65) 公開番号    | 特開2016-136638 (P2016-136638A)                                      |

| (43) 公開日     | 平成28年7月28日 (2016.7.28)                                             |

| 審査請求日        | 平成28年3月31日 (2016.3.31)                                             |

| (31) 優先権主張番号 | 特願2010-12627 (P2010-12627)                                         |

| (32) 優先日     | 平成22年1月22日 (2010.1.22)                                             |

| (33) 優先権主張国  | 日本国 (JP)                                                           |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| 審査官       | 竹口 泰裕                                          |

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

酸化物半導体層と、

第1乃至第4の導電層と、

第1の絶縁層と、を有し、

前記酸化物半導体層は、前記第1の導電層上方に位置する領域を有し、

前記第2の導電層は、前記酸化物半導体層上方に位置する領域を有し、

前記第1の導電層は、前記酸化物半導体層に電気的に接続され、

前記第2の導電層は、前記酸化物半導体層に電気的に接続され、

前記第3の導電層は、前記第1の絶縁層を介して前記酸化物半導体層と重なる領域を有し、 10

前記第4の導電層は、前記第1の導電層と電気的に接続され、

前記第4の導電層は、前記酸化物半導体層上方に位置する領域を有し、

前記第3の導電層は、前記第1の絶縁層上方に位置する領域を有し、

前記第3の導電層は、前記酸化物半導体層及び前記第1の絶縁層を介して前記第1の導電層と重なる領域を有し、

前記第3の導電層は、前記第4の導電層と重ならないことを特徴とする半導体装置。

【請求項 2】

酸化物半導体層と、

第1乃至第5の導電層と、

第 1 の絶縁層と、を有し、前記酸化物半導体層は、前記第 1 の導電層上方に位置する領域を有し、前記第 2 の導電層は、前記酸化物半導体層上方に位置する領域を有し、前記第 1 の導電層は、前記酸化物半導体層に電気的に接続され、前記第 2 の導電層は、前記酸化物半導体層に電気的に接続され、前記第 3 の導電層は、前記第 1 の絶縁層を介して前記酸化物半導体層と重なる領域を有し、前記第 4 の導電層は、前記第 1 の導電層と電気的に接続され、前記第 4 の導電層は、前記酸化物半導体層上方に位置する領域を有し、前記第 5 の導電層は、前記第 2 の導電層と電気的に接続され、前記第 3 の導電層は、前記第 1 の絶縁層上方に位置する領域を有し、前記第 3 の導電層は、前記酸化物半導体層及び前記第 1 の絶縁層を介して前記第 1 の導電層と重なる領域を有し、前記第 3 の導電層は、前記第 4 の導電層と重ならず、前記第 3 の導電層は、前記第 5 の導電層と重ならないことを特徴とする半導体装置。**【請求項 3】**請求項 1 または請求項 2 において、前記酸化物半導体層は、In、Ga、及びZnを含むことを特徴とする半導体装置。**【発明の詳細な説明】****【技術分野】**

20

**【0001】**

本発明は、半導体装置に関する。または半導体装置の駆動方法に関する。または半導体装置を具備する電子機器に関する。

**【0002】**

また、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば、パワーデバイス、当該パワーデバイスを有する表示装置及び集積回路等は半導体装置に含まれる。

**【背景技術】****【0003】**

パワーデバイスとして用いられる半導体装置には、シリコン系の材料を用いて作製されるパワーデバイスが広く流通している。シリコンを用いたパワーデバイスはバンドギャップが小さいため、高温での動作範囲に限界がある。このため、近年ではバンドギャップが広いSiCやGaNを用いたパワーデバイスの開発がされている（例えば特許文献1を参照）。

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2009-10142号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

GaNを用いたパワーデバイスとしてHEMT（ヘテロ接合電界効果トランジスタ）がある。HEMTは、SiC基板上に、緩衝層であるAlN層、GaN層、AlGaN層が積層され、AlGaN層上にソース電極、ゲート電極、及びドレイン電極が設けられた構造を有する。また、GaN層及びAlGaN層のバンドギャップの違いにより、GaN層及びAlGaN層の界面に高濃度の二次元電子ガス層が形成される。二次元電子ガス層の伝導帯はフェルミ準位よりエネルギー準位が低くなるため、HEMTでは二次元電子ガス層がチャネルとなり、ゲートに電圧を印加しない状態であっても電流が流れるノーマリーオン状態となり、駆動回路や保護回路が複雑になるため問題となっている。パワーデバイスをノーマリーオフ化させるために単純に電子濃度を減少させると、今度は素子の抵抗が増

30

40

50

加するため、ノーマリーオフ化と低抵抗化の両立は非常に困難である。またデバイス構造を工夫してノーマリーオフ化を実現しようとする試みもなされているが、デバイスの構造が複雑化して製造コストが増大するといった問題がある。

【0006】

そこで本発明の一形態は、消費電力の増加を招くことなく、オフの状態を実現することのできる半導体装置を提供することを課題とする。

【課題を解決するための手段】

【0007】

本発明の一形態は、ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。また、上記スイッチング用の電界効果トランジスタは、チャネル領域がi型化または実質的にi型化された酸化物半導体層で形成される半導体装置である。スイッチング用の電界効果トランジスタにより、パワー素子のゲートに高電位または低電位を印加して、パワー素子のオン状態及びオフ状態を得る。

10

【0008】

本発明の一形態は、第1のゲート及び第2のゲートを有し、チャネル領域がn型である酸化物半導体層で形成されるパワーMOSFETと、パワーMOSFETの第1のゲート及び第2のゲートに正電圧を印加するためのスイッチング用の電界効果トランジスタと、パワーMOSFETの第1のゲート及び第2のゲートに負電圧を印加するためのスイッチング用の電界効果トランジスタとを有し、パワーMOSFETの第1のゲート及び第2のゲートのノードはスイッチング用の電界効果トランジスタに接続し、上記スイッチング用の電界効果トランジスタのチャネル領域がi型化または実質的にi型化された酸化物半導体層で形成される半導体装置である。スイッチング用の電界効果トランジスタにより、パワーMOSFETの第1のゲート及び第2のゲートに高電位または低電位を印加して、パワーMOSFETのオン状態及びオフ状態を得る。

20

【0009】

また、本発明の一形態は、高電圧発生源に接続する第1の電界効果トランジスタと、第1の電界効果トランジスタに接続する第2の電界効果トランジスタと、第2の電界効果トランジスタに接続し、且つ低電圧発生源に接続する第3の電界効果トランジスタと、第2の電界効果トランジスタ及び第3の電界効果トランジスタに接続する容量素子と、第1の電界効果トランジスタ及び第2の電界効果トランジスタに接続するパワーMOSFETとを有し、パワーMOSFETは、第1のゲート及び第2のゲートと、第1のゲートに接する第1の絶縁層と、第2のゲートに接する第2の絶縁層と、第1の絶縁層及び第2の絶縁層の間に形成される酸化物半導体層と、酸化物半導体層に接するソース領域及びドレイン領域として機能する第1の端子及び第2の端子を有し、第1のゲート及び第2のゲートのノードは、第1の電界効果トランジスタ及び第2の電界効果トランジスタに接続し、第1の電界効果トランジスタ乃至第3の電界効果トランジスタのチャネル形成領域は、i型化された酸化物半導体層で形成され、パワーMOSFETの前記酸化物半導体層は、n型である半導体装置である。

30

【0010】

パワーMOSFETの酸化物半導体層のキャリア濃度は $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{17} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下である。

40

【0011】

スイッチング用の電界効果トランジスタ、第1の電界効果トランジスタ乃至第3の電界効果トランジスタの酸化物半導体層のキャリア濃度は $5 \times 10^{14} \text{ cm}^{-3}$ 未満である。

【0012】

パワーMOSFETの第1のゲートまたは第2のゲートは、第1の端子及び第2の端子の

50

一方と重畳し、他方と重畳しなくともよい。

【発明の効果】

【0013】

本発明の一形態によれば、消費電力の増加を招くことなくオフの状態を実現できるパワーデバイス及びそれを有する半導体装置を提供することができる。

【図面の簡単な説明】

【0014】

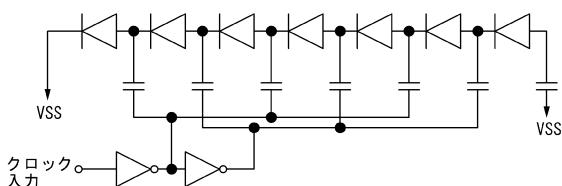

【図1】本発明の一態様の半導体装置を説明する等価回路図である。

【図2】本発明の一態様の半導体装置を説明する等価回路図である。

【図3】本発明の一態様の半導体装置を説明する等価回路図である。

10

【図4】本発明の一態様の半導体装置を説明する等価回路図である。

【図5】本発明の一態様の半導体装置を説明する断面図及び上面図である。

【図6】本発明の一態様の半導体装置を説明する断面図である。

【図7】本発明の一態様の半導体装置の作製工程を説明する断面図である。

【図8】本発明の一態様の半導体装置を説明する断面図である。

【図9】本発明の一態様の半導体装置を説明する断面図及び上面図である。

【図10】本発明の一態様の半導体装置を説明する断面図である。

【図11】本発明の一態様の半導体装置の作製工程を説明する断面図である。

【図12】本発明の一態様の半導体装置を説明する等価回路図である。

20

【図13】本発明の一態様の半導体装置を説明する等価回路図である。

【図14】本発明の一態様の半導体装置を説明する等価回路図である。

【図15】本発明の一態様の半導体装置を説明する等価回路図である。

【図16】本発明の一態様の半導体装置を説明する等価回路図である。

【図17】本発明の一態様の半導体装置を説明する等価回路図である。

【図18】電子機器を説明する図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

30

【0016】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、または領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0017】

また、本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

40

【0018】

また、電圧とは、ある電位と、基準の電位（例えばグラウンド電位）との電位差のことを示す場合が多い。よって、電圧、電位、電位差を、各々、電位、電圧、電圧差と言い換えることが可能である。

【0019】

また、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電層、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関

50

係以外のものも含むものとする。

【0020】

(実施の形態1)

本実施の形態では、パワーデバイスである半導体装置の回路構成およびその動作について説明する。

【0021】

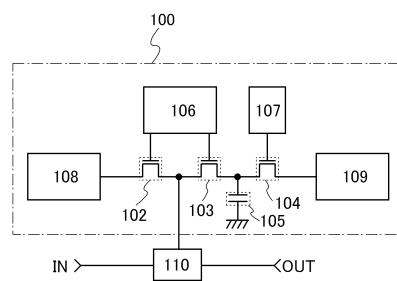

図1で示す半導体装置は、パワー素子110及び制御回路100を有する。制御回路100は、電界効果トランジスタ102(第1のトランジスタともいう。)、電界効果トランジスタ103(第2のトランジスタともいう。)、電界効果トランジスタ104(第3のトランジスタともいう。)、容量素子105、過電圧検出回路106、リフレッシュ制御回路107、高電圧発生源108、及び低電圧発生源109を有する。

10

【0022】

制御回路100は、パワー素子110に印加する電圧を、高電圧発生源108で発生させた高電圧または低電圧発生源109で発生させた低電圧に切り替えると共に、入力端子IN及び出力端子OUTの間に過電圧が印加された際に、パワー素子110を流れる電流量を制御する。

【0023】

電界効果トランジスタ102は、ゲートが過電圧検出回路106に接続され、第1の端子が高電圧発生源108に接続され、第2の端子がパワー素子110に接続される。電界効果トランジスタ102は、第2の端子に接続されたパワー素子110への高電位の印加を制御する。

20

【0024】

電界効果トランジスタ103は、ゲートが過電圧検出回路106に接続され、第1の端子が容量素子105及び電界効果トランジスタ104の第2の端子に接続され、第2の端子がパワー素子110に接続される。

【0025】

電界効果トランジスタ103は、低電圧発生源109から容量素子105に充電された低電位を、第2の端子に接続されたパワー素子110に印加することを制御する。

【0026】

なお、本明細書で説明するオフ電流とは、電界効果トランジスタが非導通のときに、ソースとドレインとの間、すなわち第1の端子と第2の端子との間に流れる電流をいう。

30

【0027】

電界効果トランジスタ104は、ゲートがリフレッシュ制御回路107に接続され、第1の端子が低電圧発生源109に接続され、第2の端子が容量素子105及び電界効果トランジスタ103の第1の端子に接続される。電界効果トランジスタ104は、第2の端子に接続された容量素子105の低電位の充電を制御する。

【0028】

電界効果トランジスタ102乃至電界効果トランジスタ104のチャネル領域は、i型化または実質的にi型化された酸化物半導体層で形成される。i型化または実質的にi型化された酸化物半導体層は、キャリア密度が $5 \times 10^{14} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{12} \text{ cm}^{-3}$ 未満、より好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ 以下である。また、ドナーとして寄与する水素や酸素欠陥は少ないことが好ましく、水素濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 以下が好ましい。なお、キャリア密度は、ホール効果測定により得られる。また、より低濃度のキャリア密度の測定は、CV測定(Capacitance-Voltage-Measurement)の測定結果により得られる。また、酸化物半導体層中の水素濃度測定は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られる。

40

【0029】

i型化または実質的にi型化された酸化物半導体をチャネル領域に用いた電界効果トランジスタ102は、オフ電流が $1 \times 10^{-16} \text{ A} / \mu\text{m}$ 以下、さらには $1 \times 10^{-19} \text{ A} / \mu\text{m}$ 以下

50

$\mu m$  以下と小さくすることができる。i型化または実質的にi型化された酸化物半導体は、バンドギャップが広く、電子の励起のために大きな熱エネルギーが必要であるため、直接再結合及び間接再結合が生じにくい。このため、ゲート電極に負の電位が印加された状態（オフ状態）では、少数キャリアであるホールは実質的にゼロであるため、直接再結合及び間接再結合が生じにくく、電流は限りなく小さくなる。この結果、電界効果トランジスタの非導通（オフ、OFFともいう。）状態において、酸化物半導体層は絶縁体とみなせて回路設計を行うことができる。一方で、i型化または実質的にi型化された酸化物半導体層は、電界効果トランジスタの導通状態においては、非晶質シリコンで形成される半導体層よりも高い電流供給能力を見込むことができる。このため、電界効果トランジスタ 102 乃至電界効果トランジスタ 104 は、エンハンスメント型であり、オフ状態では極めてリーク電流の小さくノーマリーオフ状態となり、優れたスイッチング特性を有する。10

#### 【0030】

容量素子 105 は、間欠的な電界効果トランジスタ 104 の導通（オン、ONともいう。）により、パワー素子 110 に印加する低電位を保持するための素子である。容量素子 105 としては、絶縁層を導電体で挟持する構造により形成すればよい。

#### 【0031】

過電圧検出回路 106 は、入力端子 IN 及び出力端子 OUT の間の電圧に応じて、電界効果トランジスタ 102 及び電界効果トランジスタ 103 の導通または非導通を制御するための回路である。具体的には、入力端子 IN 及び出力端子 OUT の間に過電圧が印加された際に、電界効果トランジスタ 102 を導通、電界効果トランジスタ 103 を非導通とし、高電圧発生源 108 からパワー素子 110 への高電位の印加を制御する。また、入力端子 IN 及び出力端子 OUT の間に過電圧が印加されない際には、電界効果トランジスタ 102 を非導通、電界効果トランジスタ 103 を導通とし、パワー素子 110 への低電圧発生源 109 から容量素子 105 に充電された低電位の印加を制御する。20

#### 【0032】

リフレッシュ制御回路 107 は、低電圧発生源 109 から容量素子 105 への低電位の充電を制御するために、電界効果トランジスタ 104 の導通または非導通を制御する回路である。具体的には、低電圧発生源 109 から容量素子 105 への充電により保持される低電位がパワー素子 110 へ放電する前に、間欠的に電界効果トランジスタ 104 を導通とし、低電位の充電をするための回路である。30

#### 【0033】

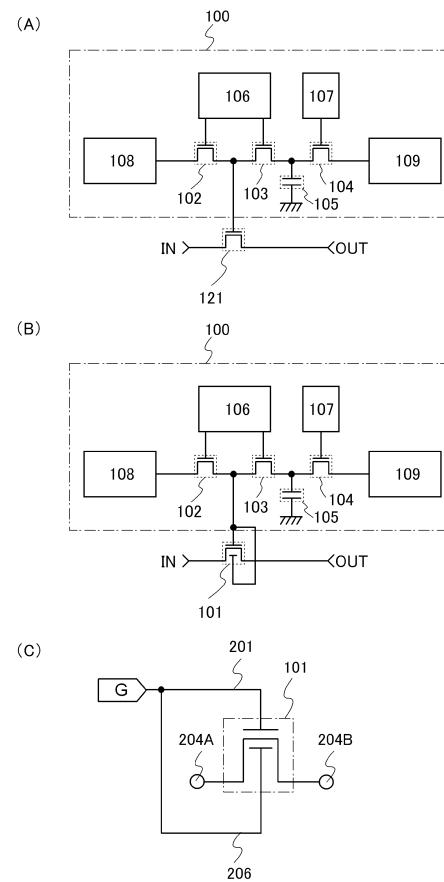

パワー素子 110 は、ゲートに電圧を印加しない状態でオン状態となるパワー素子を用いる。パワー素子 110 としては、Si、SiC、GaN、酸化物半導体を用いた、バイポーラトランジスタ、電界効果トランジスタ（FET（Field-Effect Transistor））、ゲートターンオフサイリスタ、絶縁ゲートバイポーラトランジスタ（IGBT）等を適宜用いることができる。また、電界効果トランジスタにおいては、パワー-MOSFET（Metal Oxide Semiconductor FET）、HFET、JFET（ジャンクション接合型電界効果トランジスタ）等を適宜用いることができる。3 端子のパワー素子 121 の等価回路を図 2 (A) に示す。パワー素子 121 のゲートが電界効果トランジスタ 102 及び電界効果トランジスタ 103 に接続する。また、パワー素子 121 のソース端子及びドレイン端子の一方を第 1 の端子とし、ソース端子及びドレイン端子の他方を第 2 の端子とすると、第 1 の端子が入力端子 IN に接続し、第 2 の端子が出力端子 OUT に接続する。40

#### 【0034】

本実施の形態では、これ以降、パワー素子 110 の代表例として、図 2 (B) に示すように、4 端子のパワー-MOSFET 101 を用いて説明する。

#### 【0035】

パワー-MOSFET 101 は、四つの端子、代表的には、第 1 のゲート端子（第 1 のゲートという）と、第 2 のゲート端子（第 2 のゲートという）と、ドレイン端子（ドレインともいう）と、ソース端子（ソースともいう）と有する。パワー-MOSFET 101 は、チ50

チャネル領域の上下に、第1のゲート及び第2のゲートが配置され、第1のゲート及び第2のゲートに、パワーMOSFET 101のスイッチングを制御する信号が供給される。

【0036】

チャネル領域の上下に第1のゲート201及び第2のゲート206が配置されるパワーMOSFET 101の回路記号を図2(C)に示す。図2(C)に示すように、パワーMOSFET 101は、第1のゲート201と、第2のゲート206と、第1の端子204Aと、第2の端子204Bとを有する。パワーMOSFET 101は、第1のゲート201及び第2のゲート206に高電圧発生源108または低電圧発生源109から出力される信号(図2(C)に示す信号G)が入力される。高電圧発生源108または低電圧発生源109から出力される信号より、パワーMOSFET 101の第1の端子204A及び第2の端子204Bの間における導通または非導通といったスイッチングが制御される。

10

【0037】

パワーMOSFET 101のチャネル領域は、n型である酸化物半導体層で形成されてもよい。n型である酸化物半導体層は、キャリア密度が $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{17} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下である。また、酸化物半導体において、水素及び酸素欠損がドナーとして寄与するため、水素濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ であることが好ましい。

【0038】

パワーMOSFET 101は、チャネル領域にn型である酸化物半導体層を有するため、チャネル領域にi型である酸化物半導体層を有するパワーMOSFETと比較してオン抵抗を低減することが可能であり、大電流を流すことが可能である。しかしながら、n型である酸化物半導体層をチャネル領域に有するため、デプレッション型であり、ゲートに電圧を印加しない状態であっても電流が流れるノーマリーオンである。本実施の形態に示すパワーMOSFETは、第1のゲート201と共に、第2のゲート206を有し、第1のゲート201及び第2のゲート206に負の電圧を印加することでオフさせることができると、このため、オン抵抗が低く、大電流を流すことが可能であるパワーMOSFETをオフさせることができる。一方、第1のゲート201及び第2のゲート206に正の電圧を印加することでオンさせることができると、また、パワーMOSFET 101は第1のゲート201及び第2のゲート206を有するため、シングルゲートのパワーMOSFETと比較して、チャネル領域の厚さを厚くすることでしきい値電圧がより負になり、オン電流を大きくすることができます。

20

【0039】

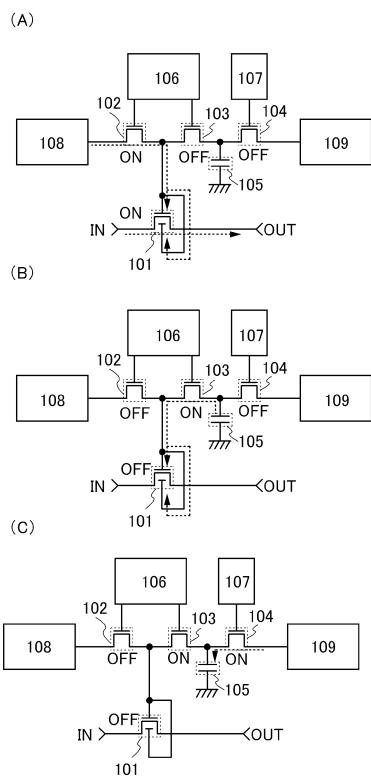

次に、図2(B)に示す半導体装置の動作について図3及び図4を用いて説明する。図3及び図4での説明において、点線矢印は、パワーMOSFET 101及び各電界効果トランジスタの導通または非導通による信号の流れをわかりやすくするために可視化して示したものである。また、半導体装置を構成するパワーMOSFET 101のチャネル領域にはn型となる酸化物半導体層を用いており、高電圧発生源108からの高電位により導通、低電圧発生源109からの低電位により非導通、となるものである。なお、図2(A)に示す半導体装置の動作は、図3及び図4に示す等価回路において、パワーMOSFET 101をパワー素子121に置換えればよい。

30

【0040】

図3(A)では、パワーMOSFET 101を導通とする際の動作について説明する。過電圧検出回路106の制御により、電界効果トランジスタ102を導通、電界効果トランジスタ103を非導通とし、リフレッシュ制御回路107の制御により電界効果トランジスタ104を非導通とさせる。電界効果トランジスタ102を導通とさせることにより、高電圧発生源108から高電位がパワーMOSFET 101の第1のゲート及び第2のゲートに印加され、パワーMOSFET 101が導通する。

40

【0041】

図3(B)では、パワーMOSFET 101を非導通とさせる際の動作について説明する。過電圧検出回路106の制御により、電界効果トランジスタ102を非導通、電界効果

50

トランジスタ 103 を導通とし、リフレッシュ制御回路 107 の制御により、電界効果トランジスタ 104 を非導通とさせる。図 3 (B) に示すように、電界効果トランジスタ 103 を導通とさせることにより、低電圧発生源 109 から容量素子 105 に充電された低電位がパワー MOSFET 101 の第 1 のゲート及び第 2 のゲートに印加され、パワー MOSFET 101 が非導通となる。

【0042】

図 3 (C) では、図 3 (B) で述べた容量素子 105 に低電位を充電する動作について説明する。過電圧検出回路 106 の制御により、電界効果トランジスタ 102 を非導通、電界効果トランジスタ 103 を導通とし、リフレッシュ制御回路 107 の制御により、電界効果トランジスタ 104 を導通とし、低電圧発生源 109 から容量素子 105 への低電位の充電を行う。

10

【0043】

なお、図 3 (C) で述べた容量素子 105 への低電位の充電は、リフレッシュ制御回路 107 の制御により、一定の周期で行われる。具体的には、低電圧発生源 109 からの充電により容量素子 105 でパワー MOSFET 101 を非導通とさせる低電位を保持している間、半導体装置は図 3 (B) の状態を保持する。そして、間欠的に図 3 (C) の状態として、電界効果トランジスタ 104 を導通とし、低電位を容量素子 105 に充電する。例えば、図 3 (C) の動作は、1 分に 1 回の割合で、充電に十分な時間をかけて行えばよい。

20

【0044】

上記説明のように本実施の形態の構成では、図 3 (A) の状態または図 3 (B) の状態と、図 3 (C) の状態とを繰り返すものの、図 3 (B) の状態を保持する期間が長くなる。

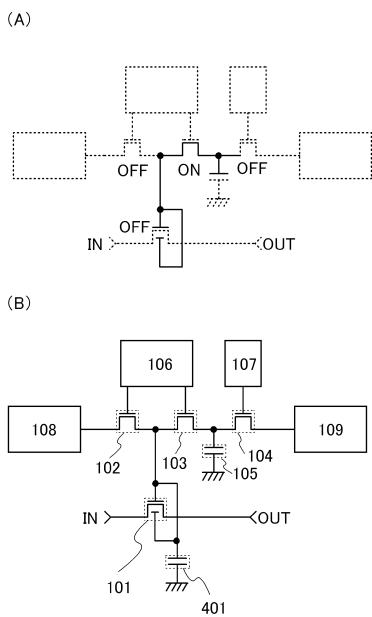

【0045】

ここで、図 4 (A) を用いて本実施の形態の効果について詳述する。図 4 (A) は、上述した図 3 (B) の状態におけるパワー MOSFET 101 の第 1 のゲート及び第 2 のゲートに接続されたノード、電界効果トランジスタ 103、並びに容量素子 105 の一方の端子を実線で表して示し、それ以外の接続を破線で示したものである。

【0046】

電界効果トランジスタ 102 及び電界効果トランジスタ 104 が非導通となることにより、パワー MOSFET 101 の第 1 のゲート及び第 2 のゲートに接続されたノードは、電気的に浮遊状態（フローティング状態）となる。上述したように電界効果トランジスタ 102 及び電界効果トランジスタ 104 は、チャネル領域を i 型化または実質的に i 型化された酸化物半導体層で構成しているため、オフ電流が極めて小さい。このため、パワー MOSFET 101 の第 1 のゲート及び第 2 のゲートに接続されたノードは、低電圧発生源 109 から容量素子 105 に充電された低電位を長期間保持することができる。恒常に容量素子に低電位を印加せず、間欠的に容量素子に低電位を印加すればよい。また、パワー MOSFET 101 の第 1 のゲート及び第 2 のゲートに低電位が印加されるとパワー MOSFET 101 はオフ状態となる。このため、本実施の形態の半導体装置は、消費電力の増加を招くことなく、パワー MOSFET 101 のオフの状態を実現することができる。

30

【0047】

また、図 2 (C) に示す半導体装置において、パワー MOSFET 101 の第 1 のゲート及び第 2 のゲートに接続されたノードの電位の保持特性を高めるために、図 4 (B) に示すように別途、第 1 のゲート及び第 2 のゲートに接続されたノードに容量素子 401 を設ける構成としてもよい。なお、図 2 (A) 及び図 2 (B) に示す半導体装置においては、パワー MOSFET 101、パワー素子 121 のゲートに容量素子 401 を設ける構成としてもよい。

40

【0048】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、または置き換えなどを自由に行うことができる。

50

## 【0049】

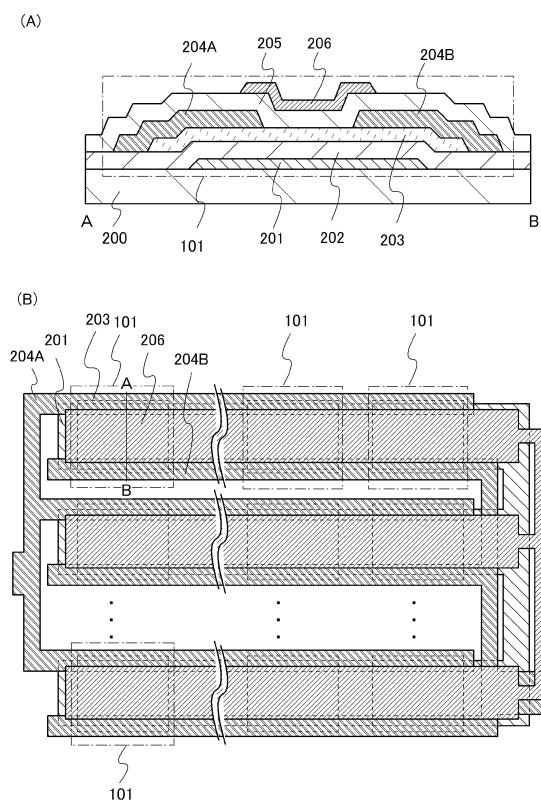

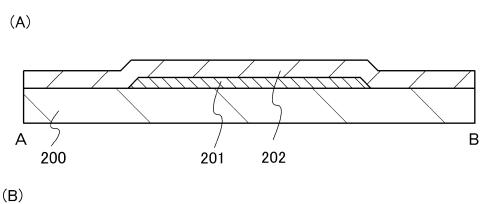

(実施の形態2)

本実施の形態では、実施の形態1に示すパワーMOSFET101の構造及び作製方法について、図5乃至図7を用いて説明する。

## 【0050】

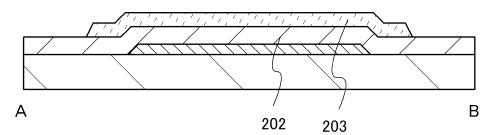

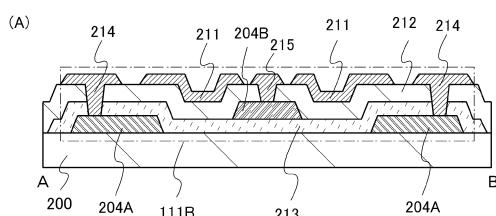

図5(A)に、実施の形態1に示すパワーMOSFET101の断面構成の一形態を示し、図5(B)にパワーMOSFET101の上面図を示す。図5(B)のA-Bの断面図が図5(A)に相当する。

## 【0051】

図5(A)に示すパワーMOSFET101は、基板200上に導電層でなる第1のゲート201が設けられ、第1のゲート201上にゲート絶縁層202が設けられ、ゲート絶縁層202上にn型である酸化物半導体層203が設けられ、酸化物半導体層203上を一部覆って導電層でなる第1の端子204A及び第2の端子204Bが設けられ、酸化物半導体層203、第1の端子204A、及び第2の端子204Bを覆って絶縁層205が設けられ、絶縁層205上に、第1の端子204A及び第2の端子204Bそれぞれの一部に重畠する導電層でなる第2のゲート206が設けられるように形成される。

## 【0052】

基板200は、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。基板200としてガラス基板を用いる場合、歪み点が730以上的ものを用いることが好ましい。ガラス基板には、例えば、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられる。なお、B<sub>2</sub>O<sub>3</sub>よりBaOを多く含むガラス基板を用いることが好ましい。

## 【0053】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いることができる。他にも、結晶化ガラスなどを用いることができる。さらには、シリコンウェハ等の半導体基板の表面や金属材料よりなる導電性の基板の表面に絶縁層を形成したものを用いることもできる。

## 【0054】

なお、図5(A)には図示していないが、基板200及び第1のゲート201の間に熱伝導率の高い絶縁層を形成することで、耐熱性の高いパワーMOSFET101を作製することができる。熱伝導率の高い絶縁層としては、窒化アルミニウム層、窒化酸化アルミニウム層、窒化シリコン層等がある。

## 【0055】

第1のゲート201は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金などを用いて形成することができる。また、マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか一または複数から選択された金属元素を用いてもよい。また、第1のゲート201は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム層の単層構造、アルミニウム層上にチタン層を積層する二層構造、窒化チタン層上にチタン層を積層する二層構造、窒化チタン層上にタンゲステン層を積層する二層構造、チタン層と、そのチタン層上にアルミニウム層を積層し、さらにその上にチタン層を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の層、または複数組み合わせた合金層、もしくは窒化物層を用いてもよい。

## 【0056】

また、第1のゲート201は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を適用することもできる。また

10

20

30

40

50

、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

【0057】

ゲート絶縁層202は、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、または酸化アルミニウム層を単層でまたは積層して形成することができる。ゲート絶縁層202は、酸化物半導体層203と接する部分が酸素を含むことが好ましく、特に好ましくは酸化シリコン層により形成する。酸化シリコン層を用いることで、酸化物半導体層203に酸素を供給することができ、特性を良好にすることができる。

【0058】

また、ゲート絶縁層202は、ハフニウムシリケート( $HfSiO_x$ )、窒素が添加されたハフニウムシリケート( $HfSi_xO_yN_z$ )、窒素が添加されたハフニウムアルミニート( $HfAl_xO_yN_z$ )、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用いることでゲートリーク電流を低減できる。さらには、high-k材料と、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、または酸化アルミニウム層のいずれか一以上との積層構造とすることができる。ゲート絶縁層202の厚さは100nm以上300nmとすることができる。

10

【0059】

n型である酸化物半導体層203は、四元系金属酸化物であるIn-Sn-Ga-Zn-O系金属酸化物や、三元系金属酸化物であるIn-Ga-Zn-O系金属酸化物、In-Sn-Zn-O系金属酸化物、In-Al-Zn-O系金属酸化物、Sn-Ga-Zn-O系金属酸化物、Al-Ga-Zn-O系金属酸化物、Sn-Al-Zn-O系金属酸化物や、二元系金属酸化物であるIn-Zn-O系金属酸化物、Sn-Zn-O系金属酸化物、Al-Zn-O系金属酸化物、Zn-Mg-O系金属酸化物、Sn-Mg-O系金属酸化物、In-Mg-O系金属酸化物などを用いることができる。ここでは、n元系金属酸化物はn種類の金属酸化物で構成される。なお、酸化物半導体層には、不純物として、主成分とする金属酸化物以外の元素が1%、好ましくは0.1%入ってもよい。

20

【0060】

また、n型である酸化物半導体層203は、三元系金属酸化物であり、 $InM_xZn_yO_z$ ( $Y = 0.5 \sim 5$ )で表現される金属酸化物を用いてもよい。ここで、Mは、ガリウム(Ga)やアルミニウム(Al)やボロン(B)などの13族元素から選択される—または複数種類の元素を表す。なお、In、M、Zn、及びOの含有量は任意であり、Mの含有量がゼロ(即ち、 $x = 0$ )の場合を含む。一方、In及びZnの含有量はゼロではない。すなわち、上述の表記には、In-Ga-Zn-O系金属酸化物やIn-Zn-O系金属酸化物半導体などが含まれる。

30

【0061】

また、n型である酸化物半導体層203を形成する金属酸化物は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。

【0062】

n型である酸化物半導体層203は、非晶質構造、微結晶構造、多結晶構造、または単結晶構造の酸化物半導体を適宜用いることができる。また、表面に垂直な方向にc軸がほぼ平行な結晶を有する酸化物半導体を用いることができる。

40

【0063】

n型である酸化物半導体層203は、キャリア密度が $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{17} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下である。酸化物半導体において、水素及び酸素欠損がドナーとして寄与するため、水素濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ であることが好ましい。

【0064】

また、n型である酸化物半導体層203の厚さは、第1のゲート及び第2のゲートに負の電圧が印加されたときに、空乏層がチャネル領域に広がり、パワーMOSFET101をオフ状態とすることが可能な厚さとする。キャリア密度が $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{20} \text{ cm}^{-3}$ 以下、誘電率が15、バンドギャップが3.15、伝導帯の実効状態密

50

度が  $N_c = 2.8 \times 10^{19} \text{ cm}^{-3}$  、価電子帯の実効状態密度が  $N_v = 1.04 \times 10^{19} \text{ cm}^{-3}$  であり、酸化物半導体層の一方の面側にゲートがある場合、最大空乏層幅は  $7 \text{ nm}$  以上  $677 \text{ nm}$  以下である。図 5 (A) に示すパワー MOSFET は第 1 のゲート 201 及び第 2 のゲート 206 を有するため、n 型である酸化物半導体層 203 の厚さを  $14 \text{ nm}$  以上  $1354 \text{ nm}$  以下とすることができます。また、キャリア密度が  $1 \times 10^{17} \text{ cm}^{-3}$  以上  $1 \times 10^{20} \text{ cm}^{-3}$  以下の場合、最大空乏層幅は  $7 \text{ nm}$  以上  $218 \text{ nm}$  以下である。この場合は、n 型である酸化物半導体層 203 の厚さを  $14 \text{ nm}$  以上  $436 \text{ nm}$  以下とすることができます。

【 0 0 6 5 】

第1の端子204A及び第2の端子204Bは、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた金属元素、上述した金属元素を成分とする合金、または上述した金属元素を組み合わせた合金などを用いて形成することができる。また、マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか一または複数から選択された金属元素を用いててもよい。また、第1の端子204A及び第2の端子204Bは、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム層の単層構造、アルミニウム層上にチタン層を積層する二層構造、窒化チタン層上にチタン層を積層する二層構造、窒化チタン層上にタンゲステン層を積層する二層構造、窒化タンタル層上にタンゲステン層を積層する二層構造、チタン層と、そのチタン層上にアルミニウム層を積層し、さらにその上にチタン層を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の層、または複数組み合わせた合金層、もしくは窒化物層を用いててもよい。

[ 0 0 6 6 ]

また、第1の端子204A及び第2の端子204Bは、インジウム錫酸化物、酸化タンゲスタンを含むインジウム酸化物、酸化タンゲスタンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

〔 0 0 6 7 〕

絶縁層 205 は、ゲート絶縁層 202 に示す材料を適宜用いることができる。

【 0 0 6 8 】

第2のゲート206は、第1のゲート201に示す材料を適宜用いることができる。

〔 0 0 6 9 〕

図5に示すパワーMOSFET101は、チャネル領域にn型である酸化物半導体層を有するため、オン抵抗を低減することが可能であり、大電流を流すことが可能である。しかしながら、n型である酸化物半導体層をチャネル領域に有するため、デプレッション型であり、ゲートに電圧を印加しない状態であっても電流が流れるノーマリーオン状態である。本実施の形態に示すパワーMOSFETは、第1のゲート201と共に、第2のゲート206を有し、第1のゲート201及び第2のゲート206に負の電圧を印加することでオフさせることができる。このため、オン抵抗が低く、大電流を流すことが可能であるパワーMOSFETのオフ状態を実現させることができる。一方、第1のゲート201及び第2のゲート206に正の電圧を印加することでオンさせることができる。また、パワーMOSFET101は第1のゲート201及び第2のゲート206を有するため、シングルゲートのパワーMOSFETと比較して、チャネル領域の厚さを厚くすることが可能であり、大電流を流すことが可能である。

【 0 0 7 0 】

また、図5（B）に示すように、パワーMOSFET101を並列に接続することで、トランジスタのチャネル幅Wを大きくするように設計することができる。このため、大電流を流すことが可能なパワーデバイスを作製することができる。

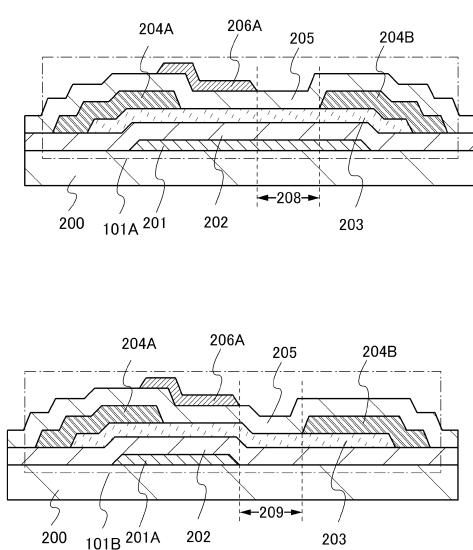

## 【0071】

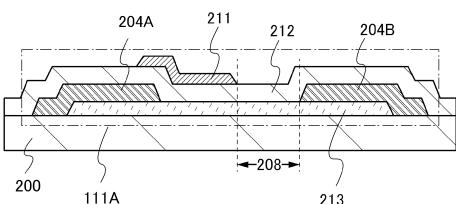

次に、図6に、図5とは異なるパワーMOSFETの断面構成を示す。図6(A)に示すパワーMOSFET101Aは、第2のゲート206Aが第1の端子204A及び第2の端子204Bの一方と重畠し、他方と重畠しないことを特徴とする。

## 【0072】

図6(A)に示すパワーMOSFET101Aは、基板200上に導電層でなる第1のゲート201が設けられ、第1のゲート201上にゲート絶縁層202が設けられ、ゲート絶縁層202上にn型である酸化物半導体層203が設けられ、酸化物半導体層203上を一部覆って導電層でなる第1の端子204A、第2の端子204Bが設けられ、酸化物半導体層203、第1の端子204A、及び第2の端子204Bを覆って絶縁層205が設けられるように形成される。また、絶縁層205上に、第1の端子204A及び第2の端子204B一方に重畠し、他方に重畠しない、導電層でなる第2のゲート206Aが設けられるように形成される。即ち、酸化物半導体層203が、第2のゲート206Aと、第1の端子204Aと、第2の端子204Bと重畠しない領域208が形成される。

10

## 【0073】

第2のゲート206Aは、図5に示す第2のゲート206と同様の材料及び作製方法を用いて形成することができる。

## 【0074】

図6(B)に示すパワーMOSFET101Bは、基板200上に導電層でなる第1のゲート201Aが設けられ、第1のゲート201A上にゲート絶縁層202が設けられ、ゲート絶縁層202上にn型である酸化物半導体層203が設けられ、酸化物半導体層203上を一部覆って導電層でなる第1の端子204A、第2の端子204Bが設けられ、酸化物半導体層203、第1の端子204A、及び第2の端子204Bを覆って絶縁層205が設けられるように形成される。また、絶縁層205上に、第1の端子204A及び第2の端子204B一方に重畠し、他方に重畠しない、導電層でなる第2のゲート206Aが設けられるように形成される。即ち、酸化物半導体層203が、第1のゲート201Aと、第2のゲート206Aと、第1の端子204Aと、第2の端子204Bと重畠しないオフセット領域209が形成される。

20

## 【0075】

第1のゲート201Aは、図5に示す第1のゲート201と同様の材料及び作製方法を用いて形成することができる。

30

## 【0076】

図6に示すパワーMOSFET101A及びパワーMOSFET101Bは、n型である酸化物半導体層203をチャネル領域に有するため、オン抵抗を低減することが可能であり、大電流を流すことが可能である。しかしながら、n型である酸化物半導体層をチャネル領域に有するため、デプレッション型であり、ゲートに電圧を印加しない状態であっても電流が流れるノーマリーオン状態である。本実施の形態に示すパワーMOSFETは、第1のゲート201または201Aと共に、第2のゲート206Aを有し、第1のゲート201または201A及び第2のゲート206Aに負の電圧を印加することでオフさせることができ、第1のゲート201または201A及び第2のゲート206Aに正の電圧を印加することでオンさせることができ。このため、オン抵抗が低く、大電流を流すことが可能であるパワーMOSFETのオフ状態を実現させることができる。また、第1のゲート201または201A及び第2のゲート206Aを有するため、シングルゲートのパワーMOSFETと比較して、チャネル領域の厚さを厚くすることが可能であり、大電流を流すことが可能である。更に、図6(B)に示すパワーMOSFET101Bにおいては、n型である酸化物半導体において、第1のゲート201A、第2のゲート206A、第1の端子204A、及び第2の端子204Bに覆われないオフセット領域209を有するため、図5(A)に示すパワーMOSFET101と比較して、ドレイン耐圧を高めることができ、第1の端子204Aまたは第2の端子204Bに高い電圧を印加することができる。

40

50

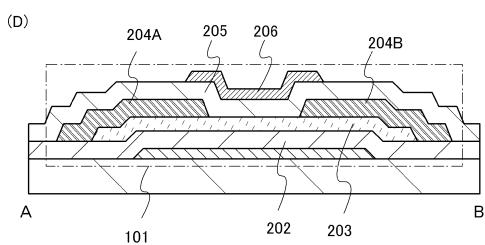

## 【0077】

ここで、図5に示すパワーMOSFET101の作製方法について、図7を用いて説明する。

## 【0078】

図7(A)に示すように、基板200上に、第1のゲート201を形成する。次に、第1のゲート201上に、ゲート絶縁層202を形成する。

## 【0079】

第1のゲート201は、印刷法、インクジェット法等を用いて作製することで、工程数を削減することができる。または、スパッタリング法、CVD法、蒸着法等により導電層を形成した後、フォトリソグラフィ工程により形成したレジストをマスクとして導電層をエッチングして、第1のゲート201を形成することができる。なお、第1のゲート201は端部がテーパー形状であると、のちに形成する絶縁層、半導体層、及び導電層の被覆率を高めることができるために好ましい。また、基板200と第1のゲート201の間に、熱伝導率の高い絶縁層を、スパッタリング法、CVD法、塗布法、印刷法等により形成することが好ましい。

10

## 【0080】

ゲート絶縁層202は、スパッタリング法、CVD法、印刷法、塗布法等により形成することができる。または、 $\mu$ 波(例えば、周波数2.45GHz)を用いた高密度プラズマCVDにより、緻密で絶縁耐圧の高い高品質なゲート絶縁層202を形成できる。酸化物半導体層と高品質なゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好とすることができます。また、高密度プラズマCVDにより得られたゲート絶縁層202は、一定の厚さで形成できるため、段差被覆性に優れている。また、高密度プラズマCVDにより得られるゲート絶縁層202は、厚さを精密に制御することができる。

20

## 【0081】

次に、図7(B)に示すように、ゲート絶縁層202上にn型である酸化物半導体層203を形成する。n型である酸化物半導体層203は、印刷法、インクジェット法等を用いて作製することで、工程数を削減することができる。または、ゲート絶縁層202上に、スパッタリング法、CVD法、塗布法、パルスレーザー蒸着法等によりn型である酸化物半導体層を形成した後、フォトリソグラフィ工程により形成したレジストをマスクとして上記酸化物半導体層をエッチングして、島状のn型である酸化物半導体層203を形成することができる。

30

## 【0082】

酸化物半導体層のキャリア密度は、成膜条件における原料ガス及びターゲットの水素濃度及び酸素濃度、成膜する材料及びその組成などに依存する。酸化物半導体層の水素濃度を高くする、または、酸化物半導体層の酸素濃度を低くし酸素欠損を含ませることで、ドナーとして寄与する水素または酸素欠損を酸化物半導体層に含有させることができるので、n型である酸化物半導体層を形成することができる。

## 【0083】

なお、酸化物半導体層203を形成した後、加熱処理を行って、微結晶構造、多結晶構造、または単結晶構造の酸化物半導体層としてもよい。また、表面に垂直な方向にc軸がほぼ平行な結晶を有する結晶構造の酸化物半導体層としてもよい。

40

## 【0084】

次に、図7(C)に示すように、ソース電極及びドレイン電極として機能する第1の端子204A及び第2の端子204Bを形成する。第1の端子204A、及び第2の端子204Bは、印刷法、インクジェット法等を用いて作製することで、工程数を削減することができる。または、ゲート絶縁層202及び酸化物半導体層203上に、スパッタリング法、CVD法、蒸着法等により導電層を形成した後、フォトリソグラフィ工程により形成したレジストをマスクとして上記導電層をエッチングして、第1の端子204A及び第2の端子204Bを形成することができる。

## 【0085】

50

次に、図7(D)に示すように、ゲート絶縁層202、酸化物半導体層203、第1の端子204A、及び第2の端子204B上に絶縁層205を形成する。絶縁層205は、ゲート絶縁層202と同様に形成することができる。次に、絶縁層205上に第2のゲート206を形成する。第2のゲート206は、第1のゲートと同様に形成することができる。

#### 【0086】

以上の工程により、n型である酸化物半導体層をチャネル領域に有し、デプレッション型であるパワーMOSFET101を作製することができる。なお、上記作製工程において、第2のゲートのレイアウトを変更することで、図6(A)に示すパワーMOSFET101A又は図6(B)に示すパワーMOSFET101Bを作製することができる。

10

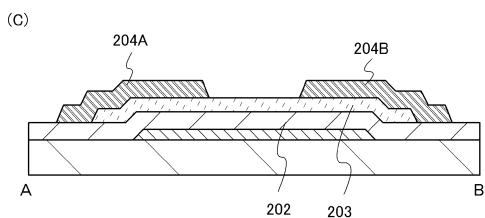

#### 【0087】

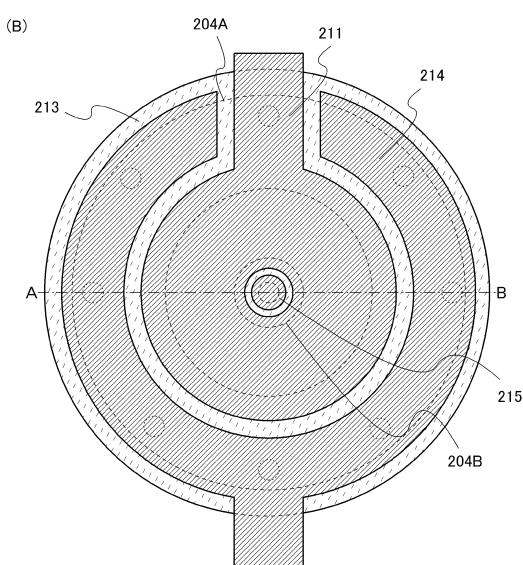

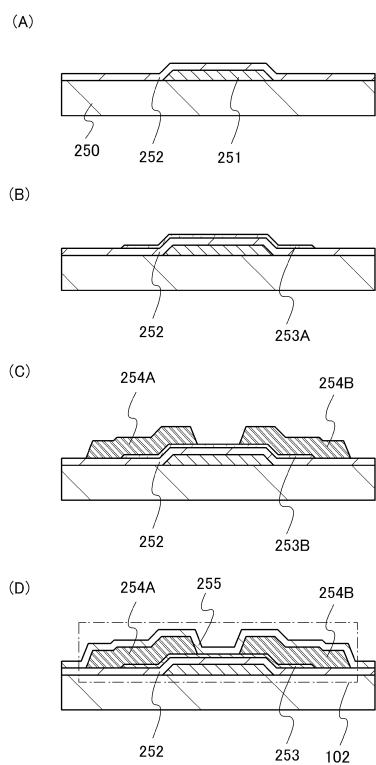

##### (実施の形態3)

本実施の形態では、実施の形態1及び実施の形態2に示すパワーMOSFET101の代わりに用いることが可能なパワーMOSFETの構造について、図8及び図9を用いて説明する。

#### 【0088】

図8及び図9に示すパワーMOSFETは、図6に示すパワーMOSFETと比較して、基板200及び酸化物半導体層213の間にゲートを有さない点が異なる。

#### 【0089】

図8に示すパワーMOSFET111Aは、基板200上にn型である酸化物半導体層213が設けられ、酸化物半導体層213上を一部覆って導電層でなる第1の端子204A、第2の端子204Bが設けられ、酸化物半導体層213、第1の端子204A、及び第2の端子204Bを覆ってゲート絶縁層212が設けられ、ゲート絶縁層212上に、第1の端子204A及び第2の端子204Bの一方の一部に重畳する導電層でなるゲート211が設けられるように形成される。即ち、酸化物半導体層213が、ゲート211と、第1の端子204Aと、第2の端子204Bと重畳しない領域208が形成される。

20

#### 【0090】

なお、実施の形態2に示すパワーMOSFET101と同様に、基板200及び酸化物半導体層213の間に熱伝導率の高い絶縁層を形成することで、耐熱性の高いパワーMOSFET111Aを作製することができる。また、第1の端子204A、及び第2の端子204Bを、基板200及び酸化物半導体層213の間に設けてもよい。また、図5(A)と同様に、領域208を有さず、第1の端子204A及び第2の端子204Bそれぞれの一部に重畳する導電層でなるゲート211が設けられてもよい。

30

#### 【0091】

図9(A)に示すパワーMOSFET111Bは、基板200上に導電層でなる第1の端子204Aが設けられ、導電層でなる第1の端子204Aを覆ってn型である酸化物半導体層213が設けられ、酸化物半導体層213上を一部覆って導電層でなる第2の端子204Bが設けられ、酸化物半導体層213及び第2の端子204Bを覆ってゲート絶縁層212が設けられ、ゲート絶縁層212上に、導電層でなるゲート211と、第1の端子204Aに接続する配線214と、第2の端子204Bに接続する配線215とが設けられるように形成される。

40

#### 【0092】

図9(B)は、図9(A)に示すパワーMOSFET111Bの上面図である。図9(B)のA-Bの断面図が図9(A)に相当する。図9(B)に示すように、第2の端子204B、及び第2の端子204Bに接続する配線215の周囲にゲート211が配置される。また、ゲート211の周囲に、第1の端子204A、及び第1の端子204Aに接続する配線214が配置される。

#### 【0093】

即ち、第1の端子204Aと、第2の端子204Bとは、重畳しない。ゲート211は、第1の端子204A及び第2の端子204Bと重畳しない領域を含む領域に設けられる。

50

また、ゲート 211 の一部（端部）は、第 1 の端子 204A 及び第 2 の端子 204B の一方または両方と重畠してもよい。

【0094】

なお、実施の形態 2 に示すパワー MOSFET 101 と同様に、基板 200 と、第 1 の端子 204A 及び酸化物半導体層 213 の間に熱伝導率の高い絶縁層を形成することで、耐熱性の高いパワー MOSFET 111B を作製することができる。

【0095】

図 8 及び図 9 に示す酸化物半導体層 213 は、実施の形態 2 に示す酸化物半導体層 203 と同様の材料を用いて形成することができる。なお、図 8 に示すパワー MOSFET 111A 及び図 9 に示すパワー MOSFET 111B は、ゲート 211 が酸化物半導体層 213 の一方の面側にしか形成されない。このため、酸化物半導体層 213 の厚さは、ゲート 211 に負の電圧が印加されたときに、空乏層がチャネル領域に広がり、パワー MOSFET 111B をオフ状態とすることが可能な厚さとするが、本実施の形態ではゲートの数が実施の形態 2 に示すパワー MOSFET 101 の半分のため、キャリア密度が  $1 \times 10^{16} \text{ cm}^{-3}$  以上  $1 \times 10^{20} \text{ cm}^{-3}$  以下の場合、最大空乏層幅は 7 nm 以上 677 nm 以下である。このため、n 型である酸化物半導体層 213 の厚さを 7 nm 以上 677 nm 以下とすることができます。また、キャリア密度が  $1 \times 10^{17} \text{ cm}^{-3}$  以上  $1 \times 10^{20} \text{ cm}^{-3}$  以下の場合、最大空乏層幅は 7 nm 以上 218 nm 以下である。この場合は、n 型である酸化物半導体層 213 の厚さを 7 nm 以上 218 nm 以下とすることができます。

10

20

【0096】

なお、図 8 及び図 9 に示すパワー MOSFET の作製方法は、図 8 及び図 9 に示す構成にあわせて、実施の形態 2 に示すパワー MOSFET の作製方法を適宜用いることができる。

【0097】

図 8 及び図 9 に示すパワー MOSFET は、チャネル領域に n 型である酸化物半導体層を有するため、オン抵抗を低減することが可能であり、大電流を流すことが可能である。しかしながら、n 型である酸化物半導体層をチャネル領域に有するため、デプレッション型であり、ゲートに電圧を印加しない状態であっても電流が流れるノーマリーオン状態である。本実施の形態に示すパワー MOSFET は、ゲート 211 に負の電圧を印加することでオフさせることができ、ゲート 211 に正の電圧を印加することでオンさせることができます。このため、オン抵抗が低く、大電流を流すことが可能であるパワー MOSFET のオフ状態を実現させることができます。

30

【0098】

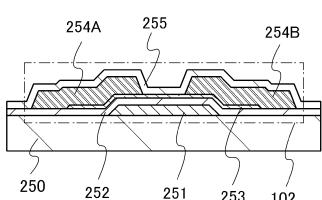

（実施の形態 4）

本実施の形態では、実施の形態 1 に示す電界効果トランジスタ 102 乃至電界効果トランジスタ 104 の構造及び作製方法について、図 10 及び図 11 を用いて説明する。電界効果トランジスタ 102 乃至電界効果トランジスタ 104 は、同じ構造でよいため、ここでは代表例として電界効果トランジスタ 102 を用いて説明する。

【0099】

40

図 10 に示す電界効果トランジスタ 102 は、基板 250 上に導電層でなるゲート 251 が設けられ、ゲート 251 上にゲート絶縁層 252 が設けられ、ゲート絶縁層 252 上に i 型化または実質的に i 型化された酸化物半導体層 253 が設けられ、酸化物半導体層 253 上を一部覆って導電層でなる第 1 の端子 254A 及び第 2 の端子 254B が設けられ、酸化物半導体層 253、第 1 の端子 254A、及び第 2 の端子 254B を覆って絶縁層 255 が設けられるように形成される。

【0100】

基板 250 は、実施の形態 2 に示す基板 200 を適宜用いることができる。

【0101】

ゲート 251 は、実施の形態 2 に示す第 1 のゲート 201 に示す材料を適宜用いることが

50

できる。

【0102】

ゲート絶縁層252は、実施の形態2に示すゲート絶縁層202に示す材料を適宜用いることができる。ゲート絶縁層252の厚さは、50nm以上500nm以下とすることができます。ゲート絶縁層252の厚さを厚くすることで、ゲートリーク電流を低減することができる。

【0103】

酸化物半導体層253は、実施の形態2に示す酸化物半導体層203に示す金属酸化物を用いることができる。また、非晶質構造、多結晶構造、または単結晶構造の酸化物半導体を適宜用いることができる。また、表面に垂直な方向にc軸がほぼ平行な結晶を有する結晶構造の酸化物半導体を用いることができる。但し、酸化物半導体層253はi型化または実質的にi型化されているため、キャリア密度が $5 \times 10^{14} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{12} \text{ cm}^{-3}$ 未満、より好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ 以下である。また、ドナーとして寄与する水素や酸素欠陥は少ないことが好ましく、水素濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 以下が好ましい。

10

【0104】

水素を徹底的に除去することにより高純度化され、酸素欠損を低減し化学量論比を満たすことでi型化または実質的にi型化された酸化物半導体層をチャネル領域に用いた電界効果トランジスタ102は、オフ電流が $1 \times 10^{-16} \text{ A}$ 以下とすることができます。つまり、電界効果トランジスタの非導通状態において、酸化物半導体層は絶縁体とみなせて回路設計を行うことができる。一方で、酸化物半導体層253は、電界効果トランジスタの導通状態においては、非晶質シリコンで形成される半導体層よりも高い電流供給能力を見込むことができる。このため電界効果トランジスタ102は、エンハンスマント型であり、オフ状態では極めてリーク電流の小さいノーマリーオフ状態となり、優れたスイッチング特性を有する。

20

【0105】

第1の端子254A及び第2の端子254Bは、実施の形態2に示す第1の端子204A及び第2の端子204Bに示す材料を適宜用いることができる。

【0106】

絶縁層255は、酸化絶縁層で形成することが好ましい。酸化絶縁層の代表例としては、酸化シリコン層、酸化窒化シリコン層、または酸化アルミニウム層がある。なお、絶縁層205を酸化絶縁層及び窒化絶縁層の積層構造としてもよい。窒化絶縁層の代表例としては、窒化シリコン層、窒化酸化シリコン層、または窒化アルミニウム層がある。絶縁層255において、酸化物半導体層253と接する領域を酸化絶縁層で形成することで、酸化物半導体層の酸素欠損を低減し、化学量論比を満たすことができる。

30

【0107】

なお、電界効果トランジスタ102は、様々な形態をとることができ、特定の構成に限定されない。例えば、ゲートが2個以上のマルチゲート構造を適用することができる。また、チャネル領域の上下にゲート電極が配置されている構造とすることができます。なお、チャネル領域の上下にゲートが配置される構成にすることにより、2つの電界効果トランジスタが並列に接続されたような構成とすることも可能である。

40

【0108】

ここで、図10に示す電界効果トランジスタ102の作製方法について、図11を用いて説明する。

【0109】

図11(A)に示すように、基板250上に、ゲート251を形成する。次に、ゲート251上に、ゲート絶縁層252を形成する。

【0110】

ゲート251は、実施の形態2に示す第1のゲート201の作製方法を適宜用いることができる。また、ゲート絶縁層252は、実施の形態2に示すゲート絶縁層202の作製方

50

法を適宜用いることができる。なお、*i*型化または実質的に*i*型化された酸化物半導体層は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁層252を、 $\mu$ 波を用いた高密度プラズマCVDで形成することで、界面準位を低減して界面特性を良好とすることができる。

【0111】

なお、ゲート絶縁層252を形成する際に、基板200を加熱することで、ゲート絶縁層252に含まれる水素、水、水酸基、水素化物などを低減することができる。

【0112】

また、ゲート絶縁層252に含まれる水素、水、水酸基、水素化物などを低減するため、スパッタリング法でゲート絶縁層252を形成する場合は、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつゲート絶縁層252を形成することが好ましい。処理室内に残留する水素、水、水酸基、水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。吸着型の真空ポンプの代表例は、クライオポンプ、イオンポンプ、チタンサブリメーションポンプである。また、排気手段としては、ターボポンプにコールドトラップを加えたものを用いることができる。

10

【0113】

また、ゲート絶縁層252を形成する際に用いるスパッタリングガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることで、ゲート絶縁層252に含まれる水素、水、水酸基、水素化物などを低減することができる。

20

【0114】

次に、図11(B)に示すように、ゲート絶縁層202上に酸化物半導体層253Aを形成する。酸化物半導体層253Aは、印刷法、インクジェット法等を用いて形成することができる。または、ゲート絶縁層252上に、スパッタリング法、CVD法、塗布法、パルスレーザー蒸着法等により酸化物半導体層を形成し、フォトリソグラフィ工程により形成したレジストをマスクとして上記酸化物半導体層をエッチングして、島状の酸化物半導体層253Aを形成することができる。

【0115】

酸化物半導体層のキャリア密度は、成膜条件における原料ガス及びターゲットの水素濃度及び酸素濃度、成膜する材料及びその組成、加熱処理条件などに依存する。酸化物半導体層の水素濃度を低くする、または、酸化物半導体層の酸素濃度を高くし酸素欠損を低減させることで、酸化物半導体層は、*i*型または実質的に*i*型となる。本実施の形態では、酸化物半導体層を*i*型化または実質的に*i*型化する処理を後に行うため、酸化物半導体層253Aは*i*型でも*n*型でもよい。

30

【0116】

なお、酸化物半導体層をスパッタリング法で形成する場合、基板を加熱することで、酸化物半導体層に含まれる水素、水、水酸基、水素化物などの不純物を低減することができる。また、第1の加熱処理において、結晶成長を促すことができる。

【0117】

また、酸化物半導体層をスパッタリング法で形成する場合、金属酸化物ターゲット中の金属酸化物の相対密度を80%以上、好ましくは95%以上、さらに好ましくは99.9%以上とすることで、酸化物半導体層中の不純物濃度を低減することができ、電気特性、及び信頼性の高いトランジスタを得ることができる。

40

【0118】

また、酸化物半導体層を形成する前にプレヒート処理を行うことで、スパッタリング装置内壁や、ターゲット表面やターゲット材料中に残存している水素、水、水酸基、水素化物等を除去できるため、酸化物半導体層に含まれる水素、水、水酸基、水素化物などの不純物を低減することができる。

【0119】

また、ゲート絶縁層252と同様に、酸化物半導体層を形成する前、または形成中、また

50

は形成後に、スパッタリング装置内に残存している水素、水、水酸基、水素化物などを除去するために、吸着型の真空ポンプを用いることが好ましい。この結果、水素、水、水酸基、水素化物などが排気されるため、酸化物半導体層に含まれる水素、水、水酸基、水素化物などの濃度を低減できる。

【0120】

次に、第1の加熱処理を行い、酸化物半導体層253Åに含まれる水素、水、水酸基、水素化物などの不純物を除去する。即ち、脱水化及び脱水素化の少なくとも一方を行なうことができる。なお、第1の加熱処理において、酸化物半導体層253Åの酸素欠損も形成される。第1の加熱処理により、水素、水、水酸基、水素化物などの不純物が除去された酸化物半導体層を、図11(C)において、酸化物半導体層253Bと示す。

10

【0121】

第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。加熱処理装置として、第1の加熱処理に用いる加熱処理装置は特に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、電気炉や、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。

20

【0122】

第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴンなどの希ガスに、水素、水、水酸基または水素化物などなどが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴンなどの希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0123】

また、第1の加熱処理において、昇温時には炉の内部を窒素雰囲気とし、冷却時には炉の内部を酸素雰囲気として雰囲気を切り替えてよく、窒素雰囲気で脱水または脱水素化が行われた後、雰囲気を切り替えて酸素雰囲気にすることで酸化物半導体層内部に酸素を補給でき、水素濃度が低減され、且つ酸素欠損が形成された酸化物半導体層の酸素欠損に酸素を供給することが可能であり、i型化または実質的にi型化された酸化物半導体層を形成することができる。

30

【0124】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層253Åは結晶化し、結晶を有する酸化物半導体層となる場合もある。例えば、結晶化率が90%以上、または80%以上の結晶を有する酸化物半導体層となる場合もある。

【0125】

また、第1の加熱条件、または酸化物半導体層の材料によっては、非晶質の酸化物半導体層の表層部に、表面に垂直な方向にc軸がほぼ平行な結晶を有する結晶構造が形成される酸化物半導体層となる場合もある。

40

【0126】

なお、第1の加熱処理は、酸化物半導体層上に第1の端子及び第2の端子を形成した後に行ってよい。

【0127】

ここでは、電気炉に基板を導入し、窒素、希ガスなどの不活性ガス雰囲気において450で1時間の加熱処理を行う。

【0128】

次に、図11(C)に示すように、ソース電極及びドレイン電極として機能する第1の端

50

子 2 5 4 A 及び第 2 の端子 2 5 4 B を形成する。

【 0 1 2 9 】

第 1 の端子 2 5 4 A 及び第 2 の端子 2 5 4 B は、実施の形態 2 に示す第 1 の端子 2 0 4 A 及び第 2 の端子 2 0 4 B と同様に形成することができる。

【 0 1 3 0 】

次に、図 1 1 ( D ) に示すように、ゲート絶縁層 2 5 2 、酸化物半導体層 2 5 3 B 、第 1 の端子 2 5 4 A 及び第 2 の端子 2 5 4 B 上に絶縁層 2 5 5 を形成する。絶縁層 2 5 5 は、スパッタリング法、CVD 法、印刷法、塗布法等により形成することができる。なお、絶縁層 2 5 5 として、スパッタリング法により酸化シリコン層を形成すると、酸化シリコン層から第 1 の加熱処理で発生した酸化物半導体層 2 5 3 A に含まれる酸素欠損に酸素を供給することができ、ドナーとして寄与する酸素欠損を低減し、化学量論比を満たす構成とすることが可能である。この結果、i 型化または実質的に i 型化された酸化物半導体層 2 5 3 を形成することができる。10

【 0 1 3 1 】

次に、不活性ガス雰囲気、または酸素ガス雰囲気で、第 2 の加熱処理（好ましくは 2 0 0 以上 4 0 0 以下、例えば 2 5 0 以上 3 5 0 以下）を行う。第 2 の加熱処理は、絶縁層 2 5 5 上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。当該加熱処理により、絶縁層 2 5 5 の酸化絶縁層から第 1 の加熱処理で発生した酸化物半導体層に含まれる酸素欠損に酸素を供給することができ、ドナーとして寄与する酸素欠損を低減し、化学量論比を満たす構成とすることが可能である。この結果、より i 型化または実質的に i 型化された酸化物半導体層 2 5 3 を形成することができる。20

【 0 1 3 2 】

本実施の形態では、窒素雰囲気において 2 5 0 で 1 時間の第 2 の加熱処理を行う。

【 0 1 3 3 】

さらに、大気中で 1 0 0 以上 2 0 0 以下の加熱処理を 1 時間以上 3 0 時間以下、行ってもよい。当該加熱処理により、電界効果トランジスタの信頼性を高めることができる。

【 0 1 3 4 】

以上の工程により、i 型化または実質的に i 型化された酸化物半導体層をチャネル領域に有し、オフ電流が極めて小さく、エンハンスメント型である電界効果トランジスタ 1 0 2 を作製することができる。30

【 0 1 3 5 】

( 実施の形態 5 )

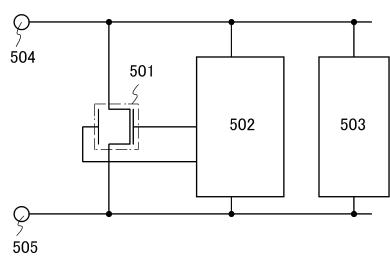

図 1 2 に、実施の形態 1 乃至実施の形態 3 に示すパワー素子を保護素子に用いた半導体装置の一形態を示す。保護素子は、電源端子に過電圧が入力された際に、保護素子であるパワー素子に電流を流して、保護対象回路に過電流が流れないように機能する。保護対象回路は過電圧の印加により破壊される耐圧の低い回路を全て含む。本実施の形態では、パワー素子の一例として、実施の形態 1 及び実施の形態 2 に示す 4 端子のパワー MOSFET を用いて説明する。

【 0 1 3 6 】

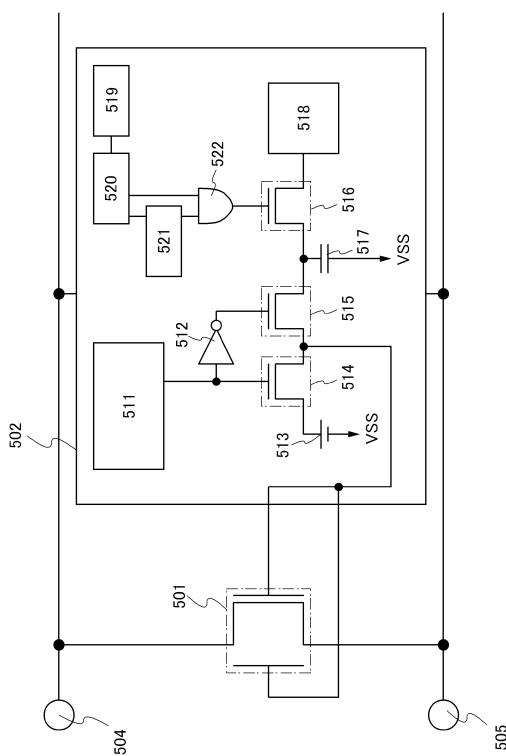

図 1 2 は、パワー MOSFET 5 0 1 、制御回路 5 0 2 、保護対象回路 5 0 3 、入力端子 5 0 4 、及び出力端子 5 0 5 を有する半導体装置である。制御回路 5 0 2 は、入力端子 5 0 4 または出力端子 5 0 5 に印加された過電圧を検知して、保護素子となるパワー MOSFET 5 0 1 の動作を制御するものである。40

【 0 1 3 7 】

図 1 3 は、制御回路 5 0 2 に詳細を示したものである。制御回路 5 0 2 は、過電圧検出回路 5 1 1 、インバータ 5 1 2 、正電源 5 1 3 、スイッチトランジスタ 5 1 4 、5 1 5 、5 1 6 、容量素子 5 1 7 、負電圧発生回路 5 1 8 、発振回路 5 1 9 、分周回路 5 2 0 、遅延回路 5 2 1 、AND 回路 5 2 2 より構成されている。正電源 5 1 3 は、実施の形態 1 に示す高電圧発生源 1 0 8 に相当する。スイッチトランジスタ 5 1 4 、5 1 5 、5 1 6 はそれぞれ、実施の形態 1 に示す電界効果トランジスタ 1 0 2 、1 0 3 、1 0 4 に相当する。容50

量素子 517 は、実施の形態 1 に示す容量素子 105 に相当する。また、負電圧発生回路 518 は実施の形態 1 に示す低電圧発生源 109 に相当する。発振回路 519、分周回路 520、遅延回路 521、及び AND 回路 522 は、実施の形態 1 に示すリフレッシュ制御回路 107 に相当する。なお、制御回路 502 は当該構成に限定されるものではない。

【0138】

次に、図 13 に示す制御回路 502 及びパワー MOSFET 501 の動作について説明する。過電圧検出回路 511 は通常の電源電圧を大きく超えるような過電圧が入力端子 504 に入力されたときに動作する回路であり、本実施の形態では過電圧が入力された際にハイのパルスを出力する機能を有する。

【0139】

過電圧検出回路 511 の出力端子は、スイッチトランジスタ 514 のゲート端子及びインバータ 512 の入力端子に接続される。インバータ 512 の出力端子は、スイッチトランジスタ 515 のゲート端子に接続される。これによって、過電圧が入力されるとスイッチトランジスタ 514 がオンして、パワー MOSFET 501 のゲート端子は、正電源 513 に接続され、パワー MOSFET 501 はオンする。これによって入力端子 504 から出力端子 505 に電流が流れ、図 12 に示す保護対象回路 503 に過電流が流れるのを防止する。

【0140】

過電圧が印加されていないときには、過電圧検出回路 511 の出力はロウであり、スイッチトランジスタ 514 はオフ、スイッチトランジスタ 515 はオンとなる。負電圧発生回路 518 は、図 17 に示すチャージポンプ回路などで構成され、負電圧を発生させる。

【0141】

保護回路は頻繁に動作する回路ではないので、恒常的に大電流を流すようにするのは消費電力の面から適切ではない。従って小さな電流能力で、容量素子 517 にチャージを蓄えることが、消費電力削減に有効である。従って、間欠的に負電圧発生回路 518 よりスイッチトランジスタ 516 を介して容量素子 517 に充電を行うことで消費電力を低減することができる。

【0142】

発振回路 519 によって得られた発振信号を分周回路 520 で分周し、分周された信号は、スイッチトランジスタ 516 のゲート端子に供給される。即ち、分周回路 520 の出力端子の一方は、AND 回路 522 の第 1 の入力端子に接続する。また、分周回路 520 の出力端子の他方は、遅延回路 521 を介して AND 回路 522 の第 2 の入力端子に接続する。このようにして、遅延回路 521 の遅延時間分のパルス幅を有し、周期が分周回路 520 の出力と同様のパルスを得ることができる。当該パルスを用いることによって、スイッチトランジスタ 516 のゲート端子を制御することができる。

【0143】

発振回路 519 は、一般的な発振回路、例えばリングオシレータなどを使用することができるがその種類は限定しない。また、分周回路 520 は、フリップフロップを使用することができる。遅延回路 521 は、インバータを使った回路、CR 遅延回路を使った回路等が使用できるが特に限定されない。また、パルスの形成方法はこれ以外の方法を用いることもできる。

【0144】

このようにして、容量素子 517 には負電圧が保持され、過電圧が印加されないときには、スイッチトランジスタ 515 を介してパワー MOSFET 501 に負電圧が印加される。パワー MOSFET 501 のゲート端子に負電圧が印加されている間は、パワー MOSFET 501 はオフになり電流を流さない。

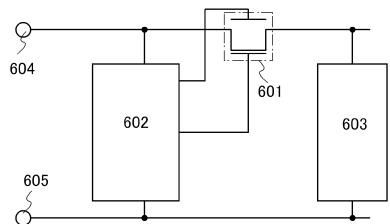

【0145】

図 14 は、パワー MOSFET を保護対象回路と直列に接続した半導体装置である。図 12 とは異なり、入力端子に過電圧が印加されたときには、パワー MOSFET 601 がオフとなり保護対象回路 603 に過電圧がかかるのを防止する。

10

20

30

40

50

## 【0146】

図14に示す半導体装置は、パワーMOSFET601、制御回路602、保護対象回路603、入力端子604、出力端子605からなっている。制御回路602は、入力端子604または出力端子605に印加された過電圧を検知して、保護素子となるパワーMOSFET601を制御するものである。

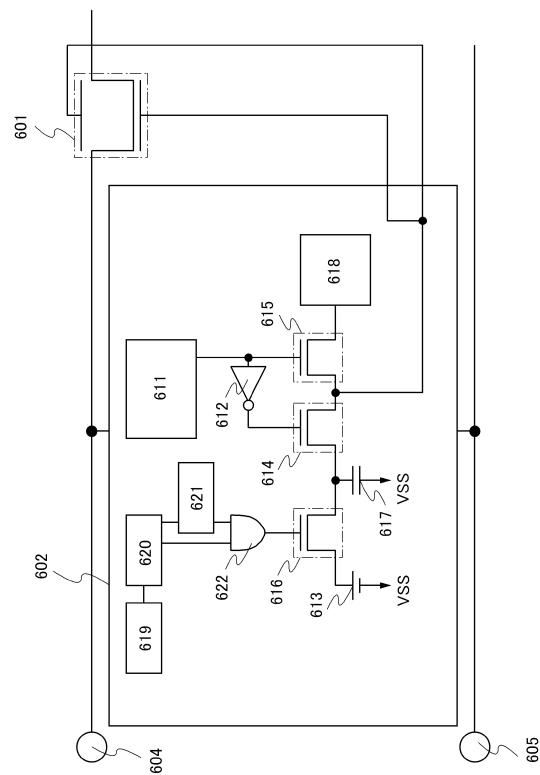

## 【0147】

図15に制御回路602詳細を示す。制御回路602は、過電圧検出回路611、インバータ612、正電源613、スイッチトランジスタ614、615、616、容量素子617、負電圧発生回路618、発振回路619、分周回路620、遅延回路621、AND回路622より構成されている。正電源613は、実施の形態1に示す高電圧発生源108に相当する。スイッチトランジスタ614、615、616はそれぞれ、実施の形態1に示す電界効果トランジスタ103、102、104に相当する。容量素子617は、実施の形態1に示す容量素子105に相当する。また、負電圧発生回路618は実施の形態1に示す低電圧発生源109に相当する。発振回路619、分周回路620、遅延回路621、及びAND回路622は、実施の形態1に示すリフレッシュ制御回路107に相当する。なお、制御回路602は当該構成に限定されるものではない。

## 【0148】

次に、図15に示す制御回路602及びパワーMOSFET601の動作について説明する。過電圧検出回路611は通常の電源電圧を大きく超えるような過電圧が入力端子604に入力されたときに動作する回路であり、本実施の形態では過電圧が入力された際にハイのパルスを出力する機能を有する。

## 【0149】

過電圧検出回路611の出力端子は、スイッチトランジスタ615のゲート端子とインバータ612に接続される。インバータ612の出力端子は、スイッチトランジスタ614のゲート端子に接続される。これによって、入力端子604に過電圧が入力されると、スイッチトランジスタ615がオンして、パワーMOSFET601のゲート端子は、負電圧発生回路618に接続され、オフする。これによって入力端子604及び保護対象回路603は分断され、保護対象回路603に過電流が流れるのを防止する。負電圧発生回路618は、図17に示すチャージポンプ回路などで構成され、負電圧を発生させる。

## 【0150】

過電圧が印加されていないときには、過電圧検出回路611の出力はロウであり、スイッチトランジスタ615はオフ、スイッチトランジスタ614はオンとなり、パワーMOSFET601のゲート端子は容量素子617に接続される。容量素子617には後述するように正電源から正電圧が保持されているため、パワーMOSFET601はオンする。

## 【0151】

保護回路は頻繁に動作する回路ではないので、恒常に大電流を流すようにするのは消費電力の面から適切ではない。従って、小さな電流能力で、容量素子617にチャージを蓄えることが、消費電力削減に有効である。従って、間欠的に正電源613よりスイッチトランジスタ616を介して容量素子617に充電を行うことで消費電力を低減することができる。

## 【0152】

発振回路619によって得られた発振信号を分周回路620で分周し、分周した信号は、スイッチトランジスタ616のゲート端子に供給される。即ち、分周回路620の出力端子の一方は、AND回路622の第1の入力端子に接続する。また、分周回路620の出力端子の他方は、遅延回路621を介してAND回路622の第2の入力端子に接続する。このようにして遅延回路621の遅延時間分のパルス幅を有し、周期が分周回路620の出力と同様のパルスを得ることができる。当該パルスを用いることによって、スイッチトランジスタ616のゲート端子を制御することができる。

## 【0153】

発振回路619は、一般的な発振回路たとえばリングオシレータなどが使用することがで

10

20

30

40

50

きるがその種類は限定しない。また、分周回路 620 は、フリップフロップを使用することができる。遅延回路 621 は、インバータを使った回路、C R 遅延回路を使った回路等が使用できるが特に限定されない。また、パルスの形成方法はこれ以外の方法を用いたものでも良い。

【0154】

このようにして、容量素子 617 には正電圧が保持され、過電圧が加えられないときには、スイッチトランジスタ 614 を介して正電圧がパワー MOSFET 601 に印加される。パワー MOSFET 601 のゲート端子に正電圧が印加されている間は、パワー MOSFET 601 はオンになり、入力端子 604 と図 14 に示す保護対象回路 603 が接続される。

10

【0155】

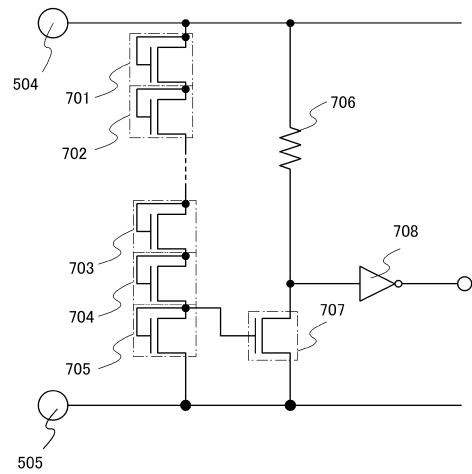

図 16 は、過電圧検出回路 511、611 の一構成例である。図 16 はトランジスタ 701 ~ 705 をダイオード接続したダイオードチェーンと、トランジスタ 707、抵抗 706、インバータ 708 より構成される。ダイオードチェーンの段数を  $n$  段としたとき、トランジスタのしきい値電圧を  $V_{th}$  とすると、通常の動作電圧  $< n V_{th}$  となるように  $n$  を設定し、過電圧が印加された場合にトランジスタ 701 ~ 705 がオンして、ダイオードチェーンに電流が流れるようになる。トランジスタ 705 がオンすると、トランジスタ 707 もオンし、インバータ 708 の出力からハイが出力される。

【0156】

本実施の形態では、バンドギャップが大きい酸化物半導体層をチャネル領域に用いた、ノーマリーオンのパワー MOSFET を保護素子に用いて、過電圧の印加による半導体装置の破壊を防止することができる。

20

【0157】

(実施の形態 6)

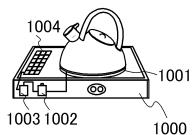

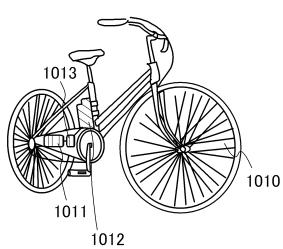

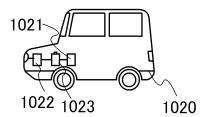

本実施の形態では、上記実施の形態で説明したパワーデバイスの用途について説明する。上記実施の形態で説明したパワーデバイスである半導体装置は、例えば、コンピュータ等の画像を表示しうるディスプレイなどの電子機器のバッテリーの保護回路の他、電磁調理器または固定電源の電力で駆動する乗物類（自転車等）等に設けるバッテリーの保護回路として使用することができる。

【0158】

30

図 18 を参照して、パワーデバイスであって保護回路として機能する半導体装置を備えた応用例の一例について説明する。

【0159】

図 18 (A) は、保護回路として機能する半導体装置を備えた応用例として、電磁調理器 1000 を示している。電磁調理器 1000 は、コイル部 1001 に電流を流すことによって生じる電磁誘導を利用して調理器等に加熱するものである。また電磁調理器 1000 は、コイル部 1001 に流す電流を供給するためのバッテリー 1002、保護回路として機能する半導体装置 1003、及びバッテリー 1002 を充電するための太陽電池 1004 を有する。なお図 18 (A) では、バッテリー 1002 を充電するための手段として太陽電池 1004 を示したが他の手段で充電する構成でもよい。保護回路として機能する半導体装置 1003 は、バッテリー 1002 への過電圧の印加を低減でき、保護回路の機能が非動作時における低消費電力化を図ることができる。

40

【0160】

図 18 (B) は、保護回路として機能する半導体装置を備えた応用例として、電動自転車 1010 を示している。電動自転車 1010 は、モーター部 1011 に電流を流すことによって動力を得るものである。また電動自転車 1010 は、モーター部 1011 に流す電流を供給するためのバッテリー 1012、及び保護回路として機能する半導体装置 1013 を有する。なお図 18 (B) では、バッテリー 1012 を充電するための手段として特に図示しないが、別途発電機等を設けて充電する構成でもよい。保護回路として機能する半導体装置 1013 は、充電時におけるバッテリー 1012 への過電圧の印加を低減でき

50

、保護回路の機能が非動作時における低消費電力化を図ることができる。なお、図18(C)ではペダルを図示したが、なくてもよい。

【0161】

図18(C)は、保護回路として機能する半導体装置を備えた応用例として、電気自動車1020を示している。電気自動車1020は、モーター部1021に電流を流すことによって動力を得るものである。また電気自動車1020は、モーター部1021に流す電流を供給するためのバッテリー1022、及び保護回路として機能する半導体装置1023を有する。なお図18(C)では、バッテリー1022を充電するための手段として特に図示しないが、別途発電機等を設けて充電する構成でもよい。保護回路として機能する半導体装置1023は、充電時におけるバッテリー1022への過電圧の印加を低減でき、保護回路の機能が非動作時における低消費電力化を図ることができる。

10

【0162】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、または置き換えなどを自由に行うことができる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

## 【図15】

### 【図16】

### 【図17】

### 【図18】

(A)

(B)

(C)

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/088 (2006.01) H 01 L 27/088 F

(56)参考文献 特開2007-134687 (JP, A)

特開2006-286772 (JP, A)

国際公開第2007/125671 (WO, A1)

特開2009-117619 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336, 29/786