## (19) World Intellectual Property Organization International Bureau

# (43) International Publication Date 24 July 2003 (24.07.2003)

#### **PCT**

# (10) International Publication Number WO 03/060960 A2

- (51) International Patent Classification<sup>7</sup>: H01L 21/00

- (21) International Application Number: PCT/EP02/14911

- (22) International Filing Date:

19 December 2002 (19.12.2002)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) **Priority Data:** 10/052,620 18 Januar

18 January 2002 (18.01.2002) US

- (71) Applicant (for all designated States except MC): INTERNATIONAL BUSINESS MACHINES CORPORATION [US/US]; New Orchard Road, Armonk, NJ 10504 (US).

- (71) Applicant (for MC only): COMPAGNIE IBM FRANCE [FR/FR]; Tour Descartes, La Défense 5, 2, Avenue Gambetta, F-9400 Courbevoie (FR).

- (72) Inventors: MAGERLEIN, John, Harold; 1424 Trout Brook Drive, Yorktown Heights, NY 10598 (US). PETRARCA, Kevin, Shawn; 28 Laurie Lane, Newburgh, NY 12550 (US). PURUSHOTHAMAN, Sampath; 2075 Lavoie Court, Yorktown Heights, NY 10598 (US). SAMBUCETTI, Carlos, Juan; 5 Sassi Drive, Croton-On-Hudson, NY 10520 (US). VOLANT, Richard, Paul; 16 Fulton Drive, New Fairfield, CT 06812 (US). WALKER, George, Frederick; Apartment 11K, 1540 York Avenue, New York, NY 10028 (US).

- (74) Agent: KLEIN, Daniel; Compagnie IBM France, Direction de la Propriété Intellectuelle, F-06610 La Gaude (FR).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

[Continued on next page]

$\textbf{(54) Title:} \ \textbf{HIGH DENSITY AREA ARRAY SOLDER MICROJOINING INTERCONNECT STRUCTURE AND FABRICATION \\ \textbf{METHOD}$

(57) Abstract: A system for interconnecting a set of device chips by means of an array of microjoints disposed on an interconnect carrier is taught. The carrier is provided with a dense array of microjoint receptacles with an adhesion layer, barrier layer and a noble metal layer; the device wafers are fabricated with an array of microjoining pads comprising an adhesion layer, barrier layer and a fusible solder layer with pads being located at matching locations in reference to the barrier receptacles; said device chips are joined to said carrier through the microjoint arrays resulting in interconnections capable of very high input/output density and inter-chip wiring density.

## WO 03/060960 A2

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# HIGH DENSITY AREA ARRAY SOLDER MICROJOINING INTERCONNECT STRUCTURE AND FABRICATION METHOD

#### FIELD OF THE INVENTION

This invention pertains to the field of microelectronics, 5 and more particularly to the field of fabricating and interconnecting extremely small semiconductor devices, commonly referred to as "chips."

#### BACKGROUND OF THE INVENTION

Increased levels of integration in the silicon transistor

10 technology over the last two decades have facilitated the migration from large scale integrated (LSI) to very large scale integrated (VLSI) and now to ultra-large scale integrated (ULSI) circuits for use in silicon chips for computing, communication and micro controller applications.

15 Optimum utilization of these highly integrated silicon chips requires a more space efficient packaging with supporting devices such as memory chips. Further, with the advent of mobile communication devices, hand held organizers and computing devices, there has also been a push to integrate such varied functions into a single compact system. This in turn has led to the push in the microelectronics industry towards system-on-a-chip (SOC) approach.

Simply stated, the SOC approach attempts to integrate as many of these different device functionalities on the same 25 silicon chip so that a single large chip can provide a variety of functions to the end user. Although conceptually very

2

attractive, such an approach is practically daunting due to several reasons. First, the materials, fabrication processes and feature sizes optimum for the different microelectronic (such as memory chips, logic chips, wireless 5 communication chips, etc.) are quite different from each other. Combining them all onto the same chip implies making compromises that can limit the performance achievable in each of the device blocks in the SOC. Second, integration of a large number of functional blocks requires a large chip size 10 with many levels of wiring constructed on the chip. these factors tend to reduce the yield and increase the cost per chip, which is undesirable. Third, one has to design and build every unique combination of functions (e.g., memory and microprocessor, wireless communication and microprocessor, 15 etc.) leading to a large variety of chip part numbers and product mix that is not conducive to low cost manufacturing. Last, the expertise required for combining a diverse set of materials, process and integration schemes on a single SOC is often not available in a single enterprise as these are 20 currently part of different microelectronic businesses.

An attractive alternative to SOC is system-on-a-package or SOP wherein a number of chips, each optimized for its unique function and perhaps manufactured in different factories specially tailored to produce the specific chips, 25 are combined on a first level packaging carrier that interconnects them and allows the resulting package function as a single system. The level of interconnection and input-output- (I/O) density required in such a package is expected to be far greater than those currently available in 30 printed circuit board or multilayer ceramic technologies. Since this SOP carrier with chips assembled on it is expected to replace an SOC, it is reasonable to expect that the interconnect and I/O densities should be somewhere between those used in the far back end of the line (FBEOL) 35 interconnect levels on chips (typically wiring and vias on

3

500nm to 1000nm pitch) and the most aggressive packaging substrates (typically vias and wiring on 10,000 to 20,000nm pitch). Extension of the FBEOL processes at the required wiring size and pitch for the SOP carrier is feasible if the 5 carrier itself is made of silicon. In addition, however, the carrier would be required to support a high I/O density in order to interconnect the various device chips mounted on it. Greater the granularity of the system, that is, finer the division of the system into sub-units or chips, greater will 10 be the number of I/Os required. It is expected that such I/O densities will necessitate bonding pads that are on the order of 5 to 10μm size and spaces which are presently outside the realm of possibility of typical packaging I/O pads which are at least 10 to 20 times coarser in size and spacing.

- It is therefore highly desirable to enable a microjoining structure to interconnect several chips on to a system-on-a-package carrier to achieve significantly higher input/output density between the chips as compared to the current state-of-the-art.

- Accordingly, a primary object of the present invention is to make possible ultra high density of interconnections facilitating the use in ultra large scale integrated circuit chips (logic, microprocessor, memory, network switching). Current flip chip solder technology can achieve only about 75mm pads on 150µm centers. Our method is capable of aerial densities up to 1000 times or more this level. This is made possible by the unique process flow that does not require any special lithographic steps in the fabrication of the contact pads and uses the fine features in these device chips at the 30 back end of the line (BEOL) interconnection level.

#### SUMMARY OF THE INVENTION

A structure is proposed, comprising a fine pitch (down to about 2.5µm pads on 5µm centers) array of interconnects between a device component (semiconductor chip, optical device such as a laser, discrete or integrated passive components, 5 and the like) also referred to as a chiplet; and a carrier that houses one or many of these components. The carrier can be a silicon, ceramic or organic substrate but most preferably made of silicon to achieve the highest interconnection The joining metallurgy on the device side comprises 10 an adhesion layer, solder reaction barrier layer and a fusible solder joint ball. On the carrier side the matching contact pads are intentionally made larger than the ones on the device side and comprise an adhesion layer, solder reaction barrier layer and a noble metal protection/solder wetting layer. 15 Alternately, the said larger contact pads can be part of the top level of the device and the fusible solder bearing structure integrated on the carrier if so desired.

The foregoing and still further objects and advantages of the present invention will be more apparent from the following 20 detailed explanation of the preferred embodiments of the invention in connection with the accompanying drawing.

#### BRIEF DESCRIPTION OF DRAWINGS

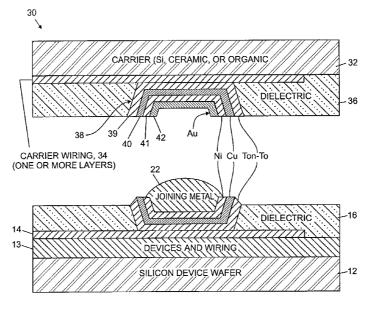

Figure 1 is a sectional view of a device chiplet after the deposition of TaN-Ta, Cu, Ni, and joining metal.

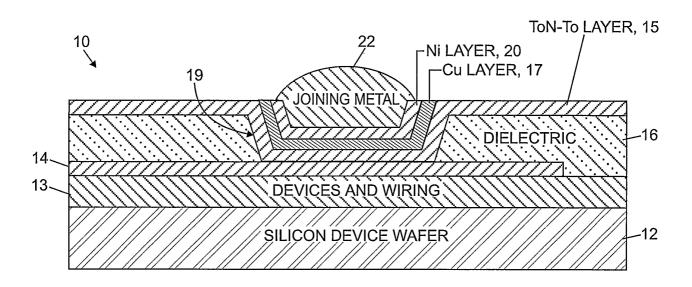

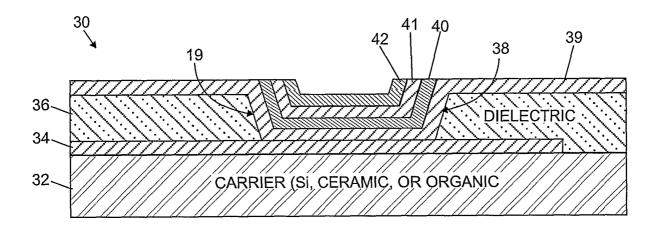

Figure 2 is a sectional view of the carrier wafer after the deposition of TaN-Ta, Cu, Ni, and noble metal.

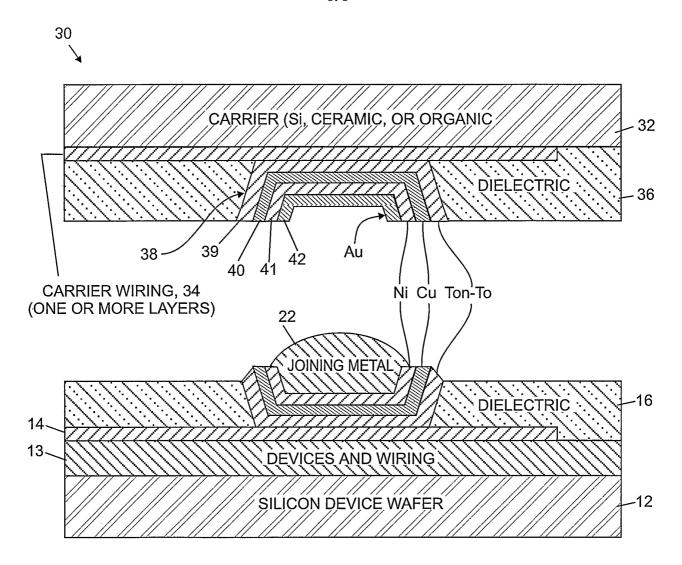

Figure 3 is a sectional view of the completed carrier (top) ready for joining to the completed device chiplet 30 (bottom).

#### DESCRIPTION OF PREFERRED EMBODIMENT

Referring now to the Figures of the Drawing, the details of the preferred method for fabricating and assembling the interconnections are now described, first, with respect to a 5 device chiplet 10:

#### Chiplet Process:

Referring now to the Figures of the drawing, the chiplet process begins with fabricating the silicon device chiplet wafer 12 through the semiconductor device and bottom wiring 10 layers 13 and the top metal wiring level 14, application of the final passivation dielectric stack 16, and the opening of the terminal pad vias (TV) 19. The TV via openings 19 can be as small as 2.5 microns in width and the passivation layer is about 1 micron or less in thickness. Then the following steps 15 are carried out: Deposit by sputtering or other vacuum deposition methods a liner layer 15, which typically comprises about 40nm tantalum nitride (TaN) and 40nm Tantalum(Ta) and a seed layer 17, comprising about 100nm or more of vacuum deposited copper. Other liner materials that can be used 20 include Ti, TiN, W, WN and Cr among others. The wafer is then subjected to chemical-mechanical polishing (CMP) so as to polish the copper from the top surface of the wafer stopping on the Ta surface. This results in a structure as shown in Figure 1 wherein the copper seed 17 is preserved only at the 25 bottom and the side walls of the TV openings 19. Electroplate a barrier layer 20, which can be Ni, Co, Pt, Pd and the like of about 500nm thickness followed by a joining metal layer 22, which is a fusible solder such as 97% Pb 3% Sn alloy, Au-Sn alloys or other solders depending upon the application and 30 solder hierarchy desired. Pb free solders based on Sn and its alloys are also possible for layer 22. The solder layer thickness can be chosen to be between 2 microns to 100 microns depending on the solder alloy and the application need.

key feature to note is that layers 20 and 22 plate up only on the Cu present in the TV openings 19 and not on the liner layer 15 present on the top of the wafer. The liner layer 15 serves simply as an electrode to carry the plating current in 5 the process. Layer 15 is subsequently removed by dry plasma or wet chemical etching from the chiplet top surface regions between the contact pads leaving behind a residual TaN Ta layer 15', only in the TV via bottom and side walls of the chiplet pad structure as shown in Figure 3 (bottom).

### 10 Carrier Process (for a Silicon Carrier):

This process provides the mating connection to the solder microjoints fabricated on the chiplets. The carrier wafers 30 are fabricated through the final interconnect wiring 34, deposition of final passivation stack 36 and the opening of TV vias 38. The TV vias on the carrier will be larger in dimension than the nominal dimension of the microjoint solder pads on the chiplet to ensure that the microjoints can be comfortably located into the carrier via receptacles.

The subsequent process flow for the carrier wafers has 20 the following steps: Deposit by sputtering or other vacuum deposition methods a liner layer 39, which typically comprises about 40nm tantalum nitride (TaN) and 40nm Tantalum (Ta) and a seed layer 40, comprising about 100nm of vacuum deposited copper. The wafer is then subjected to chemical-mechanical polishing (CMP) so as to polish the copper from the top surface of the wafer stopping on the Ta surface. This results in a structure on the carrier as shown in Figure 2 wherein the copper seed 40, is preserved only at the bottom and the side walls of the TV openings 38. Electroplate a barrier layer 41, 30 which can be Ni, Co, Pt, Pd and the like of about 500nm thickness followed by a noble metal layer 42, which is preferably gold in the thickness range of 100 to 1000nm. The key feature to note is that layers 41 and 42 plate up only on

the Cu present in the TV openings 38, and not on the liner layer present on the top surface of the carrier wafer. liner layer 39, serves simply as an electrode to carry the plating current in the process. Layer 39 is subsequently 5 removed by dry plasma or wet chemical etching from the top surface regions between the pads leaving behind a residual TaN Ta layer 39, only in the TV via bottom and side walls of the carrier pad structure as shown in Figure 3 (top). Other methods for applying the barrier layer 41 and noble metal include electroless deposition. 10 layer 42 deposition of Ni, Co, Pd as well as noble metal Au is known in electroplating. and can be used instead of Electroless Au plating and immersion Au are particularly suitable if thin Au (about 80 to 120nm) is deemed sufficient. 15 The resulting feature on the carrier is receptacle 44 for receiving microjoints fabricated on the chiplet.

## Assembly Process (and the resulting final structure):

The assembly involves pick and place of the chiplets in a manner similar to the regular flip chip assembly (split optics 20 and/or capacitance aligned) and subjected to reflow joining. A hydrogen reflow without flux may be preferred since the gap between the chiplet and the carrier may be too small for efficient flux cleaning.

It will now have become apparent that further key advantages of the disclosed invention over the prior art are as follows: The microjoining scheme allows area array mounting of very small devices such as lasers, microsensors, or actuators. These devices can be as small as 100µm x 100µm or less and are too small to be mounted with standard flip 30 chip contacts. The use of PbSn solders allows reworkable connections for device chip replacement for upgrade or repair. The devices with these microjoining solder pads can be tested, burned in and sorted for known good devices using any

8

conventional temporary device attach structure. Thus, obtaining known good die is not an issue despite the fine pitch of the interconnects.

The invention having been thus described with particular 5 reference to the preferred forms thereof, it will be obvious that various changes and modifications may be made therein without departing from the spirit and scope of the invention as defined in the appended claims.

WO 03/060960

PCT/EP02/14911

CLAIMS

9

What is Claimed is:

A system for connecting a set of device chips by means of an array of microjoint structures on an interconnect carrier

comprising:

carrier including a multilayer substrate having a plurality of microjoint receptacles in one surface.

a set of microjoint pads, including solder balls, on the device chips joined to the receptacles in the one carrier 10 surface,

interconnect wiring mounted in the carrier connecting to the microjoint pad arrays to enable the interconnection between device chips mounted on the carrier.

- 2. A system as defined in Claim 1, wherein said receptacles 15 on said interconnect carrier comprise successive layers of a liner layer, seed layer, barrier layer and a noble metal layer, respectively, these layers lining the inner surface of said receptacles.

- 3. A system as defined in Claim 2, wherein the liner layer 20 is selected from the group consisting of Ta, TaN, Ti, TiN, W, WN, Cr and combination thereof.

- 4. A system as defined in Claim 3, wherein the liner layer thickness is between 5nm and 120nm.

- 5. A system as defined in Claim 2, wherein the seed layer is 25 copper with thickness in the range 30 to 200nm.

- 6. A system as defined in Claim 2, wherein the barrier layer is selected from the group consisting of Ni, Co, Pt, Pd and alloys or combinations thereof.

- 7. A system as defined in Claim 6 wherein the barrier layer 5 thickness is between 100 and 1000nm.

- 8. A system as defined in Claim 1 wherein said microjoint pads on said device chips comprise successive layers of a liner layer, seed layer, barrier layer and a fusible solder layer, respectively.

- 10 9. A system as defined in Claim 8 wherein the liner layer is selected from the group comprising Ta, TaN, Ti, TiN, W, WN, Cr and combinations thereof..

- 10. A system as defined in Claim 8 wherein the seed layer is copper with thickness in the range 30 to 200nm.

- 15 11. A system as defined in Claim 8 wherein the barrier layer is selected from the group comprising Ni, Co, Pt, Pd and alloys or combinations thereof.

- 12. A system in accordance with Claim 11 wherein the barrier layer thickness is between 100 and 1000nm.

- 20 13. A system as defined in Claim 2 wherein the carrier is made of silicon and includes a set of interconnect wiring disposed thereon, a dielectric passivation layer over the top surface of the interconnect wiring and said receptacles being in the dielectric passivation layer.

- 25 14. A system as defined in Claim 12 wherein the device chiplet includes a set of devices built on it connected by wiring, a dielectric passivation layer over the top surface of

the wiring and said microjoint pads being in the dielectric passivation layer.

- 15. A system as defined in Claim 12 wherein the device chiplets are selected from the group comprising microprocessor 5 chip, memory chip, microcontroller chip, laser diode chip, laser driver chip, photodetector chip, wireless communication chip, and logic processor chip.

- 16. A microjoint interconnect structure comprising:

- (a) a carrier substrate having an array of interconnects 10 for connecting device components;

- (b) the carrier, including a substrate and a dielectric film, and microjoint receptacles comprising an adhesion layer, diffusion barrier layer and a noble metal layer.

- (c) microjoining pads on the device side, comprising an 15 adhesion layer, solder reaction barrier layer and fusible solder joint ball for each component

- (d) said microjoint pads on the device on the carrier side matching said microjoint receptacles on the carrier side.

- 17. A microjoint interconnect structure as defined in Claim 20 16 wherein the device components are semiconductor chips, optical component chips and the like.

- 18. A process for connecting a set of device chips by means of an array of microjoint structures on an interconnect carrier comprising:

- forming the carrier including a multilayer substrate having a plurality of microjoint receptacles in one surface.

forming a set of microjoint pads, including solder balls, on the device chips joined to the receptacles in the one carrier surface,

forming interconnect wiring mounted in the carrier 5 connecting to the microjoint pad arrays to enable the interconnection between device chips mounted on the carrier.

- 19. A microjoint interconnect structure comprising:

- (a) a carrier substrate having an array of interconnects for connecting device components.

- (b) the carrier, including a substrate and dielectric film with microjoining pads each comprising an adhesion layer, solder reaction barrier layers and fusible solder joint ball.

- (c) the microjoint receptacles on the device side comprising an adhesion layer, diffusion barrier layer and a 15 noble metal layer.

- (d) said microjoint pads on the carrier side matching said microjoint receptacles on the device.

- 20. A microjoint interconnect structure as defined in Claim 19 wherein the device chips are selected from the group 20 comprising semiconductor chips, optical device chips, communication chips.

- 21. A process for connecting a set of device chips by means of an array of microjoint structures on an interconnect carrier comprising:

- forming the carrier including a multilayer substrate having a plurality of microjoint pads including solder balls on one surface.

13

forming a set of microjoint receptacles on one surface of the device chips that are joined to the carrier by the solder balls on the carrier.

forming interconnect wiring on the carrier connecting the 5 microjoint pad arrays to enable the interconnection between the chips.

1/3

FIG. 1

2/3

FIG. 2

3/3

FIG. 3