**【特許請求の範囲】****【請求項 1】**

入力された又は記録媒体から読み出された圧縮画像データに対して再生のための画像処理を施す画像処理装置であって、

前記圧縮画像データに対して伸長処理を施して伸長画像データを得る伸長処理手段と、前記伸長画像データを記憶する記憶する記憶手段と、

前記記憶手段に記憶された前記伸長画像データをブロック単位で読み出してリサイズ処理を施すことにより表示用画像データを得るリサイズ手段と、

前記記憶手段に記憶されている伸長画像データのデータ数に応じて前記リサイズ手段による前記リサイズ処理の実行を制御する制御手段と、

を具備することを特徴とする画像処理装置。

**【請求項 2】**

前記制御手段は、

前記記憶手段に記憶された前記伸長画像データのデータ数をカウントするカウント手段と、

前記カウント手段でカウントされた前記伸長画像データのデータ数を所定値と比較する比較手段と、

を含むことを特徴とする請求項 1 に記載の画像処理装置。

**【請求項 3】**

前記制御手段は、前記比較手段における比較の結果、前記伸長画像データのデータ数が前記所定値未満の場合に前記リサイズ手段に対して前記リサイズ処理を待機させるウェイト信号を出力し、前記比較手段における比較の結果、前記伸長画像データのデータ数が前記所定値以上になった場合に前記リサイズ手段に対して前記ウェイト信号の出力を停止することにより、前記リサイズ処理の実行を制御することを特徴とする請求項 2 に記載の画像処理装置。

**【請求項 4】**

前記所定値は、予めレジスタに設定された値であることを特徴とする請求項 2 に記載の画像処理装置。

**【請求項 5】**

前記伸長処理手段は、第 1 の所定データ数の伸長画像データが得られた場合に第 1 の転送完了信号を前記カウント手段に出力し、

前記リサイズ手段は、第 2 の所定データ数の伸長画像データをリサイズ処理した場合に第 2 の転送完了信号を前記カウント手段に出力し、

前記カウント手段による前記伸長画像データのデータ数のカウントは、前記第 1 の転送完了信号が入力された場合に前記第 1 の所定データ数だけカウント値を増加させ、前記第 2 の転送完了信号が入力された場合に前記第 2 の所定データ数だけ前記カウント値を減少させることを行うことを特徴とする請求項 2 に記載の画像処理装置。

**【請求項 6】**

前記第 1 の所定データ数及び前記第 2 の所定データ数は、予めレジスタに設定された値であることを特徴とする請求項 5 に記載の画像処理装置。

**【請求項 7】**

前記伸長処理手段における前記伸長処理と前記リサイズ処理手段における前記リサイズ処理とは略同時に開始されることを特徴とする請求項 1 に記載の画像処理装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、画像処理装置に関し、特に圧縮画像データを再生表示することが可能な画像処理装置に関する。

**【背景技術】****【0002】**

10

20

30

40

50

複数の画像処理をパイプライン処理可能とする画像処理装置に関する提案として、例えば特許文献1では、JPEG処理（JPEG圧縮及びJPEG伸長）等を行う画像処理と画像の拡大縮小（リサイズ処理）を行う拡大縮小処理との間に小容量のメモリを直列に接続しておくことで、両者の処理をパイプライン処理可能としている。即ち、特許文献1では、イメージプロセスで処理された画像データを一旦メモリに記憶させ、記憶された画像データを所定ブロック単位で読み出して拡大縮小処理を行うようにしている。

#### 【0003】

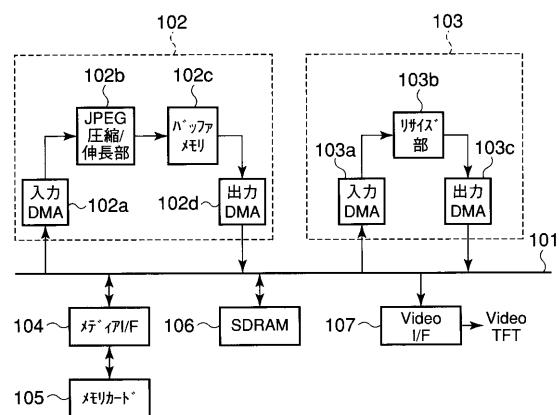

図5を参照して特許文献1の技術について説明する。図5の画像処理装置においては、バス101にJPEG処理部102と、リサイズ処理部103と、メディアインターフェイス(I/F)104を介してメモリカード105と、メモリ(SDRAM)106と、Video I/F107とが接続されている。ここで、JPEG処理部102は、入力DMA102aと、JPEG圧縮／伸長部102bと、バッファメモリ102cと、出力DMA102dとから構成されており、リサイズ処理部103は、入力DMA103aと、リサイズ部103bと、出力DMA103cとから構成されている。

10

#### 【0004】

このような構成において、メモリカード105に記録されている画像を再生する場合には、まずメディアI/F104を介してメモリカード105から圧縮画像データが読み出され、読み出された圧縮画像データがSDRAM106に一旦記憶される。次に、JPEG処理部102内の入力DMA102aを介してSDRAM106に記憶された圧縮画像データが読み出される。読み出された圧縮画像データはJPEG圧縮／伸長部102bに入力されて伸長される。JPEG圧縮／伸長部102bで伸長されて得られた伸長画像データはバッファメモリ102c及び出力DMA102dを介してバス101に出力され、SDRAM106に記憶される。

20

#### 【0005】

その後、リサイズ処理部103内の入力DMA103aを介してSDRAM106に記憶された伸長画像データが読み出される。読み出された伸長画像データはリサイズ部103bに入力されて適正な表示サイズにリサイズされる。リサイズされた伸長画像データは出力DMA103cを介してバス101に出力され、SDRAM106に記憶される。

#### 【0006】

その後、Video I/F107によってSDRAM106に記憶された伸長画像データが読み出されて図示しないTFT LCD等の画像表示装置上に画像表示がなされる。

30

#### 【0007】

これらの処理のうち、伸長処理とリサイズ処理とは図6に示すように時間的に連続して行われる。即ち、特許文献1の手法では、ユーザによって画像再生のキー操作がなされると、メディアI/F104を介して圧縮画像データの読み出しが開始され、圧縮画像データの読み出しが終了すると伸長処理が開始される。伸長処理において1フレーム分の圧縮画像データの伸長が終了するとリサイズ処理が開始され、伸長画像データが所定ブロック毎にリサイズされる。

#### 【特許文献1】特開2000-311241号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

上述したように、特許文献1の手法では、圧縮画像データの伸長が1フレーム全て終了してから、画像のリサイズを行っているので、この時間の分、ユーザによって画像再生指示が行われてから実際に画像が表示されるまでのレスポンス時間が長くなってしまう。

#### 【0009】

本発明は、上記の事情に鑑みてなされたもので、画像再生指示が行われてから実際に画像が表示されるまでのレスポンス時間を短くすることができる画像処理装置を提供することを目的とする。

#### 【課題を解決するための手段】

10

20

30

40

50

## 【0010】

上記の目的を達成するために、本発明の第1の態様による画像処理装置は、入力された又は記録媒体から読み出された圧縮画像データに対して再生のための画像処理を施す画像処理装置であって、前記圧縮画像データに対して伸長処理を施して伸長画像データを得る伸長処理手段と、前記伸長画像データを記憶する記憶する記憶手段と、前記記憶手段に記憶された前記伸長画像データをプロック単位で読み出してリサイズ処理を施すことにより表示用画像データを得るリサイズ手段と、前記記憶手段に記憶されている伸長画像データのデータ数に応じて前記リサイズ手段による前記リサイズ処理の実行を制御する制御手段とを具備することを特徴とする。

## 【0011】

この第1の態様によれば、前記記憶手段に記憶されている伸長画像データのデータ数に応じてリサイズ処理を行うようにすることで、1フレーム分の伸長画像データが得られなくともリサイズ処理を行うことができる。

## 【発明の効果】

## 【0012】

本発明によれば、画像再生指示が行われてから実際に画像が表示されるまでのレスポンス時間を短くすることができる画像処理装置を提供することができる。

## 【発明を実施するための最良の形態】

## 【0013】

以下、図面を参照して本発明の実施形態を説明する。

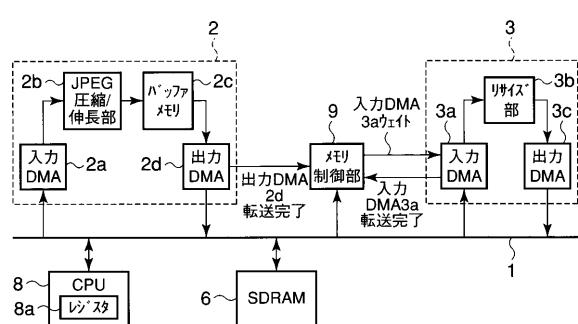

図1は、本発明の一実施形態に係る画像処理装置の構成について示すブロック図である。

## 【0014】

図1の画像処理装置においては、バス1に、伸長処理手段としてのJPEG処理部2と、リサイズ手段としてのリサイズ処理部3と、記憶手段としてのメモリ(SDRAM)6と、CPU8と、制御手段としてのメモリ制御部9とが接続されている。ここで、図1においては図示を省略しているが、バス1には、圧縮画像データが記録されるメモリカードとの間でのデータ転送を行うためのメディアI/Fや TFTLCD等の画像表示装置との間でのデータ転送を行うためのVideoI/F等も接続されている。

## 【0015】

また、図1においてJPEG処理部2は、入力DMA2aと、JPEG圧縮/伸長部2bと、バッファメモリ2cと、出力DMA2dとから構成されている。更に、リサイズ処理部3は、入力DMA3aと、リサイズ部3bと、出力DMA3cとから構成されている。

## 【0016】

また、図1において、JPEG処理部2の出力DMA2dとリサイズ処理部3の入力DMA3aとは、メモリ制御手段としてのメモリ制御部9に接続されている。

## 【0017】

また、CPU8の内部にはレジスタ8aが設けられており、メモリ制御部9はバス1を介してレジスタ8aに記憶されたレジスタ設定値を読み出し可能ないように構成されている。ここで、レジスタ8aに記憶されたレジスタ設定値は、第1の所定データ数としての出力DMA2d転送ライン数、第2の所定データ数としての入力DMA3a転送ライン数、及び所定値としての必要データライン数である。これらレジスタ設定値については後述する。

## 【0018】

図1のような構成を有する画像処理装置の動作について説明する。まず、図示しないメディアI/Fを介して圧縮画像データが読み出されると、読み出された圧縮画像データがSDRAM6に一旦記憶される。次に、JPEG処理部2によってSDRAM6に記憶された圧縮画像データが読み出される。読み出された圧縮画像データは、入力DMA2aを介してJPEG圧縮/伸長部2bに入力されて伸長される。

10

20

30

40

50

## 【0019】

本一実施形態では、JPEG圧縮／伸長部2bで伸長されて得られた伸長画像データが順次バッファメモリ2c及び出力DMA2dを介してバス1に出力されてSDRAM6に記憶される。そして、所定ライン数の伸長画像データの転送が終了すると、出力DMA2dからメモリ制御部9に出力DMA2d転送完了信号が出力される。ここで、圧縮画像データとして、例えばYCbCr22のJPEG画像データを伸長する場合には1回の伸長処理で8ライン分の画像データが伸長される。本一実施形態では、この8ライン分の伸長画像データが転送される毎に出力DMA2d転送完了信号がメモリ制御部9に出力される。

## 【0020】

ここで、本一実施形態においては、リサイズ部3b内におけるリサイズ処理、より詳しくはリサイズ部3b内の入力DMA3aにおける画像データ読み出しがメモリ制御部9によって制御されている。即ち、リサイズ部3bでリサイズ処理が行えるだけの伸長画像データがSDRAM6に記憶されていない場合に、メモリ制御部9からリサイズ処理部3の入力DMA3aに入力DMA3aウェイト信号が出力される。入力DMA3aでは、入力DMA3aウェイト信号が出力されている間は、伸長画像データの読み出しが行われず、リサイズ処理が待機される。

## 【0021】

一方、SDRAM6にリサイズ処理を行うのに充分な伸長画像データが記憶されている場合には、メモリ制御部9から入力DMA3aへの入力DMA3aウェイト信号の出力が停止される。この場合には、入力DMA3aを介してリサイズに必要な分の伸長画像データの読み出しが開始され、読み出された伸長画像データがリサイズ部3bに入力される。入力DMA3aからリサイズ部3bにリサイズに必要な分の伸長画像データの転送が終了すると、入力DMA3aからメモリ制御部9に入力DMA3a転送完了信号が出力される。その後、リサイズ部3bでは入力された伸長画像データが適正な表示サイズにリサイズされ、表示用画像データが生成される。

## 【0022】

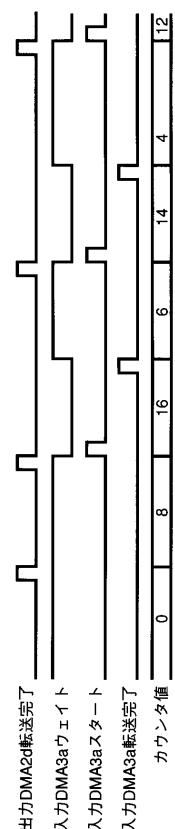

図2は、本一実施形態の要部としてのメモリ制御部9の詳細な構成について示す図である。

## 【0023】

図2のメモリ制御部9は、カウンタ9aと比較器9bとから構成されている。図2において、カウンタ9aのUp入力端子には上記出力DMA2d転送完了信号が入力される。また、カウンタ9aのDown入力端子には上記入力DMA3a転送完了信号が入力される。

## 【0024】

更に、図2においてカウンタ9aの加算値入力端子と減算値入力端子とには、それぞれレジスタ8aのレジスタ設定値が入力される。カウンタ9aの加算値入力端子にはレジスタ設定値「出力DMA2d転送ライン数」が入力される。この出力DMA2d転送ライン数は、出力DMA2dから出力DMA2d転送完了信号が出力されるタイミングを示す設定値である。例えば、YCbCr22のJPEG画像データの場合には、伸長画像データが8ラインづつ得られる。そこで、本一実施形態では出力DMA2d転送ライン数を8とする。なお、出力DMA2d転送ライン数の値は出力DMA2dの仕様などに応じて変化させることができる。

## 【0025】

また、カウンタ9aの減算値入力端子にはレジスタ設定値「入力DMA3a転送ライン数」が入力される。この入力DMA3a転送ライン数は、入力DMA3aから入力DMA3a転送完了信号が出力されるタイミングを示す設定値である。本一実施形態においては入力DMA3a転送ライン数をリサイズ処理部3でリサイズ処理が可能なデータライン数、例えば10とする。なお、入力DMA3a転送ライン数の値は入力DMA3aの仕様などに応じて変化させることができる。

## 【0026】

10

20

30

40

50

更に、図2において、カウンタ9aの出力部は比較器9bの一方の入力部に接続されている。また、比較器9bの他方の入力部にはレジスタ設定値「必要データライン数」が入力される。この必要データライン数は、リサイズ部3bがリサイズ処理に必要とするデータ数である。例えば本一実施形態では必要データライン数を10ライン(1ブロック)とする。

#### 【0027】

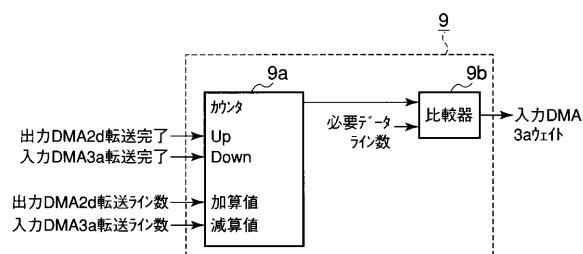

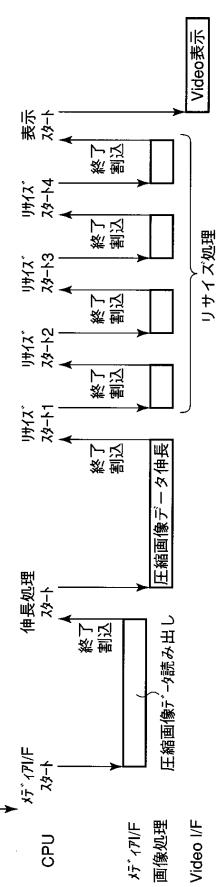

図2のような構成を有するメモリ制御部9の動作について図3を参照して説明する。図3は、画像再生時における出力DMA2d、メモリ制御部9、入力DMA3a、及びカウンタ9aのそれぞれの状態について時系列的に示したタイミングチャートである。

#### 【0028】

画像再生時において、圧縮画像データが読み出されて、JPEG処理部2の出力DMA2dにおいて8ライン分の伸長画像データの転送が完了すると、出力DMA2dからカウンタ9aに出力DMA2d転送完了信号が出力される。これを受け、カウンタ9aでは出力DMA2d転送ライン数=8だけカウント値を増加させる。これにより、カウンタ9aのカウント値は「8」となる。次に、比較器9bにおいてカウンタ9aのカウント値「8」と必要データライン数「10」とが比較される。今回はカウント値<必要データライン数であり、SDRAM6にはリサイズ処理に必要な分の伸長画像データが記憶されていないので、入力DMA3aウェイト信号の出力が継続される。

#### 【0029】

その後、再びJPEG処理部2の出力DMA2dにおいて8ライン分の伸長画像データの転送が完了すると、出力DMA2dからカウンタ9aに出力DMA2d転送完了信号が出力される。これを受けてカウンタ9aのカウント値が増加して、カウンタ9aのカウント値が「16」となる。次に、比較器9bにおいてカウンタ9aのカウント値「16」と必要データライン数「10」とが比較される。今回はカウント値>必要データライン数となり、SDRAM6にはリサイズ処理に必要な分の伸長画像データが記憶されているので、入力DMA3aウェイト信号の出力が停止される。

#### 【0030】

これによって入力DMA3aを介して伸長画像データの読み出しが開始される。入力DMA3aによって読み出された伸長画像データのリサイズ部3bへの転送が完了すると、入力DMA3aからカウンタ9aに入力DMA3a転送完了信号が出力される。これを受けて、カウンタ9aでは入力DMA3a転送ライン数=10だけカウント値を減少させる。これにより、カウンタ9aのカウント値は「6」となる。次に、比較器9bにおいてカウンタ9aのカウント値「6」と必要データライン数「10」とが比較される。今回はカウント値<必要データライン数であり、SDRAM6にはリサイズ処理に必要な分の伸長画像データが記憶されていないので、入力DMA3aウェイト信号の出力が再開される。以後、同様にしてカウント値と必要データライン数とが比較器9bにおいて比較されることによって、入力DMA3aウェイト信号の出力制御が行われる。

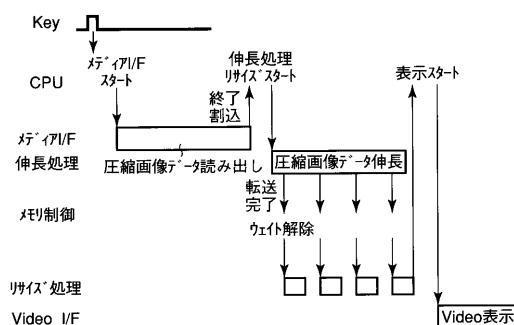

#### 【0031】

図4に、本一実施形態における画像再生時のタイミングチャートを示す。図4に示すように、本一実施形態においては、圧縮画像データの読み出しが終了すると、JPEG伸長処理とリサイズ処理とが略同時に開始される。そして、圧縮画像データが所定データ数(1ブロック)分伸長され、SDRAM6に記憶されると、リサイズ処理部3のウェイトが解除されてブロック毎のリサイズ処理が実行される。

#### 【0032】

このように、本一実施形態では、1フレーム分の画像データの伸長処理が終了しなくともリサイズ処理に必要な伸長画像データがSDRAM6に記憶されている場合にはリサイズ処理が行われるので、JPEG処理とリサイズ処理とをパイプライン処理できると共に、ユーザによって画像再生のキー操作がなされてから実際に画像が表示されるまでのレスポンス時間を短縮することができる。また、伸長画像データの転送ライン数とリサイズ処理した画像データのライン数をCPU8で監視して追従する必要がないので、CPU8の

10

20

30

40

50

負荷を増やすことなく、追従処理を行うことができる。

【0033】

以上実施形態に基づいて本発明を説明したが、本発明は上記した実施形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形や応用が可能なことは勿論である。

【0034】

さらに、上記した実施形態には種々の段階の発明が含まれており、開示される複数の構成要件の適当な組合せにより種々の発明が抽出され得る。例えば、実施形態に示される全構成要件からいくつかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題が解決でき、発明の効果の欄で述べられている効果が得られる場合には、この構成要件が削除された構成も発明として抽出され得る。

10

【図面の簡単な説明】

【0035】

【図1】本発明の一実施形態に係る画像処理装置の構成について示すブロック図である。

【図2】メモリ制御部の詳細な構成について示す図である。

【図3】画像再生時における出力DMA2d、メモリ制御部9、入力DMA3a、及びカウンタ9aのそれぞれの状態について時系列的に示したタイミングチャートである。

【図4】画像再生時におけるデータ処理の流れを時系列的に示した図である。

【図5】従来例の画像処理装置の構成について示すブロック図である。

【図6】従来例の画像処理装置の画像再生時におけるデータ処理の流れを時系列的に示した図である。

20

【符号の説明】

【0036】

1...バス、2...JPEG処理部、2a, 3a...入力DMA、2b...JPEG圧縮／伸長部、2c...バッファメモリ、2d, 3c...出力DMA、3...リサイズ処理部、3b...リサイズ部、6...メモリ(SDRAM)、8...CPU、8a...レジスタ、9...メモリ制御部、9a...カウンタ、9b...比較器

【図1】

【図3】

【図2】

【図4】

【図6】

【図5】

## フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 中薗 啓介

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス株式会社内

(72)発明者 上野 晃

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス株式会社内

F ターム(参考) 5B057 CA18 CB08 CB12 CB16 CD05 CG05 CH05

5C059 KK11 KK38 MA00 TA00 TB08 TC01 TD07 TD12 UA05 UA36

5C076 AA01 AA21 AA22 AA36 BA03 BA04 BA06

5C078 AA04 BA57 CA31 DA01 DA02 DB04