(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3584494号

(P3584494)

(45) 発行日 平成16年11月4日(2004.11.4)

(24) 登録日 平成16年8月13日(2004.8.13)

(51) Int.C1.<sup>7</sup>

F 1

|               |         |        |       |         |

|---------------|---------|--------|-------|---------|

| G 11 C        | 16/04   | G 11 C | 17/00 | 6 2 2 C |

| H 01 L        | 21/822  | H 01 L | 27/04 | F       |

| H 01 L        | 21/8247 | H 01 L | 27/10 | 4 3 4   |

| H 01 L        | 27/04   | H 01 L | 29/78 | 3 7 1   |

| H 01 L 27/115 |         |        |       |         |

請求項の数 5 (全 19 頁) 最終頁に続く

|           |                       |

|-----------|-----------------------|

| (21) 出願番号 | 特願平6-172956           |

| (22) 出願日  | 平成6年7月25日(1994.7.25)  |

| (65) 公開番号 | 特開平8-36890            |

| (43) 公開日  | 平成8年2月6日(1996.2.6)    |

| 審査請求日     | 平成12年5月29日(2000.5.29) |

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都品川区北品川6丁目7番35号 |

| (74) 代理人  | 100094053<br>弁理士 佐藤 隆久                    |

| (72) 発明者  | 荒瀬 謙士朗<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内  |

| (72) 発明者  | 官下 勝<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内    |

| 審査官 長島 孝志 |                                           |

最終頁に続く

(54) 【発明の名称】半導体不揮発性記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ビット線、ソース線とも主配線と副配線とに階層化され、それぞれ主配線と副配線とが動作に応じて選択的に接続され、かつ副ソース線と副ビット線間に複数のメモリセルが並列接続され、各メモリセルのゲートがワード線に接続され、上記副ソース線と副ビット線が素子分離膜の下部に形成された埋め込み拡散層より構成されるコンタクトレスメモリアレイ構造を有する半導体不揮発性記憶装置であつて、

データの書き込み時には、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、上記ビット線の主配線が基準電位または第2の正電圧に設定され、上記ソース線の主配線を基準電位として、FNトンネリングにより、チャネル全面から電荷蓄積層中に電荷を注入することにより所定データの書き込みを行い、

消去時には、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを接続状態とし、選択されたワード線が負電圧に設定され、非選択のワード線が基準電位に設定され、上記ビット線の主配線が正電圧に設定され、上記ソース線の主配線を基準電位として、FNトンネリングによりドレイン側から電荷蓄積層中の電荷を引き抜くことにより消去を行う

半導体不揮発性記憶装置。

**【請求項 2】**

上記コンタクトレスメモリアレイ構造が複数並列に配列されたメモリアレイを有し、上記書き込み時は、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、第1のデータを書き込むメモリセルが接続された上記ビット線の主配線が基準電位に設定され、第2のデータを書き込むメモリセルが接続された上記ビット線の主配線が第2の電圧に設定され、上記ソース線の主配線を基準電位として、ワード線セクタを単位として全ビット並列的にデータの書き込みを行い、10

上記消去時は、

全ビット線の主配線と副配線とを接続状態とし、全ソース線の主配線と副配線とを接続状態とし、選択されたワード線が負電圧に設定され、非選択のワード線が基準電位に設定され、全ビット線の主配線が正電圧に設定され、上記ソース線の主配線を基準電位として、消去を行う

請求項1記載の半導体不揮発性記憶装置。

**【請求項 3】**

上記コンタクトレスメモリアレイ構造が複数並列に配列されたメモリアレイを有し、上記書き込み時は、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、第1のデータを書き込むメモリセルが接続された上記ビット線の主配線が基準電位に設定され、第2のデータを書き込むメモリセルが接続された上記ビット線の主配線が第2の電圧に設定され、上記ソース線の主配線を基準電位として、ワード線セクタを単位として全ビット並列的にデータの書き込みを行い、20

上記消去時は、ワード線セクタを単位として、

全ビットビット線の主配線と副配線とを接続状態とし、全ソース線の主配線と副配線とを接続状態とし、選択されたワード線が負電圧に設定され、非選択のワード線が基準電位に設定され、全ビット線の主配線が正電圧に設定され、上記ソース線の主配線を基準電位とし、かつ消去パルスが複数の消去パルスに分割され、消去の終了したセルのビット線パルスが正電圧から基準電位に切り換えられる30

請求項1記載の半導体不揮発性記憶装置。

**【請求項 4】**

ビット線、ソース線とも主配線と副配線とに階層化され、それぞれ主配線と副配線とが動作に応じて選択的に接続され、かつ副ソース線と副ビット線間に複数のメモリセルが並列接続され、各メモリセルのゲートがワード線に接続され、上記副ソース線と副ビット線が素子分離膜の下部に形成された埋め込み拡散層より構成されるコンタクトレスメモリアレイ構造を有する半導体不揮発性記憶装置であって、

データの書き込み時には、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、上記ビット線の主配線が基準電位または第2の正電圧に設定され、上記ソース線の主配線を基準電位として、FNトンネリングにより、チャンネル全面から電荷蓄積層中に電荷を注入することにより所定データの書き込みを行い40

、

消去時には、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを接続状態とし、全ワード線が負電圧に設定され、上記ビット線の主配線が基準電位に設定され、上記ソース線の主配線を基準電位として、FNトンネリングによりチャンネル全面から電荷蓄積層中の電荷を引き抜くことにより消去を行う50

半導体不揮発性記憶装置。

【請求項 5】

上記コンタクトレスメモリアレイ構造が複数並列に配列されたメモリアレイを有し、上記書き込み時は、

ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、第1のデータを書き込むメモリセルが接続された上記ビット線の主配線が基準電位に設定され、第2のデータを書き込むメモリセルが接続された上記ビット線の主配線が第2の電圧に設定され、上記ソース線の主配線を基準電位として、ワード線セクタを単位として全ビット並列的にデータの書き込みを行い、10

上記消去時は、

全ビット線の主配線と副配線とを接続状態とし、全ソース線の主配線と副配線とを接続状態とし、全ワード線が負電圧に設定され、全ビット線の主配線が基準電位に設定され、上記ソース線の主配線を基準電位として、消去を行う

請求項4記載の半導体不揮発性記憶装置。

【発明の詳細な説明】

【0001】

【産業上の利用分野】

本発明は、電気的に書き換え可能な不揮発性メモリ、たとえばフラッシュ EEPROMなどの半導体不揮発性記憶装置に関するものである。20

【0002】

【従来の技術】

従来、NOR型フラッシュメモリは、データの書き込みはCHE(チャンネルホットエレクトロン)によりドレイン側からフローティングゲート中に電子を注入することにより行い、消去はFN(Fowler-Nordheim)トンネリングによりソース側からフローティングゲート中の電子を引き抜くことにより行う。

【0003】

しかし、この方法の場合、データの書き込みをCHEで行っているために、書き込み時にドレイン-ソース間に大電流が流れ、単一電源で動作させることは不可能である。

【0004】

ところが近年、携帯用小型電子機器市場の拡大に伴い、ランダムアクセススピードの点で有利なNOR型フラッシュで、しかも、単一電源で動作できるフラッシュメモリの実現が要望されている。

このような観点から、データ書き込み/消去をともにFNトンネリングにより行うことにより、単一電源動作できることを目的としたNOR型のフラッシュメモリとして、たとえば、

- (1) DINOR型フラッシュメモリ

- (2) AND型フラッシュメモリ

- (3) ACEE型フラッシュメモリ

が提案されている。40

【0005】

以下、これら3種類のフラッシュメモリについて、その構造・動作、そして、それらの問題点について詳しく説明する。

【0006】

(1) DINOR型フラッシュメモリ

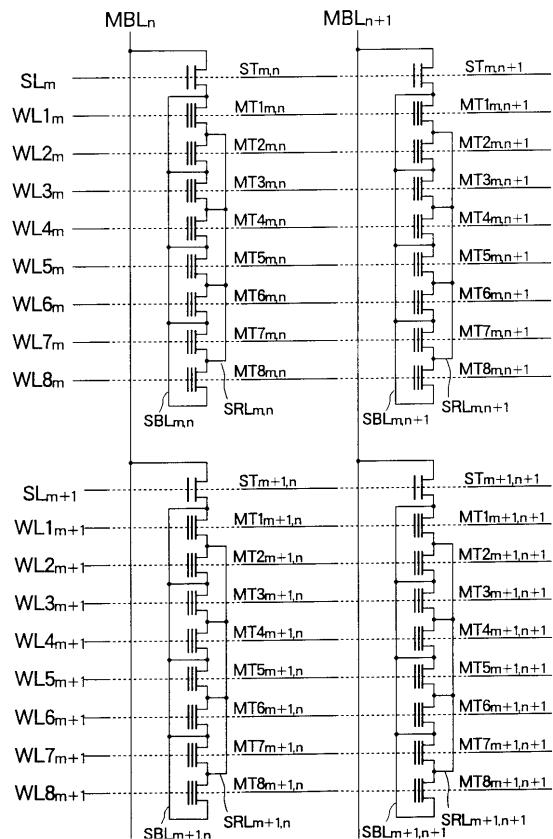

図15は、主ビット線2本、副ビット線に連なるワード線8本の2群から構成されるDINOR型フラッシュのメモリアレイ構成を示す図である。

図15のメモリアレイにおいて、WL1m~WL8m, WL1m+1~WL8m+1はワード線、SLm, SLm+1は選択ゲート線、MBLn, MBLn+1は主ビット線、SBLm, n, SBLm+1, n, SBLm, n+1, SBLm+1, n+50

1 は副ビット線、 $SRL_m, n$ 、 $SRL_{m+1}, n$ 、 $SRL_m, n+1$ 、 $SRL_{m+1}, n+1$  は共通ソース線、 $MT1_m, n \sim MT8_m, n$ 、 $MT1_{m+1}, n \sim MT8_{m+1}, n$ 、 $MT1_m, n+1 \sim MT8_m, n+1$ 、 $MT1_{m+1}, n+1 \sim MT8_{m+1}, n+1$  はメモリセルトランジスタ、 $STM, n$ 、 $STM_{m+1}, n$ 、 $STM, n+1$ 、 $STM_{m+1}, n+1$  は選択トランジスタをそれぞれ示している。

#### 【0007】

図16は、図15に示すようなDINOR型フラッシュメモリの消去、書き込み、並びに読み出し時のバイアス条件を示す図である。

図16に示すように、DINOR型フラッシュメモリの消去動作は、選択ゲート線 $SL$ およびソースに $0V$ 、ワード線 $WL$ に $20V$ を印加し、ビット線 $BL$ をフローティング状態に保持することによって、フローティングゲート中に電子を注入することにより行われる。

データの書き込みは、選択ゲート線 $SL$ に $10V$ 、ワード線 $WL$ に $-10V$ 、ビット線 $BL$ に $0V$ または $6V$ を印加し、ソースをフローティング状態に保持することによって、ワード線セクタ毎に全ビット並列書き込み動作が行われる。

データの読み出しがは、選択されたワード線 $WL$ および選択ゲート線 $SL$ に $3 \sim 5V$ 、選択されたビット線 $BL$ に $1 \sim 2V$ 、ソースに $0V$ を印加することにより行われる。

#### 【0008】

DINOR型フラッシュメモリにおいて、特に問題となるのは、データ書き込み動作、具体的には、「1」データ書き込みセル、つまりFNトンネリングによりフローティングゲート中の電子を引き抜くセルにおいて、ドレイン-基板間にバンド間トンネル電流が流れることである。

#### 【0009】

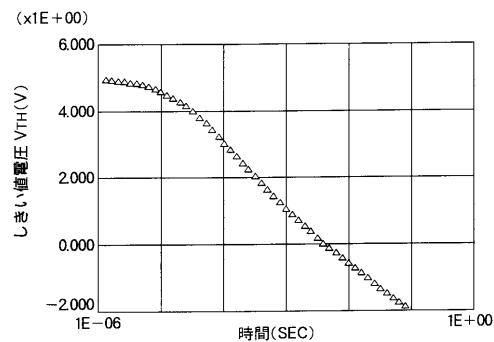

図17は、標準的な $0.6\mu m$ プロセスにより試作されたDINOR型フラッシュメモリのデバイスパラメータを用いてシミュレーションにより計算した書き込み動作結果を示す図である。図17において、横軸は時間を、縦軸はしきい値電圧をそれぞれ表している。図17からわかるように、ワード線に $-10V$ 、ビット線に $6V$ を印加することにより、およそ $1m$ 秒の書き込み時間で、しきい値電圧 $VTH$ が $5V$ から $1V$ に遷移し、書き込み動作が完了する。

#### 【0010】

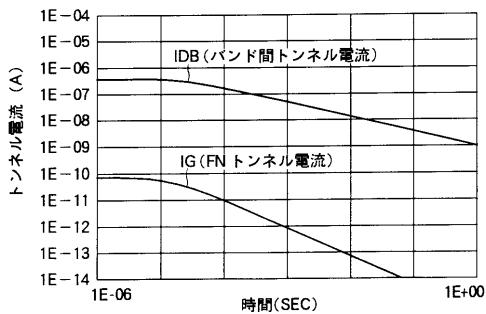

また、図18は、図17の書き込み動作におけるFNトンネリングによるゲート電流 $IG$ と、バンド間トンネリングによるドレイン-基板間電流 $IDB$ をシミュレーションにより計算した結果を示す図である。図18において、横軸は時間を、縦軸はトンネル電流値をそれぞれ表している。

図18に示すように、ゲート電流 $IG$ と、ドレイン-基板間電流 $IDB$ とも、書き込み動作の進行とともに減少するが、ここで重要な点は、ドレイン-基板間電流 $IDB$ はゲート電流 $IG$ よりも4桁近くも大きく、1セルにつき $300 \sim 400 nA$ 以上にもなっていることである。

#### 【0011】

したがって、一般的なDINOR型フラッシュメモリのように、書き込み動作を全ビット並列的に行うと、ドレインと基板との間に大電流が流れ、ドレイン電圧 $6V$ を、チップ内昇圧電源を用いて動作させることが困難となる可能性がある。

たとえば、ビット線の本数を1024本とした場合、最大限 $300 \sim 400 \mu A$ にもなる電流が、ドレイン-基板間に流れる可能性がある。

#### 【0012】

##### (2) AND型フラッシュメモリ

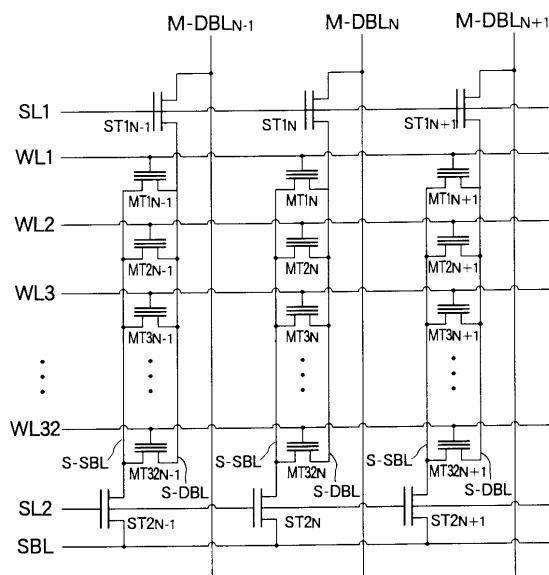

図19は、主ビット線3本、副ビット線および副ソース線に並列に接続されるメモリセルが32個の場合のAND型フラッシュメモリのメモリアレイ構成を示す図である。

このAND型フラッシュメモリは、ビット線、ソース線とも主配線と副配線とに階層化さ

10

20

30

40

50

れ、それぞれ主配線と副配線との間に選択トランジスタが配置され、副ソース線と副ビット線間にメモリセルトランジスタが並列に配置された、いわゆるコンタクトレスNOR型メモリアレイ構造を有している。

#### 【0013】

図19のメモリアレイにおいて、WL1～WL32はワード線、SL1, SL2は選択ゲート線、M-DBLN-1, M-DBLN, M-DBLN+1は主ビット線、S-DBLは副ビット線、SBLは共通ソース線、S-SBLは副ソース線、MT1N-1～MT32N-1, MT1N～MT32N, MT1N+1～MT32N+1はメモリセルトランジスタ、ST1N-1, ST1N, ST1N+1, ST2N-1, ST2N, ST2N+1は選択トランジスタをそれぞれ示している。 10

#### 【0014】

このAND型フラッシュメモリアレイは、図15に示すDINOR型フラッシュメモリアレイと比較すると、いわゆる、コンタクトレスメモリアレイ構造のために、同一デザインルールの場合、セル面積が小さくなるという利点がある。

#### 【0015】

図20は、図19に示すようなAND型フラッシュメモリの消去、書き込み、並びに読み出し時のバイアス条件を示す図である。

このAND型フラッシュメモリの場合もDINOR型フラッシュメモリと同様のバイアス条件下で各動作制御が行われ、消去はFNトンネリングによるフローティングゲート中への電子注入により行われ、データ書き込みは、FNトンネリングによりフローティングゲート中の電子をドレインより引き抜くことにより行われる。 20

したがって、AND型フラッシュメモリの場合においても、DINOR型フラッシュメモリの場合と同様の問題が生じる。

つまり、ワード線セクタ毎に、全ビット並列的にデータ書き込み動作を行うとバンド間トンネリングによりドレイン-基板間に大電流が流れ、単一電源で動作させることが困難となる可能性がある。

#### 【0016】

##### (3) ACEE型フラッシュメモリ

図21は、ACEE型フラッシュメモリのメモリセル構成を示す図である。また、図22は、図21に示すようなACEE型フラッシュメモリの消去、書き込み、並びに読み出し時のバイアス条件を示す図である。 30

ACEEセルは、ソースおよびドレインが埋め込み拡散層により形成される、いわゆるコンタクトレスアレイ構造を有しており、AND型フラッシュのメモリアレイ構造と基本的に同じである。

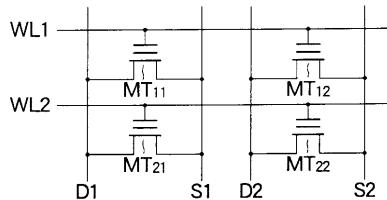

図21において、WL1, WL2はワード線、D1, D2はドレイン側ビット線、S1, S2はソース側ビット線、MT11, MT12, MT21, MT22はメモリセルトランジスタをそれぞれ示している。

#### 【0017】

しかし、ACEE型フラッシュメモリの動作は、消去はFNトンネリングによりフローティングゲート中の電子をソース側から引き抜くことにより、データの書き込みをFNトンネリングによりソース側からフローティングゲート中に電子を注入することにより行われ、その動作は、上述したDINOR型フラッシュメモリおよびAND型フラッシュメモリと逆になっている。 40

したがって、ACEE型フラッシュメモリの場合には、DINOR型フラッシュメモリおよびAND型フラッシュメモリの場合のようなバンド間トンネル電流の問題はまったく生じない。

つまり、ACEE型フラッシュの場合においても、消去時にソース-基板間にバンド間トンネル電流が流れるが、消去動作の場合は書き込み動作の場合と違ってデータの「1」、「0」を制御する必要がないために、消去時に印加するソース電圧は昇圧電圧を用いる必要がなく電源電圧V<sub>CC</sub>が印加される。 50

**【0018】**

しかしながら、A C E E セルは、電子の注入・引き抜きをF L O T O X セルのように、ソース拡散層の部分領域に設けられたトンネル窓を介して行ったり、ドレイン側のチャンネル部にコントロールゲートによる選択トランジスタ部を設けることにより過剰消去セルを救済する等、完全な1トランジスタメモリタイプのコンセプトに基づいていない。

したがって、A C E E セルは、セル面積が大きくなり、大容量のフラッシュメモリに適していない。

**【0019】****【発明が解決しようとする課題】**

上述したように、D I N O R 型、A N D 型、およびA C E E 型のフラッシュメモリは、データの書き込み／消去とともにF N トンネリングにより行われるが、上述した各問題がある。10

すなわち、D I N O R 型フラッシュメモリおよびA N D 型フラッシュメモリの場合には、データ書き込み時にドレイン - 基板間に流れるバンド間トンネル電流のために、単一電源で動作させることが困難である。

**【0020】**

また、A C E E 型フラッシュメモリの場合には、完全な1トランジスタメモリタイプのコンセプトに基づいていないために、セル面積が大きくなり、大容量のフラッシュメモリに適していない。

**【0021】**

本発明は、かかる事情に鑑みてなされたものであり、その目的は、単一電源で動作可能で、しかも完全な1トランジスタメモリタイプのセル面積の小さい半導体不揮発性記憶装置を提供することにある。20

**【0022】****【課題を解決するための手段】**

上記目的を達成するため、本発明では、ビット線、ソース線とも主配線と副配線とに階層化され、それぞれ主配線と副配線とが動作に応じて選択的に接続され、かつ副ソース線と副ビット線間に複数のメモリセルが並列接続され、各メモリセルのゲートがワード線に接続され、上記副ソース線と副ビット線が素子分離膜の下部に形成された埋め込み拡散層より構成されるコンタクトレスメモリアレイ構造を有する半導体不揮発性記憶装置であって、データの書き込み時には、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、上記ビット線の主配線が基準電位または第2の正電圧に設定され、上記ソース線の主配線を基準電位として、F N トンネリングにより、チャンネル全面から電荷蓄積層中に電荷を注入することにより所定データの書き込みを行い、消去時には、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを接続状態とし、選択されたワード線が負電圧に設定され、非選択のワード線が基準電位に設定され、上記ビット線の主配線が正電圧に設定され、上記ソース線の主配線を基準電位として、F N トンネリングによりドレイン側から電荷蓄積層中の電荷を引き抜くことにより消去を行う。30

**【0023】**

また、本発明の半導体不揮発性記憶装置では、上記コンタクトレスメモリアレイ構造が複数並列に配列されたメモリアレイを有し、上記書き込み時は、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、第1のデータを書き込むメモリセルが接続された上記ビット線の主配線が基準電位に設定され、第2のデータを書き込むメモリセルが接続された上記ビット線の主配線が第2の電圧に設定され、上記ソース線の主配線を基準電位として、ワード線セクタを単位として全ビット並列的にデータの書き込みを行い、上記消去時は、全ビット線の主配線と副配線とを接続状態とし、全ソース線の主配線と副配線とを接続状態とし、選択され40

たワード線が負電圧に設定され、非選択のワード線が基準電位に設定され、全ビット線の主配線が正電圧に設定され、上記ソース線の主配線を基準電位として、消去を行う。

また、本発明の半導体不揮発性記憶装置では、上記コンタクトレスメモリアレイ構造が複数並列に配列されたメモリアレイを有し、上記書き込み時は、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、第1のデータを書き込むメモリセルが接続された上記ビット線の主配線が基準電位に設定され、第2のデータを書き込むメモリセルが接続された上記ビット線の主配線が第2の電圧に設定され、上記ソース線の主配線を基準電位として、ワード線セクタを単位として全ビット並列的にデータの書き込みを行い、上記消去時は、ワード線セクタを単位として、全ビットビット線の主配線と副配線とを接続状態とし、全ソース線の主配線と副配線とを接続状態とし、選択されたワード線が負電圧に設定され、非選択のワード線が基準電位に設定され、全ビット線の主配線が正電圧に設定され、上記ソース線の主配線を基準電位とし、かつ消去パルスが複数の消去パルスに分割され、消去の終了したセルのビット線パルスが正電圧から基準電位に切り換えられる。

## 【0024】

また、本発明の半導体不揮発性記憶装置では、ビット線、ソース線とも主配線と副配線とに階層化され、それぞれ主配線と副配線とが動作に応じて選択的に接続され、かつ副ソース線と副ビット線間に複数のメモリセルが並列接続され、各メモリセルのゲートがワード線に接続され、上記副ソース線と副ビット線が素子分離膜の下部に形成された埋め込み拡散層より構成されるコンタクトレスメモリアレイ構造を有する半導体不揮発性記憶装置であって、データの書き込み時には、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、上記ビット線の主配線が基準電位または第2の正電圧に設定され、上記ソース線の主配線を基準電位として、FNトンネリングにより、チャンネル全面から電荷蓄積層中に電荷を注入することにより所定データの書き込みを行い、消去時には、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを接続状態とし、全ワード線が負電圧に設定され、上記ビット線の主配線が基準電位に設定され、上記ソース線の主配線を基準電位として、FNトンネリングによりチャンネル全面から電荷蓄積層中の電荷を引き抜くことにより消去を行う。

また、上記コンタクトレスメモリアレイ構造が複数並列に配列されたメモリアレイを有し、上記書き込み時は、ビット線の主配線と副配線とを接続状態とし、ソース線の主配線と副配線とを非接続状態とし、選択されたワード線が第1の正電圧に設定され、非選択のワード線が上記第1の正電圧より低い第2の正電圧に設定され、第1のデータを書き込むメモリセルが接続された上記ビット線の主配線が基準電位に設定され、第2のデータを書き込むメモリセルが接続された上記ビット線の主配線が第2の電圧に設定され、上記ソース線の主配線を基準電位として、ワード線セクタを単位として全ビット並列的にデータの書き込みを行い、上記消去時は、全ビット線の主配線と副配線とを接続状態とし、全ワード線が負電圧に設定され、全ビット線の主配線が基準電位に設定され、上記ソース線の主配線を基準電位として、消去を行う。

## 【0025】

また、本発明では、電荷蓄積層を備えたメモリセルを複数有する半導体不揮発性装置であって、メモリセルが消去ブロック単位毎に分割され、各分割ブロックに対応して設けられた複数のカラムデコーダを有し、少なくとも消去および書き込み動作をカラムデコーダ単位で行う。

## 【0026】

## 【作用】

本発明の半導体不揮発性記憶装置によれば、ビット線、ソース線とも主配線と副配線とに階層化され、それぞれ主配線と副配線とが動作に応じて選択的に接続され、かつ副ソース

10

20

30

40

50

線と副ビット線間にメモリセルが並列接続された構成において、データの書き込み動作がF Nトンネリングによる電子注入により行われ、消去動作がF Nトンネリングによる電子引き抜きによって行われる。その結果、データ書き込み時にバンド間トンネル電流が流れないため、単一電源で動作可能な半導体不揮発性記憶装置が実現される。

また、本半導体不揮発性記憶装置は、いわゆるコンタクトレスN O R型メモリアレイ構造を有する完全な1トランジスタメモリタイプのフラッシュメモリであり、大容量フラッシュメモリに適している。

#### 【0027】

さらに、本発明の半導体不揮発性装置は、その消去動作において、ビット毎ペリファイ消去動作を行うために、消去時のしきい値電圧分布のバラツキが狭い。その結果、ドレイン側に選択ゲートを設ける必要がない完全な1トランジスタメモリタイプの半導体不揮発性記憶装置を実現できるだけでなく、今後の電源電圧の低電圧化に対しても充分に読み出しマージンが確保される。10

#### 【0028】

また、本発明の半導体不揮発性装置によれば、消去および書き込み動作がカラムデコード単位で行われる。その結果、N O R型の半導体不揮発性記憶装置において、新たな配線層を増やすことなく、ドレインディスターブ耐性の向上を図れるメモリセル構造が実現される。

#### 【0029】

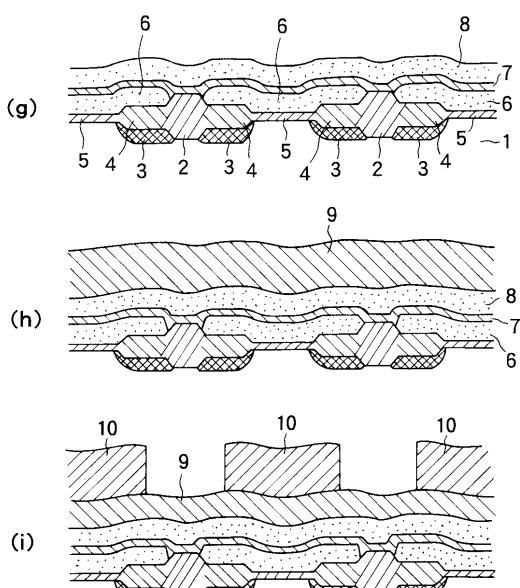

#### 【実施例】

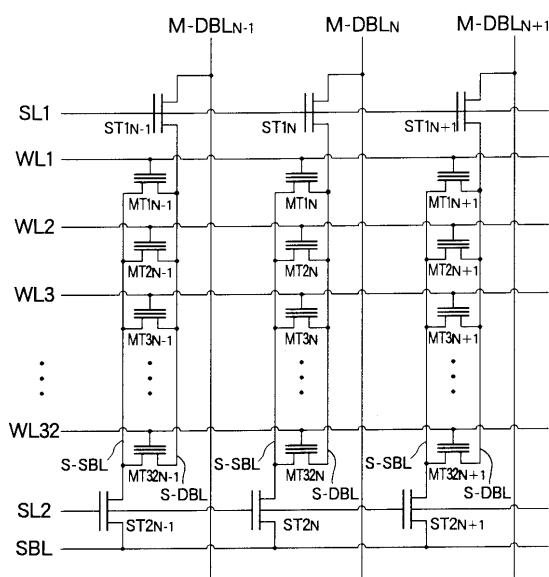

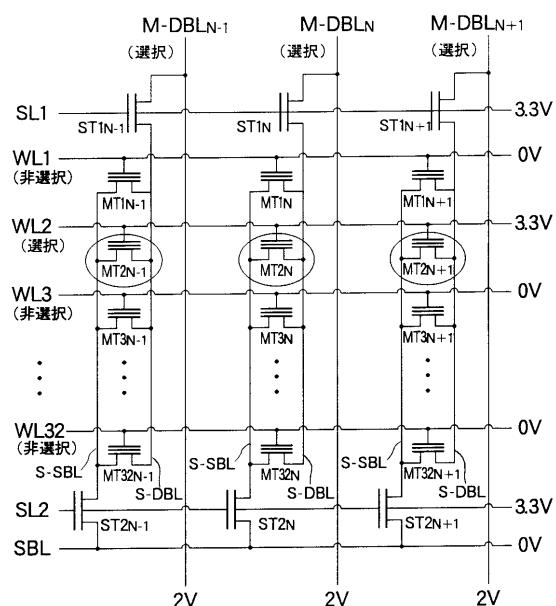

図1は、本発明に係るフラッシュメモリのメモリアレイ構成を示す図である。図1のメモリアレイにおいて、W L 1 ~ W L 3 2はワード線、S L 1 ~ S L 2は選択ゲート線、M - D B L N - 1 , M - D B L N , M - D B L N + 1 は主ビット線、S - D B L は副ビット線、S B Lは共通ソース線、S - S B Lは副ソース線、M T 1 N - 1 ~ M T 3 2 N - 1 , M T 1 N ~ M T 3 2 N , M T 1 N + 1 ~ M T 3 2 N + 1 はメモリセルトランジスタ、S T 1 N - 1 , S T 1 N , S T 1 N + 1 、S T 2 N - 1 , S T 2 N , S T 2 N + 1 は選択トランジスタをそれぞれ示している。20

#### 【0030】

このメモリアレイ構成自体は、図19のA N D型メモリアレイ構成と同じである。つまり、ビット線、ソース線とも主配線と副配線とに階層化され、それぞれ主配線と副配線との間に選択トランジスタが配置され、副ソース線と副ビット線間にメモリセルトランジスタが並列に配置された、いわゆるコンタクトレスN O R型メモリアレイ構造を有している。しかし、図2および図3に示すように、消去、書き込み、並びに読み出し時の各配線に対するバイアス条件が、図20に示す従来のA N D型メモリアレイのバイアス条件と異なる。

以下に、本発明に係るフラッシュメモリの構造、消去、書き込み、および読み出し時の各配線に対するバイアス条件、並びに動作について、図面に関連づけて順を追って説明する。

#### 【0031】

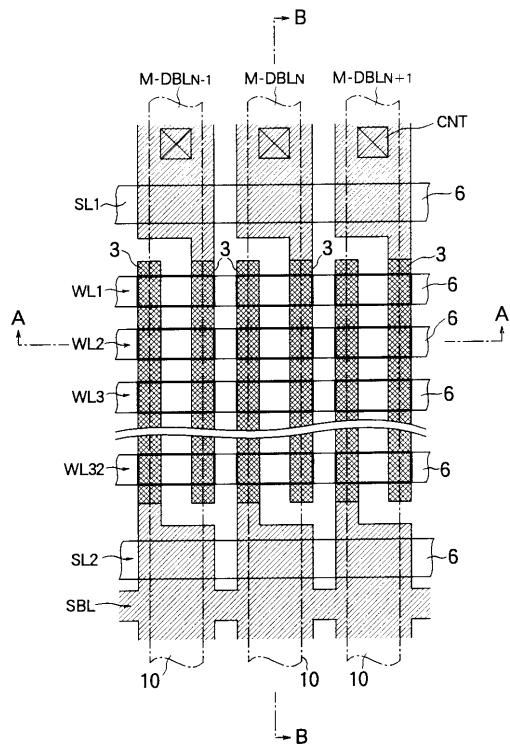

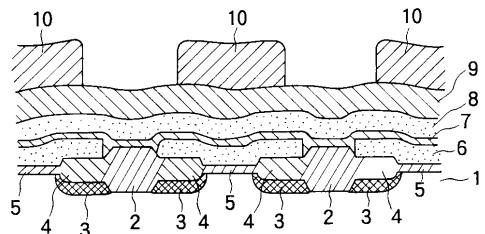

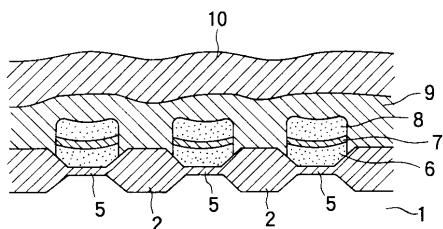

図4は図1のメモリアレイの平面パターンレイアウト図で、図5は図4中のA - A線矢視方向における断面図、図6は図4のB - B線矢視方向における断面図である。40

図において、1は半導体基板、2は第1L O C O S、3はN<sup>+</sup>埋め込み拡散層、4は第2L O C O S、5はトンネル酸化膜、6はフローティングゲート用ポリシリコン層、7はO N O積層絶縁膜、8はコントロールゲート用ポリシリコン層、9は絶縁膜、10はアルミニウム(A 1)配線、C N Tはコンタクトホールをそれぞれ示している。

#### 【0032】

図4～図6に示すように、副ビット線S - D B Lおよび副ソース線S - S B Lが、第2L O C O S酸化膜4の下部に形成された埋め込み拡散層3により構成される、いわゆるコンタクトレスN O R型メモリアレイ構造をなしている。

#### 【0033】

10

20

30

40

50

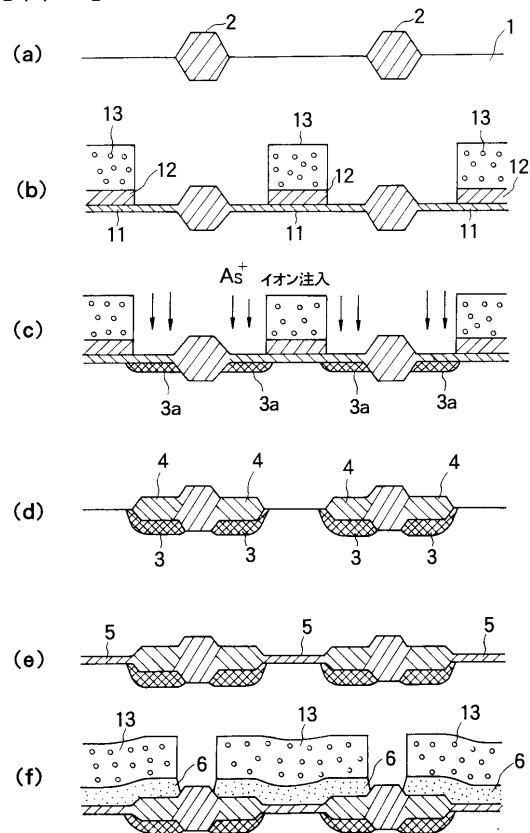

次に、A - A 線断面から眺めた場合の製造方法の一例を、図7および図8を参照しながら説明する。

まず、図7(a)に示すように、半導体基板1に対して、素子分離のためのLOCOS酸化を行い、第1LOCOS2を形成する。

次に、図7(b)に示すように、厚さ10nm程度のパッド酸化膜11を形成し、さらに30nm程度のSi<sub>3</sub>N<sub>4</sub>膜12をデポ後、埋め込み拡散層形成のためのエッティングを行う。

そして、図7(c)に示すように、レジスト膜13を所望の領域に形成した状態で、As<sup>+</sup>イオンを1E14~1E16程度イオン注入し、ソース・ドレイン拡散層3aを形成する。 10

#### 【0034】

次に、図7(d)に示すように、レジスト膜13を剥離後、第2LOCOS酸化を行い、ソース・ドレイン拡散層3a上に膜厚100nm程度の第2LOCOS4を形成し、埋め込みソース・ドレイン拡散層3を構成する。そして、第2LOCOS酸化後、Si<sub>3</sub>N<sub>4</sub>膜12、パッド酸化膜11を除去する。

#### 【0035】

次に、図7(e)に示すように、トンネル酸化膜5を10nm程度の膜厚に形成する。続いて、図7(f)に示すように、N<sup>+</sup>ドープポリシリコンよりなるフローティングゲート用ポリシリコン層6を100nm程度の膜厚にデポ後、エッティング加工する。

#### 【0036】

次いで、図8(g)に示すように、層間のONO積層絶縁膜7を形成後、コントロールゲート用ポリシリコン層8をデポする。 20

このONO積層絶縁膜7は、たとえば、次のように形成される。まず、フローティングゲート用ポリシリコン層6の熱酸化膜を14nmの厚さに形成後、厚さ11nm程度のSi<sub>3</sub>N<sub>4</sub>膜をCVD法にて形成し、最後にSi<sub>3</sub>N<sub>4</sub>膜上に熱酸化により厚さ2nm程度の熱酸化膜を形成する。このようにして形成されるONO積層酸化膜7の膜厚は、SiO<sub>2</sub>換算で22nm程度である。

また、コントロールゲート用ポリシリコン層8は、100nm程度のN<sup>+</sup>ドープポリシリコンと100nm程度のタンゲステンシリサイド膜よりなるポリサイド構造である。 30

#### 【0037】

次に、図8(h)に示すように、コントロールゲート用ポリシリコン層8、ONO積層絶縁膜7、およびフローティングゲート用ポリシリコン層6をセルファラインでエッティング加工する。

そして、コントロールゲート用ポリシリコン層8上に絶縁膜9を形成した後、通常のCMOSプロセスと同様、図8(i)に示すように、主ビット線M-DBLN-1、M-DBLN、M-DBLN+1としてのA1配線10を形成する。

#### 【0038】

次に、本発明に係るフラッシュメモリの消去、書き込み、読み出しの各種動作について、図9~図13を参照しながら説明する。 40

#### 【0039】

図9は、本発明に係るフラッシュメモリにおける消去動作の第1の実施例によるバイアス条件を示す図である。

この第1の実施例による消去動作は、FNトンネリングによりドレイン側からフローティングゲート中の電子を引き抜くことにより行われる。

つまり、選択するワード線、たとえば図7に示すように、ワードWL2に-14V、全主ビット線M-DBLN-1, M-DBLN, M-DBLN+1に3.3V(電源電圧V<sub>CC</sub>)、選択ゲート線SL1, SL2に5Vを印加することにより行われる。このとき、他のワード線WL1, WL~WL32および共通ソース線SBLには0Vを印加する。 50

#### 【0040】

この図 7 に示す消去時においても、ドレイン - 基板間にバンド間トンネル電流が流れる。しかしながら、DINOR型およびAND型フラッシュメモリのデータ書き込み動作と違って、この場合、ビット線電圧によりデータの「1」、「0」を制御する必要がないため、印加するビット線電圧は電源電圧 $V_{CC}$ でよいことから、バンド間トンネル電流は問題にならない。

#### 【0041】

また、消去ブロックの単位として、ワード線セクタを単位とする場合と、同じ副ビット線に連なる32ワード線を単位とする場合が考えられるが、前者の場合、データ書き込み時のディスターブが厳しくなるため、後者の方が適当である。この場合、消去動作は、ワード線セクタを単位として、WL1～WL32と順々に消去を行っていけばよい。

10

また、図7の消去動作において、各ビット線電圧を3.3V～0Vと制御することにより、ビット毎ペリファイ消去動作が可能となり、消去時のしきい値電圧VTH分布の広がりを狭く抑えることが可能となる。

#### 【0042】

このビット毎ペリファイ消去動作は、消去パルスを複数の消去パルスに分割して、次のように行う。

まず、全ビット線の図示しない読み出し／書き込み用ラッチをセットすることにより、消去時に全ビット線に電源電圧 $V_{CC}$ (3.3V)が印加されるように設定する。

次に、各消去パルス印加後、ワード線にペリファイ電圧を印加するペリファイ読み出し動作により、消去が終了したビット線メモリセルの読み出し／書き込み用ラッチをリセットすることにより、消去時にビット線電圧が0Vになるように設定する。

20

そして、全ビット線の読み出し／書き込み用ラッチがリセットされることで、消去動作を終了する。

#### 【0043】

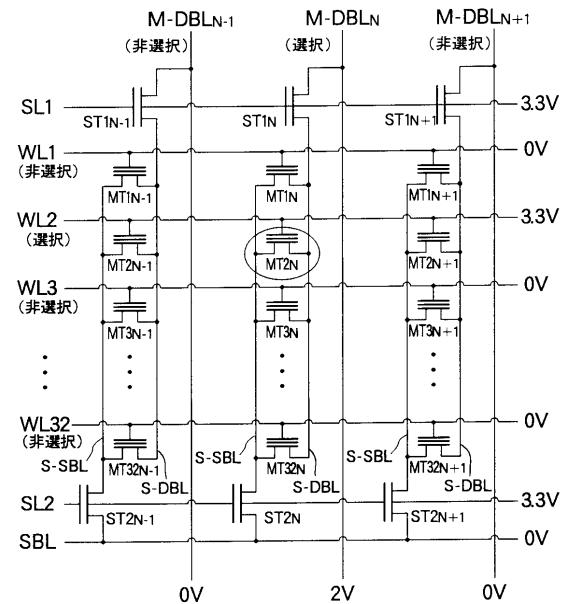

図10は、本発明に係るフラッシュメモリにおける消去動作の第2の実施例によるバイアス条件を示す図である。

第2の実施例においては、消去動作は、FNトンネリングによりチャンネル全面からフローティングゲート中の電子を引き抜くことにより行われる。

たとえば、図10の例においては、ワード線WL1～WL32に-18Vを印加することによりブロック消去が行われる。

30

ただし、図10の第2の実施例の場合においては、図9の第1の実施例の場合と異なり、ビット毎ペリファイ消去動作を行うことが不可能であり、消去後のしきい値電圧VTH分布のバラツキ抑制という観点からは、第1の実施例と比べて不利になる。

#### 【0044】

次に、書き込み動作について説明する。

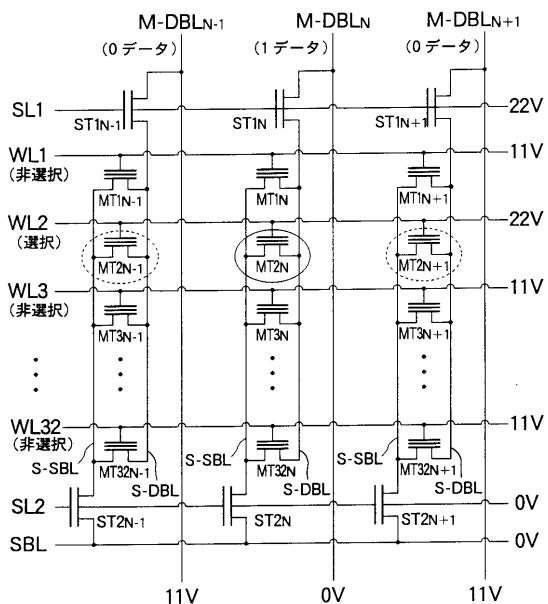

図11は、本発明に係るフラッシュメモリにおけるデータ書き込み動作の一実施例におけるバイアス条件を示す図である。

本例では、データの書き込み動作は、FNトンネリングによりチャンネル全面からフローティングゲート中に電子を注入することにより行われる。

たとえば、図11の例においては、選択するワード線WL2および選択ゲート線SL1に22Vを印加し、「1」データ(所定データまたは第1のデータ)書き込みセルMT2Nが接続された主ビット線M-DBLNに0V、「0」データ(第2のデータ)書き込みセルMT2N-1、MT2N+1が接続された主ビット線M-DBLN-1、M-DBLN+1に中間電位11Vを印加することにより、ワード線セクタを単位として、全ビット並列的にデータ書き込みが行われる。このとき選択ゲート線SL2および共通ソース線SBLは0Vに保持される。

40

その結果、「1」データ書き込みセルにのみフローティングゲート中に電子が注入され、メモリセルのVTHが5V以上になる。

#### 【0045】

また、図11の書き込み動作において、各副ソース線S-SBLは、それぞれの各副ビッ

50

ト線 S - D B L と同電位になるが、ソース側の選択ゲート線 S L 2 が 0 V になって共通ソース線 S B L と切り離されているため、隣合う副ソース線間の短絡が防止される。

#### 【 0 0 4 6 】

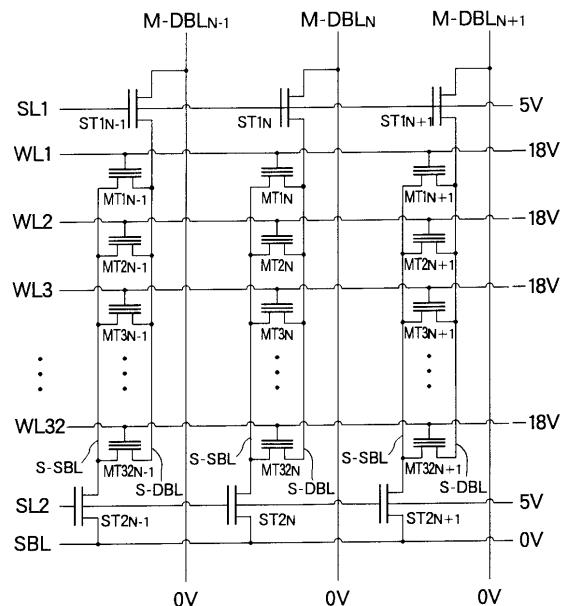

次に、読み出し動作について説明する。

図 1 2 および図 1 3 は、本発明に係るフラッシュメモリにおける読み出し動作の実施例のバイアス条件を示す図である。具体的には、図 1 2 はランダムアクセスモードにおける読み出し動作時のバイアス条件を示し、図 1 3 はワード線を単位としたページモードでの読み出し動作時のバイアス条件を示している。

#### 【 0 0 4 7 】

図 1 2 のランダムモードでは、選択するメモリセル、たとえばメモリセル M T 2 N が接続されたワード線 W L 2 に 3 . 3 V、主ビット線 M - D B L N に 2 V を印加し、選択ゲート線 S L 1 , S L 2 に 3 . 3 V を印加する。このとき、非選択のワード線 W L 1 , W L 3 ~ W L 3 2 、主ビット線 M - D B L N - 1 , M - D B L N + 1 、並びに共通ソース線 S B L は 0 V に保持される。

10

その結果、読み出しセルがオンしている場合にデータ「 0 」、オフしている場合にデータ「 1 」と、図示しない制御系により判断される。

#### 【 0 0 4 8 】

また、図 1 3 のページモードでは、選択するワード線 W L 2 に 3 . 3 V、全主ビット線 M - D B L N - 1 , M - D B L N , M - D B L N + 1 に 2 V を印加する。

その結果、選択するワード線 W L 2 上のメモリセルの M T 2 N - 1 , M T 2 N , M T 2 N + 1 のデータ内容が、それぞれのビット線毎の図示しない読み出し / 書き込み用ラッチに読み込まれる。

20

#### 【 0 0 4 9 】

以上の消去、書き込み、読み出しの各動作時のバイアス条件を図表にまとめたものが図 2 および図 3 であり、図 2 が消去動作が図 9 の第 1 の実施例の場合であり、図 3 が消去動作が図 1 0 の第 2 の実施例の場合である。

#### 【 0 0 5 0 】

以上説明したように、本実施例によれば、D I N O R 型フラッシュメモリおよびA N D 型フラッシュメモリにおいて問題となるバンド間トンネル電流の問題を回避でき、しかもF L O T O X 型 E E P R O M およびA C E E 型フラッシュメモリのようにセル面積を大きくしない完全な 1 トランジスタメモリタイプの F N / F N 式 N O R 型フラッシュメモリを実現することができる。

30

よって、単一電源で動作可能な大容量 N O R 型フラッシュメモリが実現できる。

#### 【 0 0 5 1 】

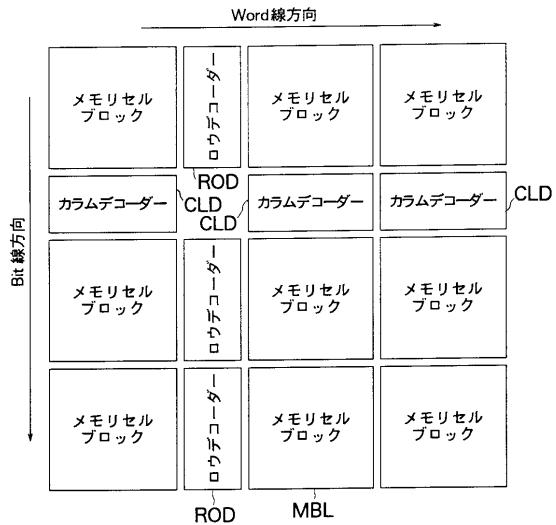

図 1 4 は、本発明に係るフラッシュメモリ回路の他の実施例を示すブロック構成図である。

図 1 4 において、C L D はカラムデコーダ、R O D はロウデコーダ、M B L はメモリセルブロックをそれぞれ示している。

#### 【 0 0 5 2 】

本実施例は、図 1 4 に示すように、メモリセルを消去ブロック単位毎に分割し、そのブロック M B L 每にカラムデコーダ C L D を配置して、書き込みおよび消去をカラムデコーダ C L D 単位で行うことを特徴としている。

40

この構成において、一つのブロック M B L 内のメモリセルの構造は、たとえば通常の N O R 型の構造をしている。ここで、メモリセル内での 1 本のビット線に連なるトランジスタの数は、ドレインディスターブに対してのマージンが取れる範囲、たとえば数百ビット程度に設定されている。

#### 【 0 0 5 3 】

このような構成において、消去動作は、たとえばセルのコントロールゲート、すなわちワード線に + 2 0 V 、ソース、ドレイン、すなわちビット線、および基板に 0 V を印加して、フローティングゲートに電子を注入することで実現される。

書き込み動作は、たとえばセルのコントロールゲート（ワード線）に -12V、ドレイン（ビット線）に 5V を印加して、フローティングゲートより電子を引き抜くことで実現される。

また、同じコントロールゲート（ワード線）上に存在する、書き込みを行いたくないセルは、ドレイン（ビット線）を 0V に保持するため、フローティングゲートとドレインとの間の電界が緩和され、フローティングゲートからの電子の抜けが発生しなくなる。

読み出し動作は、セルのコントロールゲートに電源電圧  $V_{CC}$  、ドレイン（ビット線）に +1V、ソースおよび基板に 0V を印加して、セル電流が流れるか否かでデータの「1」、「0」を判断する。

#### 【0054】

このように本実施例では、フラッシュメモリセルにおいて、そのオペレーションをカラムデコード単位（ビット線方向）単位で行うことから、以下に示すような利点がある。

すなわち、たとえば、フローティングゲートを持つ NOR 型のフラッシュメモリでは、そのビット線に多数（数 k ビット）のメモリセルトランジスタが連なる構造をしている。このため、セルの書き込みを行う際、ドレンディスターブが起こり、これが深刻な問題となっていた。

#### 【0055】

このようなドレンディスターブに対する回避策として、前述したビット線を分割する DINOR 型のメモリセル構造がある。この構造では、メインの主ビット線にサブの副ビット線が連なり、これらの間を選択トランジスタで分割する構成を取っている。

副ビット線には数十ビットのメモリセルしか接続されていないため、NOR 型で問題となる書き込み時のドレンディスターブに対しては 2 衔程度マージンが広がることになる。

#### 【0056】

しかしながら、この DINOR 型フラッシュメモリでは、ビット線を分割してサブのビット線を形成するため、さらにもう一層の配線層が必要となる。

これに対して、本実施例の回路では、新たに配線層を増やすことなく、メモリセルを形成できる。すなわち、新たな配線層を増やすことなく、ドレンディスターブ耐性の向上を図れるメモリセル構造を実現できる。

また、この構造は C H E 書き込み方式にも適用が可能である。

#### 【0057】

#### 【発明の効果】

以上説明したように、本発明によれば、DINOR 型半導体不揮発性記憶装置およびAND 型半導体不揮発性記憶装置において問題となるバンド間トンネル電流の問題を回避でき、しかも FLOTAX 型 EEPROM および ACEE 型半導体不揮発性記憶装置のようにセル面積が大きくならず、完全な 1 トランジスタメモリタイプの FN / FN トンネリング方式の NOR 型半導体不揮発性記憶装置を実現することができる。

よって、单一電源で動作可能な、大容量 NOR 型半導体不揮発性記憶装置を実現できる利点がある。

#### 【0058】

また、NOR 型の半導体不揮発性記憶装置において、新たな配線層を増やすことなく、ドレンディスターブ耐性の向上を図れるメモリセル構造を実現できる。

#### 【図面の簡単な説明】

【図 1】本発明に係るフラッシュメモリのメモリアレイ構成を示す図である。

【図 2】本発明に係るフラッシュメモリの第 1 の消去、書き込み、読み出しの各動作時のバイアス条件を示す図である。

【図 3】本発明に係るフラッシュメモリの第 2 の消去、書き込み、読み出しの各動作時のバイアス条件を示す図である。

【図 4】図 1 のメモリアレイの平面パターンレイアウトを示す図である。

【図 5】図 4 の A - A 線矢視方向における断面図である。

【図 6】図 4 の B - B 線矢視方向における断面図である。

【図 7】図 4 のフラッシュメモリの製造方法を説明するための工程図である。

【図 8】図 4 のフラッシュメモリの製造方法を説明するための工程図である。

【図 9】本発明に係るフラッシュメモリにおける消去動作の第 1 の実施例によるバイアス条件を示す図である。

【図 10】本発明に係るフラッシュメモリにおける消去動作の第 2 の実施例によるバイアス条件を示す図である。

【図 11】本発明に係るフラッシュメモリにおける書き込み動作のバイアス条件を示す図である。

【図 12】本発明に係るフラッシュメモリのランダムモードにおける読み出し動作のバイアス条件を示す図である。 10

【図 13】本発明に係るフラッシュメモリのページモードにおける読み出し動作のバイアス条件を示す図である。

【図 14】本発明に係るフラッシュメモリ回路の他の実施例を示すブロック構成図である。

【図 15】主ビット線 2 本、副ビット線に連なるワード線 8 本の 2 群から構成される D I N O R 型フラッシュのメモリアレイ構成を示す図である。

【図 16】図 15 に示すような D I N O R 型フラッシュメモリの消去、書き込み、並びに読み出し時のバイアス条件を示す図である。

【図 17】標準的な 0 . 6  $\mu$ m プロセスにより試作された D I N O R 型フラッシュメモリのデバイスパラメータを用いてシミュレーションにより計算した書き込み動作結果を示す図である。 20

【図 18】図 17 の書き込み動作における F N トンネリングによるゲート電流と、バンド間トンネリングによるドレイン - 基板間電流をシミュレーションにより計算した結果を示す図である。

【図 19】主ビット線 3 本、副ビット線および副ソース線に並列に接続されるメモリセルが 32 個の場合の A N D 型フラッシュメモリのメモリアレイ構成を示す図である。

【図 20】図 19 に示すような A N D 型フラッシュメモリの消去、書き込み、並びに読み出し時のバイアス条件を示す図である。

【図 21】A C E E 型フラッシュメモリのメモリセル構成を示す図である。

【図 22】図 21 に示すような A C E E 型フラッシュメモリの消去、書き込み、並びに読み出し時のバイアス条件を示す図である。 30

#### 【符号の説明】

W L 1 ~ W L 3 2 ... ワード線

S L 1 , S L 2 ... 選択ゲート線

M ... D B L は主ビット線

S - D B L ... 副ビット線

S B L ... 共通ソース線

S - S B L ... 副ソース線

M T 1 N - 1 ~ M T 3 2 N - 1 , M T 1 N ~ M T 3 2 N , M T 1 N + 1 ~ M T 3 2 N + 1 ... メモリセルトランジスタ 40

S T 1 N - 1 , S T 1 N , S T 1 N + 1 , S T 2 N - 1 , S T 2 N , S T 2 N + 1 ... 選択トランジスタ

1 ... 半導体基板

2 ... 第 1 L O C O S

3 ... N<sup>+</sup> 埋め込み拡散層

4 ... 第 2 L O S O S

5 ... トンネル酸化膜

6 ... フローティングゲート用ポリシリコン層

7 ... O N O 積層絶縁膜

8 ... コントロールゲート用ポリシリコン層

9 ... 絶縁膜

10 ... アルミニウム (A1) 配線

【図1】

【図2】

|                   | SL1  | SL2  | WL                | DBL                     | ソース |

|-------------------|------|------|-------------------|-------------------------|-----|

| 消去                | 5V   | 5V   | 選択 -14V<br>非選択 0V | 3.3V → 0V               | 0V  |

| データ書き込み           | 22V  | 0V   | 選択 22V<br>非選択 11V | [1]データ 0V<br>[0]データ 11V | 0V  |

| データ読み出し (ランダムモード) | 3.3V | 3.3V | 選択 3.3V<br>非選択 0V | 選択 2V<br>非選択 0V         | 0V  |

| データ読み出し (ページモード)  | 3.3V | 3.3V | 選択 3.3V<br>非選択 0V | 2V                      | 0V  |

【図3】

|                   | SL1  | SL2  | WL                | DBL                     | ソース |

|-------------------|------|------|-------------------|-------------------------|-----|

| 消去                | 5V   | 5V   | -18V              | 0V                      | 0V  |

| データ書き込み           | 22V  | 0V   | 選択 22V<br>非選択 11V | [1]データ 0V<br>[0]データ 11V | 0V  |

| データ読み出し (ランダムモード) | 3.3V | 3.3V | 選択 3.3V<br>非選択 0V | 選択 2V<br>非選択 0V         | 0V  |

| データ読み出し (ページモード)  | 3.3V | 3.3V | 選択 3.3V<br>非選択 0V | 2V                      | 0V  |

【図4】

【図5】

【図6】

【図7】

【図8】

【 図 9 】

【 図 1 0 】

【 図 1 1 】

【図12】

【図13】

【図14】

【図15】

【図16】

|            | SL   | WL   | BL      | ソース     |

|------------|------|------|---------|---------|

| 消去         | 0V   | 20V  | フローティング | 0V      |

| [1]データ書き込み | 10V  | -10V | 6V      | フローティング |

| [0]データ書き込み | 10V  | -10V | 0V      | フローティング |

| 読みだし       | 3~5V | 3~5V | 1~2V    | 0V      |

【図17】

【図18】

【図19】

【図20】

|            | SL1  | SL2  | WL   | DBL     | ソース |

|------------|------|------|------|---------|-----|

| 消去         | 0V   | 10V  | 20V  | フローティング | 0V  |

| [1]データ書き込み | 10V  | 0V   | -10V | 6V      | 0V  |

| [0]データ書き込み | 10V  | 0V   | -10V | 0V      | 0V  |

| 読みだし       | 3~5V | 3~5V | 3~5V | 1~2V    | 0V  |

【図21】

【図22】

|      | WL1  | WL2  | S1 | D1      | S2   | D2      |

|------|------|------|----|---------|------|---------|

| 消去   | -11V | -11V | 5V | フローティング | 3.3V | フローティング |

| 書き込み | 7V   | 18V  | 0V | フローティング | 7V   | フローティング |

| 読み出し | 0V   | 3.3V | 0V | 1V      | 0V   | 1V      |

---

フロントページの続き

(51)Int.Cl.<sup>7</sup> F I

H 01 L 29/788

H 01 L 29/792

(56)参考文献 特開平06-077437(JP,A)

特開平06-196715(JP,A)

特開平05-326980(JP,A)

特開平06-139785(JP,A)

特開平05-275659(JP,A)

特開平05-334885(JP,A)

特開平05-055530(JP,A)

特開平06-151785(JP,A)

特開昭57-098191(JP,A)

特開昭63-140483(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G11C 16/00-16/34

H01L 27/115

H01L 29/788-29/792