## 명세서

### 청구범위

#### 청구항 1

하부 패키지 기판, 상기 하부 패키지 기판 상에 실장된 하부 반도체 칩을 포함하는 하부 반도체 패키지, 및 상기 하부 패키지 기판의 상부면과 상기 하부 반도체 칩의 측면을 덮으며 제 1 연결홀(hole)을 포함하는 하부 몰딩막;

상기 하부 반도체 패키지 상에 배치되는 상부 패키지 기판, 및 상기 상부 패키지 기판 상에 실장된 상부 반도체 칩을 포함하는 상부 반도체 패키지;

상기 하부 패키지 기판과 상기 상부 패키지 기판을 연결시키며 상기 제 1 연결홀 안에 배치되는 제 1 연결 솔더 범프; 및

상기 하부 반도체 패키지 및 상기 상부 반도체 패키지와 접하며 상기 연결 솔더 범프의 측면을 덮는 밀봉막을 포함하되,

상기 제 1 연결 솔더 범프의 상부는 상기 제 1 연결홀 밖으로 돌출되고,

상기 밀봉막은 상기 제 1 연결홀을 채우고 상기 제 1 연결홀 밖으로 연장되어 상기 연결 솔더 범프의 돌출된 상부를 감싸는 패키지 온 패키지 장치.

#### 청구항 2

제 1 항에 있어서,

상기 밀봉막은 예폭시 수지를 포함하며 플러스 기능을 가지는 패키지 온 패키지 장치.

#### 청구항 3

제 1 항에 있어서,

상기 제 1 연결홀의 측벽은 상기 제 1 연결 솔더 범프의 측벽과 이격되는 패키지 온 패키지 장치.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 연결홀의 측벽의 표면 거칠기는 상기 하부 몰딩막의 상부면의 표면 거칠기보다 큰 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 5

제 1 항에 있어서,

상기 하부 몰딩막의 상부면과 상기 밀봉막 사이에 박리 영역이 존재하는 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 6

제 1 또는 2 항에 있어서,

상기 밀봉막은 연장되어 상기 하부 반도체 패키지와 상기 상부 반도체 패키지 사이를 채우는 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 7

제 6 항에 있어서,

상기 밀봉막은 상기 연결 솔더 범프의 측벽과 접하는 제 1 밀봉막; 및

상기 하부 반도체 칩과 상기 상부 패키지 기판 사이의 공간을 채우는 제 2 밀봉막을 포함하는 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 8

제 7 항에 있어서,

상기 제 2 밀봉막은 플러스 기능을 갖지 않는 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 9

제 1 항에 있어서,

상기 하부 반도체 칩은 상기 하부 패키지 기판 상에 플립 칩 본딩 방식으로 실장되는 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 10

제 1 항에 있어서,

상기 상부 반도체 칩은 상기 하부 반도체 칩과 다른 것을 특징으로 하는 패키지 온 패키지 장치.

#### 청구항 11

하부 패키지 기판, 상기 하부 패키지 기판 상에 배치된 하부 반도체 칩, 상기 하부 패키지 기판 상에 배치되며 상기 하부 반도체 칩과 이격된 하부 솔더 범프, 및 상기 하부 패키지 기판의 상부면과 상기 하부 반도체 칩의 측면을 덮으며 상기 하부 솔더 범프를 노출시키는 연결홀(hole)을 포함하는 하부 몰딩막을 포함하는 하부 반도체 패키지를 제조하는 단계;

상부 패키지 기판, 상기 상부 패키지 기판 상에 배치된 상부 반도체 칩, 및 상기 상부 패키지 기판 하부에 배치되는 상부 솔더 범프를 포함하는 상부 반도체 패키지를 제조하는 단계;

상기 하부 솔더 범프 및 상기 상부 솔더 범프 중 적어도 하나를 밀봉막 수지 용액으로 도포하는 단계;

상기 상부 솔더 범프가 상기 연결홀 안에 배치되도록 상기 상부 반도체 패키지를 상기 하부 반도체 패키지 상에 위치시키는 단계; 및

상기 하부 솔더 범프와 상기 상부 솔더 범프를 용착시켜 연결 솔더 범프를 형성하며 상기 연결 솔더 범프의 측벽을 덮으며 상기 상부 반도체 패키지 및 상기 하부 반도체 패키지와 접하는 밀봉막을 형성하는 단계를 포함하는 패키지 온 패키지 장치의 제조 방법.

#### 청구항 12

제 11 항에 있어서,

상기 밀봉막 수지 용액으로 도포하는 단계는,

상기 연결홀 안에 상기 밀봉막 수지 용액을 넣는 단계를 포함하는 패키지 온 패키지 장치의 제조 방법.

#### 청구항 13

제 11 항에 있어서,

상기 밀봉막 수지 용액으로 도포하는 단계는,

상기 상부 솔더 범프를 상기 밀봉막 수지 용액 안에 담그는 단계를 포함하는 패키지 온 패키지 장치의 제조 방법.

#### 청구항 14

삭제

## 청구항 15

삭제

## 청구항 16

제 11 항에 있어서,

상기 밀봉막 수지 용액은 에폭시 수지를 포함하며 플러스 기능을 가지는 패키지 온 패키지 장치의 제조 방법.

## 청구항 17

제 11 항에 있어서,

상기 밀봉막 수지 용액으로 도포하는 단계는 상기 밀봉막 수지 용액으로 상기 하부 반도체 패키지의 상부 전면 및 상기 상부 반도체 패키지의 하부 전면 중 적어도 하나를 덮는 단계를 포함하는 패키지 온 패키지 장치의 제조 방법.

## 청구항 18

제 1 항에 있어서,

상기 하부 몰딩막은 상기 제 1 연결홀에 인접한 제 2 연결홀을 더 포함하고,

상기 패키지 온 패티지 장치는 상기 하부 패키지 기판과 상기 상부 패키지 기판을 연결시키며 상기 제 2 연결홀 안에 배치되는 제 2 연결 솔더 범프를 더 포함하되,

상기 밀봉막은 상기 제 1 연결홀 밖으로 연장되어 상기 제 2 연결홀을 채우는 패키지 온 패키지 장치.

## 청구항 19

제 18 항에 있어서,

상기 제 2 연결 솔더 범프의 상부는 상기 제 2 연결홀 밖으로 돌출되며,

상기 밀봉막은 연장되어 상기 제 2 연결홀 밖으로 돌출된 상기 제 2 연결 솔더 범프의 상부를 감싸는 패키지 온 패키지 장치.

## 청구항 20

제 11 항에 있어서,

상기 하부 몰딩막의 상부면과 상기 밀봉막 사이에 박리 영역이 형성되는 패키지 온 패키지 장치의 제조 방법.

## 청구항 21

제 11 항에 있어서,

상기 연결 솔더 범프의 상부는 상기 연결홀 밖으로 돌출되도록 형성되고,

상기 밀봉막은 상기 연결홀을 채우고 상기 연결홀 밖으로 돌출된 상기 연결 솔더 범프의 상부를 감싸도록 형성되는 패키지 온 패키지 장치의 제조 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 패키지 온 패키지 장치 및 이의 제조 방법에 관한 것이다.

### 배경 기술

[0002] 전자 산업의 발달로 전자 부품의 고기능화, 고속화 및 소형화 요구가 증대되고 있다. 이러한 추세에 대응하여 현재 반도체 실장 기술은 하나의 패키지 기판에 여러 반도체 칩들을 적층하여 실장하거나 패키지 위에 패키지를 적층하는 방법이 대두되고 있다. 이중에 특히 패키지 위에 패키지를 적층하는 패키지 온 패키지(Package on

package, PoP) 장치는 각각의 적층되는 패키지 안에 반도체 칩과 패키지 기판을 포함하므로 전체 패키지의 두께가 두꺼워지는 문제점을 가진다. 이러한 PoP 장치에서 두께가 두꺼워지는 것을 방지하기 위하여, 각각의 패키지를 형성할 때 얇은 반도체 칩을 이용할 수 있으나, 이 경우 반도체 칩 및 각각의 패키지의 흠(warpage) 문제가 대두되고 있다.

## 발명의 내용

### 해결하려는 과제

[0003] 본 발명이 해결하고자 하는 다른 과제는 흠 정도가 완화되는 패키지 온 패키지 장치를 제공하는데 있다.

[0004] 본 발명이 해결하고자 하는 과제는 흠 정도를 완화시키는 구조의 패키지 온 패키지 장치를 빠르고 간단하게 제조할 수 있는 패키지 온 패키지 장치의 제조 방법을 제공하는데 있다.

### 과제의 해결 수단

[0005] 상기 과제를 달성하기 위한 본 발명에 따른 패키지 온 패키지 장치는, 하부 패키지 기판, 및 상기 하부 패키지 기판 상에 실장된 하부 반도체 칩을 포함하는 하부 반도체 패키지; 상기 하부 패키지 상에 배치되는 상부 패키지 기판, 및 상기 상부 패키지 기판 상에 실장된 상부 반도체 칩을 포함하는 상부 반도체 패키지; 상기 하부 패키지 기판과 상기 상부 패키지 기판을 연결시키는 연결 솔더 범프; 및 상기 하부 반도체 패키지 및 상기 상부 반도체 패키지와 접하며 상기 연결 솔더 범프의 측면을 덮는 밀봉막을 포함한다.

[0006] 일 예에 있어서, 상기 밀봉막은 에폭시 수지를 포함하여 플렉스 기능을 가질 수 있다.

[0007] 상기 하부 반도체 패키지는 상기 하부 패키지 기판의 상부면과 상기 하부 반도체 칩의 측면을 덮으며 상기 연결 솔더 범프가 배치되는 연결홀(hole)을 포함하는 하부 몰딩막을 더 포함할 수 있으며, 상기 연결홀의 측벽은 상기 연결 솔더 범프의 측벽과 이격될 수 있으며, 상기 밀봉막은 상기 연결홀을 채울 수 있다.

[0008] 상기 연결홀의 측벽의 표면 거칠기는 상기 하부 몰딩막의 상부면의 표면 거칠기보다 클 수 있다.

[0009] 상기 하부 몰딩막의 상부면과 상기 밀봉막 사이에 박리 영역이 존재할 수 있다.

[0010] 상기 밀봉막은 연장되어 상기 하부 반도체 패키지와 상기 상부 반도체 패키지 사이를 채울 수 있다.

[0011] 상기 밀봉막은 상기 연결 솔더 범프의 측벽과 접하는 제 1 밀봉막; 및 상기 하부 반도체 칩과 상기 상부 패키지 기판 사이의 공간을 채우는 제 2 밀봉막을 포함할 수 있다. 이때 상기 제 2 밀봉막은 플렉스 기능을 갖지 않을 수 있다.

[0012] 상기 하부 반도체 칩은 상기 하부 패키지 기판 상에 플립 칩 본딩 방식으로 실장될 수 있다.

[0013] 상기 상부 반도체 패키지는 상기 하부 반도체 패키지와 다를 수 있다.

[0014] 상기 다른 과제를 달성하기 위한 본 발명에 따른 패키지 온 패키지 장치의 제조 방법은, 하부 패키지 기판, 상기 하부 패키지 기판 상에 배치된 하부 반도체 칩, 및 상기 하부 패키지 기판 상에 배치되며 상기 하부 반도체 칩과 이격된 하부 솔더 범프를 포함하는 하부 반도체 패키지를 제조하는 단계; 상부 패키지 기판, 상기 상부 패키지 기판 상에 배치된 상부 반도체 칩, 및 상기 상부 패키지 기판 하부에 배치되는 상부 솔더 범프를 포함하는 상부 반도체 패키지를 제조하는 단계; 상기 하부 솔더 범프 및 상기 상부 솔더 범프 중 적어도 하나를 밀봉막 수지 용액으로 도포하는 단계; 및 상기 하부 솔더 범프와 상기 상부 솔더 범프를 용착시켜 연결 솔더 범프를 형성하며 상기 연결 솔더 범프의 측벽을 덮으며 상기 상부 반도체 패키지 및 상기 하부 반도체 패키지와 접하는 밀봉막을 형성하는 단계를 포함한다.

[0015] 상기 하부 반도체 패키지는 상기 하부 패키지 기판의 상부면과 상기 하부 반도체 칩의 측면을 덮으며 상기 하부 솔더 범프를 노출시키는 연결홀(hole)을 포함하는 하부 몰딩막을 더 포함할 수 있다. 이때, 상기 연결 솔더 범프와 상기 밀봉막을 형성하는 단계는, 상기 연결홀 안에 상기 밀봉막 수지 용액을 넣는 단계; 상기 상부 솔더 범프가 상기 연결홀 안에 배치되도록 상기 상부 반도체 패키지를 상기 하부 반도체 패키지 상에 위치시키는 단계; 및 상기 상부 솔더 범프와 상기 하부 솔더 범프를 가열시키는 단계를 포함할 수 있다.

[0016] 상기 밀봉막 수지 용액으로 도포하는 단계는, 상기 상부 솔더 범프를 상기 밀봉막 수지 용액 안에 담그는 단계 및/또는 상기 하부 솔더 범프 상에 상기 밀봉막 수지 용액을 공급하는 단계를 포함할 수 있다.

[0017] 상기 밀봉막 수지 용액은 에폭시 수지를 포함하며 플렉스 기능을 가질 수 있다.

### 발명의 효과

[0018] 본 발명의 일 예에 따른 패키지 온 패키지 장치는, 상부 반도체 패키지와 하부 반도체 패키지 사이에 밀봉막이 존재하여 상부 반도체 패키지와 하부 반도체 패키지 간의 접촉 면적이 증가하며(또는 미접촉 영역이 줄어드므로) 휨 정도를 완화시킬 수 있다. 또한 상기 밀봉막에 의해 연결 솔더 범프, 상부 반도체 패키지와 하부 반도체 패키지를 습기나 외부 오염, 부식 등으로부터 보호할 수 있다.

[0019] 상기 밀봉막은 상기 연결 솔더 범프의 측벽을 감싸며, 상기 상부 반도체 패키지와 상기 하부 반도체 패키지와 동시에 접하므로, 상기 연결 솔더 범프에 금이 가거나 부러지는 크랙(crack)을 방지하고, 보호하는 역할을 한다. 즉, 상기 밀봉막에 의해 상기 상부 반도체 패키지와 상기 하부 반도체 패키지 사이의 연결 크랙(joint crack) 문제를 해결할 수 있다.

[0020] 하부 반도체 칩이 하부 패키지 기판 상에 플립 칩 본딩 방식으로 실장되므로, 전기적 패스(path) 길이가 짧아 신호 전달 속도를 빠르게 향상시킬 수 있다.

[0021] 본 발명의 다른 예에 따른 패키지 온 패키지 장치의 제조 방법은, 하부 솔더 범프 및 상부 솔더 범프 중 적어도 하나를 플렉스 기능이 있는 밀봉막 수지 용액으로 도포하고 가열함으로써, 간단하고 빠르게 연결 솔더 범프와 밀봉막을 형성할 수 있다.

### 도면의 간단한 설명

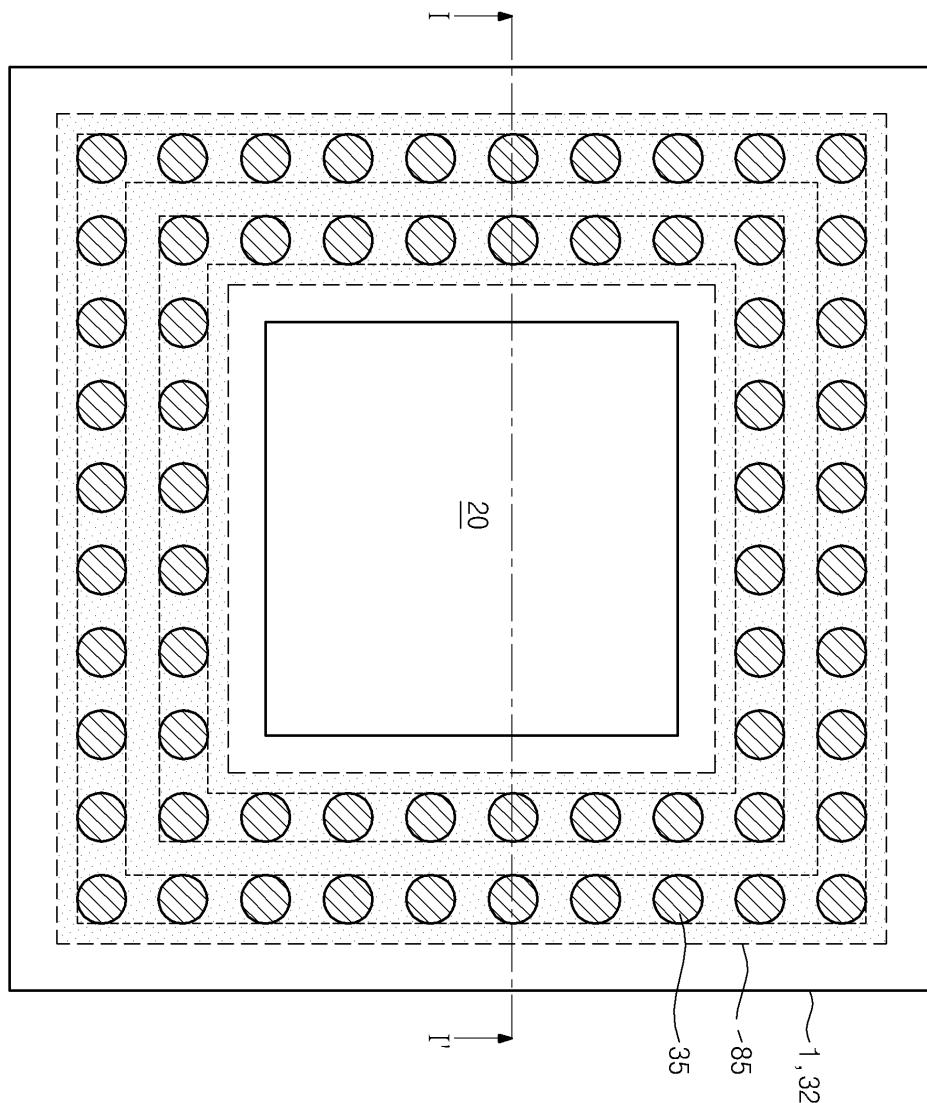

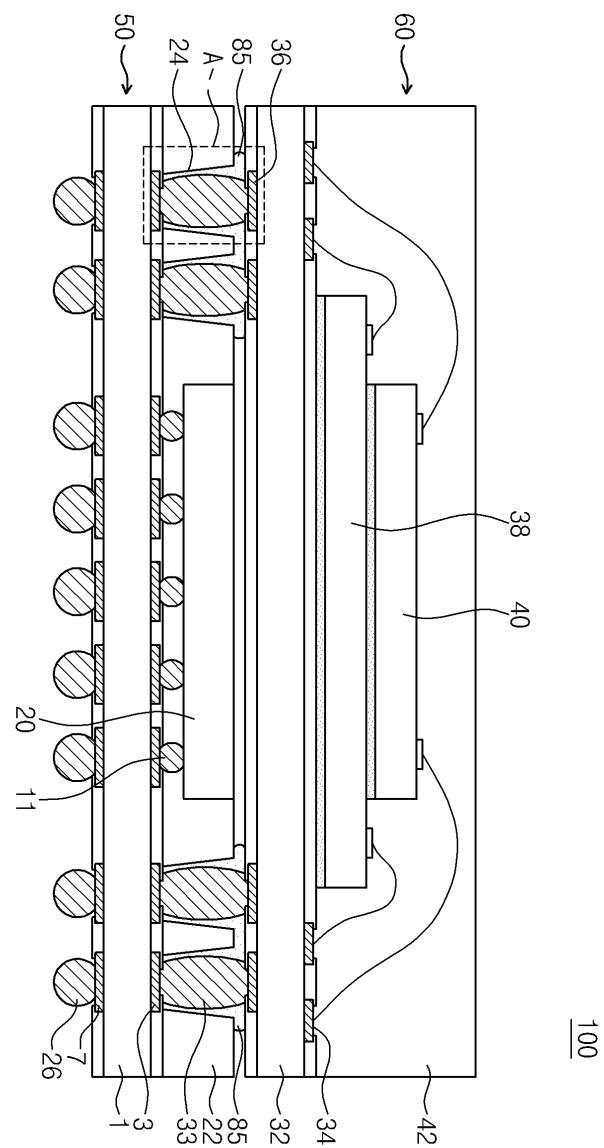

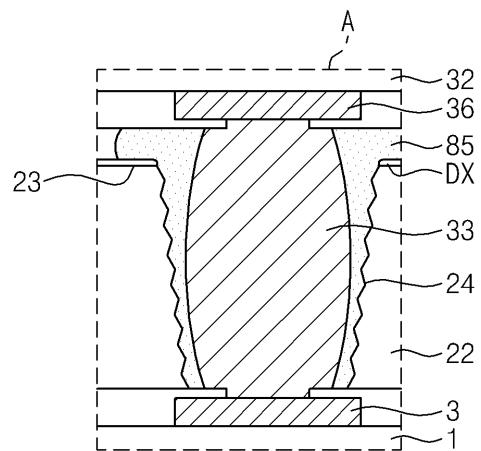

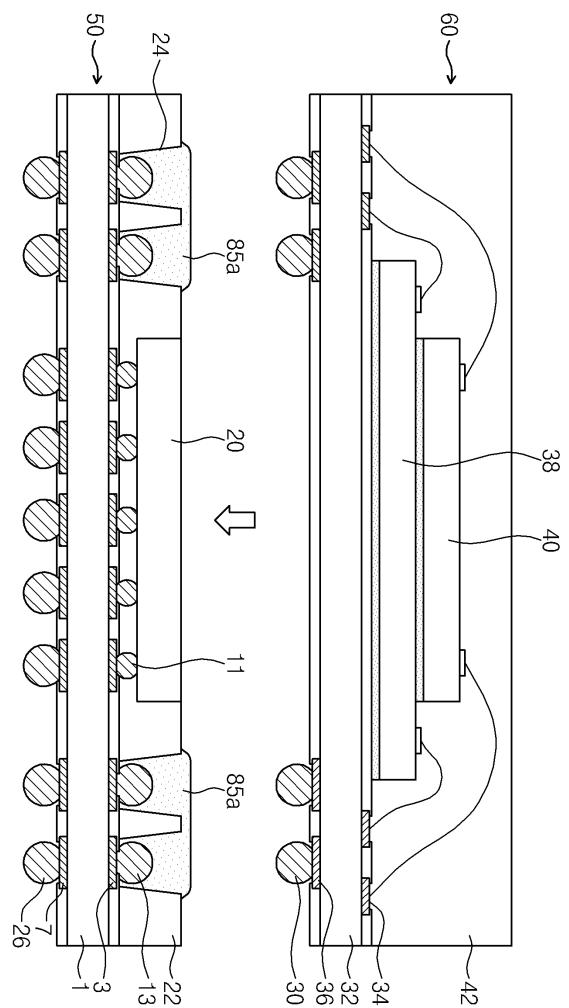

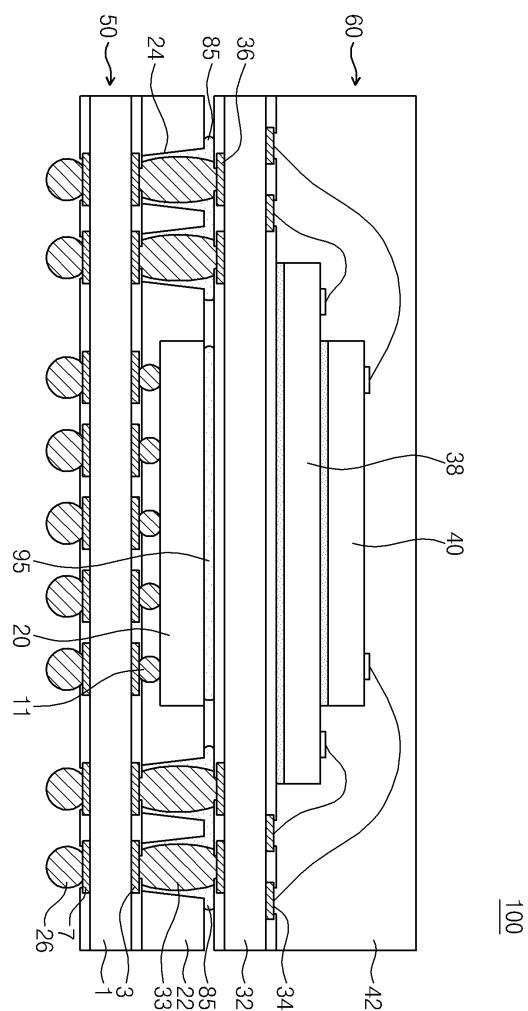

[0022] 도 1a는 본 발명의 일 예에 따른 패키지 온 패키지 장치의 평면도이다.

도 1b는 도 1a를 I-I'선으로 자른 것으로, 본 발명의 일 예에 따른 패키지 온 패키지 장치의 단면도이다.

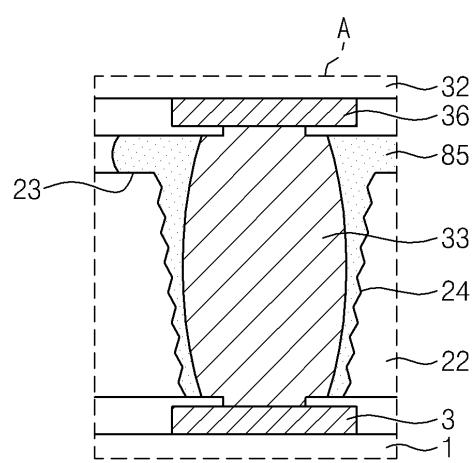

도 1c와 1d는 도 1a의 'A' 부분을 확대한 단면도들이다.

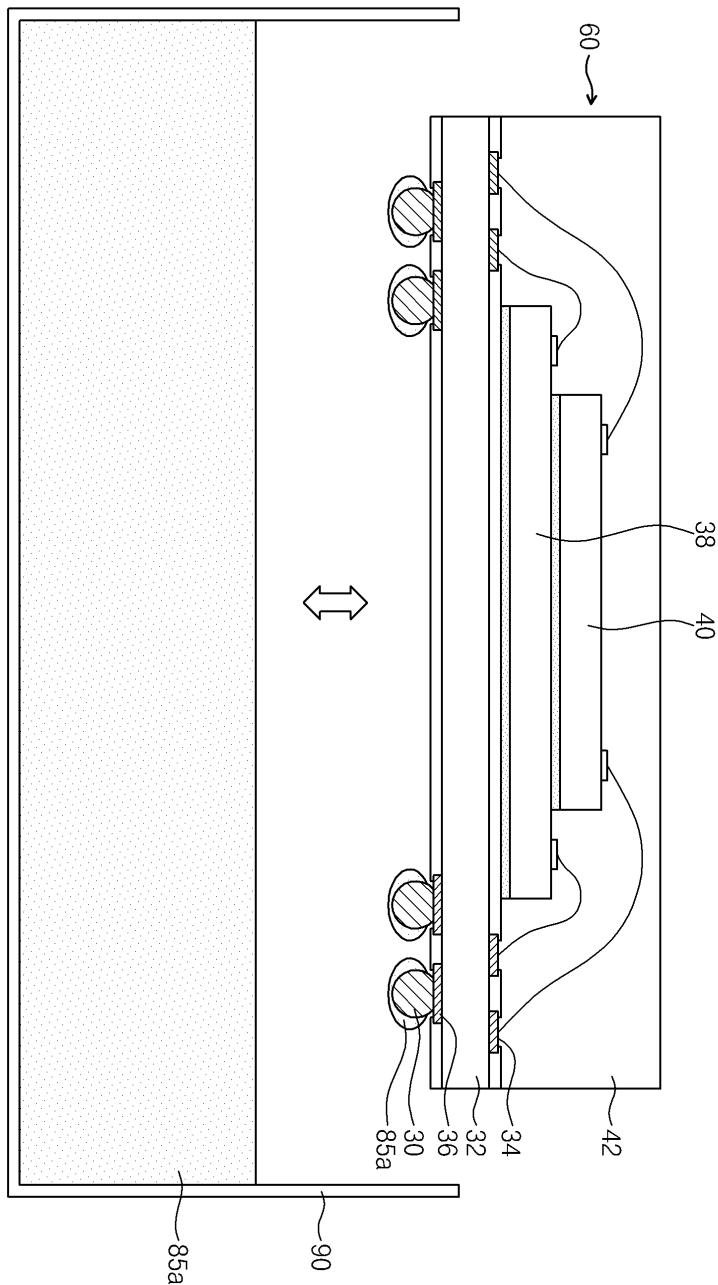

도 2 및 3은 본 발명의 일 예에 따라 도 1b의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도들이다.

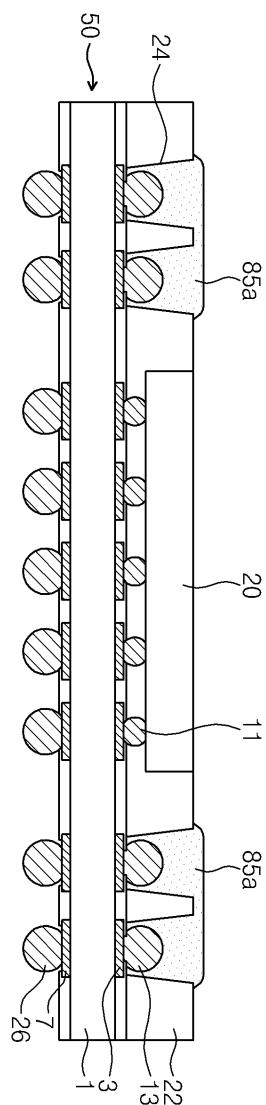

도 4 및 5는 본 발명의 다른 예에 따라 도 1b의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도들이다.

도 6은 본 발명의 또 다른 예에 따라 도 1b의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도이다.

도 7a, 7b 및 7c는 본 발명의 다른 예들에 따른 패키지 온 패키지 장치의 단면도들이다.

도 8은 본 발명의 일 예에 따라 도 7a의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도이다.

도 9는 본 발명의 다른 예에 따라 도 7a의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도이다.

도 10 내지 13은 본 발명의 또 다른 예들에 따른 패키지 온 패키지 장치의 단면도들이다.

도 14a는 본 발명의 또 다른 예에 따른 패키지 온 패키지 장치의 평면도이다.

도 14b는 도 14a를 I-I'선으로 자른 것으로, 본 발명의 또 다른 예에 따른 패키지 온 패키지 장치의 단면도이다.

도 15는 본 발명의 실시예들에 따른 반도체 패키지를 구비한 전자 장치를 도시한 사시도이다.

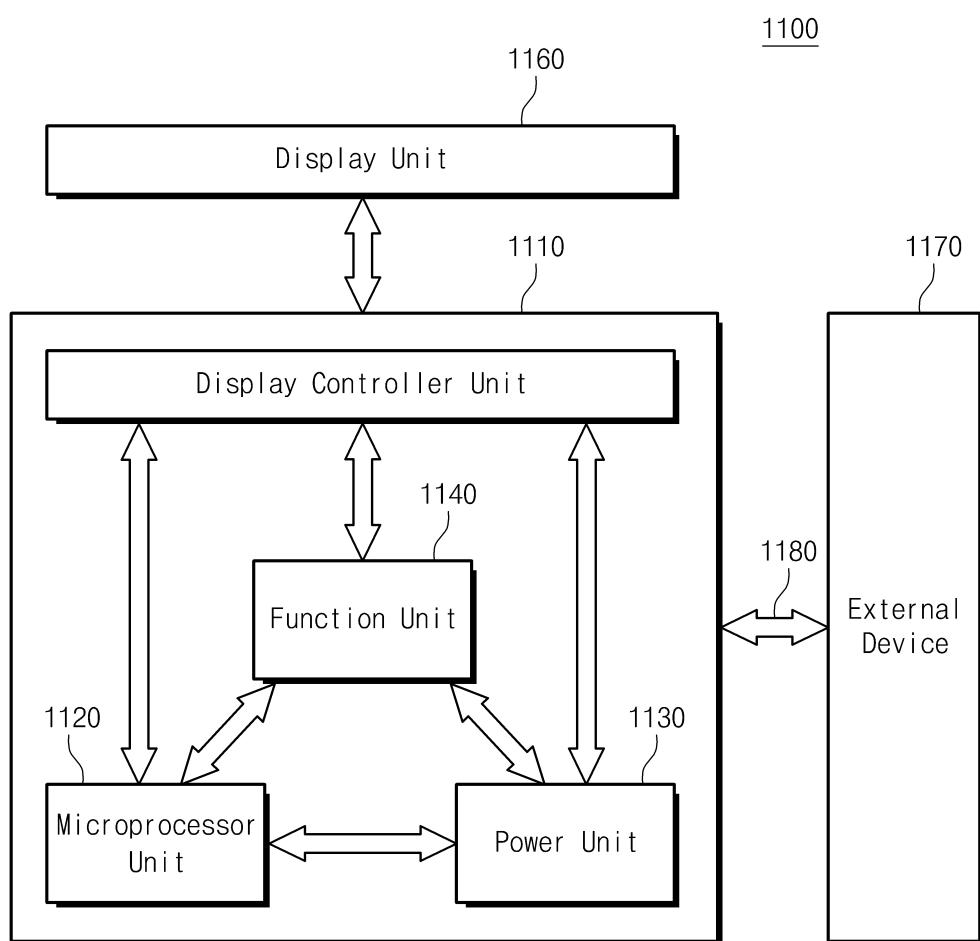

도 16은 본 발명의 일 예에 따른 반도체 패키지를 적용한 전자 장치의 시스템 블록도이다.

도 17은 본 발명의 기술이 적용된 반도체 패키지를 포함하는 전자 장치의 예를 보여주는 블럭도이다.

### 발명을 실시하기 위한 구체적인 내용

[0023] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 침부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 본 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

- [0024] 소자(elements) 또는 층이 다른 소자 또는 층의 "위(on)" 또는 "상(on)"으로 지칭되는 것은 다른 소자 또는 층의 바로 위뿐만 아니라 중간에 다른 층 또는 다른 소자를 개재한 경우를 모두 포함한다. 반면, 소자가 "직접 위(directly on)" 또는 "바로 위"로 지칭되는 것은 중간에 다른 소자 또는 층을 개재하지 않은 것을 나타낸다. "및/또는"은 언급된 아이템들의 각각 및 하나 이상의 모든 조합을 포함한다.

- [0025] 공간적으로 상대적인 용어인 "아래(below)", "아래(beneath)", "하부(lower)", "위(above)", "상부(upper)" 등은 도면에 도시되어 있는 바와 같이 하나의 소자 또는 구성 요소들과 다른 소자 또는 구성 요소들과의 상관관계를 용이하게 기술하기 위해 사용될 수 있다. 공간적으로 상대적인 용어는 도면에 도시되어 있는 방향에 더하여 사용시 또는 동작 시 소자의 서로 다른 방향을 포함하는 용어로 이해되어야 한다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

- [0026] 비록 제1, 제2 등이 다양한 소자, 구성요소 및/또는 섹션들을 서술하기 위해서 사용되나, 이들 소자, 구성요소 및/또는 섹션들은 이들 용어에 의해 제한되지 않음은 물론이다. 이들 용어들은 단지 하나의 소자, 구성요소 또는 섹션들을 다른 소자, 구성요소 또는 섹션들과 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 소자, 제1 구성요소 또는 제1 섹션은 본 발명의 기술적 사상 내에서 제2 소자, 제2 구성요소 또는 제2 섹션일 수도 있음을 물론이다.

- [0027] 본 명세서에서 기술하는 실시예들은 본 발명의 이상적인 개략도인 평면도 및 단면도를 참고하여 설명될 것이다. 따라서, 제조 기술 및/또는 허용 오차 등에 의해 예시도의 형태가 변형될 수 있다. 따라서, 본 발명의 실시예들은 도시된 특정 형태로 제한되는 것이 아니라 제조 공정에 따라 생성되는 형태의 변화도 포함하는 것이다. 따라서, 도면에서 예시된 영역들은 개략적인 속성을 가지며, 도면에서 예시된 영역들의 모양은 소자의 영역의 특정 형태를 예시하기 위한 것이고, 발명의 범주를 제한하기 위한 것은 아니다.

- [0028] 이하, 본 발명을 보다 구체적으로 설명하기 위하여 본 발명에 따른 실시예들을 첨부 도면을 참조하면서 보다 상세하게 설명하고자 한다.

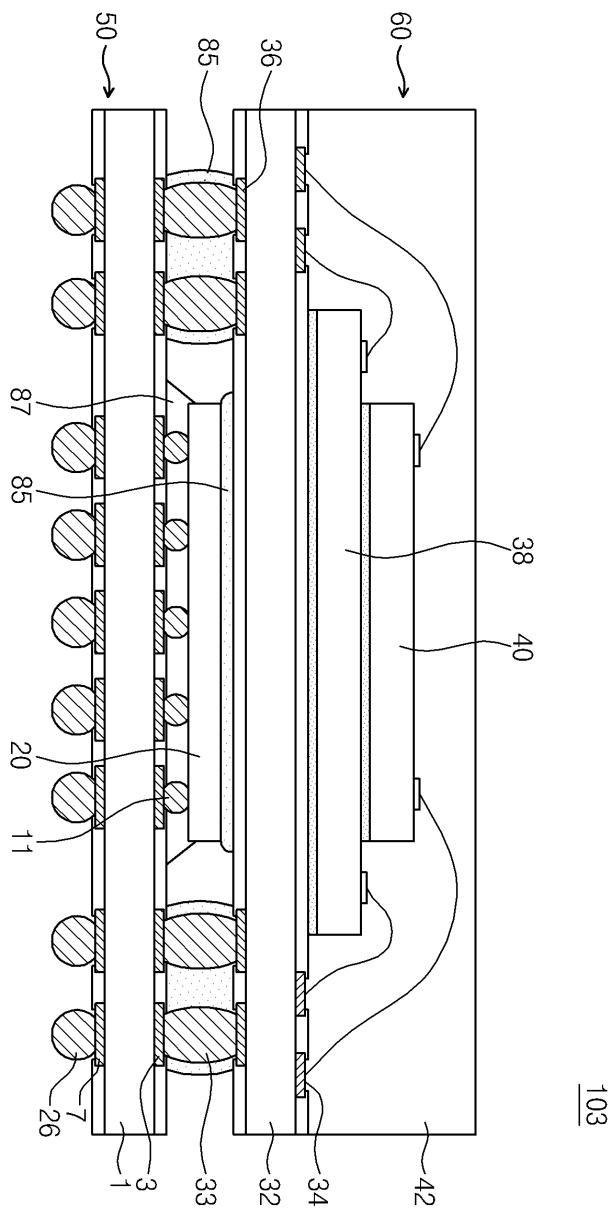

- [0029] 도 1a는 본 발명의 일 예에 따른 패키지 온 패키지 장치의 평면도이다. 도 1b는 도 1a를 I-I' 선으로 자른 것으로, 본 발명의 일 예에 따른 패키지 온 패키지 장치의 단면도이다. 도 1c와 1d는 도 1a의 'A' 부분을 확대한 단면도들이다.

- [0030] 도 1a 및 1b를 참조하면, 본 예에 따른 패키지 온 패키지 장치(100)는, 하부 반도체 패키지(50)와 상부 반도체 패키지(60)을 포함한다.

- [0031] 상기 하부 반도체 패키지(50)는 하부 패키지 기판(1), 상기 하부 패키지 기판(1) 상에 실장된 하부 반도체 칩(20), 및 이들을 덮는 하부 몰딩막(22)을 포함한다. 상기 하부 패키지 기판(1) 상하에는 각각 제 1 하부 패드들(3)과 제 2 하부 패드들(7)이 배치된다. 상기 제 1 및 제 2 하부 패드들(3,7)은 절연막들로 덮일 수 있다. 상기 하부 반도체 칩(20)은 상기 제 1 하부 패드들(3)에 제 1 하부 솔더 범프들(11)을 이용하여 전기적으로 연결되며, 플립 칩 본딩 방식으로 실장될 수 있다. 상기 제 2 하부 패드들(7)에는 제 2 하부 솔더 범프들(26)이 배치된다. 상기 하부 몰딩막(22)은 상기 하부 반도체 칩(20)의 측벽을 덮되 상기 하부 반도체 칩(20)의 상부면은 노출시킬 수 있다. 즉, 상기 하부 반도체 칩(20)의 상부면은 상기 하부 몰딩막(22)에 의해 덮이지 않을 수 있다. 상기 하부 몰딩막(22)은 상기 하부 반도체 칩(20)과 이격되는 연결홀(24)을 포함한다.

- [0032] 상기 상부 반도체 패키지(60)는 상부 패키지 기판(32), 상기 상부 패키지 기판(32) 상에 실장된 상부 반도체 칩들(38, 40), 및 이들을 덮는 상부 몰딩막(42)을 포함한다. 상기 상부 반도체 칩들(38, 40)은 상기 상부 패키지 기판(32) 상에 와이어 본딩 방식으로 실장될 수 있다. 상기 상부 패키지 기판(32) 상하에는 각각 제 1 상부 패드들(34)과 제 2 상부 패드들(36)이 배치된다. 상기 상부 및 하부 몰딩막들(42, 22)은 수지막과, 상기 수지막에 분산된 복수 개의 필러 입자(filler particle)들을 포함할 수 있다. 상기 수지막은 적어도 하나의 고분자 물질을 포함할 수 있다. 상기 필러 입자는 실리카나 알루미나 같은 물질을 포함할 수 있다.

- [0033] 상기 상부 반도체 패키지(60)는 상기 하부 반도체 패키지(50) 상에 적층되며, 이들을 연결하는 연결 솔더 범프(33)에 의해 서로 전기적으로 연결된다. 상기 연결 솔더 범프(33)는 제 2 상부 패드(36) 및 제 1 하부 패드(3)와 접한다. 도 1c 및 1d를 참조하면, 상기 연결 솔더 범프(33)는 상기 연결홀(24) 안에 배치된다. 상기 연결 솔더 범프(33)의 측벽과 상기 연결홀(24)의 내측벽은 서로 이격될 수 있다. 상기 연결 솔더 범프(33)의 측벽과 상기 연결홀(24)의 내측벽 사이의 공간은 밀봉막(85)으로 채워질 수 있다. 상기 밀봉막(85)은 연장되어 상기 상부 반도체 패키지(60)의 하부면과 상기 하부 반도체 패키지(50)의 상부면과 동시에 접한다. 상기 연결홀(24)의 측벽의 표면 거칠기는 상기 하부 몰딩막(22)의 표면 거칠기보다 클 수 있다. 상기 연결홀(24)의 측

벽의 표면 거칠기가 커져 표면적이 증가되므로, 상기 연결홀(24)의 측벽과 상기 밀봉막(85)과의 접착력은 증가될 수 있다. 도 1c에서처럼, 상기 밀봉막(85)은 상기 하부 몰딩막(22)의 상부면(23)과 접할 수 있다. 또는 도 1d에서처럼, 상기 밀봉막(85)과 상기 하부 몰딩막(22)의 상부면(23) 사이에 박리 영역(DX)이 존재할 수 있다.

[0034] 상기 밀봉막(85)은 예폭시 수지를 포함한다. 상기 예폭시 수지는 예를 들면 비스페놀 F형 예폭시 수지일 수 있다. 더 나아가, 상기 밀봉막(85)은 플렉스 기능을 가질 수 있다. 상기 밀봉막(85)이 플렉스 기능을 갖기 위해, 상기 예폭시 수지가 플렉스 기능을 가질 수 있다. 또는 상기 밀봉막(85)이 포함하는 다른 성분이 플렉스 기능을 가질 수 있다. 예를 들면, 상기 밀봉막(85)은 상기 예폭시 수지를 경화시키기 위한 경화제를 더 포함할 수 있으며, 이 경화제가 플렉스 기능을 가질 수 있다. 예를 들면 플렉스 기능을 가지는 경화제로 페놀 수지, 페놀계 카본산, 산무수물, 카본산, 방향족 히드라지드 등의 물질이 사용될 수 있다. 또는 상기 밀봉막(85)은 플렉스 기능을 가지는 별도의 플렉스 성분을 더 포함할 수 있다. 상기 플렉스 성분으로 카본산, 유황 함유 페놀 화합물, 로진, 로진의 유도체 및 합성 수지 등의 물질이 사용될 수 있다. 상기 밀봉막(85)은 실리카와 같은 무기질 충전제를 더 포함할 수 있다.

[0035] 상기 밀봉막(85)은 상기 연결 솔더 범프(33)의 측벽을 감싸며, 상기 상부 반도체 패키지(60)과 상기 하부 반도체 패키지(50)와 동시에 접하므로, 상기 연결 솔더 범프(33)에 금이 가거나 부러지는 크랙(crack)을 방지하고, 보호하는 역할을 한다. 즉, 상기 밀봉막(85)에 의해 상기 상부 반도체 패키지(60)과 상기 하부 반도체 패키지(50) 사이의 연결 크랙(joint crack) 문제를 해결할 수 있다.

[0036] 또한, 상기 밀봉막(85)에 의해 상기 상부 반도체 패키지(60)와 상기 하부 반도체 패키지(50) 간의 접촉 면적이 증가하며(또는 미접촉 영역이 줄어드므로) 전체 패키지 온 패키지 장치(100)의 휨 정도를 완화시킬 수 있다. 또한 상기 밀봉막(85)에 의해 상기 연결 솔더 범프(33), 상부 반도체 패키지(60)와 하부 반도체 패키지(50)를 습기나 외부 오염, 부식 등으로부터 보호할 수 있다.

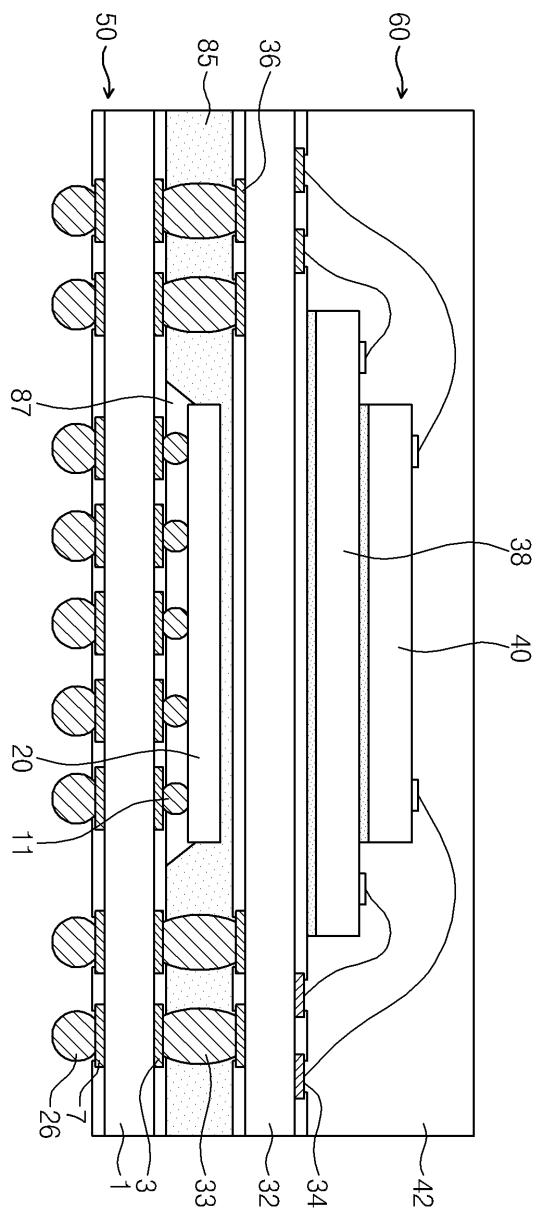

[0037] 도 2 및 3은 본 발명의 일 예에 따라 도 1b의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도들이다.

[0038] 도 2를 참조하면, 밀봉막 수지 용액(85a)이 담긴 용기(90)를 준비한다. 상기 밀봉막 수지 용액(85a)은 예폭시 수지를 포함할 수 있으며 플렉스 기능을 가질 수 있다. 상기 예폭시 수지는 예를 들면 비스페놀 F형 예폭시 수지일 수 있다. 상기 밀봉막 수지 용액(85a)이 플렉스 기능을 갖기 위해, 상기 예폭시 수지가 플렉스 기능을 가질 수 있다. 또는 상기 밀봉막 수지 용액(85a)이 포함하는 다른 성분이 플렉스 기능을 가질 수 있다. 예를 들면, 상기 밀봉막 수지 용액(85a)은 상기 예폭시 수지를 경화시키기 위한 경화제를 더 포함할 수 있으며, 이 경화제가 플렉스 기능을 가질 수 있다. 예를 들면 플렉스 기능을 가지는 경화제로 페놀 수지, 페놀계 카본산, 산무수물, 카본산, 방향족 히드라지드 등의 물질이 사용될 수 있다. 또는 상기 밀봉막 수지 용액(85a)은 플렉스 기능을 가지는 별도의 플렉스 성분을 더 포함할 수 있다. 상기 플렉스 성분으로 카본산, 유황 함유 페놀 화합물, 로진, 로진의 유도체 및 합성 수지 등의 물질이 사용될 수 있다. 상기 밀봉막 수지 용액(85a)은 실리카와 같은 무기질 충전제를 더 포함할 수 있다. 상기 밀봉막 수지 용액(85a)은 상기 예폭시 수지, 경화제 및/또는 플렉스 성분들을 용해/분산시키기 위한 용매를 더 포함할 수 있다.

[0039] 상기 용기(90) 상에 상부 반도체 패키지(60)를 위치시킨다. 상기 상부 반도체 패키지(60)는 상부 패키지 기판(32), 상기 상부 패키지 기판(32) 상에 실장된 상부 반도체 칩들(38, 40), 이들을 덮는 상부 몰딩막(42), 제 1 상부 패드들(34) 및 제 2 상부 패드들(36)을 포함한다. 상기 제 2 상부 패드들(36)에는 상부 솔더 범프(30)가 부착된다. 상기 상부 반도체 패키지(60)를 하강시켜 상기 밀봉막 수지 용액(85a)을 상기 상부 솔더 범프(30)의 표면에만 묻힌다.

[0040] 도 3을 참조하면, 상기 상부 반도체 패키지(60)를 하부 반도체 패키지(50) 상에 위치시킨다. 상기 하부 반도체 패키지(50)는 하부 패키지 기판(1), 상기 하부 패키지 기판(1) 상에 실장된 하부 반도체 칩(20), 및 이들을 덮는 하부 몰딩막(22), 제 1 하부 패드들(3), 제 2 하부 패드들(7), 제 1 하부 솔더 범프들(11) 및 제 2 솔더 범프들(26)을 포함한다. 또한 상기 하부 반도체 패키지(50)는 상기 제 1 하부 솔더 범프들(11)과 이격된 제 1 하부 패드들(3) 상에 배치되는 제 3 하부 솔더 범프(13)를 더 포함한다. 상기 제 3 하부 솔더 범프(13)는 상기 연결홀(24)에 의해 노출된다. 상기 연결홀(24)은 상기 하부 몰딩막(22)을 레이저로 구멍을 뚫음으로써 형성될 수 있다. 따라서 상기 연결홀(24)의 표면 거칠기는 도 1c 및 1d에서처럼, 상기 하부 몰딩막(22)의 상부면(23)의 표면 거칠기보다 클 수 있다. 상기 상부 반도체 패키지(60)를 하부 반도체 패키지(50) 상에 위치시킬 때, 상기 밀봉막 수지 용액(85a)이 묻은 상기 상부 솔더 범프(30)가 상기 연결홀(24) 안에 들어가 상기 제 3 하부 솔더 범프(13)와 만나도록 한다. 상기 연결홀(24)은 상기 밀봉막 수지 용액(85a)이 외부로 흘러가지 않도록

가두는 컨테이너 역할을 할 수 있으며 또한 상기 상부 반도체 패키지(60)의 위치를 고정시키는 역할을 할 수 있다.

[0041] 그리고 다시 도 1a 내지 1c를 참조하여, 상기 상부 솔더 범프(30)와 상기 제 3 하부 솔더 범프(13)의 융점 이상으로 상기 상부 솔더 범프(30)와 상기 제 3 하부 솔더 범프(13)를 가열시킨다. 이때 상기 연결홀(24) 안의 상기 밀봉막 수지 용액(85a)에 포함된 플럭스 성분 또는 상기 밀봉막 수지 용액(85a)의 플럭스 기능에 의해 상기 상부 솔더 범프(30)와 상기 제 3 하부 솔더 범프(13) 표면의 산화막을 제거하고 솔더링에 대한 표면 장력을 감소시킨다. 이로써, 상기 상부 솔더 범프(30)와 상기 제 3 하부 솔더 범프(13)가 도 1b에서처럼 융착되어 연결 솔더 범프(33)를 형성할 수 있다. 이 과정에서 상기 밀봉막 수지 용액(85a)에 포함된 에폭시 수지는 경화될 수 있으며 용매는 제거될 수 있다. 이로써 상기 밀봉막 수지 용액(85a)은 밀봉막(85)이 될 수 있다.

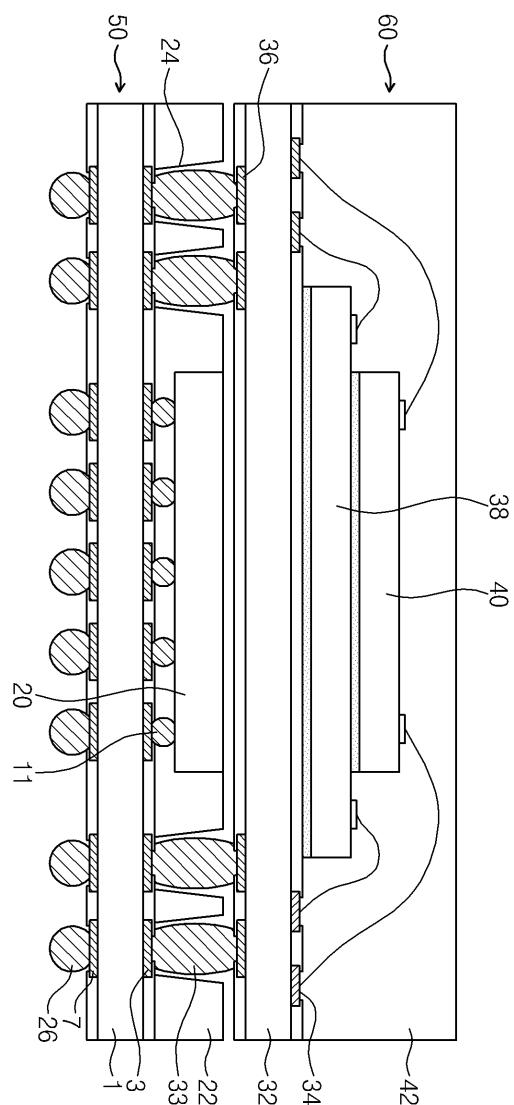

[0042] 도 4 및 5는 본 발명의 다른 예에 따라 도 1b의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도들이다.

[0043] 도 4를 참조하면, 하부 반도체 패키지(50) 상에 밀봉막 수지 용액(85a)을 도포한다. 이때 상기 밀봉막 수지 용액(85a)은 상기 연결홀(24) 안에 배치되도록 선택적으로 도포될 수 있다. 상기 연결홀(24)은 상기 밀봉막 수지 용액(85a)이 외부로 흘러가지 않도록 가두는 컨테이너 역할을 할 수 있다.

[0044] 도 5를 참조하면, 상부 반도체 패키지(60)를 상기 하부 반도체 패키지(50) 상에 위치시켜, 상기 상부 솔더 범프(30)가 상기 밀봉막 수지 용액(85a)이 들어있는 상기 연결홀(24) 안에 들어가 상기 제 3 하부 솔더 범프(13)와 만나도록 한다.

[0045] 그리고 위에서 설명한 바와 같이 가열 공정을 진행하여 연결 솔더 범프(33)와 밀봉막(85)을 형성한다.

[0046] 도 3 또는 도 5를 참조하여 설명한 패키지 온 패키지 장치의 제조 방법은, 제 3 하부 솔더 범프(13) 및 상부 솔더 범프(30) 중 적어도 하나를 플럭스 기능이 있는 밀봉막 수지 용액(85a)으로 도포하고 가열함으로써, 간단하고 빠르게 연결 솔더 범프(33)와 밀봉막(85)을 형성할 수 있다.

[0047] 또는, 도 1b의 패키지 온 패키지 장치를 제조하는 과정은 이와는 다를 수도 있다. 도 6은 본 발명의 또 다른 예에 따라 도 1b의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도이다.

[0048] 도 6을 참조하면, 상부 반도체 패키지(60)를 상기 하부 반도체 패키지(50) 상에 위치시키고, 에폭시 수지 없이 플럭스 기능만을 가지는 용액으로 도포시키고 가열하여 연결 솔더 범프(33)를 먼저 형성한다. 그 후에 에폭시 수지를 포함하는 밀봉막 수지 용액을 상기 상부 반도체 패키지(60)와 상기 하부 반도체 패키지(50) 사이에 주입한 후 경화시킴으로써 도 1a의 밀봉막(85)을 형성할 수도 있다.

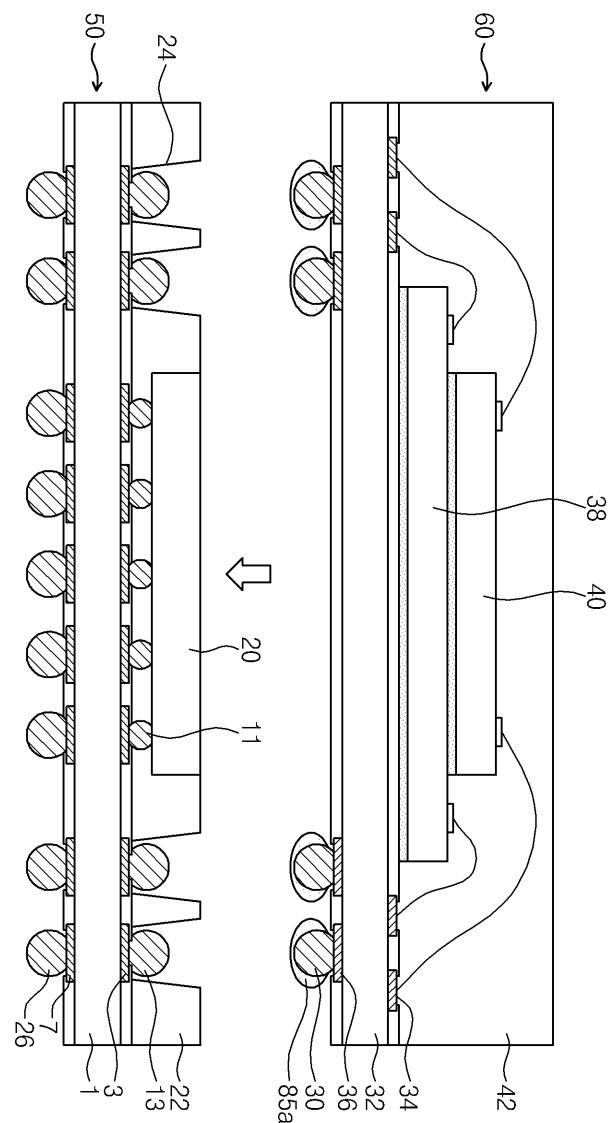

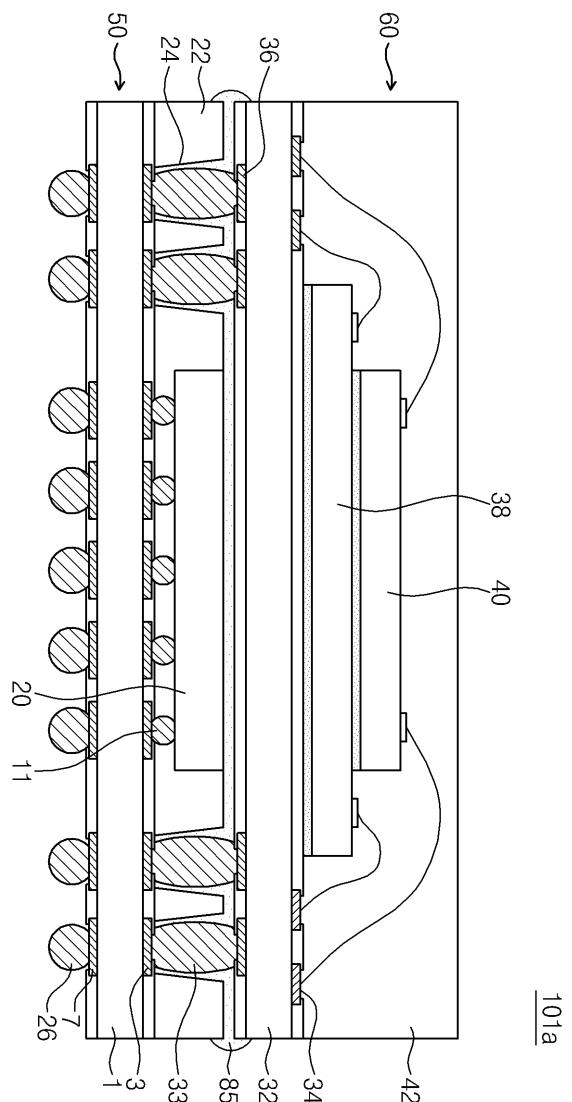

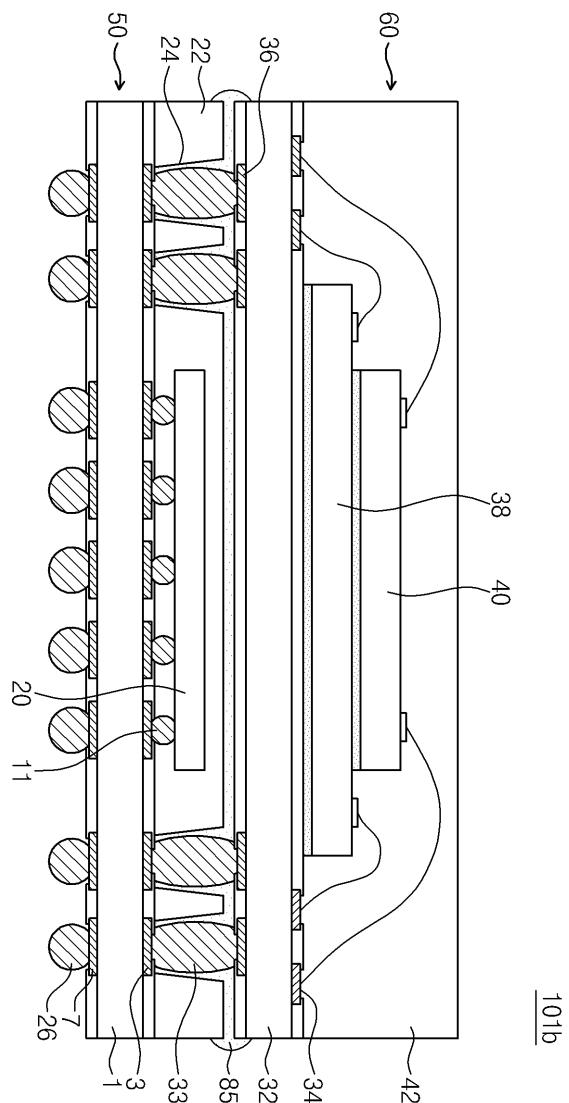

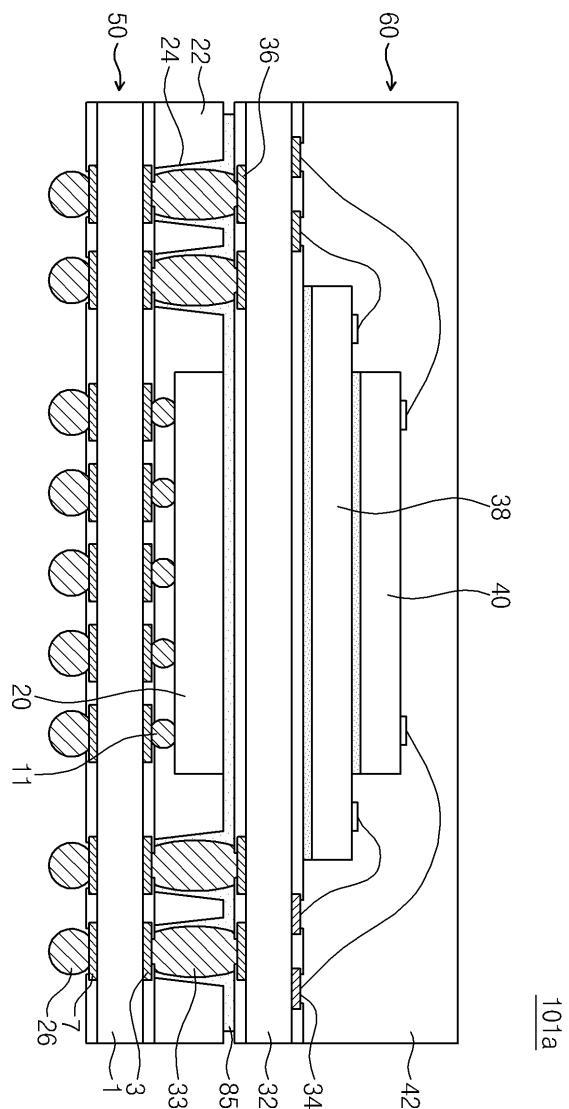

[0049] 도 7a, 7b 및 7c는 본 발명의 다른 예들에 따른 패키지 온 패키지 장치의 단면도들이다.

[0050] 도 7a를 참조하면, 본 예에 따른 패키지 온 패키지 장치(101a)는 도 1a의 밀봉막(85)이 연장되어 상부 반도체 패키지(60)와 하부 반도체 패키지(50) 사이의 공간을 모두 채울 수 있다. 상기 밀봉막(85)은 연장되어 상기 상부 반도체 패키지(60)와 하부 반도체 패키지(50) 사이 공간의 밖으로 돌출되어, 상기 하부 몰딩막(22)의 측벽과 상기 상부 패키지 기판(32)의 측벽을 덮을 수 있다. 그외의 구성은 도 1b와 같다. 이때, 상기 밀봉막(85)이 하부 반도체 칩(20)의 상부면과 접할 수 있다. 이때의 상기 패키지 온 패키지 장치(101a)의 휨 정도는 보다 완화될 수 있다.

[0051] 도 7b를 참조하면, 본 예에 따른 패키지 온 패키지 장치(101b)에서 하부 몰딩막(22)이 하부 반도체 칩(20)의 상부면을 덮을 수 있다. 그외의 구성은 도 7a와 같다. 이때, 상기 밀봉막(85)이 하부 몰딩막(22)의 상부면과 접할 수 있다.

[0052] 도 7c를 참조하면, 본 예에 따른 패키지 온 패키지 장치(101c)는 도 7a와 유사하나, 상기 밀봉막(85)이 상기 상부 반도체 패키지(60)와 하부 반도체 패키지(50) 사이 공간의 밖으로 돌출되지 않는다. 그 외의 구성은 도 7a와 같다.

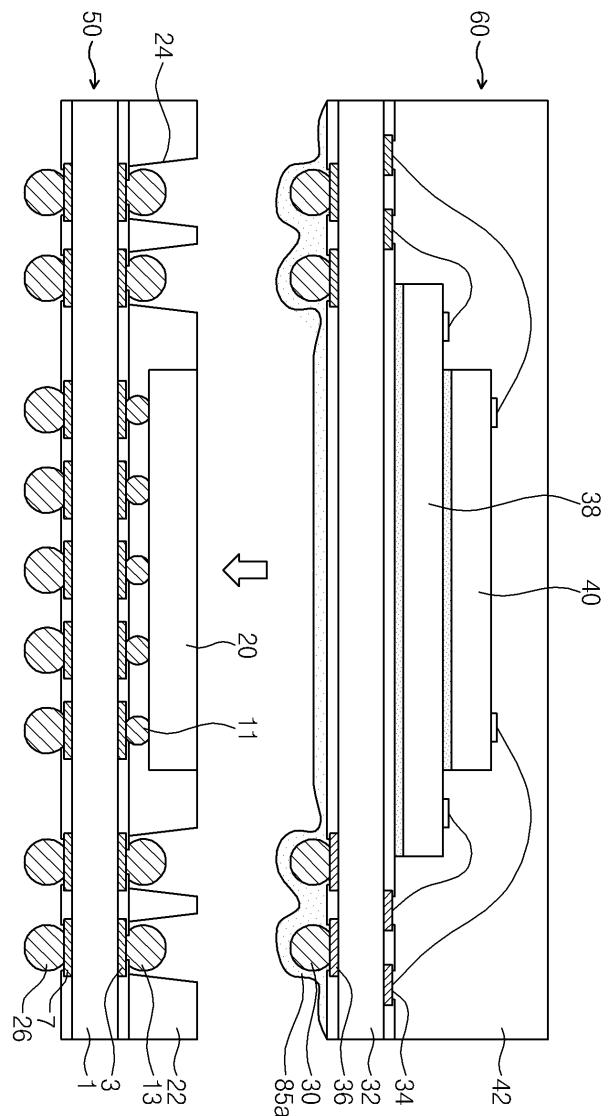

[0053] 도 8은 본 발명의 일 예에 따라 도 7a의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도이다.

[0054] 도 8을 참조하면, 도 2에서처럼, 상부 반도체 패키지(60)의 하부를 밀봉막 수지 용액(85a)에 담그나, 이때 상기 밀봉막 수지 용액(85a)이 상기 상부 반도체 패키지(60)의 하부면을 모두 도포하도록 한다. 그리고 상기 상부 반도체 패키지(60)를 하부 반도체 패키지(50) 상에 위치시키고 가열하여 도 7a의 패키지 온 패키지 장치(101a)를 형성할 수 있다.

[0055] 도 9는 본 발명의 다른 예에 따라 도 7a의 패키지 온 패키지 장치를 제조하는 과정을 나타내는 단면도이다.

[0056] 도 9를 참조하면, 하부 반도체 패키지(50)의 전면 상에 밀봉막 수지 용액(85a)을 도포한다. 그리고 상부 반도체 패키지(60)를 상기 하부 반도체 패키지(50) 상에 위치시키고 가열하여 도 7a의 패키지 온 패키지 장치(101a)를 형성할 수 있다.

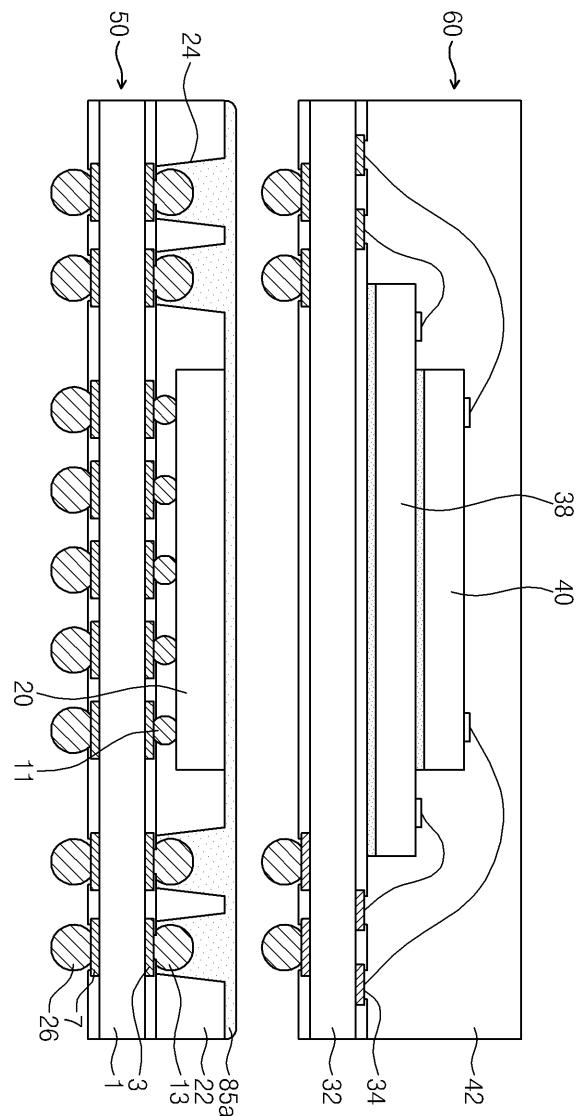

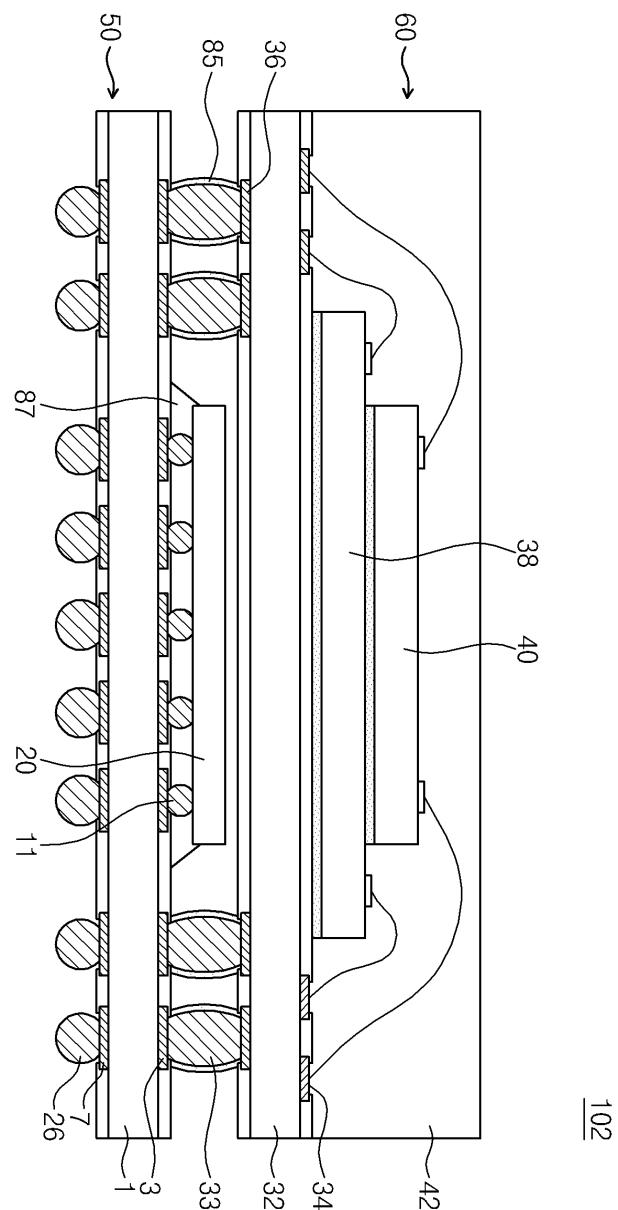

[0057] 도 10 내지 13은 본 발명의 또 다른 예들에 따른 패키지 온 패키지 장치의 단면도들이다.

[0058] 도 10을 참조하면, 본 예에 따른 패키지 온 패키지 장치(102)에서 하부 반도체 패키지(50)는 하부 몰딩막(22)을 포함하지 않을 수 있다. 연결 솔더 범프(33)의 측면은 밀봉막(85)으로 덮일 수 있다. 또한 상기 밀봉막(85)은 연장되어 상기 하부 반도체 패키지(50)와 상부 반도체 패키지(60)과 동시에 접할 수 있다. 이때 하부 반도체 칩(20)과 하부 패키지 기판(1) 사이는 언더필 수지막(87)으로 채워질 수 있다. 상기 언더필 수지막(87)은 상기 밀봉막(85)과 동일/유사할 수 있다. 그 외의 구성은 도 1a와 동일/유사할 수 있다. 도 10의 패키지 온 패키지 장치(102)의 제조 과정은 도 3과 유사할 수 있다.

[0059] 도 11을 참조하면, 본 예에 따른 패키지 온 패키지 장치(103)에서 밀봉막(85)은 이웃하는 두개의 연결 솔더 범프들(33)의 측면을 덮으며 이들 사이의 공간을 채울 수 있다. 또한 상기 밀봉막(85)은 하부 반도체 칩(20)과 상부 패키지 기판(32) 사이에도 개재될 수 있다. 그 외의 구성은 도 10과 동일/유사할 수 있다. 도 11의 패키지 온 패키지 장치(103)의 제조 과정은 도 5와 유사할 수 있다.

[0060] 도 12를 참조하면, 본 예에 따른 패키지 온 패키지 장치(104)에서 하부 반도체 패키지(50)과 상부 반도체 패키지(60) 사이의 공간은 모두 밀봉막(85)으로 채워질 수 있다. 그 외의 구성은 도 11과 동일/유사할 수 있다. 도 12의 패키지 온 패키지 장치(104)의 제조 과정은 도 5와 유사할 수 있다.

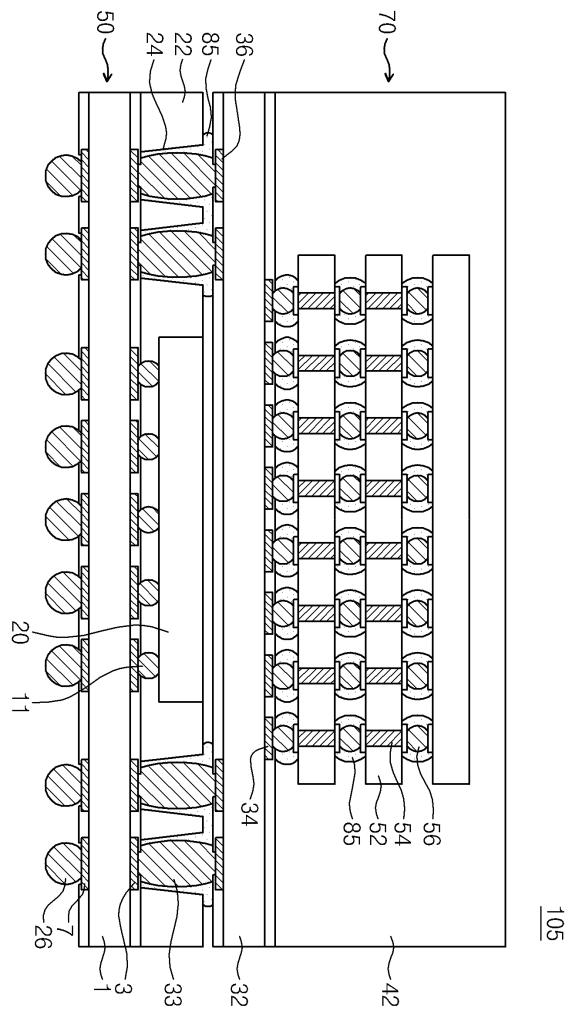

[0061] 도 13을 참조하면, 본 예에 따른 패키지 온 패키지 장치(105)는 하부 반도체 패키지(50)와 상부 반도체 패키지(70)을 포함한다. 상기 상부 반도체 패키지(70)는 상부 패키지 기판(32) 및 복수개의 상부 반도체 칩들(52)을 포함할 수 있다. 상기 상부 패키지 기판(32) 상에 복수개의 상부 반도체 칩들(52)이, 상부 내부 솔더 범프들(56)을 이용하여 플립 칩 본딩 방식으로 적층되어 실장될 수 있다. 상기 상부 반도체 칩들(52)은 상기 상부 내부 솔더 범프(56)와 중첩되며 내재되는 관통 비아(54)를 포함할 수 있다. 상기 상부 내부 솔더 범프들(56)의 측면도 밀봉막(85)으로 덮일 수 있다. 그 외의 구조는 도 1a와 동일/유사할 수 있다.

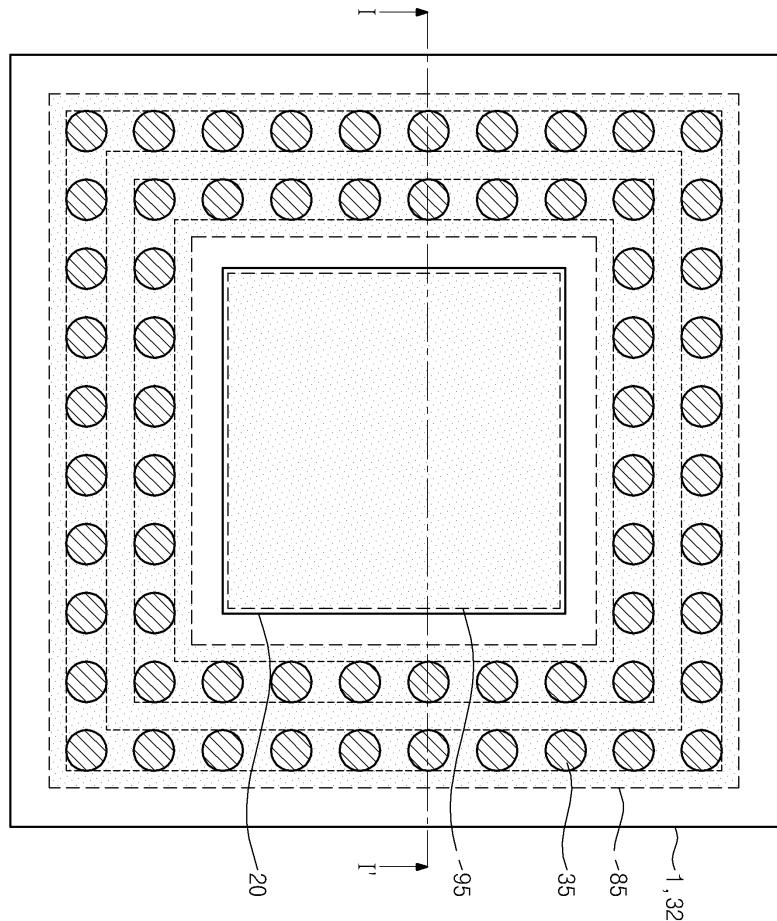

[0062] 도 14a는 본 발명의 또 다른 예에 따른 패키지 온 패키지 장치의 평면도이다. 도 14b는 도 14a를 I-I' 선으로 자른 것으로, 본 발명의 또 다른 예에 따른 패키지 온 패키지 장치의 단면도이다.

[0063] 도 14a 및 14b를 참조하면, 본 예에 따른 패키지 온 패키지 장치(106)는 연결 솔더 범프(33)의 측벽을 덮는 제1 밀봉막(85)과 하부 반도체 칩(20)과 상부 패키지 기판(32) 사이의 공간을 채우는 제2 밀봉막(95)을 포함할 수 있다. 상기 제1 밀봉막(85)은 도 1b를 참조한 바와 같을 수 있다. 상기 제2 밀봉막(95)은 에폭시 수지를 포함하되, 플렉스 기능은 포함하지 않을 수 있다. 상기 제2 밀봉막(95)이 플렉스 기능을 포함하지 않음으로써, 상기 제2 밀봉막(95)과 상기 하부 반도체 칩(20) 사이 그리고 상기 제2 밀봉막(95)과 상부 패키지 기판(32) 사이의 접착력을 더욱 증가될 수 있다.

[0064] 도 14a 및 14b의 패키지 온 패키지 장치(106)를 제조하는 과정은 플렉스 기능을 포함하거나 포함하지 않는 밀봉막 수지 용액(85a)을 연결홀(24)을 채우도록 넣고, 상기 하부 반도체 칩(20) 상에는 플렉스 기능을 포함하지 않는 밀봉막 수지 용액으로 도포한 후에, 상부 반도체 패키지(60)와 하부 반도체 패키지(50)를 배치시킨다. 그 후, 가열하여 연결 솔더 범프(33)와 상기 제1 및 제2 밀봉막들(85, 95)을 형성한다.

[0065] 그외의 구성 및 제조 과정은 도 1b를 참조하여 설명한 예와 동일/유사할 수 있다.

[0066] 상술한 반도체 패키지 기술은 다양한 종류의 반도체 소자들 및 이를 구비하는 패키지 모듈에 적용될 수 있다.

[0067] 도 15는 본 발명의 실시예들에 따른 반도체 패키지를 구비한 전자 장치를 도시한 사시도이다.

[0068] 도 15를 참조하면, 본 발명의 실시예에 따른 패키지 온 패키지 장치는 스마트 폰과 같은 전자 장치(1000)에 응용될 수 있다. 본 실시예의 패키지 온 패키지 장치는 사이즈 축소 및 성능 향상 측면에서 우수하므로, 다양한 기능을 동시에 구현하는 전자 장치(1000)의 경박 단소화에 유리하다. 전자 장치는 도 15에 도시된 스마트폰에 한정되는 것이 아니며, 가령 모바일 전자 기기, 랩톱(laptop) 컴퓨터, 휴대용 컴퓨터, 포터블 멀티미디어 플레이어(PMP), 앰피쓰리(MP3) 플레이어, 캠코더, 웹 태블릿(web tablet), 무선 전화기, 네비게이션, 개인 휴대용 정보 단말기(PDA; Personal Digital Assistant) 등 다양한 전자 기기를 포함할 수 있다.

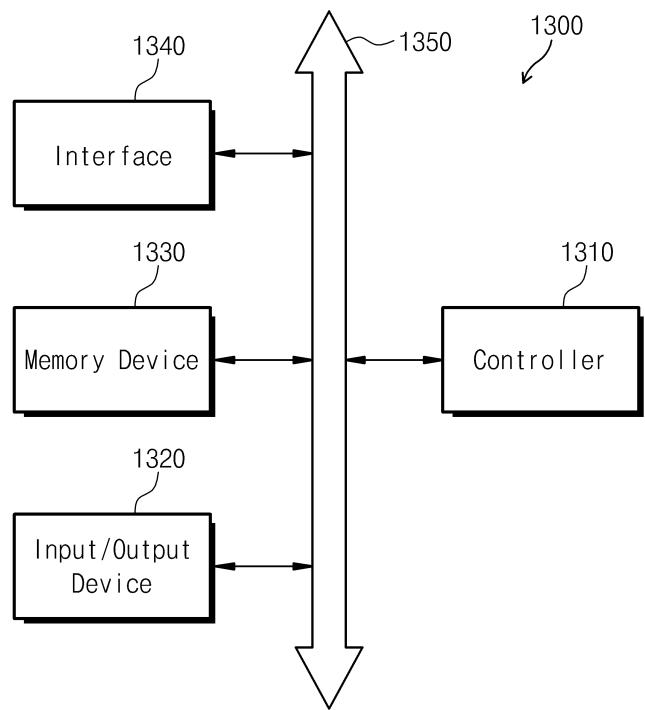

- [0069] 도 16은 본 발명의 일 예에 따른 반도체 패키지를 적용한 전자 장치의 시스템 블록도이다.

- [0070] 도 16을 참조하면, 상술한 반도체 패키지(100~105)는 전자 장치(1100)에 적용될 수 있다. 상기 전자 장치(1100)는 바디(1110: Body)와, 마이크로 프로세서 유닛(1120: Micro Processor Unit)과, 파워 유닛(1130: Power Unit)과, 기능 유닛(1140: Function Unit)과, 그리고 디스플레이 컨트롤러 유닛(1150: Display Controller Unit)을 포함할 수 있다. 상기 바디(1110)는 내부에 인쇄 회로 기판으로 형성된 세트 보드(Set Board)를 포함할 수 있으며, 마이크로 프로세서 유닛(1120), 파워 유닛(1130), 기능 유닛(1140), 디스플레이 컨트롤러 유닛(1150) 등이 상기 바디(1110)에 실장될 수 있다.

- [0071] 파워 유닛(1130)은 외부 배터리(미도시) 등으로부터 일정 전압을 공급 받아 이를 요구되는 전압 레벨로 분기하여 마이크로 프로세서 유닛(1120), 기능 유닛(1140), 디스플레이 컨트롤러 유닛(1150) 등으로 공급한다.

- [0072] 마이크로 프로세서 유닛(1120)은 파워 유닛(1130)으로부터 전압을 공급받아 기능 유닛(1140)과 디스플레이 유닛(1160)을 제어할 수 있다. 기능 유닛(1140)은 다양한 전자 시스템(1100)의 기능을 수행할 수 있다. 예를 들어, 전자 시스템(1100)가 휴대폰인 경우 기능 유닛(1140)은 다이얼링, 외부 장치(1170: External Apparatus)와의 통신으로 디스플레이 유닛(1160)로의 영상 출력, 스피커로의 음성 출력 등과 같은 휴대폰 기능을 수행할 수 있는 여러 구성요소들을 포함할 수 있으며, 카메라가 함께 형성된 경우 카메라 이미지 프로세서(Camera Image Processor)일 수 있다. 예를 들어, 전자 시스템(1100)가 용량 확장을 위해 메모리 카드 등과 연결되는 경우, 기능 유닛(1140)은 메모리 카드 컨트롤러일 수 있다. 기능 유닛(1140)은 유선 혹은 무선의 통신 유닛(1180: Communication Unit)을 통해 외부 장치(1170)와 신호를 주고 받을 수 있다. 예를 들어, 전자 시스템(1100)가 기능 확장을 위해 유에스비(USB, Universal Serial Bus) 등을 필요로 하는 경우 기능 유닛(1140)은 인터페이스(interface) 컨트롤러일 수 있다. 본 발명의 실시예에 따른 패키지 온 패키지 장치(100~105)는 마이크로 프로세서 유닛(1120)과 기능 유닛(1140) 중 적어도 어느 하나에 쓰일 수 있다.

- [0073] 상술한 반도체 패키지 기술은 전자 시스템에 적용될 수 있다.

- [0074] 도 17은 본 발명의 기술이 적용된 반도체 패키지를 포함하는 전자 장치의 예를 보여주는 블럭도이다.

- [0075] 도 17을 참조하면, 전자 시스템(1300)은 제어기(1310), 입출력 장치(1320) 및 기억 장치(1330)를 포함할 수 있다. 상기 제어기(1310), 입출력 장치(1320) 및 기억 장치(1330)는 버스(1350, bus)를 통하여 결합될 수 있다. 상기 버스(1350)는 데이터들이 이동하는 통로라 할 수 있다. 예컨대, 상기 제어기(1310)는 적어도 하나의 마이크로프로세서, 디지털 신호 프로세서, 마이크로컨트롤러, 그리고 이들과 동일한 기능을 수행할 수 있는 논리 소자들 중에서 적어도 어느 하나를 포함할 수 있다. 상기 제어기(1310) 및 기억 장치(1330)는 본 발명에 따른 패키지 온 패키지 장치를 포함할 수 있다. 상기 입출력 장치(1320)는 키패드, 키보드 및 표시 장치(display device) 등에서 선택된 적어도 하나를 포함할 수 있다. 상기 기억 장치(1330)는 데이터를 저장하는 장치이다. 상기 기억 장치(1330)는 데이터 및/또는 상기 제어기(1310)에 의해 실행되는 명령어 등을 저장할 수 있다. 상기 기억 장치(1330)는 휘발성 기억 소자 및/또는 비휘발성 기억 소자를 포함할 수 있다. 또는, 상기 기억 장치(1330)는 플래시 메모리로 형성될 수 있다. 이러한 플래시 메모리는 반도체 디스크 장치(SSD)로 구성될 수 있다. 이 경우 전자 시스템(1300)은 대용량의 데이터를 상기 기억 장치(1330)에 안정적으로 저장할 수 있다. 상기 전자 시스템(1300)은 통신 네트워크로 데이터를 전송하거나 통신 네트워크로부터 데이터를 수신하기 위한 인터페이스(1340)를 더 포함할 수 있다. 상기 인터페이스(1340)는 유무선 형태일 수 있다. 예컨대, 상기 인터페이스(1340)는 안테나 또는 유무선 트랜시버 등을 포함할 수 있다. 그리고, 도시되지 않았지만, 상기 전자 시스템(1300)에는 응용 칩셋(Application Chipset), 카메라 이미지 프로세서(Camera Image Processor:CIS), 그리고 입출력 장치 등이 더 제공될 수 있음을 이 분야의 통상적인 지식을 습득한 자들에게 자명하다.

- [0076] 이상의 상세한 설명은 본 발명을 예시하는 것이다. 또한 전술한 내용은 본 발명의 바람직한 실시 형태를 나타내고 설명하는 것에 불과하며, 본 발명은 다양한 다른 조합, 변경 및 환경에서 사용할 수 있다. 즉, 본 명세서에 개시된 발명의 개념의 범위, 저술한 개시 내용과 균등한 범위 및/또는 당업계의 기술 또는 지식의 범위 내에서 변경 또는 수정이 가능하다. 전술한 실시예들은 본 발명을 실시하는데 있어 최선의 상태를 설명하기 위한 것이며, 본 발명과 같은 다른 발명을 이용하는데 당업계에 알려진 다른 상태로의 실시, 그리고 발명의 구체적인 적용 분야 및 용도에서 요구되는 다양한 변경도 가능하다. 따라서, 이상의 발명의 상세한 설명은 개시된 실시 상태로 본 발명을 제한하려는 의도가 아니다. 또한 첨부된 청구범위는 다른 실시 상태도 포함하는 것으로 해석되어야 한다.

## 부호의 설명

[0077]

1: 하부 패키지 기판

3,7, 34, 36: 패드

11, 13, 26: 하부 솔더 범프

20: 하부 반도체 칩

22: 하부 몰딩막

24: 연결홀

30: 상부 솔더 범프

33: 연결 솔더 범프

32: 상부 패키지 기판

38,40: 상부 반도체 칩

42: 상부 몰딩막

50: 하부 반도체 패키지

54: 관통비아

56: 내부 솔더볼

60, 70: 상부 반도체 패키지

85: 밀봉막

85a: 밀봉막 수지 용액

100~105: 패키지 온 패키지 장치

도면

도면 1a

도면 1b

도면 1c

도면 1d

도면2

### 도면3

도면4

도면5

도면6

도면7a

도면7b

도면7c

도면8

도면9

도면10

도면11

도면12

도면13

도면14a

도면14b

도면15

도면16

도면17