(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6415187号

(P6415187)

(45) 発行日 平成30年10月31日(2018.10.31)

(24) 登録日 平成30年10月12日(2018.10.12)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO4N 5/365 (2011.01) | HO4N 5/365 |

| HO4N 5/374 (2011.01) | HO4N 5/374 |

| HO4N 5/359 (2011.01) | HO4N 5/359 |

| HO4N 5/378 (2011.01) | HO4N 5/378 |

| HO4N 5/347 (2011.01) | HO4N 5/347 |

請求項の数 9 (全 17 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2014-174954 (P2014-174954) |

| (22) 出願日  | 平成26年8月29日 (2014.8.29)       |

| (65) 公開番号 | 特開2016-51949 (P2016-51949A)  |

| (43) 公開日  | 平成28年4月11日 (2016.4.11)       |

| 審査請求日     | 平成29年8月24日 (2017.8.24)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100094112<br>弁理士 岡部 譲                      |

| (74) 代理人  | 100101498<br>弁理士 越智 隆夫                     |

| (74) 代理人  | 100106183<br>弁理士 吉澤 弘司                     |

| (74) 代理人  | 100128668<br>弁理士 斎藤 正巳                     |

| (72) 発明者  | 高田 佳明<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】 固体撮像装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が信号を出力する増幅トランジスタを備える複数の画素が複数行および複数列の2次元に配置されるとともに、n (nは1以上の自然数)個の前記増幅トランジスタの出力が混合されるn行の第1領域、およびm (m > n)個の前記増幅トランジスタの出力が混合されるm行の第2領域を含む画素領域と、

前記増幅トランジスタからの電圧が出力される列信号線と、

前記列信号線における電圧をクリップするとともに、前記第2領域よりも前記第1領域に近い位置に配置されたクリップ回路と、

前記増幅トランジスタの負荷となる列電流源と、

を有し、

前記列信号線に、前記列電流源、前記クリップ回路、前記第1領域、前記第2領域が順に配置された固体撮像装置。

## 【請求項 2】

各々が信号を出力する増幅トランジスタを備える複数の画素が複数行および複数列の2次元に配置されるとともに、オンである期間が重なるn (nは1以上の自然数)個の前記増幅トランジスタからの信号が出力されるn行の第1領域、およびオンである期間が重なるm (m > n)個の前記増幅トランジスタからの信号が出力されるm行の第2領域を含む画素領域と、

前記増幅トランジスタからの電圧が出力される列信号線と、

10

20

前記列信号線における電圧をクリップするとともに、前記第2領域よりも前記第1領域に近い位置に配置されたクリップ回路と、

前記増幅トランジスタの負荷となる列電流源と、

を有し、

前記列信号線に、前記列電流源、前記クリップ回路、前記第1領域、前記第2領域が順に配置された固体撮像装置。

**【請求項3】**

前記第1領域は、前記複数の画素の一部である複数のオプティカル・ブラック画素が複数行に亘って配されたオプティカル・ブラック画素領域に設定され、前記第2領域は前記複数の画素の一部である複数の開口画素が複数行に亘って配された開口画素領域に設定される請求項1または2に記載の固体撮像装置。 10

**【請求項4】**

前記増幅トランジスタは、n型MOSトランジスタであり、前記増幅トランジスタのソースの電流は、前記列信号線を介して前記列電流源に流れる、請求項1乃至3のいずれか1項に記載の固体撮像装置。

**【請求項5】**

前記増幅トランジスタは、p型MOSトランジスタであり、前記列電流源からの電流は、前記列信号線を介して前記増幅トランジスタのソースに流れる請求項1乃至3のいずれか1項に記載の固体撮像装置。

**【請求項6】**

前記列信号線は第1列信号線および第2列信号線を含み、第1列信号線には、前記列電流源、前記クリップ回路、前記第1領域、前記第2領域が順に配置され、第2列信号線には、前記クリップ回路、前記第1領域、前記第2領域、前記列電流源が順に配置された請求項1乃至5のいずれか1項に記載の固体撮像装置。 20

**【請求項7】**

前記画素は光電変換により得られた電荷を蓄積する浮遊拡散容量を有し、前記クリップ回路はリセットされた前記浮遊拡散容量の電圧に基づく前記列信号線の電圧をクリップする請求項1乃至6のいずれか1項に記載の固体撮像装置。

**【請求項8】**

複数の前記浮遊拡散容量における電荷を混合する接続トランジスタをさらに備える請求項7に記載の固体撮像装置。 30

**【請求項9】**

請求項1乃至8のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置から出力された信号を処理する信号処理部とを有する撮像システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は固体撮像装置および撮像システムに関する。

**【背景技術】**

**【0002】**

特許文献1には、CMOS型固体撮像装置において強い光が画素に入射したときでも、列信号線(特許文献1の図1のV1～V3)の電圧がクリップMOS(特許文献1の図1のM71～73)により設定された電圧に制限されることが開示されている。また、特許文献2には、撮像領域(図1の11)の複数の増幅トランジスタ(図1のTb)の信号出力を列信号線(図1のVLIN1、VLIN2、VLIN3)上で混合することが開示されている。 40

**【先行技術文献】**

**【特許文献】**

**【0003】**

【特許文献1】特開2001-230974号公報

10

20

30

40

50

【特許文献 2】特開 2011-097646 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1 および特許文献 2 は縦縞ノイズを低減する回路構成を開示していない。本発明の課題は、黒沈み現象を抑制しながら、縦縞ノイズを低減可能な固体撮像装置を提供することである。

【課題を解決するための手段】

【0005】

本発明に係る固体撮像装置は、各々が信号を出力する増幅トランジスタを備える複数の画素が複数行および複数列の 2 次元に配置されるとともに、 $n$  ( $n$  は 1 以上の自然数) 個の前記増幅トランジスタの出力が混合される  $n$  行の第 1 領域、および  $m$  ( $m > n$ ) 個の前記増幅トランジスタの出力が混合される  $m$  行の第 2 領域を含む画素領域と、前記増幅トランジスタからの電圧が出力される列信号線と、前記列信号線における電圧をクリップするとともに、前記第 2 領域よりも前記第 1 領域に近い位置に配置されたクリップ回路と、前記増幅トランジスタの負荷となる列電流源と、を有し、前記列信号線に、前記列電流源、前記クリップ回路、前記第 1 領域、前記第 2 領域が順に配置される。

本発明に係る他の固体撮像装置は、各々が信号を出力する増幅トランジスタを備える複数の画素が複数行および複数列の 2 次元に配置されるとともに、オンである期間が重なる  $n$  ( $n$  は 1 以上の自然数) 個の前記増幅トランジスタからの信号が出力される  $n$  行の第 1 領域、およびオンである期間が重なる  $m$  ( $m > n$ ) 個の前記増幅トランジスタからの信号が出力される  $m$  行の第 2 領域を含む画素領域と、前記増幅トランジスタからの電圧が出力される列信号線と、前記列信号線における電圧をクリップするとともに、前記第 2 領域よりも前記第 1 領域に近い位置に配置されたクリップ回路と、前記増幅トランジスタの負荷となる列電流源と、を有し、前記列信号線に、前記列電流源、前記クリップ回路、前記第 1 領域、前記第 2 領域が順に配置される。

【発明の効果】

【0006】

本発明によれば、混合行数の少ない画素領域に近い位置にクリップ回路を配置することにより、画像の黒沈み現象を抑制しながら、縦縞ノイズを低減可能な固体撮像装置を提供することができる。

【図面の簡単な説明】

【0007】

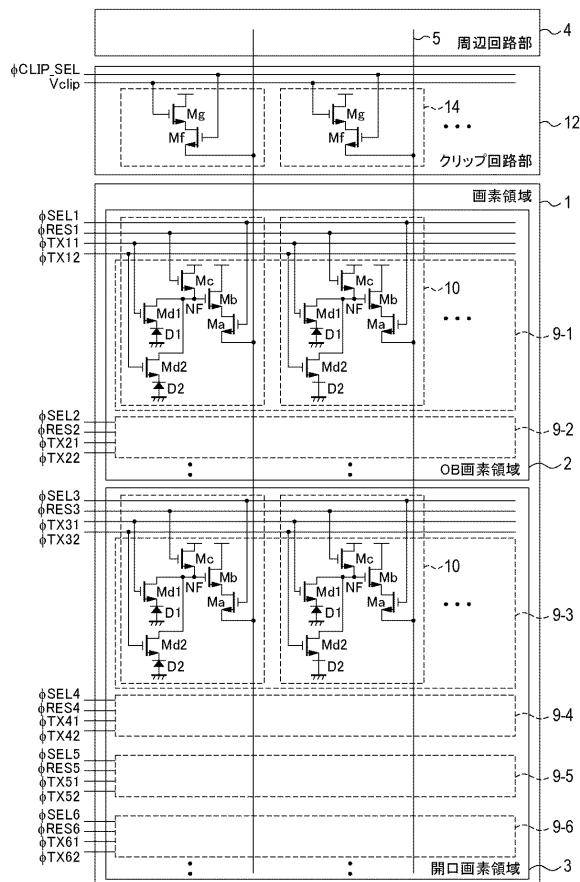

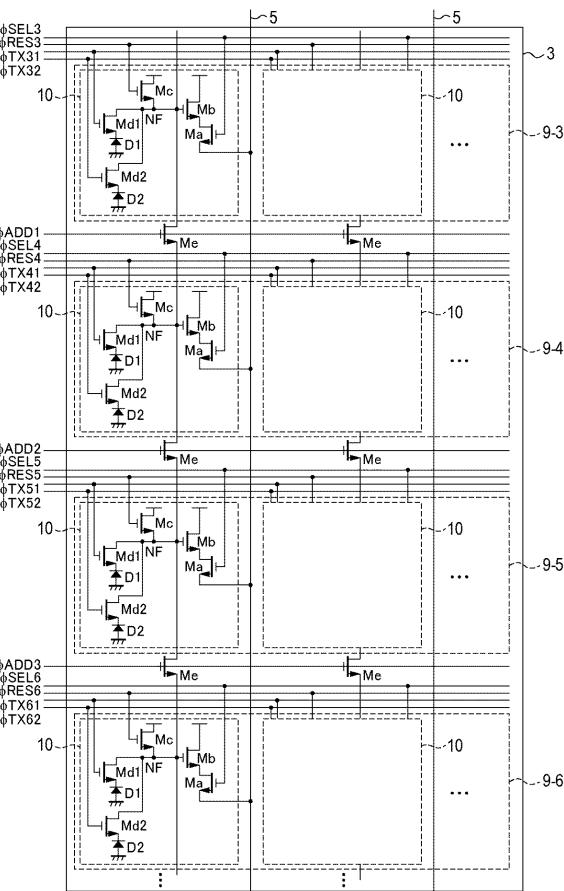

【図 1】第 1 実施形態の固体撮像装置の回路図

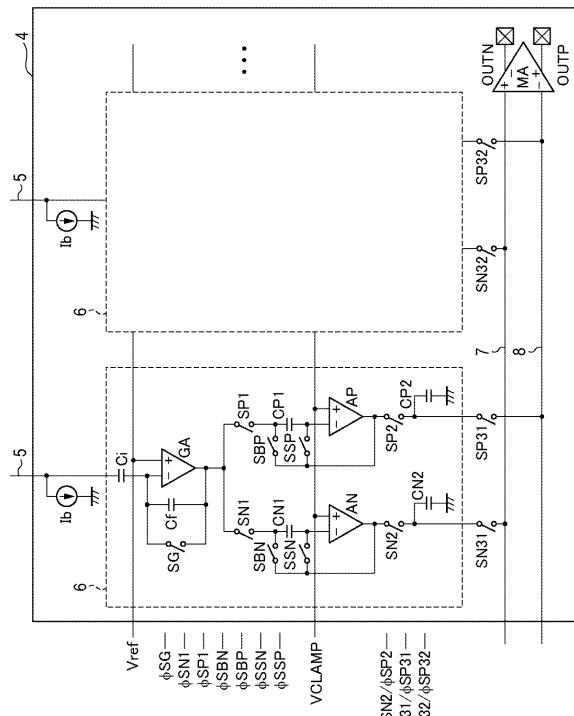

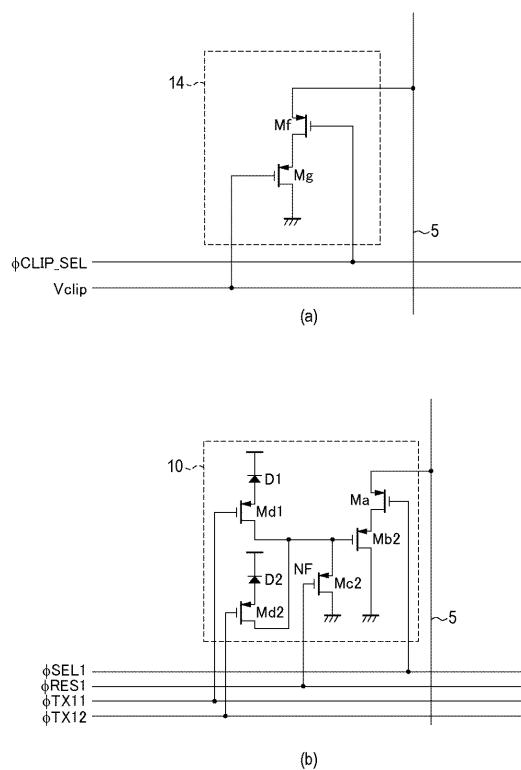

【図 2】第 1 実施形態の周辺回路部の回路図

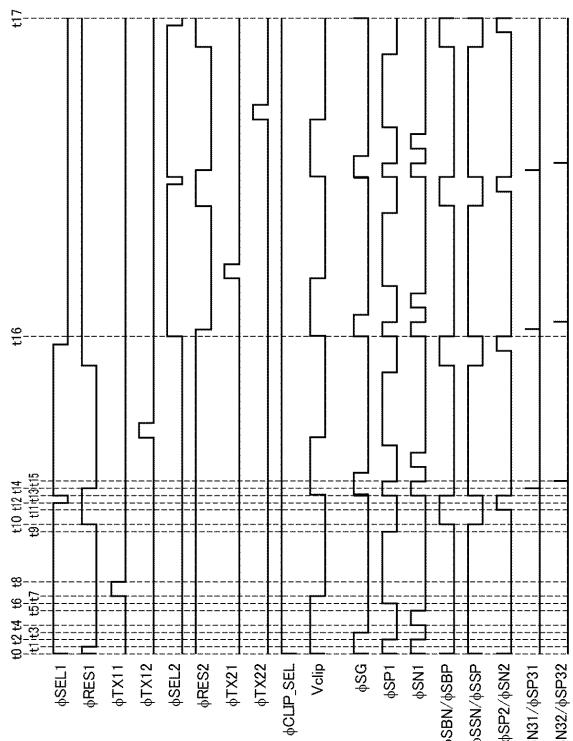

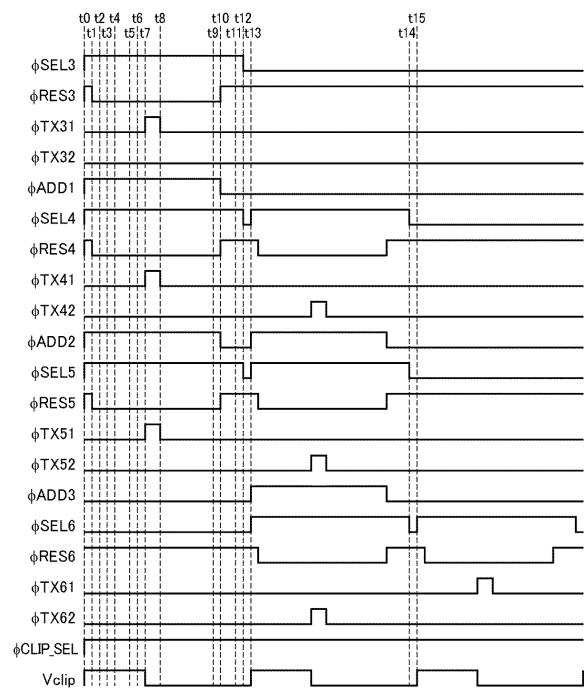

【図 3】第 1 実施形態の O B 画素領域走査時の動作を表すタイミングチャート

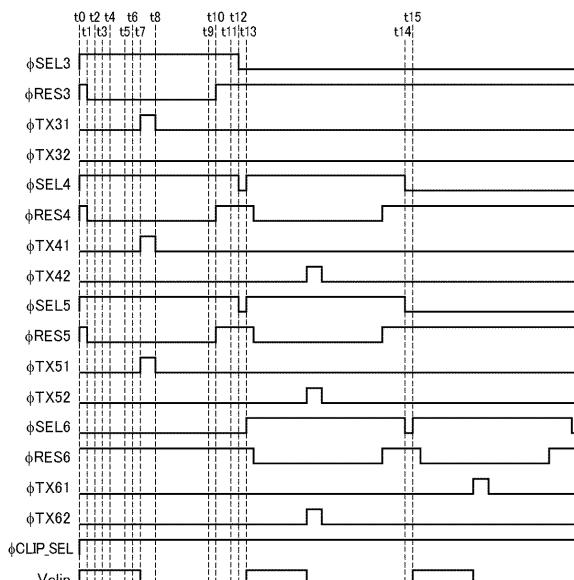

【図 4】第 1 実施形態の開口画素領域走査時の動作を表すタイミングチャート

【図 5】第 1 実施形態のクリップ電圧の説明図

【図 6】第 1 実施形態のクリップ電圧の説明図

【図 7】第 2 実施形態の固体撮像装置の回路図

【図 8】第 3 実施形態の開口画素領域の回路図

【図 9】第 3 実施形態の開口画素領域走査時の動作を表すタイミングチャート

【図 10】第 4 実施形態の単位画素回路およびクリップ回路の回路図

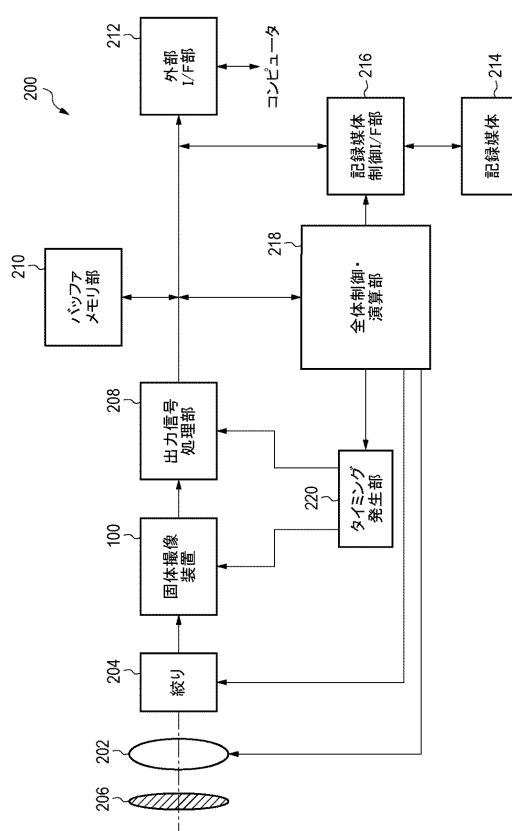

【図 11】第 5 実施形態の撮像システムのブロック図

【発明を実施するための形態】

【0008】

(第 1 実施形態)

図 1 は、第 1 実施形態の固体撮像装置の回路構成を示している。固体撮像装置は、画素領域 1、周辺回路部 4、および、列信号線 5 の電圧が所定の値以下にならないように制限するためのクリップ回路部 1 2 を備える。画素領域 1 は、行および列の 2 次元に配列され

10

20

30

40

50

た複数の単位画素 10 を備えている。また、画素領域 1 は、フォトダイオードが A1 などで遮光された単位画素 10 からなるオプティカル・ブラック画素領域 (OB 画素領域) 2、フォトダイオードが遮光されていない単位画素 10 からなる開口画素領域 3 を含む。なお、本明細書において、行方向とは図面において横方向を示し、列方向とは図面において縦方向を示すものとする。

#### 【0009】

OB 画素領域 2 は複数の画素行からなるが、図 1 では画素行 9-1、9-2 のみが示されている。また、開口画素領域 3 も同様に複数の画素行からなるが、図 1 では画素行 9-3、9-4、9-5、9-6 のみが示されている。各画素行はそれぞれ 2 画素共有された複数の単位画素 10 からなり、図 1 では 4 つの単位画素 10 が示されている。単位画素 10 は、フォトダイオード D1、D2、第 1 行の転送トランジスタ M d1、第 2 行の転送トランジスタ M d2、リセットトランジスタ M c、増幅トランジスタ M b、選択トランジスタ M a、および、増幅トランジスタ M b の入力ノード N F を有する。本実施形態においては、単位画素 10 のトランジスタは n 型 MOS トランジスタにより構成されている。

#### 【0010】

入力ノード N F は、転送トランジスタ M d1、M d2 のドレイン、リセットトランジスタ M c のソース、増幅トランジスタ M b のゲートに接続されている。2 個のフォトダイオード D1、D2、2 個の転送トランジスタ M d1、M d2 は、リセットトランジスタ M c、増幅トランジスタ M b、選択トランジスタ M a、入力ノード N F を共有している。転送トランジスタ M d1、M d2 がオンになるとにより、フォトダイオード D1、D2 の電荷が入力ノード N F に転送され、入力ノード N F はいわゆる浮遊拡散容量 (フローティングディフュージョン、以下「FD」と称する) として機能する。なお、画素領域 1 には、多数の単位画素 10 が存在し、画素領域 1 の画素行数を M、列数を N とすれば、 $2 \times M \times N$  個のフォトダイオードが存在する。以後の説明では、単位画素 10 は 2 つのフォトダイオード行を含むので、画素行内の 2 つのフォトダイオード行をそれぞれ D1 行および D2 行と称する。

#### 【0011】

画素領域 1 には、信号線 S E L 1 ~ 6、R E S 1 ~ 6、T X 1 1 ~ 6 1、T X 1 2 ~ 6 2 が行方向に延在して配置されている。転送トランジスタ M d1 のゲートには T X 1 1 が接続され、T X 1 1 がハイレベルとなると、転送トランジスタ M d1 はフォトダイオード D1 において光電変換により得られた電荷を入力ノード N F に転送する。同様に、転送トランジスタ M d2 のゲートには T X 1 2 が接続され、T X 1 2 がハイレベルとなると、転送トランジスタ M d2 はフォトダイオード D2 の電荷を入力ノード N F に転送する。増幅トランジスタ M b は入力ノード N F における電圧に応じた信号を出力する。リセットトランジスタ M c のゲートには R E S 1 が接続され、R E S 1 がハイレベルとなると、リセットトランジスタ M c は入力ノード N F の電荷をリセットする。選択トランジスタ M a のゲートには S E L 1 が接続され、S E L 1 がハイレベルになると、選択トランジスタ M a は増幅トランジスタ M b からの信号を列信号線 5 に出力する。列信号線 5 には、入力ノード N F のリセット時のリセット電圧、およびフォトダイオード D1、D2 の電荷に基づく輝度電圧が出力され得る。画素領域 1 の各列には、列信号線 5 がそれぞれ配置されている。列信号線 5 は、列方向に並ぶ単位画素 10 の選択トランジスタ M a のソースに接続され、これら単位画素 10 に共通の信号線をなしている。

#### 【0012】

クリップ回路部 12 は列信号線 5 のそれぞれに設けられた複数のクリップ回路 14 を有している。クリップ回路 14 は、それぞれ n 型 MOS トランジスタであるクリップトランジスタ M g、クリップ選択トランジスタ M f を含む。クリップトランジスタ M g のドレインは電源に接続され、ソースはクリップ選択トランジスタ M f を介して列信号線 5 に接続されている。また、クリップトランジスタ M g のゲートにはクリップ電圧の閾値に対応するクリップ電圧 V clip が印加される。クリップ選択トランジスタ M f のゲートには信号線 C L I P \_ S E L が接続されており、C L I P \_ S E L がハイレベルになると、クリ

10

20

30

40

50

ップトランジスタMgのソースはクリップ選択トランジスタMfを介して列信号線5に接続される。一方、単位画素10において、SEL1がハイレベルになると、増幅トランジスタMbのソースは選択トランジスタMaを介して列信号線5に接続される。クリップトランジスタMgのソース、増幅トランジスタMbのソースは共通に接続され、クリップトランジスタMg、増幅トランジスタMbは差動の構成となる。増幅トランジスタMbのゲート電圧がクリップ電圧Vclipよりも十分に高い場合には、クリップトランジスタMgはオフとなり、増幅トランジスタMbのゲート電圧に応じた電圧が列信号線5に出力される。増幅トランジスタMbのゲート電圧が低下し、クリップ電圧Vclipに近づくと、クリップトランジスタMgがオンになり、増幅トランジスタMbのソース電圧はクリップされる。従って、列信号線5はクリップ電圧Vclipによって定められた電圧以下には下がらない。10

#### 【0013】

周辺回路部4は列信号線5に出力された輝度電圧、リセット電圧をサンプリングし、増幅する回路を含む。また、図示されていないが、固体撮像装置は制御信号を生成するタイミングジェネレータ、画素行を選択する垂直走査回路を備える。垂直走査回路は、任意の複数の画素行の画素信号の混合を行い、複数行を同時読み出しすることが可能である。画素領域1には、n(nは1以上の自然数)個の単位画素10から列信号線に信号出力する画素行を有するn行混合領域と、m(m>n)個の単位画素10から列信号線5に信号出力する画素行を有するm行混合領域とが設定され得る。本実施形態においては、n行混合領域はOB画素領域2に設定され、m行混合領域は開口画素領域3に設定される。列信号線5の信号電圧を制限するクリップ回路部12は、m行混合領域よりもn行混合領域に近い位置に配置されている。なお、n行混合領域は開口画素領域3に配置されても良い。以上のような回路配置で画素混合を行うことで、後述するように、最適なクリップ電圧を設定でき、黒沈み現象を抑制するとともに縦縞ノイズをも低減できる。20

#### 【0014】

図2は、周辺回路部4の回路図である。周辺回路部4は、列読み出し回路6、ゲインアンプGA、入力容量Ci、フィードバック容量Cf、リセット電圧用容量CN1、輝度電圧用容量CP1、リセット電圧用容量CN2、輝度電圧用容量CP2、リセット電圧用アンプAN、輝度電圧用アンプAPを含む。また、周辺回路部4は、列電流源Ib、差動チップ外出力回路MA、MOSトランジスタからなるスイッチSG、SN1、SP1、SBN、SSN、SBP、SSP、SN2、SP2、SN31、SP31、SN32、SP32を含む。これらのスイッチは図示されていないタイミングジェネレータ、水平走査回路によって駆動される。30

#### 【0015】

列電流源Ibは、選択トランジスタMaがオンとなった場合において、増幅トランジスタMbの負荷となる。すなわち、増幅トランジスタMbのソースからの電流は、列信号線5を介して列電流源Ibに流れる。ゲインアンプGAは差動増幅器から構成され、非反転入力には基準電圧Vrefが印加され、反転入力には入力容量Ciを介して列信号線5が接続されている。フィードバック容量CfにはスイッチSGが並列に接続されており、スイッチSGがオンになると、ゲインアンプGAはボルテージフォロアとして動作する。スイッチSGがオフになると、ゲインアンプGAは(Ci/Cf)のゲインにて動作する。40

#### 【0016】

リセット電圧用容量CN1はリセット時の信号を保持するためのコンデンサであり、ここで、リセット時とはフォトダイオードD1の電荷が転送される前の状態をいう。すなわち、リセット時の入力ノードNFに対応した信号が増幅トランジスタMb、ゲインアンプGAを介してリセット電圧用容量CN1に書き込まれる。輝度電圧用容量CP1は輝度電圧を保持するためのコンデンサであり、フォトダイオードD1の電荷が転送された後の入力ノードNFに対応した信号が増幅トランジスタMb、ゲインアンプGAを介して輝度電圧用容量CP1に書き込まれる。

#### 【0017】

10

20

30

40

50

リセット電圧用アンプ A N は差動増幅器から構成されており、非反転入力にはクランプ電圧 V C L A M P が印加され、反転入力にはリセット電圧用容量 C N 1 が接続されている。リセット電圧用アンプ A N の出力はスイッチ S N 2 を介してリセット電圧用容量 C N 2 に接続されている。リセット電圧用容量 C N 2 はさらにスイッチ S N 3 1 を介してリセット電圧用の水平信号線 7 に接続され、水平信号線 7 は差動チップ外出力回路 M A に接続されている。輝度電圧用アンプ A P 、輝度電圧用容量 C P 2 も同様に構成され、輝度電圧用アンプ A P の出力はスイッチ S P 3 1 、輝度電圧用の水平信号線 8 を介して差動チップ外出力回路 M A に接続されている。差動チップ外出力回路 M A は、（輝度電圧 - リセット電圧）の信号を生成し、相関二重サンプリングした電圧をチップ外に出力する。

【0018】

10

図 3 のタイミングチャートを参照しながら、第 1 実施形態の固体撮像装置の O B 画素領域 2 の信号の読み出し動作を説明する。まず、時刻 t 0 において、S E L 1 がハイレベルになり、n 型 M O S の選択トランジスタ M a がオンし、画素行 9 - 1 が選択される。同時に、C L I P \_ S E L がハイレベルになり、クリップ選択トランジスタ M f がオンし、クリップ回路 1 4 が選択されるとともに、クリップトランジスタ M g のゲートに所定のクリップ電圧 V clip が供給される。同時に、S G がハイレベルでスイッチ S G がオンになり、ゲインアンプ G A が基準電圧 V r e f に対するボルテージフォロワとして動作し、基準電圧 V r e f を出力する。さらに、S B N 、S B P がローレベルでスイッチ S B N 、S B P がオフとなり、S S N 、S S P がハイレベルでスイッチ S S N 、S S P がオンとなる。これにより、リセット電圧用アンプ A N と輝度電圧用アンプ A P がサンプリングモードとなり、リセット電圧用容量 C N 1 と輝度電圧用容量 C P 1 は信号を書き込み可能な状態となる。そして、S N 1 と S P 1 がハイレベルになることで、基準電圧 V r e f がゲインアンプ G A を介してリセット電圧用容量 C N 1 と輝度電圧用容量 C P 1 に書き込まれる。

20

【0019】

時刻 t 1 において、R E S 1 がローレベルになり、画素行 9 - 1 のリセットトランジスタ M c がオフとなり、入力ノード N F が浮遊状態になる。時刻 t 2 において、S N 1 、S P 1 がローレベルでスイッチ S N 1 、S P 1 がオフとなり、リセット電圧用容量 C N 1 と輝度電圧用容量 C P 1 への基準電圧 V r e f の書き込みが終わる。

【0020】

30

時刻 t 3 において、S G がローレベルでスイッチ S G がオフとなり、ゲインアンプ G A のゲインが ( C i / C f ) になる。時刻 t 4 において、S N 1 がハイレベルでスイッチ S N 1 がオンとなり、画素行 9 - 1 に含まれる単位画素 1 0 の入力ノード N F のリセット時の電圧が、列電流源 I b を負荷とした増幅トランジスタ M b を介して、リセット電圧用容量 C N 1 に書き込まれ始める。すなわち、フォトダイオード D 1 、D 2 の電荷が転送される前の状態の信号がリセット電圧用容量に供給される。時刻 t 5 において、S N 1 がオフとなり、入力ノード N F におけるリセット電圧のリセット電圧用容量 C N 1 への書き込みが終わる。

【0021】

40

時刻 t 6 において、S P 1 がハイレベルでスイッチ S P 1 がオンとなり、画素行 9 - 1 に含まれる単位画素 1 0 の入力ノード N F の電圧が増幅トランジスタ M b を介して輝度電圧用容量 C P 1 に書き込まれ始める。時刻 t 7 において、クリップ電圧 V clip が 0 V となり、クリップの有効期間が終了する。また、T X 1 1 がハイレベルとなり、画素行 9 - 1 の D 1 行の転送トランジスタ M d 1 がオンし、フォトダイオード D 1 への光照射で蓄積された電子が、入力ノード N F に転送される。すると、入力ノード N F の電圧がフォトダイオード D 1 の蓄積電荷量に応じて下がり、その電圧が輝度電圧用容量 C P 1 に書き込まれる。

【0022】

50

時刻 t 8 において、T X 1 1 がローレベルとなり、画素行 9 - 1 の D 1 行の転送トランジスタ M d 1 がオフになり、フォトダイオード D 1 で蓄積された電子の、入力ノード N

Fへの転送が終了する。時刻  $t_9$ において、S P 1 がローレベルでスイッチ S P 1 がオフとなり、輝度電圧用容量 C P 1 への輝度電圧の書き込みが終了する。

【0023】

時刻  $t_{10}$ において、R E S 1 がハイレベルで、画素行 9 - 1 の n 型M O S リセットトランジスタ M c がオンとなり、入力ノード N F の浮遊状態が終わる。同時に、S B N 、S B P がハイレベルでスイッチ S B N 、S B P がオンになり、S S N 、S S P がローレベルでスイッチ S S N 、S S P がオフとなる。これにより、リセット電圧用アンプ A N がリセット電圧用容量 C N 1 の信号読み出しモードになり、輝度電圧用アンプ A P が輝度電圧用容量 C P 1 の信号読み出しモードになる。時刻  $t_{11}$ において、S N 2 がハイレベルでスイッチ S N 2 がオンとなり、リセット電圧用容量 C N 1 に書き込まれたりセット電圧がリセット電圧用アンプ A N により、リセット電圧用容量 C N 2 に書き込まれ始める。また、S P 2 がハイレベルでスイッチ S P 2 がオンになり、輝度電圧が輝度電圧用アンプ A P により輝度電圧用容量 C P 2 に書き込まれ始める。10

【0024】

時刻  $t_{12}$ において、S E L 1 がローレベルで画素行 9 - 1 の選択トランジスタ M a がオフし、画素行 9 - 1 の D 1 行の画素信号の、周辺回路部 4 への読み出しが終わる。時刻  $t_{13}$ において、S N 2 と S P 2 がローレベルになり、リセット電圧用容量 C N 2 と輝度電圧用容量 C P 2 へのリセット電圧と輝度電圧の書き込みが終了する。同時に、S B N 、S B P がローレベルでスイッチ S B N 、S B P がオフ、S S N 、S S P がハイレベルでスイッチ S S N 、S S P がオンとなり、リセット電圧用アンプ A N と輝度電圧用アンプ A P がサンプリングモードに復帰する。20

【0025】

時刻  $t_{14}$ において、S N 3 1 と S P 3 1 がハイレベルでスイッチ S N 3 1 と S P 3 1 がオンになる。すると、リセット電圧用容量 C N 2 と輝度電圧用容量 C P 2 に蓄積された 1 列目のリセット電圧と輝度電圧が、それぞれリセット電圧用水平信号線 7 と輝度電圧用水平信号線 8 に読み出される。ここで、輝度電圧用容量 C P 2 の容量値を C 1 、リセット電圧用水平信号線 7 と輝度電圧用水平信号線 8 の容量値を C 2 とした場合、リセット電圧および輝度電圧は  $C_1 / (C_1 + C_2)$  で表されるゲインで読み出される。この時、リセット電圧用容量 C N 2 と輝度電圧用容量 C P 2 における電圧も同様に  $C_1 / (C_1 + C_2)$  のゲインで変化する。差動チップ外出力回路 M A は、リセット電圧用水平信号線 7 と輝度電圧用水平信号線 8 から（輝度電圧 - リセット電圧）の信号を生成し、相関二重サンプリングした電圧をチップ外に出力する。30

【0026】

時刻  $t_{15}$ において、S N 3 2 と S P 3 2 がハイレベルでスイッチ S N 3 2 と S P 3 2 がオンになる。これにより、リセット電圧用容量 C N 2 と輝度電圧用容量 C P 2 に蓄積された 2 列目のリセット電圧と輝度電圧が、それぞれリセット電圧用水平信号線 7 と輝度電圧用水平信号線 8 に読み出される。S N 3 2 と S P 3 2 以降のスイッチは時刻  $t_{15}$  以降、順次オンする。全列のスイッチオンが終了し、最終列の相関二重サンプリングされた電圧が差動チップ外出力回路 M A によって出力された時点で、画素行 9 - 1 の D 1 行の画素信号のチップ外への出力が終了する。40

【0027】

時刻  $t_{13}$  以降、画素行 9 - 1 の D 2 行のリセット電圧と輝度電圧が読み出される。D 2 行の読み出し動作は、画素行 9 - 1 の D 1 行の読み出し動作（時刻  $t_0 \sim t_{13}$  ）と同様であるので、その説明を省略する。さらに、時刻  $t_{16}$  から  $t_{17}$  において、画素行 9 - 2 の画素信号が読み出される。画素行 9 - 2 の読み出し動作は、画素行 9 - 1 の読み出し動作（時刻  $t_0 \sim t_{16}$  ）と同様である。ただし、上述の説明において、S E L 1 、R E S 1 、T X 1 1 、T X 1 2 は、それぞれ S E L 2 、R E S 2 、T X 2 1 、T X 2 2 に読み替えられる。

【0028】

次に、図 4 のタイミングチャートを参照しながら、第 1 実施形態の開口画素領域 3 の信50

号の読み出し動作を説明する。周辺回路部4の動作は、OB画素領域2の信号の読み出し動作と同じであるため、図4のタイミングチャートでは周辺回路部4の制御信号は省略されている。

#### 【0029】

まず、時刻t0において、SEL3、SEL4、SEL5がハイレベルになり、選択トランジスタMaがオンとなり、開口画素領域3の画素行9-3、9-4、9-5が同時に選択される。CLIP\_SELがハイレベルになり、クリップ選択トランジスタMfがオンとなり、クリップ回路14が選択される。クリップトランジスタMgのゲートに所定のクリップ電圧Vclipが供給され、列信号線5の電圧はクリップ可能な状態となる。

10

#### 【0030】

時刻t1において、RES3、RES4、RES5がローレベルになり、画素行9-3、9-4、9-5のリセットトランジスタMcがオフになる。これにより、入力ノードNFが浮遊状態になり、入力ノードNFのリセット電圧が読み出される。このとき、画素行9-3、9-4、9-5が選択されているため、これら3つの画素行からの画素信号が列信号線5上で混合され、その電圧がリセット電圧用容量CN1に書き込まれる。

#### 【0031】

時刻t7において、クリップ電圧Vclipが0Vとなり、クリップの有効期間が終了する。また、TX31、TX41、TX51がハイレベルで画素行9-3、9-4、9-5のD1行の転送トランジスタMd1がオンとなり、フォトダイオードD1への光照射で蓄積された電子が、入力ノードNFに転送される。すると、入力ノードNFの電圧がフォトダイオードD1の蓄積電荷量に応じて下がる。

20

#### 【0032】

時刻t8において、TX31、TX41、TX51がローレベルとなり、画素行9-3、9-4、9-5のD1行の転送トランジスタMd1がオフとなる。これにより、フォトダイオードD1への光照射で蓄積された電子の、入力ノードNFへの転送が終了する。次いで、入力ノードNFの輝度電圧が読み出される。このとき、同時に選択されている画素行9-3、9-4、9-5からの画素信号が列信号線5上で混合され、その電圧が輝度電圧用容量CP1に書き込まれる。

30

#### 【0033】

時刻t10において、RES3、RES4、RES5がハイレベルで、画素行9-3、9-4、9-5のリセットトランジスタMcがオンとなり、入力ノードNFの浮遊状態が終わる。時刻t12において、SEL3、SEL4、SEL5がローレベルで画素行9-3、9-4、9-5の選択トランジスタMaがオフとなり、画素行9-3、9-4、9-5の画素信号の、周辺回路部4への読み出しが完了する。

#### 【0034】

時刻t13以降、画素行のD2行のリセット電圧と輝度電圧が読み出される。D2行の読み出し動作は、D1行の読み出し動作（時刻t0～t12）と同様である。時刻t15以降、時刻t0～t14と同様、3つの画素行が同時に選択されていく。

40

#### 【0035】

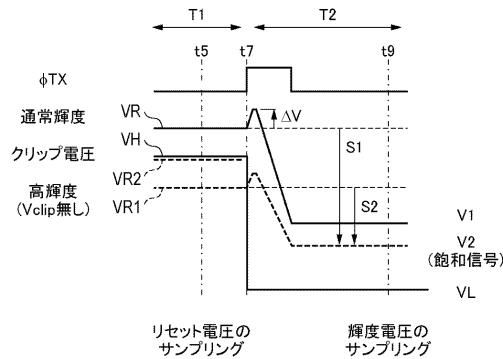

図5は、通常輝度の被写体、高輝度の被写体のそれぞれの撮影時における、列信号線5の電圧変化を示している。図5において、上から順に、転送パルスTX、通常輝度時の電圧、クリップ電圧、高輝度時の電圧が示されている。期間T1は単位画素10がリセットされてからTXがハイレベルになるまで（時刻t7）の期間を表し、期間T2は光電荷の転送以降の期間を表している。時刻t5は、リセット電圧VRを確定するサンプリング時刻であり、時刻t9は、輝度電圧V1あるいはV2を確定するサンプリング時刻である。

#### 【0036】

通常輝度の被写体撮像時において、入力ノードNFのリセット時の画素信号がリセット電圧VRとして列信号線5に出力される。期間T1においてクリップ電圧Vclipは電圧V

50

Hとなっているが、リセット電圧VRは電圧VHよりも高いため、リセット電圧VRはクリップされることなくサンプリングされる（時刻t5）。時刻t7において、転送パルスTXがハイレベルとなり、フォトダイオードの電荷が読み出され、輝度電圧として列信号線に出力される。Vは、転送パルスTXがハイレベルおよびローレベルに変化することによる信号の振幅を示している。TXがハイレベルに変化する際、フォトダイオードD1の電荷はFDへ転送され、列信号線の電圧はその電荷に基づき低下し始める。時刻t7において、クリップ電圧Vclipは輝度電圧がクリップされない電圧VL（例えば0V）まで低下する。時刻t9において輝度電圧V1がサンプリングされ、その後、相関二重サンプリングにより差分信号（V1 - VR）が得られる。

## 【0037】

10

次に高輝度被写体撮像時の黒沈み現象について説明する。図5において、高輝度被写体撮像時の画素信号は破線で示されている。期間T1において、太陽光のように非常に強い光がフォトダイオードに入射すると、フォトダイオードに発生した多量の光電荷の一部がFDに漏れ込み、FDの電圧が低下する。仮に、クリップ回路が無いとすると、リセット電圧VRに漏れ込み電圧が重畠された電圧VR1が列信号線に出力されてしまう。期間T2において、輝度電圧である画素の飽和信号をV2とすると、通常輝度被写体撮像時には、リセット電圧VRを基準電圧とした相関二重サンプリングがなされ、差分信号S1（=V2 - VR）が飽和信号レベルとして得られる。ところが、高輝度被写体撮像時には、電圧VR1を基準電圧とした相関二重サンプリングがなされ、差分信号S2（=V2 - VR1）が飽和信号レベルとなる。このように、基準電圧であるリセット電圧の変動により、差分信号S2は差分信号S1より小さくなってしまう。例えば、スポット光のような高輝度被写体の画像部分では、スポット部の画像信号が周囲の通常輝度被写体の画像に対して低い画像信号レベルとなり、黒く見える。この状態を黒沈み現象と呼んでいる。

## 【0038】

20

この黒沈み現象を抑制するために、クリップ回路14は期間T1の列信号線のリセット電圧の低下を制限している。すなわち、高輝度被写体撮像時の期間T1において、列信号線のリセット電圧はVR1ではなくクリップ電圧VHに制限される。なお、制限されたりセット電圧は、破線で示すVR2であるが、これはクリップ電圧VHとほぼ同じ電圧である。

## 【0039】

30

このように、クリップ回路14は、期間T1の列信号線電圧が低下しすぎないよう制限することが目的であるから、クリップ電圧は十分に高い必要がある。しかし、列信号線5の電圧は、列信号線5に接続されている列電流源Ib、列信号線5の抵抗による電圧降下、複数の画素を同時に駆動する画素混合などの要因によって変化し得る。この電圧変化を考慮しないでクリップ電圧を設定すると、リセット電圧をサンプリングする際に、増幅トランジスタMbのゲート電圧がクリップ電圧VHに近づくことがある。この場合、クリップトランジスタMgに電流が流れ始め、リセット電圧のクリップが開始される。このクリップによるリセット電圧VRが列信号線毎に異なり、縦縞状のノイズとして現れる。すなわち、黒沈み現象を抑制するためにクリップ電圧を上げ過ぎると、暗時において縦縞ノイズが生じ易くなる。

## 【0040】

40

本実施形態によれば、黒沈み現象を抑制しながら、かつ縦縞ノイズが発生しないように、列信号線の動作点をクリップ電圧よりも十分に高くすることができる。次に、本実施形態におけるクリップ電圧の設定について説明する。

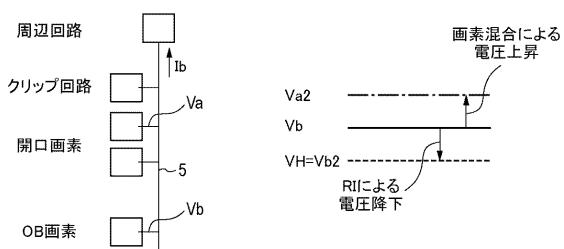

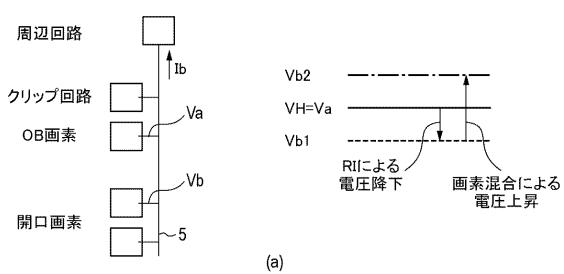

## 【0041】

図6(a)の左図は、本実施形態における、単位画素10、クリップ回路14、および、周辺回路部4の配置を示し得る。クリップ回路14に近い単位画素10の電圧をVa、遠い単位画素10の電圧をVbとする。列信号線5には、単位画素10からクリップ回路14に向かって電流が流れ、列信号線5の抵抗Rによる電圧降下が発生し、電圧Vaは電圧Vbよりも低くなる。単位画素10の増幅トランジスタMbの出力電圧がクリップ回路

50

14からの距離に依らず一定であると仮定すると、読み出す単位画素10がクリップ回路14から遠いほど、列信号線5の抵抗によってクリップ回路14近傍の列信号線5の電圧は低くなる。一方、画素混合動作では、複数の選択トランジスタM<sub>a</sub>を同時にオンとし、複数の増幅トランジスタM<sub>b</sub>が並列に列信号線5に接続されるため、増幅トランジスタM<sub>b</sub>の実質的なチャネル幅が大きくなる。これは、増幅トランジスタM<sub>b</sub>のゲート・ソース間電圧が小さくなることを意味し、これにより、増幅トランジスタM<sub>b</sub>のソース電圧、すなわち列信号線5の動作点が高くなる。よって、n画素混合を行ったOB画素領域2に比べて、n行より多いm画素混合を行った開口画素領域3の列信号線5の電圧の動作点が高くなる。列信号線5の電圧の動作点が上昇することにより、クリップ電圧を高くしたとしても、クリップトランジスタM<sub>g</sub>はオンし難くなり、暗時における縦縞ノイズを低減することができる。また、クリップ電圧を高くすることができるため、クリップ電圧の範囲を拡大することができ、高輝度時の黒沈み現象を有効に抑制することが可能となる。

#### 【0042】

図6(a)の右図は、本実施形態の周辺回路部4、クリップ回路部12、OB画素領域2、開口画素領域3の順に配置した時の列信号線5の電圧を示している。列信号線5においてクリップ回路14から離れた単位画素10の電圧V<sub>b</sub>は、電圧V<sub>a</sub>に対して、列信号線の抵抗の電圧降下R<sub>I</sub>だけ低下し、クリップ回路14において破線で示す電圧V<sub>b</sub>1になる。一方、OB画素領域2はn画素の同時読み出し、開口画素領域3ではm画素(m>n)の画素混合動作を行うので、電圧V<sub>b</sub>1は高くなり、クリップ回路14における電圧は一点鎖線で示す電圧V<sub>b</sub>2に上昇する。従って、クリップ電圧V<sub>H</sub>をクリップ回路14の近傍の電圧V<sub>a</sub>に設定した場合であっても、クリップトランジスタM<sub>g</sub>に電流が流れ難くなり、縦縞ノイズは低減される。

#### 【0043】

図6(b)は、図6(a)に対して、OB画素と開口画素の位置を入れ替わった構成を示している。列信号線5においてクリップ回路14から離れた単位画素10の電圧V<sub>b</sub>は、列信号線5の抵抗Rによる電圧降下R<sub>I</sub>だけ低下し、クリップ回路14において電圧V<sub>b</sub>2となる。クリップ回路14近傍の単位画素10の電圧V<sub>a</sub>は、画素混合により上昇し、一点鎖線で示す電圧V<sub>a</sub>2になる。この場合、開口画素領域3よりも相対的に遠くに位置するOB画素領域2を読み出す際の電圧V<sub>b</sub>2が最も低くなる。すなわち、OB画素領域2の単位画素を読み出す際に、クリップトランジスタM<sub>g</sub>が最もオンになり易く、縦縞ノイズが生じやすくなる。ここで、列信号線5の電圧がクリップされないようにするために、クリップ電圧V<sub>H</sub>をV<sub>b</sub>2に下げる必要がある。ところが、クリップ電圧を下げるに、クリップ電圧範囲は狭くなり、高輝度撮像時における黒沈み現象を抑制し難くなる。従って、高輝度時における黒沈み現象を低減しながら、暗時の縦縞ノイズを抑制するためには、図6(b)の回路配置よりも、本実施形態である図6(a)の回路配置が有効であることが上述の考察から確認できる。

#### 【0044】

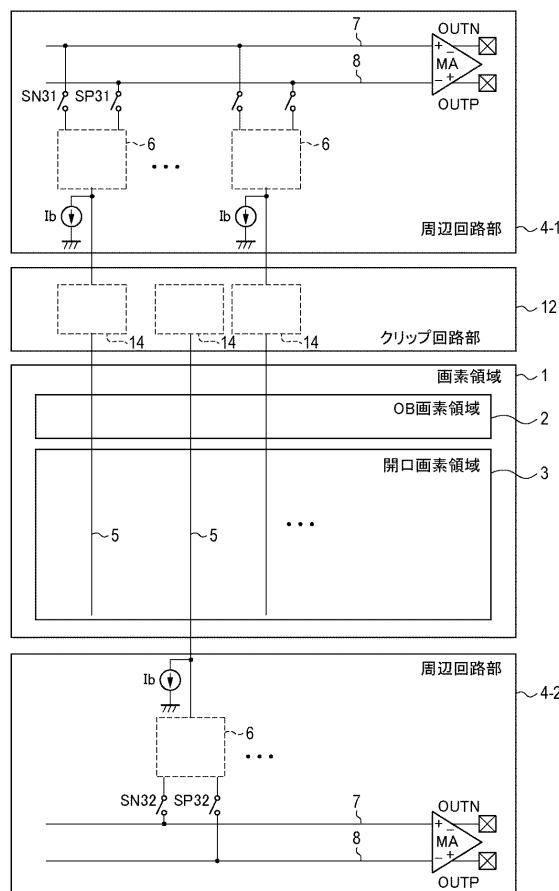

##### (第2実施形態)

図7は、第2実施形態の固体撮像装置の回路構成を示している。図1との差異は、周辺回路部が画素領域1の両側に配置されており、一方が奇数列の画素信号を読み出す周辺回路部4-1、他方が偶数列の画素信号を読み出す周辺回路部4-2となっていることにある。OB画素領域2の画素行走査および開口画素領域3の画素行の走査の読み出し動作は、それぞれ図3および図4と同様である。

#### 【0045】

奇数列(第1列信号線)では、第1実施形態において説明したように、読み出す画素行がクリップ回路部12から遠いほど、クリップ回路14近傍の列信号線5の電圧は低くなり、縦縞ノイズが発生し易くなる。一方、偶数列(第2列信号線)では、列信号線5を流れる電流の向きが奇数列とは逆向きになる。このため、クリップ回路部12から遠い画素行の信号を読み出すときのほうが、クリップ回路部12近傍の列信号線5の電圧は高くなり、クリップトランジスタに電流が流れ難くなる。よって、本実施形態では、クリップ回

10

20

30

40

50

路部 1 2 から遠い奇数列の単位画素を読み出す際に、クリップ回路部 1 2 近傍の列信号線の電圧が最も低くなり得る。一方、O B 画素領域 2 では n 画素の同時読み出し、開口画素領域 3 では m 画素 ( $m > n$ ) の画素混合動作を行っている。このため、図 7 のようにクリップ回路部 1 2 、O B 画素領域 2 、開口画素領域 3 の順に配置することにより、クリップ回路部 1 2 近傍の列信号線 5 の電圧を高くすることができる。従って、リセット電圧読み出し時においてクリップトランジスタがオンし難くなり、縦縞ノイズを効果的に抑制することができる。

#### 【 0 0 4 6 】

本実施形態では、クリップ回路部 1 2 から遠くに位置し、縦縞ノイズが発生しやすい奇数列の単位画素を含む領域を、m 行の混合を行う開口画素領域とすることで、縦縞ノイズが生じること無く、クリップ電圧の範囲を広げることができる。これにより、黒沈み現象を有効に抑制しながら、縦縞ノイズをも低減することが可能となる。

#### 【 0 0 4 7 】

##### ( 第 3 実施形態 )

図 8 は、第 3 実施形態の固体撮像装置の開口画素領域 3 の回路を示している。第 1 実施形態との差異は、複数の単位画素 1 0 の入力ノード N F の間に、F D 領域を導通もしくは非導通とする F D 接続トランジスタ M e が設けていることにある。また、O B 画素領域 2 にも F D 接続トランジスタ M e を設けている。F D 接続トランジスタのゲートには制御信号 ADD 1 ~ 3 が入力され、ADD 1 ~ 3 がハイレベルになると、隣接する行の単位画素 1 0 の入力ノード N F が相互に接続される。本実施形態の O B 画素領域 2 の読み出し動作は、第 1 実施形態 O B 画素領域走査時のタイミングチャート（図 3 ）で示された動作と同様である。つまり、F D 接続トランジスタ M e は O B 画素領域 2 にも設けられているが、O B 画素領域 2 の信号を読み出す際には、O B 画素領域 2 に存在する F D 接続トランジスタ M e はオフになる。

#### 【 0 0 4 8 】

図 9 は、本実施形態の開口画素領域 3 の走査時のタイミングチャートである。図 4 との差異は、F D 接続トランジスタ M e の制御信号 ADD 1 、ADD 2 、ADD 3 が追加されている点である。ADD 1 、ADD 2 、ADD 3 以外の制御信号の動作は図 4 に示された動作と同様である。時刻 t 0 において、ADD 1 、ADD 2 がハイレベルとなり、F D 接続トランジスタ M e がオンになり、画素行 9 - 3 、9 - 4 、9 - 5 の入力ノード N F が接続される。時刻 t 7 において、転送トランジスタ M d 1 または M d 2 がオンになり、3 つの単位画素 1 0 に存在するフォトダイオード D 1 あるいは D 2 からの電荷が、接続された入力ノード N F 上で加算および混合される。

#### 【 0 0 4 9 】

F D 接続トランジスタ M e を設けることで、F D 接続トランジスタ M e が無い場合と比較して、混合する単位画素からの信号の強さに差がある場合であっても、より正確に信号を混合することができる。また、本実施形態においても、第 1 実施形態と同様に、m 行の混合を行う開口画素領域よりも n 行 ( $m > n$ ) の混合を行う O B 画素領域に近い位置にクリップ回路部 1 2 をすることで、黒沈み現象を抑制しながら、縦縞ノイズを低減することができる。

#### 【 0 0 5 0 】

##### ( 第 4 実施形態 )

図 1 0 は、第 4 実施形態の単位画素 1 0 およびクリップ回路 1 4 を示している。第 1 実施形態との差異は、選択トランジスタ M a 、増幅トランジスタ M b 、リセットトランジスタ M c 、転送トランジスタ M d 1 、M d 2 、クリップ選択トランジスタ M f 、クリップトランジスタ M g が、n 型 M O S トランジスタから p 型 M O S トランジスタに置き換わっていることにある。また、本実施形態では、列電流源 I b は電源に接続される。すなわち、列電流源 I b からの電流は、列信号線 5 を介して増幅トランジスタ M b のソースに流れる。

#### 【 0 0 5 1 】

10

20

30

40

50

本実施形態のO B画素領域2および開口画素領域3の読み出し動作は、それぞれ、図3、図4のタイミングチャートにおいて、パルスのハイレベルとローレベルを入れ替えたものと等価である。ただし、クリップトランジスタMgのゲートに印加されるクリップ電圧は、リセット電圧のサンプリング時には所定のVclip電圧に設定され、輝度電圧サンプリング時には電源電圧に設定される。

#### 【0052】

本実施形態においては、列電流源Ibは電源に接続されるため、列信号線5からの電流は、クリップ回路部12から画素領域1へ向かって流れる。よって、電圧降下により、列信号線5の電圧は、クリップ回路部12に近づくにつれて高くなる。従って、単位画素10の増幅トランジスタMbの出力電圧がクリップ回路部12からの距離に依らず一定であると仮定すると、読み出す単位画素10がクリップ回路部12から遠いほど、クリップ回路部12近傍の列信号線5の動作点の電圧は高くなる。クリップ回路部12近傍の列信号線5の動作点の電圧が高くなると、クリップトランジスタMgのゲート・ソース間電圧の絶対値が大きくなる。よって、クリップ回路部12から遠い画素行の信号を読み出すときほど、クリップトランジスタMgに電流が流れやすくなる。以上のことから、縦縞ノイズが発生しないクリップ電圧範囲の下限は、クリップ回路部12から遠い画素行によって定められる。一方、本実施形態では、開口画素領域3の走査時において混合を行っている。このため、混合をしないO B画素領域2に比べ、画素信号を読み出す際の列信号線電圧の動作点が低くなり、縦縞ノイズの発生が抑制される。つまり、本実施形態では、クリップ回路部12から遠くに位置し、縦縞ノイズが発生しやすい画素行を含む領域を、混合化動作を行う開口画素領域としている。これにより、縦縞ノイズを抑制しながら、黒沈み現象が発生しないようにクリップ電圧の範囲を広げることができる。

#### 【0053】

本実施形態では、画素領域1においてp型MOSトランジスタを使用している。一般に、p型MOSトランジスタのほうがn型MOSトランジスタよりも1/fノイズが小さいため、本実施形態ではn型MOSトランジスタを用いた第1実施形態に比較して、ノイズを低減する効果が得られる。

#### 【0054】

##### (撮像システムの実施形態)

本発明の第5実施形態による撮像システムについて図11を用いて説明する。図1乃至図10に示す第1乃至第4実施形態による固体撮像装置と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

#### 【0055】

図11は、本実施形態による撮像システムの構成を示すブロック図である。上記第1乃至第4実施形態で述べた固体撮像装置は、種々の撮像システムに適用可能である。撮像システムの一例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラなどがあげられる。図11に例示した撮像システム200は、固体撮像装置100、被写体の光学像を固体撮像装置100に結像させるレンズ202、レンズ202を通過する光量を可変にするための絞り204、レンズ202の保護のためのバリア206を有する。レンズ202及び絞り204は、固体撮像装置100に光を集光する光学系である。撮像システム200は、また、固体撮像装置100より出力される出力信号の処理を行う出力信号処理部208を有する。出力信号処理部208は、固体撮像装置100が出力するアナログ信号をデジタル信号に変換するA/D変換を行う。また、出力信号処理部208はその他、必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。

#### 【0056】

撮像システム200は、さらに、画像データを一時的に記憶するためのバッファメモリ部210、外部コンピュータ等と通信するための外部インターフェース部(外部I/F部)212を有する。さらに撮像システム200は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体214、記録媒体214に記録又は読み出しを行うための記録媒体制御インターフェース部(記録媒体制御I/F部)216を有する。なお、記

10

20

30

40

50

録媒体 214 は、撮像システム 200 に内蔵されていてもよく、着脱可能であってもよい。

。

#### 【0057】

さらに撮像システム 200 は、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部 218、固体撮像装置 100 と出力信号処理部 208 に各種タイミング信号を出力するタイミング発生部 220 を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システム 200 は少なくとも固体撮像装置 100 と、固体撮像装置 100 から出力された出力信号を処理する出力信号処理部 208 とを有すればよい。

#### 【0058】

なお、像面位相差 AF を行う固体撮像装置 100 の場合には、固体撮像装置 100 は、

10 焦点検出用画素が出力する信号に基づく焦点検出用信号と撮像信号とを出力信号処理部 208 に出力する。出力信号処理部 208 は、焦点検出用信号を用いて、合焦しているか否かを検出する。また、出力信号処理部 208 は、撮像信号を用いて、画像を生成する。なお、出力信号処理部 208 が合焦していないことを検出した場合には、全体制御・演算部 218 は、合焦する方向に光学系を駆動する。再び出力信号処理部 208 は、固体撮像装置 100 から出力される焦点検出用信号を用いて、再び合焦しているか否かを検出する。以下、固体撮像装置 100 、出力信号処理部 208 、全体制御・演算部 218 は、合焦するまでこの動作を繰り返す。

#### 【0059】

以上のように、本実施形態の撮像システムは、固体撮像装置 100 を適用して撮像動作を行なうことが可能である。第 1 又は第 2 実施形態による固体撮像装置 100 を用いて撮像システムを構成することにより、S/N 比の高い高性能の撮像システムを実現することができる。

20

#### 【0060】

上記実施形態は、本発明を適用しうる幾つかの態様を例示したものに過ぎず、本発明の趣旨を逸脱しない範囲で適宜修正や変形を行うことを妨げるものではなく、第 1 乃至第 4 実施形態の構成を組み合わせることも可能である。例えば、第 3 の実施形態に係る FD 接続トランジスタを第 1 実施形態または第 2 実施形態に係る画素領域に設けても良い。さらに、第 1 乃至第 3 実施形態の固体撮像装置において、第 4 実施形態に係る p 型 MOS トランジスタの構成を採用しても良い。

30

#### 【符号の説明】

#### 【0061】

- 1 画素領域

- 2 OB 画素領域

- 3 開口画素領域

- 4 周回路部

- 5 列信号線

- 10 単位画素

- 12 クリップ回路部

- 14 クリップ回路

- D 1、D 2 フォトダイオード

- M c リセットトランジスタ

- M b 増幅トランジスタ

- M g クリップトランジスタ

- M e FD 接続トランジスタ

40

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 岩根 正晃

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 大下内 和樹

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 橋 高志

(56)参考文献 特開2010-187230(JP, A)

特開2011-097646(JP, A)

特開2009-033316(JP, A)

特開2009-164846(JP, A)

国際公開第2012/144181(WO, A1)

米国特許出願公開第2008/0054320(US, A1)

(58)調査した分野(Int.Cl., DB名)

H04N 5/365

H04N 5/347

H04N 5/359

H04N 5/374

H04N 5/378