#### WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>6</sup> : |    | (11) International Publication Numbe | r: WO 95/32525              |

|---------------------------------------------------------|----|--------------------------------------|-----------------------------|

| H01L 29/76, 29/762, 29/765, 29/775, 29/78               | A1 | (43) International Publication Date: | 30 November 1995 (30.11.95) |

|                                                         |    |                                      |                             |

| ı | (21) International Application Number: | PCT/US95/05848         | (81) Designated States: BY, CA, CN, DE, DK, ES, GB, JP, KP, |

|---|----------------------------------------|------------------------|-------------------------------------------------------------|

|   | ••                                     |                        | KR, MX, NO, RU, SE, SG, UA, European patent (AT, BE,        |

|   | (22) International Filing Date:        | 16 May 1995 (16.05.95) | CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT,         |

| ı |                                        | •                      | SE).                                                        |

US

US

| Not furnished                                       | 10 May 1995 (10.05.95) | US |  |

|-----------------------------------------------------|------------------------|----|--|

|                                                     |                        |    |  |

| (71) Applicant: THE COVERNMENT OF THE UNITED STATES |                        |    |  |

19 May 1994 (19.05.94)

10 May 1995 (10.05.95)

- OF AMERICA, represented by THE SECRETARY OF THE NAVY [US/US]; Naval Surface Warfare Center, Dahlgren Division, Dahlgren, VA 22448 (US).

- (72) Inventors: SANTIAGO, Francisco; 6640 Ducketts Lane, Elkridge, MD 21227 (US). CHU, Tak-Kin; 5106 Elsmere Avenue, Bethesda, MD 20814 (US).

- (74) Agent: BECHTEL, James, B.; Office of Counsel (Patents) Code C222, Naval Surface Warfare Center, Dahlgren Division, Dahlgren, VA 22448 (US).

#### Published With international search report.

(54) Title: BaF2/GaAs ELECTRONIC COMPONENTS

#### (57) Abstract

(30) Priority Data: 08/246,206

Not furnished

Metal insulator semiconductor field effect transistor (MISFETs), charged coupled devices (CCDs), and capacitors based on an epitaxial barium fluoride/gallium arsenide reaction product layer (32) deposited on a single crystal gallium arsenide substrate (20) and a single crystal barium fluoride insulator layer (34) deposited directly on the reaction product layer.

# FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| ΑT   | Austria                  | GB     | United Kingdom               | MR | Mauritania               |

|------|--------------------------|--------|------------------------------|----|--------------------------|

| AU   | Australia                | GE     | Georgia                      | MW | Malawi                   |

| BB   | Barbados                 | GN     | Guinea                       | NE | Niger                    |

| BE · | Belgium                  | GR     | Greece                       | NL | Netherlands              |

| BF   | Burkina Faso             | HU     | Hungary                      | NO | Norway                   |

| BG   | Bulgaria                 | IE     | Ireland                      | NZ | New Zealand              |

| BJ   | Benin                    | IT     | Italy                        | PL | Poland                   |

| BR   | Brazil                   | JP     | Japan                        | PT | Portugal                 |

| BY   | Belarus                  | KE     | Kenya                        | RO | Romania                  |

| CA   | Canada                   | KG     | Kyrgystan                    | RU | Russian Federation       |

| CF   | Central African Republic | KP     | Democratic People's Republic | SD | Sudan                    |

| CG   | Congo                    |        | of Korea                     | SE | Sweden                   |

| CH   | Switzerland              | KR     | Republic of Korea            | SI | Slovenia                 |

| CI   | Côte d'Ivoire            | KZ     | Kazakhstan                   | SK | Slovakia                 |

| CM   | Cameroon                 | LI     | Liechtenstein                | SN | Senegal                  |

| CN   | China                    | LK     | Sri Lanka                    | TD | Chad                     |

| CS   | Czechoslovakia           | LU     | Luxembourg                   | TG | Togo                     |

| CZ   | Czech Republic           | LV     | Latvia                       | ТJ | Tajikistan               |

| DE   | Germany                  | MC     | Monaco                       | TT | Trinidad and Tobago      |

| DK   | Denmark                  | MD     | Republic of Moldova          | UA | Ukraine                  |

| ES   | Spain                    | MG     | Madagascar                   | US | United States of America |

| FI   | Finland                  | ML     | Mali                         | UZ | Uzbekistan               |

| FR   | France                   | MN     | Mongolia                     | VN | Viet Nam                 |

| GA.  | Gahon                    | 1721 1 |                              |    |                          |

WO 95/32525 PCT/US95/05848

# BaF<sub>2</sub>/GaAs ELECTRONIC COMPONENTS

5

## CROSS REFERENCE TO RELATED APPLICATION

This application is a continuation-in-part of copending United States patent application Serial No. 08/246,206 filed on May 19, 1994.

#### **BACKGROUND OF THE INVENTION**

Materials used in semiconductor devices must have good semiconducting properties, good electron mobility, and the ability to host an epitaxial insulating material. Several materials are available which have good semiconducting properties and good electron mobilities but which are unsuitable because a good epitaxial insulator cannot be formed on them. Silicon, however, is widely used in semiconductor devices because epitaxial silicon dioxide forms naturally on silicon and silicon dioxide is an insulator. The disadvantage of silicon is that its mobility is not as high as in other semiconductors and silicon dioxide is not the strongest insulator available. This means that compromises in speed and performance are made when silicon is used in electronic devices.

Gallium arsenide (GaAs) is also a semiconductor and is used in some electronic

applications. A device made out of GaAs would be faster than the same device made out

of silicon because GaAs has an electron mobility that is considerably higher than that of

silicon. Unfortunately, there is no native insulating oxide suitable for GaAs electronic

devices.

Several materials have been used to provide insulating films on III-V compound semiconductor devices. Some of these films were previously used on silicon semiconductor devices. Examples include SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, and P<sub>2</sub>O<sub>3</sub> films. New films

10

have also been developed specifically for the III-V compound semiconductors. For instance, A.J. Shuskus (U.S. Patent No. 4,546,372) developed an essentially oxygen-free, amorphous, phosphorous-nitrogen glass passivating film for III-V compound semiconductors. Similarly, J. Nishizawa et al. (U.S. Patent No. 4,436,770) disclose new gallium oxynitride and aluminum oxynitride insulating films for III-V compound semiconductors. These materials have found only limited application.

It would be useful to provide a new insulating material in gallium arsenide circuit elements which would provide advantages such as greater insulation and a high-break down voltage.

#### SUMMARY OF THE INVENTION

Accordingly, an object of this invention is to provide gallium arsenic circuit elements having high breakdown voltages.

Another object is to provide new, faster gallium arsenide circuit elements.

A further object of this invention is to provide new, improved gallium arsenide

15 metal insulator semiconductor field effect transistors (MISFETs).

Yet another object of this invention is to provide new, improved gallium arsenide charge coupled devices (CCDs).

Yet a further object of this invention is to provide effective capacitors for gallium arsenide integrated circuits.

These and other objects of this invention are accomplished by providing:

gallium arsenide metal insulator semiconductor field effect transistors (MISFETs),

charge couple devices (CCDs), and integrated circuit capacitor which are based on an

insulator that is a single crystal epitaxial layer of barium fluoride grown or deposited

directly onto a single crystal gallium arsenide substrate wherein the barium fluoride layer

WO 95/32525 PCT/US95/05848

3

is separated from the gallium arsenide substrate only by a thin (~12Å) layer of barium fluoride/gallium arsenide reaction product formed during the barium fluoride deposition process. The single crystal gallium arsenide substrate may be a wafer or epitaxial layer of gallium arsenide or a gallium arsenic based semiconductor alloy or a heterostructure of 5 super-lattice made of a combination of gallium arsenic based alloys.

## BRIEF DESCRIPTION OF THE DRAWINGS

These and other features, aspects, and advantages of the present invention will become better understood with regard to the following description, appended claims, and accompanying drawings where:

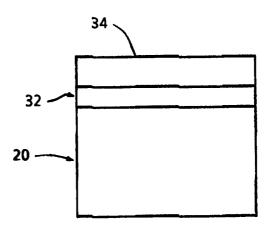

- 10 FIG. 1 is a schematic drawing of a barium fluoride/gallium arsenide epitaxial structure;

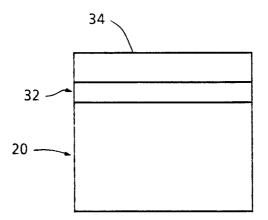

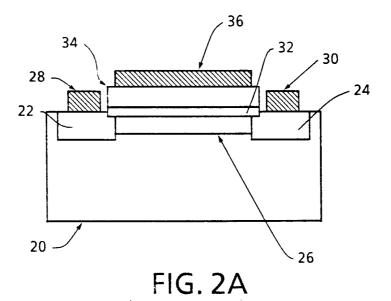

- FIG. 2A is a schematic drawing of a depletion mode metal insulator semiconductor field effect transistor (MISFET) containing the epitaxial structure of FIG. 1;

- FIG. 2B is a schematic drawing of an enhancement mode MISFET containing the 15 epitaxial structure of FIG. 1;

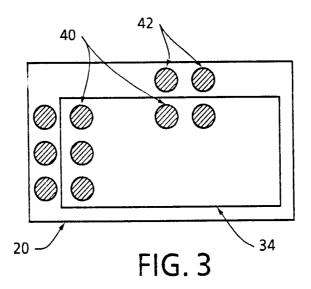

- FIG. 3 is a schematic drawing of a top view of the test set up used in example 6 to measure the capacitance and the breakdown voltage of (100) oriented single crystal epitaxial barium fluoride film; and

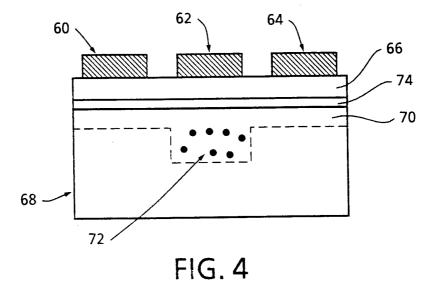

- FIG. 4 is a schematic of a charge coupled device (CCD) containing of the epitaxial 20 structure of FIG. 1.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

The present invention is directed to the use of single crystal epitaxial layers of barium fluoride as improved insulators in gallium arsenide circuit devices such as metal insulator semiconductor field effect transistors (MISFETs), charge couple devices

4

(CCDs), and circuit capacitors. The single crystal epitaxial barium fluoride insulator layer is grown directly onto the clean single crystal gallium arsenide substrate and has the same crystal orientation as the substrate. The term single crystal gallium arsenide substrate includes gallium arsenide single crystal wafers, gallium arsenide epitaxial layers 5 commonly known as epilayers on gallium arsenide single crystal wafers, doped gallium arsenide epilayers on gallium arsenide single crystal wafers, epilayers of alloys of gallium arsenide (for example, gallium aluminum arsenide, gallium indium arsenide, etc.) on gallium arsenide single crystal wafers, heterostructures of super-lattice made of combinations of alloys of gallium arsenide on gallium arsenide single crystal wafers, 10 doped or undoped gallium arsenide epilayers on any suitable substrate materials, heterostructures of super-lattice made of combinations of alloys of gallium arsenide on a suitable substrate material. The barium fluoride is deposited in ultrahigh vacuum at a rate and temperature that allows the barium fluoride to react with the gallium arsenide to form a uniform single crystal epitaxial layer of barium fluoride/gallium arsenide reaction 15 product which is one or two monolayers (about 12 Å) thick. The reaction product layer provides a surface upon which the single crystal epitaxial layer of barium fluoride will then deposit in the same crystal orientation as the underlying gallium arsenide substrate.

Single crystal epitaxial barium fluoride film is formed by exposing a clean, hot single crystal gallium arsenide substrate to barium fluoride vapor in ultrahigh vacuum environment with low background pressure. The single crystal gallium arsenide substrate bulk stoichiometry may be balanced, gallium rich, or arsenic rich. The single crystal gallium arsenide substrate may be doped or undoped. However because the single crystal gallium arsenide substrate is heated at from 500°C to 700°C for substantial periods of time during the BaF<sub>2</sub> deposition, some doping operations may have to be done after the

barium fluoride deposition to alter the doping profile of the doped areas. The single crystal gallium arsenide substrate may have any of the conventional orientations including (100), (111), and their equivalents. In the experiments and examples we used commercial standard electronic grade polished and etched (100) and (111) oriented crystal wafers.

The commercial standard grade single crystal gallium arsenide substrate wafers come with a polycrystalline oxide passivation layer that must be removed. The presence of the polycrystalline passivation layer can be detected by analytical techniques like x-ray photoelectron spectroscopy (XPS) and reflective high energy electron diffraction (RHEED). The passivation layer will show oxygen in the XPS spectrum and a RHEED diffraction pattern that shows scattered dots and concentric circles. Removal of the passivation layer leaves the bare gallium arsenide surface whose smoothness is confirmed by the RHEED pattern that shows ordered spots connected with streaks and the absence of oxygen in the XPS spectrum. Conventional methods for removing the passivation layer may be used. A preferred method is be annealing the gallium arsenide in a vacuum.

In the Examples, the single crystal gallium arsenide wafers were annealed in a VG Semicon V8OH deposition chamber for one hour at 600°C in a vacuum of better than 1 x 10°9 millibar.

A critical part of this invention is the formation of a thin, uniform, single crystal, epitaxial layer of barium fluoride/gallium arsenide reaction product on the surface of the single crystal gallium arsenide substrate. The barium fluoride/gallium arsenide reaction product is formed by exposing a clean, hot single crystal gallium arsenide substrate to barium fluoride vapor in ultrahigh vacuum. The temperature of the single crystal gallium arsenide substrate and the barium fluoride vapor flux rate are adjusted to allow the complete formation of the uniform reaction product layer before a substantial amount of

6

barium fluoride can be deposited. The thickness of the barium fluoride/gallium arsenide reaction product layer is self limiting. After one or two monolayers (about 12Å) of the uniform reaction product layer is formed, the barium fluoride deposits as a single crystal epitaxial layer of barium fluoride on the reaction product layer. If the barium fluoride is deposited too rapidly before a uniform, single crystal epitaxial layer of barium fluoride/gallium arsenide reaction product is completely formed, epitaxial growth of barium fluoride will occur in those places where the reaction product is first completed and an three dimensional island mode of barium fluoride growth will result. Channels between the barium fluoride islands present paths of conduction that defeat the insulative properties of the barium fluoride. This problem is avoided when, according to this invention, care is taken to slowly deposit barium fluoride initially so that a uniform, single crystal, epitaxial layer of reaction product is formed before substantial barium fluoride epitaxial formation begins. When this care is taken, the barium fluoride will deposit as a uniform, single crystal, epitaxial layer which is an excellent insulator.

15 The preferred method of producing the barium fluoride/gallium arsenide reaction layer on the single crystal gallium arsenide substrate is illustrated by examples 1 and 4. A standard commercial grade single crystal gallium arsenide crystal wafer is placed in a standard substrate heater in a commercial molecular beam epitaxial (MBE) deposition chamber model Semicon V8OH made by Vacuum Generators. The chamber is evacuated to a background pressure of preferably less than 10<sup>-8</sup> millibars, more preferably less than 10<sup>-9</sup> millibars, and still more preferably less than 10<sup>-10</sup> millibars and is trapped with liquid nitrogen. The single crystal gallium arsenide wafer is heated for about an hour under vacuum at a heater temperature of 600°C to remove the polycrystalline oxide passivation layer from the single crystal gallium arsenide surface. Barium fluoride is then vapor

deposited at a rate of 2.5Å per minute onto the clean, hot single crystal gallium arsenide substrate (600°C heater temperature). The barium fluoride deposition was continued until the single crystal gallium arsenide reflective high energy electron diffraction (RHEED) pattern gives way to the epitaxial barium fluoride RHEED pattern. This takes 5 about 5 minutes indicating that the barium fluoride/gallium arsenide reaction product layer is about 12Å thick after which the single crystal epitaxial barium fluoride layer is deposited. If the single crystal gallium arsenide substrate surface has a (100) crystal orientation, the single crystal epitaxial barium fluoride layer will have a three dimensional (100) oriented structure as shown by RHEED pattern. On the other hand, if the single 10 crystal gallium arsenide substrate surface has a (111) crystal orientation, the single crystal epitaxial barium fluoride layer will have a two dimensional (111) oriented structure as shown by RHEED pattern. The rate of deposition of barium fluoride must be slow enough to allow the complete formation of the uniform, single crystal, epitaxial barium fluoride/gallium arsenide reaction product layer before substantial amounts of barium 15 fluoride are deposited on the reaction product layer. Example 3 illustrates that when barium fluoride is deposited at a rate of 25Å per minute at 600°C (heater temperature) from the beginning, the barium fluoride layer will grow as three dimensional islands with current conducting channels in between. In contrast, example 1 shows that a barium fluoride deposition rate of  $10\text{\AA}$  per minute at  $600^{\circ}\text{C}$  (heater temperature) produces a 20 uniform, single crystal, epitaxial barium fluoride/gallium arsenide reaction product layer upon which a uniform, single crystal, epitaxial layer of barium fluoride is formed. Nevertheless, to assure the best quality, it is preferable to deposit the barium fluoride at a rate of from 1 to 5 Å per minute and more preferably at from 2 to 3 Å per minute, and most preferably at about 2.5Å per minute. At a deposition rate of 2.5Å per minute the

uniform, single crystal epitaxial barium fluoride/gallium arsenide layer is formed in about 1 minute. Finally, the temperature given is the substrate heater temperature. As shown by example 1, the substrate is at a somewhat lower temperature. This is true for other

commercial substrate heaters and is understood by those of ordinary skill in this art.

Moreover, heater temperatures over the range of from 500°C to 700°C produce the same uniform, single crystal, epitaxial barium fluoride/gallium arsenide reaction product layer. Substrate heater temperature ranges are preferably from 500°C to 700°C, more preferably from 550°C to 650°C and still more preferably from 575°C to 625°C, and most preferably at about 600°C. At heater temperatures near the lower end of the range, the deposition rate is decreased to permit the complete formation of the reaction layer before a substantial amount of barium fluoride is deposited.

The barium fluoride/gallium arsenide reaction product layer is too thin (about 12Å) for a determination of the actual structure and stoichiometric composition to be made. However, the same reaction product is consistently produced even at different substrate heater temperatures over the range of 500°C to 700°C. Moreover, the reaction product can be characterized by a number of physical properties. First, the RHEED pattern of the reaction product is similar to that of BaF<sub>2</sub> (same symmetry, different spot shapes). Next, XPS results indicate lower Ba 3d bonding energies than those of BaF<sub>2</sub>. Most important, uniform single crystal, epitaxial barium fluoride is deposited on single crystal gallium arsenide substrates that are coated with a uniform, epitaxial barium fluoride/gallium arsenide reaction product layer under conditions that would have produced amorphous or polycrystalline barium fluoride on a bare, clean single crystal arsenide substrate without the reaction product layer. It is the deposition of the uniform single crystal, epitaxial barium fluoride layer that confirms that the desired reaction product layer is present.

X-ray photoelectron spectroscopy (XPS) analyses show that the uniform, single crystal, epitaxial barium fluoride/gallium arsenide reaction product layer is free of fluorine (fluorides). This indicates that the reaction mechanism involves the breaking of the barium-fluorine bonds which allows the fluorine to escape or be removed and the 5 barium to react with the gallium arsenide surface. Any barium compound in which the barium-anions bonds are broken under the above process reaction conditions should produce the same reaction product as barium fluoride does. Examples of suitable substitute barium compounds for barium fluoride include barium chloride (BaCl<sub>2</sub>), barium iodide (BaI<sub>2</sub>), barium bromide (BaBr<sub>2</sub>), barium fluochloride (BaF<sub>2</sub>•BaCl<sub>2</sub>), barium fluobromide (BaF<sub>2</sub>•BaBr<sub>2</sub>), barium hydride (BaH<sub>2</sub>), and barium peroxide (BaO<sub>2</sub>). However, using a compound other than barium fluoride to produce the uniform reaction product layer is less desirable than using barium fluoride. First, it requires that an additional material vapor source be added with the resulting increase in complexity and cost of the manufacturing system. Second, a step must be added to the process to remove 15 unreacted barium compound which would be an impurity in the final barium fluoride insulator structure. This can be done by removing all vapor sources and continuing to heat the coated substrate at the same temperature in the same vacuum until substantially all the unreacted barium compound has been removed. Third, any unreacted barium compound that remains will be an impurity in the final product. These problems are avoided when barium fluoride is used to produce the reaction product. However the uniform, single crystal reaction product layer is produced, it provides the surface onto which a uniform, single crystal, epitaxial barium fluoride insulator layer is deposited.

Once the uniform, single crystal, epitaxial barium fluoride/gallium arsenide reaction product layer has been formed on the single crystal gallium arsenide substrate, the

deposition of a uniform, single crystal, epitaxial barium fluoride insulator layer becomes simple. The rate of deposition of barium fluoride is no longer as critical. For instance, example 4 shows that barium fluoride deposited at a rate of about 50Å per minute (20 X 2.5Å per minute) produces a uniform, single crystal epitaxial barium fluoride layer after 5 the reaction layer has been form. This is in direct contrast with example 3 where barium fluoride deposited at 25Å per minute at 600°C onto a bare single crystal gallium arsenide substrate produces a barium fluoride layer having three dimension island growth with channels in between. Recently, it has been discovered that uniform, single crystal epitaxial barium fluoride can be formed by depositing barium fluoride vapor on uniform, 10 epitaxial barium fluoride/gallium arsenide reaction product coated substrates at temperatures of 400°C, 300°C, and room temperature at deposition rates of 50Å per minute. The crystal orientation of the uniform, single crystal epitaxial barium fluoride layer is the same as that of the single crystal gallium arsenide substrate. For example uniform (100) oriented single crystal epitaxial barium fluoride layers are deposited on 15 (100) oriented single crystal gallium arsenide substrates and uniform (111) oriented single crystal epitaxial barium fluoride layers are deposited on (111) single crystal gallium arsenide substrates. This means that the intervening barium fluoride/gallium arsenide reaction product layer is uniform and of the same crystal orientation as the single crystal gallium arsenide substrate.

After the uniform epitaxial barium fluoride/gallium arsenide reaction product layer is formed, the vacuum is maintained at a background pressure of preferably less than 10<sup>-8</sup> millibars, more preferably less than 10<sup>-9</sup> millibars, and still more preferably less than 10<sup>-10</sup> millibars. The barium fluoride is deposited at a rate of preferably 1 to 100Å per minute, more preferably 1 to 50Å per minute, and still more preferably 1 to 25Å per minute.

Single crystal epitaxial layers of barium fluoride grown at temperatures above 500°C contain small amounts of gallium on the order of 1 to 50 ppm. We have found that these traces of gallium do not adversely affect the insulative properties of the barium fluoride layer. As illustrated by example 5, gallium containing barium fluoride (1800Å thick) produced at 600°C has a capacitance of 48.0 ± 2.0 pF, an average breakdown voltage of 944,000 V/cm, and a dielectric constant of ~7.5 which is close to that of bulk barium fluoride. Depositing barium fluoride on the uniform epitaxial layer of barium fluoride/gallium arsenide reaction product at temperatures of 400°C or lower produces a single crystal epitaxial barium fluoride layer that is free of gallium. However, the insulating properties of the gallium-containing and the gallium-free barium fluoride layers are the same. Therefore the term barium fluoride layer as used in describing the improved devices (capacitors, MISFETs, CDDs, etc.) of this invention includes both gallium-containing and gallium free barium fluoride.

FIG. 1 is a schematic drawing of a cross section of a basic structure comprising a

15 single crystal gallium arsenide semiconductor substrate 20, a uniform, epitaxial layer of

the barium fluoride/gallium arsenide reaction product 32 covering a portion of the surface

of the single crystal gallium arsenide substrate 20, and a uniform, single crystal epitaxial

barium fluoride insulator layer 34 which was deposited on the uniform epitaxial barium

fluoride/gallium arsenide reaction product layer 32. The uniform, epitaxial barium

20 fluoride/gallium arsenide reaction product layer 32 is about 12Å thick. For electronic

devices the uniform, single crystal epitaxial barium fluoride insulator layer 34 will be

from about 150 to 1000Å thick, but layers up to 2500Å are easy to produce. In practice,

the electrical properties of the thin barium fluoride/gallium arsenide reaction product layer

32 may be ignored and the structure may simply be considered to be a single crystal

epitaxial layer of barium fluoride 34 deposited on the single crystal gallium arsenide substrate. This basic structure can be used to make integrated circuit capacitors, metal insulator semiconductor field effect transistors (MISFETS), charge couple devices (CCDs), and other types of gallium arsenide electronic devices requiring a metal insulator semiconductor junction.

A structure of the type shown in FIG. 1 can be used as the dielectric portion of a gallium arsenide semiconductor integrated circuit capacitor. Epitaxial barium fluoride is formed on the gallium arsenide to provide the dielectric insulator element of the capacitor and 2 metal electrodes are deposited on opposite surfaces of the epitaxial barium fluoride to form a metal insulator metal (MIM) integrated circuit capacitor. Similarly, by depositing one metal on top of the single crystal epitaxial barium fluoride layer and another electrode on the gallium arsenide semiconductor a metal insulator semiconductor (MIS) capacitor can be produced. A similar procedure can be used to produce an semiconductor insulator semiconductor (SIS) capacitor.

The basic barium fluoride epitaxial insulator layer 34 single crystal gallium arsenide semiconductor substrate 20 structure shown in FIG. 1 can also be used as the basis of an improved gallium arsenide metal insulator semiconductor field effect transistor (MISFET). The element may be used to make depletion mode MISFETs as well as enhancement mode MISFET's. This will include n-channel depletion mode MISFET's p-channel depletion mode MISFET's, n-channel enhancement mode MISFET's, and p-channel enhancement mode MISFET's. FIG. 2A is a schematic drawing representing a depletion mode MISFET according to this invention. Shown are a single crystal gallium arsenide semiconductor substrate 20 which has been doped to produce a source region 22, a drain region 24, and a channel region 26 all of the same carrier type. The channel

region 26 connects the source region 22 to the drain region 24. An ohmic (metal) source electrode 28 is deposited onto the source region 22 and an ohmic (metal) drain electrode 30 is deposited onto the drain region 24. An insulator epitaxial barium fluoride layer 34 is deposited on the surface of the single crystal gallium arsenide semiconductor substrate 20 over the channel region 26. A metal gate electrode 36 is deposited onto the barium fluoride epitaxial layer 34 so that the barium fluoride layer 34 insulates the gate electrode 36 from the channel region 26. The thin barium fluoride/gallium arsenide reaction product zone 32 is shown between the barium fluoride epitaxial layer 34 and the channel region 26 of the single crystal gallium arsenide semiconductor substrate 20. The reaction 10 product zone 32 will not significantly affect the operation of the MISFET device. FIG. 2B is a schematic drawing representing an enhancement mode MISFET according to this invention. The labeled parts are the same as in FIG. 2A except that the channel region 26 is doped with a different carrier type than that of the source region 22 and the drain region 24.

The relatively high temperature (500°C or above) of the present process, may require that certain doping steps be performed after the barium fluoride epitaxial layer has been grown. However, the single crystal gallium substrate under the barium fluoride layer may be doped by using conventional ion beam implantation techniques. The dopant ions will pass through the barium fluoride layer and be implanted in the single crystal gallium arsenide substrate will then be annealed to diffuse the dopant ions in the single crystal gallium arsenide substrate. For example, a MISFET device may be produced by combining the present process within beam implantation as follows. First, a barium fluoride epitaxial crystal insulator layer is grown on a single crystal gallium arsenide substrate according to the process of this invention.

Holes are left in the barium fluoride film for source and drain regions. The source and drain regions are then doped according to conventional techniques. metal electrodes are then deposited onto the source and drain regions. Next an ion beam is used to implant dopant ions through the barium fluoride film into the channel region in the single crystal gallium arsenide substrate. The metal electrodes protect the source and drain regions from the ion beam. The single crystal gallium arsenide substrate is annealed to diffuse the ion implanted dopant to complete the doping of the channel region.

The process and products of the present invention are designed to be used to produce large scale integrated circuits. For example, this includes large scale computer logic and control circuit arrays containing many depletion mode MISFETS, enhancement mode MISFETs, MIM capacitors, etc. It also includes large scale memory arrays containing many charge couple devices and associated circuitry.

FIG. 4 is a schematic drawing representing a charge coupled device (CCD) according to this invention. Shown is a p-type single crystal gallium arsenide wafer 68 with or without an epitaxial layer of single crystal gallium arsenide. An insulator barium fluoride epitaxial layer 66 is deposited onto the gallium arsenide wafer 68. The thin barium fluoride/gallium arsenide reaction product layer 74 is shown between the barium fluoride epitaxial layer 66 and the gallium arsenide wafer 68. The reaction product layer 74 will not significantly affect the operation of the charge coupled device. Metal gate electrodes 60, 62, and 64 are deposited onto the barium fluoride epitaxial layer 66 so that the barium fluoride layer 66 insulates the metal gate electrodes 60, 62, and 64 from the p-type single crystal gallium arsenide wafer 68. The metal gate electrodes 60, 62, and 64 serve as gates for the charge transfer signals. When gate 62 has a higher (more positive) voltage than gates 60 and 64, the charges 72 are concentrated in region 70 just below gar

62 which serves as a charge storage. When either gate 60 or 64 is pulsed to a higher (more positive) voltage than gate 62 the charge 72 will be transferred to the pulsed gate. The device shown in FIG. 4 is just an illustrative example of how to use the present invention in charge couple devices, different schemes and layouts can be used for the charge couple devices.

Finally, a useful intermediate product is produced by forming the uniform, thin coating of barium fluoride/gallium arsenide reaction product on a single crystal gallium arsenide substrate according to the method described above, and then removing the barium fluoride vapor source and continuing to heat the substrate in the vacuum until any unreacted barium fluoride is removed from the coating. Single crystal epitaxial barium fluoride layers can then be deposited on the barium fluoride/gallium arsenide reaction product layer by the methods described above. Moreover, by depositing the barium fluoride vapor at a temperature of from room temperature to 400°C, or preferably from room temperature to 300°C with the other conditions (deposition rate, vacuum) being the same, a uniform, single crystal epitaxial barium fluoride insulator layer is formed which is free of gallium ions.

As stated above, the term single crystal gallium arsenide substrate preferably includes doped or undoped gallium arsenide single crystal wafers, doped or undoped gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, doped or undoped epitaxial layers of gallium arsenide alloys (for example, gallium aluminum arsenide, gallium indium arsenide, etc.) on single crystal gallium arsenide wafers, heterostructures of super-lattice made of combinations of gallium arsenide alloys on gallium arsenide single crystal wafers, doped or undoped gallium arsenide single crystal epitaxial layers on suitable substrate materials, doped or undoped epitaxial layers of

gallium arsenide alloys on suitable substrate materials, and heterostructures of super-lattice made of combinations of gallium arsenide alloys on suitable substrate materials. More preferably the single crystal gallium arsenide substrate includes doped or undoped gallium arsenide single crystal wafers, doped or undoped gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, and doped or undoped gallium arsenide single crystal epitaxial layers on suitable substrate materials. The gallium arsenide alloys include those that are conventionally used in semiconductor devices.

Gallium arsenide alloy that are rich in gallium are preferred. The suitable substrate materials include materials that provide physical support for a thin epitaxial layer of gallium arsenide or gallium arsenide alloys without chemically or electrically interfering with the operation of the epitaxial layer. For example, a thin single crystal epitaxial layer of gallium arsenide on a hybrid semiconductor device or on a chemically inert, electrically insulating circuit board structure. Thus, the single crystal gallium arsenide substrate need not be a wafer but rather can be a thin epitaxial layer requiring support by a non-gallium

## **EXAMPLE 1**

The barium fluoride film was grown on single crystal gallium arsenide using a standard procedure called molecular beam epitaxy (MBE). The film was grown inside a commercial MBE deposition chamber made by Vacuum Generators (model V80-M). The MBE system above has both Knudsen cells and e-beam sources and a 30 kV RHEED system to monitor the film structure during film deposition. The substrate heater is capable of holding up to 3 inch diameter wafers and control the substrate temperature to within  $\pm 0.1$ °C at 1000°C and a maximum deviation of the temperature across the substrate of  $\pm 0.1$ °C. The temperature is controlled by using a thermocouple located

inside the substrate heater. All temperatures quoted here are the substrate heater thermocouple readings. Independent measurements of the sample temperatures done using an optical pyrometer shows that when the thermocouple monitoring the substrate heater read 750.0°C the substrate temperature was closer to 710.0°C  $\pm$  0.5°C (0.5°C is the 5 accuracy of the optical pyrometer). Differences between the substrate temperature and the thermocouple readings change with temperature. However reproducibility in the thermocouple readings results in reproducibility in the growth conditions. The pressure inside the MBE system is kept below 3.0X10<sup>-11</sup> mbars most of the time. When the substrate and Knudsen cells containing the source are heated to the conditions for deposition the pressure inside the chamber will rise to a pressure not above 1.0X10<sup>-10</sup> mbars. The single crystal gallium arsenide substrate used was a commercial (100) oriented 2 inch diameter wafer with a carrier concentration of 3.0X10<sup>18</sup> carriers/cm<sup>3</sup> and an arsenic to gallium concentration ratio of 50/50. The wafer was polished and etched using standard industry procedures. Before deposition of the film the gallium arsenide 15 crystal was cleaned by standard heat treatment in ultrahigh vacuum. Then the gallium arsenide crystal wafer was heated at 600°C until the electron diffraction pattern looked "streaky". This took about 60 minutes.

Once the gallium arsenide was heat treated the substrate crystal (GaAs) was kept at 600°C ± 1°C. The barium fluoride was heated in a standard Knudsen cell inside the

MBE system. The cell containing the barium fluoride was heated until 1050°C ± 1°C.

This condition created a flux rate of approximate 10<sup>14</sup> atoms/(cm<sup>2</sup>xsec). When a consistent flux was obtained, deposition of barium fluoride was achieved by opening shutters located in front of both the barium fluoride source and the gallium arsenide crystal. Deposition for 60 minutes yielded a barium fluoride film approximately 600Å

thick. After the desired barium fluoride film thickness was achieved (1800Å) the shutters were closed and both the source and the gallium arsenide were cooled down to room temperature (25°C) using a cooling rate of 0.5°C per second. Once the gallium arsenide crystal with the barium fluoride film reached room temperature it was taken out of the MBE system. A (100) oriented single crystal epitaxial film of barium fluoride was produced.

#### EXAMPLE 2

The procedure of example 1 was repeated using a commercial standard electronic grade polished and etched (111) oriented single crystal gallium arsenide wafer. In this example the single crystal gallium arsenide wafer had the same carrier concentration density (3.0X10<sup>18</sup> carriers/cm<sup>2</sup>) but the ratio of As to Ga was 52/48. A (111) oriented single crystal epitaxial film of barium fluoride was produced.

#### **EXAMPLE 3**

The procedure of example 1 was repeated except the rate of barium fluoride

15 deposition was increased to 25Å per minute. The resulting barium fluoride layer was

unsuitable as an insulator because three dimensional island growth had occurred with

channels between the islands.

#### **EXAMPLE 4**

The procedure of example 1 was repeated except that the barium fluoride deposition rate was only 2.5Å per minute and was stopped when the GaAs RHEED pattern gave way to a three dimensional epitaxial BaF<sub>2</sub> RHEED pattern. This indicates the completion of the epitaxial layer of barium fluoride/gallium arsenide reaction product. This happened in less than 5 minutes.

5

The presence of a barium fluoride/gallium arsenide reaction product layer is demonstrate by the XPS spectra which showed new lines near the Ba 3d 3/2 and 5/2 peaks as the barium fluoride was evaporated off. These peaks do not correspond to  $BaF_2$ . The reaction layer is not volatile at 600°C in vacuum.

Barium fluoride was then deposited at a rate of about 50Å per minute onto the barium fluoride/gallium arsenide reaction product layer to produce a uniform single crystal epitaxial layer of barium fluoride on the substrate. This contrasts with Example 3 where barium fluoride deposition at a ratio of 25Å per minute onto a clean (no reaction product layer) gallium arsenide surface produced a barium fluoride layer containing three dimensional islands and channels.

## **EXAMPLE 5**

The procedure of example 1 was repeated until a (100) oriented single crystal epitaxial film 1800Å thick was produced. FIG. 3 is schematic top view of the test set up shown are an array of 5 (five) gold dots 40 evaporated onto the (100) oriented single crystal epitaxial barium fluoride film 34 and a corresponding array of 5 (five) gold dots 42 evaporated on to the adjoining edge of the (100) oriented single crystal gallium arsenide substrate 20 not exposed to the barium flux. Adjacent gold dots 40 and 42 form pairs that were used in the measurements. Indium-soldered gold wires were attached to the gold dots 40 on the barium film 34 and to the gold dots 42 on the gallium arsenide substrate 20. Capacitance and breakdown voltage measurements were done on all five pairs of adjacent gold dots (electrodes. Result s showed that capacitance values of 48.0 pF between the barium film and the gallium arsenide with a maximum deviation of ± 2.0 pF were obtained. Breakdown fields ranging between 8.5 x 105 and 1.1 x 106 V/cm were

obtained. The dielectric constant was found to be  $\sim$ 7.5, a value close to that of the bulk material.

#### EXAMPLE 6

The procedure of example 1 was repeated except that the barium fluoride deposition

5 rate was only 2.5Å per minute and was stopped when the GaAs RHEED pattern gave way

to a three dimensional epitaxial BaF<sub>2</sub> RHEED pattern. This happened in less than 5

minutes. The substrate temperature was then reduced to 500, 400, and 300°C and held for

30 minutes at each temperature while deposition of BaF<sub>2</sub> at 2.5Å per minute continued.

The RHEED pattern was continuously monitored during this time. Other than a decrease

10 in the spot size and an increase in spot intensity, no change in the RHEED pattern was

detected. After depositing for 30 minutes at 300°C, the BaF<sub>2</sub> source temperature was

raised from 1000°C to 1100°C. The resultant flux gauge reading increased by a factor of

about twenty. (to about 50Å per minute) The RHEED pattern, however, was not affected.

The film was then stored in the deposition chamber for four days. BaF<sub>2</sub> deposition was

resumed with a substrate temperature of 25°C and at the same range of flux gauge

readings. The RHEED pattern remained unchanged.

Obviously, numerous other modifications and variations of the present invention are possible in light of the foregoing teachings. It is therefore to be understood that within the scope of the appended claims the invention may be practiced otherwise than as specifically described.

What is claimed is:

## **CLAIMS**

- 1. An insulator structure comprising:

- A. a single crystal gallium arsenide substrate;

- B. a uniform, epitaxial layer of a barium fluoride/gallium arsenide reaction product covering a portion of the gallium arsenide substrate surface,

wherein the reaction product is characterized by the product of the reaction between barium fluoride vapor and the clean single crystal gallium arsenide substrate surface which is being heated at from 500°C to 700°C in a vacuum of less than 10<sup>-9</sup> millibars background pressure, wherein the barium fluoride vapor flux produces a barium fluoride deposition rate of from 1 to 5Å per minute on the single crystal gallium arsenide substrate surface during the reaction; and

- C. An electrically insulating, single crystal epitaxial layer of barium fluoride which is deposited onto the uniform, epitaxial layer of barium fluoride/gallium arsenide reaction product.

- 2. The insulator of claim 1 wherein the single crystal gallium arsenide substrate surface was heated at from 550°C to 650°C during the formation of the barium fluoride/gallium arsenide reaction product.

- 3. The insulator structure of claim 2 wherein the single crystal gallium arsenide substrate surface was heated at from 575°C to 625°C during the formation of the barium fluoride gallium arsenide reaction product.

2 2

- 4. The insulator structure of claim 1 wherein the barium fluoride was being deposited at a rate of from 2 to 3Å per minute during the formation of the barium fluoride/gallium arsenide reaction product.

- 5. The insulator structure of claim 1 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, epitaxial layers of gallium arsenide alloys on single crystal gallium arsenide wafers, heterostructures of super-lattice made of combinations of gallium arsenide alloys on gallium arsenide single crystal wafers, gallium arsenide single crystal epitaxial layers on suitable substrate materials, epitaxial layers of gallium arsenide alloys on suitable substrate materials, and heterostructures of super-lattice made of combinations of gallium arsenide alloys on suitable substrate materials.

- 6. The insulator structure of claim 5 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, and gallium arsenide single crystal epitaxial layers on suitable substrate materials.

- 7. The insulator structure of claim 6 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers.

- 8. The insulator structure of claim 6 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal epitaxial layers on gallium arsenide single crystal wafers.

- 9. The insulator structure of claim 1 wherein the single crystal gallium arsenide surface has a (100) or equivalent orientation and the uniform epitaxial layer of barium fluoride/gallium arsenide reaction product has the same orientation.

- 10. The insulator structure of claim 9 wherein the single crystal gallium arsenide substrate surface has a (100) orientation.

- 11. The insulator structure of claim 1 wherein the single crystal gallium arsenide surface has a (111) or equivalent orientation and the uniform epitaxial layer of barium fluoride/gallium arsenide reaction product has the same orientation.

- 12. The insulator structure of claim 11 wherein the single crystal gallium arsenide substrate surface has a (111) orientation.

- 13. An improved gallium arsenide metal insulator semiconductor field effect transistor comprising a single crystal gallium arsenide semiconductor substrate having a source, a drain, a channel connecting the source to the drain, and an insulator layer which is deposited onto the channel and which separates the channel from a metal gate electrode which controls the current in the channel, the improvement comprising:

the insulator layer being a single crystal epitaxial layer of barium fluoride which is separated from the single crystal gallium arsenide substrate by only a thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product.

- 14. The metal insulator semiconductor field effect transistor of claim 13 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, epitaxial layers of gallium arsenide alloys on single crystal gallium arsenide wafers, heterostructures of super-lattice made of combinations of gallium arsenide alloys on gallium arsenide single wafers, gallium arsenide single crystal epitaxial layers on suitable substrate materials, epitaxial layers of gallium arsenide alloys on suitable substrate materials, and heterostructures of super-lattice made of combinations of gallium arsenide alloys on suitable substrate materials.

- 15. The metal insulator semiconductor field effect transistor of claim 14 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, and gallium arsenide single crystal epitaxial layers on suitable substrate materials.

- 16. The metal insulator semiconductor field effect transistor of claim 15 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers.

- 17. The metal insulator semiconductor field effect transistor of claim 15 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal epitaxial layers on gallium arsenide single crystal wafers.

- 18. The metal insulator semiconductor field effect transistor of claim 13 which is a depletion mode field effect transistor.

- 19. The metal insulator semiconductor field effect transistor of claim 18 which is an n-channel depletion mode field effect transistor.

- 20. The metal insulator semiconductor field effect transistor of claim 18 which is a p-channel depletion mode field effect transistor.

- 21. The metal insulator semiconductor field effect transistor of claim 13 which is an enhancement mode field effect transistor.

- 22. The metal insulator semiconductor field effect transistor of claim 21 which is an n-channel enhancement mode field effect transistor.

- 23. The metal insulator semiconductor field effect transistor of claim 21 which is a p-channel enhancement mode field effect transistor.

- 24. The metal insulator semiconductor field effect transistor of claim 13 wherein the single crystal gallium arsenide substrate surface has a (100) or equivalent orientation and the single crystal epitaxial barium fluoride layer has the same orientation.

- 25. The metal insulator semiconductor field effect transistor of claim 24 wherein the single crystal gallium arsenide substrate surface and the single crystal epitaxial barium fluoride layer both are (100) oriented.

- 26. The metal insulator semiconductor field effect transistor of claim 13 wherein the single crystal gallium arsenide substrate surface has a (111) or equivalent orientation and the single crystal epitaxial barium fluoride layer has the same orientation.

- 27. The metal insulator semiconductor field effect transistor of claim 26 wherein the single crystal gallium arsenide substrate surface and the single crystal epitaxial barium fluoride layer both are (111) oriented.

- 28. The metal insulator semiconductor field effect transistor of claim 13 wherein the thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product is less than 20Å thick.

- 29. The metal insulator semiconductor field effect transistor of claim 28 wherein the thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product is less than 15Å thick.

30. In a metal insulator metal capacitor for gallium arsenide integrated circuits the improvement comprising:

the insulator being a single crystal epitaxial layer of barium fluoride which is separated from a single crystal gallium arsenide substrate by only a thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product.

- 31. The metal insulator metal capacitor of claim 30 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, epitaxial layers of gallium arsenide alloys on single crystal gallium arsenide wafers, heterostructures of super-lattice made of combinations of gallium arsenide alloys on gallium arsenide single wafers, gallium arsenide single crystal epitaxial layers on suitable substrate materials, epitaxial layers of gallium arsenide alloys on suitable substrate materials, and heterostructures of super-lattice made of combinations of gallium arsenide alloys on suitable substrate materials.

- 32. The metal insulator metal capacitor of claim 31 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, and gallium arsenide single crystal epitaxial layers on suitable substrate materials.

- 33. The metal insulator metal capacitor of claim 32 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers.

- 34. The metal insulator metal capacitor of claim 32 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal epitaxial layers on gallium arsenide single crystal wafers.

- 35. An improved gallium arsenide charge couple device comprising a doped single crystal gallium arsenide semiconductor substrate and an array of metal gate electrodes which are separated from the surface of the substrate by an insulator layer, the improvement comprising:

the insulator layer being a single crystal epitaxial layer of barium fluoride which is separated from the doped single crystal gallium arsenide substrate by only a thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product.

36. The charge couple device of claim 35 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, epitaxial layers of gallium arsenide alloys on single crystal gallium arsenide wafers, heterostructures of super-lattice made of combinations of gallium arsenide alloys on gallium arsenide single crystal wafers, gallium arsenide single crystal epitaxial layers on suitable substrate materials, epitaxial layers of gallium arsenide alloys on suitable substrate materials, and heterostructures of super-lattice made of combinations of gallium arsenide alloys on suitable substrate materials.

- 37. The charge couple device of claim 36 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, and gallium arsenide single crystal epitaxial layers on suitable substrate materials.

- 38. The charge couple device of claim 37 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers.

- 39. The charge couple device of claim 37 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal epitaxial layers on gallium arsenide single crystal wafers.

- 40. The charge couple device of claim 35 wherein the single crystal gallium arsenide substrate surface has a (100) or equivalent orientation and the single crystal epitaxial barium fluoride layer has the same orientation.

- 41. The charge couple device of claim 40 wherein the single crystal gallium arsenide substrate surface and the single crystal epitaxial barium fluoride layer both are (100) oriented.

- 42. The charge couple device of claim 35 wherein the single crystal gallium arsenide substrate surface has a (111) or equivalent orientation and the single crystal epitaxial barium fluoride layer has the same orientation.

- 43. The charge couple device of claim 42 wherein the single crystal gallium arsenide substrate surface wherein the single crystal gallium arsenide substrate surface and the single crystal epitaxial barium fluoride layer both are (111) oriented.

- 44. The charge couple device of claim 35 wherein the thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product is less than 20Å thick.

ţ

- 45. The charge couple device of claim 44 wherein the thin, uniform epitaxial layer of barium fluoride/gallium arsenide reaction product is less than 15Å thick.

- 46. A coated substrate comprising:

- A. a single crystal gallium arsenide substrate and

- B. a uniform, epitaxial layer of a barium fluoride/gallium arsenide reaction product covering a portion of the gallium arsenide substrate surface,

wherein the reaction product is characterized by the product of the reaction between barium fluoride vapor and the clean single crystal gallium arsenide substrate surface which is being heated at from 500°C to 700°C in a vacuum of less than 10°9 millibars background pressure, wherein the barium fluoride vapor flux produces a barium fluoride deposition rate of from 1 to 5Å per minute on the single crystal gallium arsenide substrate surface during the reaction, and further wherein the surface of the uniform, epitaxial layer of barium fluoride/gallium arsenide reaction product is substantially free of unreacted barium fluoride after the reaction is completed.

- 47. The coated substrate of claim 46 wherein the single crystal gallium arsenide substrate surface was heated at from 550°C to 650°C during the formation of the barium fluoride/gallium arsenide reaction product.

- 48. The coated substrate of claim 47 wherein the single crystal gallium arsenide substrate surface was heated at from 575°C to 625°C during the formation of the barium fluoride gallium arsenide reaction product.

- 49. The coated substrate of claim 46 wherein the barium fluoride was being deposited at a rate of from 2 to 3Å per minute during the formation of the barium fluoride/gallium arsenide reaction product.

- 50. The coated substrate of claim 46 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers, gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, epitaxial layers of gallium arsenide alloys on single crystal gallium arsenide wafers, heterostructures of super-lattice made of combinations of gallium arsenide alloys on gallium arsenide single crystal wafers, gallium arsenide single crystal epitaxial layers on suitable substrate materials, epitaxial layers of gallium arsenide alloys on suitable substrate materials, and heterostructures of super-lattice made of combinations of gallium arsenide alloys on suitable substrate materials.

- 51. The coated substrate of claim 50 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers,

gallium arsenide epitaxial layers on gallium arsenide single crystal wafers, and gallium arsenide single crystal epitaxial layers on suitable substrate materials.

52. The coated substrate of claim 51 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal wafers.

١,

- 53. The coated substrate of claim 51 wherein the single crystal gallium arsenide substrate is selected from the group consisting of gallium arsenide single crystal epitaxial layers on gallium arsenide single crystal wafers.

- 54. The coated substrate of claim 46 wherein the single crystal gallium arsenide surface has a (100) or equivalent orientation and the uniform epitaxial layer of barium fluoride/gallium arsenide reaction product has the same orientation.

- 55. The coated substrate of claim 54 wherein the single crystal gallium arsenide substrate surface has a (100) orientation.

- 56. The coated substrate of claim 46 wherein the single crystal gallium arsenide surface has a (111) or equivalent orientation and the uniform epitaxial layer of barium fluoride/gallium arsenide reaction product has the same orientation.

- 57. The coated substrate of claim 56 wherein the single crystal gallium arsenide substrate surface has a (111) orientation.

FIG. 1

28 24 24 26 26

FIG. 2B

# INTERNATIONAL SEARCH REPORT

Inernational application No.

PCT/US95/05848

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(6) : HO1L 29/76, 29/762, 29/765, 29/775, 29/78  US CL : 257/192, 194, 392, 410, 24, 26, 27 |                                                                                                                                    |                                                                                                                                    |                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                                                                                                                                     | o International Patent Classification (IPC) or to both                                                                             | national classification and IPC                                                                                                    |                                                         |

| <b></b>                                                                                                                             | LDS SEARCHED                                                                                                                       |                                                                                                                                    |                                                         |

| l ,                                                                                                                                 | ocumentation searched (classification system followed 257/192, 194, 392, 410, 24, 26, 27                                           | by classification symbols)                                                                                                         |                                                         |

| Documentat                                                                                                                          | ion searched other than minimum documentation to the                                                                               | e extent that such documents are included                                                                                          | in the fields searched                                  |

| Electronic d                                                                                                                        | lata base consulted during the international search (na                                                                            | ame of data base and, where practicable                                                                                            | , search terms used)                                    |

| APS SEARCH TERMS: (barium flouride or BaF#)(P)GaAs                                                                                  |                                                                                                                                    |                                                                                                                                    |                                                         |

| C. DOC                                                                                                                              | CUMENTS CONSIDERED TO BE RELEVANT                                                                                                  |                                                                                                                                    |                                                         |

| Category*                                                                                                                           | Citation of document, with indication, where ap                                                                                    | opropriate, of the relevant passages                                                                                               | Relevant to claim No.                                   |

| Υ                                                                                                                                   | Appl. Phys. Lett. Volume. 60,<br>Hung et al, "Epitaxial growth of a<br>on HF-treated Si", pages 201-203                            | lkaline earth fluoride films                                                                                                       | 1-57                                                    |

| Υ                                                                                                                                   | JP, A, 02-266569 (Kitamura) constitution).                                                                                         | 1-17                                                                                                                               |                                                         |

| Υ                                                                                                                                   | US, A, 4,847,666 (Heremans et a document).                                                                                         | 14,15, 44, 45                                                                                                                      |                                                         |

| Y                                                                                                                                   | Semiconductor devices Physics ar see pages 208-210.                                                                                | 6-11                                                                                                                               |                                                         |

| Y                                                                                                                                   | US,A, 5,124,762 (Childs et al) 23 and 2).                                                                                          | 3 June 1992 (see figures 1                                                                                                         | 2-5,38-41                                               |

|                                                                                                                                     |                                                                                                                                    |                                                                                                                                    | :                                                       |

| Furti                                                                                                                               | ner documents are listed in the continuation of Box C                                                                              | See patent family annex.                                                                                                           |                                                         |

| 1                                                                                                                                   | secial categories of cited documents:                                                                                              | "T" later document published after the inte<br>date and not in conflict with the applica<br>principle or theory underlying the inv | ation but cited to understand the                       |

|                                                                                                                                     | be of particular relevance rlier document published on or after the international filing date                                      | "X" document of particular relevance; the                                                                                          | e claimed invention cannot be                           |

| cit                                                                                                                                 | ocument which may throw doubts on priority claim(s) or which is ted to establish the publication date of another citation or other | when the document is taken alone  "Y" document of particular relevance; th                                                         |                                                         |

| *O* do                                                                                                                              | ecial reason (as specified)  cument referring to an oral disclosure, use, exhibition or other  cans                                | considered to involve an inventive<br>combined with one or more other such<br>being obvious to a person skilled in the             | step when the document is h documents, such combination |

|                                                                                                                                     | ocument published prior to the international filing date but later than e priority date claimed                                    | *&* document member of the same patent                                                                                             | family                                                  |

| <del></del>                                                                                                                         | actual completion of the international search                                                                                      | Date of mailing of the international sea                                                                                           | arch report                                             |

| 06 JULY                                                                                                                             | 1995                                                                                                                               | 19 JUL 1995                                                                                                                        |                                                         |

| Name and                                                                                                                            | mailing address of the ISA/US oner of Patents and Trademarks                                                                       | Authorized officer                                                                                                                 |                                                         |

| Box PCT                                                                                                                             | on, D.C. 20231                                                                                                                     | Wael M. FAHMY & Mac                                                                                                                | alund                                                   |

| Facsimile N                                                                                                                         |                                                                                                                                    | Telephone No. (703) 308-4918                                                                                                       |                                                         |