(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5007017号

(P5007017)

(45) 発行日 平成24年8月22日(2012.8.22)

(24) 登録日 平成24年6月1日(2012.6.1)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 27/10   | (2006.01) | HO1L 27/10 | 481  |

| HO1L 27/115  | (2006.01) | HO1L 27/10 | 434  |

| HO1L 21/8247 | (2006.01) | HO1L 27/08 | 102C |

| HO1L 27/088  | (2006.01) | HO1L 29/78 | 371  |

| HO1L 21/8234 | (2006.01) |            |      |

請求項の数 6 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2004-193554 (P2004-193554)

(22) 出願日

平成16年6月30日 (2004.6.30)

(65) 公開番号

特開2006-19373 (P2006-19373A)

(43) 公開日

平成18年1月19日 (2006.1.19)

審査請求日

平成19年6月29日 (2007.6.29)

審判番号

不服2010-26800 (P2010-26800/J1)

審判請求日

平成22年11月29日 (2010.11.29)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 坂井 健志

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 石井 泰之

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 岡崎 勉

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板の第1領域に不揮発性メモリセルを有し、前記半導体基板の第2領域に第1MISFETを有する半導体装置の製造方法であって、

(a) 前記第1領域および前記第2領域の前記半導体基板上に、第1導電膜を形成する工程、

(b) 前記(a)工程の後に、前記第1導電膜上に選択的にフォトトレジスト膜を形成し、前記第1導電膜をパターニングすることで、前記第1領域に前記不揮発性メモリセルのコントロールゲート電極を形成すると共に、前記第2領域に前記第1MISFETのゲート電極を形成する工程、

(c) 前記(b)工程の後に、前記第1領域および前記第2領域の前記半導体基板上に、前記コントロールゲート電極および前記第1MISFETのゲート電極を覆うように、電荷蓄積膜を形成する工程、

(d) 前記(c)工程の後に、前記電荷蓄積膜上に第2導電膜を形成する工程、

(e) 前記(d)工程の後に、前記第2導電膜を異方性エッチングすることで、前記コントロールゲート電極の側壁、および、前記第1MISFETのゲート電極の側壁にサイドウォール状のメモリゲート電極を形成する工程、

(f) 前記(e)工程の後に、前記コントロールゲート電極の一方の側壁に前記メモリゲート電極が残されるように、前記第1領域において前記コントロールゲート電極の他方の側壁の前記メモリゲート電極を除去すると共に、前記第2領域において前記メモリゲート

10

20

電極を除去する工程、

(g) 前記(f)工程の後に、前記第1領域において前記コントロールゲート電極の他方の側壁側の前記電荷蓄積膜を除去すると共に、前記第2領域において前記電荷蓄積膜を除去する工程、

(h) 前記(g)工程の後に、前記第1領域において前記コントロールゲート電極の他方の側壁側の前記半導体基板に第1不純物領域を形成する工程、

(i) 前記(g)工程の後に、前記第1領域において前記メモリゲート電極の側壁側の前記半導体基板に第2不純物領域を形成する工程、

(j) 前記(g)工程の後に、前記第2領域において前記半導体基板に第3不純物領域を形成する工程、

(k) 前記(h)～(j)工程の後に、前記第1領域において前記コントロールゲート電極の他方の側壁、前記メモリゲート電極の側壁、および、前記第1MISFETのゲート電極の側壁に、絶縁膜からなるサイドウォールスペーサを形成する工程、

(l) 前記(k)工程の後に、前記第1領域の半導体基板に、前記第1不純物領域と接続し、且つ、前記第1不純物領域よりも高濃度の第4不純物領域を形成し、前記第1領域の半導体基板に、前記第2不純物領域と接続し、且つ、前記第2不純物領域よりも高濃度の第5不純物領域を形成し、前記第2領域の半導体基板に、前記第3不純物領域と接続し、且つ、前記第3不純物領域よりも高濃度の第6不純物領域を形成する工程、

を有し、

前記(b)工程では、前記コントロールゲート電極の高さを、前記コントロールゲート電極のゲート長方向の長さよりも大きくなるように形成し、

前記(d)工程では、前記第2導電膜として、不純物が導入された多結晶シリコン膜をCVD法によって堆積し、

前記(e)工程では、前記メモリゲート電極の高さを、前記メモリゲート電極のゲート長方向の長さよりも大きくなるように形成することを特徴とする半導体装置の製造方法。

#### 【請求項2】

請求項1記載の半導体装置の製造方法であって、

前記半導体基板の第3領域に、前記第1MISFETよりも高耐圧の第2MISFETを更に有し、

前記(a)工程の前に、前記第1領域において前記コントロールゲート電極下のゲート絶縁膜と、前記第1MISFETのゲート絶縁膜とを同時に形成する工程を有することを特徴とする半導体装置の製造方法。

#### 【請求項3】

請求項1または2記載の半導体装置の製造方法であって、

前記電荷蓄積膜は、第1酸化シリコン膜と、前記第1酸化シリコン膜上に形成された第1窒化シリコン膜と、前記第1窒化シリコン膜上に形成された第2酸化シリコン膜とを含み、

前記第1酸化シリコン膜および前記第2酸化シリコン膜は、ISSG酸化法によって形成され、

前記第1窒化シリコン膜は、CVD法またはALD法によって形成されることを特徴とする半導体装置の製造方法。

#### 【請求項4】

請求項1～3の何れか1項に記載の半導体装置の製造方法であって、

前記(a)工程における前記第1導電膜はアンドープドシリコン膜であり、

前記(a)工程と前記(b)工程との間に、イオン注入によって、前記第1導電膜に不純物を導入する工程を有することを特徴とする半導体装置の製造方法。

#### 【請求項5】

請求項4記載の半導体装置の製造方法であって、

前記第1導電膜に導入された不純物は、n型の導電性を示すことを特徴とする半導体装置の製造方法。

**【請求項 6】**

請求項 1 記載の半導体装置の製造方法であって、

前記第 2 導電膜に導入された不純物は、n 型の導電性を示すことを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、不揮発性半導体記憶装置およびその製造技術に関し、特に、MONOS (Metal Oxide Nitride Oxide Semiconductor) 型トランジスタを有する不揮発性半導体記憶装置の製造に適用して有効な技術に関するものである。

10

**【背景技術】****【0002】**

電気的にデータの書き換えが可能な不揮発性メモリ (Electrically Erasable and Programmable Read Only Memory) の一種として、MONOS (Metal Oxide Nitride Oxide Semiconductor) 膜を用いたスプリットゲート型のメモリセル構造が知られている。

**【0003】**

上記 MONOS 型不揮発性メモリは、メモリセル中の窒化シリコン膜に電荷を蓄積して書き込みを行うので、多結晶シリコン膜からなるフローティングゲートに電荷を蓄積するフラッシュメモリに比べて、

1 ) 離散的に電荷を蓄積するので、データ保持の信頼性に優れている。

20

2 ) 窒化シリコン膜を挟む 2 層の酸化シリコン膜を薄膜化でき、書き込み動作や消去動作を低電圧で行うことができる。

といった利点を備えている。

**【0004】**

MONOS 型不揮発性メモリの消去方式には、BTT (Band-To-Band Tunneling) ホットホール注入方式とトンネリング方式との 2 種類があり、前者については、例えば特許文献 1 (U.S.P. 5,969,383 号公報) に記載があり、後者については、特許文献 2 (特開 2001-102466 号公報) に記載がある。

**【0005】**

BTT ホットホール注入方式は、ソース領域とゲート電極との間に高電圧を印加し、BTT によって発生させたホール (正孔) を窒化シリコン膜中に注入することによって消去を行う。これに対し、トンネリング消去方式は、窒化シリコン膜中に注入した電子を基板またはゲート電極へ引き抜くことによって消去を行う。

30

【特許文献 1】 U.S.P. 5,969,383 号公報

【特許文献 2】 特開 2001-102466 号公報

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

本発明者が開発中の MONOS 型不揮発性メモリは、コントロールトランジスタとメモリトランジスタとでメモリセルを構成している。このメモリセルは、半導体基板の主面の p 型ウエル上にゲート絶縁膜を介して形成されたコントロールゲートと、一部が前記コントロールゲートの一方の側壁に形成されると共に、他部が前記第 1 p 型ウエル上に形成された電荷蓄積層と、前記コントロールゲートの前記一方の側壁に形成され、前記電荷蓄積層の前記一部を介して前記コントロールゲートと電気的に分離されると共に、前記電荷蓄積層の前記他部を介して前記第 1 p 型ウエルと電気的に分離されたメモリゲートと、前記第 1 p 型ウエルの表面に形成され、一端が前記コントロールゲートの近傍に配置された第 2 導電型のドレイン領域と、前記第 1 p 型ウエルの表面に形成され、一端が前記メモリゲートの近傍に配置された第 2 導電型のソース領域とを有している。電荷蓄積層は、2 層の酸化シリコン膜とそれらに挟まれた窒化シリコン膜とで構成されている。

40

**【0007】**

50

このMONOS型不揮発性メモリは、データの消去方式としてBTTBTホットホール注入方式を採用する。すなわち、コントロールゲートとメモリゲートとの中間付近のチャネル領域で発生したホットエレクトロンを電荷蓄積層に注入することによって書き込みを行い、ソース領域側の端部のチャネル領域で発生したホットホールを電荷蓄積層に注入することによって消去を行う。

#### 【0008】

ところが、電荷蓄積層に注入された電子やホールは、窒化シリコン膜中のトラップに捕獲され、窒化シリコン膜中を自由に移動することができないので、上記のようにホットエレクトロンの発生場所とホットホールの発生場所が離れていると、電荷蓄積層に注入された電子の位置とホールの位置も離れてしまう結果、ホールによる電子の消去効率が低下し、消去時間の遅延、書き換え耐性の低下、データ保持特性の劣化といった問題が生じる。

10

#### 【0009】

また、データの読み出し時には、選択したメモリセルのコントロールゲートに正の電圧を印加してコントロールトランジスタをONにし、メモリゲートに印加する電圧を、書き込み状態におけるメモリトランジスタのしきい値電圧と、消去状態におけるメモリトランジスタのしきい値電圧との間に設定して書き込み状態と消去状態とを判別する。

#### 【0010】

従って、読み出し動作を高速で行うためには、選択したメモリセルと非選択メモリセルとの間でコントロールトランジスタのON/OFFを高速で行う必要がある。このとき、インピーダンスの関係でメモリゲートに切り替えノイズが発生するが、メモリゲートの抵抗が高い場合は、このノイズが大きくなつて読み出しえラーを引き起こす。

20

#### 【0011】

本発明の目的は、MONOS型トランジスタを有する不揮発性半導体記憶装置の高性能化を推進することのできる技術を提供することにある。

#### 【0012】

本発明の他の目的は、MONOS型トランジスタを有する不揮発性半導体記憶装置の製造工程を簡略化することのできる技術を提供することにある。

#### 【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

30

#### 【課題を解決するための手段】

#### 【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0015】

本発明は、半導体基板の第1領域に不揮発性メモリセルを有し、前記半導体基板の第2領域に第1MISFETを有する半導体装置の製造方法であつて、

(a) 前記第1領域および前記第2領域の前記半導体基板上に、第1導電膜を形成する工程、

(b) 前記(a)工程の後に、前記第1導電膜上に選択的にフォトレジスト膜を形成し、前記第1導電膜をパターニングすることで、前記第1領域に前記不揮発性メモリセルのコントロールゲート電極を形成すると共に、前記第2領域に前記第1MISFETのゲート電極を形成する工程、

40

(c) 前記(b)工程の後に、前記第1領域および前記第2領域の前記半導体基板上に、前記コントロールゲート電極および前記第1MISFETのゲート電極を覆うように、電荷蓄積膜を形成する工程、

(d) 前記(c)工程の後に、前記電荷蓄積膜上に第2導電膜を形成する工程、

(e) 前記(d)工程の後に、前記第2導電膜を異方性エッチングすることで、前記コントロールゲート電極の側壁、および、前記第1MISFETのゲート電極の側壁にサイドウォール状のメモリゲート電極を形成する工程、

50

( f ) 前記 ( e ) 工程の後に、前記コントロールゲート電極の一方の側壁に前記メモリゲート電極が残されるように、前記第 1 領域において前記コントロールゲート電極の他方の側壁の前記メモリゲート電極を除去すると共に、前記第 2 領域において前記メモリゲート電極を除去する工程、

( g ) 前記 ( f ) 工程の後に、前記第 1 領域において前記コントロールゲート電極の他方の側壁側の前記電荷蓄積膜を除去すると共に、前記第 2 領域において前記電荷蓄積膜を除去する工程、

( h ) 前記 ( g ) 工程の後に、前記第 1 領域において前記コントロールゲート電極の他方の側壁側の前記半導体基板に第 1 不純物領域を形成する工程、

( i ) 前記 ( g ) 工程の後に、前記第 1 領域において前記メモリゲート電極の側壁側の前記半導体基板に第 2 不純物領域を形成する工程、10

( j ) 前記 ( g ) 工程の後に、前記第 2 領域において前記半導体基板に第 3 不純物領域を形成する工程、

( k ) 前記 ( h ) ~ ( j ) 工程の後に、前記第 1 領域において前記コントロールゲート電極の他方の側壁、前記メモリゲート電極の側壁、および、前記第 1 M I S F E T のゲート電極の側壁に、絶縁膜からなるサイドウォールスペーサを形成する工程、

( l ) 前記 ( k ) 工程の後に、前記第 1 領域の半導体基板に、前記第 1 不純物領域と接続し、且つ、前記第 1 不純物領域よりも高濃度の第 4 不純物領域を形成し、前記第 1 領域の半導体基板に、前記第 2 不純物領域と接続し、且つ、前記第 2 不純物領域よりも高濃度の第 5 不純物領域を形成し、前記第 2 領域の半導体基板に、前記第 3 不純物領域と接続し、且つ、前記第 3 不純物領域よりも高濃度の第 6 不純物領域を形成する工程、20

を有し、

前記 ( b ) 工程では、前記コントロールゲート電極の高さを、前記コントロールゲート電極のゲート長方向の長さよりも大きくなるように形成し、

前記 ( d ) 工程では、前記第 2 導電膜として、不純物が導入された多結晶シリコン膜を C V D 法によって堆積し、

前記 ( e ) 工程では、前記メモリゲート電極の高さを、前記メモリゲート電極のゲート長方向の長さよりも大きくなるように形成するものである。

#### 【発明の効果】

#### 【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。30

#### 【0017】

M O N O S 型トランジスタを有する不揮発性半導体記憶装置の読み出し動作を高速で行うことができる。

#### 【0018】

また、M O N O S 型トランジスタを有する不揮発性半導体記憶装置の製造工程を簡略化することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。40

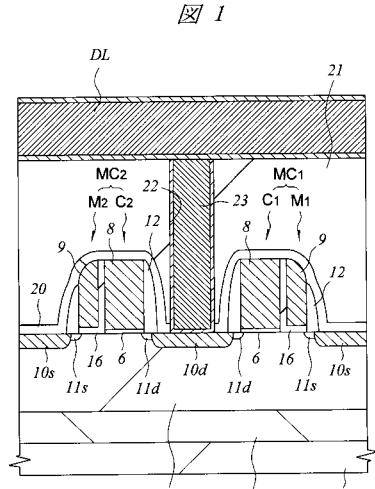

#### 【0020】

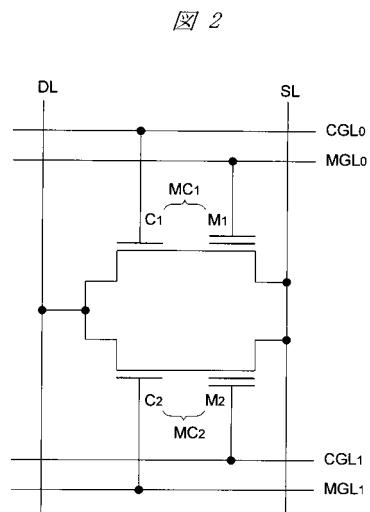

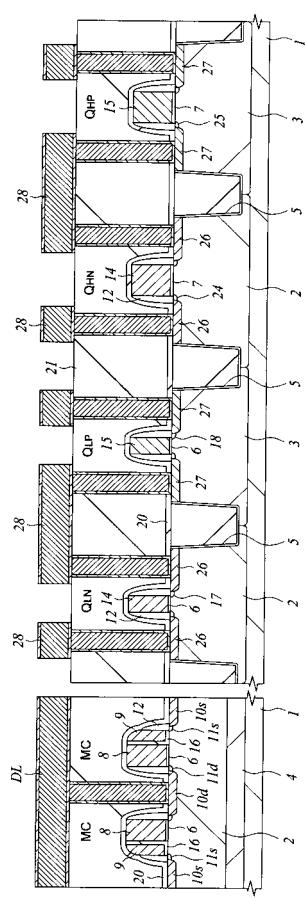

図 1 は、本実施の形態のM O N O S 型不揮発性メモリを示す要部断面図、図 2 は、図 1 に示すM O N O S 型不揮発性メモリの等価回路図である。なお、図 1 および図 2 は、互いに隣接して配置された 2 個のメモリセル ( M C <sub>1</sub> 、 M C <sub>2</sub> ) を示している。

#### 【0021】

M O N O S 型不揮発性メモリのメモリセル ( M C <sub>1</sub> ) は、p 型の単結晶シリコンからなる半導体基板 ( 以下、単に基板という ) 1 の p 型ウエル 2 に形成されている。p 型ウエル50

2は、ウエルアイソレーション用のn型埋込み層4を介して基板1と電気的に分離され、所望の電圧が印加されるようになっている。

#### 【0022】

メモリセル(MC<sub>1</sub>)は、コントロールトランジスタ(C<sub>1</sub>)とメモリトランジスタ(M<sub>1</sub>)とで構成されている。コントロールトランジスタ(C<sub>1</sub>)のゲート電極(コントロールゲート8)はn型多結晶シリコン膜からなり、酸化シリコン膜からなるゲート絶縁膜6上に形成されている。また、メモリトランジスタ(M<sub>1</sub>)のゲート電極(メモリゲート9)はn型多結晶シリコン膜からなり、コントロールゲート8の一方の側壁に配置されている。このメモリゲート9は、一部がコントロールゲート8の一方の側壁に形成され、他部がp型ウエル2上に形成された断面L字状の電荷蓄積層16を介してコントロールゲート8およびp型ウエル2と電気的に分離されている。電荷蓄積層16は、2層の酸化シリコン膜とそれらの間に形成された窒化シリコン膜とからなる。データの書き込み時には、チャネル領域で発生したホットエレクトロンが電荷蓄積層16に注入され、窒化シリコン膜中のトラップに捕獲される。

10

#### 【0023】

コントロールゲート8の近傍のp型ウエル2には、メモリセル(MC<sub>1</sub>)のドレイン領域として機能するn<sup>+</sup>型半導体領域10dが形成されている。また、メモリゲート9の近傍のp型ウエル2には、メモリセル(MC<sub>1</sub>)のソース領域として機能するn<sup>+</sup>型半導体領域10sが形成されている。

20

#### 【0024】

n<sup>+</sup>型半導体領域(ドレイン領域)10dに隣接した領域のp型ウエル2には、n<sup>+</sup>型半導体領域10dよりも不純物濃度が低いn<sup>-</sup>型半導体領域11dが形成されている。n<sup>-</sup>型半導体領域11dは、n<sup>+</sup>型半導体領域(ドレイン領域)10dの端部の高電界を緩和し、コントロールトランジスタ(C<sub>1</sub>)をLDD(Lightly Doped Drain)構造にするためのエクステンション領域である。また、n<sup>+</sup>型半導体領域(ソース領域)10sに隣接した領域のp型ウエル2には、n<sup>+</sup>型半導体領域10sよりも不純物濃度が低いn<sup>-</sup>型半導体領域11sが形成されている。n<sup>-</sup>型半導体領域11sは、n<sup>+</sup>型半導体領域(ソース領域)10sの端部の高電界を緩和し、メモリトランジスタ(M<sub>1</sub>)をLDD構造にするためのエクステンション領域である。

30

#### 【0025】

コントロールゲート8の他方の側壁およびメモリゲート9の一方の側壁には、酸化シリコン膜からなるサイドウォールスペーサ12が形成されている。これらのサイドウォールスペーサ12は、n<sup>+</sup>型半導体領域(ドレイン領域)10dおよびn<sup>+</sup>型半導体領域(ソース領域)10sを形成するために利用される。

30

#### 【0026】

上記のように構成されたメモリセル(MC<sub>1</sub>)の上部には、窒化シリコン膜20と酸化シリコン膜21とを介してデータ線(DL)が形成されている。データ線(DL)は、n<sup>+</sup>型半導体領域(ドレイン領域)10dの上部に形成されたコンタクトホール22内のプラグ23を介してn<sup>+</sup>型半導体領域(ドレイン領域)10dと電気的に接続されている。データ線(DL)は、アルミニウム合金を主体としたメタル膜からなり、プラグ23は、タンゲステンを主体としたメタル膜からなる。

40

#### 【0027】

図2に示すように、コントロールトランジスタ(C<sub>1</sub>)のコントロールゲート8は、コントロールゲート線(CGL<sub>0</sub>)に接続され、メモリトランジスタ(M<sub>1</sub>)のメモリゲート9は、メモリゲート線(MGL<sub>0</sub>)に接続されている。また、ソース領域10sは、ソース線(SL)に接続されており、p型ウエル2には、図示しない電源線を通じて所望の電圧が印加される。

#### 【0028】

メモリセル(MC<sub>1</sub>)に隣接するメモリセル(MC<sub>2</sub>)は、メモリセル(MC<sub>1</sub>)と同一の構造で構成され、そのドレイン領域10dは、メモリセル(MC<sub>1</sub>)のドレイン領域1

50

0 d と共有されている。前述したように、このドレイン領域 10 d は、データ線 (D L) に接続されている。2 個のメモリセル (M C<sub>1</sub>、M C<sub>2</sub>) は、共通のドレイン領域 10 d を挟んで対称となるように配置されている。コントロールトランジスタ (C<sub>2</sub>) のコントロールゲート 8 は、コントロールゲート線 (C G L<sub>1</sub>) に接続され、メモリトランジスタ (M<sub>2</sub>) のメモリゲート 9 は、メモリゲート線 (M G L<sub>1</sub>) に接続されている。また、ソース領域 10 s は、ソース線 (S L) に接続されている。

#### 【0029】

次に、上記メモリセル (M C<sub>1</sub>) を選択メモリセルとした場合の書き込み、消去および読み出しの各動作について説明する。ここでは、電荷蓄積層 16 に電子を注入することを「書き込み」、ホールを注入することを「消去」とそれぞれ定義する。

10

#### 【0030】

書き込みは、いわゆるソースサイド注入方式と呼ばれるホットエレクトロン書き込み方式を採用する。書き込み時には、コントロールゲート 8 に 0.7 V、メモリゲート 9 に 10 V、ソース領域 10 s に 6 V、ドレイン領域に 0 V、p 型ウエル 2 に 0 V をそれぞれ印加する。これにより、ソース領域 10 s とドレイン領域 10 d との間に形成されるチャネル領域のうち、コントロールゲート 8 とメモリゲート 9 との中間付近の領域でホットエレクトロンが発生し、これが電荷蓄積層 16 に注入される。注入された電子は窒化シリコン膜中のトラップに捕獲され、メモリトランジスタ (M<sub>1</sub>) のしきい値電圧が上昇する。

#### 【0031】

消去は、チャネル電流を利用したホットホール注入消去方式を採用する。消去時には、コントロールゲート 8 に 0.7 V、メモリゲート 9 に -8 V、ソース領域 10 s に 7 V、ドレイン領域に 0 V、p 型ウエル 2 に 0 V をそれぞれ印加する。これにより、コントロールゲート 8 の下部の p 型ウエル 2 にチャネル領域が形成される。また、ソース領域 10 s に高電圧 (7 V) が印加されるため、ソース領域 10 s から伸びた空乏層がコントロールトランジスタ (C<sub>1</sub>) のチャネル領域に近づく。この結果、チャネル領域を流れる電子が、チャネル領域の端部とソース領域 10 s との間の高電界によって加速されてインパクトイオン化が生じ、電子とホールの対が生成される。そして、このホールがメモリゲート 9 に印加された負電圧 (-8 V) によって加速されてホットホールとなり、電荷蓄積層 16 に注入される。注入されたホールは窒化シリコン膜中のトラップに捕獲され、メモリトランジスタ (M<sub>1</sub>) のしきい値電圧が低下する。

20

#### 【0032】

読み出し時には、コントロールゲート 8 に 1.5 V、メモリゲート 9 に 1.5 V、ソース領域 10 s に 0 V、ドレイン領域に 1.5 V、p 型ウエル 2 に 0 V をそれぞれ印加する。すなわち、メモリゲート 9 に印加する電圧を、書き込み状態におけるメモリトランジスタ (M<sub>1</sub>) のしきい値電圧と、消去状態におけるメモリトランジスタ (M<sub>1</sub>) のしきい値電圧との間に設定し、書き込み状態と消去状態とを判別する。

30

#### 【0033】

このように、MONOS 型不揮発性メモリは、選択メモリセルのコントロールゲート 8 に電圧を印加してコントロールトランジスタ (C<sub>1</sub>) を ON にし、メモリゲート 9 に電圧を印加した状態で読み出しを行う。従って、読み出し動作を高速で行うためには、選択メモリセルと非選択メモリセルとの間でコントロールトランジスタの ON / OFF を高速で行う必要がある。このとき、インピーダンスの関係でメモリゲート 9 に切り替えノイズが発生するが、メモリゲート 9 の抵抗が高い場合は、このノイズが大きくなってしまい、読み出しえラーを引き起こす。後述するように、本実施の形態の MONOS 型不揮発性メモリは、メモリゲート 9 を構成する n 型多結晶シリコン膜の抵抗が低いので、このようなノイズの増大が抑制され、読み出し動作を高速で行うことができる。

40

#### 【0034】

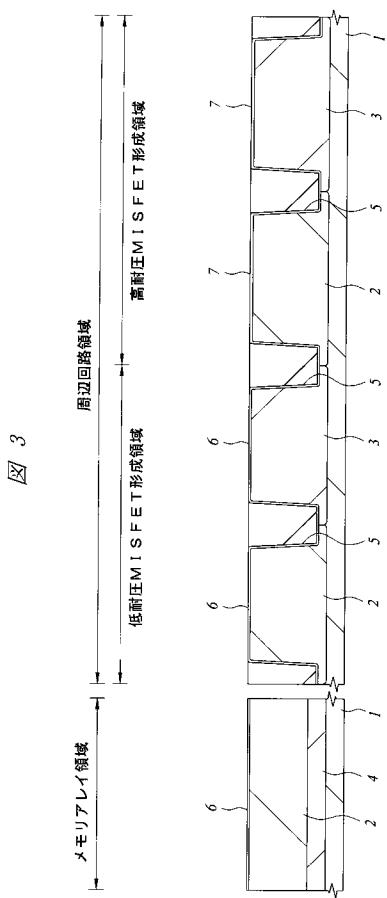

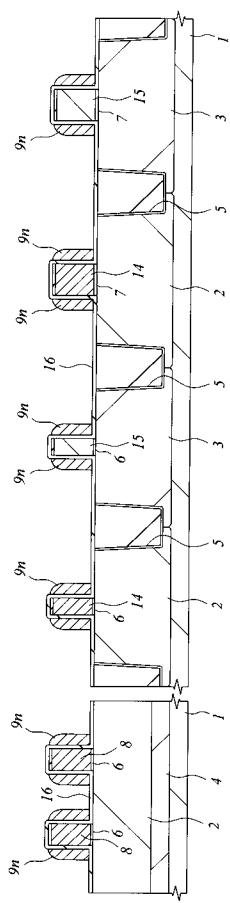

次に、図 3 ~ 図 20 を用いて上記 MONOS 型不揮発性メモリの製造方法を工程順に説明する。

#### 【0035】

50

まず、図3に示すように、周知の製造方法を用いて基板1の主面に素子分離溝5を形成した後、メモリアレイ領域の基板1の主面にn型埋込み層4とp型ウエル2とを形成し、周辺回路領域の基板1の主面にp型ウエル2とn型ウエル3とを形成する。なお、MONOS型不揮発性メモリの周辺回路は、例えばセンスアンプ、カラムデコーダ、ロウデコーダのように、低耐圧MISFETで構成される回路と、例えば昇圧回路のように、高耐圧MISFETで構成される回路とがある。従って、図にはメモリアレイ領域、低耐圧MISFET形成領域および高耐圧MISFET形成領域を示す。

#### 【0036】

次に、基板1を熱酸化することによって、p型ウエル2とn型ウエル3のそれぞれの表面に酸化シリコンからなるゲート絶縁膜6、7を形成する。ゲート絶縁膜6は、メモリアレイ領域と低耐圧MISFET形成領域とに形成し、ゲート絶縁膜7は、高耐圧MISFET形成領域に形成する。ゲート絶縁膜7は、耐圧を確保するために、ゲート絶縁膜6の膜厚(3~4nm程度)よりも厚い膜厚(7~8nm程度)で形成する。すなわち、メモリアレイ領域のゲート絶縁膜6と低耐圧MISFET形成領域のゲート絶縁膜6は同工程で形成された同一の膜である。後述するように、メモリアレイ領域のゲート絶縁膜6はコントロールゲート8のゲート絶縁膜となる。従って、高耐圧MISFETのゲート絶縁膜7でなく、低耐圧MISFETのゲート絶縁膜6をコントロールゲート8のゲート絶縁膜として、メモリセルの高速動作が可能となる。

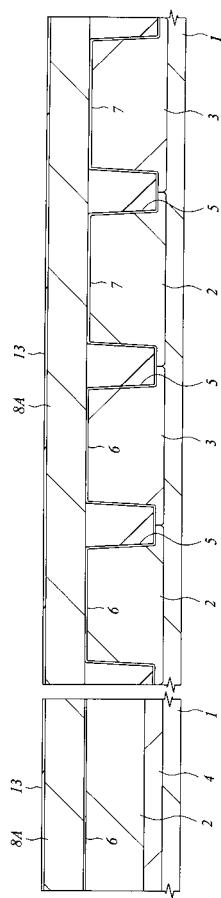

#### 【0037】

次に、図4に示すように、基板1上にCVD法で膜厚250nm程度のアンドープドシリコン膜8Aを堆積した後、アンドープドシリコン膜8Aの表面を保護するために、その上部にCVD法で薄い酸化シリコン膜13を堆積する。

#### 【0038】

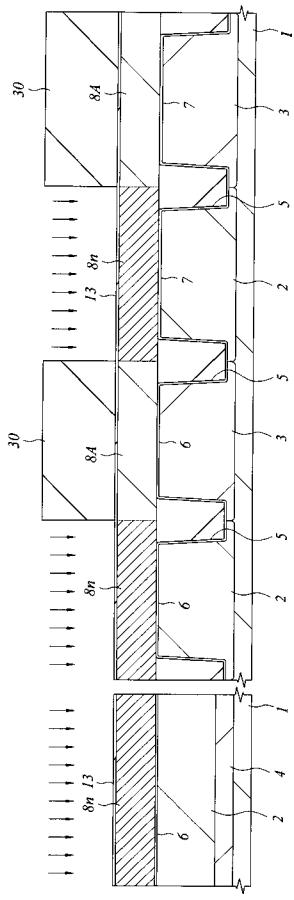

次に、図5に示すように、周辺回路領域のうち、pチャネル型MISFET形成領域(n型ウエル3)のアンドープドシリコン膜8Aをフォトレジスト膜30で覆い、nチャネル型MISFET形成領域およびメモリアレイ領域のアンドープドシリコン膜8Aに不純物(リンまたはヒ素)をイオン注入することによって、これらの領域のアンドープドシリコン膜8Aをn型シリコン膜8nに変える。不純物がリンである場合、そのドーズ量は、 $6 \times 10^{15} \text{ atoms/cm}^2$ 程度である。その後、必要に応じて、pチャネル型MISFET形成領域のアンドープドシリコン膜8Aをp型シリコン膜とすることもできる。その場合、同様にしてnチャネル型MISFET形成領域(p型ウエル2)のアンドープドシリコン膜8Aをフォトレジスト膜で覆い、pチャネル型MISFET形成領域のアンドープドシリコン膜8Aに不純物(ボロンまたはフッ化ボロン)をイオン注入することによって、これらの領域のアンドープドシリコン膜8Aをp型シリコン膜に変える。

#### 【0039】

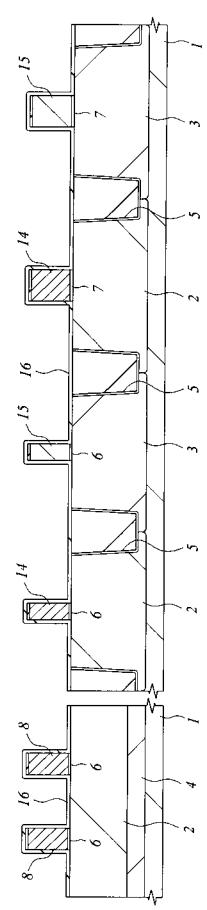

次に、図6に示すように、フォトレジスト膜31をマスクにして酸化シリコン膜13、アンドープドシリコン膜8Aおよびn型シリコン膜8nをドライエッチングする。これにより、メモリアレイ領域にn型シリコン膜8nからなるコントロールゲート8が形成され、周辺回路領域のnチャネル型MISFET形成領域(p型ウエル2)にn型シリコン膜8nからなるゲート電極14が形成される。また、周辺回路領域のpチャネル型MISFET形成領域(n型ウエル3)には、アンドープドシリコン膜8Aからなるゲート電極15が形成される。アンドープドシリコン膜8Aからなるゲート電極15には、後の工程で不純物(ホウ素)がイオン注入されてp型シリコン膜になる。このように、アンドープドシリコン膜8Aにイオン注入する不純物の種類を局所的に変えることにより、アンドープドシリコン膜8Aを用いてメモリセルのコントロールゲート8と周辺回路領域のゲート電極14、15とを同時に形成することができるので、ゲート形成工程を簡略することができる。

#### 【0040】

メモリアレイ領域に形成されるコントロールゲート8のゲート長は、180nm程度である。コントロールゲート8のゲート長が180nm程度まで短くなった場合、コントロ

10

20

30

40

50

一ルゲート 8 のアスペクト比（ゲート長に対する高さの比）は、1 よりも大きくなる。このような高アスペクト比のコントロールゲート 8 をメモリゲート 9 の形成後に形成しようとすると、コントロールゲート 8 の加工が困難となるので、本実施の形態では、コントロールゲート 8 を形成してからメモリゲート 9 を形成する。また、これにより、コントロールゲート 8 よりもさらに小さいゲート長を有するメモリゲート 9 をコントロールゲート 8 の側壁に形成することが可能となる。

#### 【0041】

次に、図 7 に示すように、基板 1 上に電荷蓄積層 16 を形成する。電荷蓄積層 16 は、酸化シリコン膜、窒化シリコン膜および酸化シリコン膜の3層膜で構成する。これらの3層膜のうち、下層の酸化シリコン膜は、熱酸化法またはCVD法で形成する。または、熱酸化装置のチャンバ内に水素と酸素を直接導入し、加熱したウエハ上でラジカル酸化反応を行うISSG (In situ Steam Generation)酸化法を用いて形成してもよい。窒化シリコン膜は、CVD法またはALD (atomic layer deposition) 法で形成し、上層の酸化シリコン膜は、CVD法またはISSG酸化法で形成する。なお、下層の酸化シリコン膜を形成した後、窒化シリコン膜を形成する前に、N<sub>2</sub>Oなどの窒素酸化物を含んだ高温雰囲気中で酸化シリコン膜を窒化処理することによって、酸化シリコン膜と基板 1 (p型ウエル 2、n型ウエル 3)との界面に窒素を偏析させてもよい。この窒化処理を行うことにより、メモリセルを構成するコントロールトランジスタおよびメモリトランジスタのホットキャリア耐性が向上するので、メモリセルの特性（書き換え特性など）が向上する。

#### 【0042】

また、コントロールゲート 8 を形成した後、電荷蓄積層 16 を形成する工程に先立って、メモリアレイ領域のp型ウエル 2 にコントロールトランジスタのしきい値電圧を調整するための不純物や、メモリトランジスタのしきい値電圧を調整するための不純物をイオン注入してもよい。これにより、コントロールトランジスタおよびメモリトランジスタのしきい値電圧を最適化することができる。

#### 【0043】

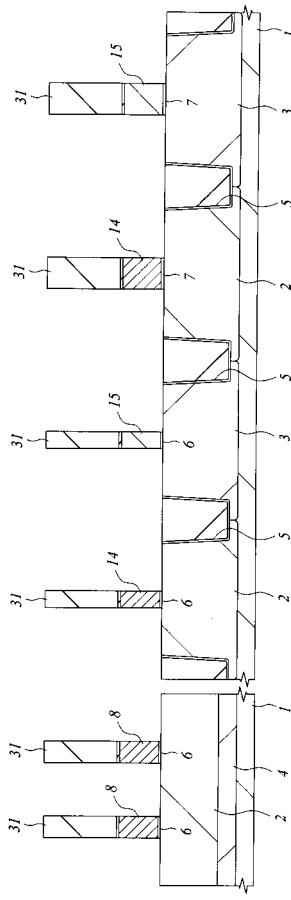

次に、コントロールゲート 8 の一方の側壁にメモリゲート 9 を形成する。メモリゲート 9 を形成するには、まず、図 8 に示すように、基板 1 上にCVD法でn型多結晶シリコン膜 9n を堆積する。

#### 【0044】

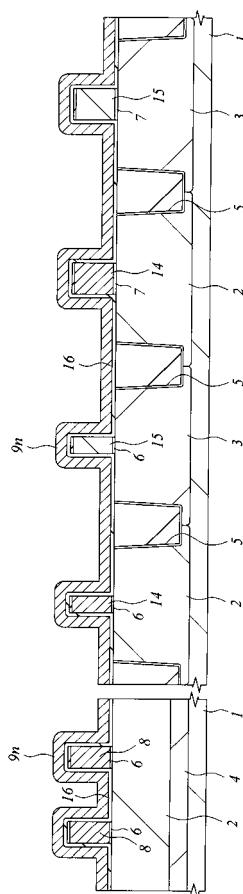

次に、図 9 に示すように、このn型多結晶シリコン膜 9n を異方性エッチングすることによって、コントロールゲート 8 と、周辺回路のゲート電極 14、15 の両側壁にn型多結晶シリコン膜 9n を残す。n型多結晶シリコン膜 9n の不純物（リンまたはヒ素）濃度は、1 × 10<sup>20</sup>atoms/cm<sup>3</sup> ~ 6 × 10<sup>20</sup>atoms/cm<sup>3</sup>程度である。

#### 【0045】

次に、図 10 に示すように、メモリゲート形成領域を覆うフォトレジスト膜 32 をマスクにしてn型多結晶シリコン膜 9n をエッチングする。これにより、コントロールゲート 8 の一方の側壁にn型多結晶シリコン膜 9n からなるメモリゲート 9 が形成される。

#### 【0046】

コントロールゲート 8 の側壁に形成されるメモリゲート 9 のゲート長は、80nm程度であり、そのアスペクト比（ゲート長に対する高さの比）は1よりも大きい。本実施の形態では、コントロールゲート 8 を形成してからメモリゲート 9 を形成するので、コントロールゲート 8 よりもさらにゲート長が小さい高アスペクト比のメモリゲート 9 を容易に形成することができる。

#### 【0047】

前述したように、本実施の形態のMONOS型不揮発性メモリは、コントロールゲート 8 とメモリゲート 9 との中間付近のチャネル領域で発生したホットエレクトロンを電荷蓄積層 16 に注入することによって書き込みを行い、ソース領域 10s 側の端部のチャネル領域で発生したホットホールを電荷蓄積層 16 に注入することによって消去を行う。

#### 【0048】

10

20

30

40

50

ところが、電荷蓄積層 16 に注入された電子やホールは、窒化シリコン膜中のトラップに捕獲され、窒化シリコン膜中を自由に移動することができないので、上記のようにホットエレクトロンの発生場所とホールの発生場所が離れていると、電荷蓄積層 16 に注入された電子の位置とホールの位置も離れてしまう結果、ホールによる電子の消去効率が低下し、消去時間の遅延、書き換え耐性の低下、データ保持特性の劣化といった問題が生じる。これに対し、本実施の形態の MONOS 型不揮発性メモリは、メモリゲート 9 のゲート長が極めて小さく、従って、ホットエレクトロンの発生場所とホールの発生場所が近接しているので、ホールによる電子の消去を効率的に行うことができる。

#### 【 0049 】

また、本実施の形態では、アンドープドシリコン膜 8 A に不純物をイオン注入してコントロールゲート 8 を形成する一方、n 型多結晶シリコン膜 9 n を使ってメモリゲート 9 を形成する。成膜時に不純物を導入するいわゆるドープドポリシリコン膜（n 型多結晶シリコン膜 9 n）は、成膜後に不純物をイオン注入する場合に比べて電気抵抗を下げるができるので、n 型多結晶シリコン膜 9 n で形成したメモリゲート 9 のシート抵抗（約 80 ）は、コントロールゲート 8 のシート抵抗（約 120 ）より小さくなる。また、イオン注入をする際のマスクを低減できるので、製造工程を簡略化することができる。

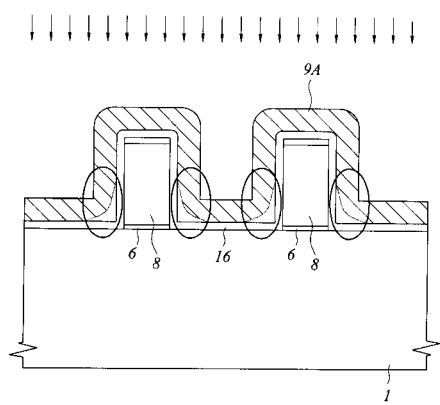

#### 【 0050 】

また、仮にアンドープドシリコン膜にイオン注入する方法を用いた場合では、次のような問題があることを見出した。図 11 に示すように、アンドープドシリコン膜に不純物をイオン注入して形成した低抵抗シリコン膜は、不純物が膜の底部にまで充分に到達しないので、イオン注入がなされない領域、もしくは他の領域に比べて不純物濃度が薄い領域が形成されてしまう（図中の矢印で示した領域）。これにより、膜の底部の抵抗が高くなる。従って、このようなシリコン膜を使ってメモリゲート 9 を形成した場合は、メモリゲート 9 に電圧を印加した際、メモリゲート 9 の下部に形成された電荷蓄積層 16 との界面近傍に空乏層が形成され易くなるので、メモリトランジスタ（M<sub>1</sub>）の駆動能力が低下する。

#### 【 0051 】

ドープドポリシリコン膜（n 型多結晶シリコン膜 9 n）を使ってメモリゲート 9 を形成する本実施の形態によれば、メモリゲート 9 を低抵抗化することができる。前述したように、読み出し時にコントロールトランジスタの ON / OFF を高速で行っても、メモリゲート 9 に大きな切り替えノイズが発生しない。

#### 【 0052 】

次に、図 12 に示すように、電荷蓄積層 16 を構成する 3 層の絶縁膜をフッ酸とリン酸とを使ってエッチングする。これにより、不要な領域に形成された電荷蓄積層 16 が除去され、コントロールゲート 8 の一方の側壁とメモリゲート 9 の下部のみに電荷蓄積層 16 が残る。

#### 【 0053 】

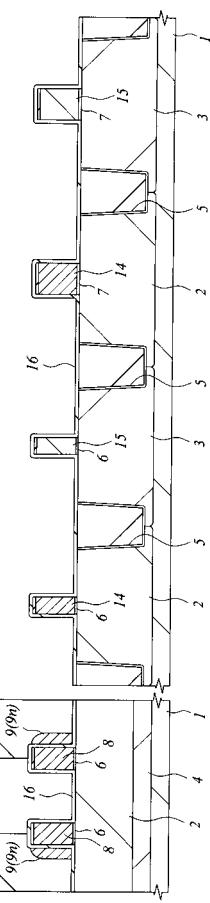

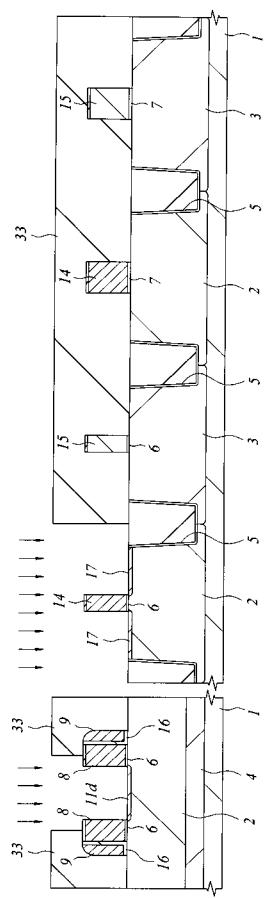

次に、図 13 に示すように、フォトレジスト膜 33 をマスクにして周辺回路の低耐圧 n チャネル型 MISFET 形成領域に不純物（リンまたはヒ素）をイオン注入することによって、n<sup>-</sup> 型半導体領域 17 を形成する。また、このとき、メモリアレイ領域の一部にも不純物（リンまたはヒ素）をイオン注入することによって、n<sup>-</sup> 型半導体領域 11 d を形成する。n<sup>-</sup> 型半導体領域 17 は、低耐圧 n チャネル型 MISFET を LDD 構造にするためのエクステンション領域であり、n<sup>-</sup> 型半導体領域 11 d は、メモリセルのコントロールトランジスタを LDD 構造にするためのエクステンション領域である。

#### 【 0054 】

なお、n<sup>-</sup> 型半導体領域 11 d の不純物濃度と n<sup>-</sup> 型半導体領域 17 の不純物濃度をそれぞれ最適化したい場合は、フォトマスクを 2 枚用意し、上記イオン注入を 2 回に分けて行ってよい。また、n<sup>-</sup> 型半導体領域 11 d および n<sup>-</sup> 型半導体領域 17 を形成するためのイオン注入は、電荷蓄積層 16 を除去する前に行ってよいが、浅い p-n 接合を形成するためには、電荷蓄積層 16 を除去した後に行った方が有利である。なお、図示はしないが

10

20

30

40

50

、このマスクを用いてエクステンション領域へ p 型の不純物を注入してもよい。この p 型の不純物領域は n<sup>-</sup>型半導体領域 11 d および n<sup>-</sup>型半導体領域 17 の下方に形成され、メモリセルおよび低耐圧 n チャネル型 M I S F E T の短チャネル効果を抑制するための領域（ハロー領域）として機能する。

#### 【 0 0 5 5 】

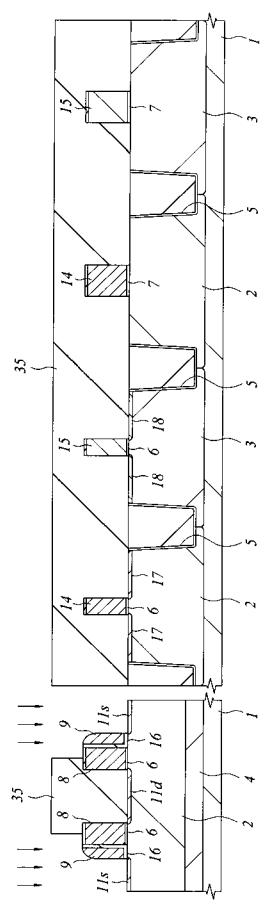

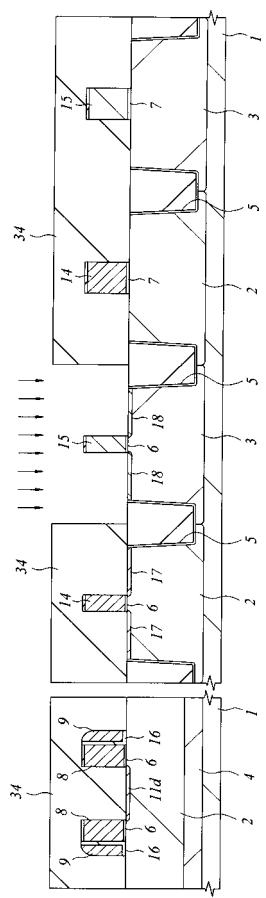

次に、図 14 に示すように、フォトレジスト膜 34 をマスクにして周辺回路の低耐圧 p チャネル型 M I S F E T 形成領域に不純物（ホウ素）をイオン注入することによって、p<sup>-</sup>型半導体領域 18 を形成する。p<sup>-</sup>型半導体領域 18 は、低耐圧 p チャネル型 M I S F E T を L D D 構造にするためのエクステンション領域である。なお、図示はしないが、このマスクを用いて、エクステンション領域へ n 型の不純物を注入してもよい。この n 型の不純物領域は p<sup>-</sup>型半導体領域 18 の下方に形成され、低耐圧 p チャネル型 M I S F E T の短チャネル効果を抑制するための領域（ハロー領域）として機能する。10

#### 【 0 0 5 6 】

次に、図 15 に示すように、フォトレジスト膜 35 をマスクにしてメモリアレイ領域の一部に不純物（リンまたはヒ素）をイオン注入することによって、n<sup>-</sup>型半導体領域 11 s を形成する。n<sup>-</sup>型半導体領域 11 s は、メモリセルのメモリトランジスタを L D D 構造にするためのエクステンション領域である。なお、n<sup>-</sup>型半導体領域 11 s を形成するためのイオン注入は、電荷蓄積層 16 を除去する前に行ってもよいが、浅い p n 接合を形成するためには、電荷蓄積層 16 を除去した後に行った方が有利である。また、図示はしないが、このマスクを用いて、エクステンション領域へ p 型の不純物を注入してもよい。この p 型の不純物領域は n<sup>-</sup>型半導体領域 11 s の下方に形成され、メモリセルの短チャネル効果を抑制するための領域（ハロー領域）として機能する。20

#### 【 0 0 5 7 】

次に、図 16 に示すように、フォトレジスト膜 36 をマスクにして周辺回路の高耐圧 n チャネル型 M I S F E T 形成領域に不純物（リンまたはヒ素）をイオン注入することによって、n<sup>-</sup>型半導体領域 24 を形成する。n<sup>-</sup>型半導体領域 24 は、高耐圧 n チャネル型 M I S F E T を L D D 構造にするためのエクステンション領域である。なお、図示はしないが、このマスクを用いて、エクステンション領域へ p 型の不純物を注入してもよい。この p 型の不純物領域は n<sup>-</sup>型半導体領域 24 の下方に形成され、高耐圧 n チャネル型 M I S F E T の短チャネル効果を抑制するための領域（ハロー領域）として機能する。30

#### 【 0 0 5 8 】

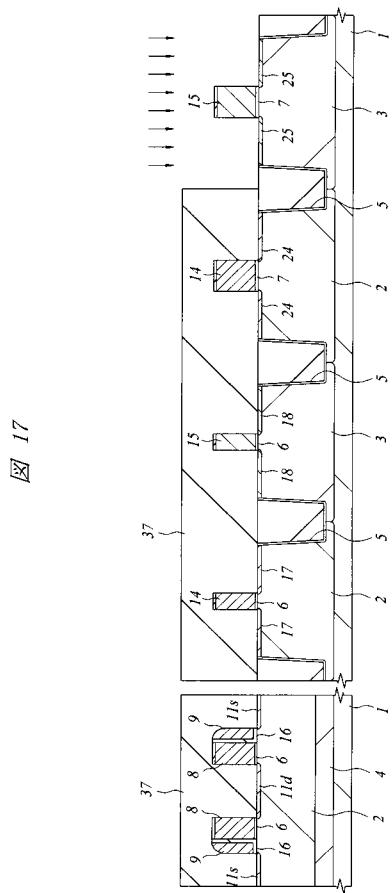

次に、図 17 に示すように、フォトレジスト膜 37 をマスクにして周辺回路の高耐圧 p チャネル型 M I S F E T 形成領域に不純物（ホウ素）をイオン注入することによって、p<sup>-</sup>型半導体領域 25 を形成する。p<sup>-</sup>型半導体領域 25 は、高耐圧 p チャネル型 M I S F E T を L D D 構造にするためのエクステンション領域である。なお、図示はしないが、このマスクを用いて、エクステンション領域へ n 型の不純物を注入してもよい。この n 型の不純物領域は p<sup>-</sup>型半導体領域 25 の下方に形成され、高耐圧 p チャネル型 M I S F E T の短チャネル効果を抑制するための領域（ハロー領域）として機能する。

#### 【 0 0 5 9 】

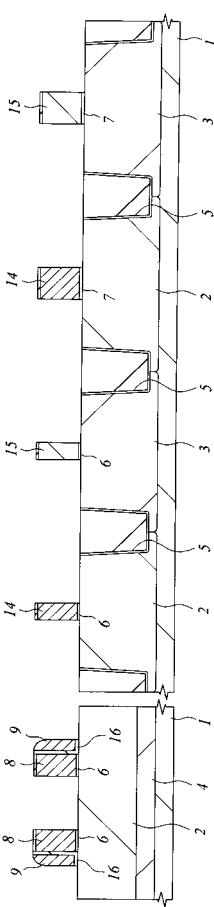

次に、図 18 に示すように、メモリアレイ領域に形成されたコントロールゲート 8 およびメモリゲート 9 のそれぞれの一方の側壁にサイドウォールスペーサ 12 を形成し、周辺回路領域のゲート電極 14 およびゲート電極 15 のそれぞれの両側壁にサイドウォールスペーサ 12 を形成する。サイドウォールスペーサ 12 は、基板 1 上に C V D 法で堆積した酸化シリコン膜を異方性エッティングすることによって形成する。40

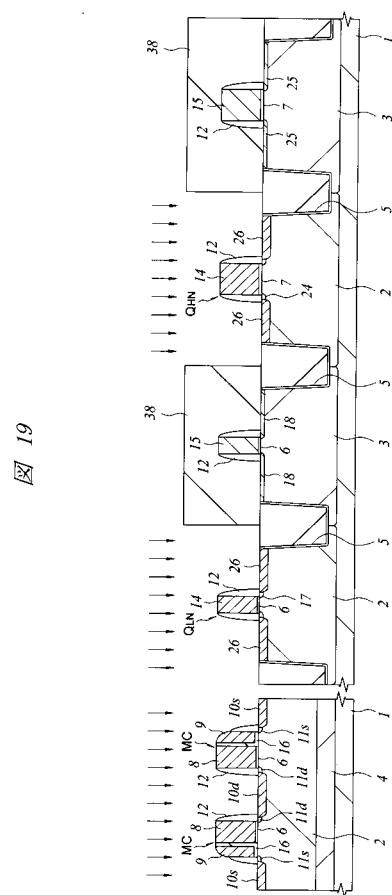

#### 【 0 0 6 0 】

次に、図 19 に示すように、フォトレジスト膜 38 をマスクにしてメモリアレイ領域および周辺回路の n チャネル型 M I S F E T 形成領域に不純物（リンまたはヒ素）をイオン注入する。これにより、メモリアレイ領域に n<sup>+</sup>型半導体領域（ドレイン領域） 10 d および n<sup>+</sup>型半導体領域（ソース領域） 10 s が形成され、メモリセル M C が完成する。また、周辺回路領域に n<sup>+</sup>型半導体領域（ソース領域、ドレイン領域） 26 が形成され、低50

耐圧nチャネル型MISFET ( $Q_{LN}$ ) および高耐圧nチャネル型MISFET ( $Q_{HN}$ ) が完成する。

#### 【0061】

上記したソース、ドレイン領域 (10s, 10d, 26) を形成するためのイオン注入工程では、コントロールゲート8やメモリゲート9にも不純物が注入される。また、このイオン注入は、エクステンション領域 (11s, 11d, 17, 24) を形成するためのイオン注入に比べて、不純物のドーズ量が多く ( $1 \times 10^{13} \text{ atoms/cm}^2$  程度)、かつ注入エネルギーも高い (40KeV程度)。そのため、コントロールゲート8やメモリゲート9に注入された不純物がその下部のゲート絶縁膜6や電荷蓄積層16を貫通してp型ウエル2の表面に達すると、コントロールトランジスタやメモリトランジスタのしきい値電圧が変動してしまう。

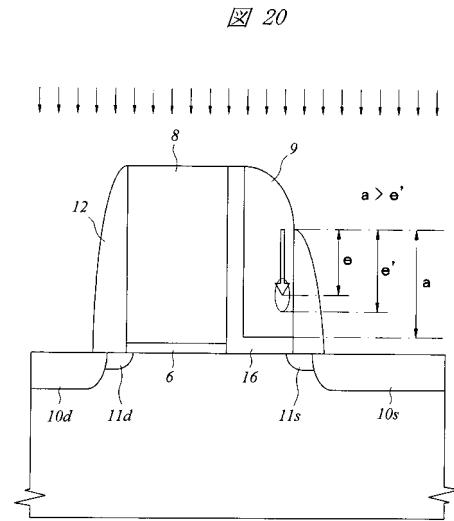

#### 【0062】

図20に示すように、メモリゲート9のうち、コントロールゲート8から最も離れた部分は、膜厚が最も薄い (膜厚 = a)。従って、上記イオン注入工程では、メモリゲート9に注入された不純物の基板方向への拡散距離が、コントロールゲート8から最も離れた部分の膜厚 (a) を超えないように注入エネルギーを制御する必要がある。すなわち、メモリゲート9に注入された不純物の基板方向への平均拡散距離を e、拡散距離のばらつきを考慮した最大拡散距離を e'とした場合、この最大拡散距離 e' が膜厚 (a) を超えないように ( $a > e'$ ) する。

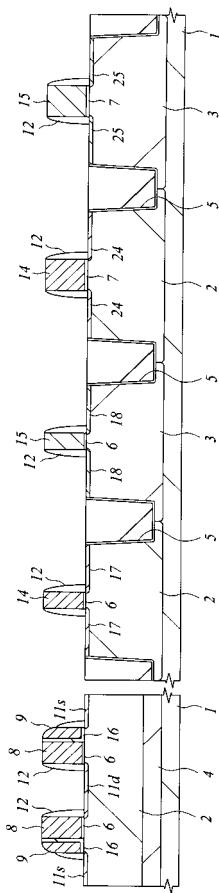

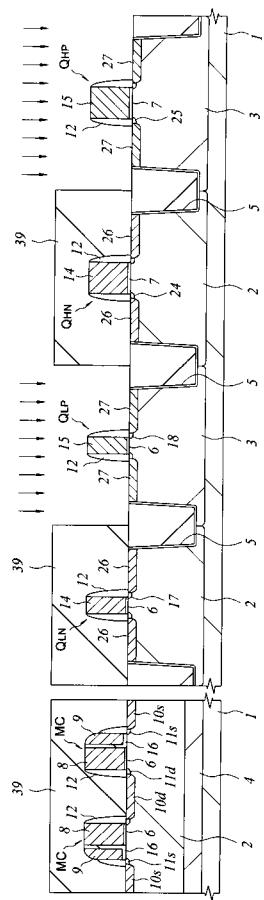

#### 【0063】

次に、図21に示すように、フォトレジスト膜39をマスクにして周辺回路のpチャネル型MISFET形成領域に不純物 (ホウ素) をイオン注入する。これにより、周辺回路領域にp<sup>+</sup>型半導体領域 (ソース領域、ドレイン領域) 27が形成され、低耐圧pチャネル型MISFET ( $Q_{LP}$ ) および高耐圧pチャネル型MISFET ( $Q_{HP}$ ) が完成する。また、上記したソース、ドレイン領域 (27) を形成するためのイオン注入工程では、pチャネル型MISFET ( $Q_{LP}$ ,  $Q_{HP}$ ) のゲート電極15にも不純物が注入されるので、ゲート電極15を構成するシリコン膜が低抵抗p型シリコン膜となる。これにより、ゲート電極15を構成するシリコン膜に不純物をイオン注入する工程とそのとき使用するフォトマスクが省略できる。さらに、上記したソース、ドレイン領域 (27) を形成するためのイオン注入工程では、フォトレジスト膜39を使用せずに不純物をイオン注入することも可能である。これにより、フォトマスクの毎数をさらに減らすことができる。ただし、この場合は、低耐圧nチャネル型MISFET ( $Q_{LN}$ ) および高耐圧nチャネル型MISFET ( $Q_{HN}$ ) にも不純物がイオン注入されるので、それらの特性変動を考慮する必要がある。

#### 【0064】

次に、図22に示すように、基板1上にCVD法で窒化シリコン膜20と酸化シリコン膜21とを堆積した後、メモリアレイ領域の酸化シリコン膜21上にデータ線DLを形成し、周辺回路領域に配線28を形成する。その後、配線28の上層に層間絶縁膜を挟んで複数の配線を形成するが、それらの図示は省略する。なお、基板1上に窒化シリコン膜20を形成する工程に先立って、メモリセルMCのコントロールゲート8、メモリゲート9、ソース領域10s、ドレイン領域10d (および周辺回路のMISFETのゲート電極、ソース領域、ドレイン領域) の表面にコバルトシリサイドなどのシリサイド層を形成することによって、コントロールゲート8やメモリゲート9などをさらに低抵抗化することもできる。

#### 【0065】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【産業上の利用可能性】

#### 【0066】

10

20

30

40

50

本発明は、MONOS型トランジスタを有する不揮発性半導体記憶装置に利用されるものである。

【図面の簡単な説明】

【0067】

【図1】本発明の一実施の形態であるMONOS型不揮発性メモリを示す半導体基板の要部断面図である。

【図2】図1に示すMONOS型不揮発性メモリの等価回路図である。

【図3】本発明の一実施の形態であるMONOS型不揮発性メモリの製造方法を示す要部断面図である。

【図4】図3に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。 10

【図5】図4に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図6】図5に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図7】図6に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図8】図7に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図9】図8に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。 20

【図10】図9に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図11】アンドープドシリコン膜を堆積後に不純物をイオン注入することによってメモリゲートを形成する場合の問題点を示す説明図である。

【図12】図10に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図13】図12に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。 30

【図14】図13に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図15】図14に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図16】図15に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図17】図16に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図18】図17に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図19】図18に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。 40

【図20】メモリゲートに注入された不純物の基板方向への拡散距離とメモリゲートの膜厚との関係を説明する図である。

【図21】図19に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【図22】図21に続くMONOS型不揮発性メモリの製造方法を示す半導体基板の要部断面図である。

【符号の説明】

【0068】

|                                        |                                     |    |

|----------------------------------------|-------------------------------------|----|

| 2                                      | p型ウエル                               |    |

| 3                                      | n型ウエル                               |    |

| 4                                      | n型埋込み層                              |    |

| 5                                      | 素子分離溝                               |    |

| 6、7                                    | ゲート絶縁膜                              |    |

| 8                                      | コントロールゲート                           |    |

| 8 A                                    | アンドープドシリコン膜                         |    |

| 8 n                                    | n型シリコン膜                             |    |

| 9                                      | メモリゲート                              |    |

| 9 n                                    | n型多結晶シリコン膜                          | 10 |

| 9 A                                    | アンドープドシリコン膜                         |    |

| 10 d                                   | n <sup>+</sup> 型半導体領域(ドレイン領域)       |    |

| 10 s                                   | n <sup>+</sup> 型半導体領域(ソース領域)        |    |

| 11 d、11 s                              | n <sup>-</sup> 型半導体領域(エクステンション領域)   |    |

| 12                                     | サイドウォールスペーサ                         |    |

| 13                                     | 酸化シリコン膜                             |    |

| 14、15                                  | ゲート電極                               |    |

| 16                                     | 電荷蓄積層                               |    |

| 17                                     | n <sup>-</sup> 型半導体領域(エクステンション領域)   |    |

| 18                                     | p <sup>-</sup> 型半導体領域(エクステンション領域)   | 20 |

| 20                                     | 窒化シリコン膜                             |    |

| 21                                     | 酸化シリコン膜                             |    |

| 22                                     | コンタクトホール                            |    |

| 23                                     | プラグ                                 |    |

| 24                                     | n <sup>-</sup> 型半導体領域(エクステンション領域)   |    |

| 25                                     | p <sup>-</sup> 型半導体領域(エクステンション領域)   |    |

| 26                                     | n <sup>+</sup> 型半導体領域(ソース領域、ドレイン領域) |    |

| 27                                     | p <sup>+</sup> 型半導体領域(ソース領域ソース領域)   |    |

| 28                                     | 配線                                  |    |

| 30 ~ 39                                | フォトレジスト膜                            | 30 |

| C <sub>1</sub> 、C <sub>2</sub>         | コントロールトランジスタ                        |    |

| C G L <sub>0</sub> 、C G L <sub>1</sub> | コントロールゲート線                          |    |

| D L                                    | データ線                                |    |

| M <sub>1</sub> 、M <sub>2</sub>         | メモリトランジスタ                           |    |

| M C、M C <sub>1</sub> 、M C <sub>2</sub> | メモリセル                               |    |

| M G L <sub>0</sub> 、M G L <sub>1</sub> | メモリゲート線                             |    |

| Q <sub>HN</sub>                        | 高耐圧nチャネル型M I S F E T                |    |

| Q <sub>LN</sub>                        | 低耐圧nチャネル型M I S F E T                |    |

| Q <sub>HP</sub>                        | 高耐圧pチャネル型M I S F E T                |    |

| Q <sub>LP</sub>                        | 低耐圧pチャネル型M I S F E T                | 40 |

| S L                                    | ソース線                                |    |

【図1】

8 : コントロールゲート

9 : メモリゲート

【図2】

【図3】

【図4】

【図5】

図5

【図7】

図7

【図6】

図6

【図8】

図8

【図9】

図9

【図11】

図11

【図10】

【図12】

図12

【図13】

図13

【図15】

図15

【図14】

図14

【図16】

図16

【図17】

【図19】

【 図 1 8 】

【図20】

【図21】

図21

【図22】

図22

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/792 (2006.01)

H 01 L 29/788 (2006.01)

H 01 L 21/336 (2006.01)

(72)発明者 中道 勝

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 松井 俊一

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 新田 恭也

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 町田 悟

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 中川 宗克

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 塚田 祐一

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

合議体

審判長 斎藤 恭一

審判官 近藤 幸浩

審判官 西脇 博志

(56)参考文献 特開2003-309193 (JP, A)

特開2004-111749 (JP, A)

特開2003-218212 (JP, A)

特開2003-46002 (JP, A)

特開2002-231829 (JP, A)

特開2003-92388 (JP, A)

特開2001-168219 (JP, A)

特開2003-282743 (JP, A)

特開2002-289715 (JP, A)

米国特許出願公開第2004/119107 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H01L29/788

H01L29/792

H01L27/115

H01L21/8247