(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 698 36 981 T2 2007.11.22**

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 040 521 B1

(21) Deutsches Aktenzeichen: **698 36 981.5**

(86) PCT-Aktenzeichen: **PCT/US98/27030**

(96) Europäisches Aktenzeichen: **98 964 114.7**

(87) PCT-Veröffentlichungs-Nr.: **WO 1999/031731**

(86) PCT-Anmeldetag: **16.12.1998**

(87) Veröffentlichungstag

der PCT-Anmeldung: **24.06.1999**

(97) Erstveröffentlichung durch das EPA: **04.10.2000**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **24.01.2007**

(47) Veröffentlichungstag im Patentblatt: **22.11.2007**

(51) Int Cl.<sup>8</sup>: **H01L 27/12 (2006.01)**

**H01L 29/786 (2006.01)**

(30) Unionspriorität:

**991808 16.12.1997 US**

(74) Vertreter:

**Grünecker, Kinkeldey, Stockmair & Schwanhäusser, 80538 München**

(73) Patentinhaber:

**Advanced Micro Devices, Inc., Sunnyvale, Calif., US**

(84) Benannte Vertragsstaaten:

**DE, FR, GB, NL**

(72) Erfinder:

**WOLLESEN, Donald, Saratoga, CA 95070, US**

(54) Bezeichnung: **VERFAHREN ZUM BETRIEB EINES SILIZIUM-OXID-ISOLATOR (SOI)-HALBLEITERs MIT SELEKTIV ANGESCHLOSSENEM BEREICH**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Hintergrund der Erfindung**

**[0001]** US-A-5 463 238 offenbart einen CMOS-Transistor und ein Verfahren zum Betreiben desselben, um das Ausbilden eines parasitären Kanals zu verhindern, wodurch Leckströme reduziert werden und die Arbeitsgeschwindigkeit erhöht wird. Die Dicke des Siliziums wird in dem Gebiet von NMOS-Transistoren im Vergleich zu PMOS-Transistoren erhöht. Auf diese Weise werden das Gebiet unterhalb der Source- und Draingebiete des N-Transistor von der elektrisch isolierenden Schicht entsprechend einem vorbestimmten Abstand getrennt.

**[0002]** IEEE Electron Device Letters, Band 18, Nr. 3, März 1997 mit dem Titel "Körperkontakteierte SOI-MOSFET-Struktur mit kompatiblen Aufbau zu CMOS-Vollsubstrat-Bauelementen und Verfahren", Yo-Hwan-Koh et al. beschreibt eine SOI-MOSFET-Struktur zum Reduzieren der Effekte des schwebenden bzw. potentialfreien Körpers. Dies wird erreicht, indem unterhalb des Feldoxids, das entsprechende Transistoren voneinander trennt, ein Siliziumschichtbereich vorgesehen wird, der die gleiche Leitfähigkeitsart wie die entsprechenden Transistorkörper aufweist.

**[0003]** Bestehende komplementäre Metalloxid-Silizium-(CMOS)Halbleiterbauelemente, die in großen Stückzahlen hergestellt werden, werden als "Vollsubstrat-CMOS-Bauelemente" bezeichnet, da diese ein Halbleitervollsubstrat aufweisen, auf welchem aktive oder passive Schaltungselemente angeordnet sind. In jüngerer Zeit wurden Silizium-Oxid-Isolator-(SOI)Bauelemente eingeführt, die weniger Leistung verbrauchen als Vollsubstrat-CMOS-Bauelemente, was ein wesentlicher Vorteil in vielen Anwendungen ist, etwa in batteriegespeisten Mobiltelefonen und batteriegespeisten tragbaren Computern. Auch können SOI-Bauelemente vorteilhafterweise mit höheren Geschwindigkeiten als Vollsubstrat-CMOS-Bauelemente arbeiten.

**[0004]** SOI-Bauelemente zeichnen sich durch eine dünne Schicht aus isolierendem Material (die sogenannte vergrabene Oxidschicht oder „SOI“) aus, die zwischen einem Vollsubstrat und den Schaltungselementen des Bauelements angeordnet ist. Typischerweise sind keine weiteren Materialschichten zwischen dem SOI und dem Vollsubstrat angeordnet. Im hierin beschriebenen Sinne bilden die Schaltungselemente eine Schaltungskomponente, etwa einen aktiven Transistor oder eine passive Komponente, beispielsweise einen Widerstand.

**[0005]** In einem SOI-Bauelement werden die Schaltungselement über der SOI-Schicht durch Gebiete aus Feldoxid und Gebieten einer monokristallinen

Halbleiterschicht gebildet, die in geeigneter Weise mit N- und P-Leitfähigkeitsdotierstoffen dotiert sind. Beispielsweise enthält bei einem N-Kanaltransistor die isolierte Siliziumschicht ein Körpergebiet mit einem P-Dotierstoff, wobei das Körpergebiet zwischen einem Source- und einem Drain-Gebiet angeordnet ist, die mit einem N-Dotiermittel dotiert sind, wodurch ein N-Kanal-Metall-Oxid-Silizium-Feldeffekttransistor (MOSFET) oder ein lateraler NPN-Bipolartransistor gebildet werden, um nur ein Beispiel zu nennen.

**[0006]** Ein Nachteil von SOI-Bauelementen besteht darin, dass die Spannung in dem Körpergebiet sich tendenziell ändert oder sich das „Potential einstellt bzw. schwebt“. Wie von Chen et al. in „Unterdrückung der SOI-Effekte des schwebenden Körpers durch eine Bauteilstruktur mit angeschlossenem Körper“ in Symposium von VLSI-Technologie in der Zusammenfassung technischer Dokumente (1996 IEEE) beschrieben ist, gehören zu den Folgen von SOI-Bauelementen mit schwebendem Körper ein Knick im Ausgangstrom, ein annormales Stromverhalten unterhalb des Schwellwerts, Übergangsstromüberschwinger, und ein vorzeitiges Durchschlagen des Bauelement.

**[0007]** Chen et al. schlagen vor, den Effekt des schwebenden Körpers zu unterdrücken, indem der Bereich einer Siliziumschicht unvollständig oxidiert wird, auf dem das Feldoxid aufgewachsen wird, so dass die Körper der Feldeffekttransistoren (FET) miteinander durch die nicht oxidierte Siliziumschicht, die unterhalb des Feldoxids verbleibt, miteinander verbunden sind. Jedoch beschreiben Chen et. nicht, wie ihre Strategie der Unterdrückung des schwebenden Körpereffekt in diversen Komponentenkonfigurationen einzurichten wäre, und Chen et al. schlagen auch nicht vor, wie ihre Strategie zur Unterdrückung der Effekte des schwebenden Körpers unter Anwendung von Techniken einzurichten wäre, die in einfacher Weise durchgeführt werden können unter Nutzung bestehender CMOS-Herstellungsprinzipien für Vollsubstrate. Erfindungsgemäß wurde erkannt, dass es wichtig ist, den Schaltungsentwurfsingenieur in die Lage zu versetzen, diverse SOI-Komponenten unter Anwendung bestehender Herstellungsprinzipien für Vollsubstrat-CMOS-Bauelemente einzurichten, um damit die Verwendung von SOI-Bauelementen zu fördern, ohne eine Umgestaltung der Halbleiterfertigungseinrichtungen und Fertigungsstätten zu erfordern. Ferner erkennen Chen et al. nicht, dass in einigen möglichen SOI-Schaltungskomponenten, etwa Metall-Oxid-Silizium-(DTMOS)Bauelementen mit dynamischen Schwellwert, die bei sehr geringen Spannung arbeiten, der Effekt des schwebenden Körpers vorteilhafterweise beibehalten werden soll. In der Tat kann es in einigen Schaltungsanordnungen wünschenswert sein, dass einige SOI-Komponenten die Eigenschaften eines schwebenden Körpers aufweisen, wobei der schwebende Körper in anderen

SOI-Komponenten in der Anordnung vermieden wird.

**[0008]** Daher ist es eine Aufgabe der vorliegenden Erfindung, ein SOI-Bauelement bereitzustellen, in welchem die Effekte des schwebenden Körpers minimiert sind. Eine weitere Aufgabe der vorliegenden Erfindung besteht darin, ein SOI-Bauelement bereitzustellen, in welchem die Auswirkungen des schwebenden Körpers selektiv in gewissen Gebieten des Bauelements im Vergleich zu anderen Gebieten minimal gemacht werden können. Eine noch weitere Aufgabe der vorliegenden Erfindung ist es, eine Vielzahl von SOI-Bauelementen bereitzustellen, in denen die Auswirkungen des schwebenden Körpers unter Anwendung von Fertigungsprinzipien minimiert werden können. Eine weitere Aufgabe der vorliegenden Erfindung ist es, ein SOI-Bauelement bereitzustellen, das einfach angewendet und in kosteneffizienter Weise hergestellt werden kann.

#### Kurzer Überblick über die Erfindung

**[0009]** Ein Halbleiterbauelement, das für das Verständnis der vorliegenden Erfindung vorteilhaft ist, umfasst mindestens einen ersten Silizium-Oxid-Isolator-(SOI)Transistor und einen zweiten SOI-Transistor, wobei zumindest der erste SOI-Transistor ein Halbleiterkörpergebiet aufweist. Ein Halbleiterübergangsgebiet ist zwischen dem ersten und dem zweiten SOI-Transistor angeordnet. Das Übergangsgebiet besitzt eine erste Leitfähigkeitsart und steht mit einer Versorgungsspannungsquelle in Verbindung. Gemäß der vorliegenden Erfindung werden die erste Leitfähigkeitsart und die Spannungsquelle ausgewählt, um den ersten SOI-Transistor von dem zweiten Transistor zu isolieren, so dass das Körpergebiet des ersten SOI-Transistors die Wirkung eines schwebenden Körpers aufweist, oder um das Körpergebiet so anzuschließen, dass das Körpergebiet keine Wirkung des schwebenden Körpers zeigt.

**[0010]** In der bevorzugten Ausführungsform verbindet eine ohmsche Verbindung das Übergangsgebiet mit der Spannungsquelle. Das Übergangsgebiet enthält ein relativ stark dotiertes Gebiet und ein relativ leicht dotiertes Gebiet, und die ohmsche Verbindung ist mit dem relativ stark dotierten Gebiet in Kontakt. Entsprechend der vorliegenden Erfindung umfasst der erste Transistor ein Sourcegebiet und ein Draingebiet mit der ersten Leitfähigkeitsart, und das Übergangsgebiet trennt den ersten SOI-Transistor von dem zweiten SOI-Transistor. In einer derartigen Ausführungsform weist der Körper des ersten SOI-Transistors die Auswirkungen eines schwebenden Zustands auf. Wenn im Gegensatz dazu der erste Transistor Source- und Drain-Gebiete aufweist, die eine zweite Leitfähigkeitsart entgegengesetzt zur ersten Leitfähigkeitsart aufweisen, verbindet das Übergangsgebiet das Körpergebiet des ersten SOI-Transistors mit der Spannungsquelle so, dass der Körper

des ersten SOI-Transistors im Wesentlichen keinen schwebenden Zustand bzw. einen Zustand mit frei einstellbaren Potential aufweist. Wenn die Source- und Draingebiete mit einem N-Dotiermittel dotiert sind, ist die Spannungsquelle vorzugsweise eine Transistor-Drain-Spannungsquelle, und wenn die Source- und Drain-Gebiete mit einem P-Dotiermittel dotiert sind, ist die Spannungsquelle vorzugsweise eine Transistor-Source-Spannungsquelle. Oder die Versorgungsspannungsquelle kann eine variable Spannung bereitstellen, um ein vorgespanntes Metall-Oxid-Silizium-(MOS)Bauelement zu bilden.

**[0011]** Des weiteren umfasst der SOI-Transistor ein Gate und das Bauelement kann ferner einen Leiter aufweisen, der das Gate und das Übergangsgebiet verbindet, um damit ein Metall-Oxid-Silizium-(DT-MOS)Bauelement mit dynamischen Schwellwert zu bilden. Alternativ kann der erste SOI-Transistor einen Emitter und ein Gate aufweisen, und ein Leiter verbindet das Gate und den Emitter, um einen lateralen bipolaren Transistor zu bilden. In einer derartigen Ausführungsform besitzt das Gate die erste Leitfähigkeitsart.

**[0012]** In einem weiteren Aspekt, der nicht Teil der beanspruchten Erfindung ist, umfasst ein Halbleiter-SOI-Verarmungs- bzw. Abschnürwiderstand, ein Siliziumsubstrat und eine Silizium-Oxid-Isolator-(SOI)Schicht auf dem Substrat. Es ist mindestens ein relativ leicht dotiertes Halbleitergebiet, das eine erste Leitfähigkeitsart aufweist, auf der SOI-Schicht ausgebildet. Ferner sind mindestens ein erstes und ein zweites deutlich stark dotiertes Halbleitergebiet mit der ersten Leitfähigkeitsart auf dem relativ leicht dotierten Halbleitergebiet angeordnet. Des weiteren ist mindestens eine Feldoxidschicht zwischen dem ersten und dem zweiten relativ stark dotierten Halbleitergebiet angeordnet und mindestens eine erste und eine zweite ohmsche Verbindung sind entsprechend mit dem ersten und dem zweiten relativ stark dotierten Halbleitergebiet in Verbindung.

**[0013]** In einem weiteren Aspekt, der nicht Teil der beanspruchten Erfindung ist, umfasst eine Halbleiter-SOI-Diode ein Siliziumsubstrat und eine Silizium-Oxid-Isolator-(SOI)Schicht auf dem Substrat. Mindestens ein relativ leicht dotiertes Halbleitergebiet mit einer ersten Leitfähigkeitsart ist auf der SOI-Schicht angeordnet, und mindestens ein erstes und ein zweites relativ stark dotiertes Halbleitergebiet, die entsprechend eine erste und eine zweite Leitfähigkeitsart aufweisen, sind auf dem relativ leicht dotierten Halbleitergebiet angeordnet. Die erste und die zweite Leitfähigkeitsart sind zueinander entgegengesetzt. Mindestens eine erste und eine zweite ohmsche Verbindung sind entsprechend mit dem ersten und dem zweiten relativ stark dotierten Halbleitergebiet in Verbindung.

[0014] Es ist ein Verfahren offenbart, das in Anspruch 1 beschrieben ist, um ein Silizium-Oxid-Isolator-(SOI)Bauelement zu betreiben. Das Verfahren umfasst das Anordnen mindestens einer SOI-Schicht auf mindestens einem Siliziumsubstrat und das Vorsehen mindestens eines Körpergebiets auf der SOI-Schicht, wobei das Körpergebiet sich dadurch auszeichnet, dass es eine erste Leitfähigkeitsart aufweist. Das Verfahren umfasst auch das nebeneinander Anordnen von einem Sourcegebiet und einem Draingebiet im Vergleich zu dem Körpergebiet, wobei das Sourcegebiet und das Draingebiet sich durch eine zweite Leitfähigkeitsart auszeichnen. Es ist mindestens ein Übergangsgebiet in der Nähe des Körpergebiets über der SOI-Schicht angeordnet, und das Übergangsgebiet zeichnet sich durch eine Übergangsleitfähigkeitsart aus. Wie nachfolgend detaillierter erläutert ist, wird die Übergangsleitfähigkeit als die erste Leitfähigkeitsart vorgesehen, um Auswirkungen des schwebenden Körpers in dem Körpergebiet zu unterdrücken. Andererseits wird die Übergangsleitfähigkeitsart als die zweite Leitfähigkeitsart eingerichtet, um das Körpergebiet abzutrennen.

[0015] In einem noch weiteren Aspekt umfasst ein Silizium-Oxid-Isolator-(SOI)Bauelement mindestens eine SOI-Schicht und mindestens ein Siliziumsubstrat, auf dem die SOI-Schicht angeordnet ist. Mindestens ein Körpergebiet ist auf der SOI-Schicht angeordnet, wobei das Körpergebiet sich durch eine erste Leitfähigkeitsart auszeichnet. Ferner sind mindestens ein Sourcegebiet und ein Draingebiet neben dem Körpergebiet angeordnet, wobei das Sourcegebiet und das Draingebiet sich durch eine zweite Leitfähigkeitsart auszeichnen. Es ist mindestens ein Übergangsgebiet in der Nähe des Körpergebiets über der SOI-Schicht angeordnet, wobei das Übergangsgebiet eine Übergangsleitfähigkeitsart aufweist. Entsprechend den nachfolgend erläuterten Prinzipien wird die Übergangsleitfähigkeit als die erste Leitfähigkeitsart eingerichtet, um Auswirkungen des schwebenden Körpers in dem Körpergebiet zu unterdrücken, und wird als die zweite Leitfähigkeitsart eingerichtet, um das Körpergebiet zu isolieren.

[0016] Weitere Merkmale der vorliegenden Erfindung gehen aus dem Abschnitt hervor mit dem Titel: „Detaillierte Beschreibung der Erfindung“

#### Kurze Beschreibung der Zeichnungen

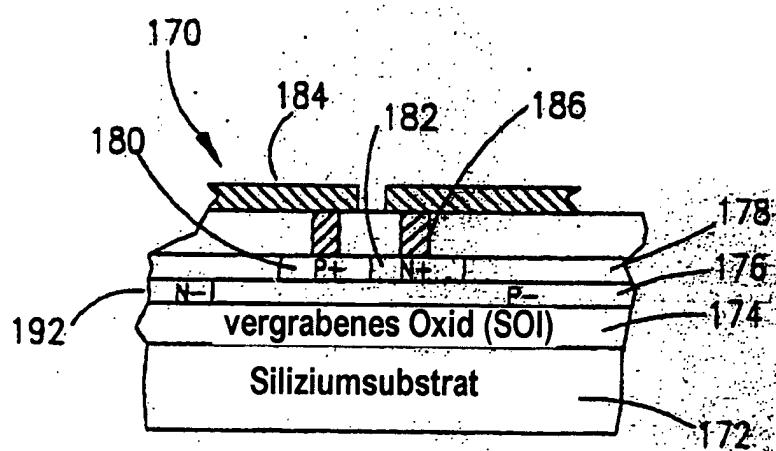

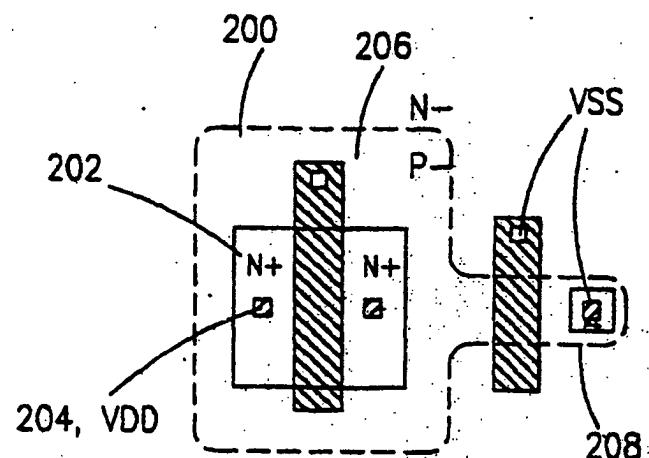

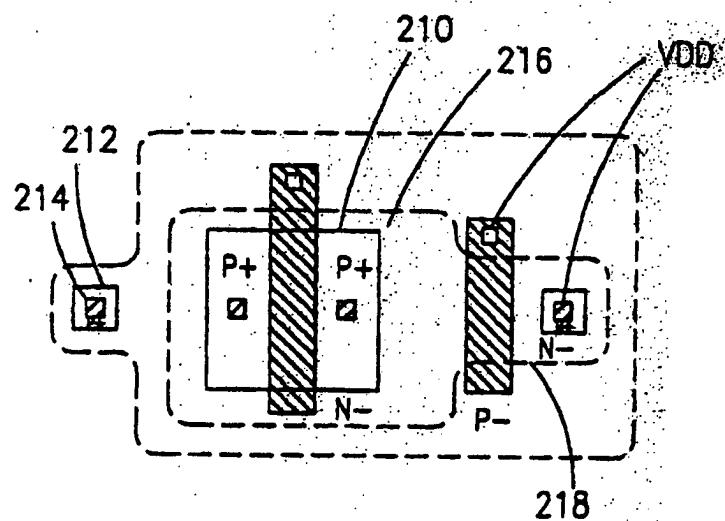

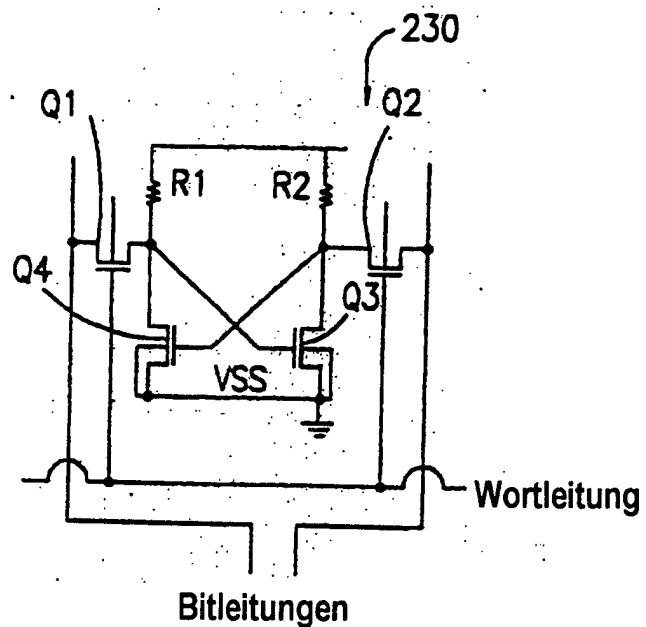

[0017] Für ein vollständigeres Verständnis der vorliegenden Erfindung wird auf die begleitenden Zeichnungen in der folgenden detaillierten Beschreibung für die beste Art zum Ausführen der vorliegenden Erfindung verwiesen. In den Zeichnungen sind im Allgemeinen Metallelemente mit Schraffur und Halbleiterelemente, mit Ausnahme von Draufsichten von Gategebieten, in unschraffierter Weise dargestellt.

[0018] Es zeigen:

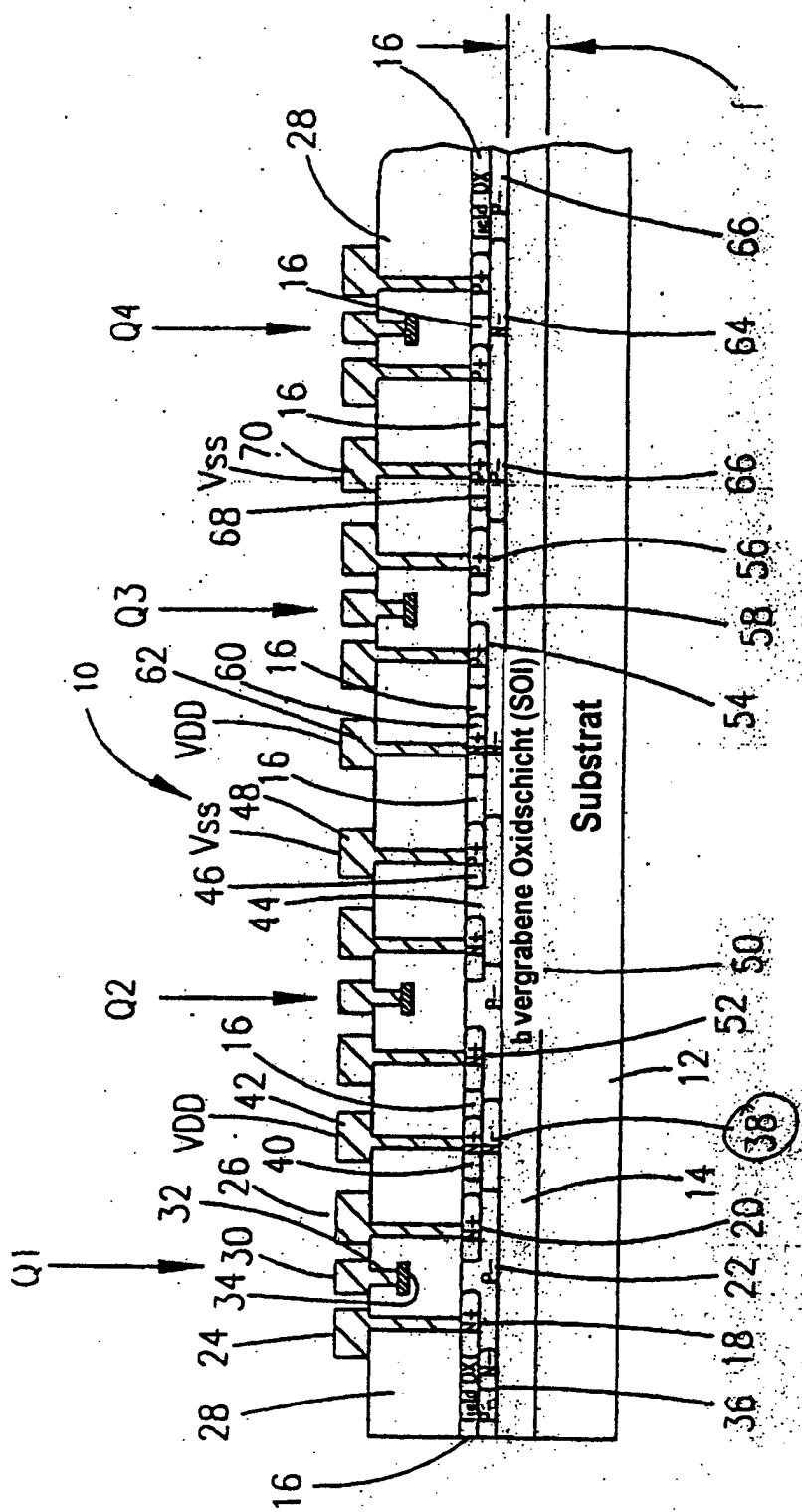

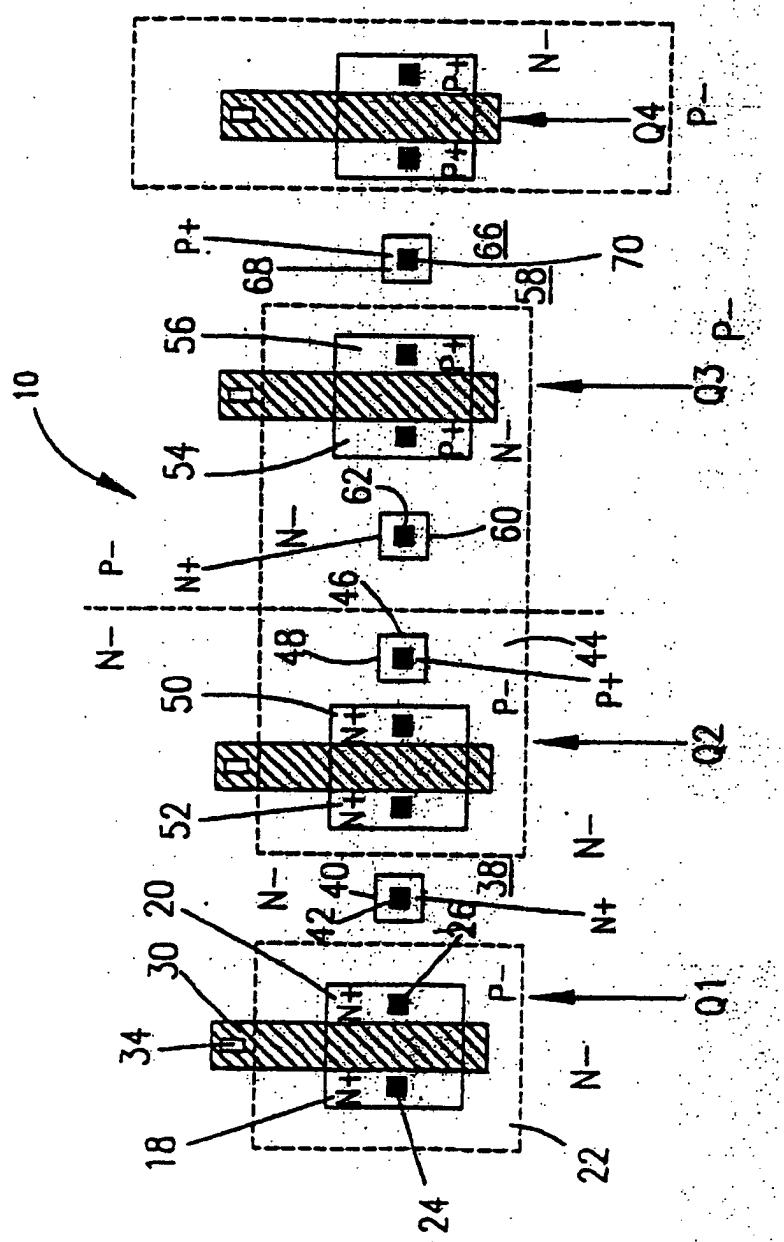

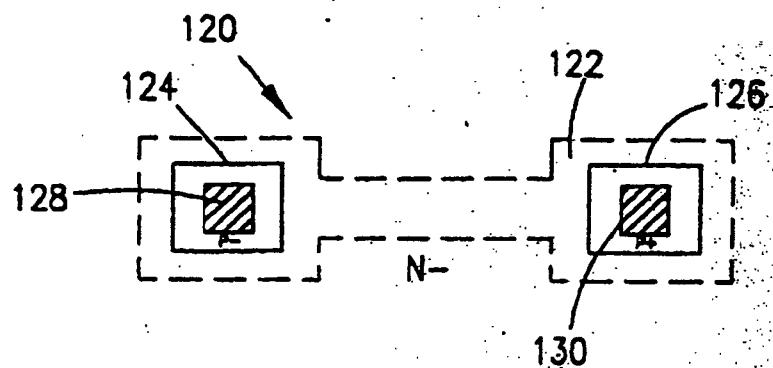

[0019] [Fig. 1](#) schematisch eine Draufsicht eines SOI-Bauelements mit vier Transistoren;

[0020] [Fig. 2](#) eine schematische Draufsicht des in [Fig. 1](#) gezeigten Bauelements, wobei Bereiche unvollständig gezeigt sind;

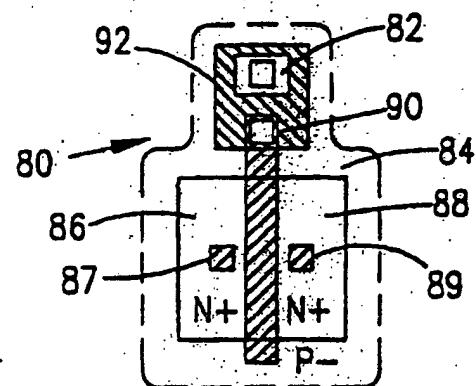

[0021] [Fig. 3](#) eine schematische Draufsicht eines SOI-DMOS der vorliegenden Erfindung ist;

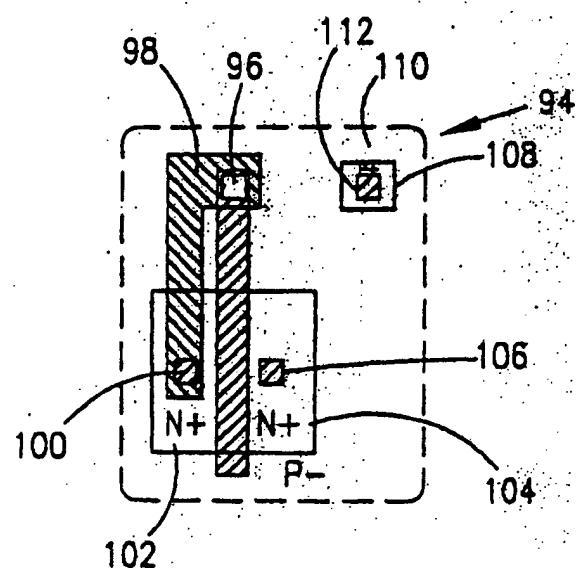

[0022] [Fig. 4](#) eine schematische Draufsicht eines SOI-NPN-Bipolartransistors der vorliegenden Erfindung ist;

[0023] [Fig. 5](#) eine schematische Draufsicht eines passiven SOI-Elements ist;

[0024] [Fig. 6](#) eine schematische Draufsicht eines passiven SOI-Abschnürwiderstands ist;

[0025] [Fig. 7](#) eine schematische Aufrissansicht des SOI-Abschnürwiderstands ist, der in den [Fig. 5](#) und [Fig. 6](#) gezeigt ist;

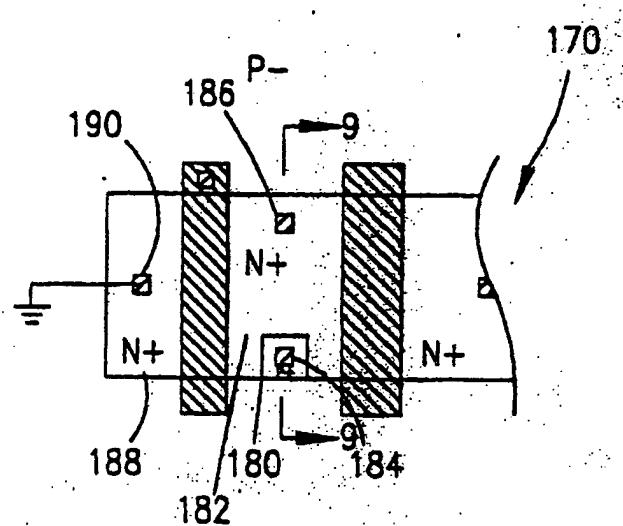

[0026] [Fig. 8](#) schematisch eine Draufsicht einer Hälfte einer SOI-Diode für Anwendungen in einem statischen Speicher mit wahlfreiem Zugriff (SRAM) ist;

[0027] [Fig. 9](#) eine schematische Querschnittsansicht der SOI-Diode ist, die in [Fig. 8](#) gezeigt ist, wie dies durch die Linie 9 in [Fig. 8](#) angegeben ist;

[0028] [Fig. 10](#) einen Körperanschluss mit hohem Widerstand für einen N-Kanaltransistor unter Anwendung eines Abschnürwiderstands zeigt;

[0029] [Fig. 11](#) einen Körperanschluss mit hohem Widerstand für einen P-Kanaltransistor unter Anwendung eines Abschnürwiderstands zeigt;

[0030] [Fig. 12](#) ein Schaltbild ist, das eine beispielhafte Schaltung zeigt, in der der erfindungsgemäße SOI-Abschnürwiderstand verwendet wird;

[0031] [Fig. 13](#) ein Schaltbild ist, das eine beispielhafte Schaltung darstellt, in der die vorliegenden SOI-Dioden verwendet sind; und

[0032] [Fig. 14](#) ein Schaltbild ist, in der eine beispielhafte analoge Schaltung mit Differenzverstärker unter Anwendung von SOI-Komponenten der vorliegenden Erfindung gezeigt ist.

[0033] In den diversen Figuren bezeichnen gleiche Bezugszeichen durchwegs die gleichen oder äquivalenten Teile der vorliegenden Erfindung.

## Detaillierte Beschreibung der Erfindung

[0034] Es sei zunächst auf die [Fig. 1](#) und [Fig. 2](#) verwiesen, in denen ein Silizium-Oxid-Isolator-(SOI)Bauelement gezeigt ist, das allgemein als **10** bezeichnet ist. Wie in [Fig. 1](#) am besten zu erkennen ist, umfasst das SOI-Bauelement **10** ein Siliziumsubstrat **12**, auf welchem eine Silizium/Oxid-Isolator-(SOI)Schicht **14** aufgebracht ist, die auch als eine „vergrabene Oxidschicht“ bezeichnet wird. Gemäß den SOI-Prinzipien kann die SOI-Schicht **14** eine Dicke „t“ von ungefähr 500 Angstrom bis ungefähr 4000 Angstrom (500 bis 4000 Angstrom) aufweisen, wobei 10 Angstrom gleich 1 nm sind. In der bevorzugten Ausführungsform ist das Siliziumsubstrat **12** leicht dotiert mit einem P-Dotiermittel mit ungefähr 50 Ohm-Zentimeter ( $\Omega \cdot \text{cm}$ ).

[0035] Eine Feldoxidschicht **16** ist auf der SOI-Schicht **12** angeordnet, und diverse Gebiete, die mit Dotiermitteln mit vorbestimmter Leitfähigkeitsart dotiert werden können, sind auf der SOI-Schicht **14** angeordnet und können durch eine teilweise erfolgte Oxidation der Feldoxidschicht **16** eingerichtet werden. In der beispielhaften gezeigten Ausführungsform sind ein N-Kanalsourcegebiet **18** und ein N-Kanal-Draingegebiet **20** mit Dotiermitteln mit einer Leitfähigkeit N<sup>+</sup> dotiert, wobei zu beachten ist, dass der Index „+“ in den Figuren eine relativ starke Dotierung angibt und die Bezeichnung „-“ in den Figuren eine relativ schwache Dotierung bezeichnet. Ferner ist ein N-Kanal-Körpergebiet **22** zwischen und unter den Source- und Drain-Gebieten **18, 20** angeordnet und ist mit einem P-Dotiermittel dotiert.

[0036] Um das Sourcegebiet **18** und das Draingegebiet **20** mit Schaltungselementen außerhalb des Bauelements **10** zu verbinden, wird eine Metall-N-Source-Elektrode **24** mit dem Sourcegebiet **18** und eine Metall-N-Kanal-Drain-Elektrode **26** mit dem Draingegebiet **20** verbunden, wobei die horizontal orientierten Bereiche der Elektroden **24, 26** von der Feldoxidschicht **16** durch eine dazwischenliegende Oxidschicht **28** getrennt sind. Andererseits enthält eine Metall-N-Kanal-Gateelektrode **30** einen Kontakt **32**, der sich zu dem N-Kanal-Körpergebiet **22** erstreckt, dessen Ende an einem Polysilizium-N-Kanalsteuergate **24** abschließt. Die zuvor beschriebene Struktur bildet ein isoliertes Schaltungselement in Form eines N-Kanaltransistors, das im Weiteren als „Q1“ bezeichnet wird.

[0037] Gemäß der vorliegenden Erfindung ist der Körper **22** des isolierten N-Kanaltransistors Q1 von den Spannungen in anderen ausgewählten Schaltungen, die in den [Fig. 1](#) und [Fig. 2](#) gezeigt sind, durch Übergangsgebiete abgetrennt. Wenn der Körper des Transistors der vorliegenden Erfindung zu trennen ist, wie dies für das Körpergebiet **22** des N-Kanaltransistors Q1 der Fall ist, sind die Übergangsgebiete

N-Übergangsisolationsgebiete **36, 38**, die entsprechend die linke bzw. rechte Seite ([Fig. 1](#)) des Körpergebiets **22** begrenzen und die sich bis zu der SOI-Schicht **14** nach unten erstrecken.

[0038] Gemäß der vorliegenden Erfindung sind die Isolationsgebiete **36, 38** relativ leicht dotiert mit einem Dotiermittel mit einer Leitfähigkeitsart, die sich von jener des Körpers **22** unterscheidet. Da der Transistor Q1 ein N-Kanaltransistor ist, sind die Isolationsgebiete **36, 38** daher mit einem N-Dotiermittel dotiert, wie dies in den [Fig. 1](#) und [Fig. 2](#) gezeigt ist. In einer gegenwärtig bevorzugten Ausführungsform sind die Isolationsgebiete **36, 38** auf ungefähr  $10^{14}$  Atome pro  $\text{cm}^3$  bis  $10^{18}$  Atome pro  $\text{cm}^3$  dotiert, und sind noch besser mit  $10^{16}$  Atomen pro  $\text{cm}^3$  bis  $10^{18}$  pro  $\text{cm}^3$  dotiert.

[0039] Ferner enthält das rechte Isolationsgebiet **38** ein relativ stark dotiertes Verbindungsgebiet **40** (beispielsweise mit ungefähr  $10^{19}$  bis  $10^{21}$  Atomen pro  $\text{cm}^3$ ). Wie in den [Fig. 1](#) und [Fig. 2](#) gezeigt ist, ist das Verbindungsgebiet **40** mit einem Dotiermittel der gleichen Leitfähigkeitsart wie das Isolationsgebiet **38** dotiert. Auch ist das Verbindungsgebiet **40** vorteilhaftweise mit einer ohmschen Verbindung verbunden, etwa einer Isolationselektrode **42** oder einer Polysiliziumverbindung, die wiederum mit einer Versorgungsspannung verbunden ist. Wenn das Verbindungsgebiet **40** mit einem N-Dotiermittel dotiert ist, ist die Isolationselektrode **42** vorzugsweise mit einer Versorgungsspannung VDD für die Drain-Leistungsversorgung des Transistors Q1 verbunden. Es ist zu beachten, dass die obigen Prinzipien auch für das entgegengesetzte Dotiermittel gelten, wenn isolierte P-Kanaltransistoren betrachtet werden, etwa der nachfolgend erläuterte Transistor Q4, wobei die Versorgungsspannung in einem derartigen Falle vorzugsweise die Source-Versorgungsspannung VSS ist. Des weiteren ist zu beachten, dass die Körpergebiete von verbundenen Transistoren über oder unterhalb von VSS/VDD in geeigneter Weise vorgespannt sein können, oder diese können mit einem festgelegten Potential fest verdrahtet sein, wie dies zuvor beschrieben ist, oder diese können in selektiver Weise mit einer Schaltung mit Vorspannung beaufschlagt werden, beispielsweise mit VDD + 0,5 Volt für den Betrieb in Wartezustand (standby) und mit VDD – 1,0 Volt für die aktive Funktion.

[0040] Unter Berücksichtigung des zuvor gesagten ist zu beachten, dass das Körpergebiet **22** durch die Übergangsgebiete (Isolationsgebiete) **36, 38** getrennt ist. Obwohl das Körpergebiet **22** die Wirkung des schwebenden Körpers aufweisen kann, kann erfindungsgemäß das Isolieren des Körpers **22**, wie dies gezeigt ist, den isolierten N-Kanaltransistor Q1 vorteilhaft für beispielsweise sehr geringe Spannungen (unter 2 Volt) machen, wie dies beispielsweise in gewissen SRAM-Anwendungen der Fall ist.

**[0041]** In jedem Falle wird, wie weiter mit Bezug zu den [Fig. 1](#) und [Fig. 2](#) erläutert ist, durch die Verwendung der ohmschen Verbindungen in Verbindung mit Übergangsgebieten dem Schaltungsgestalter die Möglichkeit gegeben, das Körpergebiet eines SOI-Transistors (beispielsweise des isolierten N-Kanaltransistors Q1) von anderen Schaltungselementen, etwa einem zweiten Transistor (beispielsweise den verbunden N-Kanaltransistor Q2) selektiv zu trennen, so dass das Körpergebiet des ersten SOI-Transistors die Wirkung des sich selbst einstellenden Potentials aufweist, wie dies zuvor beschrieben ist. Oder durch die Verwendung von ohmschen Verbindungen im Zusammenwirken mit den Übergangsgebieten erhält die betroffene Schaltung die Option, das Körpergebiet eines Transistors so anzuschließen, dass das Körpergebiet nicht die Auswirkung des schwebenden Körpers aufweist, wie dies nachfolgend beschrieben ist. Insbesondere sei nun auf den angeschlossenen N-Kanaltransistor Q2 verwiesen, der in den [Fig. 1](#) und [Fig. 2](#) gezeigt ist, wobei der Transistor Q2 ein Körpergebiet **44** aufweist, das mit einem P-Dotiermittel dotiert ist, und wobei das Körpergebiet **44** über ein N<sup>+</sup>-Kontaktgebiet **46** mit einer externen Spannungsversorgung über einem Kontakt **48** verbunden ist. In dem breiten Sinne der vorliegenden Erfindung repräsentiert das Kontaktgebiet **46** ein Übergangsgebiet.

**[0042]** Wie zuvor erwähnt ist, wird der Kontakt **48** vorzugsweise mit der Versorgungsspannung für das Source VSS des Transistors verbunden, wenn der Transistor Q2 ein N-Kanaltransistor ist (d. h. ein Transistor mit einem P-dotierten Körpergebiet **44** und einem N<sup>+</sup> dotierten Drain- und Sourcegebiet **50**, **52**), der mit einer externen Spannungsquelle zu verbinden ist. Alternativ kann der Kontakt **48** mit einer variablen Spannungsquelle verbunden werden, so dass das Übergangsverbindungsgebiet **46** einen Steueranschluss für beispielsweise einen spannungssteuerten Oszillator (VCO) in einer Phasenregelschaltung bilden kann. Somit ist anders als der schwebende Körper des Transistors Q1 der Körper des Transistors Q2 mittels eines ohmschen Kontakts mit einer Spannungsreferenz verbunden, wodurch die oftmals unerwünschten Auswirkungen des „schwebenden Körpers“, die normalerweise mit der SOI-Technologie verknüpft sind, minimiert oder umgangen werden.

**[0043]** Die [Fig. 1](#) und [Fig. 2](#) zeigen einen angeschlossenen P-Kanaltransistor Q3, der das inverse Bauteil des angeschlossenen N-Kanaltransistors Q2 ist. Genauer gesagt, der angebundene P-Kanaltransistor Q3 umfasst P-dotierte Source- und Drain-Gebiete **54**, **56** und ein N<sup>-</sup> Körpergebiet **58**, und das Körpergebiet **58** ist mit einer externen Spannungsversorgung durch ein P<sup>+</sup>-dotiertes Übergangsgebiet **60** und einen Kontakt **63**, der damit verbunden ist, angeschlossen. Der Kontakt **62** ist wiederum mit einer Ver-

sorgungsspannung in Verbindung, vorzugsweise der Drain-Spannung VDD, um den Körper **58** des angeschlossenen P-Kanaltransistors Q3 mit der Versorgungsspannung zu verbinden. Dadurch werden die Auswirkungen des schwebenden Körpers in dem Transistor Q3 im Wesentlichen unterdrückt.

**[0044]** Fernen kann ein isolierter P-Kanaltransistor Q4 bereitgestellt werden, der das inverse Bauelement des isolierten N-Kanaltransistors Q1 ist, indem der N<sup>-</sup> dotierte Körper **64** des isolierten P-Kanaltransistors Q4 von externen Spannungen abgetrennt ist. Insbesondere umfasst der Transistor Q4 ein Übergangsgebiet, das ein P<sup>-</sup> dotiertes Isolationsgebiet **66** ist, das ein relativ stark dotiertes P<sup>+</sup> Verbindungsgebiet **68** enthält. Das Verbindungsgebiet **68** ist mit einem Kontakt **70** verbunden, der wiederum mit einer Versorgungsspannung VDD für die Drain-Versorgungsspannung des Transistors Q4 verbunden ist.

**[0045]** Die zuvor beschriebenen Strukturen können unter Anwendung zweier Masken hergestellt werden, wobei eine für das N-Gebiet und eine für das P-Gebiet dient. Oder es kann eine selbstjustierende Lösung eingesetzt werden, in der andere Alternativen, etwa Siliziumnitrid als Hardmaske verwendet werden, um damit entsprechende Feldimplantationsgebiete herzustellen, die den N- oder P-Übergangsgebieten entsprechen, wie sie zuvor beschrieben sind, wobei anschließend die Siliziumnitridmaske entfernt wird und die verbleibenden Implantationsgebiete als P- oder N-Übergangsgebiete dienen.

**[0046]** Obwohl sich die vorhergehende Offenbarung darauf konzentriert, Übergangsgebiete mit Konstantspannungsquellen zu verbinden, umfasst die vorliegende Erfindung auch, dass Übergangsgebiete in schwebenden SOI-Körpern mit variablen Spannungen verbunden werden können, falls dies gewünscht ist. Um beispielsweise die Leistungsaufnahme in integrierten Schaltungen für Mobiltelefone zu reduzieren, kann die Schaltung selektiv deaktiviert werden, wobei der Strom im Aus-Zustand der Transistoren in der Schaltung weiter reduziert werden kann, indem eine negative Spannung an die Übergangsgebiete in den N-Kanal-Körpergebieten und eine positive Spannung an die Übergangsgebiete in dem P-Kanal-Körpergebieten angelegt wird, wodurch die Leckströme unterhalb des Schwellwertes reduziert werden. Analoge Schaltungen können in ähnlicher Weise verbessert werden, um damit geringere Leckströme zu erreichen. Ferner können derartige Schaltungen auch auf Masse gelegt werden oder in Vorwärtsrichtung vorgespannt werden, indem Spannungen an die Übergangsgebiete für Funktionen, etwa Stromspiegel oder Stromquellen, angelegt werden.

**[0047]** [Fig. 3](#) zeigt eine Metall-Oxid-Silizium-Transistor in Form eines SOI-N-Kanalbauelements mit dynamischem Schwellwert (DTMOS) **80**, der ein P<sup>+</sup>-

Übergangsgebiet **82** aufweist, das in einem P<sup>-</sup>-Körpergebiet **84** angeordnet ist. Der DTMOS **80** enthält ferner ein N<sup>+</sup>-Sourcegebiet **86** mit einer Elektrode **87**, ein N<sup>+</sup>-Draingegebiet **88** mit einer Elektrode **89** und ein Gate **90**. Wie gezeigt ist, verbindet eine ohmsche Verbindung, etwa eine Metallelektrode **92** das Gate **90** mit dem Übergangsgebiet **82**, um den DTMOS **80** zu bilden. Zu beachten ist, dass ein P-Kanal DTMOS unter Anwendung der obigen Prinzipien auch aufgebaut werden kann, indem die Dotierstoffarten invertiert werden.

**[0048]** Es sei nun auf [Fig. 4](#) verwiesen. Zu beachten ist, dass das erfindungsgemäße Übergangsgebiet mit der ohmschen Verbindung auch verwendet werden kann, um einen SOI-NPN-Bipolartransistor **94** zu bilden, der für Bandlückenreferenzanwendungen, Stromspiegelanwendungen und andere analoge Schaltungsanwendungen geeignet ist. Wie in [Fig. 4](#) gezeigt ist, enthält der Bipolartransistor **94** ein Gate **96**, das über eine ohmsche Verbindung **98** mit der Elektrode **100** eines N<sup>+</sup> Emitters **102** verbunden ist. Alternativ kann das Gate **96** mit einer separaten Spannungsquelle mit festgelegter oder variabler Spannung (nicht gezeigt) verbunden sein. Der Bipolartransistor **94** umfasst ferner einen N<sup>+</sup>-Kollektor **104** mit einer Elektrode **106**.

**[0049]** In der in [Fig. 4](#) gezeigten Ausführungsform ist das Übergangsgebiet ein P<sup>+</sup> dotiertes Übergangsgebiet **108**, das in einem P<sup>-</sup> dotierten Basisgebiet **110** angeordnet ist. Eine ohmsche Verbindung **112** verbindet das Übergangsgebiet **108** mit einer externen Spannungsquelle. Mit diesem Aufbau wir das N<sup>+</sup>-Sourcegebiet eines N-Kanaltransistors zu einem N<sup>+</sup>-Emitter eines Bipolartransistors, während das N<sup>+</sup>-Draingegebiet eines N-Kanaltransistors zu einem N<sup>+</sup>-Kollektors einer Bipolartransistors wird. Bei Bedarf kann das Beta (N<sub>Fe</sub>) des Bipolartransistors **94** durch diverse Gateabmessungen variabel gestaltet werden, und kann elektrisch durch Variieren der Gatespannung variiert werden. Wie bei den anderen beispielhaften Ausführungsformen, die hierin gezeigt sind, kann das in [Fig. 4](#) gezeigte Bauelement auch in inverser Form aufgebaut werden, d. h. als ein PNP-Bipolartransistor, indem die zuvor offenbarten Dotierstoffarten umgekehrt werden.

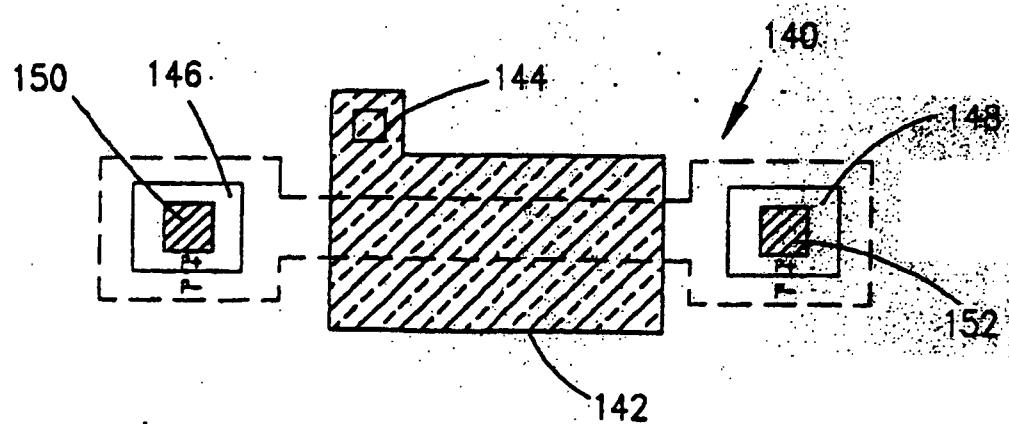

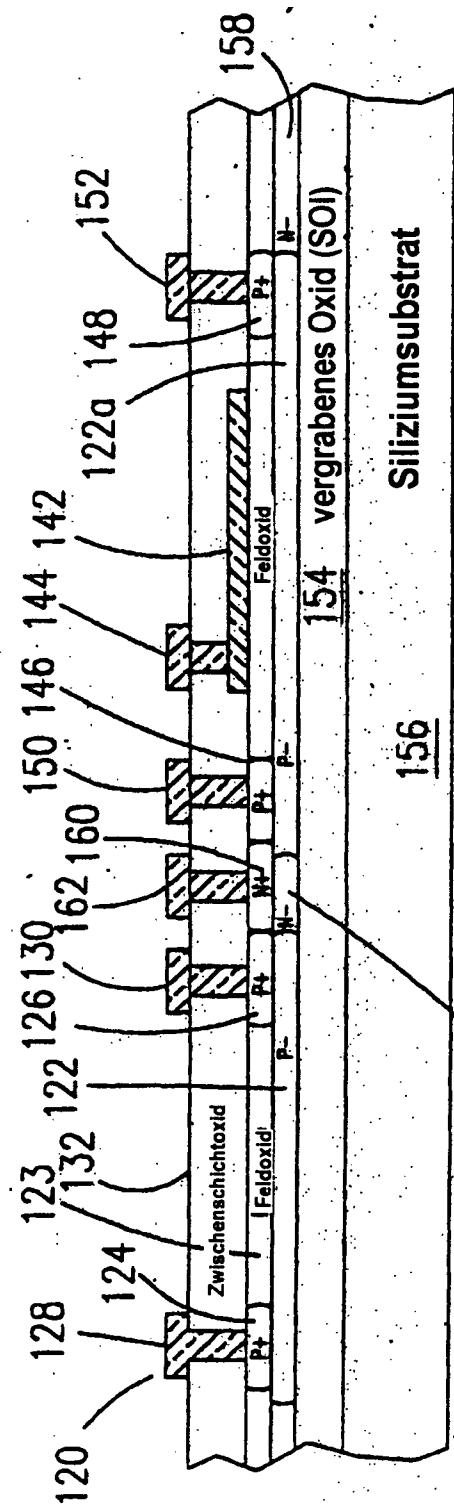

**[0050]** [Fig. 5](#) bis [Fig. 7](#) zeigen, dass die erfindungsgemäßen Prinzipien auf passive Schaltungselemente, etwa Abschnürwiderstände für Anwendungen mit sehr hohen Widerstandswerten, angewendet werden können. [Fig. 5](#) bis [Fig. 7](#) zeigen Abschnürwiderstände mit P-Verhalten, obwohl auch zu beachten ist, dass Abschnürwiderstände mit N-Verhalten unter Anwendung der hierin offenbarten Prinzipien durch Invertieren der Dotierstoffarten hergestellt werden können.

**[0051]** Wein [Fig. 5](#) und [Fig. 7](#) gezeigt ist, umfasst

ein SOI-Abschnürwiderstand, der allgemein als **120** bezeichnet ist, ein P<sup>-</sup> Feldgebiet **112** unter einem Feldoxidgebiet **123**, und zwei P<sup>+</sup> Übergangsgebiete **124**, **126**, die darin angeordnet und voneinander abstandet sind. Eine entsprechende ohmsche Verbindung **128**, **130**, die vorzugsweise aus einem leitenden Material, etwa Metall oder Polysilizium, hergestellt ist, erstreckt sich durch eine dazwischenliegende Oxidschicht **130** und verbindet jedes Übergangsgebiet **124**, **126** mit externen Schaltungskomponenten.

**[0052]** Die [Fig. 6](#) und [Fig. 7](#) zeigen einen Abschnürwiderstand **140**, der in allen wesentlichen Punkten identisch zu dem Abschnürwiderstand **120** ist, der in den [Fig. 5](#) und [Fig. 7](#) gezeigt ist, mit der Ausnahme, dass eine Polysiliziumfeldelektrode **140** in der Zwischenoxidschicht **132** über der Feldoxidschicht **123** angeordnet und mit einer externen Spannungsquelle durch eine ohmsche Abschnürverbindung aus Polysilizium **144** verbunden ist. Die Feldelektrode **142** erstreckt sich zwischen den beiden P<sup>+</sup> Übergangsgebieten **146**, **148** (mit entsprechenden ohmschen Verbindungen **150**, **152**), die in einem Bereich **122a** des P<sup>-</sup> Feldes **122** angeordnet sind, das unter der Feldelektrode **142** liegt. Wie gezeigt, sind die P<sup>-</sup> Felder **122**, **122a** auf einer SOI-Schicht **154** angeordnet, die wiederum auf einem Siliziumvollsubstrat **156** angeordnet ist.

**[0053]** Wie durch die vorliegende Erfindung gezeigt ist, kann die Feldelektrode **142** mit der Abschnürverbindung **144** verwendet werden, um die Leitfähigkeit des P<sup>-</sup> Feldgebiets **122a** zu modulieren. Genauer gesagt, der Widerstand des P<sup>-</sup> Gebiets **122a** kann durch Vorspannen der Feldelektrode **142** mit einer negativen Spannung erhöht werden, wohingegen der Widerstand des P<sup>-</sup> Gebiets **122** verringert werden kann, indem die Feldelektrode **142** mit einer positiven oder negativen Spannung vorgespannt wird. Einige der Anwendungen der Abschnürwiderstände **120**, **140**, zu denen Anwendungen mit Analogschaltungen und statische RAM's mit Widerstandslasten gehören, sind nachfolgend erläutert.

**[0054]** Ein N<sup>-</sup> Isolationsgebiet **158** erstreckt sich vertikal zwischen der Feldoxidschicht **122** und der SOI-Schicht **154** und lateral zwischen den Widerständen **120**, **140**, um die Widerstände **120**, **140** zu trennen. Gemäß der vorliegenden Erfindung enthält das N<sup>-</sup> Isolationsgebiet **158** ein N<sup>+</sup> Kontaktgebiet **160**, und eine ohmsche Verbindung **162** verbindet das Kontaktgebiet **160** mit einer Spannung, beispielsweise VDD. Das P<sup>-</sup> Gebiet **122** kann dotiert sein mit beispielsweise 1000 Ohm pro Einheitsfläche bis 1 Million Ohm pro Einheitsfläche.

**[0055]** [Fig. 8](#) und [Fig. 9](#) zeigen eine SOI-PN-Diode, die nicht Teil der beanspruchten Erfindung ist, und die im Allgemeinen als **170** bezeichnet ist. Wie in [Fig. 9](#)

gezeigt ist, enthält die Diode **170** ein Siliziumvollsubstrat **172**, auf der eine SOI-Schicht **174** angeordnet ist. Ein P<sup>-</sup> Körpergebiet **176** ist auf der SOI-Schicht **176** angeordnet, und eine Feldoxidschicht **178** ist auf dem Körpergebiet **176** angeordnet. Benachbart zu der Feldoxidschicht **178** sind zusammenhängende P<sup>+</sup> Diodengebiete angeordnet, die als **180**, **182** gezeigt sind. Jedes Diodengebiet **180**, **182** ist mit einer entsprechenden ohmschen Verbindung **184**, **186** in Kontakt, um eine Spannungsquelle oder ein anderes Schaltungselement mit dem jeweiligen Diodengebiet **180**, **182** zu verbinden. Im Falle des P<sup>+</sup> Diodengebiets **180** kann die ohmsche Verbindung **184** mit VDD verbunden werden oder kann mit einem Schaltungssignalknotenpunkt verbunden werden. Ein N<sup>+</sup> Übergangsgebiet **188** kann über eine ohmsche Verbindung **100** mit Masse oder alternativ mit einer Spannungsquelle verbunden werden. Das Übergangsisolationsgebiet **192** ist ein N<sup>-</sup> Dotiergebiet, das das Körpergebiet **176** von anderen integrierten Schaltungskomponenten und Strukturen (nicht gezeigt) trennt.

**[0056]** Mit dem obigen Aufbau wird auf Grund des erhöhten Diodensperrstromes der P<sup>+</sup>/N<sup>+</sup> Diode eine Möglichkeit geschaffen, diese als eine SRAM-Zelllast zu verwenden, vorausgesetzt, dass der Leckstrom des zugeordneten N-Kanaltransistors wesentlich kleiner ist als der Diodenleckstrom.

**[0057]** [Fig. 10](#) und [Fig. 11](#) zeigen hochohmige Körperkontakte unter Anwendung von Abschnürwiderständen. In [Fig. 10](#) ist ein N-Kanaltransistor **200** durch ein N<sup>+</sup> Übergangsgebiet **202** mit einer ohmschen Verbindung **204**, die vorzugsweise mit VDD verbunden ist, abgetrennt. Auch der P<sup>-</sup> Körper **206** des N-Kanaltransistors **200** ist mit VSS unter Anwendung eines Abschnittswiderstands **208**, der auch das Körpergebiet nutzt, verbunden.

**[0058]** In ähnlicher Weise zeigt [Fig. 11](#) einen P-Kanaltransistor **210**, der mittels eines P<sup>+</sup> Übergangsgebiets **212** mit einer ohmschen Verbindung **214**, die vorzugsweise mit VSS verbunden ist, abgetrennt ist. Der N<sup>-</sup> Körper **216** des P-Kanaltransistors **210** ist mit VDD unter Anwendung eines Abschnürwiderstands **218** verbunden.

**[0059]** Die in den [Fig. 10](#) und [Fig. 11](#) gezeigten Bauelemente sind Hybrid-SOI-Bauelemente mit schwebendem Körper, wobei die mittlere Gleichspannung durch die Abschnürwiderstände **208**, **218** auf VSS, VDD (oder eine andere bevorzugte Spannung) eingestellt wird, wie dies gezeigt ist. Mit einer relativ großen kapazitiven Kopplung zwischen dem Gate und der Kanal wird jedoch der Körper durch Signalübergänge dynamisch vorgespannt, wodurch sich der Körpervorspannkoeffizient (der im Stand der Technik mit dem griechischen Buchstaben  $\xi$  bezeichnet wird) reduziert wird. Folglich werden die Verstärkung, der dynamische  $ID_{SAT}$  und der dynamische  $ID_{off}$

verbessert. Dies ist insbesondere vorteilhaft bei geringen Betriebsspannungen. Ferner ergeben Schaltungssimulatoren genaue Vorhersagen, wenn die in den [Fig. 10](#) und [Fig. 11](#) gezeigten Bauelemente modellmäßig berechnet werden, da eine mittlere Körpervorspannung in genauer Weise bekannt ist. Andererseits wird die Schaltungsentwurfszeit deutlich verkürzt. Die Körpervorspannung entkoppelt durch den Abschnürwiderstand die Referenzvorspannung in Bezug auf das Wechselstromverhalten, so dass die Schaltungsgeschwindigkeit der Hybridbauelemente, die in den [Fig. 10](#) und [Fig. 11](#) gezeigt sind, in etwa gleich sind der Arbeitsgeschwindigkeit von Bauelementen mit schwebendem Körper. Es kann ein einzelner Abschnürwiderstand verwendet werden, um viele Transistorgruppen vorzuspannen.

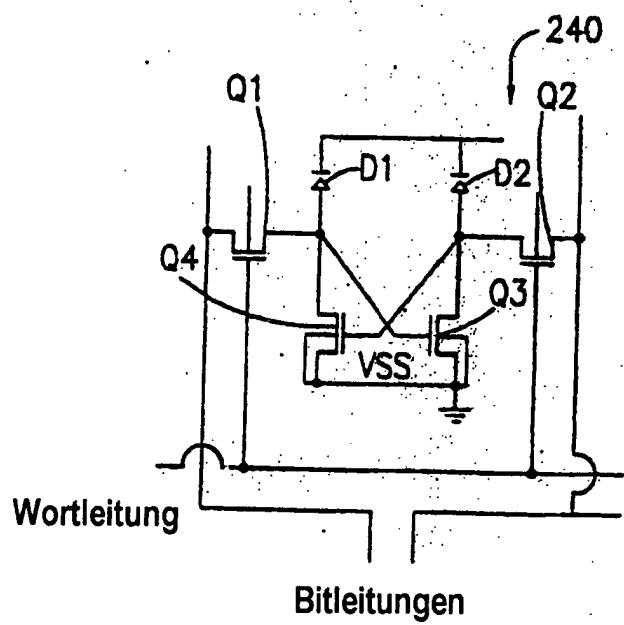

**[0060]** [Fig. 12](#) bis [Fig. 14](#) zeigen diverse Schaltungsimplementierungen der zuvor offenbarten Bauelemente. In [Fig. 12](#) kann eine Schaltung, die allgemein als **230** bezeichnet ist, als eine SRAM-Zelle eingesetzt werden. Wie gezeigt, enthält die Schaltung **230** Abschnürwiderstände **R1** und **R2**, die jeweils einer von den Abschnürwiderständen **120**, **140** sein können, wie sie in den [Fig. 5](#) bis [Fig. 7](#) gezeigt sind. Die Abschnürwiderstände **R1**, **R2** sind mit einem Anschluss an VDD geklemmt und liegen in Reihe mit den SOI-Transistoren mit schwebendem Körper **Q1**, **Q2** und sind mit den entsprechenden Transistoren mit angeschlossenem Körper **Q3**, **Q4** verbunden. Jeder der Transistoren mit schwebendem Körper **Q1** und **Q2**, die in [Fig. 12](#) gezeigt sind, können entsprechend dem Aufbau des N-Kanaltransistor mit schwebenden Körper **Q1** hergestellt werden, wie er in den [Fig. 1](#) und [Fig. 2](#) gezeigt ist. Andererseits sind die Transistoren **Q3** und **Q4** in [Fig. 12](#) SOI-Transistoren mit angeschlossenem Körper, etwa der N-Kanaltransistor **Q2** mit angeschlossenem Körper, der in den [Fig. 1](#) und [Fig. 2](#) gezeigt ist. Zu beachten ist, dass eine Schaltung unter Anwendung von P-Kanalkomponenten angewendet werden kann. Die Gates der Transistoren mit schwebendem Körper **Q1**, **Q2** sind mit der Wortleitung der SRAM-Lastschaltung, die gezeigt ist, verbunden, und das Sourcegebiet oder Draingebiet der Transistoren mit schwebenden Körper **Q1**, **Q2** ist mit den Bitleitungen verbunden.

**[0061]** [Fig. 13](#) zeigt in ähnlicher Weise eine SRAM-Lastschaltung, die allgemein als **240** gezeigt ist, in der Dioden **D1** und **D2**, etwa die Diode **170**, die in [Fig. 9](#) gezeigt ist, durch Abschnürwiderstände, wie sie in [Fig. 12](#) gezeigt sind, ersetzt sind. Die Dioden **D1**, **D2** sind mit einem Anschluss an VDD geklemmt und liegen in Reihe mit einem entsprechenden der SOI-Transistoren mit schwebendem Körper **Q1** bzw. **Q2** und dem jeweiligen Transistor mit angeschlossenem Körper **Q3** bzw. **Q4**. Jeder der Transistoren mit schwebendem Körper **Q1** und **Q2**, die in [Fig. 13](#) gezeigt sind, kann durch den N-Kanaltransistor mit schwebendem Körper **Q1**, wie er in den [Fig. 1](#) und

**Fig. 2** gezeigt ist, eingerichtet werden. Andererseits sind die Transistoren Q3 und Q4 in **Fig. 13** SOI-Transistoren mit angeschlossenem Körper, etwa dem N-Kanaltransistor mit angeschlossenem Körper Q2, wie er in den **Fig. 1** und **Fig. 2** gezeigt ist. Es ist zu beachten, dass eine Schaltung unter Anwendung von P-Kanalkomponenten ebenso eingesetzt werden kann. Die Gates der Transistoren mit schwebendem Körper Q1, Q2 sind mit der Wortleitung der gezeigten SRAM-Lastschaltung verbunden und das Sourcegebiet und das Draingebiet der Transistoren mit schwebendem Körper Q1, Q2 ist mit den Bitleitungen verbunden.

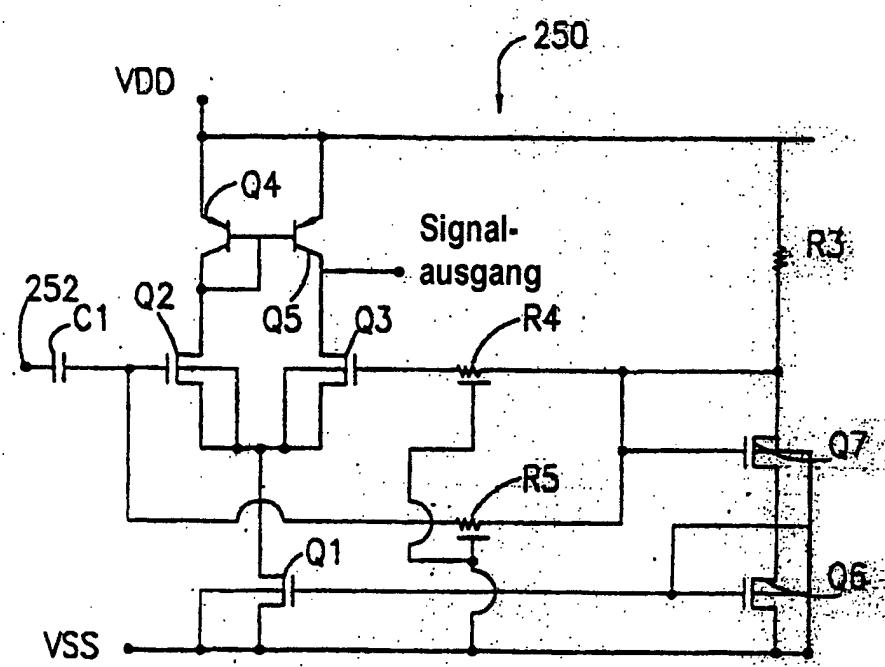

**[0062]** In **Fig. 14** ist eine analoge Differenzverstärkerschaltung **250** mit einem Signalknoten **252** über einen Kondensator C1 verbunden. Wie gezeigt, enthält die Schaltung **252** SOI-PN-Bipolartransistoren Q4, Q5. Jeder der Transistoren Q4, Q5, der in **Fig. 14** gezeigt ist, kann durch einen PNP-Bipolartransistor repräsentiert sein, der das Inverse des in **Fig. 4** gezeigten NPN-Transistors **94** ist. Ferner enthält die in **Fig. 14** gezeigte Schaltung **250** SOI-N-Kanaltransistoren Q2 und Q3, deren Körper mit deren eigenen gemeinsamen Source (anstelle von VSS) verbunden sind, wobei die Transistoren Q2, Q3 mit den jeweiligen bipolaren Transistor Q4, Q5 verbunden sind. Ferner ist ein N-Kanaltransistor mit angeschlossenem Körper Q1 mit den Transistoren mit schwebendem Körper Q2, Q3 verbunden. Gemäß den vorliegenden Prinzipien können die N-Kanaltransistoren mit angeschlossenem Körper oder vorgespanntem Körper in der Schaltung **250**, wie sie in **Fig. 14** gezeigt sind, Transistoren des Typs Q2 sein, wie er in den **Fig. 1** und **Fig. 2** gezeigt ist. Ferner können die N-Kanaltransistoren mit angeschlossenem Körper in der in **Fig. 14** gezeigten Schaltung **250** von der Art der Transistoren Q2 sein, wie sie in den **Fig. 1** und **Fig. 2** gezeigt sind, mit der folgenden Ausnahme. Die N-Kanaltransistoren mit angeschlossenem Körper in der Schaltung **250**, wie sie in **Fig. 14** gezeigt ist, besitzen Körper, die mit VSS verbunden sind. Wenn für eine gewisse Betrachtung einer speziellen Schaltung einer der Transistoren ein besseres Verhalten mit einem schwebenden Körper aufweist, dann können der N-Kanaltransistor Q1 oder der P-Kanaltransistor Q4, die in den **Fig. 1** und **Fig. 2** gezeigt sind, eingesetzt werden, ohne dass Änderungen in der Scheibenherstellung erforderlich sind.

**[0063]** **Fig. 14** zeigt, dass das Gate des N-Kanaltransistors mit schwebendem Körper Q3 mit einem SOI-Abschnürwiderstand R4 verbunden ist, der vorzugsweise eine Polysiliziumgateelektrode besitzt. Folglich kann der Abschnürwiderstand R4 durch den Abschnürwiderstand **140** eingerichtet werden, der in **Fig. 6** gezeigt ist. Die Polysiliziumfeldelektrode des Abschnürwiderstands R4 ist mit einer Polysiliziumfeldelektrode eines zweiten Abschnürwiderstands R5 verbunden. Ferner sind mit den Abschnittswiderständen

den R4, R5 SOI-N-Kanaltransistoren Q6, Q7, wobei der Transistor Q6 ein SOI-Transistor mit angeschlossenem Körper und der Transistor Q7 ein SOI-Transistor mit vorgespanntem angeschlossenen Körper ist.

**[0064]** Ein Abschnürwiderstand R3 erzeugt die Vorspannung für die Transistoren mit angeschlossenem Körper Q1, Q6, Q7. Gemäß der vorliegenden Erfindung sind die Transistoren mit angeschlossenem Körper Q1, Q6 und Q7 Stromspiegeltransistoren. Der hohe Widerstand des Abschnürwiderstands R3 ermöglicht das Einstellen einer Vorspannung mit geringem Strom für die Transistoren mit angeschlossenem Körper Q1, Q6 und Q7 für Anwendungen bei geringen Differenzströmen. Wie hierin gezeigt ist, sind die bestehenden N<sup>+</sup> oder P<sup>+</sup> Schichtwiderstände in ihren Widerstandswerten zu gering, um für die in **Fig. 14** gezeigte Anwendung nützlich zu sein.

**[0065]** In ähnlicher Weise bilden die Abschnürwiderstände der Polysiliziumfeldelektrode R4 und R5 Stromwege mit hohem Widerstand für das Vorspannen der Steuergates für die SOI-Transistoren mit vorgespanntem angeschlossenen Körper Q2, Q3, wobei die Feldelektroden die Tiefpassfilterzeitkonstante der Schaltung **250** verbessern. Es ist zu beachten, dass die Körper der SOI-Transistoren, die in **Fig. 14** gezeigt sind, mit Spannungen verbunden sind, wie dies zuvor beschrieben ist, um damit den Betrieb bei geringer Schaltung der Schaltung **250** zu optimieren.

**[0066]** Unter Berücksichtigung der obigen Offenbarung ist nunmehr zu erkennen, dass die hierin offenbarten Prinzipien die Schaltungsgestaltungsflexibilität und das Leistungsverhalten gegenüber früheren Lösungen, die sowohl in SOI-Herstellungsprozessen als auch Vollsubstratherstellungsprozessen eingesetzt wurden, erweitern. Die Prinzipien der vorliegenden Erfindung können ferner auf zahlreiche andere elektronische Bauteilstrukturen angewendet werden, etwa auf Hochspannungsbauelemente, beispielsweise Driftfeld-MOSFET's und Bipolartransistoren, MOSFET's und Bipolartransistoren mit Feldplatten und abgestuften Übergängen und dergleichen. Die vorliegende Erfindung kann auch auf Hochspannungsdiolen und diverse Kondensatoren und Induktivitäten angewendet werden, um diese Bauelemente für die Schaltungsentwurfsingenieure verfügbar zu machen, wobei die hierin offenbarten Prinzipien des angeschlossenen Körpers und des schwebenden Körpers eingesetzt werden. Erfindungsgemäß kann die Flexibilität, die durch von der vorliegenden Erfindung offenbarten Form bereitgestellt wird, das Leistungsverhalten verbessern und die Kosten verringern.

**[0067]** Die vorliegende Erfindung wurde insbesondere im Hinblick auf gewisse bevorzugte Ausführungsformen und deren Merkmale gezeigt und be-

schrieben. Selbstverständlich sollte die Verwendung des Singulars in den Ansprüchen bei der Benennung eines Elements oder einer Einrichtung „mindestens ein“ Element und nicht „nur ein“ Element bezeichnet, sofern dies nicht anders explizit in den Ansprüchen als „nur ein einzelnes“ Element dargestellt ist.

### Patentansprüche

1. Verfahren zur Herstellung mehrerer Siliziumoxidisolator-(SOI)Bauelemente, mit den Schritten:

Abscheiden mindestens einer SOI-Schicht (14) auf mindestens einem Siliziumsubstrat (12);

Halten eines ersten Körpergebiets (22) auf der SOI-Schicht (14), wobei das erste Körpergebiet (22) eine erste Leitfähigkeitsart aufweist;

Anordnen mindestens eines Source- und eines Draingebiets (18, 20) neben dem ersten Körpergebiet (22), wobei das Source- und Draingebiet (18, 20) eine zweite Leitfähigkeitsart aufweisen; und

Halten eines zweiten Körpergebiets (44) auf der SOI-Schicht (14), wobei das zweite Körpergebiet (44) die erste Leitfähigkeitsart aufweist;

Anordnen eines ersten Übergangsgebiets (38, 40) zwischen dem ersten Körpergebiet (22) und dem zweiten Körpergebiet (44) über der SOI-Schicht (14), wobei das erste Übergangsgebiet (38, 40) eine Übergangsleitfähigkeitsart aufweist, die sich von der Leitfähigkeitsart des ersten Körpergebiets (22) und des zweiten Körpergebiets (44) unterscheidet, so dass das erste Übergangsgebiet (38, 40) das erste Körpergebiet (22) von dem zweiten Körpergebiet (44) trennt, so dass das erste Körpergebiet einen Effekt mit schwebendem Potential aufweist;

Halten eines dritten Körpergebiets (58) auf der SOI-Schicht (14), wobei das dritte Körpergebiet (58) die zweite Leitfähigkeitsart aufweist;

Anordnen eines zweiten Übergangsgebiets (46; 60) zwischen dem dritten Körpergebiet (58) und dem zweiten Körpergebiet (44) über der SOI-Schicht (14), wobei das zweite Übergangsgebiet (46; 60) mit einer Stromversorgung in Verbindung steht, und wobei das zweite Übergangsgebiet (60) die zweite Leitfähigkeitsart aufweist, um die Effekte des schwebenden Potentials in dem dritten Körpergebiet (58) zu unterdrücken, indem das dritte Körpergebiet (58) und die Stromversorgung verbunden werden, oder wobei das zweite Übergangsgebiet (46) die erste Leitfähigkeitsart aufweist, um Effekte des schwebenden Potentials in dem zweiten Körpergebiet (44) durch Verbinden des zweiten Körpergebiets (44) und der Stromversorgung zu unterdrücken.

2. Verfahren nach Anspruch 1, wobei der Schritt des Anordnens eines zweiten Übergangsgebiets (46; 60) umfasst: Bilden eines relativ leicht dotierten Gebiets (38; 58) und Bilden eines relativ stark dotierten Gebiets (40; 60).

3. Verfahren nach Anspruch 2, wobei das relativ

leicht dotierte Gebiet (38; 58) mit einer Konzentration im Bereich von ungefähr  $10^{14}$  bis ungefähr  $10^{18}$  Atome/cm<sup>3</sup> dotiert und wobei das relativ stark dotierte Gebiet (40; 60) mit einer Konzentration im Bereich von ungefähr  $10^{19}$  bis ungefähr  $10^{21}$  Atome/cm<sup>3</sup> dotiert ist.

4. Verfahren nach Anspruch 1, 2 oder 3, das ferner umfasst: Ankontaktieren einer ohmschen Verbindung (48; 62) an dem zweiten Übergangsgebiet (46; 60), wobei die ohmsche Verbindung (48; 62) zur Verbindung des zweiten Übergangsgebiets (46; 60) mit der Stromversorgung dient.

5. Verfahren nach Anspruch 4, das ferner umfasst: Verbinden der ohmschen Verbindung (48; 62) mit einer Spannungsquelle, wobei die Spannungsquelle einer Transistordrainspannung entspricht, wenn das zweite Übergangsgebiet (60) die zweite Leitfähigkeitsart aufweist, und wobei die Spannungsquelle einer Transistorsourcespannung entspricht, wenn das zweite Übergangsgebiet (46) die erste Leitfähigkeitsart aufweist.

6. Verfahren nach Anspruch 5, wobei die erste Leitfähigkeitsart eine P-Leitfähigkeitsart ist und die zweite Leitfähigkeitsart eine N-Leitfähigkeitsart ist.

7. Verfahren nach einem der vorhergehenden Ansprüche, das ferner umfasst: Ankontaktieren einer zweiten ohmschen Verbindung (42) an das erste Übergangsgebiet (38, 40), wobei die zweite ohmsche Verbindung (42) eine Isolationselektrode bereitstellt.

8. Verfahren nach Anspruch 7, das ferner Verbinden der zweiten ohmschen Verbindung (42) mit einer Spannungsquelle umfasst.

Es folgen 9 Blatt Zeichnungen

1

Fig.

Fig. 2

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

158

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 13

Fig. 14