(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6107085号

(P6107085)

(45) 発行日 平成29年4月5日(2017.4.5)

(24) 登録日 平成29年3月17日(2017.3.17)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78  | 618B |

| HO1L 21/336 | (2006.01) | HO1L 29/78  | 627G |

| HO1L 21/363 | (2006.01) | HO1L 29/78  | 618Z |

| C23C 14/08  | (2006.01) | HO1L 29/78  | 618C |

| C23C 14/58  | (2006.01) | HO1L 21/363 |      |

請求項の数 9 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2012-256866 (P2012-256866)

(22) 出願日

平成24年11月22日(2012.11.22)

(65) 公開番号

特開2014-107303 (P2014-107303A)

(43) 公開日

平成26年6月9日(2014.6.9)

審査請求日

平成27年10月19日(2015.10.19)

(73) 特許権者 000183303

住友金属鉱山株式会社

東京都港区新橋5丁目11番3号

(74) 代理人 110000811

特許業務法人貴和特許事務所

(72) 発明者 中山 徳行

東京都青梅市末広町1丁目6番1号 住友

金属鉱山株式会社 技術本部 材料開発セ

ンター内

審査官 小川 将之

最終頁に続く

(54) 【発明の名称】酸化物半導体薄膜および薄膜トランジスタ

## (57) 【特許請求の範囲】

## 【請求項1】

インジウムとチタンとチタン以外の添加元素を含有する酸化物からなり、チタン含有量が、 $Ti / In$  原子数比で 0.005 ~ 0.12 であり、前記チタン以外の添加元素の含有量が、インジウムに対する原子数比で 0.0025 以下であり、

結晶質で、ビックスバイト型構造の  $In_2O_3$  相によってのみ構成されており、かつ、キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  以下で、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  以上である、

ことを特徴とする酸化物半導体薄膜。

10

## 【請求項2】

前記チタン含有量が、 $Ti / In$  原子数比で 0.01 ~ 0.06 である、請求項1に記載の酸化物半導体薄膜。

## 【請求項3】

前記キャリア移動度が  $3 \text{ cm}^2 / \text{V sec}$  以上である、請求項1または2に記載の酸化物半導体薄膜。

## 【請求項4】

前記キャリア濃度が  $5 \times 10^{17} \text{ cm}^{-3}$  以下で、前記キャリア移動度が  $5 \text{ cm}^2 / \text{V sec}$  以上である、請求項1または2に記載の酸化物半導体薄膜。

## 【請求項5】

20

前記酸化物半導体薄膜の膜厚が 15 nm ~ 200 nm である、請求項 1 ~ 4 のいずれかに記載の酸化物半導体薄膜。

【請求項 6】

前記酸化物半導体薄膜の膜厚が 40 nm ~ 100 nm である、請求項 1 ~ 4 のいずれかに記載の酸化物半導体薄膜。

【請求項 7】

前記酸化インジウム相の結晶粒径が 10 nm 以上である、請求項 1 ~ 6 のいずれかに記載の酸化物半導体薄膜。

【請求項 8】

ソース電極、ドレイン電極、ゲート電極、チャネル層およびゲート絶縁膜を備える薄膜トランジスタであって、前記チャネル層が請求項 1 ~ 7 のいずれかに記載の酸化物半導体薄膜により構成されている、薄膜トランジスタ。 10

【請求項 9】

インジウムとチタンとチタン以外の添加元素を含有する酸化物からなり、チタン含有量が、 $Ti / In$  原子数比で 0.005 ~ 0.12 であり、前記チタン以外の添加元素の含有量が、インジウムに対する原子数比で 0.0025 以下である、非晶質の酸化物半導体薄膜に対して、250 以上の加熱温度、および、1 分 ~ 120 分の処理時間で、アニール処理を施すことにより、結晶質で、ビックスバイト型構造の  $In_2O_3$  相によってのみ構成されており、かつ、キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  以下で、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  以上である、酸化物半導体薄膜を得る、酸化物半導体薄膜の製造方法。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、酸化物半導体薄膜、および、これを用いた薄膜トランジスタに関する。

【背景技術】

【0002】

薄膜トランジスタ (Thin Film Transistor : TFT) は、電界効果トランジスタ (Field Effect Transistor : FET) の 1 種である。TFT は、基本構成として、ゲート端子、ソース端子、およびドレイン端子を備えた 3 端子素子であり、基板上に成膜した半導体薄膜を、電子またはホールが移動するチャネル層として用い、ゲート端子に電圧を印加して、チャネル層に流れる電流を制御し、ソース端子とドレイン端子間の電流をスイッチングする機能を有するアクティブ素子である。 30

【0003】

現在、TFT のチャネル層として、多結晶シリコン膜やアモルファスシリコン膜が広く使用されている。特に、アモルファスシリコン膜は、大面積の第 10 世代ガラス基板への均一成膜が可能であることから、液晶パネル用 TFT のチャネル層として広く利用されている。しかしながら、キャリアである電子の移動度 (キャリア移動度) が  $1 \text{ cm}^2 / \text{V sec}$  以下と低いため、高精細パネル用 TFT への適用が困難になりつつある。すなわち、液晶の高精細化に伴い、TFT の高速駆動が要求されており、このような TFT の高速駆動を実現するためには、アモルファスシリコン膜のキャリア移動度である  $1 \text{ cm}^2 / \text{V sec}$  よりも高いキャリア移動度を示す半導体薄膜をチャネル層に用いる必要がある。 40

【0004】

これに対して、多結晶シリコン膜は、 $100 \text{ cm}^2 / \text{V sec}$  程度の高いキャリア移動度を示すことから、高精細パネル用 TFT 向けのチャネル層材料として十分な特性を有している。しかしながら、多結晶シリコン膜は、結晶粒界でキャリア移動度が低下するため、基板の面内均一性に乏しく、TFT の特性にばらつきが生じるという問題がある。また、多結晶シリコン膜の製造工程では、300 以下の比較的低温でアモルファスシリコン膜を形成した後、この膜をアニール処理工程によって結晶化させている。このアニール処理工程は、エキシマレーザアニールなどを適用する特殊なものであるため、高いランニングコストが必要とされる。加えて、対応できるガラス基板の大きさも第 5 世代程度にとど 50

まっていることから、コストの低減に限界があり、製品展開も限られたものとなっている。

#### 【0005】

このように、TFTのチャネル層の材料として、現在、アモルファスシリコン膜と多結晶シリコン膜の優れた特性を兼ね備え、かつ、低コストで得られる材料が要求されている。これに対して、特開2010-219538号公報では、気相成膜法で成膜され、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)および酸素(O)から構成される透明アモルファス酸化物薄膜(a-IGZO膜)であって、該酸化物の組成は、結晶化したときの組成が  $InGaO_3 (ZnO)_m$  ( $m$ は6未満の自然数) であり、不純物イオンを添加することなしに、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  より高く、かつ、キャリア濃度が  $10^{16} / \text{cm}^3$  以下である、透明半絶縁性アモルファス酸化物薄膜、ならびに、この透明半絶縁性アモルファス酸化物薄膜をチャネル層とした薄膜トランジスタが提案されている。

#### 【0006】

しかしながら、特開2010-219538号公報で提案された、スパッタリング法、パルスレーザ蒸着法のいずれかの気相成膜法で成膜されるa-IGZO膜は、おおむね  $1 \text{ cm}^2 / \text{V sec} \sim 10 \text{ cm}^2 / \text{V sec}$  の範囲の比較的高いキャリア移動度を示すものの、アモルファス酸化物薄膜が本来酸素欠損を生成しやすいことと、熱など外的因子に対してキャリアである電子の振る舞いが必ずしも安定でないことに起因して、TFTなどのデバイスの動作がしばしば不安定になることが問題となっている。

#### 【0007】

さらには、アモルファス膜に特有である、可視光照射下でTFT素子に負バイアスを連続的に印加すると、しきい電圧が負側にシフトする現象(光負バイアス劣化現象)の発生が、液晶などのディスプレイ用途では深刻な問題となることが指摘されている。

#### 【0008】

一方、特開2008-192721号公報には、高温のプロセスを要することなく高分子基材への素子作製が可能であり、かつ、低コストで高性能、高信頼性を達成することができる薄膜トランジスタを得ることを目的として、チャネル層に、スズ(Sn)、チタン(Ti)、タンクステン(W)のいずれかをドープした酸化インジウム膜や、WとZnおよび/またはSnとをドープした酸化インジウム膜を適用することが提案されている。特開2008-192721号公報によれば、この技術によって得られる酸化インジウム膜をチャネル層に適用することで、TFT素子のキャリア移動度を  $5 \text{ cm}^2 / \text{V sec}$  以上とすることが可能になるとされている。

#### 【0009】

また、特開2010-251604号公報には、同様に、Sn、Ti、WおよびZnの1種または2種以上をドープした酸化インジウムの焼結体をターゲットとして、無加熱のスパッタリング成膜法で形成した後、150 ~ 300で、10分~120分の熱処理を行う技術が記載されている。この技術によれば、高い移動度とアモルファス性を兼備するという特徴を維持したまま、比較的容易な制御により安定的な特性を有する酸化インジウム膜を得ることができ、さらには、この酸化インジウム膜をチャネル層として使用することで、安定的な特性を有するTFT素子を得ることが可能になるとされている。

#### 【0010】

しかしながら、これらの文献に記載の方法により得られる酸化インジウム膜は、いずれもアモルファス膜であるため、これらの文献に記載の方法では、酸素欠損を生成しやすく、熱など外的因子に対して安定でないという問題や、アモルファス膜に特有の光負バイアス劣化現象の発生という問題を、根本的に解決することはできない。また、高精細パネル用TFT向けのチャネル層材料として使用を考慮した場合、より高いキャリア移動度の達成が望まれている。

#### 【先行技術文献】

#### 【特許文献】

10

20

30

40

50

## 【0011】

【特許文献1】特開2010-219538号公報

【特許文献2】特開2008-192721号公報

【特許文献3】特開2010-251604号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0012】

本発明は、酸化物半導体薄膜としての酸化物アモルファス薄膜が有する問題を解消するため、比較的高いキャリア移動度を有し、薄膜トランジスタ(TFT)のチャネル層材料として好適な酸化物半導体薄膜を、酸化物結晶質薄膜により提供することを目的としている。

10

## 【課題を解決するための手段】

## 【0013】

本発明者らは、酸化物半導体薄膜に適用可能な酸化物アモルファス薄膜の代替材料について鋭意検討を行った。具体的には、スパッタリング法によって得られる、インジウムとチタンの酸化物に対して、アニール処理を施すことにより、結晶質の酸化物半導体薄膜を形成する実験を重ねた。その際、結晶化した酸化物半導体薄膜が高いキャリア移動度を発現する条件、すなわち、酸化物半導体薄膜としてのインジウムとチタンの酸化物の組成、膜厚、および、結晶化させる条件などについて、詳細に検討を行った。

## 【0014】

20

その結果、本発明者らは、インジウムとチタンの酸化物を主成分とする酸化物半導体薄膜における、チタン含有量を所定の範囲に規制し、かつ、このような組成の非晶質膜に対して所定条件のアニール処理を施すことで、ビックスバイト型構造の $In_2O_3$ 相のみによって構成される結晶質の薄膜とすることにより、 $1\text{ cm}^2/\text{V sec}$ 以上という高いキャリア移動度、 $1 \times 10^{19}\text{ cm}^{-3}$ 以下という低いキャリア濃度を示し、薄膜トランジスタ(TFT)のチャネル層材料として好適な酸化物半導体薄膜を得ることができるとの知見を得て、本発明を完成するに至ったものである。

## 【0015】

すなわち、本発明の酸化物半導体薄膜は、インジウムとチタンを含有する酸化物からなり、チタン含有量が、 $Ti/In$ 原子数比で $0.005 \sim 0.12$ であり、結晶質で、ビックスバイト型構造の $In_2O_3$ 相によってのみ構成されており、かつ、キャリア濃度が $1 \times 10^{19}\text{ cm}^{-3}$ 以下で、キャリア移動度が $1\text{ cm}^2/\text{V sec}$ 以上であることを特徴とする。

30

## 【0016】

このような特性を具備する本発明の酸化物半導体薄膜は、インジウムとチタンを含有する酸化物からなり、チタン含有量が、 $Ti/In$ 原子数比で $0.005 \sim 0.12$ である非晶質の酸化物半導体薄膜に対して、250以上 の加熱温度、および、1分～120分の処理時間で、アニール処理を施すことにより、結晶質で、ビックスバイト型構造の $In_2O_3$ 相によってのみ構成されており、かつ、キャリア濃度が $1 \times 10^{19}\text{ cm}^{-3}$ 以下で、キャリア移動度が $1\text{ cm}^2/\text{V sec}$ 以上である、酸化物半導体薄膜を得る工程により、製造することが可能である。

40

## 【0017】

前記チタン含有量は、 $Ti/In$ 原子数比で $0.01 \sim 0.06$ であることが好ましい。

## 【0018】

前記キャリア移動度は $3\text{ cm}^2/\text{V sec}$ 以上であることが好ましく、前記キャリア濃度は $5 \times 10^{17}\text{ cm}^{-3}$ 以下で、かつ、前記キャリア移動度が $5\text{ cm}^2/\text{V sec}$ 以上であることがより好ましい。

## 【0019】

前記酸化物半導体薄膜の膜厚は $15\text{ nm} \sim 200\text{ nm}$ であることが好ましく、 $40\text{ nm}$

50

~100 nm であることがより好ましい。

【0020】

前記酸化インジウム相の結晶粒径は、10 nm 以上であることが好ましい。

【0021】

また、本発明の薄膜トランジスタは、ソース電極、ドレイン電極、ゲート電極、チャネル層およびゲート絶縁膜を備える薄膜トランジスタであって、前記チャネル層が、本発明の酸化物半導体薄膜により構成されていることを特徴とする。

【発明の効果】

【0022】

本発明の酸化物半導体薄膜は、酸化物結晶質薄膜であるため、 $1 \text{ cm}^2 / \text{V sec}$  を超える高いキャリア移動度を有しながら、酸素欠損を生成しやすい、熱など外的因子に対して安定でない、および、光負バイアス劣化現象が発生するといった問題が生じることがない。

【0023】

さらに、本発明の酸化物半導体薄膜は、所定の組成の酸化物アモルファス薄膜を、たとえばアニール炉を用いた 400 以下の温度のアニール処理によって、ビックスバイト型構造の  $\text{In}_2\text{O}_3$  相によってのみ構成される、高い結晶性を有する酸化物結晶質薄膜を得ることができる。

【0024】

したがって、本発明の酸化物半導体薄膜をチャネル層材料として用いることにより、TFT の特性向上を低成本で実現することができるため、本発明は、工業的にきわめて有用である。

【図面の簡単な説明】

【0025】

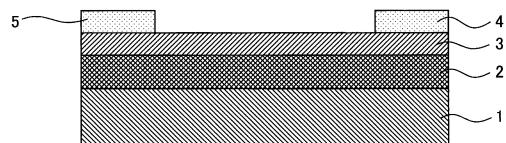

【図1】図1は、本発明のTFT素子の概略断面図である。

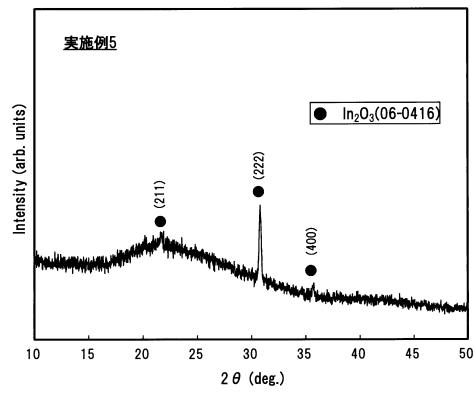

【図2】図2は、実施例5の酸化物半導体薄膜をX線回折測定した結果を示す図である。

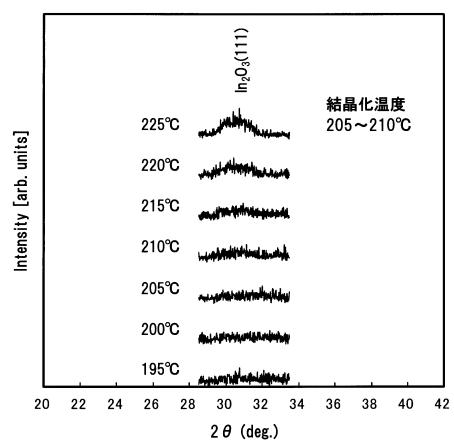

【図3】図3は、アニール処理における加熱温度と、得られる酸化物半導体膜の結晶化の関係を示した図である。

【発明を実施するための形態】

【0026】

以下、本発明の酸化物半導体薄膜、および、この酸化物半導体薄膜をチャネル層材料として用いた薄膜トランジスタ (TFT) について、詳細に説明する。

【0027】

1. 酸化物半導体薄膜

(a) 組成

本発明のインジウム (In) とチタン (Ti) を含有する酸化物からなる結晶質の酸化物半導体薄膜では、Ti 含有量を、 $\text{Ti} / \text{In}$  原子数比で 0.005 ~ 0.12 に制御することにより、キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  以下で、かつ、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  以上を示し、さらには  $3 \text{ cm}^2 / \text{V sec}$  以上という良好なキャリア特性を達成している。TFT のチャネル層としては、さらに低いキャリア濃度を示すことが好ましいが、本発明の酸化物半導体膜では、たとえば、Ti 含有量を、 $\text{Ti} / \text{In}$  原子数比で 0.01 ~ 0.06 の範囲に制御することにより、 $5 \times 10^{17} \text{ cm}^{-3}$  以下のキャリア濃度を達成することができる。

【0028】

他の添加元素を含有しない In のみの酸化物からなる結晶質の酸化物半導体薄膜のキャリア源は、主に酸素欠損であるが、酸化親和性の高い Ti を添加することによって、その生成を抑制することが可能となる。その一方で、結晶質の酸化物半導体薄膜中の Ti は 4 価のイオンとなり、ドナーとして振る舞うため、キャリア源にもなり得る。

【0029】

これらのことから、本発明者らは、キャリア源としてキャリア濃度を必要以上に高める

10

20

30

40

50

ことなく、酸素欠損の発生を抑制する作用が支配的になるTiの組成を検討したところ、Ti含有量を、Ti / In原子数比で0.005～0.12、好ましくは0.01～0.06の範囲に制御することが必要であるとの知見が得られた。すなわち、Ti含有量がTi / In原子数比で0.005未満では、Tiの酸素親和性によるキャリア源の発生を抑制する効果が十分に得られず、また、0.12を超えると、キャリア源としてのTiの作用が支配的となるため、いずれの場合も、キャリア源の発生を抑制することができないため、酸化物半導体膜のキャリア濃度が $1 \times 10^{19} \text{ cm}^{-3}$ を超えてしまう。

#### 【0030】

また、Tiは、いわゆるイオン化不純物散乱中心として振る舞うため、キャリアの散乱の原因となり、キャリア移動度を低下させる。この原理にしたがって、Ti含有量がTi / In原子数比で0.12を超えると、キャリアの散乱が著しくなり、キャリア移動度が $1 \text{ cm}^2 / \text{V sec}$ 以下となってしまう。一方、Ti含有量を、Ti / In原子数比で0.01～0.06の範囲に制御することにより、キャリア移動度を安定的に $5 \text{ cm}^2 / \text{V sec}$ 以上とすることが可能となる。

#### 【0031】

なお、本発明の酸化物半導体薄膜は、不可避的不純物を除き、InとTiからなる酸化物によって形成されるほか、InとTiを主成分とし、不可避的不純物以外の公知の添加元素(M)を、適宜含有する酸化物によっても構成することができる。この場合、InとTi以外の添加元素(M)の含有量は、M / In原子数比で0.0025以下、好ましくは0.001以下とする。

#### 【0032】

##### (b) 結晶構造

本発明の酸化物半導体薄膜は、結晶質であって、実質的にビックスバイト型構造の酸化インジウム( $\text{In}_2\text{O}_3$ )相のみによって構成されており、この構造以外の結晶相を実質的に含まないことを特徴とする。ビックスバイト型構造の $\text{In}_2\text{O}_3$ 相では、InとOからなる $\text{InO}_6$ 八面体構造が形成されている。隣り合う $\text{InO}_6$ 八面体構造が稜共有しているため、In-In間の距離が短くなり、キャリアとなる電子の軌道の重なりが大きくなり、キャリア移動度が向上する。

#### 【0033】

ビックスバイト型構造以外の $\text{In}_2\text{O}_3$ 相以外の結晶相を含まないことが好ましいが、酸化物半導体薄膜の特性(キャリア濃度およびキャリア移動度)が本発明の範囲に含まれる限り、 $\text{In}_2\text{O}_3$ 相以外の結晶相を実質的に含まず、ビックスバイト型構造の $\text{In}_2\text{O}_3$ 相によってのみ構成される薄膜であると評価することができ、このような薄膜も本発明に含まれるものとする。ただし、ビックスバイト型構造以外の結晶相であっても、 $\text{InO}_6$ 八面体構造が稜共有する結晶構造を有する限り、そのような結晶相の存在については制限されることはない。

#### 【0034】

##### (c) 結晶粒径

本発明の酸化物半導体薄膜において、酸化物半導体薄膜を構成する結晶粒の大きさ、すなわち、結晶粒径は10nm以上であることが好ましく、20nm以上であることがより好ましく、50nm以上であることが特に好ましい。結晶粒径が10nm以上の結晶粒によって構成されることにより、結晶粒界におけるキャリアの散乱が少なくなるため、キャリア移動度を安定的に $1 \text{ cm}^2 / \text{V sec}$ 以上とすることが可能となる。

#### 【0035】

##### (d) 膜厚

本発明の酸化物半導体薄膜の膜厚は、好ましくは15nm～200nm、より好ましくは30nm～150nm、さらに好ましくは40nm～100nmの範囲に制御される。

#### 【0036】

一般に、酸化物以外の材料により構成される半導体薄膜は、ガラス基板に形成されることが多い。すなわち、非晶質の基板上に、結晶質の基板が形成されることになる。したが

10

20

30

40

50

つて、本発明の酸化物半導体薄膜において、膜厚が 15 nm 未満の場合には、Ti の添加量にもよるが、基板の影響によって 400 度程度の高温でアニール処理を施した場合でも、前駆体である酸化物アモルファス薄膜が結晶化しない場合がある。また、この酸化物アモルファス薄膜が結晶化したとしても、得られる結晶膜において十分な結晶性が得られない。このため、高いキャリア移動度が得られないこととなる。さらに、膜厚が 15 nm 未満の場合、得られる結晶膜における結晶粒径を 10 nm 以上とすることが困難となる。

#### 【0037】

基板が非晶質であることによる酸化物半導体薄膜の結晶性への影響は、酸化物半導体薄膜の膜厚を 30 nm 以上とすることにより軽減されるが、40 nm 以上とすることにより、安定的にその影響を排除することが可能となる。ただし、コスト面を考慮すると、膜厚を 200 nm 以下とすることが好ましく、150 nm 以下とすることがより好ましく、100 nm 以下とすることがさらに好ましい。なお、膜厚を 100 nm 近傍に制御することにより、酸化物半導体薄膜が、ガラス基板に形成された場合、光学的な干渉によって、青色光の透過率の向上が期待できる。したがって、本発明の酸化物半導体薄膜を、透明 TFT へ適用する場合には、膜厚を 100 nm 近傍に調整することが好ましい。

#### 【0038】

##### (特性)

上述のように本発明の酸化物半導体薄膜は、インジウムとチタンを含有する酸化物からなり、結晶質で、ビックスバイト型構造の  $In_2O_3$  相によってのみ構成されている。このため、本発明の酸化物半導体薄膜を適用した TFT は、熱などの外的因子に対して高い安定性を有しており、かつ、光負バイアス劣化現象が発生し難い。

#### 【0039】

また、本発明の酸化物半導体膜では、該酸化物半導体中の Ti の含有量を、所定の範囲内に制御することにより、キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  以下であって、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  以上となるように規制されている。キャリア濃度およびキャリア移動度をこのような範囲に規制することにより、透明導電膜よりも 2 枝 ~ 4 枝も低いキャリア濃度が要求されるチャネル層の材料として適用可能になるとともに、その高いキャリア移動度により、TFT の高い画素制御性能の確保が可能となる。

#### 【0040】

キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  を超えると、TFT のチャネル層の材料として適用することが困難となる。なお、on / off 比の高い TFT を実現するためにはチャネル層のキャリア濃度を、好ましくは  $5 \times 10^{17} \text{ cm}^{-3}$  以下に規制する必要があるが、本発明の酸化物半導体薄膜は、このような低いキャリア濃度を実現することができる。

#### 【0041】

一方、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  未満では、TFT の高い画素制御性能を確保することが困難となる。特に、高精細液晶パネル用 TFT への適用を考慮すれば、キャリア移動度を、好ましくは  $3 \text{ cm}^2 / \text{V sec}$  以上、より好ましくは  $5 \text{ cm}^2 / \text{V sec}$  以上とすることが必要とされるが、本発明の酸化物半導体薄膜は、このような高いキャリア移動度を実現することができる。

#### 【0042】

本発明の酸化物半導体薄膜は、ウェットエッチングあるいはドライエッチングによって、TFT などの用途で必要な微細加工をすることができる。最初に非晶質膜を形成し、その後、結晶化温度以上で熱処理して酸化物半導体薄膜を結晶化させる方法の場合、非晶質膜の形成後に弱酸を用いたウェットエッチングによる加工を施すことができる。弱酸であれば概ね使用できるが、蔴酸を主成分とする弱酸が好ましい。たとえば、関東化学株式会社製の透明導電膜エッティング液 (ITO-06N) などを使用することができる。ドライエッティングの場合は、結晶化後の酸化物半導体薄膜や成膜時に直接基板に成膜された結晶質の酸化物半導体薄膜に対しても、適切なエッティングガスを用いて加工することができる。

## 【0043】

## 2. 酸化物半導体薄膜の製造方法

## (成膜工程)

本発明の酸化物半導体薄膜は、酸化物焼結体のターゲットやタブレットを用いて、スパッタリング法、イオンプレーティング法などの適用可能な公知の成膜技術により、基板上に形成される。原材料となる酸化物焼結体の金属元素組成比は、成膜条件に応じて適宜設定することも可能であるが、通常、酸化物焼結体の金属元素組成比を成膜後の酸化物薄膜と同じとして、成膜条件を制御して、所望の組成の酸化物薄膜を成膜することが容易な手段である。よって、本発明の酸化物半導体薄膜の金属元素組成比と同じとすることが好ましい。この場合、InとTiを含有する酸化物焼結体では、そのTi含有量を、Ti / In原子数比で0.005～0.12、好ましくは0.01～0.06とする。

## 【0044】

InとTiを含有する酸化物焼結体としては、主にビックスバイト型構造のIn<sub>2</sub>O<sub>3</sub>相によって構成される酸化物焼結体が使用される。通常、このIn<sub>2</sub>O<sub>3</sub>相にはTiが固溶している。ただし、Tiが固溶していないIn<sub>2</sub>O<sub>3</sub>相、すなわち、不可避的不純物を除き、いかなる元素も固溶していないIn<sub>2</sub>O<sub>3</sub>相が共存していてもよい。

## 【0045】

また、In<sub>2</sub>O<sub>3</sub>相以外に、TiO、TiO<sub>2</sub>などの酸化チタンの形態で、さらには、In<sub>2</sub>Ti<sub>3</sub>O<sub>12</sub>などの酸化インジウム・酸化チタン間の複合酸化物の形態で、他の結晶相が酸化インジウム焼結体中に分散している酸化物焼結体も、ターゲットやタブレットの材料とすることができる。

## 【0046】

ただし、In<sub>2</sub>O<sub>3</sub>相に対する他の結晶相の面積比率は10%以下の割合でなければならない。たとえば、通常の直流(DC)スパッタリング法では、成膜速度を向上させるために、投入する直流電力を高めることが行われている。この際、上記面積比率が10%を超えると、スパッタリングの進行とともに、他の結晶相がノジュール成長の起点となることが考えられる。しかしながら、本発明の酸化物半導体薄膜の成膜に用いられる酸化物焼結体では、他の結晶相の面積比率が10%以下に抑えられており、実質的には他の結晶相が微細分散されているため、ノジュール成長の起点となりにくい構造となっている。このような酸化物焼結体をターゲットやタブレットの材料とすることにより、成膜時に、投入する直流電力を高めても、ノジュールの発生が抑制され、アーキングなどの異常放電が発生しにくくなるため、成膜の効率を向上させることができるとなる。

## 【0047】

本発明の酸化物半導体薄膜は、通常のスパッタリング法やイオンプレーティング法を用い、これらの方法で通常採用される条件により、成膜することが可能である。本発明の酸化物半導体薄膜を、スパッタリング法により、基板上に形成する場合、特に、直流スパッタリング法であれば、成膜時の熱影響が少なく、高速成膜が可能であるため工業的に有利である。本発明の透明導電膜を直流スパッタリング法で形成するためには、スパッタリングガスとして不活性ガスと酸素、特にアルゴン(Ar)と酸素(O<sub>2</sub>)からなる混合ガスを用いることが好ましい。また、スパッタリング装置のチャンバー内を0.1Pa～1Pa、特に0.2Pa～0.8Paの圧力として、スパッタリングを行うことが好ましい。

## 【0048】

基板は、ガラス基板が代表的であるが、シリコンなど半導体デバイス用基板として用いられているものであればよく、そのほかにも、上記プロセスの温度に耐え得るものであれば、樹脂板や樹脂フィルムを、基板として使用することができる。

## 【0049】

基板温度は、InとTiを含有する酸化物からなる非晶質膜の結晶化温度以下とすることが好ましい。成膜時に結晶化すると、その後のアニール処理において酸素欠損の消失が進まず、結果として、キャリア濃度を $1 \times 10^{19} \text{ cm}^{-3}$ 以下、さらには $5 \times 10^{17} \text{ cm}^{-3}$ 以下に制御することが困難になる。このような観点から、基板温度は、膜厚が15nm～

10

20

30

40

50

70 nmの範囲であれば、200以下とし、膜厚が70 nm～200 nmの範囲であれば、100以下とすることが好ましい。いずれの場合も、室温から100までの範囲とすることがより好ましい。

【0050】

本発明において、たとえば、 $2 \times 10^{-4}$  Pa以下まで真空排気後、ArとO<sub>2</sub>からなる混合ガスを導入し、ガス圧を0.2 Pa～0.5 Paとし、ターゲット-基板間距離を10 mm～100 mm、好ましくは40 mm～70 mmの範囲に調整し、さらに、ターゲットの面積に対する直流電力、すなわち直流電力密度が1 W/cm<sup>2</sup>～3 W/cm<sup>2</sup>程度の範囲となるよう直流電力を印加して、直流プラズマを発生させ、プリスパッタリングを5分間～30分間行った後、必要により基板位置を修正したうえで、同様の条件で、スパッタリングを行うことが好ましい。

【0051】

(アニール工程)

本発明の酸化物半導体薄膜を結晶化させる方法として、基板を酸化物半導体薄膜の結晶化温度以上に加熱することによって、結晶質の酸化物半導体薄膜を成膜する、あるいは、室温近傍など低温で非晶質膜を形成してから、この非晶質膜を結晶化温度以上でアニール処理して結晶化させる方法がある。本発明の酸化物半導体膜の場合、いずれの方法も用いることができる。また、いずれの方法を用いる場合であっても、基板温度、または、アニール処理時の加熱温度を400以下とすることができます、このような温度範囲であれば、アモルファスシリコンや多結晶シリコンを用いる半導体プロセスと温度的に大きな差はないといえる。ただし、本発明では、上述したように、成膜時に結晶化させると、たとえば、その後にさらにアニール処理を施しても、酸素欠損の消失が進まず、結果として、キャリア濃度を $1 \times 10^{19}$  cm<sup>-3</sup>以下に制御することが困難となる場合がある。したがって、非晶質膜を形成した後、この非晶質膜にアニール処理を施して結晶化させることが好ましい。

【0052】

本発明の酸化物半導体薄膜を結晶化させるためには、アニール炉を用いたアニール処理の場合、加熱温度を250以上、好ましくは300以上、より好ましくは350以上とすることが必要となる。本発明では、Ti含有量を、Ti/In原子数比で0.005～0.12の範囲に規制しているが、この場合、酸化物半導体薄膜の結晶化温度は220程度となるため、加熱温度が250未満では、十分に結晶化させることができない。ただし、アニール処理の手段については、アニール炉を用いるほか、公知のアニール処理のための手段を広く用いることができ、それぞれの手段に応じた加熱温度を含むアニール条件を適用することができる。

【0053】

なお、特開2010-251604号公報には、上述したように、チャネル層などを、無加熱スパッタリング法により成膜した後、大気中、150～300で、10分～120分の条件でアニール処理をすることにより、アモルファス性を保ったまま、アモルファス膜中の過剰な欠陥を減少させる技術が記載されている。また、その実施例では、無加熱で成膜したIn-W-Zn-O膜(W=1wt%～10wt%)に対して、大気中、150で30分間のアニール処理を行っている。すなわち、特開2010-251604号公報に記載の技術は、In<sub>2</sub>O<sub>3</sub>相に固溶して結晶化温度を高めることができる元素を、相当量添加することで、上記温度範囲のアニール処理において、酸化物半導体薄膜のアモルファス性を保持することを可能とする技術であり、この点において本発明とは相違するものである。

【0054】

処理時間は、好ましくは1分～120分、より好ましくは5分～60分とする。処理時間が1分未満では、得られる酸化物半導体薄膜を十分に結晶化せることができず、120分を超えて、それ以上の効果は望めず、生産性が悪化してしまう。

【0055】

10

20

30

40

50

また、アニール処理の雰囲気については制限されることはないが、通常、大気中で行うことができる。結晶化させることに加えて、キャリア濃度を低減させることを目的とする場合、酸素を含む雰囲気が好ましく、その濃度は 20 vol % 以上がより好ましい。

【0056】

3. TFT 素子

本発明の薄膜トランジスタ (TFT) は、上記の通り、チャネル層材料に、In と Ti を含有する酸化物からなる酸化物半導体薄膜を適用している点に特徴がある。TFT の構造は限定されないが、たとえば、図 1 に示した構成の TFT 素子を例示することができる。

【0057】

10

図 1 の TFT 素子は、熱酸化によって  $\text{SiO}_2$  膜が表面に形成された  $\text{SiO}_2 / \text{Si}$  基板上に、本発明の酸化物半導体薄膜、および Au / Ti 積層電極によって構成される。この構成において、ゲート電極 1 は Si 基板、ゲート絶縁層 2 は  $\text{SiO}_2$  膜、チャネル層 3 は本発明の酸化物半導体薄膜、ソース電極 4 およびドレイン電極 5 は Au / Ti 積層電極により構成される。

【0058】

図 1 の TFT 素子では、 $\text{SiO}_2 / \text{Si}$  基板を用いたが、基板はこれに限定されるものではなく、従来から薄膜トランジスタを含む電子デバイスの基板として使用されているものを用いることもできる。たとえば、 $\text{SiO}_2 / \text{Si}$  基板や Si 基板のほかに、無アルカリガラス、石英ガラスなどのガラス基板を用いることができる。また、各種の金属基板やプラスチック基板、ポリイミドなどの透明でない耐熱性高分子フィルム基板などを用いることもできる。

20

【0059】

ゲート電極 1 について、図 1 の TFT 素子では Si 基板により構成しているが、これに限定されない。たとえば、Mo、Al、Ta、Ti、Au、Pt などの金属薄膜、これら金属の導電性酸化物、窒化物薄膜または酸化窒化物薄膜、あるいは各種の導電性高分子材料を用いることができる。透明 TFT の場合には、酸化インジウムスズ (ITO) などの透明導電膜を用いることができる。なお、本発明の酸化物半導体薄膜と同様の金属元素組成を有する酸化物半導体薄膜を透明導電膜として用いることもできる。このゲート電極 1 には、良好な導電性が求められる。これらの電極の比抵抗は、 $1 \times 10^{-6} \text{ } \cdot \text{cm} \sim 1 \times 10^{-1} \text{ } \cdot \text{cm}$  の範囲に制御されることが好ましく、 $1 \times 10^{-6} \text{ } \cdot \text{cm} \sim 1 \times 10^{-3} \text{ } \cdot \text{cm}$  の範囲に制御されることがより好ましい。

30

【0060】

また、ゲート絶縁層 2 は、 $\text{SiO}_2$ 、 $\text{Y}_2\text{O}_3$ 、 $\text{Ta}_2\text{O}_5$ 、 $\text{Hf}$  酸化物などの金属酸化物薄膜や  $\text{SiN}_x$  などの金属窒化物薄膜、あるいはポリイミドをはじめとする絶縁性の高分子材料などの公知の材料を用いることができる。ゲート絶縁層 2 の比抵抗は、 $1 \times 10^6 \text{ } \cdot \text{cm} \sim 1 \times 10^{15} \text{ } \cdot \text{cm}$  の範囲であることが好ましく、 $1 \times 10^{10} \text{ } \cdot \text{cm} \sim 1 \times 10^{15} \text{ } \cdot \text{cm}$  であればより好ましい。

【0061】

40

チャネル層 3 の比抵抗は、特に制限されるものではないが、 $10^{-1} \text{ } \cdot \text{cm} \sim 10^6 \text{ } \cdot \text{cm}$  に制御されることが好ましく、特に  $10^0 \text{ } \cdot \text{cm} \sim 10^3 \text{ } \cdot \text{cm}$  に制御されることがより好ましい。本発明の酸化物半導体薄膜の比抵抗は、スパッタリング法あるいはイオンプレーティング法における成膜条件、ならびに結晶化のアニール処理の条件の選択によって、酸素欠損の生成量が調整可能であることから、比較的容易に制御することが可能である。

【0062】

ソース電極 4 およびドレイン電極 5 としては、ゲート電極 1 と同様に、Mo、Al、Ta、Ti、Au、Pt などの金属薄膜もしくはこれらの金属の合金薄膜、それら金属の導電性酸化物または窒化物薄膜、あるいは各種の導電性高分子材料、あるいは透明 TFT 向けとして ITO などの透明導電膜を用いることができる。また、これらの薄膜を積層化し

50

てもよい。このソース電極4やドレイン電極5には良好な導電性が求められる。これらの電極の比抵抗は、 $10^{-6}$  ~  $10^{-1}$   $\cdot$  cmの範囲に制御されることが好ましく、 $10^{-6}$  ~  $10^{-3}$   $\cdot$  cmの範囲に制御されることがより好ましい。

【0063】

4. TFT素子の製造方法

本発明のTFT素子の製造方法について、詳細に説明する。なお、以下では、酸化物半導体薄膜の形成に際し、低温成膜後にアニール処理をする方法を例に挙げて説明するが、本発明のTFT素子は、高温で成膜する方法を採用することもできるし、その他、公知の方法を適宜組み合わせて製造することができる。

【0064】

初めに、高ドープのn型Siウエハ基板の表面に、熱酸化によって $SiO_2$ 膜を形成し、 $SiO_2/Si$ 基板とする。この基板を100以下に保持したまま、該基板の $SiO_2$ 膜上に、直流マグнетロンスパッタリング法により、所定の膜厚を有する非晶質の酸化物半導体薄膜を形成する。なお、この際の成膜条件については、「2. 酸化物半導体薄膜の製造方法」で説明した条件と同様であるため、ここでの説明は省略する。また、この非晶質薄膜の形成時に、マスキングをした上で成膜を行うことにより、あるいは、非晶質薄膜の形成後に、フォトリソグラフィ技術などを利用してエッチングすることにより、所望のチャネル長および/またはチャネル幅を有する酸化物半導体薄膜を形成することができる。

【0065】

次に、この酸化物半導体薄膜に対して、アニール処理を施すことにより、結晶質の酸化物半導体薄膜とする。このアニール処理の条件についても、「2. 酸化物半導体薄膜の製造方法」で説明した条件と同様であるため、ここでの説明は省略する。

【0066】

その後、得られた結晶質の酸化物半導体薄膜(チャネル層)上に、マスキングを施した上で膜厚5nmのTi薄膜および膜厚100nmのAu薄膜を順次積層して、ソース電極およびドレイン電極を形成することにより、本発明のTFT素子を得ることができる。なお、ソース電極およびドレイン電極の形成については、チャネル層の形成と同様に、Ti薄膜およびAu薄膜の形成後に、フォトリソグラフィ技術などを利用してエッチングをする方法を採用してもよい。

【実施例】

【0067】

以下、本発明の実施例を用いて、さらに詳細に説明するが、本発明は、これら実施例によって限定されるものではない。なお、酸化物焼結体、酸化物半導体薄膜およびTFT素子の評価は、下記の方法により行った。

【0068】

[酸化物焼結体の評価]

各実施例および比較例により得られた酸化物焼結体の端材に対して、X線回折装置(フィリップス社製、X'Pert PRO MPD)を用いて、粉末X線回折法による生成相の同定を行った。

【0069】

[酸化物半導体薄膜の基本特性評価]

各実施例および比較例により得られた酸化物半導体薄膜の組成を、ICP発光分光法によって測定した。また、酸化物半導体薄膜の膜厚を、表面形状測定装置(ケーラルエー・テンコール社製)で測定し、この結果と成膜時間から成膜速度を算出した。さらに、酸化物半導体薄膜のキャリア濃度および比抵抗を、ホール効果測定装置(株式会社東陽テクニカ製)によって測定し、それらの値からそのキャリア移動度を算出した。酸化物半導体薄膜の生成相の同定は、上記と同様に、X線回折測定によって行った。

【0070】

[TFT素子の特性評価]

10

20

30

40

50

TFT素子の特性評価は、半導体パラメータアナライザ（ケースレー社製、4200S CS）を用いて、TFT素子の動作を確認するとともに、on/off比、電界効果移動度を測定することにより行った。

【0071】

（実施例1）

Tiを含有する酸化インジウム（In<sub>2</sub>O<sub>3</sub>）からなる酸化物焼結体をスパッタリングターゲットとして使用して、酸化物半導体薄膜の成膜を実施した。このとき使用した酸化物焼結体は、Ti含有量が、Ti/In原子数比で0.018であり、In<sub>2</sub>O<sub>3</sub>相のみによって構成されていた。

【0072】

10

初めに、このスパッタリングターゲットを、アーキング抑制機能のない直流マグネットロンスパッタリング装置（トッキ株式会社製）の非磁性体ターゲット用カソードに取り付けた。また、基板には、無アルカリのガラス基板（コーニング社製、7059）を使用した。ターゲット-基板間距離を60mmに固定し、2×10<sup>-4</sup>Pa以下まで真空排気後、ArとO<sub>2</sub>の混合ガスを、酸素の比率が6.0%になるように導入し、ガス圧を0.6Paに調整した。

【0073】

直流電力300W（1.64W/cm<sup>2</sup>）を印加して直流プラズマを発生させ、成膜を実施した。具体的には、10分間のプリスパッタリング後、スパッタリングターゲットの静止対向位置に基板を配置し、基板を加熱せずにスパッタリングを実施した。これにより、膜厚50nmの酸化物半導体薄膜を形成した。得られた酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

20

【0074】

次に、この酸化物半導体薄膜に対して、大気中、300、30分間の条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜が結晶化していること、および、In<sub>2</sub>O<sub>3</sub>（222）を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、50nmであった。

30

【0075】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は3.0×10<sup>17</sup>cm<sup>-3</sup>であり、キャリア移動度は12.3cm<sup>2</sup>/Vsであった。

【0076】

（実施例2）

実施例1と同様にして得られた非晶質の酸化物半導体薄膜に対して、大気中、400、30分間の条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、In<sub>2</sub>O<sub>3</sub>（222）を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、59nmであった。

40

【0077】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は5.0×10<sup>17</sup>cm<sup>-3</sup>であり、キャリア移動度は11.6cm<sup>2</sup>/Vsであった。

【0078】

（実施例3）

スパッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で0.01としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組

50

成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

【0079】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $In_2O_3$ (222)を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、58nmであった。

【0080】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は $4.8 \times 10^{17} \text{ cm}^{-3}$ であり、キャリア移動度は $10.7 \text{ cm}^2/\text{Vs}$ であった。

10

【0081】

(実施例4)

スパッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で0.06としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

【0082】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $In_2O_3$ (222)を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、55nmであった。

20

【0083】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は $4.5 \times 10^{17} \text{ cm}^{-3}$ であり、キャリア移動度は $10.2 \text{ cm}^2/\text{Vs}$ であった。

【0084】

(実施例5)

スパッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で0.09としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

30

【0085】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $In_2O_3$ (222)を主ピークとしていることが確認された(図2参照)。このピークより結晶粒径を算出したところ、55nmであった。

40

【0086】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は $4.7 \times 10^{17} \text{ cm}^{-3}$ であり、キャリア移動度は $5.2 \text{ cm}^2/\text{Vs}$ であった。

【0087】

(実施例6)

実施例5と同様にして得られた非晶質の酸化物半導体薄膜に対して、大気中、400、30分間の条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $In_2O_3$ (222)を主ピークとしていることが確認された。このピークより結晶粒径を算

50

出したところ、58 nmであった。

【0088】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は $3.9 \times 10^{17} \text{ cm}^{-3}$ であり、キャリア移動度は $6.0 \text{ cm}^2 / \text{Vs e c}$ であった。

【0089】

(実施例7)

スパッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で0.005としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

【0090】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $\text{In}_2\text{O}_3(222)$ を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、53 nmであった。

【0091】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は $8.2 \times 10^{17} \text{ cm}^{-3}$ であり、キャリア移動度は $8.8 \text{ cm}^2 / \text{Vs e c}$ であった。

【0092】

(実施例8)

スパッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で0.12としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

【0093】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $\text{In}_2\text{O}_3(222)$ を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、54 nmであった。

【0094】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は $4.3 \times 10^{17} \text{ cm}^{-3}$ であり、キャリア移動度は $3.0 \text{ cm}^2 / \text{Vs e c}$ であった。

【0095】

(実施例9)

膜厚を15 nmとしたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対して、X線回折測定を行った結果、非晶質であることが確認された。

【0096】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $\text{In}_2\text{O}_3(222)$ を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、13 nmであった。

【0097】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜

のキャリア濃度は  $4.4 \times 10^{17} \text{ cm}^{-3}$  であり、キャリア移動度は  $10.5 \text{ cm}^2 / \text{Vs}$  であった。

【0098】

(実施例10)

膜厚を  $200 \text{ nm}$  としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対して、X線回折測定を行った結果、非晶質であることが確認された。

【0099】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $\text{In}_2\text{O}_3(222)$ を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、 $71 \text{ nm}$  であった。

【0100】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は  $2.7 \times 10^{17} \text{ cm}^{-3}$  であり、キャリア移動度は  $12.1 \text{ cm}^2 / \text{Vs}$  であった。

【0101】

(比較例1)

スペッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で  $0.001$  としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

【0102】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $\text{In}_2\text{O}_3(222)$ を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、 $55 \text{ nm}$  であった。

【0103】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は  $1.5 \times 10^{19} \text{ cm}^{-3}$  であり、キャリア移動度は  $9.6 \text{ cm}^2 / \text{Vs}$  であった。

【0104】

(比較例2)

スペッタリングターゲットとして使用した酸化物焼結体のTi含有量を、Ti/In原子数比で  $0.15$  としたこと以外は、実施例1と同様にして、酸化物半導体薄膜を得た。この酸化物半導体薄膜の組成を、ICP発光分析法により調べた結果、酸化物焼結体の組成とほぼ同じであることが確認された。また、この酸化物半導体薄膜に対してX線回折測定を行った結果、非晶質であることが確認された。

【0105】

次に、この酸化物半導体薄膜に対して、実施例1と同じ条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していること、および、 $\text{In}_2\text{O}_3(222)$ を主ピークとしていることが確認された。このピークより結晶粒径を算出したところ、 $50 \text{ nm}$  であった。

【0106】

その後、酸化物半導体薄膜のホール効果の測定を実施した結果、この酸化物半導体薄膜のキャリア濃度は  $1.3 \times 10^{19} \text{ cm}^{-3}$  であり、キャリア移動度は  $0.84 \text{ cm}^2 / \text{Vs}$  であった。

【0107】

10

20

30

40

50

## (比較例 3)

実施例 1 と同様にして得られた非晶質の酸化物半導体薄膜に対して、大気中、200、30分間の条件でアニール処理を実施した。アニール処理後の酸化物半導体薄膜に対して、X線回折測定を行った結果、該酸化物半導体薄膜は結晶化していないこと、および、 $In_2O_3$ 相のいずれの面方位のピークも存在しないことが確認された。このため、酸化物薄膜のホール効果測定は実施しなかった。

## 【0108】

なお、実施例 1 と同様にして得られた非晶質の酸化物半導体薄膜を別途用意し、加熱昇温しながら薄膜X線法による高温X線回折測定を実施した。この結果、酸化物半導体薄膜の結晶化が確認された加熱温度の範囲は、205～210であることが確認された(図3参照)。

## 【0109】

## 【表1】

|        | Ti/In | 膜厚<br>(nm) | アニール<br>温度(°C) | 結晶性 | 結晶粒径<br>(nm) | キャリア濃度<br>( $\times 10^{18}cm^{-3}$ ) | キャリア移動度<br>( $cm^2/V\cdot s$ ) |

|--------|-------|------------|----------------|-----|--------------|---------------------------------------|--------------------------------|

| 実施例 1  | 0.018 | 50         | 300            | 結晶質 | 50           | 0.30                                  | 12.3                           |

| 実施例 2  | 0.018 | 50         | 400            | 結晶質 | 59           | 0.50                                  | 11.6                           |

| 実施例 3  | 0.01  | 50         | 300            | 結晶質 | 58           | 0.48                                  | 10.7                           |

| 実施例 4  | 0.06  | 50         | 300            | 結晶質 | 55           | 0.45                                  | 10.2                           |

| 実施例 5  | 0.09  | 50         | 300            | 結晶質 | 55           | 0.47                                  | 5.2                            |

| 実施例 6  | 0.09  | 50         | 400            | 結晶質 | 58           | 0.39                                  | 6.0                            |

| 実施例 7  | 0.005 | 50         | 300            | 結晶質 | 53           | 0.82                                  | 8.8                            |

| 実施例 8  | 0.12  | 50         | 300            | 結晶質 | 54           | 0.43                                  | 3.0                            |

| 実施例 9  | 0.018 | 15         | 300            | 結晶質 | 13           | 0.44                                  | 10.5                           |

| 実施例 10 | 0.018 | 200        | 300            | 結晶質 | 71           | 0.27                                  | 12.1                           |

| 比較例 1  | 0.001 | 50         | 300            | 結晶質 | 55           | 15                                    | 9.6                            |

| 比較例 2  | 0.15  | 50         | 300            | 結晶質 | 50           | 13                                    | 0.84                           |

| 比較例 3  | 0.018 | 50         | 200            | 非晶質 | -            | -                                     | -                              |

10

20

30

## 【0110】

## [酸化物半導体薄膜の評価]

実施例 1～10 は、Ti 含有量が Ti / In 原子数比で 0.005～0.12 の範囲に制御され、かつ、大気中、400 以下でアニール処理が施された例である。このため、実施例 1～10 は、いずれも酸化物半導体膜は結晶化しており、結晶粒径、キャリア濃度およびキャリア濃度のいずれもが本発明に規定する範囲内となっていた。

## 【0111】

特に、実施例 1～4 では、Ti 含有量が Ti / In 原子数比で 0.01～0.06 の範囲に制御され、かつ、大気中、400 以下でアニール処理が施されているため、キャリア濃度が  $5 \times 10^{17} cm^{-3}$  以下であり、かつ、キャリア移動度が  $10 cm^2 / V \cdot sec$  以上という高い値を示すことが確認された。

40

## 【0112】

また、実施例 5 および 6 では、Ti 含有量が Ti / In 原子数比で 0.09 であり、かつ、大気中、400 以下でアニール処理が施されているため、キャリア濃度が  $5 \times 10^{17} cm^{-3}$  以下であり、かつ、キャリア移動度が  $5 cm^2 / V \cdot sec$  以上という値を示すことが確認された。

## 【0113】

さらに、実施例 9 および 10 では、Ti 含有量が Ti / In 原子数比で 0.018 であり、膜厚が 15 nm および 200 nm の場合に、アニール処理における加熱温度を 300

50

としても結晶化することができること、この場合の結晶粒径が 10 nm 以上であること、さらには、キャリア濃度が  $1 \times 10 \text{ cm}^{-3}$  以下、かつ、キャリア移動度が  $5 \text{ cm}^2 / \text{V sec}$  以上という値を示すことが確認された。

【0114】

これに対して、比較例 1 は、Ti 含有量が Ti / In 原子数比で 0.005 未満の例、すなわち下限値未満の例であり、この場合には、キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  を超えてしまうことが確認された。

【0115】

比較例 2 は、Ti 含有量が Ti / In 原子数比で 0.12 を超える例、すなわち上限値を超える例であり、この場合には、キャリア濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  を超え、かつ、キャリア移動度が  $1 \text{ cm}^2 / \text{V sec}$  未満となってしまうことが確認された。 10

【0116】

比較例 3 は、アニール処理における加熱温度を 200 とした例である。比較例 3 は、キャリア濃度およびキャリア移動度は良好な値を示しているが、酸化物半導体薄膜を非晶質であるため、酸素欠損を生成しやすく、熱など外的因子に対して不安定であると考えられる。

【0117】

(実施例 1)

In と Ti を酸化物として含有する酸化物焼結体からなるスパッタリングターゲットを用いて、熱酸化によって SiO<sub>2</sub> 膜が形成された、厚さ 300 nm の Si ウエハ基板の SiO<sub>2</sub> 膜上に、膜厚が 50 nm となるように、非晶質の酸化物半導体薄膜の成膜を実施した。このとき使用した酸化物焼結体は、Ti 含有量が Ti / In 原子数比で 0.018 であり、In<sub>2</sub>O<sub>3</sub> 相のみによって構成されていた。また、このときの酸化物半導体薄膜の成膜条件は、実施例 1 と同様にした。 20

【0118】

次に、得られた非晶質の酸化物半導体薄膜を大気中、300 、30 分間の条件でアニール処理することにより結晶化させ、これにより、上記の Si 基板、SiO<sub>2</sub> 膜ならびに結晶質の酸化物半導体薄膜を、それぞれゲート電極、ゲート絶縁層およびチャネル層とした。

【0119】

その後、前記チャネル層の表面に、直流マグネットロンスパッタ法によって、厚さ 5 nm の Ti 膜、および、厚さ 100 nm の Au 膜を順次成膜して、Au / Ti 積層膜からなるソース電極およびドレイン電極を形成し、図 1 に示す構成の薄膜トランジスタ (TFT 素子) を得た。なお、ソース電極およびドレイン電極の成膜条件は、スパッタガスを Ar のみとし、直流電力を 50 W に変更したこと以外は、酸化物半導体薄膜の成膜条件と同様とした。 30

【0120】

さらに、ソース電極およびドレイン電極に対して、メタルマスクを用いてパターニングを行い、チャネル長 100 μm 、チャネル幅 450 μm の TFT 素子を得た。

【0121】

得られた TFT 素子の動作特性を、半導体パラメータアナライザを用いて調べた結果、TFT 素子としての動作特性が確認できた。また、この TFT 素子は、on / off 比が 108 以上、電界効果移動度が  $22.5 \text{ cm}^2 / \text{V sec}$  という良好な値を示すことが確認された。 40

【符号の説明】

【0122】

- 1 ゲート電極

- 2 ゲート絶縁膜

- 3 チャネル層

- 4 ソース電極

## 5 ドレイン電極

【図1】

【図2】

【図3】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/24 (2006.01) C 23 C 14/08 D

C 23 C 14/58 A

H 01 L 29/24

(56)参考文献 国際公開第2008 / 117739 (WO, A1)

特開2011 - 146571 (JP, A)

特開2008 - 192721 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786

H 01 L 21 / 336