(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-214267

(P2007-214267A)

(43) 公開日 平成19年8月23日(2007.8.23)

| (51) Int.CI.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 27/06</b> (2006.01)  | H01L 27/06 | 311C 5FO38  |

| <b>H01L 21/822</b> (2006.01) | H01L 27/04 | H 5FO48     |

| <b>H01L 27/04</b> (2006.01)  | H01L 29/78 | 301K 5F140  |

| <b>H01L 29/78</b> (2006.01)  | H01L 29/78 | 301H        |

審査請求 未請求 請求項の数 7 O.L. (全 7 頁)

|           |                            |            |                                                 |

|-----------|----------------------------|------------|-------------------------------------------------|

| (21) 出願番号 | 特願2006-31210 (P2006-31210) | (71) 出願人   | 000002325<br>セイコーインスツル株式会社<br>千葉県千葉市美浜区中瀬1丁目8番地 |

| (22) 出願日  | 平成18年2月8日 (2006.2.8)       | (74) 代理人   | 100079212<br>弁理士 松下 義治                          |

|           |                            | (72) 発明者   | 海老原 美香<br>千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内      |

|           |                            | (72) 発明者   | 理崎 智光<br>千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内       |

|           |                            | F ターム (参考) | 5F038 BH05 BH07 BH13 BH16 EZ12<br>EZ13 EZ20     |

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【要約】

【課題】 従来のコンベンショナル型のドレイン構造を持つN MOSトランジスタを用いた静電保護回路では不可能であった動作電圧(トリガ-電圧)および保持電圧をが低く、かつ、自由に設定できる静電保護素子を容易に提供する。

【解決手段】 コンベンショナル型のドレイン構造を持つN MOSトランジスタのN型ソース・ドレイン拡散層の間に局所的にP型拡散層を形成する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

P型半導体基板上に形成されたP型ウエル領域と、

前記P型ウエル領域上に形成され、内部に能動素子領域を有するフィールド酸化膜と、

前記P型ウエル領域上にゲート酸化膜を介して形成されたゲート電極と、

前記フィールド酸化膜と前記ゲート電極とに囲まれているN型ソースおよびドレイン領域と、

前記ドレイン領域に接して、前記N型ソースおよびドレイン領域の間に形成された前記P型ウェル領域よりも高濃度のP型領域と、

前記N型ソースおよびドレイン領域と前記ゲート電極の上層に形成される配線とを電気的に絶縁する層間絶縁膜と

前記配線と前記ゲート電極と前記N型ソースおよびドレインとをそれぞれ電気的に接続するため前記層間絶縁膜に設けられたコンタクト孔とからなる半導体装置。 10

## 【請求項 2】

N型半導体基板上に形成されたP型ウエル領域と、

前記P型ウエル領域上に形成され、内部に能動素子領域を有するフィールド酸化膜と、

前記P型ウエル領域上にゲート酸化膜を介して形成されたゲート電極と、

前記フィールド酸化膜と前記ゲート電極とに囲まれているN型ソースおよびドレイン領域と、

前記ドレイン領域に接して、前記N型ソースおよびドレイン領域の間に形成された前記P型ウェル領域よりも高濃度のP型領域と、

前記N型ソースおよびドレイン領域と前記ゲート電極の上層に形成される配線とを電気的に絶縁する層間絶縁膜と

前記配線と前記ゲート電極と前記N型ソースおよびドレインとをそれぞれ電気的に接続するため前記層間絶縁膜に設けられたコンタクト孔とからなる半導体装置。 20

## 【請求項 3】

前記P型領域が前記N型ソースおよびドレイン領域の間に全面に形成された請求項1あるいは2に記載の半導体装置。 30

## 【請求項 4】

前記P型領域が前記N型ソースおよびドレイン領域の間に全面に形成された請求項1あるいは2に記載の半導体装置。 30

## 【請求項 5】

前記P型領域に導入する不純物濃度が $1\text{E}16 \sim 1\text{E}20\text{ atoms/cm}^3$ である請求項1あるいは2に記載の半導体装置。

## 【請求項 6】

前記N型ソースおよびドレイン領域に導入する不純物をリンとした請求項1あるいは2に記載の半導体装置。

## 【請求項 7】

前記N型ソースおよびドレイン領域に導入する不純物をリンおよび砒素とし、二重拡散構造にした請求項1あるいは2に記載の半導体装置。 40

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は半導体装置、特にCMOS半導体装置の静電気による破壊を防止するために用いられる半導体装置に関する。

## 【背景技術】

## 【0002】

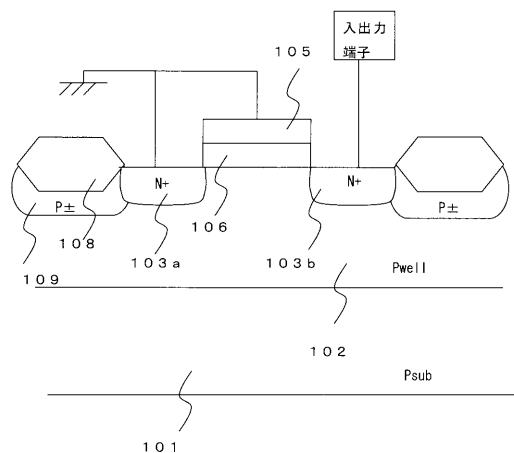

従来、CMOS半導体装置では、静電放電(Electrostatic discharge:以下ESDと称す)保護素子として、図3に示すようなゲートを基板電位におとしたコンベンショナル型のドレイン構造を持つNMOSトランジスタがよく用いられている。CMOS半導体裝 50

置の最大動作電圧以上でかつ通常のN M O Sトランジスタではブレークダウンには至らない電圧範囲にておきるこのトランジスタの表面ブレークダウンを利用して、ドレイン103bとP型基板101の間に電流を流すことでP型基板101の電位の上昇を引き起こし、エミッタとなるソース103aとベースとなるP型基板101の間に順方向電圧がかかるにより、N P Nバイポーラ動作をスイッチングさせ、大電荷を放出させるのが動作原理である。また、N M O Sトランジスタのチャネルの長さであるL長を調節することにより、N P Nバイポーラ動作時の保持電圧を半導体装置の最大動作電圧以上に容易に設定することが可能であり、全ての電荷を放出し終わった後、定常状態に復帰することができる。N M O Sトランジスタのブレークダウン時に最も熱が発生するドレイン側N+層の構造はE S D保護素子の電流耐性(熱耐性)を決める重要な因子である。発熱を分散させる構造、すなわちより深く均一なプロファイルが得られるリングN+拡散層の不純物として一般的に用いられる。

10

【特許文献1】特開2001-144191号公報

【特許文献2】特表2002-524878号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、半導体の微細化、デバイスの小型化が進められ、C M O S半導体装置の低電圧化及びゲート酸化膜の薄膜化により、従来のコンベンショナル型のドレイン構造を持つN M O Sトランジスタを用いた静電保護回路では、表面ブレークダウンに至る前にゲート酸化膜破壊電圧に達してしまったり、静電保護回路が動作する前にC M O S半導体装置が静電気により破壊してしまったりするという問題点を有していた。

20

【0004】

本発明は、従来のコンベンショナル型のドレイン構造を持つN M O Sトランジスタを用いた静電保護回路では不可能であった動作電圧(トリガ電圧)および保持電圧が低く、かつ、自由に設定できる静電保護素子を、小さな占有面積でコストをかけずに提供することを目的とする。

20

【課題を解決するための手段】

【0005】

上記目的を達成するために本発明の半導体装置が採用した手段は次の通りである。

30

(1) P型半導体基板上に形成されたP型ウエル領域と、前記P型ウエル領域上に形成されたフィールド酸化膜と、前記P型ウエル領域上にゲート酸化膜を介して形成されたゲート電極と、前記フィールド酸化膜と前記ゲート電極とに囲まれているN型ソース・ドレイン領域と、前記N型ソース・ドレイン領域の間に局所的に形成されたP型ウェル領域よりも高濃度のP型領域と、前記ゲート電極と前記N型ソース・ドレインとそれらの上層に形成される配線とを電気的に絶縁する層間膜と、前記配線と前記ゲート電極と前記N型ソース・ドレインとを電気的に接続を行うためのコンタクト孔からなる半導体装置とした。

(2) 前記N型ソース・ドレイン領域の間、全面にP型領域を形成した半導体装置とした。

40

(3) 前記N型ソース・ドレイン領域の間に形成されたP型領域に導入する不純物濃度を1E16~1E20atoms/cm<sup>3</sup>とした半導体装置とした。

(4) 前記N型ソース・ドレイン領域に導入する不純物がリンである半導体装置とした。

(5) 前記N型ソース・ドレイン領域に導入する不純物はリンと砒素とし、二重拡散構造にした半導体装置とした。

【発明の効果】

【0006】

本発明によれば、コンベンショナル型のドレイン構造を持つN M O Sトランジスタを用いた静電保護回路に、P型の不純物を導入することで、従来のコンベンショナル型のドレイン構造を持つN M O Sトランジスタを用いた静電保護回路では不可能であったトリガ電圧は低くて、保持電圧が容易に設定可能な素子を得ることができる。これにより、低電圧

50

化したC M O SトランジスタをE S Dから保護可能なE S D保護回路を実現する事が出来、多くのI Cにおいて多大な効果が得られる。

【発明を実施するための最良の形態】

【0 0 0 7】

以下、図面を参照して本発明の好適な実施例を説明する。

【実施例1】

【0 0 0 8】

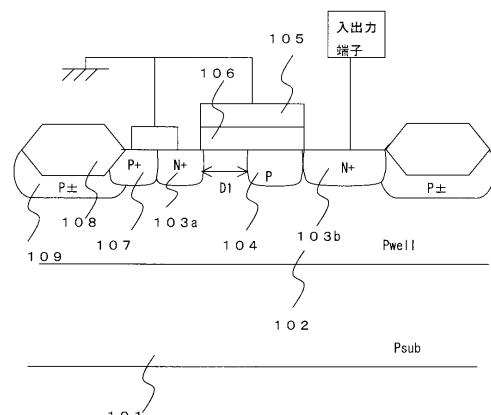

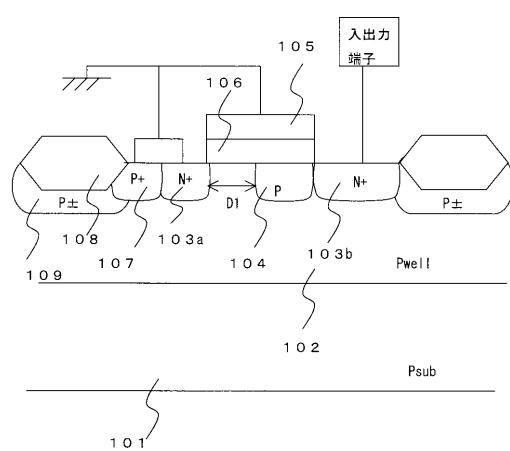

図1は本発明による半導体装置のコンベンショナル型のドレイン構造を持つN M O Sトランジスタの第一実施例を示す模式的断面図である。

【0 0 0 9】

P型シリコン半導体基板101上にP型ウェル領域102をつくり、P型ウェル領域上に形成するゲート酸化膜106及び多結晶シリコンゲート電極105と、ゲート電極両端のシリコン基板表面に形成する高濃度のN型ソース拡散層103aとN型ドレイン拡散層103bとの間に局所的に形成される高濃度のP型拡散層104及び前記P型ウェル領域102の電位を取るための高濃度のP型拡散層107から構成する。N型ドレイン拡散層103bは入出力端子への配線に接続され、N型ソース拡散層103aとP型ウェル領域102の電位を取るためのP型拡散層107及び多結晶シリコンゲート電極は基準電位であるV<sub>ss</sub>配線に接続される。また、配線とゲート電極とN型ソース・ドレインとを電気的に接続を行うためのコンタクト孔(図示せず)を堆積された層間絶縁膜(図示せず)に形成する。素子の間に分離を目的としてフィールド酸化膜108及びチャネルトップ領域109が形成される。尚、必ずしもP型シリコン半導体基板を用いる必要はなく、N型シリコン半導体基板を用いて、N M O Sトランジスタを作ってもよい。

【0 0 1 0】

入出力端子にプラス電荷が入ってきた場合、N型ドレイン拡散層103bとN型ソース・ドレイン拡散層の間に形成されたP型拡散層104のN+Pダイオードがブレークダウンし、これがトリガ電圧となり、P型ウェル層102内に電流が流れ、N型ドレイン拡散層～P型ウェル層～N型ソース拡散層からなるN P Nトランジスタのバイポーラ動作をオンさせ、すばやく電荷を放出できる構造となっている。N型ドレイン拡散層及びP型拡散層の濃度を変えることにより容易にトリガ電圧を最大定格以上でゲート酸化膜破壊電圧以下に設定できる。P型拡散層を形成するためには、BF<sub>2</sub>またはボロンをドーズ量 $1 \times 10^{12}$ ～ $1 \times 10^{16}$ atoms/cm<sup>2</sup>でイオン注入する。これは濃度に換算すると $1 \times 10^{16}$ ～ $1 \times 10^{20}$ atoms/cm<sup>3</sup>程度である。また、N型ソース拡散層とN型ドレイン拡散層の間にP型拡散層を形成することにより、パンチスルーや抑制することができ、L長を縮小することができる。

【0 0 1 1】

また、図1で示したように、N型ソース拡散層とゲート直下に形成されたP型拡散層との距離(D1)を変更することにより容易にN P Nトランジスタのバイポーラ動作の保持電圧を任意の値に設定することができる。更に、P型拡散層の濃度を変更することにより、容易に保持電圧を任意の値に設定することもできる。

【0 0 1 2】

N型ドレイン拡散層はN+Pダイオードのブレークダウン時にもっとも熱が発生するので、深く均一な濃度プロファイルが得られるリンを使用し、発熱を分散させる構造となっている。これにより、E S D保護素子の熱耐性を向上することができる。さらに、N型ソース・ドレイン拡散層を形成する際に導入する不純物をリン・砒素の二重拡散層としてもよい。砒素を注入することにより、N+Pダイオードのブレークダウン耐圧を容易に下げることができる。

【0 0 1 3】

また、ゲート電極をV<sub>ss</sub>に配線しておくことにより、リーク電流を抑制することができる構造となっている。ただし、ゲート電極は必ずしもつける必要はない。

【実施例2】

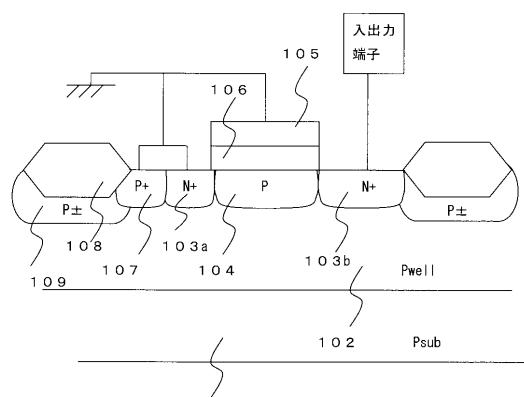

【0 0 1 4】

10

20

30

40

50

図2は本発明による半導体装置のコンベンショナル型のドレイン構造を持つN MOSトランジスタの第2実施例を示す模式的断面図である。

【0015】

図2で示したように、N型ソース・ドレイン拡散層間のゲート直下全面にP型拡散層を形成してもよい。

【図面の簡単な説明】

【0016】

【図1】本発明の半導体装置の第一実施例を示すコンベンショナル型N MOSトランジスタのESD保護素子の模式的断面図である。

【図2】本発明の半導体装置の第一実施例を示すコンベンショナル型N MOSトランジスタのESD保護素子の模式的断面図である。 10

【図3】従来のリン拡散コンベンショナル型N MOSオーフトランジスタのESD保護素子を示す断面図である。

【符号の説明】

【0017】

- 101 P型シリコン半導体基板

- 102 P型ウェル層

- 103a N+型ソース拡散層

- 103b N+型ドレイン拡散層

- 104 P型拡散層

- 105 多結晶シリコンゲート電極

- 106 ゲート酸化膜

- 107 P+型拡散層

- 108 フィールド酸化膜

- 109 チャネルストップ

【図1】

【図2】

【図3】

フロントページの続き

F ターム(参考) 5F048 AA02 AC01 AC03 BA01 BD02 BD04 BE02 BE09 BF16 BF18

BG12 BH07 CC08 CC10 CC13 CC15 CC16 CC19

5F140 AA38 AB03 BA01 BB11 BH30 BH43 BH47