(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6374036号

(P6374036)

(45) 発行日 平成30年8月15日(2018.8.15)

(24) 登録日 平成30年7月27日(2018.7.27)

(51) Int.Cl.

G O 1 K 7/01 (2006.01)

F 1

G O 1 K 7/01

C

請求項の数 29 (全 24 頁)

(21) 出願番号 特願2016-571693 (P2016-571693)

(86) (22) 出願日 平成27年5月18日 (2015.5.18)

(65) 公表番号 特表2017-517736 (P2017-517736A)

(43) 公表日 平成29年6月29日 (2017.6.29)

(86) 國際出願番号 PCT/US2015/031430

(87) 國際公開番号 WO2015/191251

(87) 國際公開日 平成27年12月17日 (2015.12.17)

審査請求日 平成29年12月8日 (2017.12.8)

(31) 優先権主張番号 14/300,110

(32) 優先日 平成26年6月9日 (2014.6.9)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

Q U A L C O M M I N C O R P O R A T

E D

アメリカ合衆国、カリフォルニア州 92

1 2 1 - 1 7 1 4 、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

最終頁に続く

(54) 【発明の名称】低電力低成本温度センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

温度センサであって、

ゲートを有する第1のトランジスタと、

前記第1のトランジスタの前記ゲートに結合されたゲートを有する第2のトランジスタと、

前記第1および第2のトランジスタの前記ゲートに結合されたキャパシタと、

前記第1および第2のトランジスタの前記ゲートにバイアスをかけること、ここにおいて、前記第1および第2のトランジスタは、サブスレッショルド領域において動作する、および前記第2のトランジスタのソースに結合されたレジスタを使用して、前記第1のトランジスタのゲート・ソース間電圧と前記第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することを行うように構成されたバイアス回路と、ここにおいて、前記第1のトランジスタの前記ゲート・ソース間電圧と前記第2のトランジスタの前記ゲート・ソース間電圧との前記差は、前記レジスタの両端に印加され、前記生成された電流は、前記レジスタ中を流れる電流に比例する。

前記電流をデジタル温度示数に変換するように構成されたアナログ・デジタル変換器(A D C)と

を備える、温度センサ。

## 【請求項 2】

前記A D Cは、

10

前記電流を周波数に変換するように構成された発振器と、

前記周波数をデジタルカウント値に変換するように構成されたカウンタと、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、請求項 1 に記載の温度センサ。

**【請求項 3】**

前記生成された電流は、前記レジスタ中を流れる前記電流にほぼ等しい、請求項 1 に記載の温度センサ。

**【請求項 4】**

前記レジスタは、前記第 2 のトランジスタの前記ソースと接地との間で結合される、請求項 1 に記載の温度センサ。

10

**【請求項 5】**

前記第 1 のトランジスタは、第 1 の電界効果トランジスタ (FET) を備え、前記第 2 のトランジスタは、第 2 の FET を備える、請求項 1 に記載の温度センサ。

**【請求項 6】**

前記バイアス回路は、前記第 1 のトランジスタの電流と前記第 2 のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第 1 および第 2 のトランジスタの前記ゲートにバイアスをかけるように構成される、請求項 1 に記載の温度センサ。

**【請求項 7】**

前記比は、1 にほぼ等しい、請求項 6 に記載の温度センサ。

**【請求項 8】**

20

温度を感知するための方法であって、

第 1 および第 2 のトランジスタがサブスレッショルド領域において動作するように、前記第 1 のトランジスタのゲートおよび前記第 2 のトランジスタのゲートにバイアスをかけることと、

キャパシタを前記第 1 および第 2 のトランジスタの前記ゲートに結合することと、

前記第 1 のトランジスタのゲート・ソース間電圧と前記第 2 のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することと、

前記電流をデジタル温度示数に変換することと

を備え、

前記電流を生成することは、前記第 1 のトランジスタの前記ゲート・ソース間電圧と前記第 2 のトランジスタの前記ゲート・ソース間電圧との前記差を、レジスタの両端に印加することを備え、前記生成された電流は、前記レジスタ中を流れる電流に比例する、方法。

30

**【請求項 9】**

前記電流を前記デジタル温度示数に変換することは、

前記電流を周波数に変換することと、

前記周波数をデジタルカウント値に変換することと、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、請求項 8 に記載の方法。

**【請求項 10】**

40

前記生成された電流は、前記レジスタ中を流れる前記電流にほぼ等しい、請求項 8 に記載の方法。

**【請求項 11】**

前記第 1 のトランジスタは、第 1 の電界効果トランジスタ (FET) を備え、前記第 2 のトランジスタは、第 2 の FET を備える、請求項 8 に記載の方法。

**【請求項 12】**

前記第 1 のトランジスタの電流と前記第 2 のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第 1 および第 2 のトランジスタの前記ゲートにバイアスをかけることをさらに備える、請求項 8 に記載の方法。

**【請求項 13】**

50

前記比は、1にほぼ等しい、請求項12に記載の方法。

**【請求項14】**

温度を感知するための装置であつて、

第1および第2のトランジスタがサブスレッショルド領域において動作するように、前記第1のトランジスタのゲートおよび前記第2のトランジスタのゲートにバイアスをかけるための手段と、ここにおいて、キャパシタが前記第1および第2のトランジスタの前記ゲートに結合される、

前記第1のトランジスタのゲート・ソース間電圧と前記第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成するための手段と、

前記電流をデジタル温度示数に変換するための手段と

を備え、

前記電流を生成するための前記手段は、前記第1のトランジスタの前記ゲート・ソース間電圧と前記第2のトランジスタの前記ゲート・ソース間電圧との前記差を、レジスタの両端に印加するための手段を備え、前記生成された電流は、前記レジスタ中を流れる電流に比例する、

装置。

**【請求項15】**

前記電流を前記デジタル温度示数に変換するための前記手段は、

前記電流を周波数に変換するための手段と、

前記周波数をデジタルカウント値に変換するための手段と、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、請求項14に記載の装置。

**【請求項16】**

前記生成された電流は、前記レジスタ中を流れる前記電流にほぼ等しい、請求項14に記載の装置。

**【請求項17】**

前記第1のトランジスタは、第1の電界効果トランジスタ(FET)を備え、前記第2のトランジスタは、第2のFETを備える、請求項14に記載の装置。

**【請求項18】**

前記第1のトランジスタの電流と前記第2のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第1および第2のトランジスタの前記ゲートにバイアスをかけるための手段をさらに備える、請求項14に記載の装置。

**【請求項19】**

前記比は、1にほぼ等しい、請求項18に記載の装置。

**【請求項20】**

前記バイアス回路は、前記第1および第2のトランジスタのうちの少なくとも1つに各自結合された複数の電流ミラーをさらに備える、請求項1に記載の温度センサ。

**【請求項21】**

前記複数の電流ミラーの各々は、複数の電界効果トランジスタ(FET)を含む、請求項20に記載の温度センサ。

**【請求項22】**

前記複数の電流ミラーの各々内の前記複数のFETは、第1のゲート幅のゲート幅で構成され、

前記第1および第2のトランジスタは、前記第1のゲート幅よりも十分に大きい第2のゲート幅で構成され、

前記複数の電流ミラーの各々内の前記複数のFETがアクティブ領域において動作する一方で、前記第1および第2のトランジスタは、前記サブスレッショルド領域において動作する、

請求項21に記載の温度センサ。

**【請求項23】**

10

20

30

40

50

前記キャパシタは、前記第1および第2のトランジスタの前記ゲートにバイアスをかけることの調整を引き起こす、請求項8に記載の方法。

**【請求項24】**

バイアスをかけることは、前記第1および第2のトランジスタのうちの少なくとも1つに結合された1つまたは複数の電流ミラーを有する前記第1および第2のトランジスタに流れるか、またはそこから外に流れるより多くの電流のうちの1つをミラーすることをさらに備える、請求項8に記載の方法。

**【請求項25】**

前記1つまたは複数の電流ミラーの各々は、第1のゲート幅のゲート幅で構成された複数の電界効果トランジスタ(FET)を含み、

10

前記第1および第2のトランジスタは、前記第1のゲート幅よりも十分に大きい第2のゲート幅で構成され、

前記それぞれのゲート幅により、前記1つまたは複数の電流ミラー内の前記複数のFETをアクティブ領域において動作する一方で、前記第1および第2のトランジスタを前記サブスレッショルド領域において動作する、

請求項24に記載の方法。

**【請求項26】**

前記第1のトランジスタの前記ゲートおよび前記第2のトランジスタの前記ゲートにバイアスをかけるための前記手段を調整するための手段をさらに備え、調整するための前記手段は、前記第1および第2のトランジスタの前記ゲートに結合された前記キャパシタを含む、請求項14に記載の装置。

20

**【請求項27】**

前記第1のトランジスタの前記ゲートおよび前記第2のトランジスタの前記ゲートにバイアスをかけるための手段のための前記手段は、前記第1および第2のトランジスタの電流を電流ミラーするための手段をさらに備える、請求項14に記載の装置。

**【請求項28】**

電流ミラーするための手段は、複数の電界効果トランジスタ(FET)を含む、請求項27に記載の装置。

**【請求項29】**

電流ミラーするための前記手段内の前記複数のFETは、第1のゲート幅のゲート幅で構成され、

30

前記第1および第2のトランジスタは、前記第1のゲート幅よりも十分に大きい第2のゲート幅で構成され、

前記それぞれのゲート幅により、前記複数の電流ミラー内の前記複数のFETがアクティブ領域において動作する一方で、前記第1および第2のトランジスタは、前記サブスレッショルド領域において動作する、

請求項28に記載の装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

40

[0001] 本開示の態様は、一般に、温度感知に関し、より具体的には、温度センサに関する。

**【背景技術】**

**【0002】**

[0002] 複数の温度センサがチップ上に統合され、チップ上の様々な位置で温度をモニタリングするために使用され得る。センサからの温度示数(Temperature readings)は、温度示数に基づいてチップ上の回路(例えば、中央処理ユニット(CPU))を管理する温度管理デバイスに供給され得る。例えば、温度管理デバイスは、チップ上の1つまたは複数の位置での温度が高くなりすぎると防ぐために、温度示数に基づいて回路を管理し得、それは、場合によってはチップを傷つける可能性がある。この例では、温度示数が温

50

度閾値よりも上昇する場合、温度管理デバイスは、温度を下げる（例えば、回路の周波数を低減する）ための措置を講じ得る。

#### 【発明の概要】

##### 【0003】

[0003] 下記は、そのような実施形態の基本的な理解を提供するために、1つまたは複数の実施形態の簡略化された概要を提示する。この概要は、予期される全ての態様の広範囲に及ぶ要約ではなく、全ての実施形態のキーまたは不可欠な要素を識別すること、あるいは、任意のまたは全ての実施形態の範囲を描くことが意図されるものではない。その唯一の目的は、後に提示されるより詳細な説明への前置きとして、1つまたは複数の実施形態のうちのいくつかの概念を簡略化されたな形式で提示することである。

10

##### 【0004】

[0004] 第1の態様によると、温度センサが本明細書で説明される。温度センサは、ゲートを有する第1のトランジスタと、第1のトランジスタのゲートに結合されたゲートを有する第2のトランジスタと、第1および第2のトランジスタがサブスレッショルド領域 (a sub-threshold region) において動作するように、第1および第2のトランジスタのゲートにバイアスをかけること、および第1のトランジスタのゲート・ソース間電圧 (gate-to-source voltage) と第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することを行なうように構成されたバイアス回路と、を備える。温度センサはまた、電流をデジタル温度示数に変換することを行なうように構成されたアナログ・デジタル変換器 (A D C : analog-to-digital converter) を備える。

20

##### 【0005】

[0005] 第2の態様は、温度を感知するための方法に関する。方法は、第1および第2のトランジスタがサブスレッショルド領域において動作するように、第1のトランジスタのゲートおよび第2のトランジスタのゲートにバイアスをかけることと、第1のトランジスタのゲート・ソース間電圧と第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することとを備える。方法はまた、電流をデジタル温度示数に変換することを備える。

##### 【0006】

[0006] 第3の態様は、温度を感知するための装置に関する。本装置は、第1および第2のトランジスタがサブスレッショルド領域において動作するように、第1のトランジスタのゲートおよび第2のトランジスタのゲートにバイアスをかけるための手段と、第1のトランジスタのゲート・ソース間電圧と第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成するための手段とを備える。本装置はまた、電流をデジタル温度示数に変換するための手段を備える。

30

##### 【0007】

[0007] 第4の態様は、温度センサと温度管理デバイスとを備えるシステムに関する。温度センサは、ゲートを有する第1のトランジスタと、第1のトランジスタのゲートに結合されたゲートを有する第2のトランジスタと、第1および第2のトランジスタがサブスレッショルド領域において動作するように、第1および第2のトランジスタのゲートにバイアスをかけること、および第1のトランジスタのゲート・ソース間電圧と第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することを行なうように構成されたバイアス回路と、を備える。温度センサはまた、電流をデジタル温度示数に変換することを行なうように構成されたアナログ・デジタル変換器 (A D C ) を備える。温度管理デバイスは、温度センサに結合され、デジタル温度示数に基づいて回路の温度を決定すること、および温度に基づいて回路の1つまたは複数のパラメータを調整することを行なうように構成される。

40

##### 【0008】

[0008] 前述のおよび関連する目的を達成するために、1つまたは複数の実施形態が以下で十分に説明され、特に請求項において示される特徴を備える。下記の説明および添付された図面は、1つまたは複数の実施形態の実例となる特定の態様を詳細に説明する。し

50

かしながら、これらの態様は、様々な実施形態の原理が用いられ得る様々な方法のうちのごく一部を示すものであり、説明された実施形態は、全てのこのような態様およびそれらの同等物を含むことが意図される。

**【図面の簡単な説明】**

**【0009】**

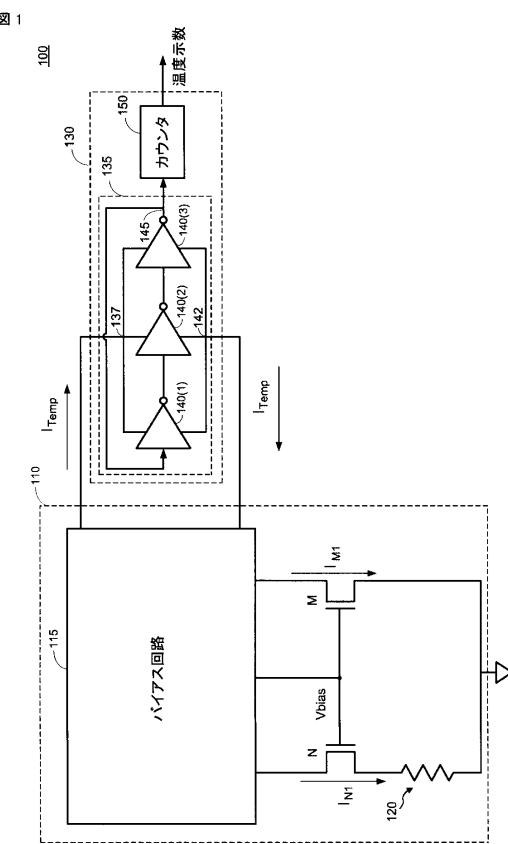

【図1】[0009] 図1は、本開示の実施形態に従った温度センサを示す。

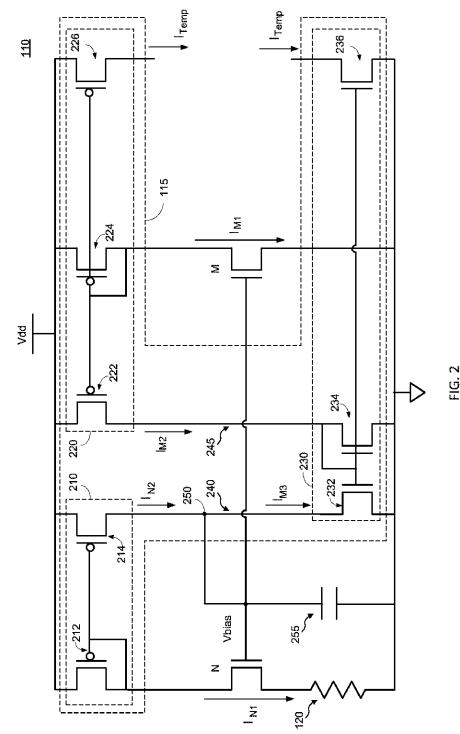

【図2】[0010] 図2は、本開示の実施形態に従った、サブスレッショルド領域内で動作するトランジスタを備える温度感知回路の例示的な実施を示す。

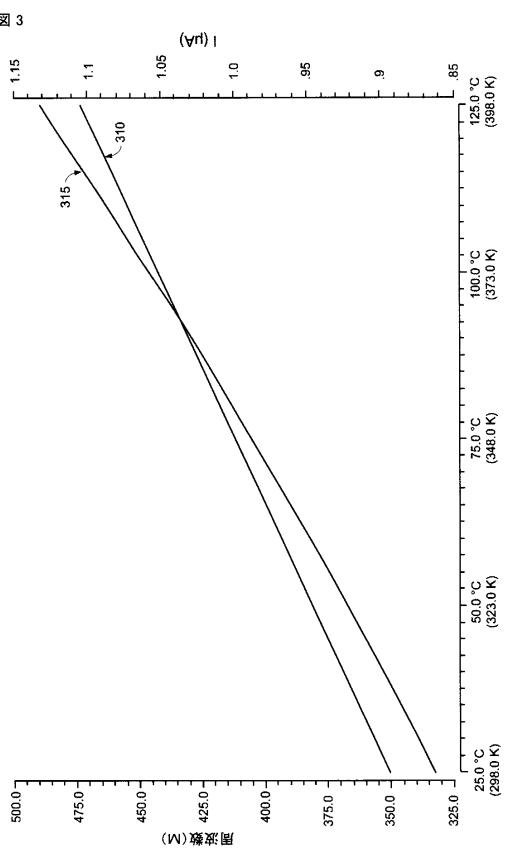

【図3】[0011] 図3は、本開示の実施形態に従った、温度に応じた温度センサにおける周波数および電流を示す表である。 10

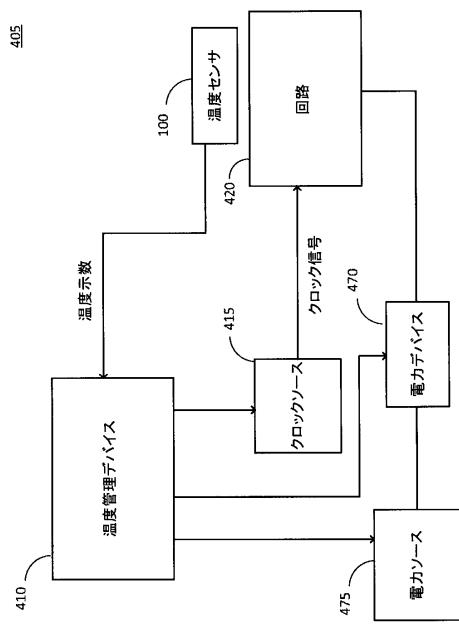

【図4】[0012] 図4は、本開示の実施形態に従った、温度管理デバイスの例を示す。

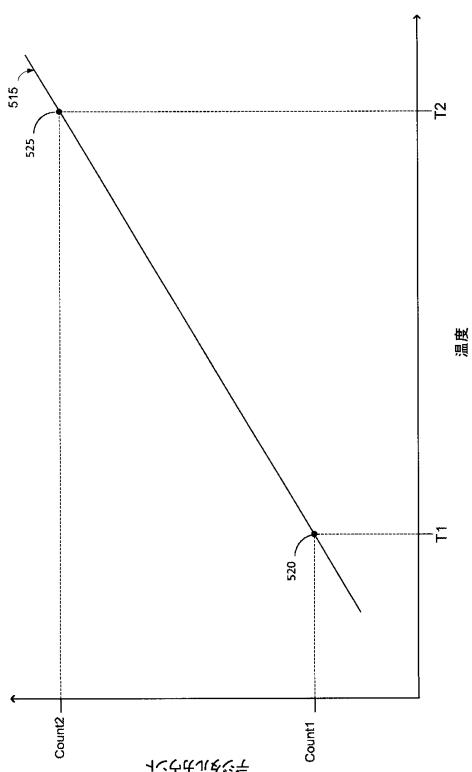

【図5】[0013] 図5は、本開示の実施形態に従った、温度較正の例を図示する表である。

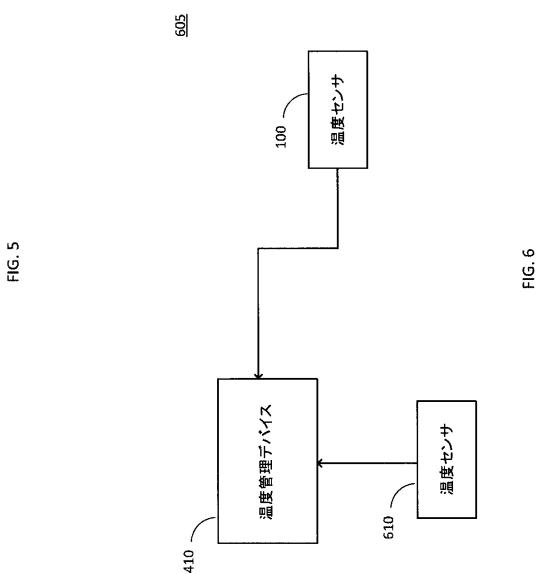

【図6】[0014] 図6は、本開示の実施形態に従った、温度センサを較正するためのシステムの例を示す。

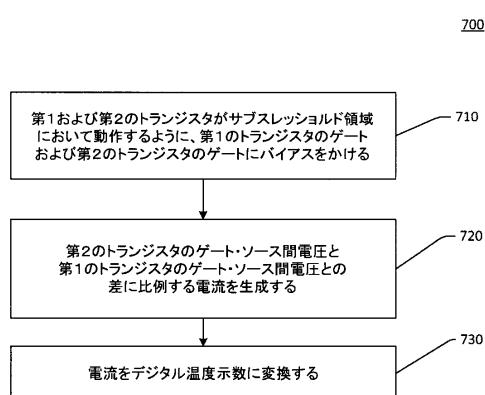

【図7】[0015] 図7は、本開示の実施形態に従った、温度を感知するための方法のフローチャートである。

**【詳細な説明】**

**【0010】**

[0016] 添付された図面に関連して下記で説明される詳細な説明は、様々な構成の説明を意図したものであり、本明細書で説明される概念が実現され得る唯一の構成を表すことを意図したものではない。詳細な説明は、様々な概念の完全な理解を提供する目的のために特定の詳細を含む。しかしながら、これらの概念が、これらの特定の詳細なしで行われ得ることは、当業者にとって明らかであろう。いくつかの例では、そのような概念をあいまいにすることを避けるために、周知の構造およびコンポーネントが、ブロック図形態で示される。 20

**【0011】**

[0017] 複数の温度センサがチップ上に統合され、チップ上の様々な位置で温度をモニタリングするために使用され得る。センサからの温度示数は、温度示数に基づいてチップ上の回路（例えば、中央処理ユニット（CPU）、グラフィック処理ユニット（GPU）、モデムなど）を管理する温度管理デバイスに供給され得る。例えば、温度管理デバイスは、チップ上の1つまたは複数の位置での温度が高くなりすぎると防ぐために、温度示数に基づいて回路を管理し得、それは、場合によってはチップを傷つける可能性がある。この例では、温度示数が温度閾値よりも上昇する場合、温度管理デバイスは、温度を下げる（例えば、回路の周波数およびまたは電源電圧を低減する）ための措置を講じ得る。 30

**【0012】**

[0018] バイポーラベースの温度センサ（bipolar-based temperature sensor）は、チップ上の温度を測定するために使用され得る。バイポーラベースの温度センサは、2つのバイポーラ接合トランジスタ（BJT：bipolar junction transistors）を備え得、ここで、BJTの電流の比が固定され、BJTのベース・エミッタ電圧（base-emitter voltages of the BJTs）に基づいて温度示数が生成される。従来のバイポーラベースの温度センサは、複素型シグマ（complex sigma）アナログ・デジタル変換器（ADC）を使用し、それは、比較的多くの量の電力を消費し、チップの比較的大きなエリアを占有する。加えて、これらの温度センサは、アナログ電力供給レール（analog power supply rail）を必要とし、それは通常、（例えば、CPUにおいて）デジタルロジックに電力を供給する（power）ために使用される電力供給レールよりも高い電圧である。結果として、これらの温度センサの配置は、アナログ供給レールが利用可能であるチップのエリアに制限される。これは、CPU内のホットスポットの正確な温度示数を得るために、CPU内にこれらのうちのセンサの1つまたは複数を配置することを妨げ得る。 40

**【0013】**

10

20

30

40

50

[0019] 従って、小さく、より低い電力の温度センサが望ましい。また、デジタルロジックに電力を供給するために使用される電力供給レールによって電力を供給されることができる温度センサが望ましい。これは、温度センサがデジタルロジックを備える回路（例えば、CPU）内に置かれる（組み込まれる）ことを可能にし得る。

#### 【0014】

[0020] 図1は、本開示の実施形態に従った温度センサ100を示す。温度センサ100は、温度感知回路110とアナログ・デジタル変換器130(ADC)とを備える。温度感知回路110は、下記にさらに説明されるような、温度に比例する電流（「 $I_{T_{em}}_p$ 」と表される）を生成するように構成される。ADC130は、温度感知回路110からの電流 $I_{T_{em}}_p$ をデジタル温度示数に変換するように構成される。

10

#### 【0015】

[0021] 温度感知回路110は、第1のトランジスタNと第2のトランジスタMとを備え、これらの両方は、N型電界効果トランジスタ(NFET:N-type field-effect transistors)であり得る。第1および第2のトランジスタNおよびMのゲートは、連結され、電圧バイアスVbiasによってバイアスをかけられる。温度感知回路110はまた、第1のトランジスタNのソースと接地との間に結合されたレジスタ120を備える。第2のトランジスタMのソースは、接地に結合される。ある態様では、レジスタ120は、対象とする温度範囲(a temperature range of interest)にわたってほぼ温度が不变である抵抗を有し、ポリシリコンレジスタ(polysilicon resistor)または他のタイプのレジスタを備え得る。

20

#### 【0016】

[0022] 温度感知回路110はさらに、第1および第2のトランジスタNおよびMのドレインと、第1および第2のトランジスタNおよびMのゲートとに結合されたバイアス回路115を備える。バイアス回路115は、第1のトランジスタNの電流（「 $I_{N_1}$ 」と表される）を感知すること、第2のトランジスタMの電流（「 $I_{M_1}$ 」と表される）を感知すること、および感知した電流に基づいて第1および第2のトランジスタNおよびMのゲートにおいて電圧バイアスVbiasを調整することを行うように構成される。より具体的には、バイアス回路115は、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ と $I_{M_1}$ との比が、対象とする温度範囲にわたってほぼ一定である（固定される）ようには、電圧バイアスVbiasを調整する。ある例では、電流 $I_{N_1}$ と $I_{M_1}$ との比は、下記でさらに説明されるように、1にほぼ等しくなり得る。バイアス回路115はまた、第1および第2のトランジスタNおよびMの両方がサブスレッショルド領域で動作する（すなわち、電圧バイアスVbiasが第1および第2のトランジスタNおよびMの閾値電圧を下回る）ように、電圧バイアスVbiasを調整する。これらの条件下で第1および第2のトランジスタNおよびMを動作させることは、下記で説明されるように、第1および第2のトランジスタNおよびMの各々の電流が温度に比例することを引き起こす。

30

#### 【0017】

[0023] サブスレッショルド領域内の第1のトランジスタNの電流 $I_{N_1}$ は、

#### 【0018】

#### 【数1】

40

$$I_{N1} = I_0 \cdot \frac{W_N}{L} \cdot e^{\frac{V_{GS\_N}}{V_T}} \quad (1)$$

によっておおよそ求められ得、ここで、 $I_0$ は処理依存型定数(process dependent constant)であり、 $W_N$ は第1のトランジスタNのゲート幅であり、 $L$ は第1のトランジスタNのゲート長であり、 $V_{GS\_N}$ は第1のトランジスタNのゲート・ソース間電圧であり、 $V_T$ は熱電圧(thermal voltage)である。バイアス回路115は、第1のトランジスタNの閾値電圧を下回るバイアス電圧Vbiasを設定することによって、サブスレッショルド領域内で第1のトランジスタNを動作させる。熱電圧 $V_T$ は、

#### 【0019】

【数2】

$$V_T = \frac{kT}{q} \quad (2)$$

によっておおよそ求められ、ここで、kはボルツマン定数であり、Tはケルビンにおける絶対温度であり、qは電子電荷である。熱電圧 $V_T$ は、室温において26mVにほぼ等しく、第1のトランジスタNの閾値電圧と混同されるべきではない。

【0020】

[0024] サブスレッショルド領域における第2のトランジスタMの電流 $I_{M1}$ は、

【0021】

【数3】

10

$$I_{M1} = I_0 \cdot \frac{W_M}{L} \cdot e^{\frac{V_{GS,M}}{V_T}} \quad (3)$$

によっておおよそ求められ得、ここで、 $I_0$ は処理依存型定数であり、 $W_M$ は第2のトランジスタMのゲート幅であり、Lは第2のトランジスタMのゲート長であり、 $V_{GS,M}$ は第2のトランジスタMのゲート・ソース間電圧であり、 $V_T$ は熱電圧である。バイアス回路115は、第2のトランジスタMの閾値電圧を下回るバイアス電圧 $V_{bias}$ を設定することによって、サブスレッショルド領域内で第2のトランジスタMを動作させる。式(3)は、第1および第2のトランジスタNおよびMが同じゲート長Lと処理依存型定数 $I_0$ とを有すると仮定する。第1および第2のトランジスタNおよびMは、それらが互いに近接するチップ上に組み立てられるので、同じ処理依存型定数 $I_0$ を有すると仮定され得る。

20

【0022】

[0025] 式(1)から式(3)を使用すると、第2のトランジスタMのゲート・ソース間電圧 $V_{GS,M}$ と、第1のトランジスタNのゲート・ソース間電圧 $V_{GS,N}$ との差は、下記のように記載される。

【0023】

【数4】

$$V_{GS,M} - V_{GS,N} = \frac{kT}{q} \cdot \ln \left( \frac{W_N}{W_M} \cdot \frac{I_{M1}}{I_{N1}} \right) \quad (4)$$

上述されるように、バイアス回路115は、電流 $I_{N1}$ と $I_{M1}$ との比が、対象とする温度範囲にわたってほぼ一定であるように、第1および第2のトランジスタNおよびMのゲートにおいて電圧バイアス $V_{bias}$ を調整する。そのため、式(4)での電流 $I_{N1}$ と $I_{M1}$ との比は、ほぼ一定である。また、第1および第2のトランジスタNおよびMのゲート幅 $W_N$ と $W_M$ との比、ボルツマン定数kおよび電子電荷qは、全てほぼ一定である。最後に、レジスタ120の抵抗Rは、対象とする温度範囲にわたってほぼ温度が不变である。そのため、温度Tを除く式(4)の項目の全ては、対象とする温度範囲にわたってほぼ一定である。結果として、第1および第2のトランジスタNおよびMのゲート・ソース間電圧の差は温度に比例し、従って、温度を測定するために使用されることができる。ある態様では、第1および第2のトランジスタNおよびMのゲート・ソース間電圧の差は、下記でさらに説明されるように、温度に比例する電流に変換される。

30

【0024】

[0026] 第1および第2のトランジスタNおよびMのゲートに印加された電圧バイアス $V_{bias}$ は、第2のトランジスタMのソースが接地される(grounded)ため、第2のトランジスタMのゲート・ソース間電圧 $V_{GS,M}$ に等しい。そのため、電圧 $V_{bias}$ は

、

【0025】

【数5】

$$V_{bias} = V_{GS,M} \quad (5)$$

のように記載され得る。

電圧バイアス $V_{bias}$ はまた、第1のトランジスタNのゲート・ソース間電圧 $V_{GS,N}$

40

50

<sub>N</sub>と、レジスタ120の両端の電圧降下(voltage drop across the resistor 120)との和に等しい。レジスタ120の両端の電圧降下は、 $I_{N1} \cdot R$ に等しく、ここで、Rはレジスタ120の抵抗である。そのため、電圧バイアスVbiasはまた、

【0026】

【数6】

$$V_{bias} = V_{GS\_N} + I_{N1} \cdot R \quad (6)$$

のようにも記載され得る。

式(5)と(6)の右側を同等と見なす(Equating)と、下記の式

【0027】

【数7】

$$V_{GS\_M} = V_{GS\_N} + I_{N1} \cdot R \quad (7)$$

が得られる。

式(7)は、第1のトランジスタNの電流 $I_{N1}$ を表すために、下記のように書き換えられ得る。

【0028】

【数8】

$$I_{N1} = \frac{V_{GS\_M} - V_{GS\_N}}{R} \quad (8)$$

そのため、第1のトランジスタNの電流 $I_{N1}$ は、レジスタ120の抵抗Rで割られた第1および第2のトランジスタNおよびMのゲート・ソース間電圧の差に等しい。上述されるように、第1および第2のトランジスタNおよびMのゲート・ソース間電圧の差は、温度に比例する。そのため、第1のトランジスタNの電流 $I_{N1}$ は温度にも比例し、従って、温度を測定するために使用されることができる。式(4)の $V_{GS\_M} - V_{GS\_N}$ についての式(expression)を式(8)に代入すると、第1のトランジスタNの電流 $I_{N1}$ についての下記の式が得られる。

【0029】

【数9】

$$I_{N1} = \frac{kT}{qR} \cdot \ln \left( \frac{W_N}{W_M} \cdot \frac{I_{M1}}{I_{N1}} \right) \quad (9)$$

そのため、レジスタ120の両端の(across the resistor 120)第1および第2のトランジスタNおよびMのゲート・ソース間電圧の差を印加することは、温度に比例する電流 $I_{N1}$ を生成する。

【0030】

[0027] 第1および第2のトランジスタNおよびMの電流 $I_{N1}$ と $I_{M1}$ との比がほぼ一定であるため、第2のトランジスタMの $I_{M1}$ の電流は、定数によって乗算された第1のトランジスタNの $I_{N1}$ の電流にほぼ等しい。結果として、第2のトランジスタMの電流 $I_{M1}$ もまた温度Tに比例し、従って、温度を測定するために使用されることがある。

【0031】

[0028] ある実施形態では、バイアス回路115は、第1および第2のトランジスタNおよびMの電流 $I_{N1}$ および $I_{M1}$ がほぼ等しくなるように、電圧バイアスVbiasを調整し得、その場合、電流 $I_{N1}$ と $I_{M1}$ との比は、1にほぼ等しい。結果として、式(9)は、下記に帰着(reduces)する。

【0032】

【数10】

$$I_{N1} = \frac{kT}{qR} \cdot \ln \left( \frac{W_N}{W_M} \right) \quad (10)$$

この実施形態では、第1のトランジスタNのゲート幅の $W_N$ は、第2のトランジスタMのゲート幅 $W_M$ よりも長くなり得る。これは、第1および第2のトランジスタNおよびMがほぼ同じ電流を有することを可能にする一方、レジスタ120の両端の電圧降下を調整す

10

20

30

40

50

る (accommodate) ために、第 1 のトランジスタ N のゲート・ソース間電圧  $V_{G_S_N}$  が第 2 のトランジスタ M のゲート・ソース間電圧  $V_{G_S_M}$  よりも小さくなることを可能にする。

### 【 0 0 3 3 】

[0029] 上述されるように、バイアス回路 115 は、温度に比例する電流  $I_{T_{emp}}$  を生成するように構成される。これを行うために、バイアス回路 115 は、(図 2 で示される) 1 つまたは複数の電流ミラー (current mirrors) を使用して、第 2 のトランジスタ M の電流  $I_{M_1}$  から電流  $I_{T_{emp}}$  を生成し得る。ある実施形態では、電流  $I_{T_{emp}}$  は、第 2 のトランジスタ M の電流  $I_{M_1}$  に比例し得る。第 2 のトランジスタ M の電流  $I_{M_1}$  が温度に比例するため、電流  $I_{T_{emp}}$  もまた温度に比例する。 10

### 【 0 0 3 4 】

[0030] バイアス回路 115 は、電流  $I_{T_{emp}}$  を ADC 130 に提供し、それは、電流  $I_{T_{emp}}$  をデジタル温度示数に変換する。これに関連して、ADC 130 は、リング発振器 135 とデジタルカウンタ 150 とを備える。リング発振器 135 は、遅延チェーンに結合された奇数のインバータ 140 (1) から 140 (3) を備え得、ここで、遅延チェーン内の最後のインバータ 140 (3) の出力は、遅延チェーン内の最初のインバータ 140 (1) の入力に結合される。これは、インバータ 140 (1) から 140 (3) の時間遅延に反比例する発振周波数 (oscillation frequency) でリング発振器 135 に発振を行わせる。リング発振器 135 は、図 1 で示される例において 3 つのインバータを備えているが、リング発振器 135 が任意の奇数のインバータを備え得ることが理解されるだろう。 20

### 【 0 0 3 5 】

[0031] リング発振器 135 のインバータ 140 (1) から 140 (3) は、図 1 で示されるようなバイアス回路 115 からの電流  $I_{T_{emp}}$  によってバイアスをかけられる。より具体的には、バイアス回路 115 は、リング発振器 135 の上部端子 (top terminal) 137 に電流  $I_{T_{emp}}$  をソース (sources) し、リング発振器 135 の下部端子 (bottom terminal) 142 から電流  $I_{T_{emp}}$  をシンク (sink) する。下記でさらに説明されるように、電流  $I_{T_{emp}}$  は、インバータ 140 (1) から 140 (3) の時間遅延を、ひいては、リング発振器 135 の発振周波数を、制御する。 30

### 【 0 0 3 6 】

[0032] ある態様では、各インバータ 140 (1) から 140 (3) の出力は、それぞれのキャパシタに結合され、ここで、キャパシタは、リング発振器 135 内のインバータの出力と、次のインバータの入力との間で結合されたキャパシタ (図示されない)、および / または次のインバータの入力キャパシタ (例えば、ゲートキャパシタ) を含み得る。この態様では、各インバータは、それぞれのキャパシタを充電することによって低出力論理状態 (low output logic state) から高出力論理状態 (high output logic state) に遷移し、それぞれのキャパシタを放電することによって、高出力論理状態から低出力論理状態に遷移する。バイアス回路 115 から、インバータ 140 (1) から 140 (3) に流れる電流  $I_{T_{emp}}$  は、各インバータがどれだけ素早くそれぞれのキャパシタを充電することができるかを制御し、インバータ 140 (1) から 140 (3) から、バイアス回路 115 に流れる電流  $I_{T_{emp}}$  は、各インバータがどれだけ素早くそれぞれのキャパシタを放電することができるかを制御する。そのため、電流  $I_{T_{emp}}$  は、インバータ 140 (1) から 140 (3) がどれだけ素早く論理状態を変更するかを、ひいてはインバータ 140 (1) から 140 (3) の時間遅延を、制御する。電流  $I_{T_{emp}}$  がより高いほど、インバータはより早く論理状態を変更し、従って、インバータの時間遅延がより短くなる。 40

### 【 0 0 3 7 】

[0033] この態様では、インバータ 140 (1) から 140 (3) の時間遅延は、バイアス回路 115 からの電流  $I_{T_{emp}}$  にほぼ反比例し得る。リング発振器 135 の発振周波数がインバータ 140 (1) から 140 (3) の時間遅延に反比例するため、発振周波 50

数は、バイアス回路 115 からの電流  $I_{T_{emph}}$  にほぼ比例する。上述されるように、バイアス回路 115 からの電流  $I_{T_{emph}}$  は、温度にほぼ比例する。結果として、リング発振器 135 の発振周波数は、温度にほぼ比例し、従って、温度を測定するために使用されることができる。

#### 【0038】

[0034] デジタルカウンタ 150 は、リング発振器 135 の出力 145 に結合され、リング発振器 135 の出力 145 における発振サイクルの数 (a number of oscillation cycles) をカウントする。例えば、デジタルカウンタ 150 は、デジタルカウント値を生成するために時間の期間にわたって、リング発振器 135 の出力 145 における立ち上がりエッジ (rising edges) の数および / または立下りエッジ (falling edges) の数をカウントする。デジタルカウント値は発振周波数に比例し、それは、言い換えると、温度に比例する。そのため、デジタルカウント値は温度にも比例し、従って、デジタル温度示数を提供する。

10

#### 【0039】

[0035] そのため、リング発振器 135 は、(温度に比例する) 温度感知回路 110 からの電流  $I_{T_{emph}}$  を周波数に変換し、カウンタ 150 は、その周波数をデジタル温度示数に変換する。デジタル温度示数は、(図 4 で示されるような) 温度管理デバイスに出力され得、それは、温度示数に基づいてチップ上の 1 つまたは複数の回路を管理し得る。

#### 【0040】

[0036] 図 2 は、本開示の実施形態に従った、温度感知回路 110 の例示的な実施を示す。図を容易にするために、図 2 に ADC 130 は示されていない。この実施形態では、バイアス回路 115 は、第 1 の電流ミラー 210、第 2 の電流ミラー 220、および第 3 の電流ミラー 230 を備える。

20

#### 【0041】

[0037] 第 1 の電流ミラー 210 は、第 1 の P 型電界効果トランジスタ PFET 212 と第 2 の PFET 214 とを備える。第 1 および第 2 の PFET 212 および 214 のゲートが連結され、第 1 の PFET 212 のゲートとドレインとが連結される。第 1 の PFET 212 のドレインは、第 1 のトランジスタ N のドレインに結合され、第 2 の PFET 214 のドレインは、第 1 の電流分岐 (first current branch) 240 に結合される。

30

#### 【0042】

[0038] 第 2 の電流ミラー 220 は、第 3 の PFET 222、第 4 の PFET 224、および第 5 の PFET 226 を備える。第 3、第 4、および第 5 の PFET 222、224、および 226 のゲートが連結されており、第 4 の PFET 224 のゲートとドレインとが連結される。第 3 の PFET 222 のドレインは、第 2 の電流分岐 245 に結合され、第 4 の PFET 224 のドレインは、第 2 のトランジスタ M のドレインに結合され、第 5 の PFET 226 のドレインは、(図 1 に示される) リング発振器 135 の上部端子 137 に結合される。

#### 【0043】

[0039] 第 3 の電流ミラー 230 は、第 1 の NFET 232、第 2 の NFET 234、および第 3 の NFET 236 を備える。第 1、第 2、および第 3 の NFET 232、234、および 236 のゲートが連結され、第 2 の NFET 234 のゲートとドレインとが連結される。第 1 の NFET 232 のドレインは、第 1 の電流分岐 240 に結合され、第 2 の NFET 234 のドレインは、第 2 の電流分岐 245 に結合され、第 3 の NFET 236 のドレインは、(図 1 で示される) リング発振器の下部端子 142 に結合される。

40

#### 【0044】

[0040] バイアス回路 115 の動作がこれから本開示の実施形態に従って説明される。考察を容易にするために、バイアス回路 115 の動作は、始めに、第 1 および第 2 のトランジスタ N および M の電流  $I_{N_1}$  および  $I_{M_1}$  がほぼ等しくなるように、バイアス回路 1

50

15が電圧バイアスV<sub>bias</sub>を調整する例を使用して説明される。この例では、第1および第2の電流ミラー210および220におけるPFETは、ほぼ同じゲートの大きさ(gate dimensions)を有し得、第3の電流ミラー230内のNFEトは、ほぼ同じゲートの大きさを有し得る。また、電流ミラー210、220、および230内のトランジスタは、活動領域(active region)内で動作し得る。電流 $I_{N_1}$ と $I_{M_1}$ との比がほぼ一定であるようにバイアス回路115が電圧バイアスV<sub>bias</sub>を調整する、より一般的な場合についてのバイアス回路の動作が後に論じられる。

#### 【0045】

[0041] 動作中、第1のPFET 212は、第1のトランジスタNの電流 $I_{N_1}$ を感じし、第2のPFET 214は、第1の電流分岐240の上部(top portion)で(すなわち、ノード250の上方で(above node 250))電流を複製(ミラー)する。第1の電流分岐240の上部におけるレプリカ電流(replica current)は、「 $I_{N_2}$ 」と表される。第4のPFET 224は、第2のトランジスタMの電流 $I_{M_1}$ を感じし、第3のPFET 222は、第2の電流分岐245で電流を複製(ミラー)する。第2の電流分岐245におけるレプリカ電流は、「 $I_{M_2}$ 」と表される。第2のNFEト234は、第2の電流分岐245における第2のトランジスタMのレプリカ電流 $I_{M_2}$ を感じし、第1のNFEト232は、第1の電流分岐240の下部で(すなわち、ノード250の下方で(below node 250))電流を複製(ミラー)する。第1の電流分岐240の下部におけるレプリカ電流は、「 $I_{M_3}$ 」と表される。

#### 【0046】

[0042] 結果として、第1のトランジスタMの電流 $I_{N_1}$ は、電流 $I_{N_2}$ として第1の電流分岐240の上部で複製され(ミラーアクション)、第2のトランジスタMの電流 $I_{M_1}$ は、電流 $I_{M_3}$ として第1の電流分岐240の下部で複製され(ミラーアクション)。電流 $I_{N_2}$ および $I_{M_3}$ が異なる(すなわち、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ および $I_{M_1}$ が異なる)場合、電流 $I_{N_2}$ および $I_{M_3}$ のうちのいずれかがより大きいかに依存して、その差に等しい電流は、ノード250に流れるか、またはそこから外へ流れる。この電流は、第1および第2のトランジスタNおよびMのゲートに結合されたキャパシタ255を充電または放電し、電圧バイアスV<sub>bias</sub>が上昇または減少することを引き起こす。電圧バイアスV<sub>bias</sub>は、電流 $I_{N_2}$ と $I_{M_3}$ との差(ゆえに、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ と $I_{M_1}$ との差)を減少させる方向に変化する。このフィードバックメカニズムは、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ および $I_{M_1}$ がほぼ等しくなるように、電圧バイアスV<sub>bias</sub>を調整する。この例では、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ および $I_{M_1}$ の両方は、温度に比例し、ここで、各電流は、(トランジスタNおよびMの両方がサブスレッシュルド領域内にあると仮定して)式(10)によっておおよそ求められる。

#### 【0047】

[0043] 上記の例では、バイアス回路115は、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ および $I_{M_1}$ がほぼ等しくなるように、電圧バイアスV<sub>bias</sub>を調整するために、電流ミラー210、220、および230を使用する。バイアス回路115はまた、電流 $I_{N_1}$ と $I_{M_1}$ との比がほぼ一定である、より一般的な場合について、電圧バイアスV<sub>bias</sub>を調整し得る。例えば、電流の比 $I_{M_1} / I_{N_1}$ がmにほぼ等しくなる場合、電流ミラー210、220、および230内のトランジスタのゲート幅は、第1の電流分岐240における電流 $I_{M_3}$ が第2のトランジスタMの電流 $I_{M_1}$ の $1/m$ 倍に等しくなるように、サイジングされ(sized)得る。これは、第2のNFEト234のゲート幅の $1/m$ に等しい第1のNFEト232のゲート幅を有することによってなされ得る。この例では、バイアス回路115は、第1の電流分岐240における電流 $I_{N_2}$ および $I_{M_3}$ がほぼ等しくなるように、電圧バイアスV<sub>bias</sub>を調整する。電流 $I_{N_2}$ が第1のトランジスタNの電流 $I_{N_1}$ にほぼ等しく、電流 $I_{M_3}$ は、第2のトランジスタMの電流 $I_{M_1}$ の $1/m$ 倍にほぼ等しいため、これは、比 $I_{M_1} / I_{N_1}$ がmにほぼ等しくなることを引き起こす。この例では、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$

10

20

30

40

50

および $I_{M_1}$ の両方は、温度に比例し、ここで、第1のトランジスタNの電流 $I_{N_1}$ は、式(9)によって求められ得、第2のトランジスタMの電流 $I_{M_1}$ は、(トランジスタNおよびMの両方がサブスレッショルド領域内にあると仮定して)mによって乗算された式(9)によって求められ得る。

#### 【0048】

[0044] バイアス回路115内のトランジスタの閾値電圧および/またはゲートの大きさは、電圧バイアスVbiasが、対象とする温度範囲にわたって第1および第2のトランジスタNおよびMの閾値電圧を下回ったままであるように選択され得る(ゆえに、第1および第2のトランジスタNおよびMがサブスレッショルド領域内に依然として存在したままである)。例えば、第1および第2のトランジスタNおよびMのゲート幅は電流ミラー-210、220、および230内のトランジスタのゲート幅よりもさらに大きい可能性がある(例えば、少なくとも10倍大きい)。これは、第1および第2のトランジスタNおよびMが、電流ミラー-210、220、および230内のトランジスタが活動領域で動作する電流レベルに関してサブスレッショルド領域内で動作することを可能にする。代替的にまたは追加的に、第1および第2のトランジスタNおよびMは、電流ミラー-210、220、および230内のトランジスタよりもより高い閾値電圧を有し得る。サブスレッショルド領域内で第1および第2のトランジスタNおよびMを動作させることによって、第1および第2のトランジスタNおよびMの電流 $I_{N_1}$ および $I_{M_1}$ は、上述されるように、温度にほぼ比例する。

#### 【0049】

[0045] 第2の電流ミラー220内の第5のP-FET 226は、第2のトランジスタMの電流 $I_{M_1}$ を複製(ミラー)する。結果として生じるレプリカ電流は、リング発振器135の上部端子137に流れる電流 $I_{Temp}$ のために使用される。第3の電流ミラー230内の第3のN-FET 236は、第2の電流分岐245において電流 $I_{M_2}$ を複製(ミラー)し、それは、第2のトランジスタMの電流 $I_{M_1}$ のレプリカである。そのため、第3のN-FET 236によって提供されるレプリカ電流は、第2のトランジスタMの電流 $I_{M_1}$ にほぼ等しい。このレプリカ電流は、リング発振器135の下部端子142からバイアス回路115に流れる電流 $I_{Temp}$ のために使用される。そのため、この実施形態では、バイアス回路115によって提供された電流 $I_{Temp}$ は、第2のトランジスタMの電流 $I_{M_1}$ にほぼ等しい。第2のトランジスタMの電流 $I_{M_1}$ が温度に比例するため、バイアス回路115によって提供された電流 $I_{Temp}$ もまた温度に比例する。これは、ADC 130が、上述されるように、電流 $I_{Temp}$ をデジタル温度示数に変換することを可能にする。

#### 【0050】

[0046] 本開示の様々な実施形態に従った温度センサ100は、従来のバイポーラベースの温度センサに優る、下記の利点のうちの1つまたは複数を提供する。第1に、温度センサ100は、バイポーラベースの温度センサよりもさらに小さくなり得、さらに少ない電力を消費し得る。これは、さらに多い数の温度センサがチップ上に置かれることを可能にする。

#### 【0051】

[0047] さらに、温度センサ100は、低い電源電圧を使用して電力供給され得る。例えば、16nm FinFETプロセスを使用して組み立てられるとき、温度センサ100は、0.79ボルトの電源電圧を使用して電力供給され得る。結果として、温度センサ100は、デジタルロジックのために使用される電力供給レール(power supply rail)によって電力供給され得る。これは、例えば、回路内のホットスポットの温度を測定するために、温度センサ100がデジタルロジックを備える回路(例えば、CPU)内に組み込まれることを可能にする。

#### 【0052】

[0048] 図3は、本開示の実施形態に従った温度センサ100についての25.0(298K)から125.0(398K)の温度範囲にわたる電流310と周波数315

10

20

30

40

50

の例を示すグラフ (plot) である。この例では、電流 310 ( $I_{T_{emp}}$ ) と温度との間の関係は、 $2.118 \text{ nA}/\text{度}$ にほぼ等しい傾斜でほぼ線形である。電流 310 は、絶対温度（すなわち、ケルビンにおける温度）に比例する。また、リング発振器 135 の周波数 315 と温度との間の関係は、 $1.578 \text{ MHz}/\text{度}$ にほぼ等しい傾斜でほぼ線形である。カウンタ 150 は、リング発振器 135 の周波数を、温度に関して線形であるデジタルカウント値に変換する。デジタルカウント値は、温度センサ 100 によって出力されるデジタル温度示数を提供する。

#### 【0053】

[0049] 上述されるように、温度センサ 100 は、温度管理アプリケーションで使用され得る。これに関連して、図 4 は、温度センサ 100、クロックソース 415、温度管理デバイス 410、および回路 420（例えば、CPU）を備えるシステム 405 を示す。

10 図 4 の温度センサ 100 は一定の縮尺で描かれてはおらず、回路 420 よりもさらに小さい可能性があることが理解されるだろう。システム 405 は、同じチップまたはダイに統合され得る。

#### 【0054】

[0050] クロックソース 415 は、回路 420 にクロック信号を提供し、回路 420 は、データサンプリング、データ処理、タイミングデジタルロジック (timing digital logic) などのためにそれを使用し得る。クロックソース 415（例えば、位相ロックループ (PLL)）は、下記でさらに説明されるように、温度管理デバイス 410 の制御下で、クロック信号の周波数を調整するように構成される。

20

#### 【0055】

[0051] 温度センサ 100 は、回路 420 の温度を測定し、温度管理デバイス 410 に、対応するデジタル温度示数を出力する。温度センサ 100 は、回路 420 の近くに位置付けられるか、または回路 420 の正確な温度示数を得るために、回路 420 内に組み込まれる。温度管理デバイス 410 は、温度示数に基づいてクロック信号の周波数を調整することによって、回路 420 の温度を管理する。

#### 【0056】

[0052] 例えば、温度示数が熱閾値よりも上昇するとき、温度管理デバイス 410 は、温度を下げるために、クロック信号の周波数を低減し得る。これは、クロック周波数を低減することが、回路 420 の動的電力消費を低減する、それは、言い換えると、温度を下げる、からである。温度管理デバイス 410 は、熱閾値に近い温度示数を維持するために、クロック周波数を動的に制御し得る。これは、安全限界 (safe limit) 内で回路 420 の温度を維持する一方、回路 420 の性能に対する影響を最小化する。

30

#### 【0057】

[0053] 热閾値は、1つまたは複数の要因に基づいて設定され得る。例えば、热閾値は、チップが熱暴走 (thermal runaway) に入る温度より下に設定され得る。熱暴走は、温度の上昇が漏れ電力 (leakage power) の増加を引き起こすとき、それは、言い換えると、温度のさらなる上昇を引き起こすとき、に発生する。チップが熱暴走に入るとき、チップの温度は急激に上昇する可能性があり、場合によっては、回路 420 を損傷する。チップが熱暴走に入る温度より下に熱閾値を設定することによって、温度管理デバイス 410 は、熱暴走が発生するのを防ぐ。

40

#### 【0058】

[0054] 温度管理デバイス 410 はまた、他の方法を使用して回路 420 の温度下げ得る。例えば、温度管理デバイス 410 は、回路 420 をシャットダウンすることによって温度を下げ得る。この例では、システム 405 はさらに、電力ソース 475、および回路 420 と電力ソース 475 との間の電力デバイス 470（例えば、電力スイッチ）を備え得る。電力デバイス 470 は、回路 420 と同じチップ上に存在し得、電力ソース 475 は、チップの外部に存在し得る。回路 420 がアクティブ状態にあるとき、電力デバイス 470 は、回路 420 に電力供給するために、電力ソース 475 に回路 420 を接続する。温度示数が高くなりすぎる（例えば、熱閾値を超える）と、温度管理デバイス 410

50

は、回路 420 をシャットダウンするために、電力ソース 475 から回路 420 を切斷するように電力デバイス 470 に命令 (command) し得る。管理デバイス 410 は、例えば、温度が回路 420 に対して深刻なダメージを与える危険を冒す極端な場合に、回路 420 をシャットダウンし得る。

#### 【0059】

[0055] 別の例では、温度管理デバイス 410 は、回路 420 への電源電圧を低減することによって温度を下げ得る。電源電圧を低減することは、回路 420 の動的電力および漏れ電力を低減し、それは、言い換えると、温度を下げる。この例では、回路 420 への電源電圧は、クロック周波数が低減されるときに低減され得る。これは、クロック周波数が低減されるときに、回路 420 内のロジックゲートがより遅いスピードで動作し得え、それは、ロジックゲートがより低い電源電圧で動作することを可能にする、からである。この例では、温度管理デバイス 410 が、温度を下げるためにクロック周波数を低減するとき、温度管理デバイス 410 はまた、温度をさらに下げるために、電源電圧を低減し得る。これを行うために、電力ソース 475 は、プログラマブル電源電圧を有する電力管理集積回路 (PMIC : power management integrated circuit) を備え得る。この例では、温度管理デバイス 410 は、PMIC に電圧コマンドを送ることによって、PMIC の電源電圧を設定し得る。そのため、温度管理デバイス 410 は、回路 420 の温度を管理するために、周波数と電圧スケーリングの組み合わせを使用し得る。10

#### 【0060】

[0056] 図の簡略化のために、図 4 には 1 つの温度センサ 100 が示されているが、システム 405 が複数の温度センサを備え得ることが理解されるだろう。例えば、チップは、複数の回路（例えば、1 つまたは複数の CPU、グラフィック処理ユニット (GPU)、モデムなど）を備え得る。この例では、システム 405 は、各回路のための 1 つまたは複数の温度センサを備え得る。温度管理デバイス 410 は、上述される方法のいずれかを使用して、それぞれの 1 つまたは複数の温度センサからの温度示数に基づいて、各回路の温度を管理し得る。20

#### 【0061】

[0057] 温度管理デバイス 410 はまた、温度センサ 100 からより正確な温度測定値を得るために、温度センサ 100 を較正し得る。カウンタ 150 からのデジタルカウント値（デジタル温度示数）と温度との間の関係は、ほぼ線形であり、従って、カウント対温度のグラフにおける線によって概算され (approximated) 得る。しかしながら、グラフ内の線の位置は、処理のバリエーションおよび / または他の要因のために、センサによって異なり得る。これを解消するため、温度センサ 100 についての線の位置を決定するために、較正プロシージャが実行され得る。30

#### 【0062】

[0058] これに関連して、図 5 は、本開示の実施形態に従った、例示的な較正プロシージャを図示するカウント対温度のグラフである。較正プロシージャは、温度センサ 100 が第 1 の既知の温度（「T1」と表される）のために組み立てられたチップを均一に加熱することを含む。例えば、チップは、外部の加熱デバイスを使用して均一に加熱され得、温度は、（例えば、チップの背面に熱的に結合された）高精度外部温度センサ (high-accuracy external temperature sensor) を使用して測定され得る。回路 420 は、この時間中、電源をオフにされ得る。温度管理デバイス 410 は、温度センサ 100 から、対応する第 1 のカウント値（「count1」と表される）を読み取り得る。第 1 の温度 T1 が既知であるため、これは、温度センサ 100 のためのカウント対温度のグラフ内の第 1 のポイント 520 を決定するのに十分な情報を提供する。40

#### 【0063】

[0059] チップは、第 2 の既知の温度（「T2」と表される）へと加熱される。温度管理デバイス 410 は、温度センサ 100 から、対応する第 2 のカウント値（「count2」と表される）を読み取り得る。第 2 の温度 T2 が既知であるため、これは、温度センサ 100 のためのカウント対温度のグラフ内の第 2 のポイント 525 を決定するのに十分50

な情報を提供する。第1および第2のポイント520および525は、他のカウント値についての温度を決定するのに十分な情報を提供する。これは、カウント値と温度との間の直線関係によって、他のカウント値が第1および第2のポイント520と525とを横切る線515上に位置するためである。

#### 【0064】

[0060] そのため、一旦2つのポイント520と525とが決定されると、他のカウント値についての温度は、線形補間(linear interpolation)を使用して決定され得る。この実施形態では、第1および第2のカウント値は、温度管理デバイス410内のメモリに記憶され、それぞれメモリ内で、第1および第2の温度に関連付けられ得る。温度管理デバイス410は、(例えば、線形補間を使用して)温度センサ100からの他のカウント値についての温度を決定するために、温度センサ100について記憶された情報を使用し得る。10

#### 【0065】

[0061] 上記の例では、チップの温度は、外部温度センサを使用して較正中に測定される。別の例では、チップの温度は、正確なオンチップ温度センサを使用して較正中に測定され得る。これに関連して、図6は、温度センサ100、温度管理デバイス410、およびオンチップ較正温度センサ610を備えるシステム605を示す。較正温度センサ610は、バイポーラベースの温度センサまたは他のタイプのオンチップ温度センサを備え得る。この例では、較正温度センサ610は、本開示の実施形態に従った、多くの温度センサを較正するために使用され得る。システム605は、同じチップ上に統合され得る。20

#### 【0066】

[0062] この例では、温度センサ100のための較正プロシージャは、(例えば、外部加熱デバイスを使用して)チップを第1の温度に均一に加熱することを含み得る。較正温度センサ610は、第1の温度を測定し、温度管理デバイス410へ対応する温度示数を出力し得る。温度管理デバイス410は、温度センサ100から対応する第1のカウント値を読み取り得る。回路420は、この時間中、電源をオフにされ得る。温度管理デバイス410は、メモリ内の第1の温度と第1のカウント値とを記憶し得、ここで、第1の温度は、較正温度センサ610からの温度示数によって提供される。

#### 【0067】

[0063] チップは、第2の温度へと加熱される。較正温度センサ610は、第2の温度を測定し、温度管理デバイス410へ対応する温度示数を出力し得る。温度管理デバイス410は、温度センサ100から対応する第2のカウント値を読み取り得る。回路420は、この時間中、電源をオフにされ得る。温度管理デバイス410は、メモリ内の第2の温度と第2のカウント値とを記憶し得、ここで、第2の温度は、較正温度センサ610からの温度示数によって提供される。温度管理デバイス410は、上述されるように、(例えば、線形補間を使用して)温度センサ100からの他のカウント値についての温度を決定するために、温度センサ100について記憶された情報を使用し得る。30

#### 【0068】

[0064] 図7は、本開示の実施形態に従った、温度を感知するための方法700を図示するフローチャートである。方法700は、温度センサ100によって実行され得る。40

#### 【0069】

[0065] ステップ710において、第1および第2のトランジスタがサブスレッショルド領域において動作するように、第1のトランジスタのゲートおよび第2のトランジスタのゲートがバイアスをかけられる。例えば、第1および第2のトランジスタ(例えば、第1および第2のトランジスタNおよびM)のゲートは、第1および第2のトランジスタの閾値電圧を下回る電圧バイアス(例えば、Vbias)においてバイアスをかけられ得る。

#### 【0070】

[0066] ステップ720において、第2のトランジスタのゲート・ソース間電圧と第1のトランジスタのゲート・ソース間電圧との差に比例する電流が生成される。例えば、電50

流（例えば、 $I_{T_{emph}}$ ）は、第2のトランジスタのゲート・ソース間電圧と第1のトランジスタのゲート・ソース間電圧の差（例えば、 $V_{GS\_M} - V_{GS\_N}$ ）を、レジスタ（例えば、レジスタ120）の両端に（across）印加することによって生成され得、ここにおいて、生成された電流は、レジスタを流れる電流に比例する。

#### 【0071】

[0067] ステップ730において、電流は、デジタル温度示数に変換される。例えば、電流は、電流制御発振器（例えば、発振器135）によって周波数に変換され得、その周波数は、カウンタ（例えば、カウンタ150）によってデジタル温度示数（例えば、デジタルカウント値）に変換され得る。

#### 【0072】

[0068] 当業者であれば、本明細書の開示に関連して説明される様々な実例となる論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、または両方の組み合わせとして実施され得ることを理解するだろう。ハードウェアおよびソフトウェアのこの互換性を明確に例示するために、様々な実例となるコンポーネント、ブロック、モジュール、回路、およびステップが、一般にそれらの機能の観点から上記で説明されている。このような機能が、ハードウェアとして実施されるか、またはソフトウェアとして実施されるかは、特定のアプリケーションおよびシステム全体に課せられている設計制約に依存する。当業者であれば、説明された機能を特定のアプリケーションごとに様々な方法で実施し得るが、このような実施の決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

#### 【0073】

[0069] 本明細書の開示に関連して説明された様々な実例となる論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ（DSP）、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、あるいは他のプログラマブル論理デバイス、ディスクリートゲートあるいはトランジスタロジック、ディスクリートハードウェアコンポーネント、あるいは、本明細書で説明された機能を実行するように設計されたそれらの任意の組み合わせ、で実施または実行され得る。汎用プロセッサはマイクロプロセッサであり得るが、代替として、このプロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであり得る。プロセッサはまた、コンピューティングデバイスの組み合わせとして、例えば、DSPとマイクロプロセッサとの組み合わせ、複数のマイクロプロセッサ、DSPコアと連動する1つまたは複数のマイクロプロセッサ、あるいは、任意の他のこのよう構成として、実施され得る。

#### 【0074】

[0070] 本明細書の開示に関連して説明された方法またはアルゴリズムのステップは、ハードウェアで直接的に、プロセッサによって実行されるソフトウェアモジュールで、または両者の組み合わせで、具現化され得る。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROM（登録商標）メモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、あるいは当該技術分野において周知の任意の他の形態の記憶媒体内に存在し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体は、プロセッサに統合され得る。プロセッサおよび記憶媒体はASICに存在し得る。ASICは、ユーザ端末内に存在し得る。代替として、プロセッサおよび記憶媒体は、ユーザ端末内に別個のコンポーネントとして存在し得る。

#### 【0075】

[0071] 1つまたは複数の例示的な設計では、説明された機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組み合わせで実施され得る。ソフトウェアで実施される場合、これら機能は、コンピュータ可読媒体上で、1つまたは複数の命令またはコードとして送信または記憶され得る。コンピュータ可読媒体は、ある場所から

10

20

30

40

50

別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体とコンピュータ記憶媒体との両方を含む。記憶媒体は、汎用コンピュータまたは専用コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく例として、このようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROM、または他の光ディスク記憶装置、磁気ディスク記憶装置、または他の磁気記憶デバイス、または、命令またはデータ構造の形式で所望のプログラムコード手段を搬送または記憶するために使用することができ、かつ、汎用または専用コンピュータ、あるいは、汎用または専用プロセッサによってアクセスされることができる任意の他の媒体を備え得る。また、任意の接続(connection)が送信信号の非一時的な記憶を伴う範囲において、コンピュータ可読媒体と厳密には呼ばれ得る。例えば、ソフトウェアがウェブサイト、サーバ、または他の遠隔ソースから、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線(DSL)、あるいは、赤外線、無線、およびマイクロ波のようなワイヤレス技術を使用して送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、あるいは、赤外線、無線、およびマイクロ波のようなワイヤレス技術は、信号が任意の非一時的な時間の長さの間デバイスマモリまたは記憶媒体上の送信チェーン内に保持される範囲において、媒体の定義に含まれる。本明細書で使用されるような、ディスク(Disk)およびディスク(disc)は、コンパクトディスク(CD)、レザーディスク(登録商標)、光ディスク、デジタル多目的ディスク(DVD)、フロッピー(登録商標)ディスクおよびBlu-ray(登録商標)ディスクを含み、ここでディスク(disk)は通常、磁気的にデータを再生し、一方ディスク.discs)は、レーザーを用いて光学的にデータを再生する。上記の組み合わせもまた、コンピュータ可読媒体の範囲内に含まれるべきである。

## 【0076】

[0072] 本開示の先の説明は、当業者が本開示を実行または使用することを可能にするために提供される。本開示に対する様々な変更は、当業者には容易に明らかであり、本明細書で定義された包括的な原理は、本開示の精神または範囲から逸脱することなく他のバリエーションに適用され得る。従って、本開示は、本明細書で説明される例に限定されることが意図されるものではなく、本明細書に開示される原理および新規の特徴と一致する最も広い範囲が付与されるべきものである。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

30

## [C1]

温度センサであって、

ゲートを有する第1のトランジスタと、

前記第1のトランジスタの前記ゲートに結合されたゲートを有する第2のトランジスタと、

前記第1および第2のトランジスタがサブスレッショルド領域において動作するように、前記第1および第2のトランジスタの前記ゲートにバイアスをかけること、および前記第1のトランジスタのゲート・ソース間電圧と前記第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することを行うように構成されたバイアス回路と、

前記電流をデジタル温度示数に変換するように構成されたアナログ・デジタル変換器(ADC)と

を備える、温度センサ。

## [C2]

前記ADCは、

前記電流を周波数に変換するように構成された発振器と、

前記周波数をデジタルカウント値に変換するように構成されたカウンタと、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、C1に記載の温度センサ。

## [C3]

前記第2のトランジスタのソースに結合されたレジスタをさらに備え、ここにおいて、

10

20

40

50

前記第1のトランジスタの前記ゲート・ソース間電圧と前記第2のトランジスタの前記ゲート・ソース間電圧との前記差は、前記レジスタの両端に印加され、前記生成された電流は、前記レジスタ中を流れる電流に比例する、C 1に記載の温度センサ。

[ C 4 ]

前記生成された電流は、前記レジスタ中を流れる前記電流にほぼ等しい、C 3に記載の温度センサ。

[ C 5 ]

前記レジスタは、前記第2のトランジスタの前記ソースと接地との間で結合される、C 3に記載の温度センサ。

[ C 6 ]

前記第1のトランジスタは、第1の電界効果トランジスタ(FET)を備え、前記第2のトランジスタは、第2のFETを備える、C 1に記載の温度センサ。

10

[ C 7 ]

前記バイアス回路は、前記第1のトランジスタの電流と前記第2のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第1および第2のトランジスタの前記ゲートにバイアスをかけるように構成される、C 1に記載の温度センサ。

[ C 8 ]

前記比は、1にほぼ等しい、C 7に記載の温度センサ。

[ C 9 ]

温度を感知するための方法であって、

20

第1および第2のトランジスタがサブスレッショルド領域において動作するように、前記第1のトランジスタのゲートおよび第2のトランジスタのゲートにバイアスをかけること、

前記第1のトランジスタのゲート・ソース間電圧と前記第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することと、

前記電流をデジタル温度示数に変換することと

を備える、方法。

[ C 10 ]

前記電流を前記デジタル温度示数に変換することは、

前記電流を周波数に変換することと、

30

前記周波数をデジタルカウント値に変換することと、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、C 9に記載の方法。

[ C 11 ]

前記電流を生成することは、前記第1のトランジスタの前記ゲート・ソース間電圧と前記第2のトランジスタの前記ゲート・ソース間電圧との前記差を、レジスタの両端に印加することを備え、前記生成された電流は、前記レジスタ中を流れる電流に比例する、C 9に記載の方法。

[ C 12 ]

前記生成された電流は、前記レジスタ中を流れる前記電流にほぼ等しい、C 11に記載の方法。

40

[ C 13 ]

前記第1のトランジスタは、第1の電界効果トランジスタ(FET)を備え、前記第2のトランジスタは、第2のFETを備える、C 9に記載の方法。

[ C 14 ]

前記第1のトランジスタの電流と前記第2のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第1および第2のトランジスタの前記ゲートにバイアスをかけることをさらに備える、C 9に記載の方法。

[ C 15 ]

前記比は、1にほぼ等しい、C 14に記載の方法。

50

## [ C 1 6 ]

温度を感じるための装置であって、

第1および第2のトランジスタがサブスレッショルド領域において動作するように、前記第1のトランジスタのゲートおよび第2のトランジスタのゲートにバイアスをかけるための手段と、

前記第1のトランジスタのゲート・ソース間電圧と前記第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成するための手段と、

前記電流をデジタル温度示数に変換するための手段と

を備える、装置。

## [ C 1 7 ]

10

前記電流を前記デジタル温度示数に変換するための前記手段は、

前記電流を周波数に変換するための手段と、

前記周波数をデジタルカウント値に変換するための手段と、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、C 1 6 に記載の装置。

## [ C 1 8 ]

前記電流を生成するための前記手段は、前記第1のトランジスタの前記ゲート・ソース間電圧と前記第2のトランジスタの前記ゲート・ソース間電圧との前記差を、レジスタの両端に印加するための手段を備え、前記生成された電流は、前記レジスタ中を流れる電流に比例する、C 1 6 に記載の装置。

20

## [ C 1 9 ]

前記生成された電流は、前記レジスタ中を流れる前記電流にほぼ等しい、C 1 8 に記載の装置。

## [ C 2 0 ]

前記第1のトランジスタは、第1の電界効果トランジスタ(FET)を備え、前記第2のトランジスタは、第2のFETを備える、C 1 6 に記載の装置。

## [ C 2 1 ]

前記第1のトランジスタの電流と前記第2のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第1および第2のトランジスタの前記ゲートにバイアスをかけるための手段をさらに備える、C 1 6 に記載の装置。

30

## [ C 2 2 ]

前記比は、1にほぼ等しい、C 2 1 に記載の装置。

## [ C 2 3 ]

システムであって、

温度センサと、ここにおいて、前記温度センサは、

ゲートを有する第1のトランジスタと、

前記第1のトランジスタの前記ゲートに結合されたゲートを有する第2のトランジスタと、

前記第1および第2のトランジスタがサブスレッショルド領域において動作するよう

に、前記第1および第2のトランジスタの前記ゲートにバイアスをかけること、および前記第1のトランジスタのゲート・ソース間電圧と前記第2のトランジスタのゲート・ソース間電圧との差に比例する電流を生成することを行うように構成されたバイアス回路と、

前記電流をデジタル温度示数に変換するように構成されたアナログ・デジタル変換器(ADC)と、

を備える、

前記温度センサに結合された温度管理デバイスと、ここにおいて、前記温度管理デバイスは、前記デジタル温度示数に基づいて回路の温度を決定すること、および前記温度に基づいて前記回路の1つまたは複数のパラメータを調整することを行うように構成される、

を備える、システム。

## [ C 2 4 ]

40

50

前記 1 つまたは複数のパラメータは、前記回路の周波数および前記回路の電源電圧のうちの少なくとも 1 つを備える、C 2 3 に記載のシステム。

[ C 2 5 ]

前記温度センサは、前記第 2 のトランジスタのソースに結合されたレジスタをさらに備え、ここにおいて、前記第 1 のトランジスタの前記ゲート・ソース間電圧と前記第 2 のトランジスタの前記ゲート・ソース間電圧との前記差は、前記レジスタの両端に印加され、前記生成された電流は、前記レジスタ中を流れる電流に比例する、C 2 3 に記載のシステム。

[ C 2 6 ]

前記バイアス回路は、前記第 1 のトランジスタの電流と前記第 2 のトランジスタの電流との比が温度範囲にわたってほぼ一定であるように、前記第 1 および第 2 のトランジスタの前記ゲートにバイアスをかけるように構成される、C 2 3 に記載のシステム。

10

[ C 2 7 ]

前記 A D C は、

前記電流を周波数に変換するように構成された発振器と、

前記周波数をデジタルカウント値に変換するように構成されたカウンタと、ここにおいて、前記デジタル温度示数は、前記デジタルカウント値を備える、

を備える、C 2 3 に記載のシステム。

[ C 2 8 ]

前記温度管理デバイスは、前記温度センサからの第 1 および第 2 のカウント値と、第 2 の温度センサからの第 1 および第 2 の温度示数とを受信することと、前記第 1 のカウント値を前記第 1 の温度示数に関連付け、前記第 2 のカウント値を前記第 2 の温度示数に関連付けることによって、前記温度センサのための較正情報を生成することと、および前記較正情報をメモリに記憶することとを行うように構成される、C 2 7 に記載のシステム。

20

[ C 2 9 ]

前記温度管理デバイスは、前記較正情報を使用して前記デジタルカウント値に基づいて前記温度を決定するように構成される、C 2 8 に記載のシステム。

[ C 3 0 ]

前記第 2 の温度センサは、バイポーラベースの温度センサを備える、C 2 8 に記載のシステム。

30

【図1】

【図2】

【 义 3 】

【図4】

FIG. 4

【図5】

図5

【図6】

図6

【図7】

図7

FIG. 7

---

フロントページの続き

(72)発明者 ジャン、ジュンモウ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ジャン、チュアン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 チェン、ナン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 菅藤 政明

(56)参考文献 特開2007-121244(JP,A)

特開昭54-48149(JP,A)

米国特許出願公開第2011/0001546(US,A1)

(58)調査した分野(Int.Cl., DB名)

G01K 7/01

H01L 27/04 - 27/118