(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0030033

(43) 공개일자 2012년03월27일

(51) 국제특허분류(Int. Cl.)

*H01L 21/336* (2006.01) *H01L 29/78* (2006.01)

(21) 출원번호 10-2011-7017916

(22) 출원일자(국제) 2009년12월29일

심사청구일자 없음

(85) 번역문제출일자 2011년07월29일

(86) 국제출원번호 PCT/EP2009/009306

(87) 국제공개번호 WO 2010/076017

국제공개일자 2010년07월08일

(30) 우선권주장

10 2008 063 427.1 2008년12월31일 독일(DE)

12/640,765 2009년12월17일 미국(US)

(71) 출원인

어드밴스드 마이크로 디바이시즈, 인코포레이티드

미국 캘리포니아 94088-3453 서니베일 원 에이엠

디 플레이스 메일 스톱68

에이엠디 팹 36 리미티드 라이어빌리티 컴퍼니 &

코. 카게

독일 01109 드레스덴 월쉬도르프 란드스트라쎄

101

(72) 발명자

크론홀츠 스텔판

독일 01129 드레스덴 바인버그스트라세 18

파파기울기오우 바실리오스

독일 01097 드레스덴 하우프트스트라세 11

베어넌크 군다

독일 01097 드레스덴 피히텐스트라세 1

(74) 대리인

박장원

전체 청구항 수 : 총 25 항

(54) 발명의 명칭 점진적으로 만들어진 형태의 구성을 가지는 매립 스트레인 유도 물질을 갖는 트랜지스터

### (57) 요 약

트랜지스터에서, 점진적으로 만들어진 형태의 캐비티들을 제공한 다음 스트레인-유도 반도체 합금으로 그 캐비티들을 채움으로써 실리콘/게르마늄, 실리콘/탄소 등과 같은 스트레인-유도 반도체 합금이 채널 영역에 아주 가까이 위치될 수 있다. 이런 목적으로, 해당 캐비티들의 서로 다른 깊이들에서 서로 다른 측면 읍셋들을 정의하기 위하여 서로 다른 예칭 거동을 갖는 둘 이상의 "일회용(disposable)" 스페이서 소자들이 이용될 수 있다. 결과적으로, 정밀한 반도체 디바이스들에 대하여도 향상된 균일성과 그에 따른 감소된 트랜지스터 변동성이 달성될 수 있다.

대 표 도 - 도2a

## 특허청구의 범위

### 청구항 1

결정질(crystalline) 반도체 영역에 제1 복수의 리세스(recess)들을 형성하는 단계와, 상기 제1 복수의 리세스들은 게이트 전극 구조로부터 상기 게이트 전극 구조의 측벽들 상에 형성되는 제1 측벽 스페이서(sidewall spacer) 만큼 옵셋(offset)을 가지고, 상기 제1 복수의 리세스들은 제1 깊이까지 확장되며;

상기 결정질 반도체 영역에 제2 복수의 리세스들을 형성하는 단계와, 상기 제2 복수의 리세스들은 상기 게이트 전극 구조로부터 상기 제1 측벽 스페이서 상에 형성되는 제2 측벽 스페이서 만큼 옵셋을 가지고, 상기 제2 복수의 리세스들은 상기 제1 깊이보다 더 깊은 제2 깊이까지 확장되며; 그리고

선택적 에피택셜 성장 공정(selective epitaxial growth process)을 수행함으로써 상기 제1 및 제2 리세스들에 스트레인 유도 반도체 합금(strain inducing semiconductor alloy)을 형성하는 단계를 포함하는 방법.

### 청구항 2

제1항에 있어서,

상기 제1 복수의 리세스들은 상기 제2 복수의 리세스들을 형성하기 전에 형성되는 방법.

### 청구항 3

제1항에 있어서,

상기 제1 복수의 리세스들을 형성하는 단계는 상기 게이트 전극 구조 및 제2 결정질 반도체 영역 위에 형성되는 제2 게이트 전극 구조 위에 제1 스페이서층을 형성하는 것과, 상기 제2 게이트 전극 구조 위에 형성되는 제1 스페이서층과 상기 제2 반도체 영역을 덮는 제1 마스크를 형성하는 것과, 상기 제1 스페이서층으로부터 상기 제1 측벽 스페이서를 형성하는 것과, 그리고 상기 제1 측벽 스페이서와 상기 제1 마스크가 있는 상태에서 상기 결정질 반도체 영역으로부터 물질을 제거하는 것을 포함하는 방법.

방법.

### 청구항 4

제3항에 있어서,

상기 제2 복수의 리세스들을 형성하는 단계는 상기 제1 마스크를 제거하는 것과, 제2 스페이서층을 증착하는 것과, 그리고 상기 제2 스페이서층으로부터 상기 제2 측벽 스페이서를 형성하는 것을 포함하는 방법.

### 청구항 5

제4항에 있어서,

상기 제2 측벽 스페이서를 형성하기 전에 상기 제2 게이트 전극 구조 및 상기 제2 결정질 반도체 영역 위에 제2 마스크를 형성하는 것을 더 포함하는 방법.

방법.

### 청구항 6

제4항에 있어서,

상기 결정질 반도체 영역에 상기 제2 복수의 리세스들을 형성할 때, 상기 제2 게이트 전극 구조에서 상기 제1 스페이서층 상에 측벽 스페이서를 형성하는 것과, 상기 제1 스페이서층을 에칭 마스크로서 이용하는 것을 더 포함하는 방법.

함하는

방법.

### 청구항 7

제1항에 있어서,

상기 제1 및 제2 복수의 리세스들을 형성하는 단계는 상기 제2 복수의 리세스들의 제1 일부분을 형성하는 것과, 상기 제2 측벽 스페이서의 적어도 일부분을 제거하는 것과, 그리고 상기 제2 복수의 리세스들과 상기 제1 복수의 리세스들의 제2 일부분을 공통으로 형성하는 것을 포함하는

방법.

### 청구항 8

제1항에 있어서,

상기 스트레인 유도 반도체 합금을 형성하는 단계는 상기 제1 측벽 스페이서가 있는 상태에서 상기 스트레인 유도 반도체 합금의 제1 일부분으로 상기 제1 리세스들을 채우기 위하여 그리고 상기 제1 및 제2 측벽 스페이서들이 있는 상태에서 상기 스트레인 유도 반도체 합금의 제2 일부분으로 상기 제2 복수의 리세스들을 채우기 위하여 제1 에피택셜 성장 공정을 수행하는 것을 포함하는

방법.

### 청구항 9

제8항에 있어서,

상기 스트레인 유도 반도체 합금의 상기 제1 및 제2 일부분들은 적어도 인-시튜 도핑의 정도에 있어서 서로 다른

방법.

### 청구항 10

제1항에 있어서,

상기 스트레인 유도 반도체 합금은 상기 게이트 전극 구조 아래의 상기 결정질 반도체 영역에 위치한 채널 영역에 압축 스트레인을 유도하도록 형성되는

방법.

### 청구항 11

제10항에 있어서,

상기 반도체 합금은 게르마늄 및 주석 중 적어도 하나를 포함하는

방법.

### 청구항 12

제1항에 있어서,

상기 스트레인 유도 반도체 합금은 상기 게이트 전극 구조 아래의 상기 결정질 반도체 영역에 위치한 채널 영역에서 인장 스트레인을 유도하도록 형성되는

방법.

### 청구항 13

제1항에 있어서,

상기 제1 측벽 스페이서는 실리콘 다이옥사이드를 포함하고, 상기 제2 측벽 스페이서는 실리콘 나이트라이드를

포함하는

방법.

#### 청구항 14

그 상에 제1 게이트 전극 구조를 형성한 제1 반도체 영역 위에 그리고 그 상에 제2 게이트 전극 구조를 형성한 제2 반도체 영역 위에 제1 스페이서층을 형성하는 단계와;

상기 제1 게이트 전극 구조의 측벽들 상에 상기 제1 스페이서층으로부터 제1 측벽 스페이서를 선택적으로 형성하는 단계와;

상기 제1 측벽 스페이서를 기반으로 상기 제1 반도체 영역에 복수의 캐비티들을 형성하도록 제1 에칭 공정을 수행하는 단계와;

상기 제1 측벽 스페이서 상에 제2 측벽 스페이서를 형성하는 단계와;

상기 제2 측벽 스페이서를 기반으로 상기 복수의 캐비티들 각각의 일부분의 깊이를 증가시키도록 제2 에칭 공정을 수행하는 단계와; 그리고

상기 캐비티들에 스트레인 유도 반도체 합금을 형성하는 단계

를 포함하는 방법.

#### 청구항 15

제14항에 있어서,

상기 제2 측벽 스페이서를 형성하는 단계는 상기 제1 및 제2 반도체 영역들과 상기 제1 및 제2 게이트 전극 구조들 위에 제2 스페이서층을 증착하는 것과, 상기 제2 반도체 영역 위의 상기 스페이서층을 마스크하면서 상기 제2 스페이서층으로부터 상기 제2 측벽 스페이서를 선택적으로 형성하는 것을 포함하는

방법.

#### 청구항 16

제14항에 있어서,

상기 제2 측벽 스페이서를 형성하는 단계는 상기 제1 및 제2 반도체 영역들과 상기 제1 및 제2 게이트 전극 구조들 위에 제2 스페이서층을 증착하는 것과, 상기 제1 측벽 스페이서 상에 그리고 상기 제2 반도체 영역 위에 형성되는 상기 제1 스페이서층 상에 상기 제2 측벽 스페이서를 형성하는 것을 포함하는

방법.

#### 청구항 17

제14항에 있어서,

상기 스트레인 유도 반도체 합금을 형성하는 단계는 상기 제1 및 제2 측벽 스페이서들을 기반으로 제1 선택적 에피택셜 성장 공정을 수행하는 것과, 상기 제2 측벽 스페이서를 제거하는 것과, 그리고 상기 제1 측벽 스페이서를 기반으로 제2 선택적 에피택셜 성장 공정을 수행하는 것을 포함하는

방법.

#### 청구항 18

제17항에 있어서,

상기 제1 및 제2 에피택셜 성장 공정들은 적어도 하나의 공정 파라미터 값에 있어서 서로 다른

방법.

#### 청구항 19

제18항에 있어서,

상기 적어도 하나의 서로 다른 공정 파라미터 값은 상기 스트레인 유도 반도체 물질의 인-시튜 도핑에서 결정되는

방법.

#### 청구항 20

제14항에 있어서,

상기 제1 스페이서층은 실리콘 다이옥사이드를 포함하고, 상기 제2 스페이서층은 실리콘 나이트라이드를 포함하는

방법.

#### 청구항 21

기판 위에 형성되는 트랜지스터를 포함하는 반도체 디바이스로서,

상기 트랜지스터는

결정질 반도체 영역 위에 형성되고 게이트 전극 물질을 포함하는 게이트 전극 구조와;

상기 결정질 반도체 영역에 형성되고 상기 게이트 전극 물질로부터 제1 측면 옵셋과 제1 깊이를 가지는 제1 스트레인 유도 반도체 합금과;

상기 결정질 반도체 영역에 형성되고 상기 게이트 전극 물질로부터 제2 측면 옵셋과 제2 깊이를 가지는 제2 스트레인 유도 반도체 합금을 포함하며,

상기 제1 및 제2 깊이들은 서로 다르고, 상기 제1 및 제2 측면 옵셋들은 서로 다른

반도체 디바이스.

#### 청구항 22

제21항에 있어서,

상기 제1 및 제2 스트레인 유도 반도체 물질들은 상기 트랜지스터의 채널 영역에서 동일한 타입의 스트레인을 유도하고, 상기 제1 및 제2 스트레인 유도 물질들은 도편트 농도와 물질 조성 중 적어도 하나에 있어서 서로 다른

반도체 디바이스.

#### 청구항 23

제22항에 있어서,

상기 스트레인 유도 반도체 합금은 상기 채널 영역에서 압축 스트레인을 유도하는

반도체 디바이스.

#### 청구항 24

제22항에 있어서,

스트레인 유도 반도체 합금은 상기 채널 영역에서 인장 스트레인을 유도하는

반도체 디바이스.

#### 청구항 25

제21항에 있어서,

상기 게이트 전극 물질의 게이트 길이는 대략 50 나노미터 이하인

반도체 디바이스.

## 명세서

### 기술분야

[0001] 개발적으로, 본 개시는 집적 회로들의 제조에 관한 것이며, 더욱 상세하게는 트랜지스터들의 채널 영역들에서 전하 캐리어 이동도를 향상시키기 위하여 매립 반도체 물질들을 이용함으로써 스트레인드 채널 영역들을 가지는 트랜지스터들에 관한 것이다.

### 배경기술

[0002] 복합 집적 회로들의 제조는 많은 수의 트랜지스터 소자들의 제공을 필요로 하며, 트랜지스터 소자들은 복합 회로들에 대해 지배적인 회로 소자에 해당한다. 예를 들면, 현재 이용가능한 복합 집적 회로들에서는 수백만 개의 트랜지스터들이 제공될 수 있다. 일반적으로, 복수의 공정 기술들이 현재 실시되며, 마이크로프로세서들, 저장 칩들 등과 같은 복합 회로에 대해 CMOS 기술은 동작 속도 및/또는 전력 소모 및/또는 비용 효율성 측면에서 우월한 특성으로 인해 현재 가장 유망한 접근법이다. CPU, 저장 칩들 등과 같은 고도의 복합 회로 어셈블리들을 설계하는데 있어서 인버터들 및 다른 로직 게이트들과 같은 회로 소자들을 형성하기 위해 상보적인 트랜지스터들, 즉 p-채널 트랜지스터들과 n-채널 트랜지스터들이 CMOS 회로들에 이용된다. CMOS 기술을 이용한 복합 집적 회로들의 제조 과정에서 트랜지스터들, 즉 n-채널 트랜지스터들 및/또는 p-채널 트랜지스터들이 결정질 반도체 층(crystalline semiconductor layer)을 포함하는 기판(substrate) 위에 형성된다. n-채널 트랜지스터를 고려하든 p-채널 트랜지스터를 고려하든 상관없이, MOS 트랜지스터 또는 일반적으로 전계 효과 트랜지스터는 고농도 도핑된(highly doped) 드레인(drain) 및 소오스(source) 영역들과, 드레인 영역 및 소오스 영역의 사이에 위치하는 반대로(inversely) 또는 저농도 도핑된(weakly doped) 채널 영역과의 계면에 의해 형성되는 소위 pn-접합(pn-junction)을 포함한다. 채널 영역의 전도도(conductivity), 즉 전도성 채널의 구동 전류 용량(drive current capability)은 채널 영역 근처에 형성되며 얇은 절연층에 의해 채널 영역과 분리되는 게이트 전극에 의해서 제어된다. 게이트 전극에 적절한 제어 전압을 인가함으로 인해 전도성 채널이 형성되었을 때의 채널 영역의 전도도는 도편트 농도(dopant concentration), 전하 캐리어 이동도(charge carriers mobility) 및 채널 길이(channel length)라고도 지칭되는 소오스 및 드레인 영역 사이의 거리(트랜지스터의 폭 방향(width direction)으로 채널 영역의 소정의 확장에 대하여)에 따라 결정된다. 따라서, 채널 길이의 감소(이와 관련한 채널 저항률(channel resistivity)의 감소)는 집적 회로의 동작 속도를 증가시킬 수 있는 지배적인 설계 기준이다.

[0003] 하지만, 트랜지스터 치수들의 지속적인 감소는 MOS 트랜지스터들의 채널 길이를 꾸준히 감소시킴으로써 얻어지는 장점들을 부당하게 상쇄시키지 않기 위하여 해결되어야 할 여러 가지 관련된 문제점들을 수반한다. 예를 들면, 원하는 채널 제어 가능성(controllability)과 함께 낮은 시트(sheet) 및 컨택(contact) 저항률을 제공하기 위하여, 수직 방향 뿐만 아니라 측면 방향으로, 고도로 정밀한 도편트 프로파일(dopant profile)이 드레인 및 소오스 영역들에서 요구된다. 게다가, 게이트 유전체 물질은 또한 요구되는 채널 제어 가능성성을 유지하기 위해 감소된 채널 길이에 맞게 조정될 수 있다. 하지만, 높은 채널 제어 가능성을 유지하기 위한 일부 메카니즘들은 트랜지스터 채널 영역의 전하 캐리어 이동도에 부정적인 영향을 가질 수 있어서, 채널 길이의 감소에 의해 얻어지는 장점들을 부분적으로 상쇄시킨다.

[0004] 임계 치수들, 즉 트랜지스터의 게이트 길이의 지속적인 크기 감소는 고도로 복합적인 공정 기법들의 조정과 아마도 그 새로운 개발을 필요하게 하고, 또한 이동도 저하로 인한 덜 현저한 성능 이득에 기여할 수 있기 때문에, 소정의 채널 길이에 대한 채널 영역의 전하 캐리어 이동도를 증가시킴으로써 트랜지스터 소자들의 채널 전도도를 향상시켜, 극도로 스케일링된 임계 치수들이 요구되는 기술 표준의 진보에 필적하는 성능 개선을 가능하게 하는 동시에, 디바이스 스케일링과 관련된 공정 조정들의 많은 것들을 방지하거나 적어도 늦출 수 있다.

[0005] 전하 캐리어 이동도를 증가시키기 위한 하나의 효율적인 메카니즘은 예컨대 채널 영역에 상응하는 스트레인을 만들도록 채널 영역의 인근에 인장(tensile) 또는 압축 스트레스(compressive stress)를 생성함으로써 채널 영역에서 격자 구조를 수정하는 것이며, 이는 각각 전자들 및 정공들(holes)의 이동도를 수정하는 결과가 된다. 예를 들면, 활성 실리콘 물질의 표준 결정학적 구성(crystallographic configuration), 즉 <110> 방향으로 정렬된 채널 길이를 갖는 (100) 표면 방위에 대하여 채널 영역에 인장 스트레인을 생성하는 것은 전자의 이동도를 증가시키고, 이는 결국 직접적으로 전도도의 상응하는 증가로 이어진다. 반면에, 채널 영역의 압축 스트레인은

정공들의 이동도를 증가시킬 수 있어서, p-타입 트랜지스터들의 성능을 향상시키기 위한 잠재력을 제공할 수 있다. 스트레인드 실리콘은 "새로운" 타입의 반도체 물질로서 고려될 수 있으며, 이는 값비싼 반도체 물질들을 필요로 하지 않고 빠르고 강력한 반도체 디바이스들의 제조를 가능하게 할 수 있는 반면, 많은 확립된 제조 기법들이 여전히 사용될 수 있기 때문에, 스트레스 또는 스트레인 공학을 접적 회로 제조에 도입하는 것은 극히 유망한 접근법이다.

[0006] 결과적으로, 예컨대 상응하는 스트레인을 유발할 수 있는 압축 스트레스를 유도하기 위하여 채널 영역 옆에 실리콘/게르마늄(silicon/germanium) 물질을 도입하는 것이 제안된바 있다. Si/Ge 물질을 형성할 때, NMOS 트랜지스터들이 마스크(mask)된 채로, PMOS 트랜지스터들의 드레인 및 소오스 영역들이 캐비티(cavity)들을 형성하기 위해 리세스(recess)되고, 후속으로 실리콘/게르마늄 물질이 에피택셜 성장(epitaxial growth)에 의해 PMOS 트랜지스터의 캐비티들에 선택적으로 형성된다.

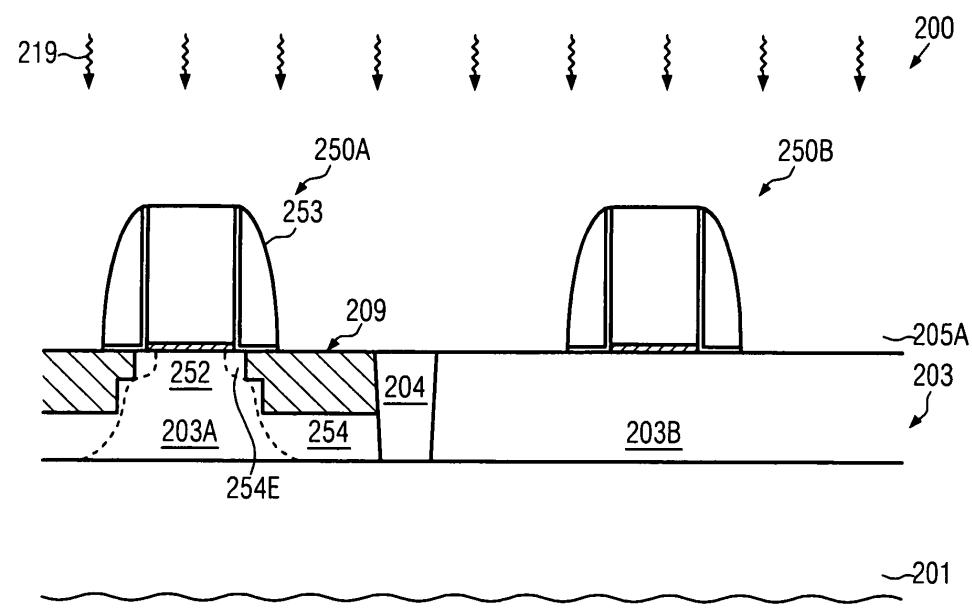

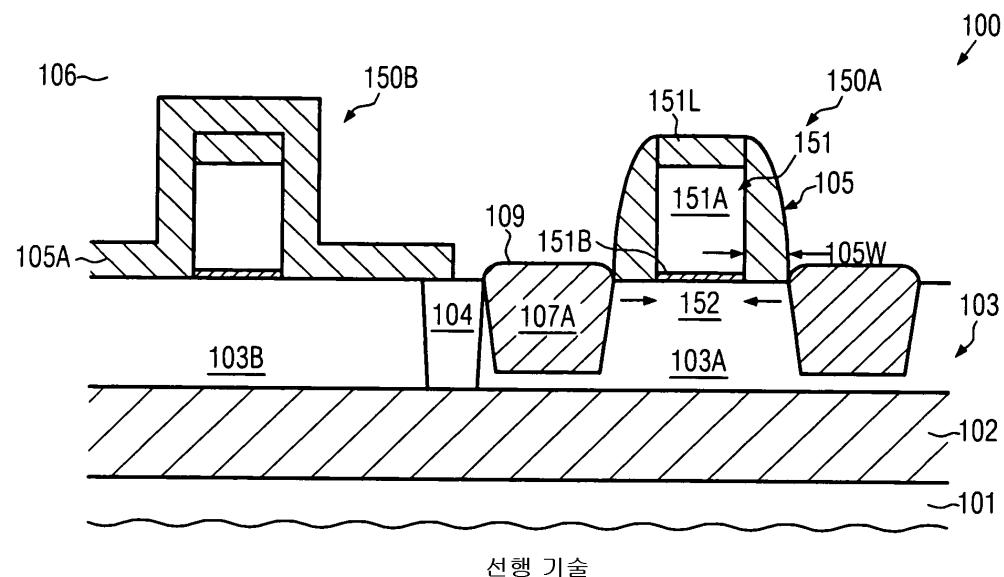

[0007] p-채널 트랜지스터들의 성능 이득과 그에 따른 전체 CMOS 디바이스의 성능 이득의 관점에서 상기 기법은 상당한 장점을 가지지만, 많은 수의 트랜지스터 소자들을 포함하는 첨단 반도체 디바이스들에서 디바이스 성능의 변동성이 증가되는 것을 관찰할 수 있으며, 이는 도 1a 내지 1e를 참조하여 더욱 상세히 서술되는 바와 같이 특히 최종적으로 달성된 스트레인을 증가시키는 측면에서 채널 영역으로부터의 실리콘/게르마늄 물질의 옵셋이 감소되어야 할 때, p-채널 트랜지스터들의 드레인 및 소오스 영역들에 스트레인드 실리콘-게르마늄 합금을 병합시키기 위한 전술된 기법과 관련될 수 있다.

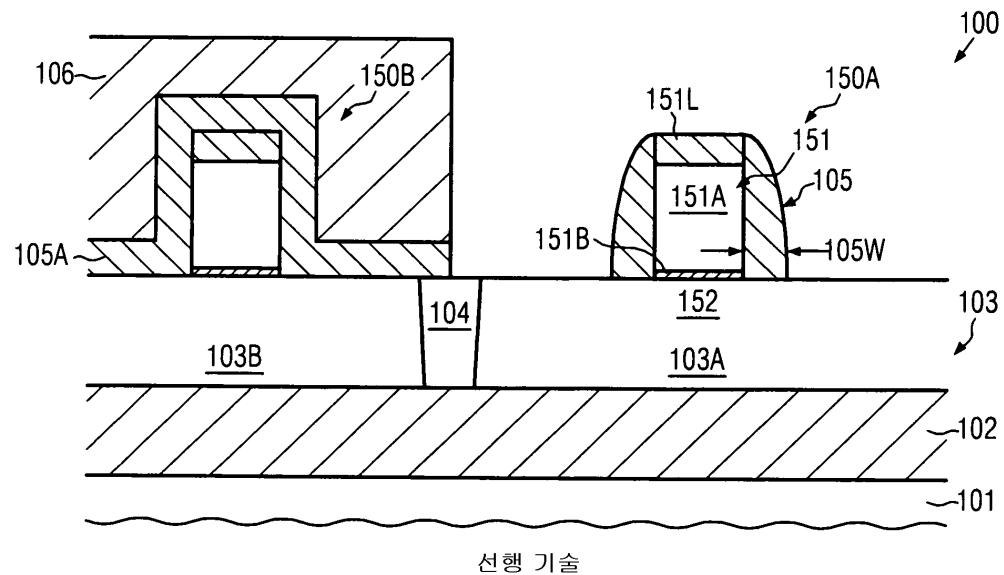

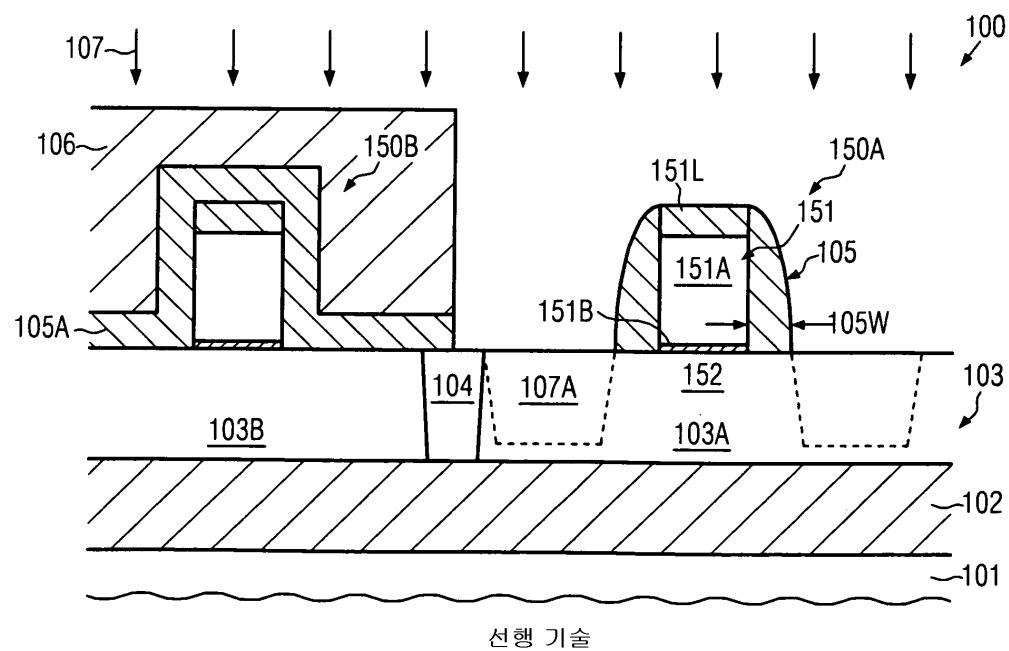

[0008] 도 1a는 p-채널 트랜지스터(150a)와 n-채널 트랜지스터(150b)를 포함하는 종래의 반도체 디바이스(100)의 단면도를 개략적으로 예시한 것이며, 위에서 설명된 바와 같이 트랜지스터(150a)의 성능이 스트레인드 실리콘/게르마늄 합금을 기반으로 향상될 것이다. 반도체 디바이스(100)는 실리콘 기판과 같은 기판(101)을 포함하며, 그 위에 매립 절연층(buried insulating layer)(102)이 형성될 수 있다. 게다가, 결정질 실리콘층(103)이 매립 절연층 위에 형성되어서, SOI(silicon on insulator) 구성을 형성할 수 있다. 예를 들어, 벌크 구성, 즉 실리콘층(103)의 두께가 층(103) 안으로 트랜지스터들(150a, 150b)의 수직 확장보다 상당히 더 클 수 있는 구성에 비해 트랜지스터들(150a, 150b)의 기생 결합 커페시턴스(parasitic junction capacitance)가 감소될 수 있기 때문에, SOI 구성은 전체 트랜지스터 성능의 관점에서 유리할 수 있다. 트랜지스터들(150a, 150b)은 일반적으로 103a, 103b로서 표시되는 각각의 "활성(active)" 영역들 안과 위에 형성될 수 있으며, 활성 영역들은 얇은 트렌치 격리(shallow trench isolation)와 같은 격리 구조(104)에 의해 분리될 수 있다. 도시된 제조 단계에서, 트랜지스터들(150a, 150b)은 실제 게이트 전극을 나타내는 게이트 전극 구조(151)를 포함하며, 이 구조는 전도성 전극 물질(151a)을 포함하는 구조로서 이해될 수 있고, 이 물질은 게이트 절연층(151b) 위에 형성될 수 있어서, 각각 해당 활성 영역들(103a, 103b) 내에 위치한 채널 영역(152)으로부터 게이트 전극 물질(151a)을 전기적으로 절연시킬 수 있다. 뿐만 아니라, 게이트 전극 구조들(151)은 예컨대 실리콘 나이트라이드(silicon nitride)를 포함하는 캡층(cap layer)(151c)을 포함할 수 있다. 뿐만 아니라, 스페이서 구조(spacer structure)(105)는 트랜지스터(150a)의 게이트 전극 구조(151)의 측벽들 상에 형성될 수 있어서, 캡층(151c)과 함께 게이트 전극 물질(151a)을 감쌀 수 있다. 다른 한편으로, 마스크층(105a)이 트랜지스터(150b) 위에 형성될 수 있어서, 해당 게이트 전극 물질(151a)을 감쌀 수 있고 또한 활성 영역(103b)을 덮을 수 있다. 게다가, 트랜지스터(150a)를 노출시키면서 마스크층(105a)을 덮도록 레지스트 마스크(resist mask) 등과 같은 마스크(106)가 형성될 수 있다.

[0009] 도 1a에 도시된 바와 같은 종래의 반도체 디바이스(100)는 다음의 공정 절차를 기반으로 형성될 수 있다.

[0010] 활성 영역들(103a, 103b)이 격리 구조(104)를 기반으로 정의될 수 있으며, 격리 구조(104)는 확립된 포토리소그래피(photolithography), 에칭(etch), 증착(deposition) 및 평탄화(planarization) 기법들을 이용함으로써 형성될 수 있다. 그 후에, 예컨대 적절한 마스크 레짐(masking regime)을 기반으로 수행되는 임플란트(implantation) 공정들에 의해 해당 활성 영역들(103a, 103b)에서 기본 도핑 레벨이 설정될 수 있다. 다음으로, 게이트 전극 물질(151a)과 게이트 절연층(151b)을 얻기 위하여 복합 리소그래피 및 패터닝(patterning) 레짐들을 이용함으로써 게이트 전극 구조들(151)이 형성되며, 또한 캡층(151c)이 패터닝될 수 있다. 다음으로, 마스크층(105a)이 예컨대 확립된 저압 CVD(low pressure chemical vapour deposition) 기법들에 의해 증착될 수 있어서, 아마도 에칭 정지 라이너(etch stop liner)로서 실리콘 다이옥사이드(silicon dioxide) 물질과 함께 실리콘 나이트라이드를 형성할 수 있다. 저압 CVD 기법들은 고도의 제어가능성을 제공하지만 그럼에도 기판(101) 전반에 일정한 불균일성(non-uniformity)을 보여줄 수 있으며, 이는 기판의 중심에 비해 기판 가장자리에서 두께가 증가되는 결과를 낳을 수 있다. 결과적으로, 일단 마스크(106)를 형성하고 앞서 증착된 마스크층(105a)으로부터 스페이서 구조(105)를 형성하기 위해 이방성 에칭 분위기(anisotropic etch ambient)에 디바이스(100)를 노출시키면, 결과적인 폭(105w)의 일정한 정도의 불균일성이 생성될 수 있고, 이는 예를 들어 기판(101)의 중심

영역들에 비해 기판(101)의 주변부에서 폭이 약간 증가되는 결과를 낳을 수 있다. 스페이서 구조(105)가 활성 영역(103a)에서 이방성 예칭 기법들에 의해 형성되는 캐비티의 측면 읍셋을 실질적으로 정의할 수 있기 때문에, 마스크층(105a)을 증착하고 후속 이방성 예칭 공정을 수행하는 동안에 도입되는 불균일성들에 따라 해당 측면 읍셋도 또한 약간 달라질 수 있다. 다른 한편으로, 정밀한 애플리케이션들에서 해당 스트레인드 실리콘-게르마늄 합금의 측면 읍셋은 인접한 채널 영역(152)의 전반적인 스트레인을 향상시키는 측면에서 감소될 수 있어서, 스트레인드 실리콘/게르마늄 합금을 채널 영역(152)에 더 가까이 위치시키기 위하여 폭(105w)이 감소되어야 할 수 있다. 전형적으로, 채널 영역(152)의 스트레인은 감소된 폭(105w)에 대하여 지나친 비율로 증가할 수 있으므로, 적정하게 작은 폭(105w)을 제공하기를 원하는 정밀한 공정 전략들에서, 층(105a)의 증착과 후속 예칭 공정에 의해 유발되는 변동성도 또한 지나친 비율로 증가될 수 있어서, 극도로 스케일링된 반도체 디바이스들에 대해 트랜지스터들(150a)의 결과적인 성능의 고도의 변동성에 기여할 수 있다.

[0011]

도 1b는 이방성 플라즈마 보조 예칭 공정(anisotropic plasma assisted etch process)(107) 동안에 반도체 디바이스(100)를 개략적으로 예시한 것이며, 이 공정에서는 적절히 선택된 플라즈마 상태들과 함께 상응하는 이방성 예칭 거동이 얻어질 수 있도록 예컨대 하이드로젠 브로마이드(hydrogen bromide) 등을 기반으로 한 적절한 예칭 화학물질이 적절한 유기 첨가물들(organic additives)과 함께 이용될 수 있다. 하지만, 위에서 설명된 바와 같이, 특히 측면 읍셋의 세세한 차이조차도 트랜지스터 성능의 상당한 변화를 일으킬 수 있는 고도로 정밀한 트랜지스터들이 고려된다면, 플라즈마 보조 예칭 공정(107) 동안에 일정한 정도의 변동성이 또한 유도될 수 있어서, 전반적인 변동성에도 역시 기여할 수 있다. 결과적으로, 층(105)의 앞선 증착에 의해 유발되고, 아마도 각각의 캐비티들(107a)을 형성하는데 이용되는 이방성 예칭 공정(107)과 함께 스페이서 구조(105)를 형성하기 위한 해당 이방성 예칭 공정에 의해 유발되는 변동 폭(105w)으로 인해, 그 위치와 크기도 또한 상응하는 정도의 변동성을 보여줄 수 있다.

[0012]

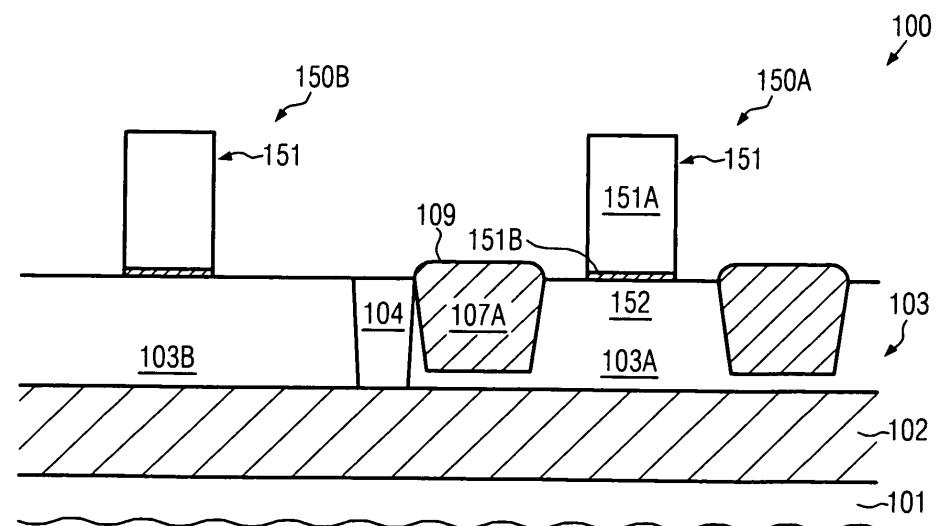

도 1c는 더 진행된 제조 단계에서 반도체 디바이스(100)를 개략적으로 예시한 것이다. 즉, 캐비티들(107a)을 형성한 후에(도 1b와 비교) 마스크(106)(도 1b와 비교)가 제거되고, 트랜지스터(150a)에 실리콘/게르마늄 합금(109)을 증착하기 위하여 선택적 에피택셜 성장 공정이 수행되는 반면, 트랜지스터(150b)는 마스크층(105)에 의해 덮여 있다. 해당 선택적 에피택셜 성장 레시피들은 확립되어 있으며, 이에 있어서 노출된 결정질 실리콘 표면들 상에 실리콘/게르마늄 물질을 상당히 증착하기 위하여 압력, 온도, 전구체 유속(precursor flow rate) 등과 같은 해당 공정 파라미터들이 적절히 선택될 수 있는 반면, 유전체 표면 영역들 상에서의 해당 물질의 증착은 상당히 감소되거나 심지어 무시해도 될 정도이다. 따라서, 실리콘/게르마늄의 자연 격자 상수(natural lattice constant)가 실리콘의 격자 상수보다 더 크기 때문에, 실리콘/게르마늄 물질(109)은 스트레인드 상태에서 성장될 수 있고, 그럼으로써 또한 인접한 채널 영역(152)에서 상응하는 압축 스트레인을 일으킬 수 있는 압축 스트레인드 물질을 얻을 수 있다. 압축 스트레인의 크기는 이전에 형성된 캐비티들의 위치와 크기에 따라 결정될 수 있고, 물질(109) 내의 게르마늄 농도에 따라 결정될 수 있다. 따라서, 물질(109)을 형성하기 위한 선택적 에피택셜 성장 공정 동안 소정의 공정 파라미터들에 대해, 마스크층(105a)을 형성하고, 스페이서 구조(105)를 패터닝하고, 캐비티들(107a)을 형성하기 위한 선행 제조 공정들의 변동성은 기판(101) 전체에 트랜지스터 성능의 일정한 불균일성을 일으킬 수 있다.

[0013]

도 1d는 더 진행된 제조 단계에서 반도체 디바이스(100)를 개략적으로 예시한 것이며, 이 단계에서는 마스크층(105a), 스페이서 구조(105) 및 캡층(151c) (도 1a와 비교)이 제거되며, 이는 확립된 선택적 예칭 기법들에 의해 달성될 수 있다. 그 후에, 디바이스 요구조건들에 따라 드레인 및 소오스 영역들을 형성하는 추가의 처리가 속행될 수 있다.

[0014]

도 1e는 기본 트랜지스터 구성이 실질적으로 완료된 제조 단계에서 반도체 디바이스(100)를 개략적으로 예시한 것이다. 예시된 바와 같이, 트랜지스터들(150a, 150b)은 측벽 스페이서 구조(153)를 포함할 수 있고, 이 구조는 드레인 및 소오스 영역들(154)의 도편트 프로파일의 요구되는 복잡도에 따라 아마도 해당 예칭 정지 라이너들(153b)과 함께 하나 이상의 스페이서 소자들(153a)을 포함할 수 있다. 스페이서 구조(153)는 확립된 기법들에 따라, 즉 예칭 정지 라이너(153b)와 해당 마스크층을 증착함으로써 형성될 수 있으며, 마스크층은 그런 다음 스페이서 소자(153a)를 형성하도록 이방성 예칭 공정들에 의해 패터닝될 수 있다. 스페이서 구조(153)를 형성하기 전에 확장 영역들(154e)을 정의하기 위하여 적절한 임플란트 공정들이 수행될 수 있으며, 확장 영역들은 스페이서 구조(153)를 기반으로 형성될 수 있는 깊은(deep) 드레인 및 소오스 영역들(154d)과 함께 드레인 및 소오스 영역들(154)을 나타낸다. 그 후에, 디바이스(100)를 어닐링(annealing)함으로써 도편트들이 활성화될 수 있고, 그럼으로써 적어도 어느 정도까지 임플란트에 의해 유도된 손상을 또한 재결정화(recrystallize)할 수 있다. 그 후에, 아마도 확립된 공정 전략들에 따라 스트레스가 가해진 유전체 물질들을 기반으로, 금속 실리사이드(metal

silicide) 영역들을 형성하고 해당 컨택 구조를 형성함으로써 추가 처리가 속행될 수 있다. 위에서 설명된 바와 같이, 정밀한 애플리케이션들에 대해 트랜지스터(150a)의 성능은 실리콘/게르마늄 합금(109)에 의해 제공되는 스트레인 유도 메카니즘에 의해 실질적으로 결정될 수 있으며, 특히 채널 영역(152)으로부터 실리콘/게르마늄 물질(109)의 원하는 감소된 측면 옵셋에 대하여 적정하게 높은 정도의 변동성은 생산 수율의 감소를 유발할 수 있는 반면, 다른 경우들에서는 채널 영역(152)으로부터의 해당 옵셋이 바람직한 것보다 더 크게 유지되어야 하기 때문에 물질(109)에 의해 제공되는 스트레인 유도 메카니즘의 잠재력을 충분히 이용되지 않을 수 있다.

[0015] 위에서 서술된 상황에 비추어, 본 개시는 에피택셜 성장된 반도체 합금에 의해 트랜지스터의 성능 향상이 달성될 수 있는 동시에 위에서 확인된 하나 이상의 문제들의 영향들을 회피하거나 적어도 감소시킬 수 있는 기법들 및 반도체 디바이스들에 관한 것이다.

### 발명의 내용

[0016] 일반적으로, 본 개시는 반도체 디바이스들과 기법들을 제공하며, 그에 있어서 둘 이상의 전용 스페이서 소자들을 기반으로 채널 영역에 대한 측면 옵셋에 대하여 향상된 제어가능성을 가지고 트랜지스터 디바이스들의 활성 영역들에서 캐비티들이 형성될 수 있고, 그럼으로써 캐비티들과 그에 따른 스트레인-유도 반도체 합금의 점진적으로 만들어진 형태의 구성이 그 안에 형성될 수 있게 할 수 있다. 예를 들어, 캐비티들의 제1 일부분이 감소된 깊이와 채널 영역으로부터 원하는 작은 옵셋을 가지고 제공될 수 있고, 이는 확립된 에칭 공정을 기반으로 달성될 수 있으며, 그럼으로써 앞서 설명된 바와 같이 종래에는 상당한 트랜지스터 변동성을 일으킬 수 있는 공정 불균일성들을 감소시킬 수 있기 때문에, 둘 이상의 스페이서 소자들의 제조를 기반으로 한 제조 시퀀스로 인해, 스트레인-유도 반도체 합금의 구성을 정의하는데 있어서 향상된 정도의 융통성이 달성될 수 있다. 그 후에, 하나 이상의 부가적인 에칭 공정들에서, 캐비티들의 깊이와 측면 확장이 전반적으로 높은 스트레인-유도 효과를 얻도록 적절하게 조정될 수 있지만, 그럼에도 전반적인 공정 불균일성들을 감소시킬 수 있다. 게다가, 본 명세서에서 개시된 일부 예시적인 양상들에서, 둘 이상의 스페이서 소자들을 기반으로 스트레인 유도 반도체 합금을 형성하기 위한 제조 시퀀스는 또한 예를 들어 인 시튜 도핑, 물질 조성 등에 있어서 서로 다른 특성들을 갖는 반도체 합금을 제공함에 있어 증가된 융통성을 제공할 수 있다. 결과적으로, 매립 반도체 합금을 기반으로 얻어지는 스트레인 유도 메카니즘의 확장성이 트랜지스터 특성들의 균일성을 지나치게 양보하지 않고 전반적인 공정 복잡도에 지나치게 기여하지 않음으로써 확장될 수 있다.

[0017] 본 명세서에서 개시된 하나의 예시적인 방법은 결정질(crystalline) 반도체 영역에 게이트 전극 구조의 측벽들 상에 형성되는 제1 측벽 스페이서에 의해 정의되는 게이트 전극 구조로부터의 옵셋(offset)을 갖는 제1 복수의 리세스(recess)들을 형성하는 단계를 포함하며, 상기 제1 복수의 리세스들은 제1 깊이까지 확장된다. 상기 방법은 상기 결정질 반도체 영역에 상기 제1 측벽 스페이서 상에 형성되는 제2 측벽 스페이서에 의해 정의되는 상기 게이트 전극 구조로부터의 옵셋을 갖는 제2 복수의 리세스들을 형성하는 단계를 포함하며, 상기 제2 복수의 리세스들은 상기 제1 깊이보다 더 깊은 제2 깊이까지 확장된다. 부가적으로, 상기 방법은 선택적 에피택셜 성장 공정(selective epitaxial growth process)을 수행함으로써 상기 제1 및 제2 리세스들에 스트레인 유도 반도체 합금(strain inducing semiconductor alloy)을 형성하는 단계를 포함한다.

[0018] 본 명세서에서 개시되는 추가의 예시적인 방법은 그 상에 제1 게이트 전극 구조를 형성한 제1 반도체 영역 위에 그리고 그 상에 제2 게이트 전극 구조를 형성한 제2 반도체 영역 위에 제1 스페이서층을 형성하는 단계를 포함한다. 상기 방법은 상기 제1 게이트 전극 구조의 측벽들 상에 상기 제1 스페이서층으로부터 제1 측벽 스페이서를 선택적으로 형성하는 단계를 더 포함한다. 뿐만 아니라, 상기 제1 측벽 스페이서를 기반으로 상기 제1 반도체 영역에 캐비티들을 형성하도록 제1 에칭 공정이 수행된다. 부가적으로, 상기 제1 측벽 스페이서 상에 제2 측벽 스페이서가 형성되고, 상기 제2 측벽 스페이서를 기반으로 상기 캐비티들 깊이를 증가시키도록 제2 에칭 공정이 수행된다. 최종적으로, 상기 캐비티들에 스트레인 유도 반도체 합금이 형성된다.

[0019] 본 명세서에서 개시되는 하나의 예시적인 반도체 디바이스는 반도체 기판 위에 형성되는 트랜지스터를 포함하며, 상기 트랜지스터는 결정질 반도체 영역 위에 형성되고 게이트 전극 물질을 포함하는 게이트 전극 구조를 포함한다. 상기 트랜지스터는 상기 결정질 반도체 영역에 형성되고 상기 게이트 전극 물질로부터 제1 측면 옵셋과 제1 깊이를 가지는 제1 스트레인 유도 반도체 합금을 더 포함한다. 부가적으로, 상기 결정질 반도체 영역에 형성되고 상기 게이트 전극 물질로부터 제2 측면 옵셋과 제2 깊이를 가지는 제2 스트레인 유도 반도체 합금이 형성되며, 상기 제1 및 제2 깊이들은 서로 다르고, 상기 제1 및 제2 측면 옵셋들은 서로 다르다.

### 도면의 간단한 설명

[0020]

본 개시의 다양한 실시예들은 첨부된 특허 청구 범위에서 정의되며, 첨부된 도면들을 참조하여 고려될 때 다음의 상세한 설명에 의해 더욱 명확해질 것이다.

도 1a 내지 1e는 종래의 복합적인 제조 시퀀스를 기반으로 실리콘/게르마늄 합금을 형성하는 다양한 제조 단계들 동안에 p-채널 트랜지스터를 포함하는 종래의 반도체 디바이스의 단면도를 개략적으로 예시한 것이다.

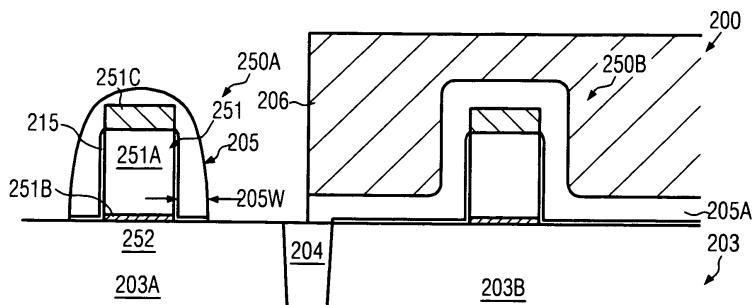

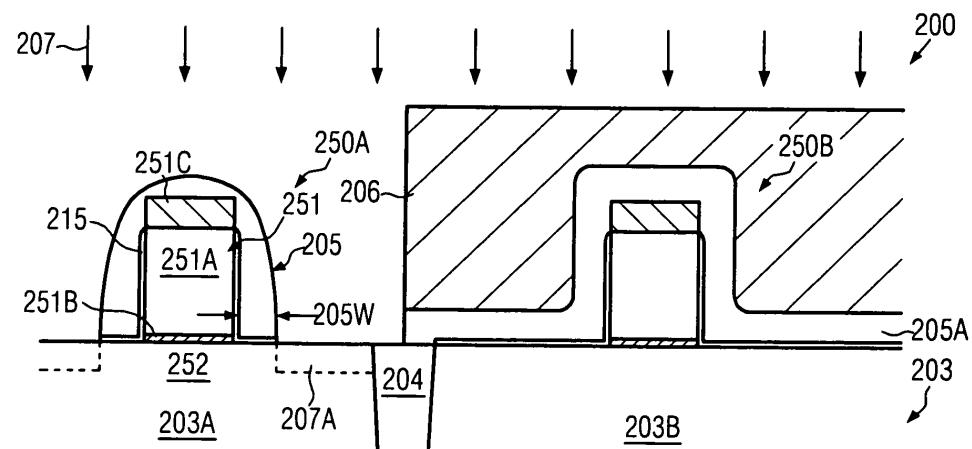

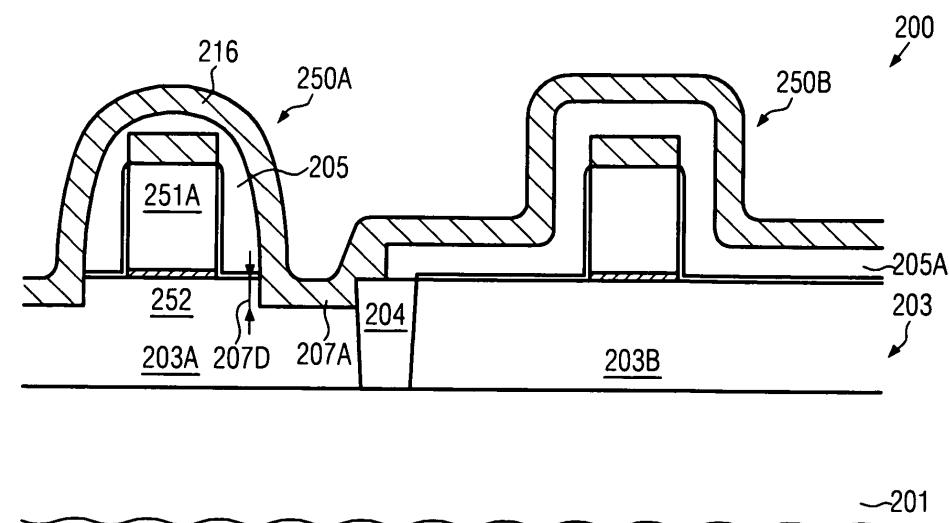

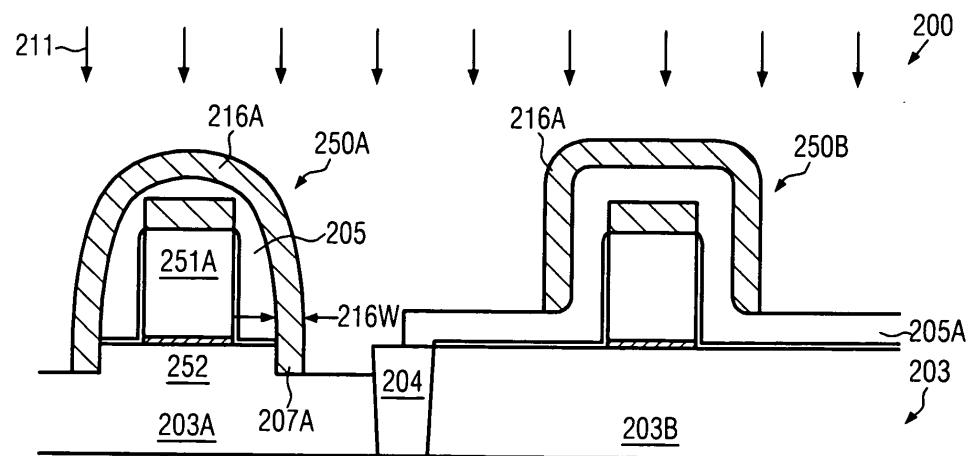

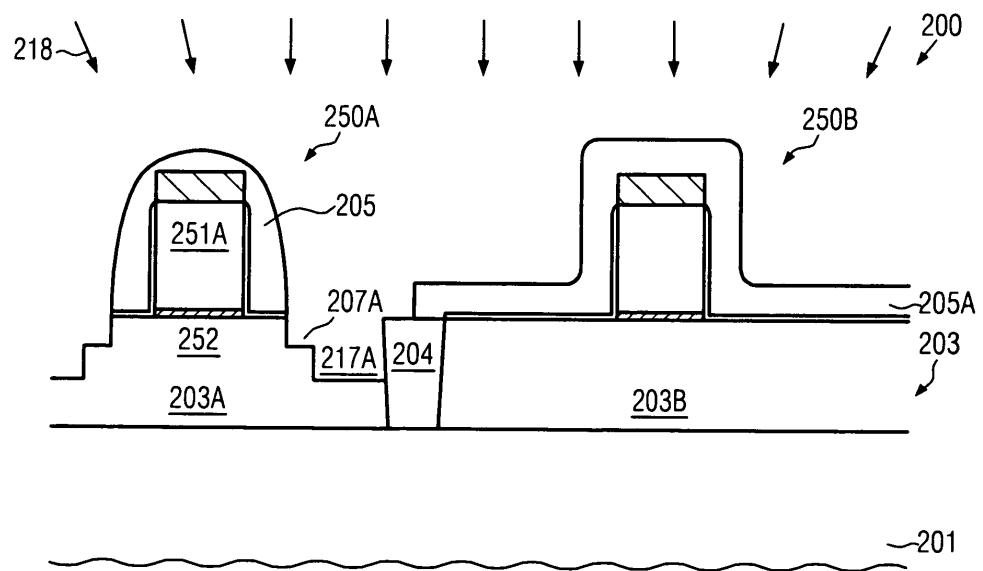

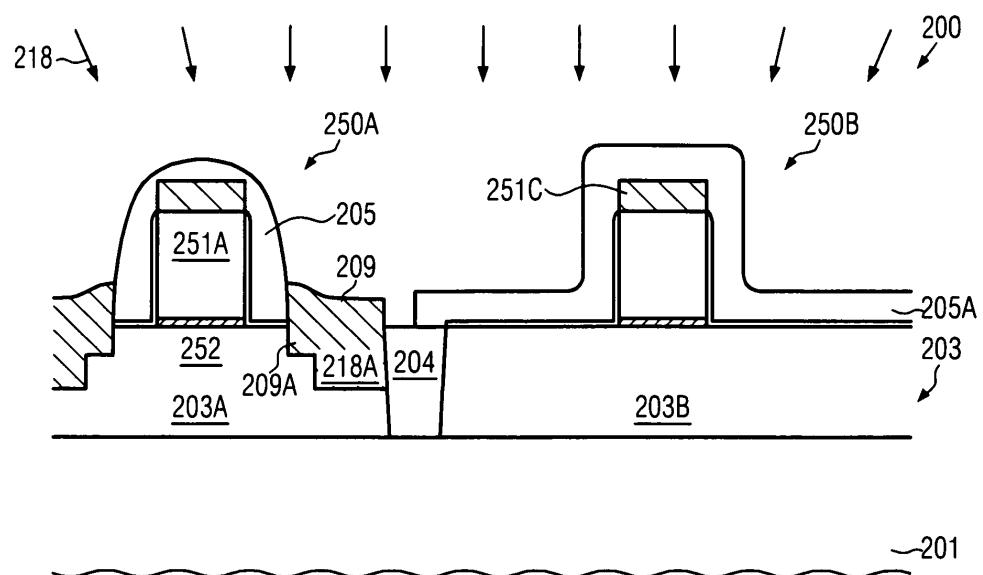

도 2a 내지 2g는 예시적인 실시예들에 따라 다단형 캐비티(graded cavity)를 기반으로 스트레인-유도 반도체 합금을 형성하는 다양한 제조 단계들 동안에 반도체 디바이스의 단면도를 개략적으로 예시한 것이다.

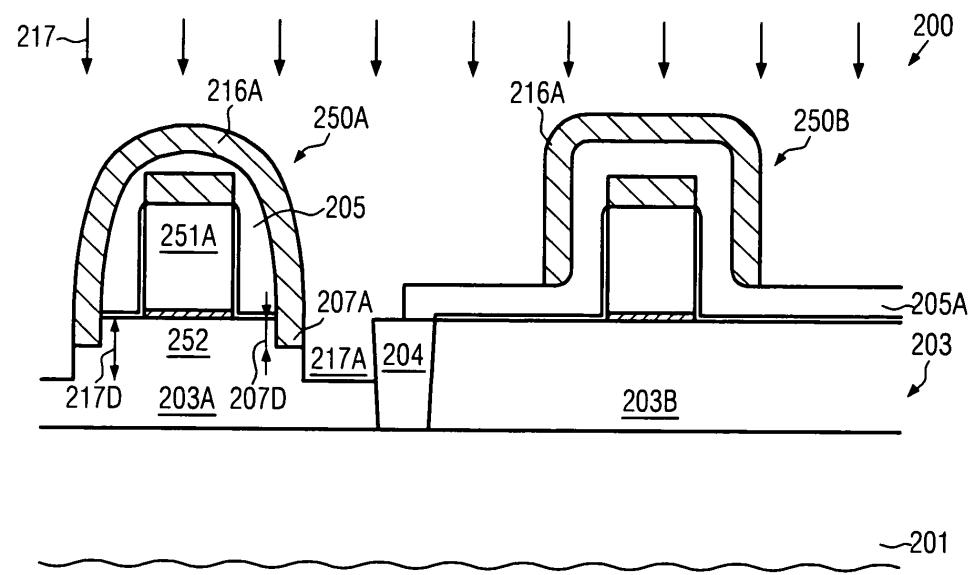

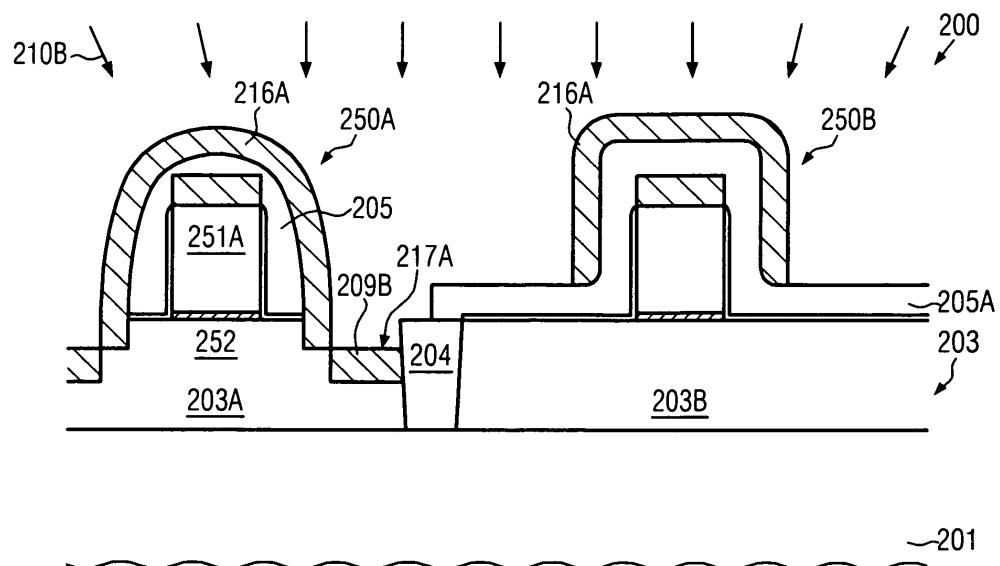

도 2h 내지 2i는 반도체 디바이스의 단면도들을 개략적으로 예시한 것이며, 여기서는 다른 추가의 예시적인 실시예들에 따라 2개의 서로 다른 에피택셜 성장 단계들을 기반으로 다단형 캐비티가 형성될 수 있다.

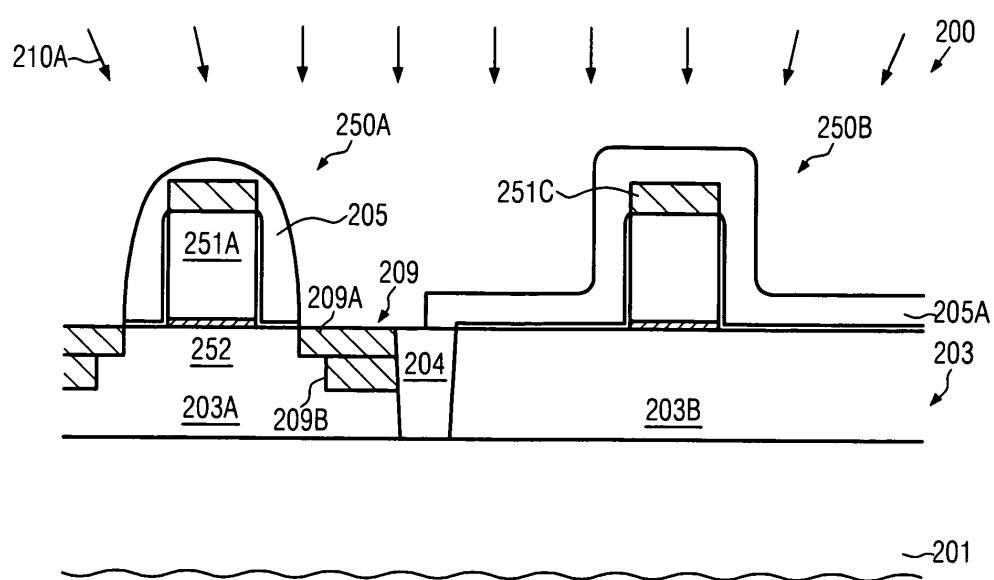

도 2j 내지 2l은 다양한 제조 단계들 동안에 반도체 디바이스의 단면도들을 개략적으로 예시한 것이며, 이 단계들에서는 다른 추가의 예시적인 실시예들에 따라 스페이서 구조의 폭을 감소시키고 중간 에칭 공정들을 수행함으로써 다단형 캐비티가 형성될 수 있다.

도 2m은 더 진행된 제조 단계에서 반도체 디바이스를 개략적으로 예시한 것이며, 이 단계에서는 예시적인 실시예들에 따라 드레인 및 소오스 영역들이 스트레인-유도 반도체 합금 내에 적어도 부분적으로 제공될 수 있다.

### 발명을 실시하기 위한 구체적인 내용

[0021]

본 개시는 도면뿐만 아니라 다음의 상세한 설명에서 예시된 바와 같은 실시예들과 관련하여 서술되지만, 도면뿐만 아니라 다음의 상세한 설명은 본 개시를 개시된 특정 예시적인 실시예들로 한정하려는 의도가 아니라, 오히려 서술된 예시적인 실시예들은 단순히 본 개시의 다양한 측면들을 예시한 것이고, 본 개시의 범위는 첨부된 특허 청구 범위에 의해 정의된다는 것을 이해하여야 한다.

[0022]

개괄적으로, 본 개시는 게이트 전극 구조에 인접하고 그로부터 옵셋(offset)을 가지는 상응하는 캐비티들을 형성하기 위한 적절한 시퀀스를 기반으로 스트레인-유도 반도체 합금의 정밀한 측면 및 수직 구성을 달성될 수 있는 기법들 및 반도체 디바이스들을 서술한다. 따라서, 해당 에칭 공정의 깊이를 제한함으로써 에칭 분위기에 지나치게 노출되는 것을 방지할 수 있기 때문에, 점진적으로 만들어진 형태의 캐비티들의 구성은 채널 영역으로부터 감소된 측면 옵셋을 가능하게 하지만, 그럼에도 해당 에칭 공정에 대해 고도의 제어가능성을 가능하게 한다. 그 후에, 적절히 구성된 스페이서 소자들을 기반으로 하나 이상의 에칭 공정들이 수행될 수 있으며, 스페이서 소자들에 있어서 캐비티들의 깊이가 증가될 수 있지만, 하나 이상의 추가적인 스페이서 소자들이 증가된 옵셋을 제공할 수 있고, 그럼으로써 또한 최종적으로 얻어지는 트랜지스터 특성들에 대한 에칭 관련 불균일성들의 영향을 감소시킬 수 있다. 결과적으로, 적정하게 높은 양의 스트레인-유도 반도체 합금이 캐비티들에 형성될 수 있으며, 게이트 절연층의 높이 레벨에 매우 근접한 높이 레벨에서 채널 영역으로부터의 감소된 측면 옵셋이 달성될 수 있지만, 해당 캐비티와 후속 중착 공정에 대해 고도의 제어가능성이 달성될 수 있어서 디바이스 변동성에 지나치게 기여하지 않을 수 있다. 본 명세서에서 개시된 일부 예시적인 실시예들에서, 예를 들어 서로 다른 정도의 인 시튜 도핑(in situ doping)으로 반도체 합금을 제공하여 향상된 융통성(flexibility)을 가지고 원하는 도편트 프로파일을 조절할 가능성을 제공함으로써 스트레인-유도 반도체 합금의 전반적인 특성들을 설계함에 있어서 향상된 융통성도 얻어질 수 있다. 게다가, 본 명세서에서 개시된 일부 예시적인 양상들에서, 점진적으로 만들어진 형태의 캐비티들의 구성은 둘 이상의 스페이서 소자들을 기반으로 달성될 수 있으며, 이를 소자들은 추가적인 리소그래피 단계들을 필요로 하지 않고 형성될 수 있어 전반적으로 고도로 효율적인 제조 공정 흐름에 기여할 수 있다. 다른 예시적인 실시예들에서, 점진적으로 만들어진 형태의 캐비티들의 구성은 후속의 해당 에칭 공정에 의해 그 폭이 순차적으로 감소될 수 있는 스페이서 구조를 제공하여 캐비티들의 노출된 부분의 깊이를 지속적으로 증가시키는 동시에, 채널 영역으로부터 측면 옵셋을 지속적으로 감소시킬 수 있으며, 최종 에칭 단계는 전용 스페이서 소자를 기반으로 고도의 제어가능성을 가지고 수행될 수 있다. 이 최종 에칭 공정에서는 또한, 요구되는 깊이가 감소될 수 있어서, 또한 이 경우에 향상된 에칭 균일성이 달성될 수 있다. 결과적으로, 본 개시는 스트레인-유도 반도체 합금 물질들의 점진적으로 만들어진 구조와 이에 수반되는 제조 시퀀스들이 향상된 공정 균일도를 제공할 수 있고 따라서 트랜지스터 특성들의 변동성 감소를 제공하여, 이를 성능 증가 메커니즘에 대해 일정한 정도의 확장성(scalability)을 제공할 수 있기 때문에, 실리콘/게르마늄 합금, 실리콘/게르마늄/주석(tin) 합금, 실리콘/주석 합금, 실리콘/탄소(carbon) 합금 등과 같은 부가된 스트레인-유도 반도체 합금들의 영향이 50 nm 및 이보다 상당히 작은 임계 치수를 가지는 트랜지스터 소자들에 대해서도 향상될 수 있는 제조 기법들과 반도체 디바이스들을 제공한다.

[0023]

도 2a 내지 2l을 참조하여, 추가의 예시적인 실시예들이 이제 더욱 상세히 서술될 것이며, 필요하다면 도 1a 내

지 1e도 역시 참조될 수 있다.

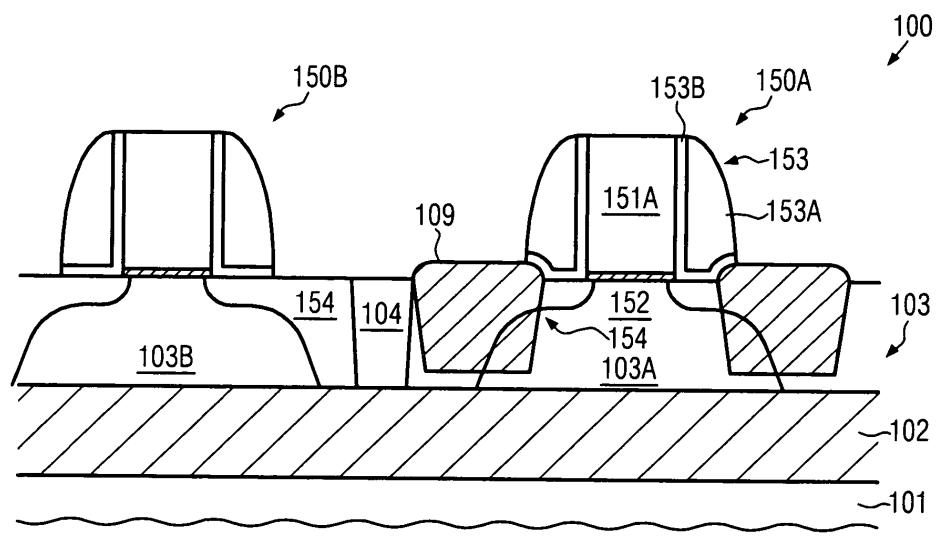

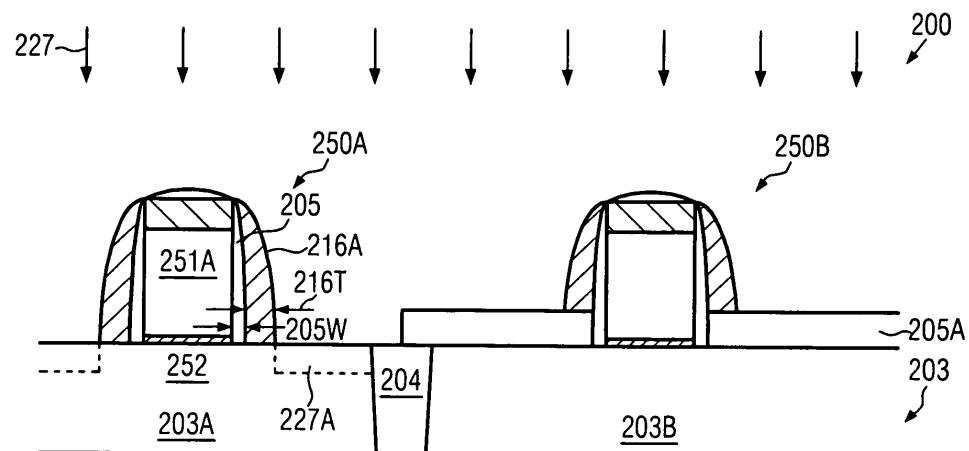

[0024] 도 2a는 반도체 디바이스(200)의 단면도를 개략적으로 예시한 것이며, 이 디바이스는 기판(201)과, 기판(201) 위에 형성되는 반도체층(203)을 포함할 수 있다. 도 1a 내지 1e에서 예시된 반도체 디바이스(100)와 관련하여 역시 서술된 바와 같이, 반도체층(203)과 함께 기판(201)은 벌크 구성(bulk configuration), SOI 구성 등과 같은 임의의 적절한 디바이스 아키텍처에 해당할 수 있다. 예를 들어, SOI 구성의 경우에, 앞에서도 역시 설명된 바와 같이, 매립 반도체층(미도시됨)이 기판(201)과 반도체층(203) 사이에 위치할 수 있다. 또한, 반도체 디바이스(200)는 격리 구조(204)를 포함할 수 있으며, 이 구조는 반도체층(203)의 각각의 부분들에 해당하는 제1 활성 영역 내지 반도체 영역(203A)을 제2 활성 반도체 영역(203B)으로부터 분리시킬 수 있고, 반도체층(203)의 안과 위에는 해당 트랜지스터들(250A, 250B)이 형성된다. 도시된 제조 단계에서, 트랜지스터들(250A, 250B)은 게이트 전극 구조(251)를 포함할 수 있고, 이 구조는 게이트 전극 물질(251A)과 게이트 절연층(251B)을 포함할 수 있고, 게이트 절연층은 각각 활성 영역들(203A, 203B)의 채널 영역(252)으로부터 게이트 전극 물질(251A)을 분리시킬 수 있다. 게다가, 반도체 디바이스(100)와 관련하여 앞에서도 역시 설명된 바와 같이, 게이트 전극 구조들(251)은 캡층(251C)을 포함할 수 있다. 게다가, 예칭 정지 라이너(215), 예컨대 옥사이드 물질 등이 게이트 전극 물질(251A)의 측벽들 상에 형성될 수 있고, 또한 활성 영역들(203A, 203B)의 물질 상에도 형성될 수 있다. 예를 들면, 일부 예시적인 실시예들에서, 활성 영역들(203A, 203B)은 실질적으로 실리콘 물질을 포함할 수 있고, 따라서 층(215)은 실리콘 다이옥사이드 물질을 나타낼 수 있다. 하지만, 다른 경우들에서, 라이너 물질은 예컨대 실리콘 다이옥사이드, 실리콘 나이트라이드 등의 형태로 증착될 수 있다는 것을 인지하여야 한다. 이 경우에, 예칭 정지 라이너(215)는 또한 캡층(251C)의 노출된 표면 영역들 상에 형성될 수 있다. 게다가, 한 예시적인 실시예에서 실리콘 다이옥사이드를 포함하는 스페이서층(205A)이 반도체 영역(203B)과 트랜지스터(250B)의 게이트 전극 구조(251) 위에 형성될 수 있다. 다른 한편으로, 스페이서 소자(205)는 게이트 전극 구조(251)의 측벽들 상에, 즉 예칭 정지 라이너(215)가 제공된다면 예칭 정지 라이너(215) 상에 형성될 수 있다. 스페이서 소자(205)는 뚜렷한 폭(205W)을 가질 수 있으며, 이 폭은 이후의 제조 단계에서 형성될 스트레인-유도 반도체 합금의 측면 옵셋을 실질적으로 결정할 수 있다. 나중에 더욱 상세히 서술될 바와 같이, 트랜지스터(250A)의 지나친 트랜지스터 변동성은 측면 폭(205W)과 함께 적절한 예칭 깊이를 선택함으로써 감소될 수 있기 때문에, 그 폭(205W)은 일부 예시적인 실시예들에서 수 나노미터 이하, 예컨대 대략 2nm 이하로 선택될 수 있으며, 그럼으로써 전반적인 공정 균일도를 향상시킬 수 있다.

[0025] 도 2a에서 예시된 바와 같은 반도체 디바이스(200)는 다음의 공정들을 기반으로 형성될 수 있다. 격리 구조(204)와 게이트 전극 구조(251)가 디바이스(100)와 관련하여 앞에서도 역시 논의된 바와 같은 공정 기법들을 이용함으로써 형성될 수 있다. 그 후에, 필요하다면, 예컨대 산화(oxidation), 증착(deposition) 등에 의해 예칭 정지 라이너(215)가 형성될 수 있고, 후속으로 스페이서층(205A)의 증착이 뒤따르는데, 이는 확립된 CVD 기법들에 의해 달성될 수 있다. 앞서 설명된 바와 같이, 해당 추가 공정 시퀀스가 점진적으로 만들어진 형태의 캐비티를 형성함에 있어서 향상된 균일성을 제공할 수 있어서, 임의의 공정 관련 트랜지스터 변동성들을 감소시킬 수 있기 때문에, 스페이서층(205A)의 두께는 스페이서 소자들(205)의 원하는 감소된 폭(205W)을 얻도록 선택될 수 있다. 일부 예시적인 실시예들에서, 스페이서층(205A)은 확립된 증착 레시피들을 이용하여 실리콘 다이옥사이드 물질을 기반으로 형성될 수 있다. 다른 예시적인 실시예들에서, 스페이서층(205A)은 실리콘 나이트라이드 등과 같은 서로 다른 물질의 형태로 제공될 수 있고, 나중에 설명될 바와 같이 적절한 다른 물질들이 부가적인 측벽 스페이서 소자를 제공하기 위한 나중의 제조 단계에서 이용될 수 있다. 다음으로, 트랜지스터(250A) 위에서 스페이서층(205A)을 노출시키고 트랜지스터(250B) 위에서 스페이서층(205A)을 덮도록 레지스트 마스크와 같은 예칭 마스크(206)가 리소그래피에 의해 형성될 수 있다. 그 후에, 제공된다면 예칭 정지 라이너(215)까지 선택적으로 또는 적어도 반도체 영역(203A)의 물질까지 선택적으로 스페이서층(205A)의 물질을 제거하여 폭(205W)을 가지는 스페이서 소자(205)를 제공하도록 적절한 이방성 예칭 공정(anisotropic etch process)이 수행될 수 있다.

[0026] 도 2b는 예칭 분위기(207)에 노출되었을 때 반도체 디바이스(200)를 개략적으로 예시한 것이며, 이 분위기는 제1 리세스 또는 캐비티의 일부분(207A)을 형성하기 위하여 스페이서 소자(205)에 대하여 반도체 영역(203A)의 물질을 선택적으로 제거하기 위한 이방성 플라즈마-보조 예칭 공정에 해당할 수 있다. 도 2b에 예시된 실시예에서, 예칭 공정(207)은 예칭 마스크(206)를 기반으로 수행될 수 있는 반면, 다른 예시적인 실시예들에서, 마스크(206)는 예칭 공정(207)을 수행하기 전에 제거될 수 있으며, 그럼으로써 스페이서층(205A)을 트랜지스터(250B)의 반도체 영역(203B)과 게이트 전극 구조(251)를 보호하기 위한 예칭 마스크로서 이용할 수 있다. 종래의 전략들과 대조적으로, 예칭 공정(207)은 소정의 화학물질에 대하여 상응하는 감소된 예칭 시간을 선택함으로써 리세스(207A)의 감소된 깊이를 얻도록 수행될 수 있으므로 고도의 제어가능성과 그에 따른 채

널 영역(252)으로부터의 리세스(207A)의 측면 옵셋의 균일성이 달성될 수 있다. 결과적으로, 도 1b의 캐비티들(107A)과 같은 해당 캐비티들의 상당한 깊이가 요구되는 공정 전략들에 비해 공정(207) 동안에 측면 에칭율(etch rate)의 해당 변동성이 감소될 수 있기 때문에, 폭(205W)에 의해 정의된 바와 같은 전반적인 재사용된 측면 옵셋에 대하여도 결과적인 트랜지스터 특성들의 향상된 기판 전체에 걸친 균일도가 달성될 수 있다. 결과적으로, 확립된 선택적 이방성 에칭 레시피들을 기반으로, 감소된 깊이를 갖는 리세스들(207A)을 형성함으로써 스트레인-유도 물질의 측면 위치의 우수한 제어가 달성될 수 있다.

[0027] 또 다른 예시적인 실시예들에서, 에칭 공정(207)은 습식 화학적 에칭 레시피(wet chemical etch recipe)를 기반으로 수행될 수 있으며, 리세스(207A)의 감소된 깊이는 또한 고도로 제어가능한 측면 에칭율을 제공할 수 있으므로, 초기 스페이서 폭(205W)을 기반으로 뚜렷한 해당 측면 옵셋이 얻어질 수 있다. 예를 들면, 리세스(207A)의 감소된 깊이로 인해 등방성 습식 화학적 에칭 분위기가 설정될 수 있고, 따라서 해당 측면 에칭율도 또한 훌륭하게 제어가능할 수 있어서, 예를 들어 게이트 전극 구조(251)의 가장자리에서 게이트 절연층(251B)의 우수한 완전성(integrity)을 제공할 수 있는 반면, 그럼에도 채널 영역(252)으로부터의 리세스(207A)의 측면 옵셋은 트랜지스터 특성들의 균일성을 양보하지 않고 낮은 값들을 기반으로 조정될 수 있다.

[0028] 도 2c는 더 진행된 제조 단계에서 반도체 디바이스(200)를 개략적으로 예시한 것이다. 예시된 바와 같이, 리세스(207A)는 반도체 영역(203A)에서 깊이(207D) 만큼 아래로 형성될 수 있으며, 이는 앞서 설명된 바와 같이 향상된 전반적인 공정 제어를 제공할 수 있다. 게다가, 추가의 스페이서층(216)이 제1 및 제2 트랜지스터들(250A, 250B) 위에 형성되며, 스페이서층(216)은 스페이서층(205A)의 물질과 서로 다른 물질을 포함할 수 있다. 예를 들면, 하나의 예시적인 실시예에서, 스페이서층(216)은 실리콘 나이트라이드를 포함할 수 있는 반면, 스페이서층(205A)은 실리콘 다이옥사이드를 기반으로 형성될 수 있다. 다른 예시적인 실시예들에서, 위에서 논의된 바와 같이, 스페이서층(205A)과 따라서 스페이서 소자(205)가 서로 다른 에칭 특성들을 가지는 물질을 기반으로 형성될 수 있는 한, 스페이서층(216)은 실리콘 다이옥사이드와 같은 서로 다른 물질들을 포함할 수 있다는 것을 인지하여야 한다. 해당 에칭 공정 파라미터들과 함께 스페이서층(216)을 기반으로 형성되는 스페이서 소자들에 대하여 적절한 두께를 얻기 위하여 스페이서층(216)은 적절한 두께로 제공될 수 있다. 이런 목적으로, 임의의 확립된 증착 기법들이 이용될 수 있다.

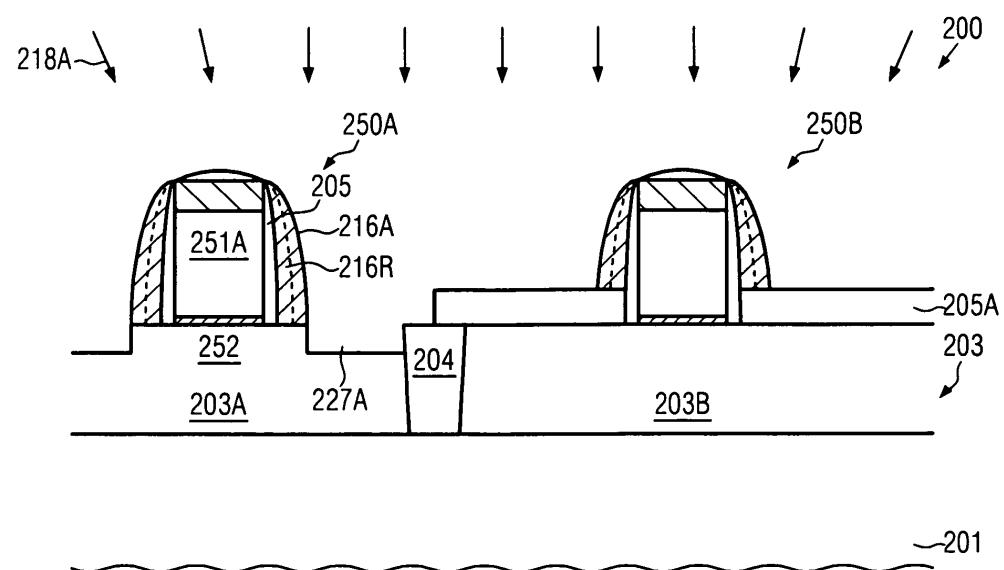

[0029] 도 2d는 트랜지스터(250A)에서 적어도 스페이서 소자(205) 상에 스페이서 소자(216A)를 형성하기 위한 추가의 이방성 에칭 공정(211) 동안에 반도체 디바이스(200)를 개략적으로 예시한 것이다. 이런 목적으로, 확립된 선택적 이방성 에칭 레시피들이 이용가능하며, 예를 들어 실리콘 다이옥사이드 물질 및 실리콘 물질에 대하여 실리콘 나이트라이드 물질이 선택적으로 제거될 수 있다. 또한, 도 2d에 도시된 실시예에서, 이방성 에칭 공정(211)은 비-마스크(non-mask) 공정으로서 수행될 수 있고, 그럼으로써 또한 트랜지스터(250B)에서 스페이서층(205A) 상에 해당 스페이서 소자(216A)를 형성할 수 있다. 결과적으로, 트랜지스터(250A)의 스페이서 소자(216A)는 부가적인 리소그래피 단계 없이 제공될 수 있고, 그럼으로써 매우 효율적인 전반적인 제조 흐름에 기여할 수 있다. 다른 예시적인 실시예들에서, 에칭 공정(211) 동안에 스페이서층(205A)의 물질 제거가 예컨대 공정(211)의 덜 현저한 에칭 선택비(etch selectivity)로 인해 및/또는 스페이서층(205A)의 감소된 두께로 인해 부적절하다고 여겨질 때에는, 에칭 공정(211)을 수행하기 전에 트랜지스터(250B)를 덮기 위하여 에칭 마스크(206)와 같은 추가의 에칭 마스크가 형성될 수 있다. 결과적으로, 에칭 공정(211) 동안에, 반도체 영역(203A)에서 형성되는 리세스들(207A)이 노출될 수 있는 동시에 원하는 폭(216W)으로 스페이서 소자(216A)를 제공할 수 있다. 예를 들면, 폭(216W)은 영역(203A)에서 형성될 반도체 물질의 원하는 점진적으로 만들어진 형태를 얻도록 선택될 수 있는 동시에, 결과적인 캐비티의 측면 형태에 대해 고도의 제어가능성이 달성될 수 있다. 게다가, 요구되는 물질 제거의 정도가 해당 캐비티들이 단일의 에칭 단계에서 형성되어야 할 수 있는 종래의 전략들에 비해 상당히 덜 현저할 수 있기 때문에, 결과적인 캐비티의 수직 확장이 향상된 효율성을 가지고 제어될 수 있다.

[0030] 도 2e는 추가의 에칭 공정(217)에 노출될 때 반도체 디바이스(200)를 개략적으로 예시한 것이며, 이 공정에서는 이전에 형성된 리세스(207A)의 노출된 부분에 추가의 리세스(217A)가 형성될 수 있다. 따라서, 에칭 분위기(217)의 공정 파라미터들과 스페이서 소자(216A)의 폭(216W)을 기반으로 추가의 리세스(217A)의 측면 옵셋이 정의되는 반면, 그 깊이는 공정(217) 동안에 소정의 제거율(removal rate)에 대한 공정 시간을 기반으로 조정될 수 있다. 일부 예시적인 실시예들에서, 리세스(217A)는 깊이(217D)까지 확장하도록 형성될 수 있고, 이 깊이는 리세스들(207A, 217A)에 의해 표현되는 캐비티의 최종 원하는 깊이, 예컨대 베이스층(203)의 두께의 50 내지 90 퍼센트에 해당할 수 있다. 이 경우에, 깊이(217D)는 리세스(207A)의 깊이와 추가의 에칭 공정(217) 동안에 얻어지는 깊이의 조합으로서 고려되어야 한다. 깊이(217D)가 초기 정의된 깊이(207D)보다 상당히 더 깊어, 아마도 리세스(217A)에 대한 채널 영역(252)으로부터의 측면 옵셋의 일정한 정도의 변동성을 일으킬 수 있다고 하더라

도, 트랜지스터 변동성에 대한 대부분의 결정적인 영향은 "얕은 부분(shallow portion)", 즉 리세스(270A)에 의해 나타내어질 수 있으며, 이 부분은 하지만 앞서 설명된 바와 같이 향상된 제어가능성을 가지고 제공될 수 있기 때문에, 종래의 전략들에 비해 전반적인 트랜지스터 변동성은 그럼에도 상당히 향상될 수 있다는 것을 인지하여야 한다.

[0031] 원한다면, 스페이서 소자(216)와 같은 하나 이상의 추가의 스페이서 소자들이 예컨대 동일한 물질을 기반으로 형성될 수 있고, 후속의 에칭 공정이 앞서-형성된 리세스의 해당 부분의 깊이를 더 증가시키도록 수행될 수 있으며, 또한 채널 영역(252)에 대한 측면 옵셋도 점진적으로 증가될 수 있다는 것을 인지하여야 한다.

[0032] 도 2f는 추가의 에칭 분위기(218)에 노출될 때 반도체 디바이스(200)를 개략적으로 예시한 것이며, 이 에칭 분위기는 스페이서 소자(205)와 스페이서층(205A)에 대하여 선택적으로 스페이서 소자들(216A)을 제거하도록 설계될 수 있다. 다른 예시적인 실시예들에서, 앞서 설명된 바와 같이, 트랜지스터(250A)에서 스페이서 소자(216A)를 형성하기 위한 공정이 앞서 논의된 바와 같이 해당 에칭 마스크를 기반으로 수행되었을 때, 트랜지스터(250B)는 스페이서층(216)에 의해 덮여질 수 있다. 이 경우에, 트랜지스터(250A)의 스페이서층(216)과 스페이서 소자(216A)는 에칭 공정(218) 동안에 제거될 수 있다. 예를 들면, 스페이서 소자(216A)가 실리콘 나이트라이드를 포함할 때, 예컨대 고온의 인산(hot phosphoric acid)을 기반으로 한 확립된 에칭 레시피들이 이용될 수 있다. 다른 경우들에서, 스페이서 소자들(216A)이 실리콘 다이옥사이드 물질의 형태로 제공될 때, 희석된 플루오르화 수소산(diluted hydrofluoric acid, diluted HF)과 같은 다른 적절한 레시피들이 이용될 수 있는 반면, 스페이서층(205A)과 스페이서(205)는 이들 컴포넌트에 의해 덮여지는 해당 물질들의 완전성을 제공할 수 있다. 따라서, 에칭 공정(218) 후에, 해당 캐비티들(218A)이 반도체 영역(203A)에 형성되고, 따라서 이는 리세스들(207A, 217A)을 포함할 수 있다.

[0033] 도 2g는 더 진행된 제조 단계에서 반도체 디바이스(200)를 개략적으로 예시한 것이며, 이 단계에서는 스트레인-유도 반도체 합금(209)으로 캐비티들(218A)을 채우기 위해 선택적 에피택셜 성장 공정(210)이 수행될 수 있다. 일부 예시적인 실시예들에서, 트랜지스터(250A)는 p-채널 트랜지스터를 나타낼 수 있고, 이 트랜지스터에서 반도체 영역(203A)의 결정학적 구성은 전류 흐름 방향을 따라, 즉 도 2g에서 수평 방향으로 작용하는 압축 스트레인 컴포넌트가 앞서 설명된 바와 같이 트랜지스터 성능의 증가를 제공할 수 있도록 되어 있다. 따라서, 반도체 합금(209)은 실리콘/케르마늄 합금의 형태로 제공될 수 있고, 이 합금에서 케르마늄의 비율은 채널 영역(252)에서 유도되는 원하는 스트레인 컴포넌트에 따라 선택될 수 있다. 뿐만 아니라, 점진적으로 만들어진 형태의 캐비티들(218A)로 인해, 물질(209)의 상응하는 점진적으로 만들어진 구성이 달성될 수 있으며, 디바이스(100)와 관련하여 앞서 설명된 바와 같이 그 얕은 부분(209A)은 지나친 트랜지스터 변동성을 방지하면서 채널 영역(252)에 아주 근접하여 위치될 수 있다. 다른 예시적인 실시예들에서, 반도체 합금(209)은 예를 들어 실리콘이나 실리콘/케르마늄과 함께 주석을 포함할 수 있어서, 채널 영역(252)에서 압축 스트레인 컴포넌트를 또한 제공할 수 있다. 또 다른 예시적인 실시예들에서, 트랜지스터(250A)는 그 성능이 인장 스트레인 컴포넌트를 기반으로 증가될 수 있는 트랜지스터에 해당할 수 있으며, 이는 반도체 합금(209)을 실리콘/탄소 합금의 형태로 제공함으로써 달성될 수 있다.

[0034] 선택적 에피택셜 성장 공정(210) 동안에, 스페이서 소자(205)와 스페이서층(205A)은 본질적으로 상당한 반도체 증착을 방지하도록 성장 마스크(growth mask)로서 작용할 수 있으며, 따라서 트랜지스터들(250A, 250B)의 게이트 전극 구조(251)의 완전성을 유지하고 또한 반도체 영역(203B)의 완전성을 유지할 수 있다.

[0035] 그 후에, 스페이서 소자(205)와 스페이서층(205A)이 실리콘 다이옥사이드 물질을 포함할 때, 예를 들어 플루오르화 수소산과 같은 확립된 에칭 레시피들을 기반으로 이들 컴포넌트를 제거함으로써 추가의 처리가 속행될 수 있다. 다른 경우들에서, 앞서 논의된 바와 같이, 스페이서(205)와 스페이서층(205A)이 실리콘 나이트라이드를 포함할 때, 예를 들어 고온의 인산과 같은 임의의 다른 선택적 에칭 레시피가 이용될 수 있다. 그 후에, 캡층(251C)이 고온의 인산과 같은 임의의 적절한 에칭 레시피에 의해 제거될 수 있고, 그 후에 예를 들어 도 1e에서 예시된 바와 같은 디바이스(100)와 관련하여 서술된 바와 같이 추가의 처리가 속행될 수 있다. 예를 들어, 드레인 및 소오스 확장 영역들(미도시됨)이 형성되고 뒤이어 적절한 스페이서 구조의 형성이 뒤따를 수 있고, 그런 다음 이는 이온 임플란트를 기반으로 깊은 드레인 및 소오스 영역들을 정의하는데 이용될 수 있으며, 선택적 에피택셜 성장 공정(210)을 기반으로 적절한 도편트 류를 넣음으로써 트랜지스터(250A)에 대한 임플란트 공정은 상당히 향상될 수 있다. 따라서, 이 경우에, 원하는 정도의 인-시튜 도핑이 공정(210) 동안에 달성될 수 있다. 그 후에, 원한다면 일정한 정도의 도편트 확산을 개시하고, 또한 도편트들을 활성화하고 임플란트-유도된 손상을 재결정화하도록 적절한 어닐링 공정들이 수행될 수 있다. 다음으로, 디바이스 요구조건들에 따라 금속

실리사이드가 형성될 수 있다.

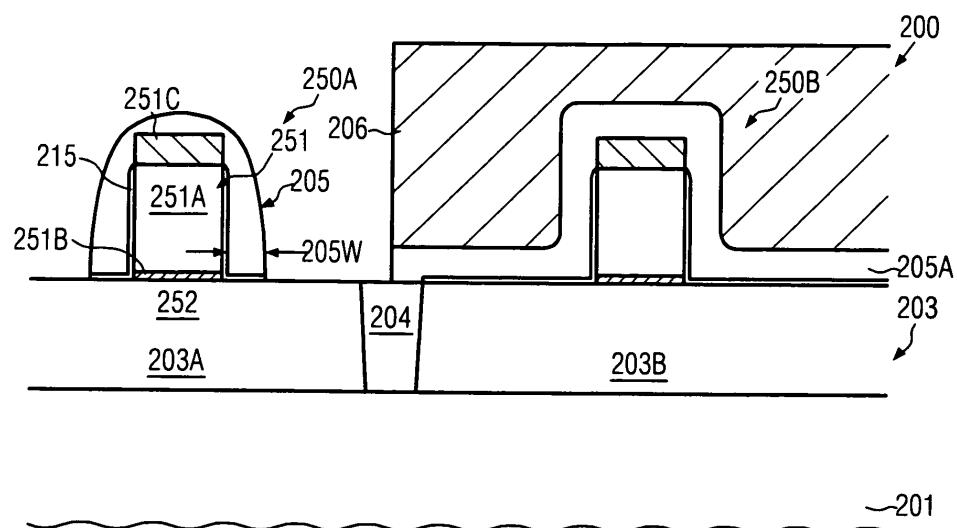

[0036] 도 2h는 추가의 예시적인 실시예들에 따라 반도체 디바이스(200)를 개략적으로 도시한 것이다. 예시된 바와 같이, 스페이서 소자(216A)가 여전히 존재할 수 있고, 디바이스(200)는 리세스(217A) 안으로 제1 부분(209B)을 채우기 위해 제1 에피택셜 성장 공정(210B)을 받을 수 있다. 따라서, 에피택셜 성장 공정(210B) 동안에, 원하는 특성들을 갖는 하위 부분(209B)을 제공하기 위하여 예를 들어 인-시튜 도핑의 정도, 물질 조성 등에 대하여 적절한 공정 파라미터들이 설정될 수 있다. 예를 들면, 인-시튜 도핑의 정도는 실질적으로 트랜지스터(250A)에 대하여 깊은 드레인 및 소오스 영역들의 원하는 도편트 농도에 해당하도록 선택될 수 있다. 또한, 원한다면, 합금(209B)의 스트레인-유도 종(species)의 농도가 전반적인 디바이스 요구조건에 따라 조정될 수 있다. 예를 들면, 압축 스트레스 컴포넌트를 원한다면 계르마늄, 주석 등의 적정하게 높은 농도가 제공될 수 있다.

[0037] 그 후에, 에칭 공정(218)(도 2f와 비교)이 트랜지스터들(250A, 250B)로부터 스페이서 소자(216A)를 제거하도록 수행될 수 있으며, 앞서 논의된 바와 같이, 해당 스페이서 소자들이 위에서 설명된 것처럼 트랜지스터(250B)에 형성되지 않을 때에는, 해당 스페이서층은 트랜지스터(250B)로부터 제거될 수 있다. 추가의 선택적 에피택셜 성장 공정을 위해 물질(201B)의 노출된 표면 부분을 준비(prepare)하기 위해 해당 세정 레시피(cleaning recipe)가 이용될 수 있다.

[0038] 도 2i는 추가의 선택적 에피택셜 성장 공정(210A)의 중착 분위기에 노출될 때 반도체 디바이스(200)를 개략적으로 예시한 것이다. 따라서, 스트레인-유도 반도체 합금(209)의 얇은 부분(209A)이 형성될 수 있으며, 물질(209)의 전반적인 향상된 표면 토포그래피(surface topography) 이외에도, 공정 및 디바이스 요구조건들에 따라 물질(209A)의 서로 다른 특성들이 조정될 수 있다. 예를 들면, 적절한 인-시튜 도핑이 공정(210A) 동안에 달성될 수 있으며, 따라서 해당 임플란트 유도된 완화 효과들이 감소될 수 있기 때문에, 여전히 형성될 드레인 및 소오스 영역들의 추가의 프로파일링(profiling)이 상당히 완화(relax)될 수 있거나 또는 심지어는 완전히 생략될 수 있고, 그럼으로써 훨씬 더 향상된 드레인 유도 효과에 기여할 수 있다. 뿐만 아니라, 원한다면, 물질 조성은 필요하다면 물질(209B)에 비해 서로 다르게 선택될 수 있다. 위에서 서술된 바와 같이, 에피택셜 성장 공정(210A) 후에 추가 처리가 속행될 수 있다.

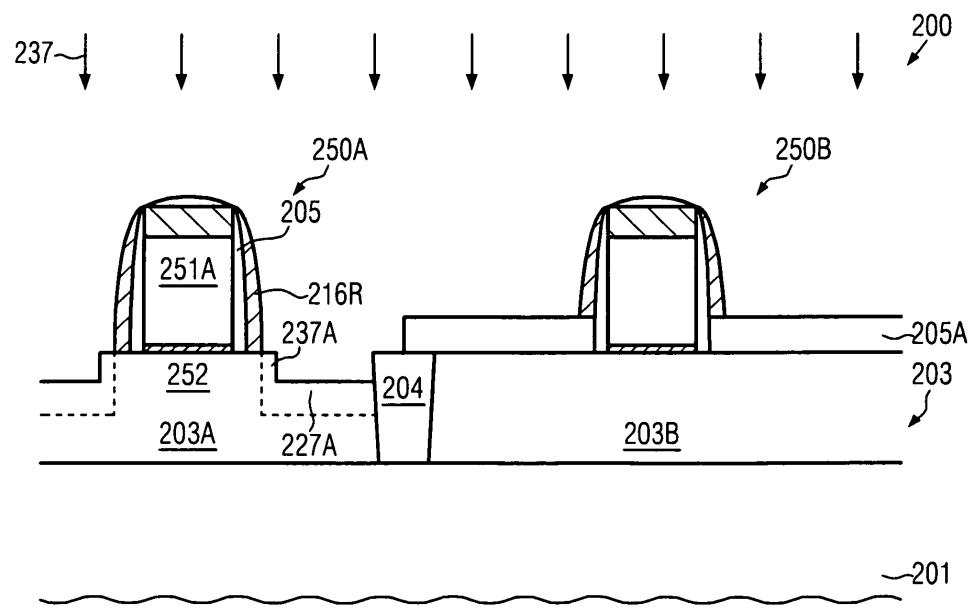

[0039] 도 2j 내지 2l을 참조하여, 추가의 예시적인 실시예들이 이제 서술될 것이며, 이 실시예들에서 스페이서 구조의 폭을 감소시키고 해당 캐비티 에칭 공정들을 수행함으로써 점진적으로 만들어진 형태의 캐비티 구성이 달성될 수 있다.

[0040] 도 2j는 한 제조 단계에서 반도체 디바이스(200)를 개략적으로 예시한 것이며, 이 단계에서는 스페이서층(205A)의 에칭 정지 능력에 따라 스페이서 소자(216A)가 적어도 트랜지스터(250A)에 형성될 수 있는 반면, 제2 트랜지스터(250B)는 해당 스페이서층 또는 스페이서 소자(216A)를 포함할 수 있다. 즉, 둘 이상의 에칭 대기들(etch atmospheres)에 스페이서층(205A)의 지나친 노출이 부적절하다고 여겨질 수 있으면, 스페이서 소자(216A)는 해당 레지스트 마스크를 기반으로 형성될 수 있고, 스페이서층은 트랜지스터(250B) 위에 유지될 수 있다. 뿐만 아니라, 스페이서 소자(216A)는 스페이서 소자(205)의 폭(205W)과 함께 해당 캐비티의 가장 깊은 깊이에 대해 원하는 옵셋에 해당할 수 있는 폭(216T)으로 제공될 수 있다. 스페이서 소자(216A)를 기반으로, 디바이스(200)는 해당 리세스(227A)를 형성하기 위해 에칭 분위기(227)에 노출될 수 있다. 에칭 공정(227)의 임의의 공정 파라미터들에 대하여, 리세스들(207A, 217A)(도 2f와 비교)을 형성하기 위해 앞서 설명된 바와 같은 동일한 기준이 적용된다.

[0041] 도 2k는 추가의 에칭 분위기(218A)에 노출될 때 반도체 디바이스(200)를 개략적으로 예시한 것이며, 스페이서 소자(216A)의 일부분이 제거될 수 있다. 예를 들면, 스페이서 소자(216A)가 실리콘 나이트라이드를 포함할 때 에칭 분위기(218A)는 고온의 인산을 기반으로 설정될 수 있다. 다른 경우들에서, 임의의 다른 적절한 선택적 에칭 레시피가 이용될 수 있다. 에칭 공정(218A) 동안에, 예를 들어 도시된 제조 단계에서 리세스(227A)를 포함할 수 있는 점진적으로 만들어진 형태의 캐비티의 추가의 측면 옵셋을 조정하기 위하여 감소된 스페이서 소자(216R)를 유지하도록 스페이서 소자(216A)의 폭이 고도로 제어가능한 방식으로 제거될 수 있다.

[0042] 도 2l은 추가의 에칭 분위기(237)에 노출될 때 반도체 디바이스(200)를 개략적으로 예시한 것이며, 에칭 동안에 리세스(227A)의 폭이 증가될 수 있는 동시에 추가의 리세스(237A)가 형성될 수 있고, 이 리세스는 채널 영역(252)에 대하여 스페이서 소자(216R)의 폭에 의해 결정되는 측면 옵셋을 가질 수 있다. 그 후에, 공정(218A)과 유사한 추가의 에칭 공정(도 2k와 비교)이 스페이서 소자(216R)를 제거하여 스페이서(205)를 노출시키도록 수행될 수 있으며, 따라서 이는 스페이서 소자(216R)에 비해 현저한 에칭 선택비로 인해 고도의 균일성을 가지고 해당 리세스의 측면 옵셋을 정의할 수 있다. 따라서, 공정(237)과 유사한 에칭 파라미터들을 기반으로 할 수 있는

후속의 예청 공정에서, 앞서 설명된 바와 같이 얇은 리세스는 고도의 공정 균일도를 가지고 채널 영역(252)으로부터 원하는 감소된 옵셋을 가지고 형성될 수 있다. 다른 한편으로, 해당 리세스들(227A, 237A)의 깊이는 얇은 리세스를 최소의 원하는 측면 옵셋으로 형성하는 동안에 더 증가될 수 있다. 결과적으로, 이 경우에도 또한, 점진적으로 만들어진 형태의 구성을 갖는 해당 캐비티들이 달성될 수 있으며, 또한 고도의 공정 균일성이 상용하는 안정한 트랜지스터 특성들을 낳을 수 있다. 따라서, 트랜지스터(250A)에 대해 점진적으로 만들어진 형태의 캐비티들을 형성한 후에, 앞서 설명된 바와 같이, 스페이서 소자(205)와 스페이서층(205A)을 제거하고 점진적으로 만들어진 형태의 캐비티에 적절한 반도체 합금을 채움으로써 추가 처리가 속행될 수 있다.

[0043] 도 2m은 더 진행된 제조 단계에서 반도체 디바이스(200)를 개략적으로 예시한 것이다. 예시된 바와 같이, 트랜지스터들(250A, 250B)은 스페이서 구조(253)를 포함할 수 있고, 이 구조는 적어도 트랜지스터(250B)에서 드레인 및 소오스 영역들(254)의 측면 및 수직 도편트 프로파일들을 조정하도록 설계될 수 있다. 즉, 도시된 실시예에서, 영역들(254)의 측면 및 수직 프로파일을 조정하기 위하여 스페이서 구조(253)를 제공하는 것과 함께 임플란트 시퀀스들을 기반으로 트랜지스터(250B)의 드레인 및 소오스 영역들(254)이 형성될 수 있다. 앞서 설명된 바와 같이, 감소된 양의 도편트 종들이 이온 임플란트 공정들에 의해 포함되어야 할 수 있고, 그럼으로써 해당 임플란트 공정들의 스트레스 완화 효과들을 감소시킬 수 있기 때문에, 반도체 합금(209)은 인-시튜 도핑된 물질로서 제공될 수 있고, 그럼으로써 해당 드레인 및 소오스 영역들(254)의 전반적인 도편트 프로파일을 설계함에 있어 향상된 융통성을 제공할 수 있다. 다른 경우들에서, 앞서 설명된 바와 같이, 드레인 및 소오스 확장 영역들(254E)에 대하여 적어도 상당한 양의 도편트 농도들이 물질(209)의 적어도 일부분의 인-시튜 도핑을 기반으로 제공될 수 있으며, 점진적으로 만들어진 형태의 물질(209)의 구성으로 인해, 해당 도편트 종들이 채널 영역에 매우 근접하여 위치될 수 있다. 뿐만 아니라, 일부 예시적인 실시예들에서, 드레인 및 소오스 영역들(254)의 도편트 프로파일은 인-시튜 도핑된 물질(209)을 기반으로 실질적으로 완전히 설정될 수 있고, 이 물질은 앞서 논의된 바와 같이 서로 다른 도편트 농도들을 가질 수 있다. 이 경우에, 원한다면, 최종 도편트 프로파일은 예를 들어 필요하다면 카운터-도핑(counter-doping) 종들을 넣는 것을 기반으로 조정될 수 있고, 이는 전형적으로 해당 임플란트 공정 동안에 상당히 감소된 양(dose)을 필요로 할 수 있으며, 그럼으로써 임플란트 유도된 손상을 지나치게 생성하지 않을 수 있다. 결과적으로, 해당 어닐링 공정(219) 동안에, 해당 pn-접합들이 물질(209)의 "외부(outside)"에 위치되어야 할 때에는 예를 들어 일정한 정도의 도편트 확산을 개시함으로써 최종적으로 원하는 도편트 프로파일이 조정될 수 있는 반면, 다른 경우들에서는, 지나친 도편트 확산을 억제하도록 유효 어닐링 시간이 매우 짧을 수 있지만, 그럼에도 도편트 활성화와 임플란트-유도된 손상의 재결정화를 제공할 수 있는 레이저-기반의(laser-based) 기법들, 플래쉬-라이트(flash-light) 어닐링 공정들과 같은 확립된 어닐링 공정들을 이용함으로써 상당한 도편트 확산이 억제될 수 있다.

[0044] 그 후에, 예를 들어 드레인 및 소오스 영역들(254)에 그리고 게이트 전극 구조(251)에 금속 실리사이드 영역들을 형성함으로써 추가 처리가 속행될 수 있고, 필요하다면 임의의 적절한 충간 유전체 물질의 증착이 뒤따를 수 있으며, 이 유전체 물질은 또한 트랜지스터(250) 및/또는 트랜지스터(250B)의 성능을 더 향상시키도록 높은 내부 스트레스 레벨들의 유전체 물질을 포함할 수 있다.

[0045] 결과적으로, 본 개시는 반도체 디바이스들과 해당 제조 기법들을 제공하며, 점진적으로 만들어진 형태의 스트레인 유도 반도체 물질이 2개의 서로 다른 스페이서 소자들을 제공하는 것을 포함하는 패터닝 시퀀스를 기반으로 제공될 수 있고, 그럼으로써 향상된 전반적인 공정 균일도를 제공할 수 있으며, 이는 결국 전반적인 트랜지스터 변동성을 지나치게 감소시키지 않고 스트레인-유도 물질을 채널 영역에 매우 가까이 위치시키는 것을 가능하게 할 수 있다.

[0046] 본 설명에 비추어 본 개시의 추가적인 수정 및 변경들은 당해 기술분야의 기술자들에게 자명할 것이다. 따라서, 본 설명은 단지 예시적인 것으로 이해되어야 하고 당해 기술분야의 기술자들에게 본 개시를 실시하는 일반적인 방법을 교시하는 목적으로 이해되어야 한다. 본 명세서에서 도시되고 설명된 형태들은 현재 바람직한 실시예들로서 받아들여져야 한다는 것을 이해하여야 한다.

## 도면

## 도면 1a

## 도면 1b

도면1c

선행 기술

도면1d

선행 기술

## 도면1e

선행 기술

## 도면2a

도면2b

도면2c

도면2d

도면2e

도면2f

도면2g

도면2h

도면2i

도면2j

도면2k

도면21

도면22