(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6612885号

(P6612885)

(45) 発行日 令和1年11月27日(2019.11.27)

(24) 登録日 令和1年11月8日(2019.11.8)

|              |                           |

|--------------|---------------------------|

| (51) Int.Cl. | F 1                       |

| H04L 7/00    | (2006.01) H04L 7/00 370   |

| G06F 13/38   | (2006.01) G06F 13/38 350  |

| G06F 13/42   | (2006.01) G06F 13/42 350A |

|              | HO4L 7/00 140             |

請求項の数 15 (全 61 頁)

(21) 出願番号 特願2017-540862 (P2017-540862)

(86) (22) 出願日 平成28年1月26日 (2016.1.26)

(65) 公表番号 特表2018-506232 (P2018-506232A)

(43) 公表日 平成30年3月1日 (2018.3.1)

(86) 國際出願番号 PCT/US2016/014977

(87) 國際公開番号 WO2016/126466

(87) 國際公開日 平成28年8月11日 (2016.8.11)

審査請求日 平成31年1月8日 (2019.1.8)

(31) 優先権主張番号 14/616,572

(32) 優先日 平成27年2月6日 (2015.2.6)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 仙石 祥一郎

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

審査官 阿部 弘

最終頁に続く

(54) 【発明の名称】シリアルバスのための受信クロック較正

## (57) 【特許請求の範囲】

## 【請求項 1】

マスタデバイス上で動作する方法であって、シリアルバスのシリアルクロックライン(SCLライン)上にクロック信号を供給するステップであって、前記クロック信号が、前記シリアルバスのシリアルデータライン(SDAライン)上のデータ送信を制御する、ステップと、

スレーブデバイスが前記SDAライン上でデータを送信しているとき、前記SCLライン上の遷移から受信クロックを生成するステップと、

前記SCLライン上に供給される前記クロック信号のエッジと、前記クロック信号の前記エッジに応答してスレーブデバイスによって前記SDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正するステップと、

前記受信クロックに前記遅延を加えることによってSDAクロックを供給するステップと、

前記SDAクロックを使用して前記SDAラインからデータを受信するステップと、を備え、

少なくとも1つの時間期間の中で、前記SCLライン上に供給される前記クロック信号が、前記SDAライン上のダブルデータレート送信を制御する、方法。

## 【請求項 2】

前記受信クロックを生成するステップが、

10

20

第1の動作モードにおいて、前記SDAライン上または前記SCLライン上のシグナリング状態における遷移から第1の受信クロックを生成するステップと、

第2の動作モードの間、前記SDAラインをマスクするステップと、

第2の動作モードにおいて、前記SCLライン上のシグナリング状態における遷移から第2の受信クロックを生成するステップと、

を備える、請求項1に記載の方法。

【請求項3】

前記SDAクロックが、前記第2の受信クロックから生成される、

請求項2に記載の方法。

【請求項4】

前記受信クロックを生成するためにクロックおよびデータ復元回路を使用するステップをさらに備える、請求項1に記載の方法。

【請求項5】

前記シリアルバス上の送信が、集積回路間(I2C)動作モードと互換性がある、

請求項1に記載の方法。

【請求項6】

第1の時間期間の間、前記シリアルバスに結合されたI2CスレーブデバイスとI2Cプロトコルに従って通信するステップをさらに備え、

前記SCLライン上に供給される前記クロック信号が前記SDAライン上のダブルデータレート送信を制御するとき、前記SCLライン上に供給される前記クロック信号が、第2の時間期間の間、前記I2Cスレーブデバイスによって無視される、

請求項1に記載の方法。

【請求項7】

第1の時間期間の間、I2Cスレーブデバイスと通信するステップと、

第2の時間期間の間、I2Cスレーブデバイス以外のスレーブデバイスと通信するステップと、

をさらに備え、

前記第2の時間期間の間、ダブルデータレートクロック信号が前記SCLライン上で送信される、

請求項1に記載の方法。

【請求項8】

シリアルデータリンクに結合されたとき、マスタデバイスとして機能するように構成された装置であって、

シリアルバスのシリアルクロックライン(SCLライン)上にクロック信号を供給するための手段であって、前記クロック信号が、前記シリアルバスのシリアルデータリンク(SDAライン)上のデータ送信を制御する、手段と、

スレーブデバイスが前記SDAライン上でデータを送信しているとき、前記SCLライン上の遷移から受信クロックを生成するための手段と、

前記SCLライン上に供給される前記クロック信号のエッジと、前記クロック信号の前記エッジに応答してスレーブデバイスによって前記SDAライン上に生成される少なくとも1つの遷移との間に測定される期間に基づいて、遅延を較正するための手段と、

前記受信クロックに前記遅延を加えることによってSDAクロックを供給するための手段と、

前記SDAクロックを使用して前記SDAラインからデータを受信するための手段と、を備え、

少なくとも1つの時間期間の中で、前記SCLライン上に供給される前記クロック信号が、前記SDAライン上のダブルデータレート送信を制御する、

装置。

【請求項9】

前記供給するための手段が、前記シリアルデータリンクのシリアルクロックライン(SCL

10

20

30

40

50

ライン)上で第1のクロック信号を送信するように構成された送信回路であって、前記第1のクロック信号が、前記シリアルデータリンクのシリアルデータライン(SDAライン)上のデータ送信を制御する、送信回路を備え、

生成するための手段が、前記スレーブデバイスが前記SDAライン上でデータを送信しているとき、前記クロック信号の遷移から第2のクロックを生成するように構成されたクロック生成回路を備え、

較正するための手段が、

前記第1のクロック信号のエッジと、前記第1のクロック信号の前記エッジに応答して前記スレーブデバイスによって前記SDAライン上に生成される前記少なくとも1つの遷移との間で測定される前記期間に基づいて、前記遅延を較正し、

10

前記第2のクロックに前記遅延を加えることによって第3のクロックを供給する、

ように構成された較正論理を備え、

受信回路が前記第3のクロックを使用して前記SDAラインからデータを受信するように構成され、

前記少なくとも1つの時間期間の中で、前記第1のクロック信号が、前記SDAライン上のダブルデータレート送信を制御する、

請求項8に記載の装置。

#### 【請求項10】

前記第1のクロック信号が、クロックパルスの列を備え、

クロックパルスの前記列の中の各パルスが、第1の動作モードにおいて、しきい値持続時間を越える持続時間を伴うハイ状態を有し、

20

クロックパルスの前記列の中の各パルスが、第2の動作モードにおいて、前記しきい値持続時間よりも短い持続時間を伴うハイ状態を有し、

前記第1の動作モードにおいて、前記スレーブデバイスが、前記シリアルデータリンクを介してI2Cプロトコルに従って通信するように構成され、

前記第2の動作モードにおいて、前記第1のクロック信号が、前記スレーブデバイスによって無視される、

請求項9に記載の装置。

#### 【請求項11】

前記しきい値持続時間が50ナノ秒である、

30

請求項10に記載の装置。

#### 【請求項12】

スレーブデバイス上で動作する方法であって、

シリアルバスのシリアルクロックライン(SCLライン)からクロック信号を受信するステップであって、前記クロック信号が、マスタデバイスによって生成され、前記シリアルバスのシリアルデータライン(SDAライン)上のデータ送信を制御する、ステップと、

ピアなスレーブデバイスが前記SDAライン上でデータを送信しているとき、前記SCLライン上の遷移から受信クロックを生成するステップと、

前記SCLライン上に供給される前記クロック信号のエッジと、前記クロック信号の前記エッジに応答してスレーブデバイスによって前記SDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正するステップと、

40

前記受信クロックに前記遅延を加えることによってSDAクロックを供給するステップと、

前記SDAクロックを使用して前記SDAラインからデータを受信するステップと、を備え、

少なくとも1つの時間期間の中で、前記SCLライン上に供給される前記クロック信号が、前記SDAライン上のダブルデータレート送信を制御する、

方法。

#### 【請求項13】

前記受信クロックを生成するステップが、

50

ダブルデータレートにおけるピアツーピア転送の間、前記SDAラインをマスクするステップ

を備える、請求項12に記載の方法。

**【請求項14】**

前記受信クロックを生成するためにクロックおよびデータ復元回路を使用するステップをさらに備える、請求項12に記載の方法。

**【請求項15】**

前記シリアルバス上の送信が、集積回路間(I2C)動作モードと互換性がある、請求項12に記載の方法。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

関連出願の相互参照

本出願は、内容全体が参照により本明細書に組み込まれる、2015年2月6日に米国特許商標庁に出願された米国非仮特許出願第14/616,572号の優先権および利益を主張する。

**【0002】**

本開示は、専用の割込みラインまたはピンの必要なしに、共有制御データバスを介したインバンド割込み動作を可能にすることに関する。

**【背景技術】**

**【0003】**

20

I2CバスまたはI<sup>2</sup>Cバスと呼ばれる場合もある集積回路間シリアルバスは、低速周辺装置をプロセッサに接続する際に使用することを意図していたシリアルシングルエンドコンピュータバスである。I2Cバスは、I2Cバス上で送信される様々なメッセージに対して、各デバイスがマスタおよびスレーブとして働くことができるマルチマスタバスである。I2Cバスは、シリアルデータライン(SDA)およびシリアルクロックライン(SCL)を含む2つの双方向オープンドレインコネクタのみを使用して、データを送信することができる。それらのコネクタは通常、プルアップ抵抗器によって終端される信号線を含む。

**【0004】**

I2Cバスの動作を管理するプロトコルは、メッセージの基本タイプを規定し、それらのメッセージはそれぞれSTARTで開始し、STOPで終了する。I2Cバスは7ビットアドレス指定を使用し、2つのタイプのノードを規定する。マスタノードは、クロックを生成し、スレーブノードとの通信を開始するノードである。スレーブノードは、クロックを受信し、マスターによってアドレス指定されたときに応答するノードである。I2Cバスはマルチマスタバスであり、それは、任意の数のマスタノードが存在できることを意味する。さらに、マスタとスレーブの役割は、メッセージ間で(すなわち、STOPが送られた後)変更される場合がある。

30

**【0005】**

カメラ実装のこの文脈では、センサーから画像を取り込み、そのような画像データをベースバンドプロセッサの中のメモリに送信するために単方向送信が使用されてもよく、一方、ベースバンドプロセッサと、センサーならびに他の周辺デバイスとの間で制御データが交換されてもよい。一例では、ベースバンドプロセッサとイメージセンサー(および/または1つもしくは複数のスレーブノード)との間のそのような制御データのために、カメラ制御インターフェース(CCI)プロトコルが使用される場合がある。一例では、CCIプロトコルは、イメージセンサーとベースバンドプロセッサとの間のI2Cシリアルバスを介して実施されてもよい。I2Cバスを介したスループットを拡張するために、CCI拡張(CCIe)プロトコルが規定された。

40

**【0006】**

CCIEプロトコル内では、スレーブノードがバスを使用することを望むことを、スレーブノードがマスタノードに示すことを可能にするために、割込みが使用される。スレーブノードがそのような割込みをマスタノードに送ることを可能にするための機構が必要である

50

。従来のI2Cシステム、すなわちカメラ制御インターフェースベースのカメラシステムは、スレーブデバイスごとに別個の割込み(IRQ)ラインを使用し、それらの割込みラインが、多数のピンに起因してデバイスのコストを増大させる。スレーブノードごとに別個の割込みピンという概念は、各スレーブデバイスが個々の専用割込みピンを有しなければならないことを意味する。

#### 【0007】

したがって、CCl実装に関して、バスを共有するマスタノードおよびスレーブノードにおける専用割込みピンの使用を排除することが望ましいことになる。

#### 【発明の概要】

#### 【課題を解決するための手段】

10

#### 【0008】

以下のものは、そのような態様の基本的な理解を与えるために、本開示の1つまたは複数の態様の簡単な概要を提示する。本概要は、本開示の考えられるすべての特徴の広い概説ではなく、本開示の全態様の鍵となる要素または不可欠な要素を特定することも、本開示の任意またはすべての態様の範囲を正確に説明することも意図していない。その唯一の目的は、後に示されるより詳細な説明の前置きとして、本開示の1つまたは複数の態様のいくつかの概念を簡単な形で提示することである。

#### 【0009】

様々な態様では、マスタデバイス上で動作する方法は、シリアルバスのSCLライン上にクロック信号を供給することと、スレーブデバイスがSDAライン上でデータを送信しているとき、SCLライン上の遷移から受信クロックを生成することと、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正することと、受信クロックに遅延を加えることによってSDAクロックを供給することと、SDAクロックを使用してSDAラインからデータを受信することとを含む。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御し得る。

20

#### 【0010】

一態様では、受信クロックを生成することは、第1の動作モードにおいて、SDA上またはSCL上のシグナリング状態における遷移から第1の受信クロックを生成することと、第2の動作モードの間、SDAをマスクすることと、第2の動作モードにおいて、SCL上のシグナリング状態における遷移から第2の受信クロックを生成することとを含む。SDAクロックは、第2の受信クロックから生成され得る。

30

#### 【0011】

一態様では、受信クロックを生成するためにクロックおよびデータ復元回路が使用され得る。

#### 【0012】

一態様では、シリアルバス上の送信は、I2C動作モードと互換性がある。

#### 【0013】

一態様では、SCLライン上に供給されるクロック信号は、SDAライン上のダブルデータレート送信を制御する。SCLライン上に供給されるクロック信号がSDAライン上のダブルデータレート送信を制御するとき、SCLライン上に供給されるクロック信号は、シリアルバスに結合された1つまたは複数のI2Cスレーブデバイスによって無視され得る。マスタデバイスは、第1の時間期間の間、I2Cスレーブデバイスと通信し得、第2の時間期間の間、I2Cスレーブデバイス以外のスレーブデバイスと通信し得、ここで、第2の時間期間の間、ダブルデータレートクロック信号がSCLライン上で送信される。

40

#### 【0014】

様々な態様では、シリアルデータリンクに結合されたとき、マスタデバイスとして機能するように構成された装置は、シリアルデータリンクのSCLライン上で第1のクロック信号を送信するように構成された送信回路と、スレーブデバイスがSDAライン上でデータを送信しているとき、クロック信号の遷移から第2のクロックを生成するように構成されたク

50

ロック生成回路と、第1のクロック信号のエッジと、第1のクロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正し、第2のクロックに遅延を加えることによって第3のクロックを供給するように構成された較正論理と、第3のクロックを使用してSDAラインからデータを受信するように構成された受信回路とを含む。第1のクロック信号は、シリアルデータリンクのSDAライン上のデータ送信を制御するために使用され得る。

#### 【0015】

様々な態様では、シリアルデータリンクに結合されたとき、マスタデバイスとして機能するように構成された装置は、シリアルバスのSCLライン上にクロック信号を供給するための手段と、スレーブデバイスがSDAライン上でデータを送信しているとき、SCLライン上の遷移から受信クロックを生成するための手段と、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正するための手段と、受信クロックに遅延を加えることによってSDAクロックを供給するための手段と、SDAクロックを使用してSDAラインからデータを受信するための手段とを含む。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御し得る。10

#### 【0016】

様々な態様では、プロセッサ可読記憶媒体は、命令および/またはデータを記憶または保持する。記憶媒体は、一時的記憶媒体および/または非一時的記憶媒体を含み得る。命令は、処理回路の1つまたは複数のプロセッサによって実行され得る。命令は、1つまたは複数のプロセッサによって実行されるとき、処理回路に、シリアルバスのSCLライン上にクロック信号を供給することと、スレーブデバイスがSDAライン上でデータを送信しているとき、SCLライン上の遷移から受信クロックを生成することと、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正することと、受信クロックに遅延を加えることによってSDAクロックを供給することと、SDAクロックを使用してSDAラインからデータを受信することとをさせ得る。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御し得る。20

#### 【0017】

様々な態様では、スレーブデバイス上で動作する方法は、シリアルバスのSCLライン上でクロック信号を受信することと、ピアなスレーブデバイスがSDAライン上でデータを送信しているとき、SCLライン上の遷移から受信クロックを生成することと、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正することと、受信クロックに遅延を加えることによってSDAクロックを供給することと、SDAクロックを使用してSDAラインからデータを受信することとを含む。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御するために、マスタデバイスによって生成され得る。クロック信号は、SDAライン上のダブルデータレート送信を制御するように適合され得る。30

#### 【0018】

一態様では、受信クロックを生成することは、ダブルデータレートにおけるピアツーピア転送の間、SDAラインをマスクすることを含む。

#### 【0019】

一態様では、受信クロックを生成するためにクロックおよびデータ復元回路が使用され得る。

#### 【0020】

一態様では、シリアルバス上の送信は、I2C動作モードと互換性がある。

#### 【0021】

様々な態様では、スレーブデバイスは、シリアルバスのSCLライン上でクロック信号を受信するように構成された第1のレシーバと、ピアなスレーブデバイスがSDAライン上でデ50

ータを送信しているとき、SCLライン上の遷移から受信クロックを生成するように構成されたクロック生成回路と、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正し、受信クロックに遅延を加えることによってSDAクロックを生成するように構成された較正論理および/または回路と、SDAクロックを使用してSDAラインからデータを受信するように構成された第2のレシーバとを含み得る。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御するために、マスタデバイスによって生成され得る。クロック信号は、SDAライン上のダブルデータレート送信を制御するように適合され得る。

## 【0022】

10

様々な態様では、装置は、シリアルバスのSCLライン上でクロック信号を受信するための手段と、ピアなスレーブデバイスがSDAライン上でデータを送信しているとき、SCLライン上の遷移から受信クロックを生成するための手段と、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正するための手段と、受信クロックに遅延を加えることによってSDAクロックを供給するための手段と、SDAクロックを使用してSDAラインからデータを受信するための手段とを含む。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御するために、マスタデバイスによって生成され得る。クロック信号は、SDAライン上のダブルデータレート送信を制御するように適合され得る。

## 【0023】

20

様々な態様では、プロセッサ可読記憶媒体は、命令および/またはデータを記憶または保持する。記憶媒体は、一時的記憶媒体および/または非一時的記憶媒体を含み得る。命令は、処理回路の1つまたは複数のプロセッサによって実行され得る。命令は、1つまたは複数のプロセッサによって実行されるとき、処理回路に、シリアルバスのSCLライン上でクロック信号を受信することと、ピアなスレーブデバイスがSDAライン上でデータを送信しているとき、SCLライン上の遷移から受信クロックを生成することと、SCLライン上に供給されるクロック信号のエッジと、クロック信号のエッジに応答してスレーブデバイスによってSDAライン上に生成される少なくとも1つの遷移との間で測定される期間に基づいて、遅延を較正することと、受信クロックに遅延を加えることによってSDAクロックを供給することと、SDAクロックを使用してSDAラインからデータを受信することとさせ得る。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御するために、マスタデバイスによって生成され得る。クロック信号は、SDAライン上のダブルデータレート送信を制御するように適合され得る。

## 【0024】

30

様々な特徴、性質、および利点は、同様の参照符号が全体にわたって対応して識別する図面と併せて読まれたとき、以下に記載する詳細な説明から明らかになる場合がある。

## 【図面の簡単な説明】

## 【0025】

40

【図1】複数の利用可能な規格のうちの1つに従って選択的に動作する集積回路デバイス間のデータリンクを採用する装置を示す図である。

【図2】ベースバンドプロセッサおよびイメージセンサーを有し、画像データバスおよび制御データバスを実装するデバイスを示すブロック図である。

【図3】本明細書で開示するいくつかの態様による、ICデバイス間のデータリンクを採用する装置のための簡略化されたシステムアーキテクチャを示す図である。

【図4】本明細書で開示するいくつかの態様による、複数のスレーブデバイスおよび1つまたは複数のマスタデバイスによって、単線IRQバスをいかに共有することができるかを示すブロック図である。

【図5】本明細書で開示するいくつかの態様による、異なるグループに割り当てるができるか、または関連付けることができる異なるIRQ信号の例を示す図である。

50

【図6】本明細書で開示するいくつかの態様による、マスタデバイスによる、IRQ信号に関する監視、およびIRQアサート中スレーブデバイスの識別を示す図である。

【図7】本明細書で開示するいくつかの態様による、共有単線IRQバス上のIRQの同時アサーションを回避することができる第1の技法を示す図である。

【図8】本明細書で開示するいくつかの態様による、共有単線IRQバス上のIRQの同時アサーションを処理することができる第2の技法を示す図である。

【図9】最短IRQ信号長に関連したタイミングを示す図である。

【図10】本明細書で開示するいくつかの態様による、インバンド割込みのために構成され得る複数のスレーブデバイスを示すブロック図である。

【図11】I2Cの1バイト書き込みデータ動作を示すタイミング図である。 10

【図12】CCleプロトコルによるシリアルバス上のデータ送信の一例を示すタイミングチャートである。

【図13】衝突の潜在的な発生を示すタイミング図である。

【図14】図13に示す衝突を回避するための技法を示すタイミング図である。

【図15】インバンドIRQが使用されるときの付加的または誤ったクロックパルスの潜在的な発生を示すタイミング図である。

【図16】本明細書で開示するいくつかの態様による、付加的または誤ったクロックパルスの抑制を示すタイミング図である。

【図17】本明細書で開示するいくつかの態様による、I2CモードとCCleモードの両方をサポートしながらインバンドIRQ期間を実施することの1つの手法を示す図である。 20

【図18】CCleモードにある間にインバンドIRQが発行される一例を示す図である。

【図19】トランスクードされたシンボル内にクロック信号を埋め込むために、トランスマッタにおいてデータビットをトランスクードされたシンボルにトランスクードするための方法の一例を示す図である。

【図20】CCle送信におけるビット19の符号化の一例を示す図である。

【図21】ビット19が様々な数にわたり得る一例を示す図である。

【図22】本明細書で開示するようなハートビートを定義するために使用され得るビット19の数空間内の範囲を示す図である。

【図23】本明細書で開示するいくつかの態様による、ハートビートクロックを示す図である。 30

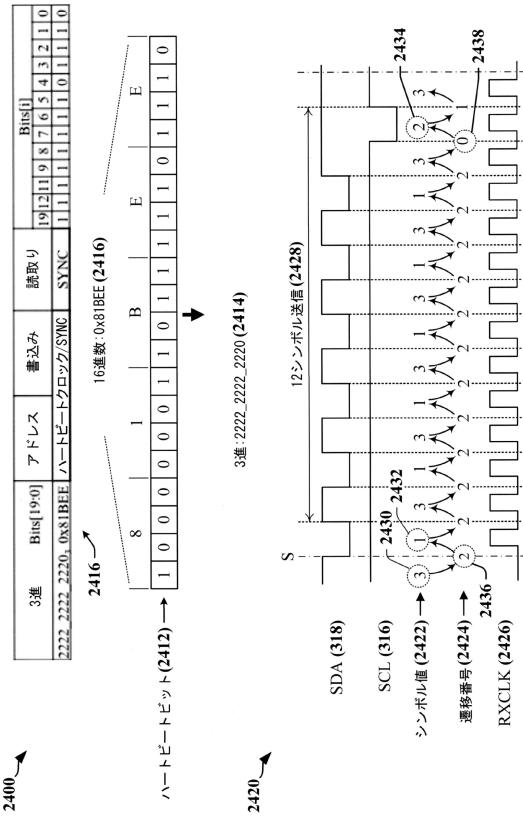

【図24】本明細書で開示するいくつかの態様による、CCleプロトコルに従って、かつCCleデバイスがハートビートクロックを取得することを可能にする方法で送信され得る、制御ワードの一例を示す図である。

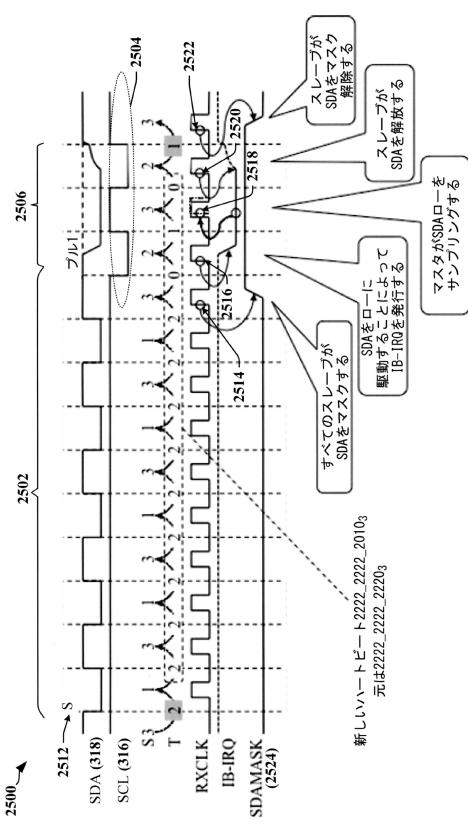

【図25】ハートビートクロックがCCleバスのSDAラインを介して送信される一例を示す図である。

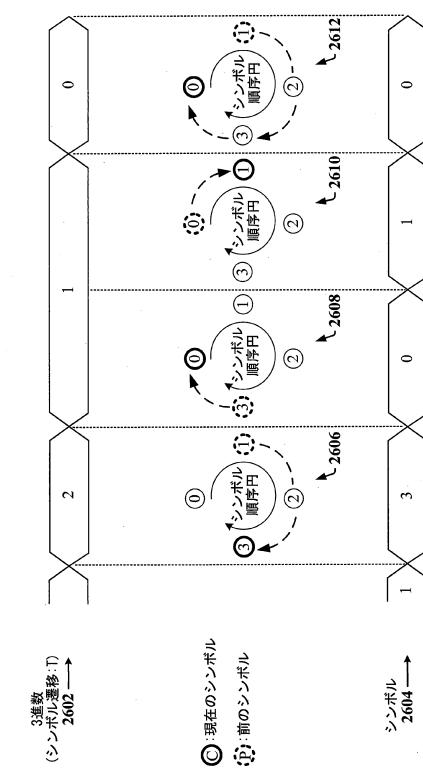

【図26】本明細書で開示するいくつかの態様による、3進遷移番号と連続シンボルとの間で変換するための方式を示す図である。

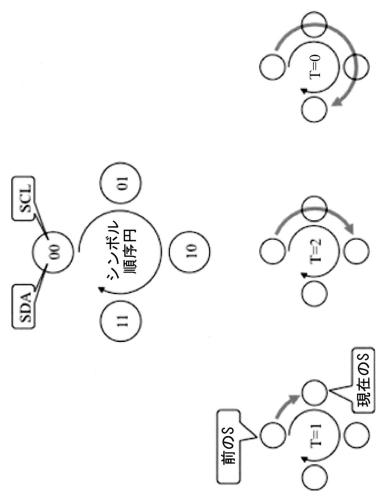

【図27】遷移番号をシンボル番号に変換するための技法の一例を示す図である。

【図28】図27に示す符号化技法のいくつかの態様を示す図である。

【図29】インバンドIRQ期間の間にSDAマスクがアサートされるときに起こり得るいくつかの条件を示す図である。 40

【図30】SDAマスクを使用することの副作用を示す図である。

【図31】インバンドIRQのためにハートビートクロックを使用することに関するいくつかの態様を示す図である。

【図32】CCleモード送信をマッピングするために、図31に示す3進数としてのビット19を使用することの一例を示す図である。

【図33】本明細書で開示するいくつかの態様による、CCleモードで動作する、または動作可能な制御データバス330上でインバンドIRQを実施するための技法を示す図である。

【図34】本明細書で開示するいくつかの態様による、CCleモードで動作する、または動作可能な制御データバス330上でインバンドIRQを実施するための技法を示す図である。 50

【図35】SDAマスクが採用されるときに起こり得るエイリアシング条件を示す図である。

【図36】本明細書で開示するいくつかの態様による、インバンドIRQの間に供給されるハートビートクロックに関するいくつかの態様を示す図である。

【図37】マスタデバイスがアクティブモードまたは節電モードにあるとき、ハートビートがそれによって送信され得る方法を示す図である。

【図38】本明細書で開示するいくつかの態様による、同期ワードとハートビートワードの組合せを示す図である。

【図39】本明細書で開示するいくつかの態様による、CCIEプロトコルのビット19内での同期およびハートビートマッピングの一例を示す図である。 10

【図40】本明細書で開示するいくつかの態様による、マスタデバイスによって制御データバスを介してスレーブデバイスへ発行され得る「SID Scan All」コマンドの一例を示す図である。

【図41】本明細書で開示するいくつかの態様による、マスタデバイスから受信されたSID Scan Allコマンドへの、スレーブデバイスの応答のタイミングを示す図である。

【図42】本明細書で開示するいくつかの態様による、CCIEプロトコルによって使用され得る可能なSID scan応答ワードを示す図である。

【図43】CCIEプロトコルの一例内での、また本明細書で開示するいくつかの態様による、割込みグループ照会呼出しを示す図である。

【図44】図43に示す割込みグループ照会呼出しのための終止ワードの一例を示す図である。 20

【図45】本明細書で開示するいくつかの態様による、グループ照会呼出しへの応答の一例を示す図である。

【図46】本明細書で開示するいくつかの態様による、DDRグローバルクロック読取りの実装形態の一例を示す図である。

【図47】本明細書で開示するいくつかの態様による、DDRグローバルクロック読取りワードに関連したタイミングを示す図である。

【図48】高スループットインターフェースにおけるタイミングを示す図である。

【図49】SCLワイヤ上およびSDAワイヤ上の信号が書き込み動作の間に位置合わせされるインターフェースを示すタイミング図である。 30

【図50】SCLワイヤ上およびSDAワイヤ上の信号が読み取り動作の間に位置合わせされないインターフェースを示すタイミング図である。

【図51】本明細書で開示するいくつかの態様による、高速シリアルインターフェースに対して較正済み遅延を使用する効果を示す図である。

【図52】本明細書で開示するいくつかの態様に従って適合され得るCDR回路を示す図である。

【図53】本明細書で開示するいくつかの態様に従って使用される、クロック信号の位置合わせのために使用される較正済み遅延回路を示す図である。

【図54】図53の較正済み遅延回路に関連するタイミングを示す図である。

【図55】本明細書で開示するいくつかの態様による、スレーブデバイスが較正済み受信クロックを使用し得るピアツーピアDDRデータ転送を示す図である。 40

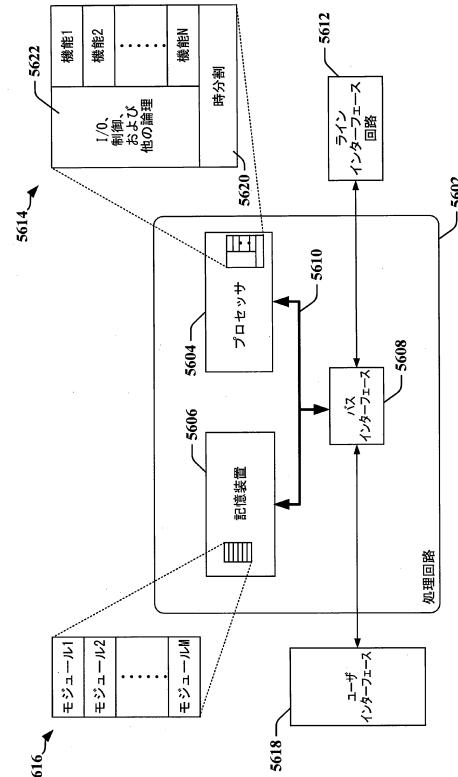

【図56】本明細書で開示するいくつかの態様に従って適合され得る処理回路を採用する装置の一例を示すブロック図である。

【図57】本明細書で開示するいくつかの態様による方法の第1の例のフローチャートである。

【図58】本明細書で開示するいくつかの態様による方法の第2の例のフローチャートである。

【図59】共有IRQバス上でIRQを処理するように適合された装置のためのハードウェア実装形態の一例を示す図である。

【図60】本明細書で開示するいくつかの態様による方法の第3の例のフローチャートで 50

ある。

【図61】本明細書で開示するいくつかの態様による方法の第4の例のフローチャートである。

【図62】受信クロック信号を較正するように適合された装置のためのハードウェア実装形態の一例を示す図である。

**【発明を実施するための形態】**

**【0026】**

以下の説明では、実施形態の完全な理解をもたらすために、具体的な詳細が与えられる。しかしながら、実施形態がこれらの具体的な詳細なしに実施されてもよいことが、当業者によって理解されよう。たとえば、不要な詳細で実施形態を不明瞭にしないために、回路がブロック図で示される場合がある。他の事例では、よく知られている回路、構造、および技法は、実施形態を不明瞭にしないために、詳細に示されない場合がある。10

**【0027】**

本明細書で開示するいくつかの実施形態は、共通I2Cバスを使用して従来のI2Cバス動作と拡張型通信インターフェースの両方をサポートするシリアルバスを使用する、通信インターフェースの性能を改善することができるシステム、方法および装置を提供する。一例では、カメラ制御インターフェース(CCI)は、I2Cバスに基づいてよく、マスターと1つまたは複数のスレーブとを接続するバスとして構成される、2ワイヤ、双方向、半二重のシリアルインターフェースを使用して配備され得る。CCI動作は、I2Cバス動作と互換性があつてよい。いくつかの態様によれば、I2CバスまたはCCIバスに接続される複数の周辺デバイスをサポートするために必要とされるIRQラインの数を最小化するシステム、装置および方法が提供される。20

**【0028】**

**概説**

本出願で使用する「構成要素」、「モジュール」、「システム」などの用語は、限定はしないが、ハードウェア、ファームウェア、ハードウェアとソフトウェアの組合せ、ソフトウェア、または実行中のソフトウェアなどの、コンピュータ関連のエンティティを含むことを意図している。たとえば、構成要素は、限定はしないが、プロセッサ上で動作するプロセス、プロセッサ、オブジェクト、実行ファイル、実行スレッド、プログラム、および/またはコンピュータであってもよい。例として、コンピュティングデバイス上で動作するアプリケーションとコンピュティングデバイスの両方が構成要素であってもよい。1つまたは複数の構成要素は、プロセスおよび/または実行スレッド内に存在してもよく、構成要素は、1つのコンピュータに局在化され、かつ/あるいは2つ以上のコンピュータ間で分散されてもよい。加えて、これらの構成要素は、その上に記憶された様々なデータ構造を有する様々なコンピュータ可読媒体から実行することができる。構成要素は、ローカルシステム内の、分散システム内の、および/または、インターネットなどのネットワークにわたる別の構成要素と対話する1つの構成要素からのデータなどの、1つまたは複数のデータパケットを有する信号などに従うローカルプロセスおよび/またはリモートプロセスにより、信号を用いて他のシステムと通信する場合がある。30

**【0029】**

その上、「または」という用語は、排他的な「または」ではなく、むしろ包括的な「または」を意味することを意図している。すなわち、別段に規定されていない限り、または文脈から明白でない限り、「XはAまたはBを採用する」という句は、自然な包括的並べ替えのいずれかを意味することを意図している。すなわち、「XはAまたはBを採用する」という句は、以下の事例、すなわち、XはAを採用する、XはBを採用する、または、XはAとBの両方を採用する、のうちのいずれによっても満たされる。加えて、本出願および添付の特許請求の範囲で使用する冠詞「a」および「an」は、別段に規定されていない限り、または単数形を対象とすることが文脈から明らかでない限り、概して「1つまたは複数」を意味するものと解釈すべきである。40

**【0030】**

50

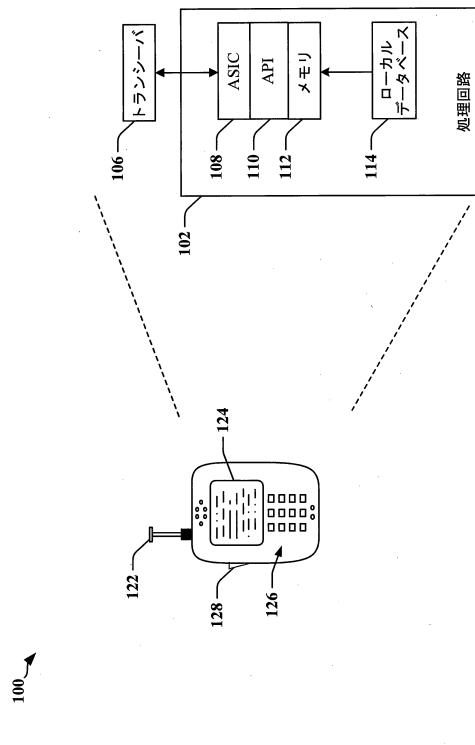

本発明のいくつかの態様は、電話、モバイルコンピューティングデバイス、アプライアンス、自動車用電子機器、アビオニクスシステムなどの、装置の下位構成要素を含み得る電子デバイス間に配備される通信リンクに適用可能であり得る。図1は、集積回路(IC)デバイス間で通信リンクを採用し得る装置を表す。一例では、装置100は、RFトランシーバを通じて、無線アクセスネットワーク(RAN)、コアアクセスネットワーク、インターネット、および/または別のネットワークと通信するワイヤレス通信デバイスを含み得る。装置100は、処理回路102に動作可能に結合される通信トランシーバ106を含み得る。処理回路102は、特定用途向けIC(ASIC)108などの1つまたは複数のICデバイスを有してよい。ASIC108は、1つまたは複数の処理デバイス、論理回路などを含み得る。処理回路102は、処理回路102によって実行され得る命令およびデータを保持し得るメモリ112などのプロセッサ可読記憶装置を含み得、かつ/またはそれに結合され得る。処理回路102は、オペレーティングシステム、および、ワイヤレスデバイスのメモリデバイス112などの記憶媒体の中には存在するソフトウェアモジュールの実行をサポートし可能にするアプリケーションプログラミングインターフェース(API)110レイヤのうちの1つまたは複数によって制御され得る。メモリデバイス112は、読み取り専用メモリ(ROM)もしくはランダムアクセスメモリ(RAM)、電気的消去可能プログラマブルROM(EEPROM)、フラッシュカード、または処理システムおよびコンピューティングプラットフォームにおいて使用され得る任意のメモリデバイスを含み得る。処理回路102は、装置100を構成し動作させるために使用される動作パラメータおよび他の情報を保持できるローカルデータベース114を含んでよく、またはそれにアクセスしてもよい。ローカルデータベース114は、データベースモジュール、フラッシュメモリ、磁気媒体、EEPROM、光媒体、テープ、ソフトディスクまたはハードディスクなどのうちの1つまたは複数を使用して実装され得る。処理回路はまた、構成要素の中でも、アンテナ122、ディスプレイ124などの外部デバイス、ボタン128および/またはキーパッド126などのオペレータ制御に、動作可能に結合され得る。

### 【0031】

#### 専用IRQラインを使用する割込み機構

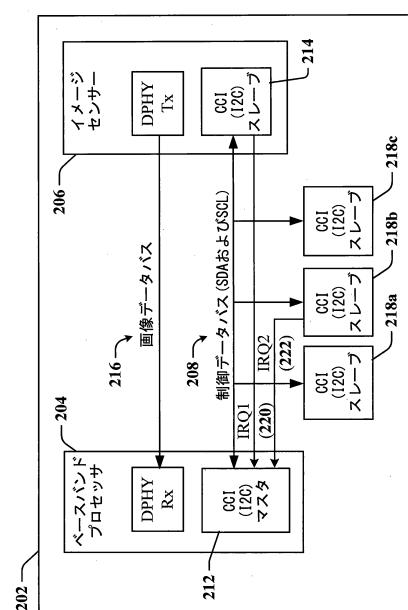

図2は、ベースバンドプロセッサ204およびイメージセンサー206を有するデバイス202の簡略化された例を示すブロック図200である。画像データバス216およびマルチモード制御データバス208は、デバイス202の中に実装され得る。図200は、単に例としてカメラデバイス202を示し、様々な他のデバイスおよび/または異なる機能が、制御データバス208を使用して、実施、動作、および/または通信し得る。図示の例では、MIPIによって規定された「DPHY」、すなわち高速差動リンクなどの画像データバス216を介して、イメージセンサー206からベースバンドプロセッサ204へ画像データが送られ得る。一例では、制御データバス208は、I2Cバスモードで動作するために構成可能である2本のワイヤを有し得る。したがって、制御データバス208は、SCLワイヤおよびSDAワイヤを含み得る。SCLは、I2Cプロトコルに従って、制御データバス208を介したデータ転送を同期させるために使用され得るクロック信号を搬送し得る。データラインSDAおよびクロックラインSCLは、制御データバス208上の複数のデバイス212、214、および218a～218cに結合され得る。この例では、制御データバス208を介して、ベースバンドプロセッサ204とイメージセンサー206との間、ならびに他の周辺デバイス218間で制御データが交換され得る。I2Cプロトコルによれば、SCLワイヤ上のクロック速度は、通常のI2C動作の場合最高100KHz、I2C高速モードの場合最高400KHz、I2C高速モードプラス(Fm+)の場合最高1MHzであり得る。I2Cバスを介したこれらの動作モードは、カメラの適用例のために使用されるとき、CCIモードと呼ばれることがある。

### 【0032】

場合によっては、2つ以上のスレーブデバイス214または218aが、対応するIRQライン220または222上で既定の論理レベルをアサートすることによって、ベースバンドプロセッサ204のアテンションを要求し得る。

### 【0033】

IRQラインを低減するための共通IRQバスの使用を示す第1の例

10

20

30

40

50

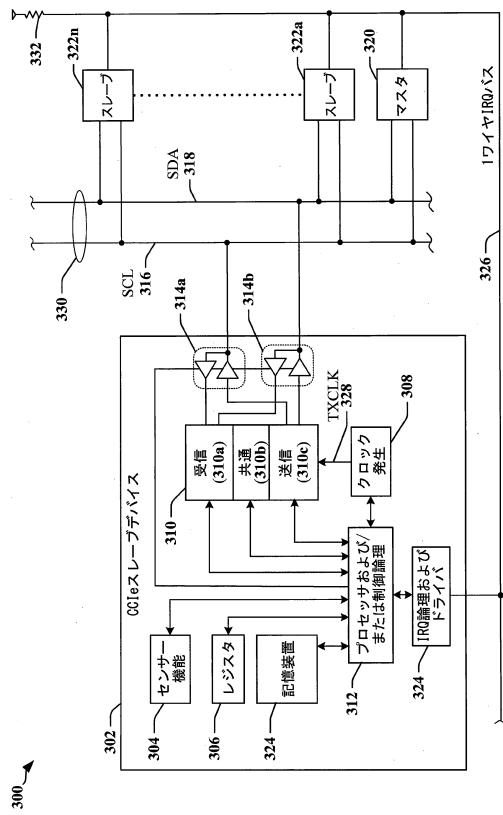

図3は、CCleバス330などの通信バスを採用し得る装置300のいくつかの態様を示すプロック概略図である。装置300は、ワイヤレスモバイルデバイス、携帯電話、モバイルコンピューティングシステム、ワイヤレス電話、ノートブックコンピュータ、タブレットコンピューティングデバイス、メディアプレーヤ、ゲーミングデバイスなどのうちの1つまたは複数において実施され得る。装置300は、CCleバス330を使用して通信する複数のCCleデバイス302、320、および/または322a～322nを含み得る。CCleバス330は、CCleバス330によってサポートされる強化された機能のために構成されているデバイス用に、従来のCCIバスの能力を拡張することができる。たとえば、CCleバス330は、CCIバス330よりも高いビットレートをサポートし得る。本明細書で開示するいくつかの態様によれば、CCleバス330のいくつかのバージョンは、16.7Mbps以上のビットレートをサポートするように構成または適合されてよく、CCleバスのいくつかのバージョンは、少なくとも23メガビット毎秒のデータレートをサポートするように構成または適合されてよい。

#### 【0034】

図3に示す例では、イメージングデバイス302は、CCleバス330上でスレーブデバイスとして動作するように構成される。イメージングデバイス302は、たとえば、イメージセンサーを管理するセンサー制御機能304を提供するように適合されてよい。さらに、イメージングデバイス302は、構成レジスタ306および/または他の記憶デバイス324、処理回路および/または制御ロジック312、トランシーバ310、ならびにラインドライバ/レシーバ314aおよび314bを含み得る。処理回路および/または制御ロジック312は、スタートマシン、シーケンサ、信号プロセッサ、または汎用プロセッサなどのプロセッサを含み得る。トランシーバ310は、レシーバ310aと、トランスミッタ310cと、タイミング、論理、および記憶回路および/またはデバイスを含むいくつかの共通回路310bとを含み得る。場合によっては、トランシーバ310は、エンコーダおよびデコーダ、クロックおよびデータ復元回路などを含むことがある。

#### 【0035】

送信クロック(TXCLK)信号328がトランスミッタ310cに供給されてよく、その場合、TXCLK信号328は、CCle通信モード用のデータ送信レートを決定するために使用され得る。SDAワイヤ318とSCLワイヤ316の両方が送信データを符号化するために使用されるとき、TXCLK信号328は、CCleバス330上で送信されるシンボルのシーケンス内に埋め込まれてよい。一例では、TXCLK信号328は、遷移クロックのトランスコーディングを使用して埋め込まれてよく、それにおいて、CCleバス330上で送信される連続するシンボルの各ペア間で少なくとも1つのワイヤ316および/または318の状態の変化が起きるように、物理リンク330を介して送信されるべきデータがトランスクードされる。

#### 【0036】

CCleデバイス302、320および/または322a～322nは、CCleバス330の2つのワイヤ316、318を使用して通信し得る。たとえば、2ワイヤCCleバス330は、I2CまたはCCI動作モードによってサポートされるデータレートよりも著しく速いデータレートをもたらすことができる、CCle双方向半二重通信モードをサポートし得る。CCleデバイス302、320、および/または322a～322nは、制御データバス330としてのSCLワイヤ316とSDAワイヤ318の両方の上でデータを送信し得、2ワイヤ制御データバス330上で送信されるシンボルのシーケンスの中にクロック情報が埋め込まれる。いくつかのCCleデバイス320は、バスマスターとして構成されてよく、いくつかのデバイス302、および/または322a～322nは、スレーブデバイスとして構成されてよい。CCleデバイス302、320、および/または322a～322nは、制御データバス330に結合されるI2Cデバイスおよび/またはCCIデバイスと互換性があるか、または共存することができ、その結果、I2Cデバイスが制御データバス330を監視しているときであっても、CCleデバイス302、320、および/または322a～322nは、CCleプロトコルおよびシグナリング仕様を使用して、1つまたは複数の他のCCleデバイス302、320、および/または322a～322nと通信し得る。本明細書で開示する一例は、CCleデバイスとI2C/CCIデバイスの両方が同じバス上に配備されるとき、バスに結合された複数のスレーブ302、および/または322a～322nを単一のマスタデバイス320を用いて処理することができるインターフ

10

20

30

40

50

エースを提供する。後者の例では、2つ以上のCCleデバイス302、320、および/または322a～322nは、CCleプロトコルを使用して通信し得、I2CデバイスまたはCCIデバイスとのいかなる通信トランザクションも、I2Cバスプロトコルに従って処理される。

#### 【0037】

本明細書で説明するいくつかの態様によれば、CCleデバイス302、320、および/または322a～322nは、共有割込み要求(IRQ)バス326に結合され得る。一態様によれば、共有IRQバス326は、スレーブデバイス302、および/または322a～322nに、ならびにマスタデバイス320に結合される単線であってよい。この共有IRQバス326は、アイドルのとき抵抗器332などを使用してプルアップ(たとえば、ハイにプル)されてよい。共有IRQバス326は、スレーブデバイス302、322a～322nが割込み信号をアサートするときローにプルされてよい。すなわち、各スレーブデバイス302、322a～322nは、IRQ信号をマスタデバイス320へ送ることによって、制御データバス330上で送信するためのアクセスを独立して要求し得る。10

#### 【0038】

いくつかの例では、単線IRQバス326は、マスタデバイス320または任意の他のデバイス302、322a～322nによって管理されない非同期バスであってよい。したがって、スレーブデバイス302、322a～322nは、いつでも一方的にIRQ信号をアサートすることができる。

#### 【0039】

別の例では、単線IRQバス326は、スレーブデバイスからマスタデバイスへの単方向信号送信に専用であってよい。すなわち、単線IRQバスは、IRQ信号だけのために使用されてよく、他のタイプの信号のために使用され得ない。20

#### 【0040】

一例では、制御データバス330はCCle互換バスであってよい。

#### 【0041】

別の例では、制御データバス330は、スレーブデバイス302、322a～322nとマスタデバイス320との間の双方向バスであってよい。

#### 【0042】

IRQラインを低減するための共通IRQバスの使用を示す第2の例

図4は、1つまたは複数のスレーブデバイス410、412、414、416、418が、共通の、または共有された単線IRQバス422上で既定の論理レベルをアサートすることによって、バスマスター404のアテンションを要求し得る一例を示すブロック図400である。単線IRQバス420は、I2C、CCIおよび/またはCCleデバイスを含んでよい複数のスレーブデバイス410、412、414、416、418によって共有され得る。図示の例では、スレーブデバイス410、412、414、416、418の各々は、CCle通信モードをサポートするように適合されてよく、バスマスター404は、I2C、CCIおよびCCle動作モードでのバスマスターの働きをするように適合されてよい。30

#### 【0043】

一態様によれば、共有単線IRQバス422が、スレーブデバイス410、412、414、416、418およびマスター404に結合される。スレーブデバイス410、412、414、416、418がいずれも割込み要求をアサートしていないときのIRQバス422のシグナリング状態を規定するために、プルアップ抵抗器420がIRQバス422のワイヤに結合されてよい。一例では、スレーブデバイス410、412、414、416、418は、マスター404に割り込むために、またはマスター404の割込みを要求するために、IRQバス422をローに駆動し得る。すなわち、各スレーブデバイス410、412、414、416、および418は、マスター404からのアテンションを要求するために、IRQ信号を駆動することによって割込み要求を独立してアサートしてよい。40

#### 【0044】

割込み要求をアサートした1つまたは複数のスレーブデバイス410、412、414、416、および/または418の識別情報の表示を提供するように各スレーブデバイス410、412、414、416、418を構成することによって、共通の共有単線IRQバス422は、複数のスレーブデバイス410、412、414、416、418によって共有され得る。場合によっては、スレーブデバイス450

10、412、414、416、418のうちの2つ以上が、マスタデバイス404のアテンションを求めて競合する場合があり、これらの競合しているスレーブデバイス410、412、414、416、および/または418の識別情報の表示は、マスタデバイス404のアテンションを求めるなどの要求が許可されるべきであるのかを決定するために使用され得る。一例では、各スレーブデバイス410、412、414、416、418は、IRQバス422を駆動するデバイス410、412、414、416、418の識別情報に対応する長さを有する時間期間にわたってIRQバス422を駆動することによって、割込み要求をアサートするように構成されてよい。

#### 【 0 0 4 5 】

場合によっては、IRQバス422を駆動するために使用されるパルスの長さが、マスタデバイス404からのアテンションを求めて競合しているスレーブデバイス410、412、414、416、418を含む、スレーブデバイス410、412、414、416、418のグループ406、408を識別し得る。一例では、第1の複数のスレーブデバイス410、412が第1のグループ406の中にあってよく、第2の複数のスレーブデバイス414、416が第2のグループ408の中にあってよく、そのようなグループ化は、たとえば、事前構成されてよく、または起動時にマスタデバイス404によって(たとえば、列挙(enumeration)によって)動的に規定されてもよい。そのようなグループ化によって、マスタデバイス404は、許容できない遅延を伴うことなく、どのスレーブデバイスがIRQバス422上でIRQ信号をトリガしたかを、より迅速に特定できるようになる。各スレーブデバイス410、412、414、416、または418は、スレーブデバイス410、412、414、416、または418が属するグループ406、408に対して規定された、および/または割り当てられた幅を有するパルスを生成するように構成され得る。たとえば、第1のグループ406の中のスレーブデバイス410および412は、第2のグループ408の中のスレーブデバイス414および416によって生成されるパルスの持続時間と異なる持続時間を有するパルスを、共有単線IRQバス422上に生成するように構成され得る。各グループ406および408は、少なくとも1つのスレーブデバイスを含む。

#### 【 0 0 4 6 】

IRQバス422のアサーションの持続時間が、要求しているスレーブデバイス410、412、414、416、または418がマスタデバイス404のアテンションを許可されるかどうかを決定し得る。一例では、優先順位付け方式が、優先順位が高いスレーブデバイス410、412、414、416、418に長いパルス幅を割り当て、優先順位が低いスレーブデバイス410、412、414、416、418に短いパルス幅を割り当ててよい。動作時に、第1のスレーブデバイス410、412、414、416、または418が、IRQバス422上にパルスを供給することによって割込み要求をアサートし得る。第2の、優先順位が高いスレーブデバイス410、412、414、416、または418は、第1のスレーブデバイス410、412、414、416、または418によって供給されるパルスの幅よりも長い幅を有するパルスをIRQバス422上に供給することによって、割込み要求をアサートし得る。IRQバス422がアサートされたとき、マスタデバイス404は、IRQバス422のアサーションの持続時間を使用して、アサートしているスレーブデバイス410、412、414、416を含む最も優先順位が高いグループ406もしくは408、および/またはIRQバス422をアサートしている最も優先順位が高いスレーブデバイス410、412、414、416、もしくは418を識別し得る。マスタデバイスは、次いで、制御データバス402上のシグナリングを使用して、IRQバス422上で観測されたパルス幅が割り当てられている1つまたは複数のスレーブデバイス410、412、414、416、418上のIRQステータスレジスタをスキャンし得る。

#### 【 0 0 4 7 】

場合によっては、第1のスレーブデバイス410、412、414、416、または418によって供給されるパルスの終了後にIRQバス422が能動的に駆動され続け、少なくとも第2の、より優先順位が高いスレーブデバイス410、412、414、416、または418も、より長いパルス幅を用いてIRQバス422を駆動することによってマスタデバイス404のアテンションを要求していることを示すとき、第1のスレーブデバイス410、412、414、416、または418は、第2のスレーブデバイス410、412、414、416、または418に譲る場合がある。そのような状況では、第1のスレーブデバイス410、412、414、416、または418は、制御データバス402を求めて競合する次の機会が生じるまで、アイドルモードまたは休止モードに戻ってよい。

10

20

30

40

50

**【 0 0 4 8 】**

場合によっては、単線IRQバス422は、スレーブデバイス410、412、414、416、418および1つまたは複数のマスタデバイス404によって共有されてよい。この例では、スレーブデバイス410、412、414、416、418は、論理的にグループ化され得る。たとえば、第1のグループ406は、第1の複数のスレーブデバイス410および412を含んでよく、第2のグループ408は、第2の複数のスレーブデバイス414および416を含んでよい。そのようなグループ化は、たとえば、事前構成されてよく、動的に規定されてよく、および/または初期化においてマスタデバイス404によって列挙によって規定されてもよい。グループ406、408を使用することによって、マスタデバイス404は、IRQバス422を駆動することによって割込み要求をアサートする1つまたは複数のスレーブデバイス410、412、414、416、および/または418を、より迅速に特定できるようになることがある。

10

**【 0 0 4 9 】**

場合によっては、単線IRQバスは、マスタデバイス404または別のデバイスの管理を伴わず、非同期に動作し得る。非同期動作では、スレーブデバイス410、412、414、416、または418は、いつでも一方的にIRQバス422を駆動してよい。場合によっては、スレーブデバイス410、412、414、416、418は、割込み要求をアサートする前に、IRQバス422がアイドルである(すなわち、別のデバイスによって駆動されていない)ことを確認してもよい。

**【 0 0 5 0 】**

場合によっては、単線IRQバス422は、スレーブデバイス410、412、414、416、418からマスタデバイス404への单方向信号送信に専用であってよい。すなわち、IRQバス422は、割込み要求シグナリングのために予約されてよく、他のタイプの信号はIRQバス422上でサポートされない。

20

**【 0 0 5 1 】**

スレーブデバイス410、412、414、416のグループ406、408は、別個のIRQ信号を使用するように構成されてよい。一例では、第1のグループ406は、第1の期間を有する第1の信号を使用してよく、第2のグループ408は、第2の期間を有する第2の信号を使用してよく、以下同様である。場合によっては、別のスレーブデバイスとグループ化されないスレーブデバイス418は、1つのデバイスとしてのグループとして扱われてよく、第3の期間を有する第3の信号を使用するように割り当てられてよい。IRQ信号の期間は、アサートしているスレーブデバイス410、412、414、416、または418によってIRQバス420が駆動される(たとえば、ローにプルされる)時間の長さとして規定され得る。他の形態の信号区別が使用されてよい。たとえば、スレーブデバイス410、412、414、416の異なるグループ406、408、および/またはグループに割り当てられないかまたはグループの唯一のメンバーとして別の方で扱われるスレーブデバイス418に、異なるIRQ信号電圧レベルが割り当てられてよい。

30

**【 0 0 5 2 】**

場合によっては、各グループ406、408が少なくとも1つのスレーブデバイス410、412、414、416、418を含み得るように、スレーブデバイス410、412、414、416、418の論理グループを規定してよい。グループ406、408は、複数のスレーブデバイス410、412、414、416、418を含んでよい。各グループ406、408に割り当てられるスレーブデバイス410、412、414、416、418の数は、グループ406、408の中の潜在的なアサートしている各スレーブデバイス410、412、414、416、418に照会し、それらを特定するための期間のような要因に基づいて決定され得る。たとえば、IRQバス422に結合されるすべてのスレーブデバイス410、412、414、416、418がマスタデバイス404によって照会されるとき、容認できないほど長い遅延が結果として生じる場合がある。

40

**【 0 0 5 3 】**

アサートしているスレーブデバイス410、412、414、416、418を特定するための時間は、スレーブデバイス410、412、414、416、418がIRQをアサートしたグループ406、408を特定し、次いで、特定されたグループ406または408の中の各メンバースレーブデバイス410、412、414、416、418に照会するために、別個のIRQ信号を使用することを通して著しく

50

低減され得る。マスタデバイス404は、IRQバス422のアサーションの発生を検出し得、マスタデバイス404は、アサーションの持続時間を決定し得る。IRQアサーションの決定された持続時間に基づいて、マスタデバイス404は、マスタデバイス404によって観測された長さの持続時間に対応するグループ406または408を特定し得る。マスタデバイス404は、次いで、どのスレーブデバイスがIRQ信号をトリガまたはアサートしたのかを特定するために、グループ406、408の中のスレーブデバイス410、412、414、416、418に照会し得る。一例では、マスタデバイス404は、IRQアサーションが第1のグループ406から生じたと決定し得る。マスタデバイス404は、制御データバス402を介して、第1のスレーブデバイス410または412に要求またはコマンドを送信し得る。マスタデバイス404は、たとえば、レジスタステータス要求を送信してよい。それに応答して、第1のスレーブデバイス410または412は、ステータス情報をマスタデバイス404へ送信してよい。第1のスレーブデバイス410または412がIRQ要求の発生源でないことをステータス情報が示す場合、マスタデバイス404は、制御データバス402を介して、第1のグループ406の中の第2のスレーブデバイス412または410へレジスタステータス要求を送信してよい。このプロセスは、IRQ信号をアサートしたスレーブデバイス410、412が特定されるまで、第1のグループ406の中のすべてのスレーブデバイス410、412に対して繰り返されてよい。

#### 【0054】

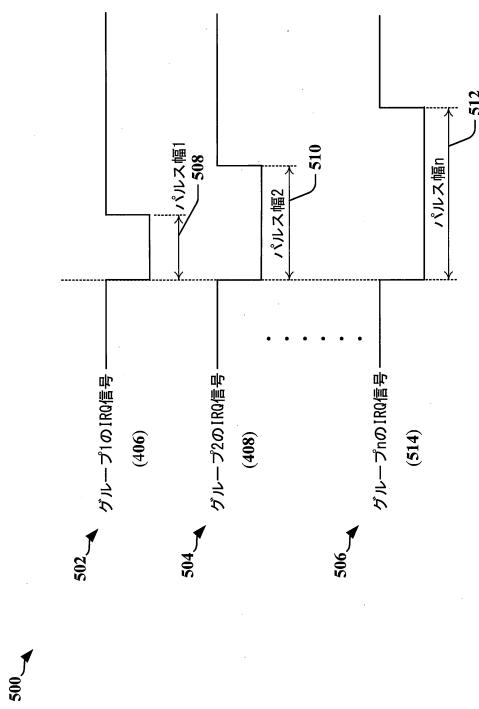

図5は、異なるグループ406、408、514によってそれぞれ使用されるIRQ信号502、504、506のタイミングの例を示すタイミング図500である。異なるIRQ信号タイミングが、異なる各グループ406、408、514に割り当てられてよく、もしくはそれらに関連付けられてよく、および/または各グループ406、408、もしくは514のメンバースレーブデバイス410、412、414、416、418のIRQ信号タイミングは、対応するグループ406、408、514に割り当てられた、もしくはそれらに関連付けられたIRQ信号タイミングに基づいてよく、もしくはそうしたIRQ信号タイミングから導出されてよい。各グループ406、408、514は、メンバースレーブデバイス410、412、414、416、418のうちの1つ、または複数のメンバーデバイス410、412、414、416、418を含んでよい。第1のグループ406は、第1のパルス幅508を有するIRQ信号502を使用してよく、第2のグループ408は、第2のパルス幅510を有するIRQ信号504を使用してよく、第nのグループ506は、第3のパルス幅512を有する第3のIRQ信号506を使用するように構成されてよい。

#### 【0055】

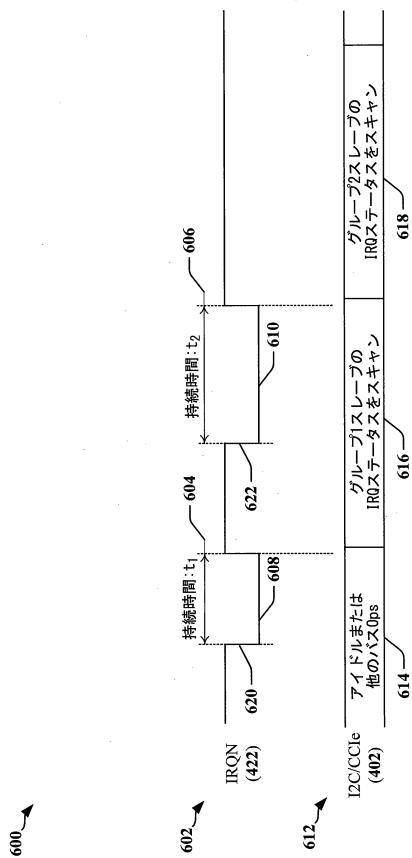

図6は、バスマスタデバイス404の観点からの共有IRQバス422の動作を示す。その例は、I2C、CClおよび/またはCCl eプロトコルに従って動作する制御データバス402上の動作のタイミング612に適用され得る。バスマスタデバイス404は、IRQバス422上の信号のタイミング602を監視して、割込み要求がアサートされたかどうかを決定し得る。バスマスタデバイス404は、IRQバス422上のパルス608、610の持続時間604、606に基づいて、割込み要求をアサートしているスレーブデバイスを特定し得る。

#### 【0056】

その例では、スレーブデバイスのグループ406、408は、既定の時間期間604、606にわたってIRQバス422を駆動するように構成され得る。したがって、バスマスタデバイス404は、パルス608および610を求めてIRQバス422を監視し得、任意の検出されたパルス608、610の持続時間604、606を測定または計時し得る。一例では、バスマスタデバイス404は、パルス608、610の開始において遷移620、622を検出すると開始されるタイマーまたはカウンタを含み得る。パルス608、610の終了後のタイマー値またはカウンタ値は、次いで、各グループ406、408に関連付けられた既定の持続時間と比較され得る。

#### 【0057】

その例では、データ制御バス402は、第1のパルス608が受信される前に、第1の時間期間614の間にアイドルであってよい。共有単線IRQバス422上で第1のIRQ信号がアサートされると、バスマスタデバイス404は、IRQバスがローにプルされたことを検出し、パルスの期間、幅、または持続時間604を決定する。たとえば、第1のパルス608の持続時間604がデバイスの第1のグループ406のメンバーからの割込み要求と一致することを、第1のパルス608

10

20

30

40

50

の終了時にバスマスタデバイス404は決定し得る。バスマスタデバイス404は、第1のデバイスグループ406のメンバーのスキャン616を開始して、それらのIRQステータスを決定するとともに第1のグループ406の1つまたは複数のどのメンバーがIRQ要求608をアサートしたかを特定し得る。一例では、バスマスタデバイス404は、各要求の受信者にIRQステータスを用いて応答させるコマンドおよび/または要求を、制御データバス402上で第1のグループ406の各メンバーへ送信し得る。バスマスタデバイス404は、第1のグループ406の特定された割り込んでいるメンバーと、データ、制御または他の情報を交換し得る。

#### 【 0 0 5 8 】

第2の割込み要求パルス610は、第1の割込み要求パルス608の後のある時点において受信され得る。第2の割込み要求パルス610は、スレーブデバイスの第2のグループ408に対応する持続時間606を有してよい。第2の割込み要求パルス610を受信すると、バスマスタデバイス404は、パルス幅、期間、または持続時間606を検出、決定または計算し得る。バスマスタデバイス404は、次いで、デバイスの第2のグループ409のメンバーのスキャン618を開始して、それらのIRQステータスを決定するとともに、第2のパルス610に対応するIRQ要求を第2のグループ408の1つまたは複数のどのメンバーがアサートしたのかを特定し得る。

#### 【 0 0 5 9 】

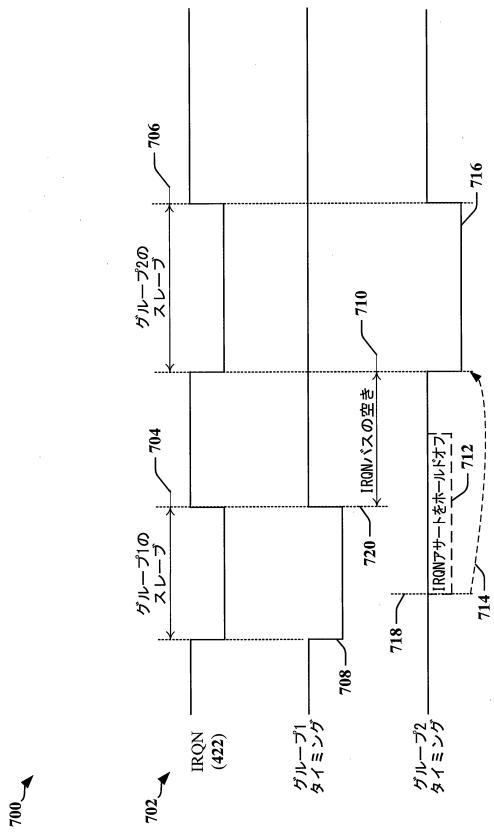

図7は、本明細書で開示するいくつかの態様による、同時の、重なり合う、および/または対立する割込み要求の発生を回避するための方法を示すタイミング図である。場合によつては、割込み要求の対立または競合につながることがある重なり合うIRQパルスの発生を回避することが望ましい場合がある。対立する割込み要求は、割込み要求をアサートする前に、IRQバス422を監視するようにスレーブデバイスを構成することによって回避され得る。別のデバイスが共有単線IRQバス422上で割込み要求708をすでにアサートしていた場合、割込み要求712は遅らせてよい(714)。

#### 【 0 0 6 0 】

図示の例では、第1のパルス704は、デバイスの第1のグループ406の中からのスレーブデバイスによって、IRQバス422上でアサートされる。第2のスレーブデバイスが、第1のパルス708の持続時間704の間に割込み要求をアサートすることを望む場合がある。一態様によれば、第2のスレーブデバイスは、IRQバス422上の割込み要求のアサーションを遅延させてよい。時間718において、第2のスレーブデバイスは、割込み要求を開始することを決定する場合がある。IRQバス422をチェックすると、第2のスレーブデバイスは、パルス708が別のスレーブデバイスによってIRQバス422上でアサートされていると決定し得る。したがって、第2のデバイスは、IRQバス422がアイドル状態に戻ることができるようするホールドオフまたは遅延期間712を始動してよい。ホールドオフ期間712は、既定の持続時間、最小バックオフ期間および/もしくはランダム遅延を含む持続時間、またはIRQバス422がアイドル状態に戻った後の既定の時間を終了する期間を有してよい。第2のスレーブデバイスは、その間はIRQバス422が空きであるかまたはアイドルである最小の時間期間710にわたって、割込み要求をアサートすることを妨げられる場合がある。IRQバス空き時間期間710は、IRQバス422上の第1のパルス708が終了し、たとえば、IRQバス422が論理ハイ状態に戻る時点720から測定されてよい。最小バス空き時間710が満了した後、次の割込み要求716がアサートされてよい。最小バス空き時間710が満了すると、第2のスレーブデバイスは、IRQバス422上にパルス716を供給することによって、割込み要求をアサートし得る。その例では、第2のスレーブデバイスはスレーブデバイスの第2のグループ408のメンバーであり、第2のパルス716の持続時間706は第1のパルス708の持続時間704とは異なる場合がある。

#### 【 0 0 6 1 】

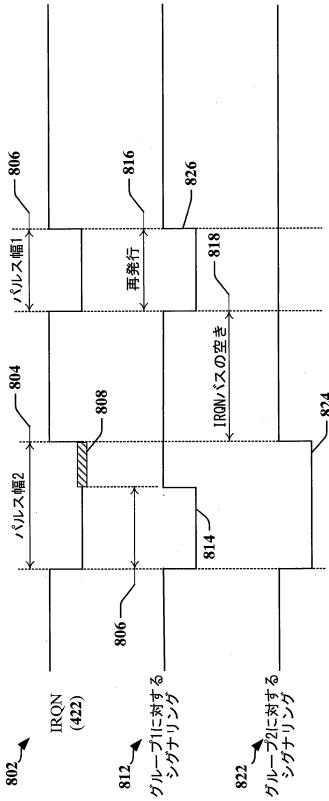

図8は、I2C、CCI、および/またはCClēインターフェースによって同時のIRQ信号がサポートされるときに採用され得る、単線IRQバスの動作モードの一例を示すタイミング図800である。同時のIRQ信号は、個々のスレーブデバイス間、および/または共有单一IRQバス422を使用する異なるグループ406、408の中のスレーブデバイス間に、競合および/または対立をもたらす場合がある。IRQバス422上の信号のタイミングが第1のタイミング図802に

10

20

30

40

50

示され、第1のグループ406および第2のグループ408の中のスレーブデバイスによる寄与が、第2のタイミング図812および第3のタイミング図822にそれぞれ示される。第1のIRQパルス814が、第2のグループ408の中の第2のスレーブデバイスによってアサートされた第2のIRQパルス824と同じ時点で、またはそれと同時に、第1のグループ406の中の第1のスレーブデバイスによってアサートされる。第2のIRQパルス824は、第1のパルスの持続時間806よりも長い持続時間804を有してよい。第1のパルス814の終了後、IRQバス422上に第2のパルス824の一部分808が存在するので、第1のスレーブデバイスは、より優先順位が高いデバイスが割込み要求をアサートしたと認識し得る。第1のスレーブデバイスは、第1のパルス814の終了後、IRQバス422を監視することによって、IRQバス422のこの状態808を事実上の衝突、競合または対立として認識し得る。第1のデバイスは、次いで、第2のスレーブデバイスがより高い優先順位を有すると決定し得、第2のパルス824の終了後に開始するIRQバス空き期間818の後まで、更新された要求を遅らせてよい。スマスマスタデバイス404は、第2のパルス824の持続時間を検出し得、割込み要求の発生源を特定およびサービスするためにデバイスの第2のグループ408をアドレス指定し得る。スマスマスタデバイス404は、第1のパルス814に気づかない場合がある。

#### 【 0 0 6 2 】

第1のスレーブデバイスは、IRQバス空き期間818の満了後にIRQバス422上に第3のパルス826を供給することによって、割込み要求を再発行してよい。

#### 【 0 0 6 3 】

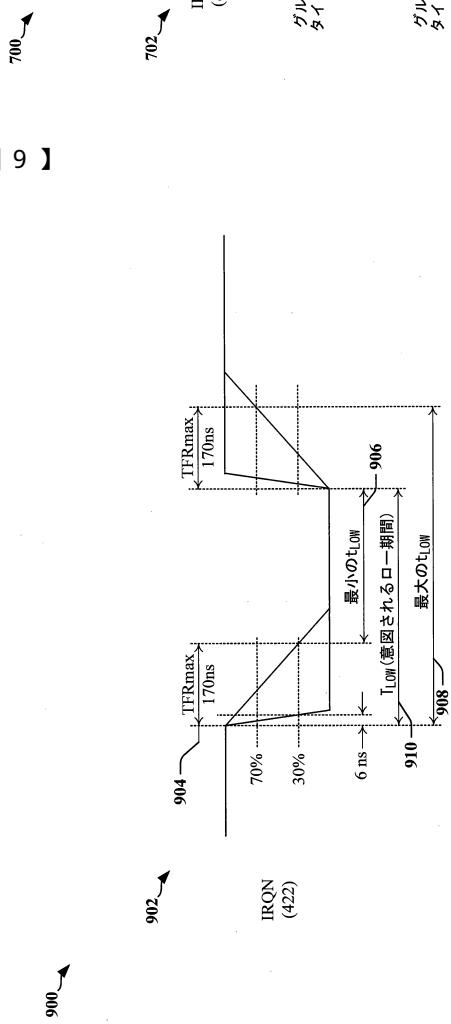

図9は、IRQパルスに関するタイミング許容差を示すタイミング図900であり、ここで、許容差は最小のIRQパルス幅を決定し得る。場合によっては、I2C、CCI、および/またはCCleインターフェース上のシグナリングを管理するプロトコルが、I2C、CCI、および/またはCCleスマスマスタデバイス404によって検出できるようにするためのロー持続時間( $t_{LOW}$ )906に関する最小値を規定し得るが、本説明では、ロー持続時間は指定された最小値を条件としない場合があることを前提としてよい。タイミング図900は、単一パルス902を示す。

#### 【 0 0 6 4 】

例示的なタイミング図900では、「ハイ」シグナリング状態を検出するための最小しきい値電圧は、スイッチング回路供給電圧(「VDD」)レベルの70%にあり、「ロー」シグナリング状態を検出するための最大しきい値電圧は、VDDレベルの30%である。レシーバ入力レベルに応じて、レシーバは、VDDレベルの30%から70%の間に存在するIRQバス422の電圧レベルに関する、ハイシグナリング状態またはローシグナリング状態のいずれかを決定し得る。最大降下-上昇時間(TFRmax)904が規定されてよい。TFRmax904の持続時間は、割込み要求をアサートするためにスレーブデバイスに割り当てられるロー期間( $T_{LOW}$ )910の持続時間を決定し得る。 $T_{LOW}$ 910の値は、スマスマスタデバイス404がスレーブデバイスの異なるグループからのIRQ信号間を区別できるように選択され得る。スマスマスタデバイス404の観点から、 $TFRmax < T_{LOW}$

の場合、ロー状態がIRQバス422上で観測され得る。

#### 【 0 0 6 5 】

スレーブデバイスグループ406、408を区別するために、異なる単位の $T_{LOW}$ がグループ406、408のためのIRQパルス幅として割り当てられてよい。一例では、第1のグループ406は、 $T_{LOW}$ としてのIRQパルス幅が割り当てられてよく、第2のグループ408は、 $2 \times T_{LOW}$ としてのIRQパルス幅が割り当てられてよい。この例では、スマスマスタデバイス404によって観測されるロー期間は、次のように計算され得る。

第1のグループ406:  $T_{LOW} - TFR < t_{LOW} < T_{LOW} + TFR$

第2のグループ408:  $2T_{LOW} - TFR < t_{LOW} < 2T_{LOW} + TFR$ 。

第1のスレーブデバイスがIRQ信号ローをアサートした後、第2のスレーブデバイスは、持続時間に関して少なくともTFRmaxでなければならない $t_{LOWmin}$ までTFRmaxを延ばす時間期間の間、IRQ信号ローを検出し得ないことに留意されたい。そのため、 $T_{LOW} > 3TFR_{max}$ および $t_{LOW min} > 2TFR_{max}$ である。したがって、 $t_{LOW}$ 906に関する最小値は、次のように計算され得る。

10

20

30

40

50

$2T_{LOW} - TFR > T_{LOW} + TFR$

$2TFR_{max} < T_{LOW}$

$3TFR_{max} < T_{LOW}$

$2TFR_{max} < t_{LOWmin}.$

#### 【 0 0 6 6 】

図3～図9に示すサイドバンドIRQ方法は、各スレーブデバイスおよびマスタデバイスに対して余分のピンの使用を必要とする。スレーブデバイスは特に、利用可能なサイズ/空間が限られていることが多い、サイドバンド割込みの使用をなくすことが望ましいはずである。

#### 【 0 0 6 7 】

#### 共有バスを介したインバンド割込み機構

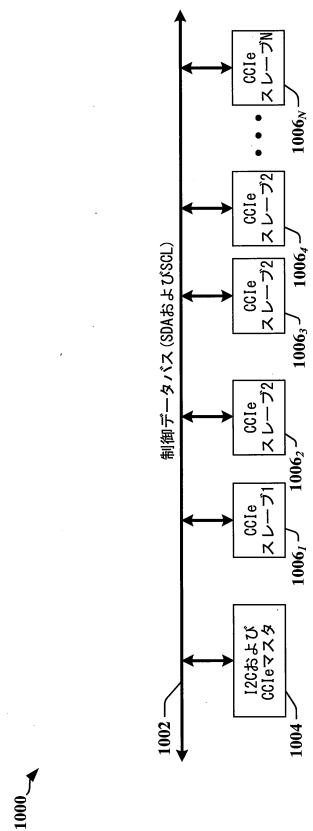

図10は、インバンド割込みに有利なように割込みバスが除去されたシステム1000を示すブロック図である。システム1000は、共有制御データバス1002に結合されるマスタデバイス1004および複数のスレーブデバイス1006<sub>1</sub>～1006<sub>N</sub>を含み得る。一例では、制御データバス1002は、2つのワイヤ、すなわち、クロックライン(SCL)およびシリアルデータライン(SDA)を備えるI2Cバスであってよい。クロックラインSCLは、すべてのデータ転送をI2Cバス1002を介して同期させるために使用され得る。データラインSDAおよびクロックラインSCLは、すべてのデバイス1004および1006<sub>1</sub>～1006<sub>N</sub>にI2Cバス1002上で結合される。この例では、割込みは、データ制御バス1002を介してインバンドで送られる。場合によっては、データ制御バス1002は、I2CデバイスとCCleデバイスの両方を同時にサポートし得る。

#### 【 0 0 6 8 】

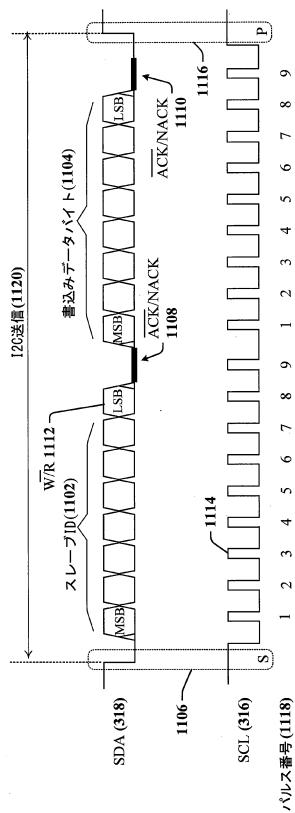

図11は、シリアルバス330(図3参照)がI2Cプロトコルに従って動作させられるとき、1バイト書き込みデータ動作の一例を示すタイミング図1100である。各I2C送信1120は、シリアルバス330上でアサートされる開始条件1106とともに開始し、停止条件1116がシリアルバス330上でアサートされたとき終了する。開始条件1106は、SCL信号ワイヤがハイ状態に保持される間にSDA信号ワイヤ318がローに遷移するとアサートされる。停止条件1116は、SCL信号ワイヤがハイ状態に保持される間にSDA信号ワイヤ318がハイに遷移するとアサートされる。I2Cプロトコルによれば、SDA信号ワイヤ318上の遷移は、開始条件1106および停止条件1116の場合を除き、SCL信号ワイヤ316がローであるときに発生する。

#### 【 0 0 6 9 】

典型的なI2C動作では、I2Cマスタノードは、マスタノードがI2Cバス上のどのスレーブノードにアクセスすることを望むのかを示すためのSDAライン318での7ビットのスレーブID1102と、動作が読み取り動作であるのかそれとも書き込み動作であるのかを示す後続の読み取り/書き込みビット1112とを送り、それにおいて、読み取り/書き込みビット1112は、書き込み動作を示すために論理0にあり、読み取り動作を示すために論理1にある。IDが7ビットのスレーブID1102と一致するスレーブノードのみが、書き込み(または、任意の他の)動作に応答することを許可される。I2Cスレーブノードがそれ自体のID1102を検出するために、マスタノードは、SCLライン316上の8個のクロックパルスとともに、SDAライン318上に少なくとも8ビットを送信する。レガシーアクセスノードがCCle動作に反応することを防止するために、この挙動が活用されてCCle動作モードでデータを送信し得る。

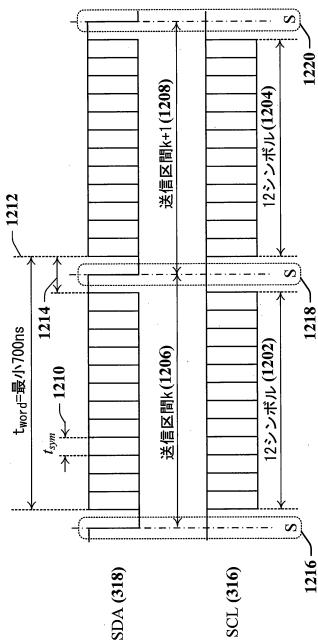

#### 【 0 0 7 0 】

図12は、CCleプロトコルに従って、および、2つ以上の通信しているデバイス202、220、222a～222nがCCleプロトコルに従って通信するように構成または適合されるとき、動作させられるシリアルバス330上のデータ送信を示すタイミング図1200である。CCle送信では、データビットは、SDAライン318およびSCLライン316を介した送信のために12シンボルにトランスクードされ得、送信モードは、「CCleモード」と呼ばれることがある。CCleモードは、プッシュプルドライバによって駆動されるソースに同期する。制御データバス330を介してデータを送信するデバイスはまた、データの中に埋め込まれたクロック情報を送信する。したがって、制御データバス上で1つのデバイスだけが、任意のある時間においてバスを駆動することが許可される。

10

20

30

40

50

## 【0071】

いくつかのCCIE動作モードでは、データは、CCIEバスの信号ワイヤ316、318上で連続的に送信される2ビットのシンボルのセットに符号化される。シンボル1202、1204のシーケンスは、連続送信区間1206、1208の中で送信され得る。シンボル1202、1204の各シーケンスは、開始条件1216、1218、1220によって先行される。開始条件1216、1218、1220は、SCL信号ワイヤがハイ状態に保持される間にSDA信号ワイヤ318がローに遷移するとアサートされる。CCIEプロトコルによれば、SDA信号ワイヤ318上の遷移は、シンボル1202、1204のシーケンスが送信されているとき、遷移がSCL信号ワイヤ316上で発生するのと同時に発生し得る。いくつかのCCIEモードでは、開始条件1216、1218、1220は、2つのシンボル区間を占有し得る。

10

## 【0072】

図示の例では、シンボル1202、1204の各シーケンスは、12シンボルを含み、16ビットのデータと3ビットのオーバーヘッドとを含み得る20ビットのデータ要素を符号化する。12シンボル1202、1204のシーケンスの中の各シンボルは、シンボル期間( $t_{sym}$ )1210ごとにSDA信号ワイヤ318およびSCL信号ワイヤ316のシグナリング状態を規定する。一例では、信号ワイヤ316、318を駆動するために使用されるプッシュプルドライバ214a、214bは、20MHzのシンボルクロックを使用して、50nsの持続時間のシンボル期間1210をサポートし得る。 $\{3,1\}$ として示され得る2シンボルのシーケンスが、シンボル1202および1204の連続するシーケンス間の期間1214において送信される。得られた14シンボルの送信(12シンボルのペイロードおよび開始条件1216、1218、1220)の場合、第1の送信1206の開始と第2の送信1208の開始との間の最小経過時間1212は、

20

$$t_{word} = 14 \times t_{sym} = 700\text{ns}$$

として計算され得る。

したがって、各12シンボルワード1206、1208において16個のデータビットが送信されるので、20ビットが700nsごとに送信されてよく、約22.86Mbpsの有用なビットレートを伴う約28.6Mbpsの未加工のビットレートをもたらす。

## 【0073】

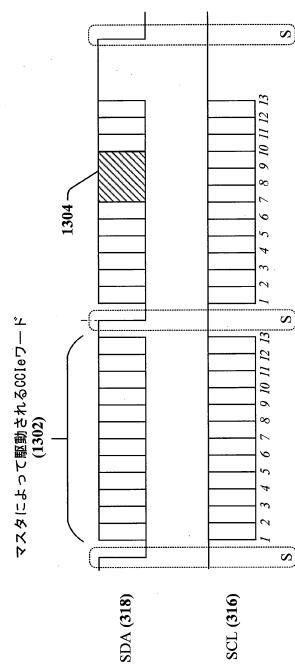

マスタデバイスはバスへのアクセスを制御し、制御データバス330を介して送信することを望むいかなるデバイスも、制御データバス330へのアクセスの許可をマスタデバイスに要求する必要がある。そのような要求は、割込み要求を発行することによって行われ得る。いくつかの態様によれば、CCIEデバイスは、既定のタイミングに従って起きるインバンド割込み機構を通じて割込み要求を発行し得る。そのようなインバンド割込み機構の使用は、バスの競合および/または衝突を防止することができる。図13は、衝突1304の発生を示すタイミング図1300を含む。マスタデバイスが制御データバス330を駆動(1302)している間に、スレーブデバイスが制御データバス330のSDAライン318またはSCLライン316のいずれかを駆動することを割込み機構が防止するとき、衝突1304は回避され得る。

30

## 【0074】

図14は、図13の衝突にとっての可能性を回避するための解決法を示すタイミング図1400である。この手法では、プロトコルは、インバンドIRQがいつ発行されてよいかを規定する。一例では、スレーブがSDAライン318を駆動することを許可される規定された時間期間1420の間に、マスタデバイスはSCLライン316上でクロックを駆動し得る。動作において、マスタデバイスは、SDAライン318をハイに駆動し得、SDAライン318上で1402、1404を送信した後、ハイ状態を維持するためのプルアップを有効化し得る。SDAライン318は、ある時点1414において解放され得、その後、スレーブは、SDAライン318上で1406、1408を送信し得る。スレーブは、次いで、SDAライン318をハイに駆動し得(1416)、SDAライン318を時点1418において解放し得る。マスタデバイスは、次いで、SDAライン318での1410の送信を開始し得る。

40

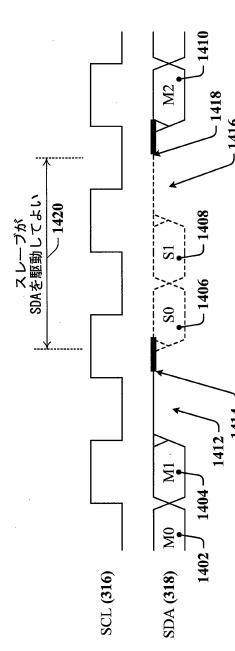

## 【0075】

図15のタイミング図1500に示すように、スレーブデバイスによってSDAライン318上で送られるインバンドIRQは、誤ったクロック1510が検出されることを引き起こす場合がある

50

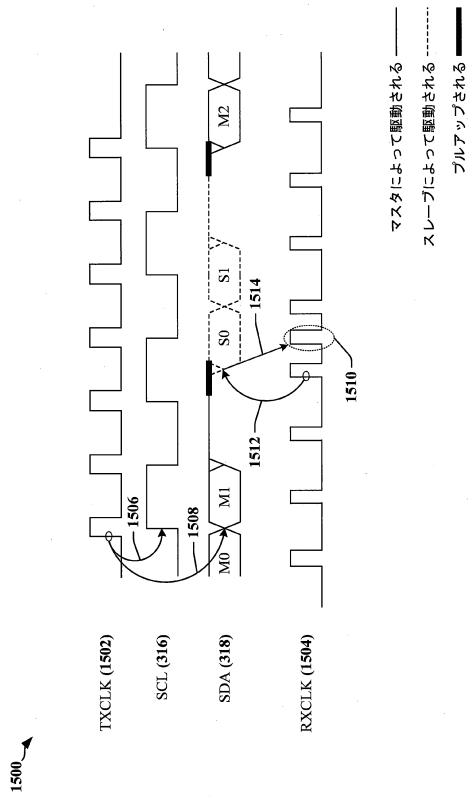

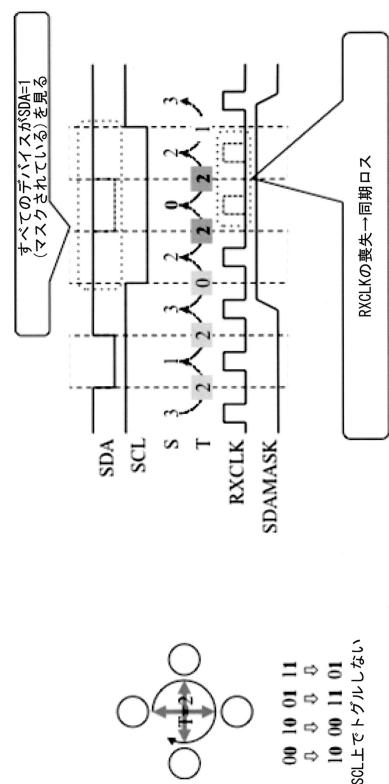

。CCleモードでは、シンボル遷移が、レシーバクロック(RXCLX)1504を生成するために使用される。すべての受信デバイスは、クロックタイミングを制御データバス330の状態遷移から復元する。状態遷移は、SDAライン318および/またはSCLライン316のシグナリング状態変化に対応し、状態遷移は、SDAライン318とSCLライン316との間でタイミング整合される。CCleクロックデータ復元(CDR)回路は、SDAライン318とSCLライン316との間のいくらかのスキューを許容し得るが、CDRの許容差よりも大きいスキューは、CCleワード境界における同期ロスをもたらす余分なレシーバクロックパルス1510をCDRに生成させる場合がある。

#### 【 0 0 7 6 】

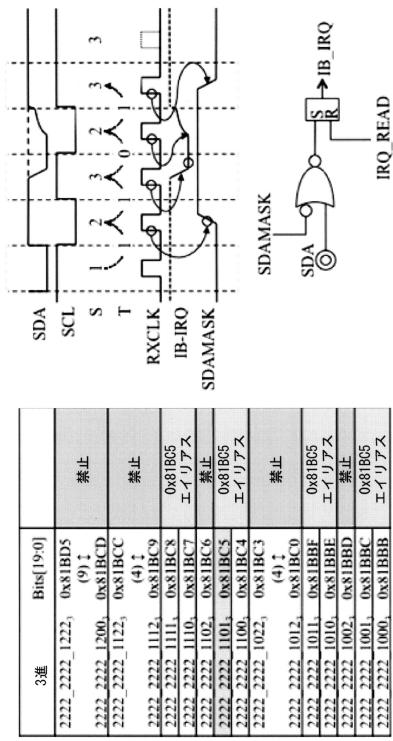

図16は、RXCLK1504上での余分なパルス1510の生成および潜在的な同期ロスを回避し得る1つの解決法を示すタイミング図1600である。SDAマスキング(SDAMASK)信号1608は、クロックデータ復元回路入力において、マスタデバイスおよびスレーブデバイスを含む各デバイスによってインバンドIRQのために使用される信号をゲートまたはマスクする。たとえば、各CDR回路は、インバンドIRQ送信の間、(インバンドIRQのためにどちらのラインが使用されていても)SDAライン318またはSCLライン316をマスクする。たとえば、スレーブデバイスがSDAライン318を特定のインバンドIRQプロトコルを用いて駆動することをマスタデバイスが許可する場合、制御データバス330上のすべてのデバイスは、誤った/余分なRXCLKパルスが検出されることを防止するために、その期間の間それらのSDAライン318の入力をマスクする必要がある。一例では、各デバイスは、インバンドIRQ期間の間、CDR回路へのその値を1(または、ハイ)として保持するために、SDAライン318をゲートする。

10

#### 【 0 0 7 7 】

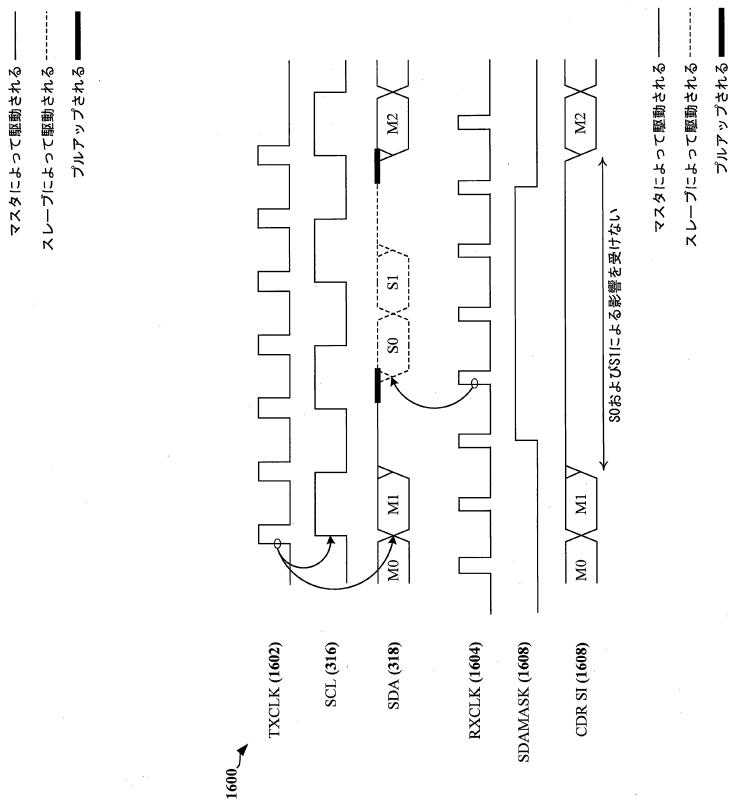

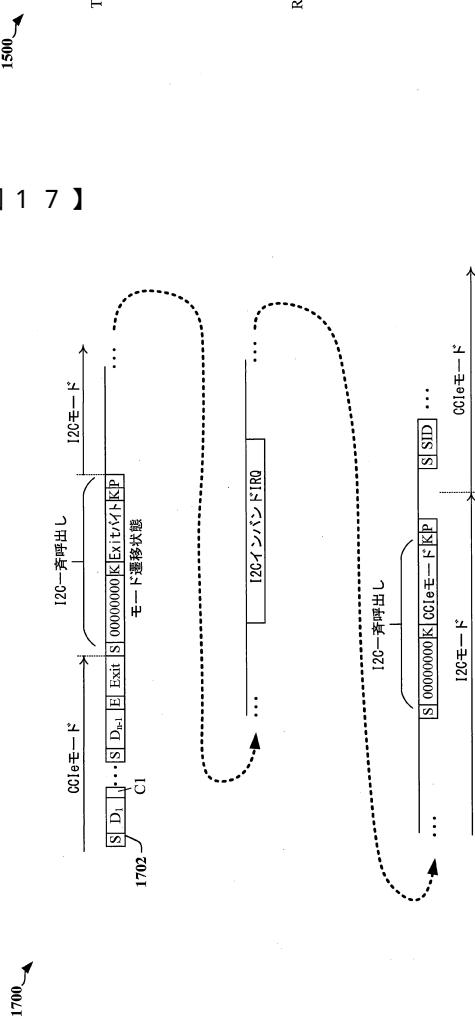

図17は、I2CモードとCCleモードの両方をサポートしながらインバンドIRQ期間を実施することの1つの手法を示す図1700である。この手法では、CCleモードは終了され、次いで、I2Cモードにある間にインバンドIRQが発行される。インバンドIRQが発行された後、制御データバスはCCleモードに戻る。しかしながら、インバンドIRQの発行のためだけにI2Cモードに切り替えなければならないことは、大きすぎるオーバーヘッド(ハードウェアと時間の両方)を生み出す。

20

#### 【 0 0 7 8 】

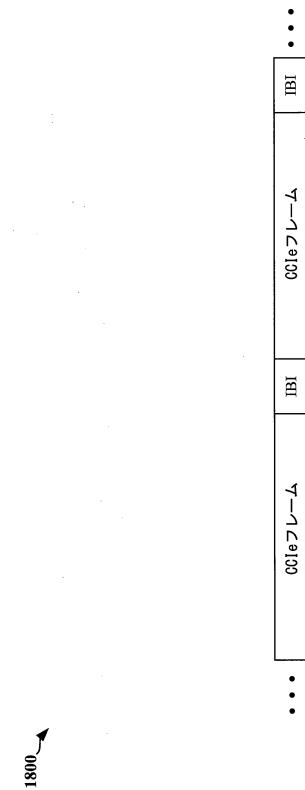

図18は、CCleモードにある間にインバンドIRQ(IBI)が発行される一例を示す図1800である。理想的には、インバンドIRQが可能な限り最小限のプロトコルオーバーヘッドを伴い、可能な限り頻繁に発行され得るように、プロトコルは1つまたは2つのCCleワードと同じくらい小型に維持され得る。たとえば、周期的なIRQウィンドウが規定され得る。

30

#### 【 0 0 7 9 】

考慮事項の中でも、スレーブデバイスによる「枯渇」を防ぐために、バスシステムが低電力モードにあるときであってもインバンドIRQ期間は利用可能であってよい。このことに対する1つの解決法は、スレーブデバイスの同期を可能にするためにバスを介してマスタデバイスによって周期的に送信されるCCle「ハートビート」ワード内でインバンドIRQを規定することであり得る。マスタデバイスは、電力節約のために十分遅く、しかし、スレーブに渴望させないほど十分速いレートで、この「ハートビート」CCleワードを送信してよい。この「ハートビート」CCleワードは、それらがIRQを発行してよいというスレーブデバイスに対するインジケータの働きをし得る。

40

#### 【 0 0 8 0 】

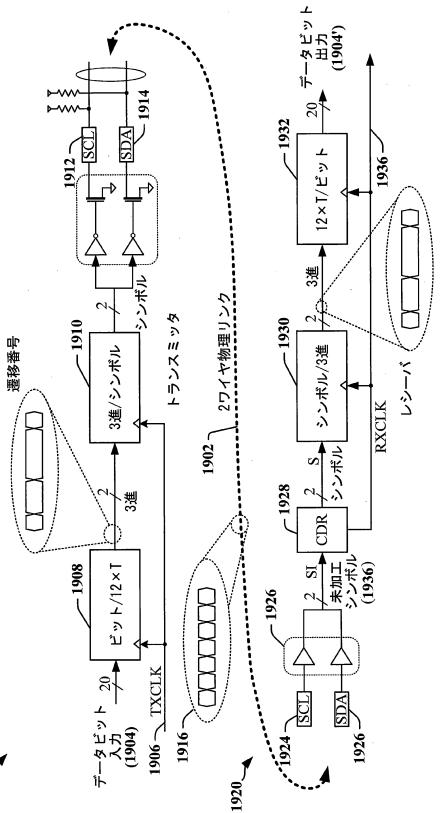

図19は、トランスコードされたシンボル内にクロック信号を埋め込むために、トランスマッタにおいてデータビットをトランスコードされたシンボルにトランスコードするための方法の一例を示すブロック図である。トランスマッタ1900において、入力データビット1904は複数桁の3進(基底3)の数に変換され、ここで、各桁は「遷移番号」と呼ばれることがある。3進数は、次いで、物理リンク1902のクロックラインSCL1912およびデータラインSDA1914上で送信される(連続)シンボルのセットに変換される。一例では、バイナリデータの元の20ビットは、ビット/遷移番号変換器ブロック1908に入力されて12桁の3進数に変換される。12桁の3進数の各桁は、「遷移番号」を表す。2つの引き続く遷移番号は、同じ

50

値を有してもよい。各遷移番号は、遷移/シンボルブロック1910において、2つの引き続く連続シンボルが同じ値を有しないような連続シンボルに変換される。シンボル値(および、ワイヤ1912、1914のシグナリング状態)の遷移が連続シンボルのすべてのペアにおけるシンボル間で保証されるので、連続シンボル遷移は、クロック信号を埋め込むように働き得る。各連続シンボル1916は、次いで、SCLライン1912およびSDAライン1914を有するI2Cバスを含んでもよい2ワイヤ物理リンク1902を介して送られる。

#### 【0081】

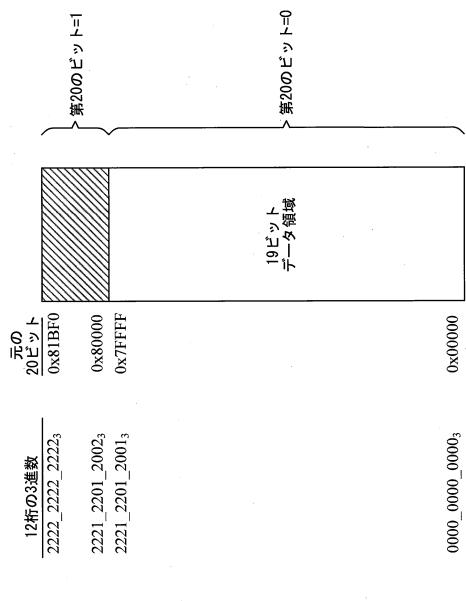

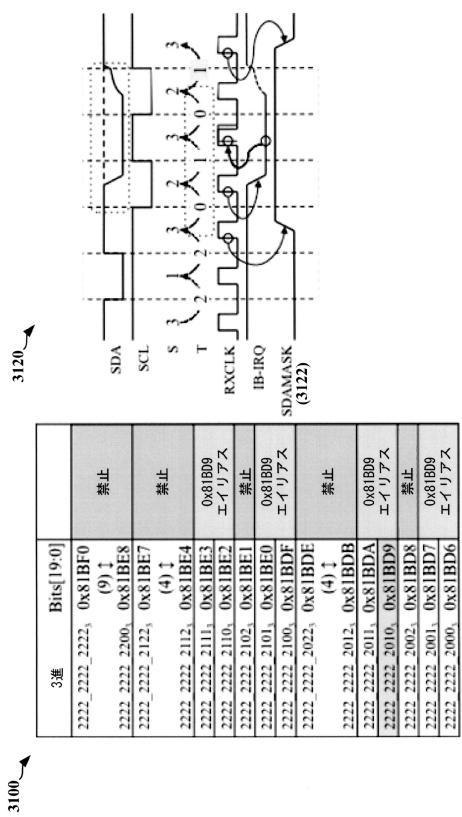

図20は、ビット19(すなわち、ビット0である最初のビットにおいてビットのカウントを開始するときの第20のビット)の符号化の一例を示す図2000である。言い換えれば、コンピュータ科学において一般的であるように、ビットごとのカウントは0において開始し、ビット19は第20のビットである。ここで、ビット0~18は、 $0000\_0000\_0000_3 \sim 2221\_2201\_2001_3$ としての3進数の範囲内で表される。 $2221\_2201\_2002_3 \sim 2222\_2222\_2222_3$ としての範囲の中の3進数は、データ送信のためには使用され得ない。したがって、3進数の範囲 $2221\_2201\_2002_3 \sim 2222\_2222\_2222_3$ は、ビット19(すなわち、第20のビット)を表すために使用されてよい。言い換えれば、 $2221\_2201\_2002_3$ という3進数は、 $1000\_0000\_0000\_0000\_0000$ という2進数(0x80000という16進数)であり、 $2222\_2222\_2222_3$ という3進数(0x81BF0)は取り得る最大の12桁の3進数である。図21および図22は、第20のビット(ビット19)の利用、およびハートビートが送信され得る第20のビット(ビット19)の数空間の一例を示す。

#### 【0082】

図21は、ビット19が数 $2221\_2201\_2002_3 \sim 2222\_2222\_2222_3$ にわたり得るとともに、数の範囲が図21の左側2102の細区分へと細分割され得る一例を示す表2100である。CCleは、マルチマスター制御データバスアーキテクチャであり、制御データバスの制御は、あるマスタデバイスから別のマスタデバイスに移されてよい。したがって、「マスタバス要求」コマンド(サブレンジ $2222\_1121\_0210_3 \sim 2222\_2112\_1121_3$ 内で)、ならびに「マスタハンドオーバ」が(サブレンジ $2222\_2220\_0002_3 \sim 2222\_2221\_1210_3$ 内で)利用可能である。

#### 【0083】

図22は、本明細書で開示するようなハートビートを定義するために使用され得るビット19の数空間内の範囲を示す表2200である。

#### 【0084】

図23は、ハートビートパルス2302a、2302b、2302c、2302dを有するハートビートクロック2300を示すタイミング図である。本明細書で開示するいくつかの態様に従って定義される制御ワード2202(図22参照)は、ハートビートクロック2300を供給するために使用され得る。ハートビートクロック2300は、比較的短い持続時間2306を有し、比較的長い時間期間2304だけ分離される、パルス2302a、2302b、2302c、2302dを供給し得る。一例では、パルス2302a、2302b、2302c、2302dは、1シンボルの持続時間(たとえば、50ns)として規定されてよく、それらのパルスは、30マイクロ秒(30 μs)だけ分離され、それによって、33.33 kHzの周波数を有するハートビートクロックを供給し得る。この例では、CCleスレーブデバイスは、ハートビートワードから抽出された33.33kHzのクロックを、様々なスタンバイ動作のために使用し得る。

#### 【0085】

図24は、CCleプロトコルに従って、かつCCleスレーブデバイスが図23に示したハートビートクロック2300を含むハートビートクロックを取得することを可能にする方法で送信され得る、制御ワード2416の一例2400を示す。一例では、制御ワード2416は、16進数0x81BEとして表現され得、それは12桁の3進数2414として表現され得る遷移番号にマッピングされるビットパターン2412を生成する。遷移番号が開始条件値を用いてカプセル化されて、シンボルのストリーム2422の中に提供される12シンボルのシーケンス2428を生成するよう計算された14個の遷移番号2424のセットを生成し得る。タイミング図2420に示すように、12シンボルのシーケンス2428の1つおきのシンボル2430は、「3」としての値を有し、SDA信号ワイヤ318とSCL信号ワイヤ316の両方の上でハイ電圧レベルを生じる。本例では、SDA信号ワイヤ318とSCL信号ワイヤ316の両方がハイ状態にあるとき、最小電流がSDA信号ワ

10

20

30

40

50

イヤ318およびSCL信号ワイヤ316の中を流れ得る。「3」としてのシンボル値は、シリアルバス330に関連した電力消費を最小限に抑え得る。12シンボルのシーケンス2422はまた、SDA信号ワイヤ318またはSCL信号ワイヤ316のうちの他方がハイのままである間に、SDA信号ワイヤ318またはSCL信号ワイヤ316のいずれかをローに駆動させる、値「1」または「2」を有するシンボル2432、2434を含む。各12シンボル送信2428では、残りのシンボル2432が「1」としての値を有する間に、1つのシンボル2434に「2」としての値が与えられてよい。結果として、ハートビート制御ワード2416は、制御ワード2416が送信されるたびに、SDA信号ワイヤ318上の6個のパルス、およびSCL信号ワイヤ316上の1つのパルスを生成する。一例では、ハートビート制御ワード2416を反復的に送信することによって、1.43MHzのクロックがSCL信号ワイヤ316上に供給され得る。

10

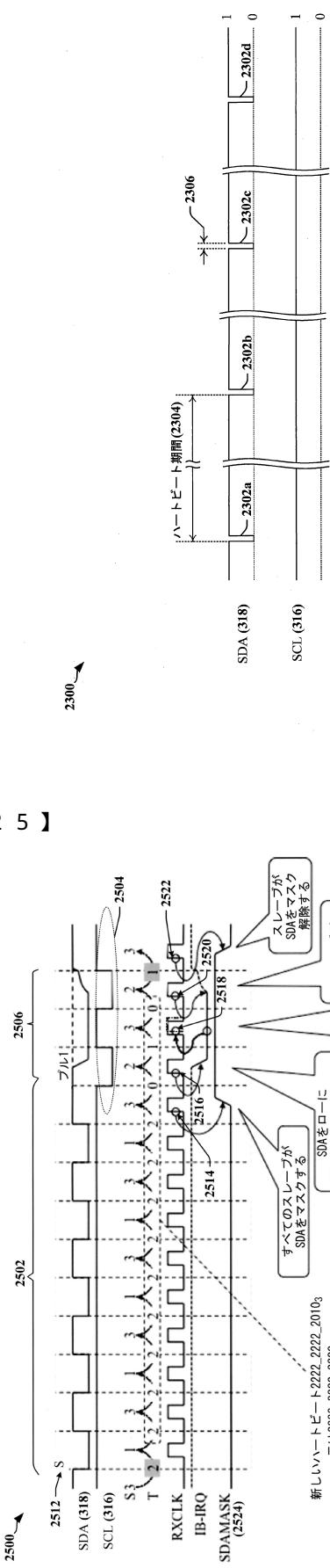

#### 【0086】

##### インバンドIRQ技法の第1の例

図25は、ハートビートクロックがSDAライン318およびSCLライン316を介して送信され得る一例を示す。この例では、ハートビートクロックは、SDAライン318上で送信されるハートビートクロックの第1の部分2502を含み、ハートビートクロックの第2の部分2504はSCLライン316上で送信されてよく、それによって、SDAライン318上にインバンドIRQのためのより大きい空間2506が生まれる。

#### 【0087】

そのプロトコルによれば、受信スレーブデバイスは、たとえば、開始Sインジケータ2512の後の第nのRXCLK2514を検出し得る。第nのRXCLK2514は、受信スレーブデバイス内で内部SDAマスク2524をトリガして、SDAライン318を内部的にマスクしてよい。

20

#### 【0088】

n+1 RXCLK2516において、スレーブデバイスは、SDAライン318をローにプルすることによってIRQをトリガし得る。SDAライン318は、マスタデバイスによってハイにプルされるか、または浮動し、その結果、(スレーブデバイスによって)ローにプルされると、これはインバンドIRQを示すように働く。n+2 RXCLK2518において、マスタデバイスは、インバンドIRQがアサートされているかどうかを確認するためにSDAライン318をサンプリングしてよい。n+3 RXCLK2520において、スレーブデバイスは、SDAライン318を解放してよく、その結果、インバンドIRQがアサート解除される。n+3 RXCLKとn+4 RXCLK2522との間で、マスタデバイスは、SDAドライバを再有効化しSDAライン318をハイに駆動し始める。したがって、受信デバイス(たとえば、スレーブデバイス)は、n+4 RXCLK2522において、SDAマスク2824を安全に解放することができる。n+4 RXCLK2522において、スレーブデバイスは、SDAマスク2524を解放してよい。このようにして、IRQは、SDAライン318上で規定されるIRQ期間2506の間、スレーブデバイスによって送信され得る。

30

#### 【0089】

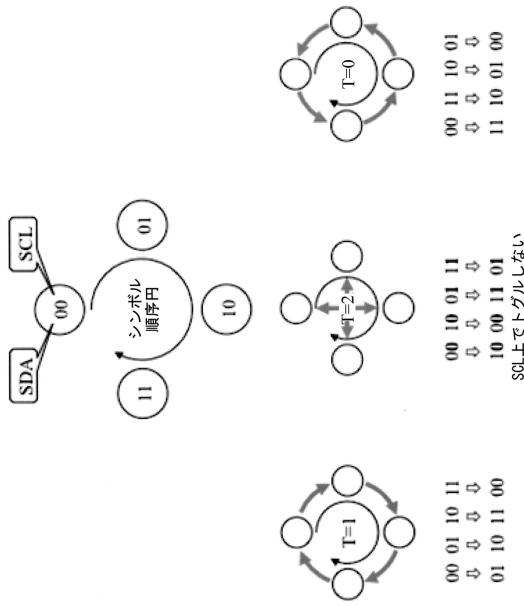

図26は、3進数(遷移番号)2602と(連続)シンボル2604との間の変換のための方式の一例を示す図2600である。3進数、すなわち、基底3の数は遷移番号とも呼ばれ、3つの取り得る数字または状態、0、1、または2のうちの1つを有することができる。2つの引き続く3進数において同じ値が現れる場合もあるが、2つの引き続くシンボルは同じ値を有しない。

40

#### 【0090】

この変換関数は、図26に例示的に記載される。送信側(TX:TからSへ)では、論理は、 $T_{tmp} = T=0?3:T$ 、および $C_s = P_s + T_{tmp}$ である。言い換えれば、遷移番号Tは0と比較され、T=0のときに $T_{tmp}$ (テンポラリー)は3に等しくなり、それ以外では(Tが0に等しくないとき) $T_{tmp}$ はTに等しくなる。また、現在のシンボル( $C_s$ )は、前のシンボル( $P_s$ )の値+ $T_{tmp}$ になる。たとえば、第1のサイクル2606ではTは2であり、そのため $T_{tmp}$ も2であり、 $P_s$ を1として新しい $C_s$ は現在3である。

#### 【0091】

第2のサイクル2608では、次のサイクルにおいて遷移番号1が入力され、遷移番号は3ではなく、そのため1としてのTの値が3としての前のシンボルの値に加算される。加算の結果、すなわち、4は3よりも大きいので、ロールオーバされた数0が現在のシンボルになる。

50

**【 0 0 9 2 】**

第3のサイクル2610では、同じ遷移番号1が入力される。Tが1であるので、 $T_{tmp}$ も1である。変換論理が前のシンボル0に1を加算して、現在のシンボル1を生成する。

**【 0 0 9 3 】**

第4のサイクル2612では、遷移番号0が入力される。変換論理は、Tが0のとき、 $T_{tmp}$ を3に等しくする。したがって、3が前のシンボル1に加算されて現在のシンボル0を生成する(加算の結果、すなわち、4は3より大きいので、ロールオーバされた数0が現在のシンボルになる)。

**【 0 0 9 4 】**

したがって、2つの引き続く3進数字2602が同じ数を有する場合であっても、この変換は10、2つの引き続くシンボル数字が異なる状態値を有することを保証する。このため、シンボルのシーケンス2604の中の保証されたシンボル遷移が、クロック信号を埋め込むように働いてよく、それによって、I2Cバスの中のクロックラインSCLをデータ送信のために解放する。レシーバ側(RX:SからTへ)では、論理は反転され、 $T_{tmp}=C_s+4-P_s$ 、および $T=T_{tmp}=3?0:T_{tmp}$ である。

**【 0 0 9 5 】**

図27は、遷移番号をシンボル番号に変換するための技法の一例を示す第1の図2700である。制御データバス330がCClEモードで動作するとき、シンボルSがSDAライン318およびSCLライン316を介して送信され得る。一例では、各シンボルは2ビットからなり得、 LSBがSCLライン216に割り当てられ、MSBがSDAライン218に割り当てられる。20

**【 0 0 9 6 】**

各3進遷移番号Tは、次のように特徴付けられ得る。

Sが前の状態から現在の状態へシンボル順序円の上を1つの状態だけ時計回りに遷移するときはT=1であり、

Sが前の状態から現在の状態へシンボル順序円の上を2つの状態だけ時計回りに遷移するときはT=2であり、

Sが前の状態から現在の状態へシンボル順序円の上を3つの状態だけ時計回りに遷移するときはT=0である。

CClEモードでのデータ制御バス330を介したデータ送信は、任意の遷移番号を採用してよい。すなわち、すべての可能な遷移番号の値は、データを符号化する各シンボルを生成するために使用されるように利用可能である。シンボルは、前に送信されたシンボルと異なるシンボルを識別するように遷移番号を使用して選択される。30

**【 0 0 9 7 】**

図28は、図27に示す符号化技法のいくつかの様子を示す第2の図2800である。この図2800では、各3進遷移番号Tは、次のように特徴付けられ得る。

Sが前の状態から現在の状態へシンボル順序円の上を1つの状態だけ時計回りに遷移するときはT=1であり、

Sが前の状態から現在の状態へシンボル順序円を横切って遷移するときはT=2であり、

Sが前の状態から現在の状態へシンボル順序円の上を1つの状態だけ反時計回りに遷移するときはT=0である。40

第2の図2800は、SCLライン316はT=0または1のときに常にトグルし、SCLライン316はT=2のときにトグルしないことを示す。

**【 0 0 9 8 】**

図29は、インバンドIRQ期間の間の条件を発生させ得る、SDAマスク3122がアサートされるときに発生することがあるいくつかの条件を示す図である。本明細書で言及するよう、SDAライン318は、余分なクロックパルスの生成を回避するために、インバンドIRQ期間の間マスクされる。SCLライン316は、遷移番号T=2が送られるときにトグルせず、I2Cプロトコルによれば、SDAライン318は、SDA信号がマスクされシンボル遷移がないとき、その実際の状態にかかわらず常にハイであるものとして観測される。したがって、SDAマスク期間の間にT=2である場合、スレーブデバイスはその受信クロック上に遷移を生成し50

ないので、SDAマスク=1である間はT=2が禁止されてよい。

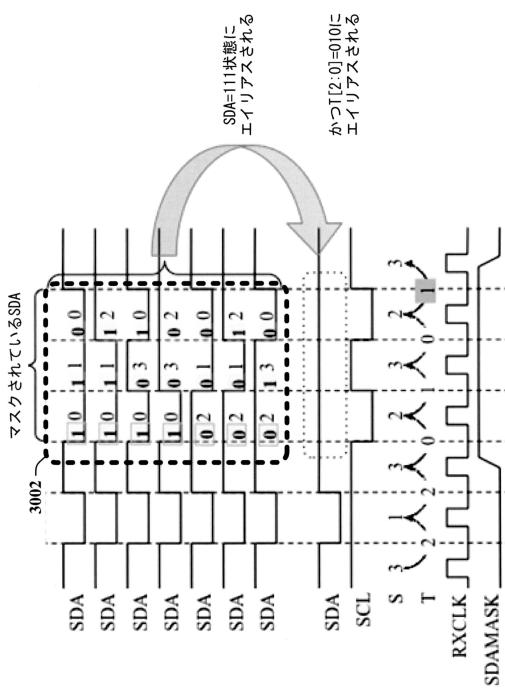

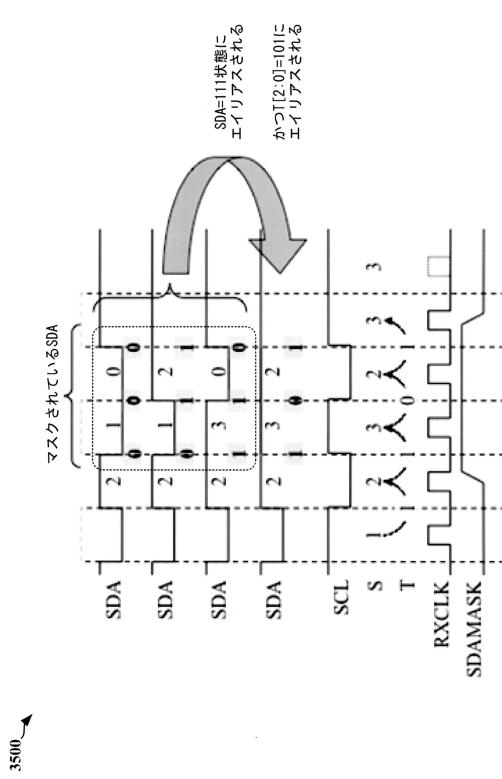

#### 【0099】

図30は、図25および図29のSDAマスクを使用することの副作用を示す。たとえTが2に等しくなくても、SDAライン318が、インバンドIRQ期間の間に常に論理1状態として見られるので、SDAライン318に対して論理0をもたらすことになる任意の遷移T値は、SDAビットが常に1であることを前提とするT[2:0]=010にエイリアスされる。

#### 【0100】

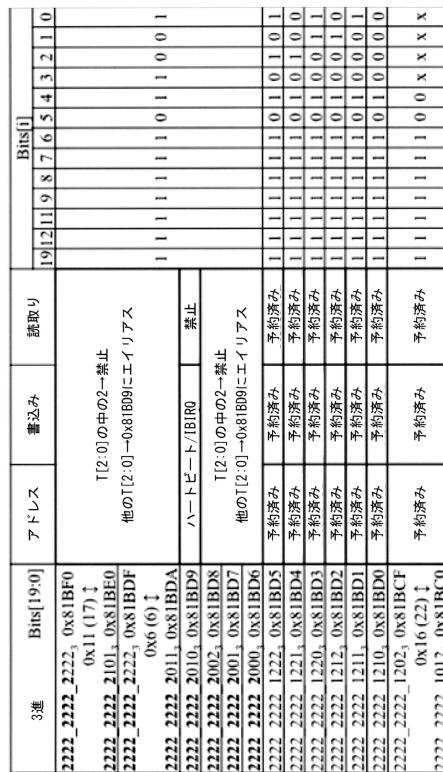

図31は、インバンドIRQのためにハートビートクロックを使用することに関するいくつかの態様を示す、表3100およびタイミング図3120を含む。ハートビートは、3進数空間内で数空間0x81BD6から0x81BF0(すなわち、27個のアドレス)を占有する値を使用して生成され得る。SDAマスク=1である間にT=2が禁止され任意の他のTの組合せがT=010にエイリアスされるという事実は、インバンドIRQをサポートするハートビートワードが1つのアドレスのみを占有するだけでなく、ビット19領域の27個のアドレスを事実上占有することを意味する。特定のハートビートパターンを使用することは、16進で81BF0であるとともに2ワードCCIE同期の最初のワードとして極めて有用である3進数2222\_2222\_2222の使用を禁止する。3進数2222\_2222\_2222は、完全な同期を容易にする。

10

#### 【0101】

図32は、CCIEモード送信をマッピングするために、図31に示す3進数としてのビット19を使用することの一例を示す表3200である。この例では、ハートビートは、3進数2222\_2222\_2010<sub>3</sub>に割り当てられてよい。この例では、2222\_2222\_2xxx<sub>3</sub>としての範囲の中の3進数が検出される限り、これがハートビートおよび/またはインバンドIRQ(たとえば、16進での0x81BD9)として解釈されてよいことに留意されたい。

20

#### 【0102】

##### インバンドIRQ技法の第2の例

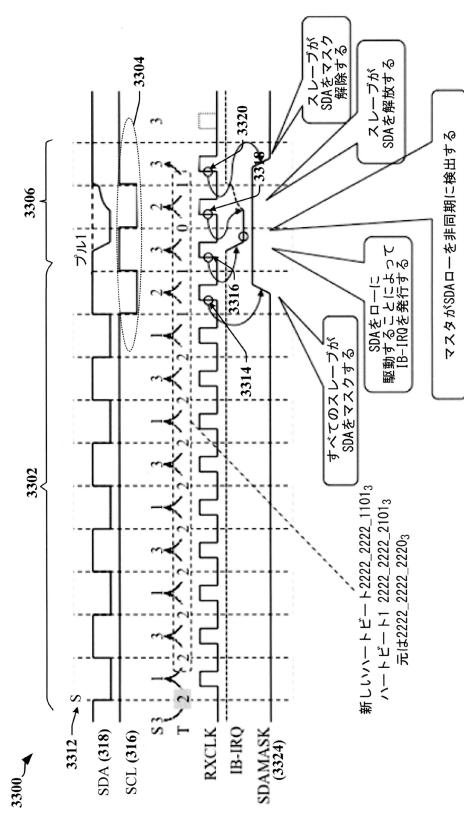

図33および図34は、CCIEモードで動作する、または動作可能な制御データバス330上でインバンドIRQを実施するための技法を示す、タイミング図3300、3400を含む。一例では、インバンドIRQを実行するために必要とされるレシーバクロックRXCLKのサイクルの数を低減することは、図25に関して説明された例に対して低減され得る。タイミング図3300は、受信スレーブデバイスが、たとえば、開始Sインジケータ3312の後に第nのRXCLKパルス3314をその中で検出し得る、インバンドIRQ期間3306を提供するためのプロトコルに対応する。第nのRXCLKパルス3314は、SDAライン318を内部的に(たとえば、受信スレーブデバイス内で)マスクするための内部SDAマスク3324をトリガしてよい。

30

#### 【0103】

n+1 RXCLKパルス3316において、スレーブデバイスは、SDAライン318をローにプルすることによって、IRQをトリガしてよい。n+1 RXCLKパルス3316の到着の前に、マスタデバイスは、抵抗性プルアップなどを使用して、SDAライン318を(弱く)ハイ状態にプルさせてよい。スレーブデバイスがSDAライン318をローにプルしたとき、インバンドIRQが示され得る。

#### 【0104】

次のクロックサイクルまで待機するのではなく、n+1 RXCLKパルス3316とn+2 RXCLKパルス3318との間で、ただしn+2 RXCLKパルス3318の前に、マスタデバイスは、インバンドIRQ要求がアサートされたという表示としてSDAライン318がローになっているかどうか、および/またはSDAライン318がいつローになったのかを確認するために、SDAライン318を監視してよい。SDAライン318のマスタデバイスによるそのような監視が、任意のIRQ要求をスレーブデバイスから非同期に検出するために、IRQ期間の間のみに実行されてよいことが諒解されよう。n+2 RXCLKパルス3318において、スレーブデバイスは、SDAライン318をアサート解除するために、インバンドIRQを解放してよい。n+2 RXCLKパルスとn+3 RXCLKパルスとの間で、マスタデバイスは、SDAドライバを再有効化してよく、SDAライン318をハイレベルに駆動し始めてよい。その結果として、アサートしているスレーブデバイスのレシーバは、n+3 RXCLKパルス3320においてSDAマスクを安全に解放することができる。

40

50

RXCLKパルス3320において、スレーブデバイスは、SDAマスク3324を解放してよい。このようにして、インバンドIRQは、SDAライン上で規定されたIRQ期間3306の間、スレーブデバイスによって送信され得る。

#### 【0105】

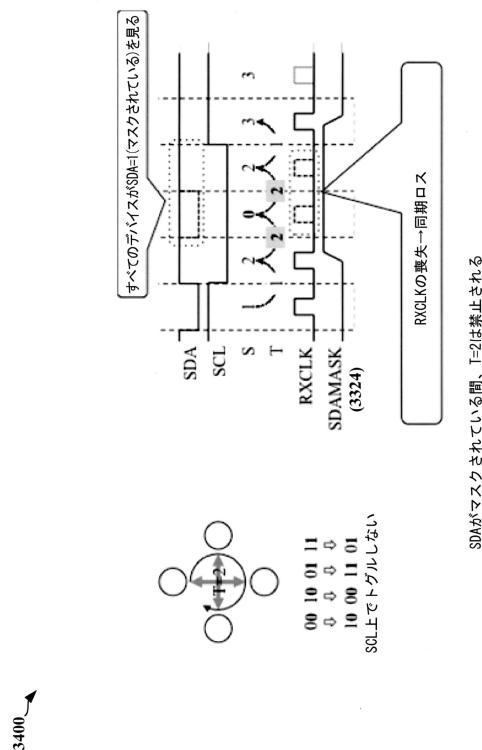

図35は、SDAマスク3324が採用されるときのエイリアシング条件を示すタイミング図3500であり、図36は、図33～図35で提示される例による、インバンドIRQの間に供給されるハートビートクロックに関するいくつかの態様を示すタイミング図3600を含む。ハートビートワードは、3進数空間内で数空間0x81BBB～0x81BD5(すなわち、27個のアドレス)を占有し得る。図25～図32に関して説明したハートビートと同様に、図33～図35の例に関する代替のハートビートも、ビット19領域の27個のアドレスを占有する。ただし、この代替のハートビートは、2222\_2222\_2222ワードが依然として同期のために利用可能であるように、2222\_2222\_2xxxとしての3進数空間を使用することを禁止しない。このハートビートパターンはまた、マスタデバイスが非同期インバンドIRQ検出回路を使用して、より短いインバンドIRQ期間を適応させることを必要とすることがある。10

#### 【0106】

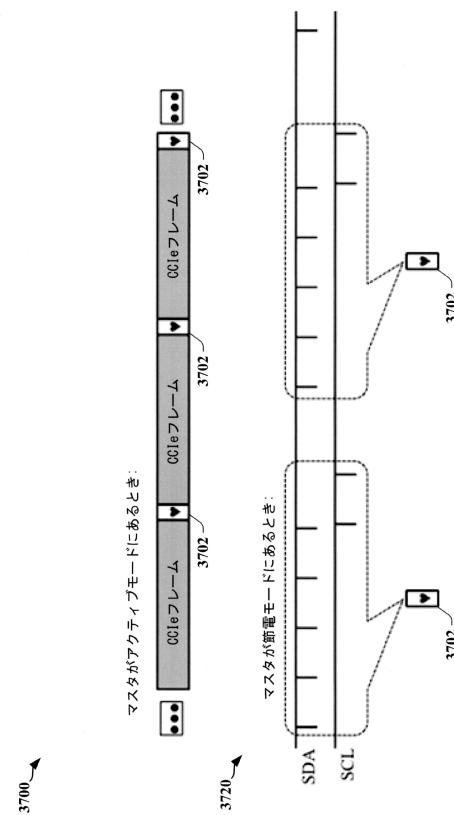

図37は、マスタデバイスがアクティブモード3700にあるとき、およびマスタデバイスが節電モード3720にあるとき、ハートビートがそれによって送信され得る方法を示す図である。通常動作の間、マスタデバイスはアクティブモード3700にあってよく、マスタデバイスは、スレーブデバイスがインバンドIRQを発行することを可能にするために、ハートビートワード3702を周期的に送ってよい。割込みをアサートするための機会をスレーブに渴むさせないようなハートビートワード間隔であってよい。20

#### 【0107】

マスタデバイスが節電モード3720にあるとき、同じハートビート3702が同様に送信されなくてよく、それによって、節電モードの間にインバンドIRQを発行するための機会をバス上のスレーブデバイスに与える。

#### 【0108】

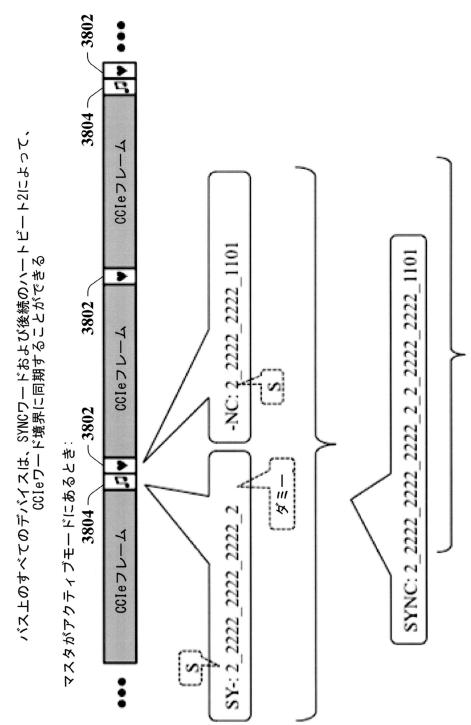

図38は、同期ワード3804とハートビートワード3802の組合せを示すタイミング図3800である。ハートビートワード3802は、2ワード同期ワードシーケンスの第2のワードとしての働きをし得る。一例では、2ワード同期シーケンスは、すべての桁=2(値=2222\_2222\_2222)を有し「SY-」として示される第1のワード3804とともに開始し得、ハートビートワード3802は、値=2222\_2222\_1101を有し「-NC」として示され得る。「SY-」ワードは、開始条件に関連付けられた1つの「2」と、バスシグナリング状態を表すシンボルが1(SDA=0、SCL=1)から3(SDA=1、SCL=1)に転じるときの最後のシンボルの後の1つの「2」とを含む、14個の遷移状態2を、受信デバイスに生成させ得る。「-NC」ワードは、開始条件に関連付けられた1つの「2」を含む9個の遷移状態2を、受信デバイスに生成させ得る。30

#### 【0109】

「SY-」ワードと「-NC」ワードとを組み合わせることは、合計23個の遷移状態2および後続の「1101」シーケンスを提供する「SYNC」と呼ばれることがある。このシーケンスは一意のシーケンスであり、他のCCIEトランザクションで発生しない。CCIEデバイスは、そのシーケンスを使用してCCIEワード境界に同期し得る。40

#### 【0110】

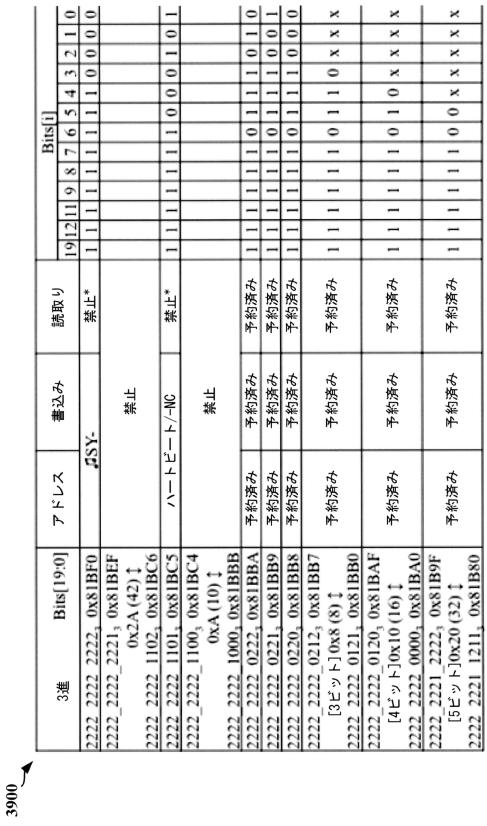

図39は、CCIEプロトコルのビット19内での同期およびハートビートマッピングを示す表3900である。27個の数にわたる16進での数値の空間0x81BD6から0x81BEFは、23個の「2」を含む2ワードパターン「SY-NC」を作るために禁止されてよく、「1101」ビットパターンは一意であり同期のみのために使用される。スレーブデバイスが同期ロスの場合に再同期することを可能にするために、またはホットプラグされたスレーブがバスに同期することを可能するために、マスタデバイスは、「-NC」ワードであるハートビートの前に「SY-」ワードを周期的に送ることができる。

#### 【0111】

インバンドSIDスキャンおよび応答50

制御データバス330に結合される各スレーブデバイスは、スレーブ識別子(SID)によって一意に識別され得る。マスタデバイスは、それらのSIDを学習するために、制御データバスに結合されているスレーブデバイスのスキャンを実行してよい。スキャンは、新しいデバイスがバス上に接続されたときに(たとえば、ホットプラグ)、および/または周期的に、デバイスの始動および/または電源投入において実行されてよい。IRQがスレーブデバイスによって発行されたことをマスタデバイスが感知したとき、マスタデバイスは、次いで、どのデバイスがIRQを発行したのかを識別するために、スレーブデバイスをスキャンしてよい。一手法では、マスタデバイスは、SIDのシーケンスまたはそれらの要素が送られるSIDスキャンを開始してよく、そのようなSIDまたはSID要素に一致するスレーブデバイスは、一致を示すためにSDAラインをローにプルする。

10

#### 【0112】

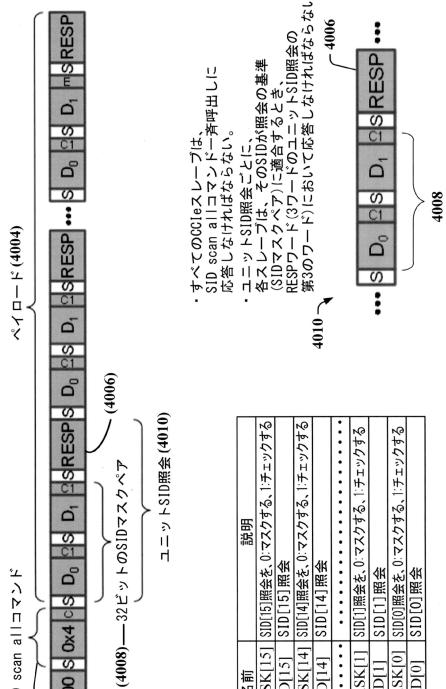

図40は、SID「Scan All」コマンド4002とその対応するペイロード4004とを含む、CCIE送信の一例4000を示す。SID「Scan All」コマンド4002(「0x4」コードによって識別される)は、マスタデバイスによって発行され得る。ペイロード4004は、ユニットSID照会シーケンス4010を含み得る。各ユニットSID照会シーケンス4010は、SIDマスクペア4008および応答(RESP)ワード4006を含む。SIDマスクペア4008は、それについて照会するためのSID内のビット位置を識別するマスクを定義し得る。

#### 【0113】

表4020に示すように、32ビットのSIDマスクペア4008(2つの16ビットデータD0およびD1に広がる)は、16ビットのSIDの1つまたは複数のビットロケーションが照会されているかどうか、かつ、そうである場合、どの値(または、ビット設定)について照会されているのかを識別するように働く。たとえば、SIDマスクペア4008のビット[1]は、SIDのビット[0]がチェックされるべきであるか、それともマスクされる(すなわち、チェックされない)べきであるかを定義し得る。ビット[1]が「チェック」を示す場合、SIDマスクペア4008のビット[0]は、照会が「0」または「1」に関するかどうかを定義する。

20

#### 【0114】

RESPワード4006によって規定される期間は、スレーブデバイスが共有バスを介してインバンドでSID照会に応答することを可能にする。ユニットSID照会シーケンス4010ごとに、対応する照会ビットに一致する1つまたは複数のマスクされていないSIDビットを有する各スレーブデバイスは(すなわち、スレーブデバイスのSIDが、照会されたロケーションまたは1つもしくは複数の照会ビットに一致するロケーションにおいて、1つまたは複数のビットを有する)、共有バスの少なくとも1つのラインを介してインバンドで照会応答を送る。このことにより、マスタデバイスが、バス上のいずれかのスレーブデバイスが部分的に一致するSID(すなわち、照会ビットに一致する、照会されたビットロケーションにおいてビットを有するSID)を有するか否かを確認することが可能になる。

30

#### 【0115】

複数のユニットSID照会シーケンス4010は、マスタデバイスによって、共有バスに結合されたすべてのデバイスのためのSIDを完全に識別するために送られる。

#### 【0116】

「Scan All」コマンド4002またはその変種は、マスタの起動に直接関係しない場合において発行されてよい。一例では、マスタデバイスは、すべてのスレーブデバイスが同期しているかどうかをチェックするために、制御バスに結合されたすべてのスレーブデバイスについてスキャンしてよい。この例では、マスタデバイスは、完全な「ブラインドスキャン」を必ずしも実行する必要があるとは限らず、マスタデバイスは、どのスレーブデバイスがバスに結合されているのかをすでに知り得るので、マスタは、マスクなしの、および/またはいかなるSIDビットも比較から排除しないマスクありの照会を、発行し得る。別の例では、マスタデバイスは、1つまたは複数の特定のスレーブデバイスが同期しているかどうかをチェックするために、制御バスに結合されたすべてのスレーブデバイスについてスキャンしてよい。この例では、マスタデバイスは、スキャンされるべき各スレーブデバイスに対して1つだけユニットSID照会を送ってよい。

40

50

## 【0117】

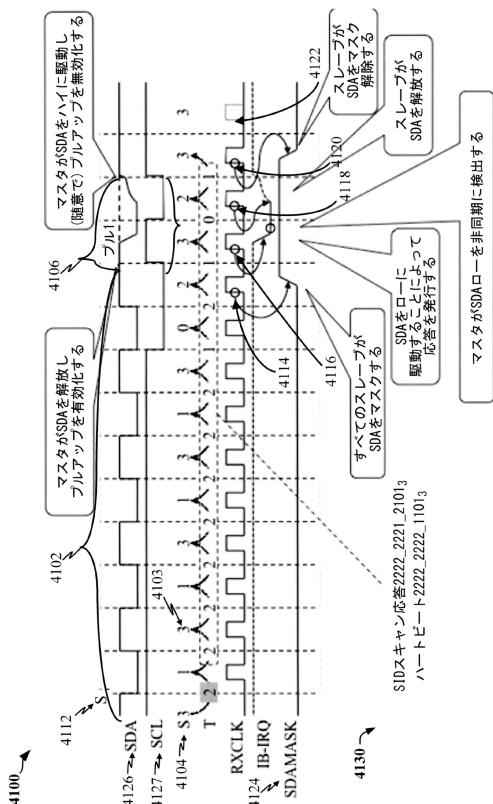

図41は、SDAラインおよびSCLラインを備える共有バスを介したSIDスキャン応答(RESPワード4006)に関するタイミング図4100を示す。この例では、SIDスキャン応答4130は、12シンボルのシーケンス3131\_3130\_2323に等しい13進数2222\_2221\_2101<sub>3</sub>または16進の0x81B8Fによって識別される。これらのシンボルは、SDAライン4126およびSCLライン4127を介して送信される。スレーブデバイスが応答期間4106の間にSDAライン4126を使用してSIDスキャン照会に応答することを可能にするために、マスタデバイスはSDAライン4126を解放し、SDAライン4126をハイに弱くプルさせる。各レシーバデバイスは、次いで、応答期間4106にわたって、そのクロックデータ復元回路(CDR)へのSDAライン入力をマスクする。マスタは、SCLラインをトグルして(その状態を変化させて)、SDAラインが使用中である間に、各レシーバデバイスがSCLライン上のそのようなトグリングからクロックを復元することができるようになる。10

## 【0118】

RESPワード4006は、ハートビートワードとほぼ同じであり得る。マスタデバイスおよび/またはスレーブデバイスがRESPワード4006をハートビートワードと区別できるように、RESPワード4006は、ハートビートワードに対して少なくとも1つの差異を有し得る。ハートビートワードおよびRESPワード4006は、ビット19の3進空間(すなわち、ビット19の値が一定であるアドレス空間)内で隣接してよく、またはほぼ隣接してよく、他の制御およびシグナリング目的のために利用可能な連続した大きい領域を残す。一例では、ビット19の高位の領域の低い部分の中の連続した大きい領域が、他の目的のために予約または使用されてよい。RESPワード4006によって提供されるインバンド応答機能が利用可能であることにより、スレーブデバイスは、専用のサイドバンドIRQラインを使用する代わりにインバンドで応答を送ることができるようになる。20

## 【0119】

CCIEプロトコルによれば、受信スレーブデバイスは、たとえば、開始Sインジケータ4112の後、第nのRXCLK4114を検出し得る。第nのRXCLK4114は、内部SDAマスク4124をトリガして、リッスンしている各CCIEデバイス内のSDAライン4126を、内部的に(たとえば、受信スレーブデバイス内で)マスクしてよい。

## 【0120】

n+1 XCLK4116において、スレーブデバイスは、SDAライン4126をローにプルすることによって、応答をアサート/発行し得る。SDAライン4126は、マスタデバイスによってハイに弱くプルされ、その結果、(スレーブデバイスによって)ローにプルされるとき、このことは、SIDスキャン照会に対する肯定的応答を示すように働く。SDAライン4126をハイに弱くプルすることによって、これによりスレーブデバイスがSDAライン4126をローにプルして、SIDスキャン照会に対する応答をアサートすることが可能になる。30

## 【0121】

次のクロックサイクルまで待機するのではなく、n+1 RXCLK4116とn+2 RXCLK4118との間で、ただしn+2 RXCLK4118の前に、マスタデバイスは、それがローになっているかどうか、および/またはそれがいつローになったのかを確認するために、SDAライン4126を監視してよく、それは応答がアサート/発行されたことを意味する。マスタデバイスによるSDAライン4126のそのような監視は、スレーブデバイスからのアサート/発行された応答を非同期に検出するために、応答期間4106の間のみに実施され得ることに留意されたい。40

## 【0122】

n+2 RXCLK4118において、スレーブデバイスは、SDAライン4126を解放してよい。

## 【0123】

n+2 RXCLK4118とn+3 RXCLK4120との間で、マスタデバイスは、そのSDAラインドライバを再有効化してよく、SDAライン4126をハイに駆動し始める。その結果として、レシーバデバイス(たとえば、アサートしているスレーブデバイス)は、n+3 RXCLK4120においてSDAマスク4124を安全に解放することができる。

## 【0124】

50

$n+3$  RXCLK4120において、スレーブデバイスは、SDAマスク4124を解放してよい。このようにして、SIDスキャン応答は、SDAライン4126上で規定された応答期間4106の間、スレーブデバイスによって送信され得る。

#### 【0125】

図42は、3進数2222\_2221\_2101<sub>3</sub>(16進の0x81B8F)を使用するためにCCleプロトコルによって使用され得る可能なSIDスキャン応答ワードを示す表4200である。

#### 【0126】

##### IRQグループ照会

IRQをアサートしているスレーブデバイスを識別するために、スレーブデバイスは「グループ」が割り当てられてよく、または「グループ」に関連付けられてよい。したがって、マスタデバイスは、IRQ要求をアサートしたスレーブデバイスを識別するための照会を送ってよい。IRQをアサートしたスレーブデバイスは、その割り当てられたグループ内の照会のみに応答してよく、それによって、マスタデバイスに対してアサートしているスレーブデバイスを識別する。10

#### 【0127】

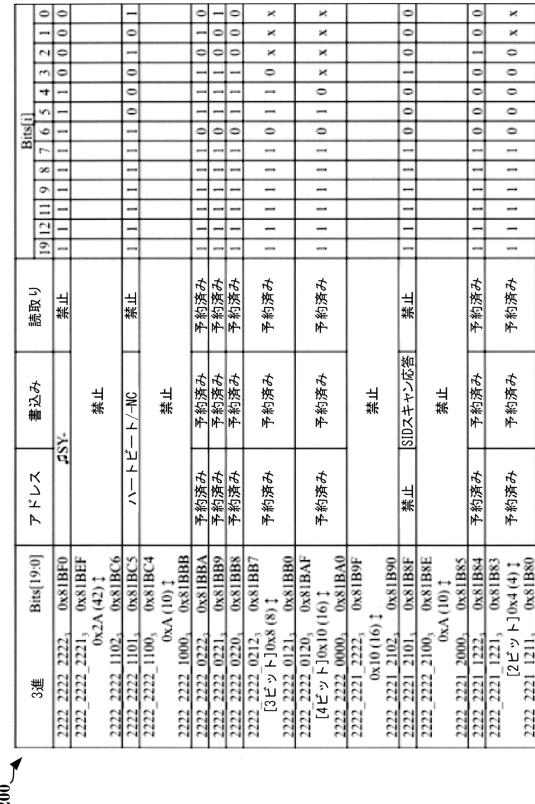

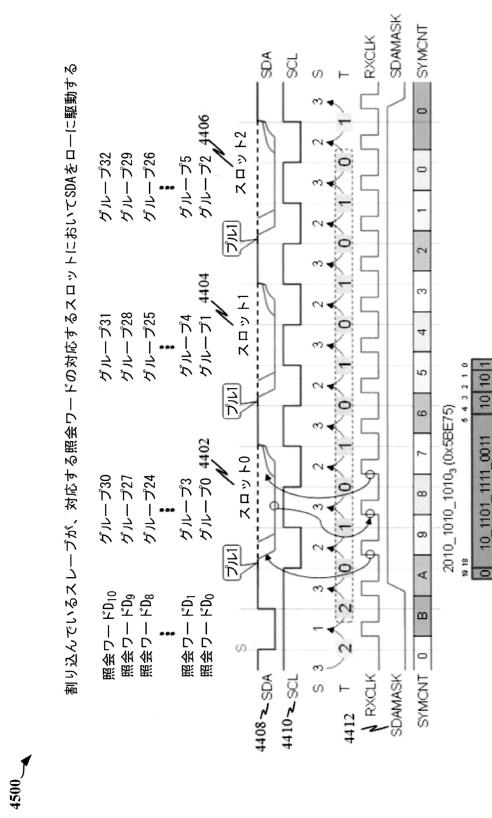

図43は、例示的なCCleプロトコル内でのIRQグループ照会の一斉呼出しを示す図4300である。マスタデバイスは、一斉呼出しのIRQグループ照会4320を共有バス上のすべてのスレーブデバイスにブロードキャストしてよい。IRQグループ照会コマンド4302の16進で0x007に続き、複数のIRQグループ照会ワード4304が送られる。一例では、各照会ワードは3個の照会応答スロットを有し、グループ0～グループ32に対して全体で33個のスロットを有する。一例では、照会ワード4304は、1～11個のIRQグループ照会ワード(IQ)と、最後に1個の終止ワード(Term)4306とを含み得る。終止ワード4400の一例が、図44に示される。各照会ワード4304に対して、すべてのスレーブデバイスは、共有バスのSDAラインをマスクする。一斉呼出しのペイロード4304の各IRQグループ照会(IQ)ワード4308において、各スレーブレシーバは、T<sub>11</sub> RXCLKにおいてSDAをマスクし始めなければならず、ダミー(T<sub>-1</sub>)RXCLKにおいてマスクを解放しなければならない。20

#### 【0128】

図43に示す例では、呼出しのメッセージタイプが値0x7を有するとき、IRQグループ照会が決定され得る。言及したように、3つの異なるIRQグループに割り当てられた一斉呼出しのペイロードの各IQワードの中に、3つのタイムスロットが存在し得る。各スロットにおいて、割り当てられた各グループの中の1つまたは複数のスレーブデバイスは、スレーブデバイスがIRQを発行したこと、またはサービスされていないIRQをスレーブデバイスが有することを示すための照会応答として、SDAラインを駆動することができる。マスタデバイスは、IRQグループ照会(IQ)ワードの数を、バスに関連するIRQグループの数に基づいて選んでよい。30

#### 【0129】

いくつかの事例では、または必要に応じて、マスタデバイスは、すべての既存のグループを包含するために必要とされるシーケンス長よりも短い照会ワードシーケンスを送ってよい。一例では、より短い照会ワードシーケンスが送られて、頻繁で短いレイテンシペントを得るために照会時間を短くしてよく、全部の照会が、バス上のすべてのグループを包含するほど頻繁には実行されないことがある。IRQグループ照会(IQ)ワードのシーケンスは、終止ワード(Term)とともに完結し得る。40

#### 【0130】

図44に示すように、終止ワード4400のシンボルパターンは、いつSDAをマスクすることをやめIRQグループ照会一斉呼出し処理を終了するべきかをレシーバが知るようなロケーションT<sub>11</sub>におけるIRQグループ照会(IQ)ではなく、各レシーバがワードが終止ワード4400(すなわち、Termワード4306)であることを認識できるように選ばれてよい。終止(Termワード4400)方式を使用することは、ペイロードの長さがフレキシブルに設定されることを可能にし、IRQグループ照会(IQ)ワードシーケンスの長さは、必要なら11ワードを上回ることができる。50

## 【0131】

スレーブデバイスにおいてSDAMASK信号4124、4424の可変長での送信および活動化に関する論理および意思決定を簡単にするために、IRQグループ照会呼出しは、いくつかのワードに対するビット値を規定し得る。一例では、RESPワード4006(図40参照)と、一斉呼出しに関連したいくつかの他のワードとの間の差異は、図41に示すRESPワードの初期シンボル4103と、図44に示すTermワード4306(図43参照)の初期シンボル4403との間の差異において観測され得る。すなわち、対応する送信されたシンボル4104と4404とのシーケンスの第1の(最上位の)シンボル4103と4403との間で明らかである差異は、全体のワードの復号が完了する前にSDAMASK信号4124、4424の性質を速やかに決定するためにレシーバによって使用されてよい。特に、スレーブデバイスは、受信されたシンボルシーケンス4104と4404の両方におけるシンボル値{3,1}として、開始条件を検出することができる。開始条件を検出すると、各スレーブデバイスは、スレーブデバイスによって受信されたシンボルの数を追跡するために使用され得るシンボルカウンタ(SYMCNT)4402を初期化してよい。一例では、SYMCNT4402は0xBとしての値を用いて初期化されてよく、SYMCNT4402は受信されたシンボルごとにデクリメントされてよい。したがって、スレーブデバイスは、SYMCNT4402が0xBとしての値を有するときに受信されたシンボル4103または4403の値に基づいて、SDAMASK信号4124、4424の状態を決定し得る。RESPワード4006が受信されているとき、SYMCNT4402が0xBとしての値を有するときにシンボル4103は3としての値を有し、それはSDAMASK信号4124が有効化されるべきであることを示す。Termワード4306が受信されているとき、SYMCNT4402が0xBとしての値を有するときにシンボル4403は3としての値を有さず(ここで、値は0である)、それはSDAMASK信号4424が無効化されるべきであることを示す。RESPワード4006およびTermワード4306を符号化するために使用されるシンボルの構成は、スレーブデバイスがRESPまたは一斉呼出しのシーケンスをオンザフライで終了することを可能にし、それによって、可変長のシーケンスが処理されることを可能にする。10

## 【0132】

いくつかの事例では、第1のIRQグループ照会(IQ)のための3つのスロットが、グループ0、1、および2に割り当てられる。数が小さいグループが、早い応答スロットに割り当てられる。グループ0は、ホットプラグされるデバイスのために、またはマスタがバスシステム上でまだ認識していないデバイスのために予約されてよい。少なくとも1つのIRQグループ照会(IQ)ワードが送られなければならないので、IRQを発行したいかなるホットプラグされたデバイスも、常に認識され得る。20

## 【0133】

図45は、グループ照会呼出しに対する応答を示す。この例では、クロッキングをSCLライン4510に転送するとともにSDAマスク4512を使用することによって、1つまたは複数の応答期間(すなわち、照会ワード)がSDAライン4508上に規定され得る。この例では、3つの別個のスロット4502、4504、および4506が、各照会(IQ)ワード4308(図43参照)に対して規定されている。各IQワード4308の中の3つのタイムスロット4502、4504、および4506の各々は、3つの異なるIRQグループに割り当てられ得る。各スロット4502、4504、および4506に割り当てられたスレーブデバイスは、スレーブデバイスがIRQを発行したこと、またはサービスされていないIRQをスレーブデバイスが有することを示すための照会応答として、割り当てられたスロット4502、4504、および4506の間、SDAライン4508を駆動することができる。各IRQグループ照会ワード4308が3つの照会応答スロット4502、4504、および4506を有するので、最大11個のIRQグループ照会(IQ)ワードが一斉呼出しのペイロード4304の中にあってよく、1つの呼出しの中に最大33個のグループスロットがあつてよい。30

## 【0134】

1つのデバイスだけが1つのグループの中にあるように、最高32個のデバイスがグループに割り当てられてよく、それによって、IRQ発行者が直ちに特定される。この手法は複数のIRQグループを一度に識別し、それによって、必要なIRQスキャンの数を減らす(たとえば、より少ないIRQネスティング)。代替的に、複数のデバイスが各グループに割り当てられてよいが、グループの中の複数のデバイスのうちのどれがIRQを発行したかを識別する4050

ために、追加の照会がマスタデバイスによって必要とされ得る。

#### 【 0 1 3 5 】

マスタデバイスは、バスシステム上のIRQグループの数に基づいて、一斉呼出しに含めるべきIRQグループ照会(IQ)ワードの数を選んでよい。いくつかの例では、マスタデバイスは、(たとえば、11個としての最大数よりも少ない)より少数の照会ワード4308を送信してよい。このことは、IRQグループ照会の一斉呼出しのための時間の短縮を可能にし得る。

#### 【 0 1 3 6 】

IRQグループ照会(IQ)ワードのシーケンスは、終止ワード(Term)4306とともに終了する。各レシーバスレープデバイスが、SDAライン4508をマスクするのをいつ止めるべきかということと、IRQグループ照会の一斉呼出しの終了とを知るために、ワードがT11 RXCLKににおいてIRQグループ照会(IQ)でなく終止(Term)であることを認識できるように、終止ワード4306のシンボルパターンは選ばれてよい。10

#### 【 0 1 3 7 】

第1のIRQグループ照会(IQ)に対する3つのスロット4502、4504、および4506は、グループ0、1、および2に割り当てられてよい。数が小さいグループが、早い応答スロットに割り当てられてよい。

#### 【 0 1 3 8 】

一例では、グループ0は、ホットプラグされるデバイス、または共有バス上でマスタデバイスがまだ認識していないデバイスのために予約されてよい。少なくとも1つのIRQグループ照会(IQ)ワードが送信されなければならないので、IRQを発行したホットプラグされたデバイスは常に認識される。20

#### 【 0 1 3 9 】

終止(Term)ワード4306の使用のおかげで、ペイロード4304の長さはフレキシブルに設定されてよく、IRQグループ照会(IQ)ワードシーケンスの長さは必要であれば11ワードを越えることができる。

#### 【 0 1 4 0 】

IRQグループ照会はサイドバンドIRQのために使用されてよく、ここで、別個のIRQ信号ラインが、割込みサービスを要求するためにスレーブデバイスによって使用され得る。マスタは、要求しているデバイスを、IRQグループ照会を使用して識別することができ、マスタデバイスは、IRQアサーション期間を正確な自走タイマーを用いて測定することによってIRQグループを決定する必要がない。この点で、スレーブデバイスは正確なタイミングを伴うIRQを生成する必要がなく、スレーブデバイスはIRQを調停する必要がない。したがって、スレーブデバイスおよび/またはマスタデバイスは、グループ識別のためのIRQ期間を生み出したりは測定するための正確な自走タイマーを用いずに、動作することができる。30

#### 【 0 1 4 1 】

いくつかの態様によれば、IRQグループ照会は、いかなるグループも調停ロスを受けることなく、複数のグループによる同時のIRQアサーションをサポートすることができる。マスタデバイスはすべてのIRQを直ちに認識することができ、スレーブデバイスは調停ロスの結果としてIRQを反復し続ける必要がない。したがって、スレーブデバイスがアクセスの「枯渇」に遭遇する可能性は小さい。40

#### 【 0 1 4 2 】

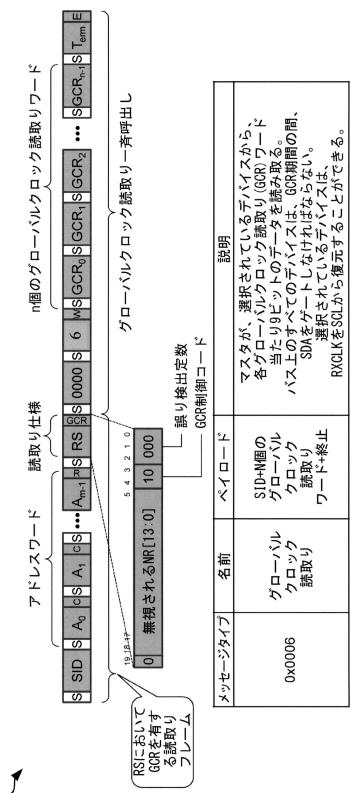

### グローバルクロック読み取り

CC1eは、ソース同期シンボル遷移クロッキングシステムである。制御データバスを介してデータを送るデバイスはまた、データ内に埋め込まれたクロック情報を送る。I2Cとは異なり、すべてのスレーブデバイスは、クロック情報とともに読み取りデータを生成するためにそれら自身のクロックソースを使用しなければならない。たとえば、すべてのスレーブデバイスにSDA入力をマスクさせるとともにスレーブデバイスがSDAラインを駆動することを可能にする間にSCLラインを常にトグルする、IRQグループ照会のための本明細書で説

明する技法はまた、グローバルクロック読取りを実行するために使用され得る。

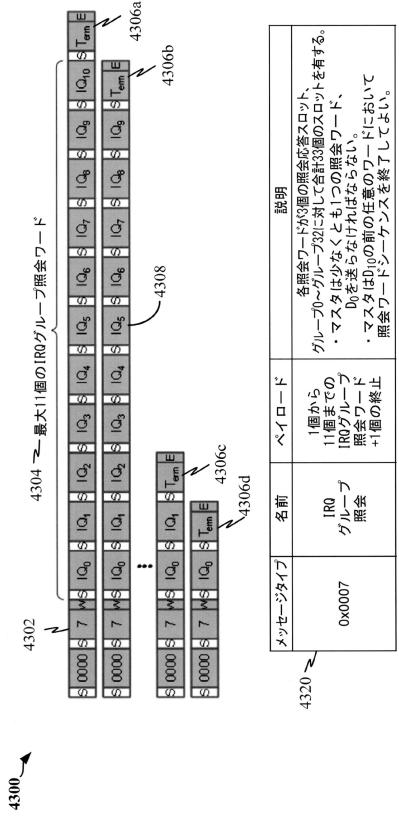

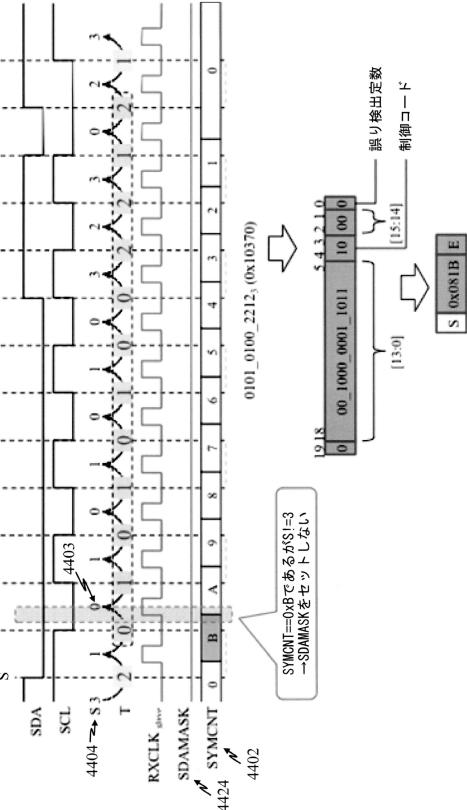

#### 【0143】

図43～図45から諒解され得るように、主に、異なるRXCLKタイミングを伴う複数のスレーブが同じタイムスロット内でSDAラインを駆動することを可能にするために、IRQグループ照会ワードは、3個のスレーブ応答しか搬送しないように限定されてよい。しかしながら、SDAマスクの間に単一のスレーブデバイスだけがSDAラインを駆動することを可能にすることは、ダブルデータレート(DDR)グローバルクロック読取りを実施することを可能にする。

#### 【0144】

図46は、DDRグローバルクロック読取り実装の一例に対応する、グローバルクロック読取りの一斉呼出しの一例4600を示す。DDRグローバルクロック読取りリシーケンスを開始する前に、マスタデバイスは、一斉呼出しなどのいくつかのPCIeプロトコル送信を発行してよい。一斉呼出しの送信は、以下のことを示し得る。

1. 後続のシーケンスがDDRグローバルクロック読取りであること。

2. DDRグローバルクロック読取りのワードの数。

3. データを読み取るべきデバイスのSID。

4. データを読み取るべきデバイスのレジスタアドレス。

#### 【0145】

バス上のデバイスの各々は、特定の数のワードが送られるまで、一斉呼出しの後のPCIeトランザクションのすべてがDDRグローバルクロック読取りに関係することを理解するよう、適合または構成される。

#### 【0146】

DDRグローバルクロックモードでは、バス上のすべてのデバイスは、ワードの終わりにおけるダミーシンボルを含むシンボル期間の間、それらのクロックデータ復元(CDR)回路へのSDA入力をマスクしてよい。アドレス指定されたスレーブデバイスは、(開始条件のそばのRXCLKを含まない)第2のRXCLKパルスにおいてSDAライン318をローに駆動し、その論理0は、SDAラインをサンプリングするためのそのクロック(SDACLK)を較正するためにマスタデバイスによって使用される。第3のRXCLKから、アドレス指定されたスレーブデバイスは、9ビットのデータを連続的に追い出すことができる。9ビットのデータは、システム要件に応じて、MSBが最初であってもLSBが最初であっても他のフォーマットであってよい。この期間の間、マスタデバイスは、SCLライン上でDDRグローバルクロックを供給または駆動する。スレーブデバイスは、第12のRXCLKにおいてSDAライン318をハイに駆動してよく、第13のRXCLKにおいてSDAライン318を解放してよい。

#### 【0147】

マスタデバイスは、第1のシンボル「3」が送信された後、SDAライン318を解放し、最後のシンボル「2」の後、そのSDAドライバを有効にするとともにSDAライン318をハイに駆動する。SDAライン318を解放した後、SDAライン318は、ハイ状態に弱くプルされてよい。マスタは、SDACLKのタイミングにおいてSDAライン318をサンプリングして、読み取られた9個のデータビットをシフトインする。マスタは、最後のシンボル(「2」)の後、シンボル「3」を送信することによってSDAライン318の駆動を再開してよい。

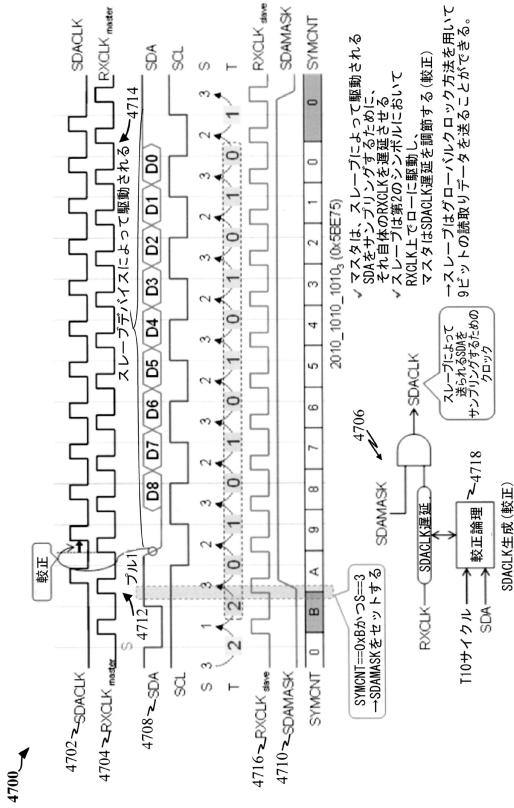

#### 【0148】

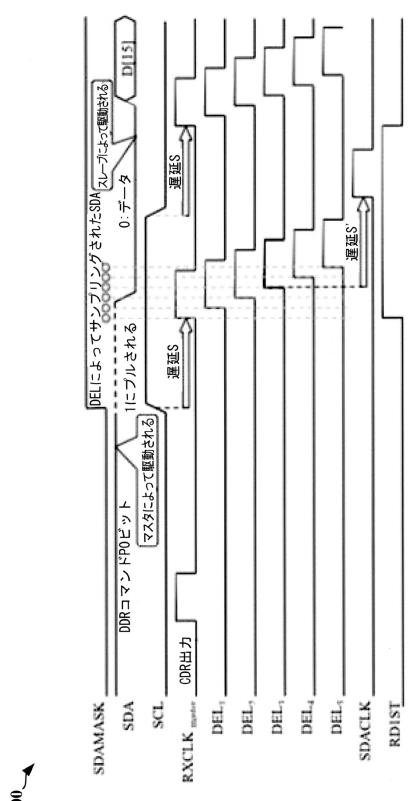

図47は、グローバルクロック読取りワードのいくつかの態様を示すタイミング図である。第1のクロック信号SDACLK4702および第2のクロック信号RXCLK4704は、マスタデバイス内の内部信号を示す。第2のクロック信号RXCLK4704は、マスタデバイスのクロックデータ復元回路(CDR)によって生成され得る。第1のクロック信号SDACLK4702は、スレーブデバイス信号によって駆動されるときに(共有バスの一部である)SDAライン4708からデータ値をサンプリングするためにマスタデバイスによって使用され得る、クロック生成回路4706によって生成され得る。第1のクロック信号SDACLK4702は、SDAMASK信号4710が1である(CDRへのSDAライン4708の入力がマスクされる)ときのみ、生成され得る。

#### 【0149】

10

20

30

40

50

グローバルクロック読取り期間の間にSDAライン4708を駆動するのはスレーブデバイスなので、バス上のすべてのデバイス(マスタデバイスを含む)は、この期間の間はCDRへのSDAライン4708入力をマスクし、その期間は、開始条件から立ち上がる(4712)第2のクロック信号RXCLKにおいて開始し、ダミーシンボルのそばのワードに対する最後のRXCLKの立ち上がり4714において終了する。

#### 【0150】

この例では、マスタデバイスは、グローバルクロック読取りワードに対して $0x5BE75(20\ 10\_1010\_1010_3)$ を送る。これはグローバルクロック読取りの一音呼出しのペイロード部分であるので、共有バス上の各デバイスは、グローバルクロック読取りワードが呼出しメッセージ「6」の後に続くことを知っており、各デバイスは、SDAMASK4710をいつ開始し終了すべきかも知っている。10

#### 【0151】

場合によっては、SDACLK4702は、SDAライン318での読取りデータターンアラウンド遅延に対処するように、マスタデバイスにおいてそのRXCLK4704に対する遅延を伴って生成されてよい。第1の知られているデータ(たとえば、SDAライン318での1から0への立下り)のターンアラウンド遅延をマスタデバイスにおいて測定することによって、遅延の持続時間は最適にされ得る。

#### 【0152】

場合によっては、スレーブデバイスは、グローバル呼出しの後でのみ、各グローバルクロック読取りワードにおいてSDAMASKを活動化させてよい。SDAライン318をマスクすることは、アドレス指定されていないバス上の任意のスレーブデバイスがGCRワードデータによって影響を受けないことを防ぐことができる(各スレーブによる $2010\_1010\_1010_3$ として見られる)。20

#### 【0153】

各デバイスは、次のワードが第1のシンボルにおいて別個の信号パターンを有する「終止」ワードではない限り、次のワードのためのグローバルクロック読取りワードを予期する。

#### 【0154】

SDAライン4708上のデータ信号はスレーブデバイスのCDRからのRXCLK4716を使用してスレーブデバイスによって駆動されるので、マスタデバイスは、マスタデバイスが十分なセットアップタイムおよびホールドタイムを伴ってデータをサンプリングするために、マスタデバイスのCDRからの第2のクロック信号RXCLK4704を「適切に」遅延させなければならない。マスタデバイスは、マスタデバイスがグローバルクロック読取りワードの第2のシンボル(すなわち、T10サイクル)を送出した後、グローバルクロック読取りプロトコルごとにスレーブデバイスによって駆動されるSDAライン4708の第1の立ち下がりエッジにおける「適切な」遅延を学習する。「較正論理」4718は、T10サイクルの開始からのSDAライン4708の立ち下がりの遅延を測定し、マスタデバイスが次のシンボルからスレーブデバイスからのSDAライン4708の送信を確実にサンプリングするように、「SDACLK遅延」を構成するためにその遅延を使用した。30

#### 【0155】

グローバルクロック読取りの他の態様および使用

いくつかのシリアルバスインターフェースは、シリアルバス上のスループットを高めるための手段としてDDR送信クロックを使用するように適合され得る。送信クロックの周波数も高められ得る。一例では、シリアル通信バスのスループットは、SCLワイヤ316上で送信されるクロック信号のサイクルごとに2つのビットを送信することによって高められ得る。この例では、レシーバは、負の遷移と正の遷移とを使用してデータをサンプリングし得る。別の例では、CClueバスなどは、送信クロックサイクルごとに2つのシンボルを送信するように適合され得る。DDRクロックを採用するインターフェースにおけるより高い周波数では、信号立ち上がり時間に割り振られる送信クロックサイクルの比率の増大、および伝搬時間の差異に関連する信号スキューなどに起因して、シグナリング問題が生じること4050

とがある。

#### 【0156】

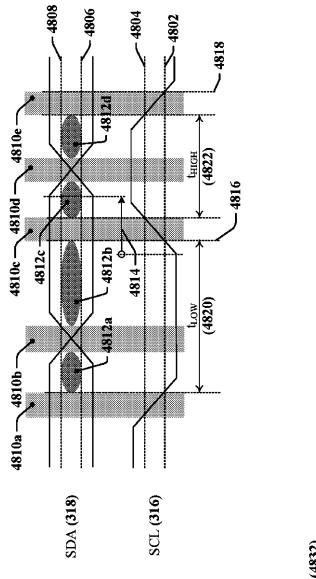

図48は、高スループットインターフェースにおけるタイミングを示す。第1のタイミング図4800は、SCLワイヤ316上で送信されるDDRクロックに従ってデータがSDAワイヤ318上で送信されるシリアルバスインターフェースに関する。第1のタイミング図4800によって表されるインターフェースは、より高速なスレーブデバイスが従来のI2Cデバイスと共に存することを可能にし得る。

#### 【0157】

I2Cデバイスとの共存は、SCL信号316上のパルスがI2Cデバイスによって認識されるほど十分長くハイ状態4822にとどまることを防止することによって実現され得る。ハイ状態4822の持続時間( $t_{HIGH}$ )は、SCL信号316の立ち上がりエッジが電圧レベル(Vdd)の30%に到達する時間4816から、SCL信号316の立ち下がりエッジが電圧レベルの30%に到達する時間4818まで測定されてよい。I2Cプロトコルは、SCL信号316上およびSDA信号318上のパルスに対する最大持続時間( $t_{SP}=50\text{ns}$ )を規定し、I2Cデバイスは、SCL信号316上およびSDA信号318上の、持続時間が50nsよりも短いパルスを阻止するスパイクフィルタを有する。したがつて、SCL信号316上のクロックパルスの持続時間が50nsよりも短いとき、I2Cデバイスとの共存が成し遂げられ得る。

#### 【0158】

I2Cデバイスとの共存が望ましいとき、DDRクロック制御されるインターフェースは、SCL信号316に対して最小ロー期間( $t_{LOW}$ )4820を維持するように適合されてよく、その結果、クロックサイクルの中に残っている時間がSCL信号316上のエッジの立ち上がり時間および立ち下がり時間を占めるように割り振られ得る。SCL信号316の立ち上がり時間に対して割り振られる時間は、論理ローから論理ローと論理ハイとの間の電圧の30%である第1のスイッチング電圧レベル4802に遷移するために必要な時間に相当し得る。SCL信号316の立ち下がり時間に対して割り振られる時間は、論理ハイから論理ローと論理ハイとの間の電圧の70%である第2のスイッチング電圧レベル4804に遷移するために必要な時間に相当し得る。立ち上がり時間および立ち下がり時間は、SDA信号のタイミングにも影響を及ぼす。

#### 【0159】

SDA信号318の立ち上がり時間に対して割り振られる時間は、論理ローから論理ローと論理ハイとの間の電圧の30%である第1のスイッチング電圧レベル4806に遷移するために必要な時間に相当し得る。SDA信号318の立ち下がり時間に対して割り振られる時間は、論理ハイから論理ローと論理ハイとの間の電圧の70%である第2のスイッチング電圧レベル4808に遷移するために必要な時間に相当し得る。

#### 【0160】

アイ開口4812a、4812b、4812c、4812dの持続時間( $t_{eye}$ )は、残りのクロック期間( $t_{SP}$ )と、SCL立ち上がり点(30%)からSCL立ち下がり点(70%)までとの間の差分として計算され得る。アイ開口4812a、4812b、4812c、4812dは、開口が立ち下がりエッジに対して起こるのか、それとも立ち上がりエッジに対して起こるのかに応じて、持続時間が変わることがある。

#### 【0161】

アイ開口4812a、4812b、4812c、4812dの持続時間は、読み取り動作および書き込み動作に対して異なる影響を有し得る。SCL信号がハイ論理状態にある期間の最小持続時間( $t_{HIGH}$ )4816は、書き込み動作の間、ほとんど重要であり得ない。読み取り動作の場合、 $t_{HIGH}$ 4816の値は、アイ開口4812a、4812b、4812c、4812dに対する最小持続時間を保証するように規定されてよい。

#### 【0162】

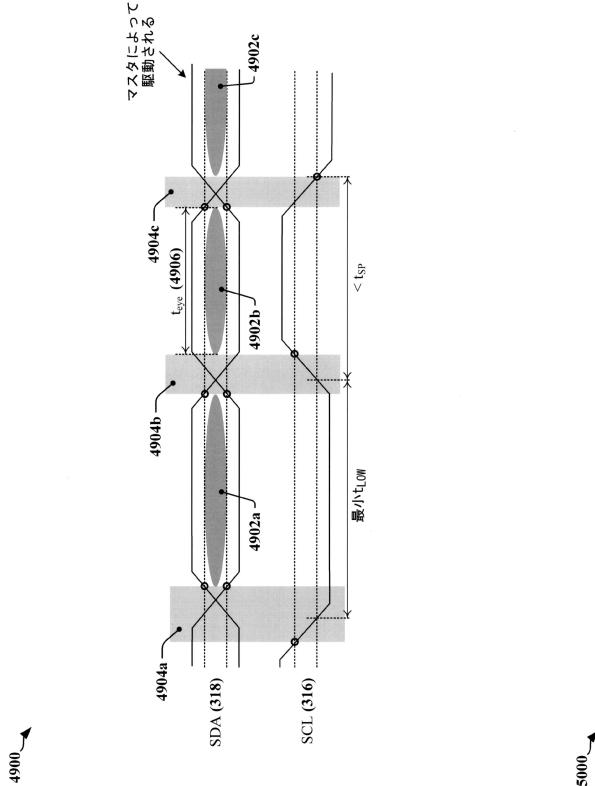

図49～図51を参照すると、シリアルバスインターフェースは、SCLワイヤ316上およびSDAワイヤ318上で送信される信号を位置合わせすることによってアイ開口を改善するために、本明細書で開示するいくつかの態様に従って適合され得る。図49におけるタイミング図4900は、SCLワイヤ316上およびSDAワイヤ318上の信号が書き込み動作の間に位置合わせされ

10

20

30

40

50

るインターフェースを示す。すなわち、マスタデバイスは、SCLワイヤ316上のクロック信号に加えて、SDAワイヤ318上で信号を送信する。図49におけるタイミング図4900は、SCLワイヤ316上およびSDA318上の信号が位置合わせされるインターフェースを示す。SCLワイヤ316上およびSDAワイヤ318上の信号の位置合わせは、位置合わせされないシグナリングの場合よりも大きい $t_{eye}$ 4906をもたらすことができる。シリアルバス上で送信されるデータビットを確実にサンプリングするために、CDR回路が採用され得る。

#### 【0163】

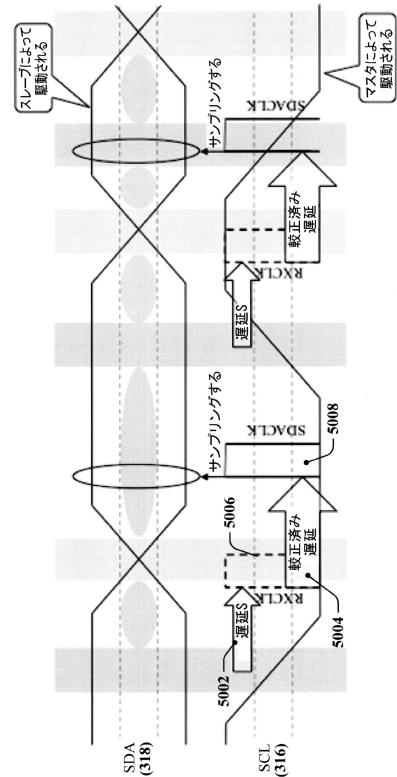

図50におけるタイミング図5000は、SCLワイヤ316上およびSDAワイヤ318上の信号が読み取り動作の間にマスタデバイスにおいて位置合わせされるインターフェースを示す。ここで、スレーブデバイスがSDAワイヤ318上で信号を送信する間、マスタデバイスは、SCLワイヤ316上でクロック信号を送信する。スレーブデバイスは、SCL信号316における遷移からRXCLK信号を生成するCDRを含む。読み取り動作の間、SDA信号318は、CDR入力部においてマスクされる。スレーブにおいて生成される受信クロックを使用してスレーブがSDA信号318を生成し、SDA信号318がSCL信号316における対応する遷移に対して遅延した遷移を有するので、SDA信号318における遷移は、SCL信号316における遷移との位置合わせから外れていることがある。タイミング図5000は、SDA信号318に対する、その内部的に生成されるSDACLKのマスタデバイスにおいて実行される位置合わせを示す。

#### 【0164】

図示の例では、1つまたは複数のクロックをマスタデバイス上で較正することによって、位置合わせが実現され得る。マスタデバイス上のCDR回路は、SCLワイヤ316上の信号の遷移に基づいて、受信クロック(RXCLK)上にパルス5006を生成するように構成され得る。RXCLKは、1つまたは複数の遅延5002を使用して、SCLワイヤ316上の遷移に対して遅延され得る。SDAワイヤ318からのCDR回路への入力は、読み取り動作の間、マスクされ得る。RXCLK上のパルス5006は、SDAワイヤ318をサンプリングするために使用されるクロック(SDACLK)上のパルス5008を生成するために、較正済み遅延5004をさらに使用して遅延され得る。SDACLKは、SDAワイヤ318から読み取られる最初のビットにおいて、較正済み遅延5004を構成することによって較正され得る。図51は、高速シリアルインターフェースに対して較正済み遅延5004を使用する効果を示す。較正済み遅延5004を用いたSDACLK生成は、マスタデバイスのRX端の中のレシーバ回路においてクロックタイミングを制御することによって、SCLワイヤ316上およびSDAワイヤ318上の信号を実質的に位置合わせすることができる。アイ開口は、そのような較正を使用して最大化され得る。

#### 【0165】

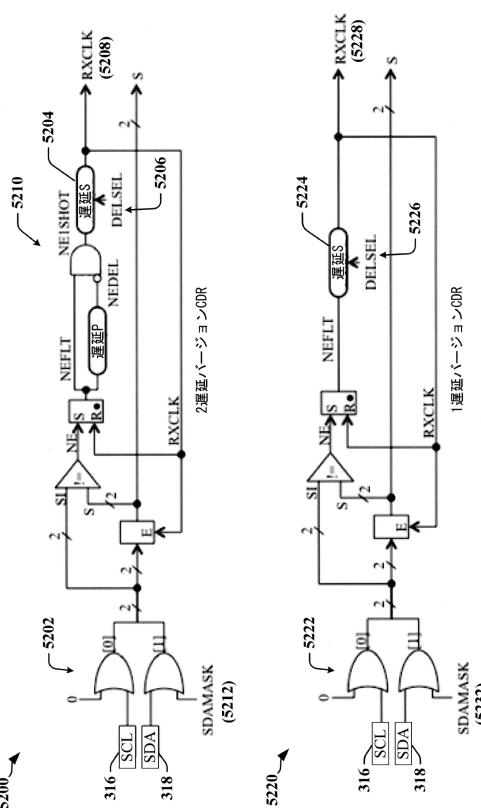

図52は、本明細書で開示するいくつかの態様に従って適合され得るCDR回路5200、5220の例を提供する。CDR回路5200、5220は、出力RXCLK信号5208、5228上にパルスを生成することによって動作し得る。2遅延CDR回路5200は、存在する場合、信号遷移の検出の後のいくらかの時間期間にわたって、SCLワイヤ316上および/またはSDAワイヤ318上のグリッチを除去できるワンショット回路5210の中で使用される遅延要素を有し得る。1遅延回路5220は、ワンショット回路5210を省略し得る。CDR回路5200、5220は、読み取り動作の間、SDAワイヤ318からの入力を阻止するように制御され得るマスキング論理5202、5222を有する。すなわち、読み取り動作の間のみ、SCL信号316における遷移に基づいてRXCLK信号5208、5228が生成され得る。CDR回路5200、5220は、モードへ入ること、モードから出ること、および再起動の条件を決定するための、追加の論理および回路を採用してよい。CDR回路5200、5220は、制御信号5206、5226によって構成され得る遅延回路5204、5224を含み得る。

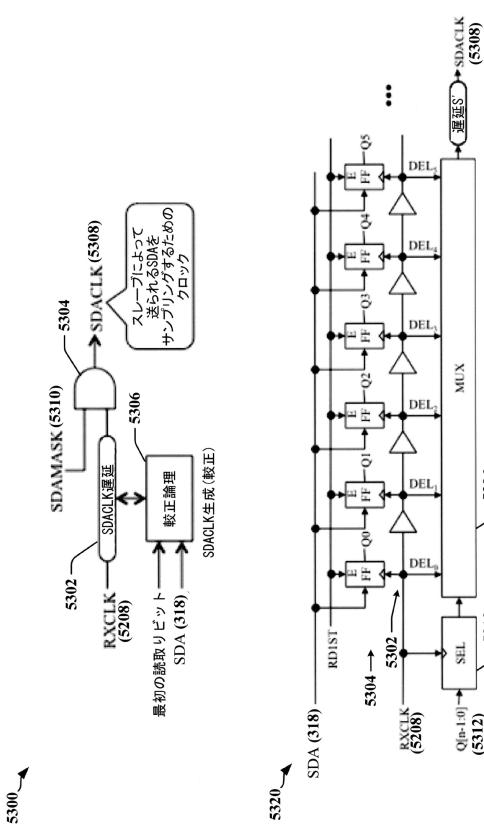

#### 【0166】

図53は、マスタデバイスの中でクロック信号を位置合わせするために使用され得る較正済み遅延回路のいくつかの態様を示す。図54は、図53における回路5320に関連するタイミングを示す。制御回路5300は、RXCLK5208からのSDACLK5308の生成を可能にする。RXCLK5208が、較正論理5306によって制御される遅延回路5302に供給され、遅延回路5302は、RXCLK5208に適用されるべき適切なまたは決定された遅延を選択する。イネーブル信号5310は、読み取り動作の間、SDAワイヤ318からの入力をマスクオフするために使用されるSDAMASK

10

20

30

40

50

信号に基づいてよく、SDACLK5308が供給されるべきかどうかを決定する。

#### 【0167】

制御回路5300のSDACLK遅延要素5302を実装するために、プログラマブル遅延回路5320が使用され得る。直列接続バッファを使用して実装され得る遅延線5302にRXCLK5208が供給され得、各バッファの出力は、他のバッファの出力とは異なる遅延を有するRXCLK5208のバージョンを供給する。バッファの出力は、フリップフロップ5304を使用してSDAワイヤ318上の信号をサンプリングするために使用され得る。マルチプレクサ5306は、RXCLK5208の選択された遅延したバージョンを供給するために、選択(較正)論理5310によって制御され得、RXCLK5208がさらに遅延されてSDACLK5308を生成し得る。選択論理5310は、較正期間の間、フリップフロップ5304の出力の状態5312に基づいて決定される選択値を出力し得る。この例では、マスタデバイスは、SCLワイヤ316へのそれ自体の出力からRXCLK5208を生成し得る。SDACLK5308は、較正論理5306を使用して遅延が最適化されている、RXCLK5208の遅延したバージョンである。DDR読取りコマンドの後に駆動される最初のDDR読取りビットの間に、較正が行われ得る。アドレス指定されたスレーブは、較正を容易にするためにSDA状態をトグルするように構成されてよい。10

#### 【0168】

いくつかの態様によれば、SDACLK5308の較正は、アイ開口のサイズを最適化し得、広いスルーマージンに対処し得る。CDR回路の使用は、遷移グリッチ耐性をもたらすことができる。較正済みSDACLK5308は、SDAワイヤ318からのビット取込みを可能にするための位相シフトを必要としない。20

#### 【0169】

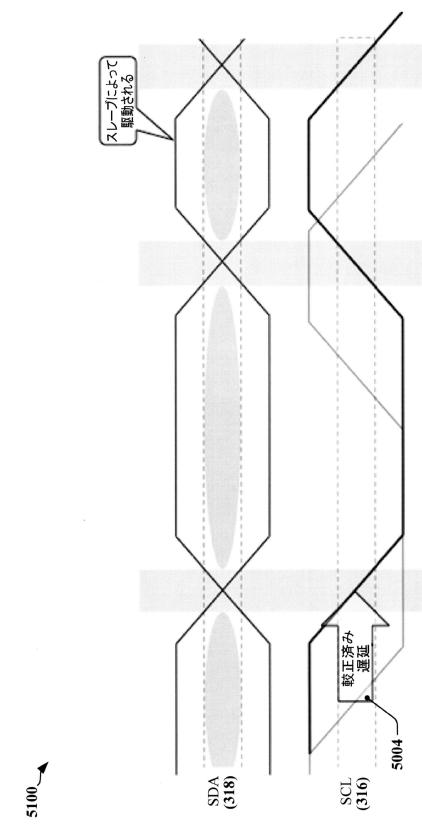

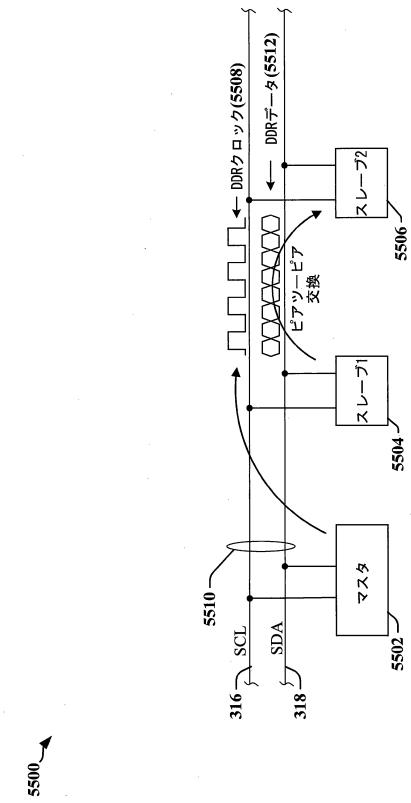

図55は、スレーブデバイスが較正済み受信クロックを使用するように適合され得るピアツーピアDDRデータ転送の例5500を示す。例5500では、シリアルバス上のデータ通信は、マスタデバイス5502によって制御され、マスタデバイス5502は、シリアルバス5510のSCLライン316上にDDRクロック信号5508を供給するように適合され得る。2つのスレーブデバイス5504および5506は、スレーブデバイス5504と5506との間で、マスタデバイス5502を通過することなくデータが直接交換され得るように構成され得る。マスタデバイス5502によって供給されるクロック信号5508は、データのこのピアツーピア交換を制御する。交換がDDR転送であるとき、受信スレーブデバイス5506は、マスタデバイス5502による読み取り動作に関して本明細書で説明することと類似の問題に遭遇することがある。すなわち、送信スレーブデバイス5504によって使用されるクロック信号は、SCLライン316上に供給されたクロック5508の遅延したバージョンであり得る。受信スレーブデバイス5506は、SDAライン518上で送信されるDDRデータ5512を最適にサンプリングするために、その内部的に生成される受信クロックを較正し得る。したがって、受信スレーブデバイス5506は、図52に示すCDR回路および/または図53に示す較正回路のうちの1つまたは複数を使用するように適合され得る。30

#### 【0170】

共通IRQバスを伴う装置、システムおよび方法の例

図56は、本明細書で開示する1つまたは複数の機能を実行するように構成され得る処理回路5602を採用する装置のためのハードウェア実施態様の簡略化された例を示す概念図5600である。本開示の様々な態様によれば、共通IRQバスを使用して割込みを管理または開始するための本明細書で開示するような要素、または要素の任意の部分、または要素の任意の組合せは、処理回路5602を使用して実施され得る。処理回路5602は、ハードウェアモジュールとソフトウェアモジュールの何らかの組合せによって制御される1つまたは複数のプロセッサ5604を含んでよい。プロセッサ5604の例は、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ(DSP)、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブル論理デバイス(PLD)、ステートマシン、シーケンサ、ゲート論理、個別ハードウェア回路、および本開示全体にわたって説明する様々な機能を実施するように構成された他の適切なハードウェアを含む。1つまたは複数のプロセッサ5604は、特定の機能を実施し、ソフトウェアモジュール5616のうちの1つによって構成され、増強され4050

、または制御されてよい専用プロセッサを含んでよい。たとえば、処理回路は、1つまたは複数のワイヤレスネットワーク上の送信のためのデータの符号化および復号を処理するよう適応され得る通信プロセッサまたは別のタイプのプロセッサとして構成されてよい。1つまたは複数のプロセッサ5604は、初期化の間にロードされる1つまたは複数のソフトウェアモジュール5616の組合せを通じて構成されてよく、動作の間にソフトウェアモジュール5616のうちの1つまたは複数をロードまたはアンロードすることによってさらに構成されてもよい。

#### 【0171】

図示の例では、処理回路5602は、バス5610によって概略的に表されるバスアーキテクチャを用いて実装されてよい。バス5610は、処理回路5602の特定の適用例および全体的な設計制約に応じて、任意の数の相互接続するバスおよびブリッジを含んでよい。バス5610は、1つまたは複数のプロセッサ5604および記憶装置5606を含む様々な回路を互いにリンクする。記憶装置5606は、メモリデバイスおよび大容量記憶デバイスを含んでよく、本明細書ではコンピュータ可読媒体と呼ばれることがある。バス5610はまた、タイミングソース、タイマー、周辺装置、電圧レギュレータ、および電力管理回路などの様々な他の回路をリンクし得る。バスインターフェース5608は、バス5610と1つまたは複数のトランシーバまたはラインインターフェース回路5612との間のインターフェースを提供し得る。ラインインターフェース回路5612は、マルチワイヤシリアルバスを含んでよい伝送媒体を介して、様々な他の装置と通信する際に使用される差動ラインドライバおよびレシーバ、CDR、エンコーダおよびデコーダを含んでよい。装置の性質に応じて、ユーザインターフェース5618(たとえば、キーパッド、ディスプレイ、スピーカー、マイクロフォン、ジョイスティック)も備えられてよく、バス5610に直接またはバスインターフェース5608を通じて通信可能に結合されてもよい。10

#### 【0172】

プロセッサ5604は、バス5610を管理すること、および/または記憶装置5606を含むことがあるコンピュータ可読媒体に記憶されたソフトウェアの実行を含んでよい一般的な処理を担当してよい。この点で、プロセッサ5604を含む処理回路5602は、本明細書で開示する方法、機能および技法のうちのいずれかを実装するために使用されてよい。記憶装置5606は、ソフトウェアを実行するとき、プロセッサ5604によって操作されるデータを記憶するために使用されてよく、ソフトウェアは、本明細書で開示する方法のうちの任意の1つを実施するように構成されてよい。20

#### 【0173】

処理回路5602の中の1つまたは複数のプロセッサ5604は、ソフトウェアを実行してよい。ソフトウェアは、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、ハードウェア記述言語、または他の名称で呼ばれるかどうかにかかわらず、命令、命令セット、コード、コードセグメント、プログラムコード、プログラム、サブプログラム、ソフトウェアモジュール、アプリケーション、ソフトウェアアプリケーション、ソフトウェアパッケージ、ルーチン、サブルーチン、オブジェクト、実行ファイル、実行スレッド、プロシージャ、関数、アルゴリズムなどを意味するように広く解釈されるものとする。ソフトウェアは、コンピュータ可読の形で記憶装置5606の中または外部コンピュータ可読媒体の中に常駐してもよい。コンピュータ可読媒体および/または記憶装置5606は、非一時的コンピュータ可読媒体であってよい。非一時的コンピュータ可読媒体は、例として、磁気記憶デバイス(たとえば、ハードディスク、フロッピーディスク、磁気ストリップ)、光ディスク(たとえば、コンパクトディスク(CD)またはデジタル多用途ディスク(DVD))、スマートカード、フラッシュメモリデバイス(たとえば、「フラッシュドライブ」、カード、スティック、またはキードライブ)、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、プログラマブルROM(PROM)、消去可能PROM(EPROM)、電気的消去可能PROM(EEPROM)、レジスタ、リムーバブルディスク、およびコンピュータがアクセスし読み取ってもよいソフトウェアおよび/または命令を記憶するための任意の他の適切な媒体を含む。コンピュータ可読媒体および/または記憶装置5606はまた、例として、搬送波、伝送線路、および30

、コンピュータがアクセスし読み取ってもよいソフトウェアおよび/または命令を送信するための任意の他の適切な媒体を含んでよい。コンピュータ可読媒体および/または記憶装置5606は、処理回路5602の中に存在するか、プロセッサ5604の中に存在するか、処理回路5602の外部に存在するか、または処理回路5602を含む複数のエンティティにわたって分散されてもよい。コンピュータ可読媒体および/または記憶装置5606は、コンピュータプログラム製品で実施されてよい。例として、コンピュータプログラム製品は、パッケージング材料の中のコンピュータ可読媒体を含んでよい。当業者は、特定の適用例および全体的なシステムに課された全体的な設計制約に応じて、本開示全体にわたって提示された記載の機能を最もよく実装する方法を認識されよう。

## 【0174】

10

記憶装置5606は、本明細書でソフトウェアモジュール5616と呼ばれることがある、ロード可能なコードセグメント、モジュール、アプリケーション、プログラムなどにおいて維持および/または編成されるソフトウェアを維持してよい。ソフトウェアモジュール5616の各々は、処理回路5602にインストールまたはロードされ、1つまたは複数のプロセッサ5604によって実行されるとき、1つまたは複数のプロセッサ5604の動作を制御するランタイムイメージ5614に寄与する命令およびデータを含んでよい。実行されるとき、いくつかの命令は、処理回路5602に、本明細書で説明するいくつかの方法、アルゴリズムおよびプロセスに従って機能を実行させてよい。

## 【0175】

20

ソフトウェアモジュール5616の一部は、処理回路5602の初期化の間にロードされてよく、これらのソフトウェアモジュール5616は、本明細書に開示する様々な機能の実行を可能にするように処理回路5602を構成してもよい。たとえば、いくつかのソフトウェアモジュール5616は、プロセッサ5604の内部デバイスおよび/または論理回路5622を構成してよく、ラインインターフェース回路5612、バスインターフェース5608、ユーザインターフェース5618、タイマー、数学コプロセッサなどの外部デバイスへのアクセスを管理してもよい。ソフトウェアモジュール5616は、割込みハンドラおよびデバイスドライバと対話するとともに、処理回路5602によって提供される様々なリソースへのアクセスを制御する、制御プログラムおよび/またはオペレーティングシステムを含んでよい。リソースは、メモリ、処理時間、ラインインターフェース5612へのアクセス、ユーザインターフェース5618などを含んでよい。

## 【0176】

30

処理回路5602の1つまたは複数のプロセッサ5604は、多機能であってもよく、それにおいて、ソフトウェアモジュール5616の一部は、異なる機能または同じ機能の異なるインスタンスを実行するようにロードおよび構成される。1つまたは複数のプロセッサ5604はさらに、たとえば、ユーザインターフェース5618、ラインインターフェース回路5612、およびデバイスドライバからの入力に応答して開始されたバックグラウンドタスクを管理するように適合されてよい。複数の機能の実行をサポートするために、1つまたは複数のプロセッサ5604は、マルチタスク環境を提供するように構成されてよく、それにおいて、複数の機能の各々が、必要または要望に応じて、1つまたは複数のプロセッサ5604によってサービスされるタスクのセットとして実装される。一例では、マルチタスク環境は、異なるタスク間でプロセッサ5604の制御を渡す時分割プログラム5620を使用して実装されてよく、それにおいて、各タスクは、任意の未処理動作が完了すると、および/または割込みなどの入力に応答して、時分割プログラム5620に1つまたは複数のプロセッサ5604の制御を戻す。タスクが1つまたは複数のプロセッサ5604の制御を有するとき、処理回路は、事实上、制御しているタスクに関連した機能によって対処される目的に事实上特化される。時分割プログラム5620は、オペレーティングシステム、ラウンドロビンベースで制御を移すメインループ、機能の優先順位付けに従って1つもしくは複数のプロセッサ5604の制御を割り振る機能、および/または、1つもしくは複数のプロセッサ5604の制御を処理機能に提供することによって外部イベントに応答する割込み駆動のメインループを含んでよい。

## 【0177】

40

50

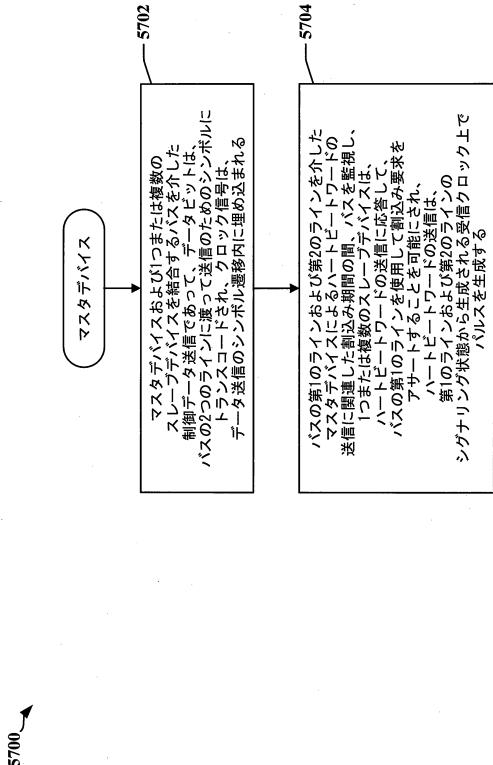

図57は、本明細書で開示するいくつかの態様による、インバンドIRQをアサート、受信、および/または処理するための方法の第1の例を示すフローチャート5700である。方法は、たとえば、マスタデバイス、またはマスタデバイスとスレーブデバイスの組合せによって実施され得る。

#### 【0178】

ロック5702において、バスを介したマスタデバイスからのデータ送信が制御され得る。データビットは、バスの2つのラインに渡って送信のためのシンボルにトランスコードされてよく、クロック信号は、データ送信のシンボル遷移内に埋め込まれる。

#### 【0179】

ロック5704において、バスの第1のラインおよび第2のラインを介したマスタデバイスによるハートビートワードの送信に関連した割込み期間の間、バスが監視され得る。1つまたは複数のスレーブデバイスは、ハートビートワードの送信に応答して、バスの第1のラインを使用して割込み要求をアサートすることを可能にされ得る。ハートビートワードの送信は、バスがアイドル動作モードにある間に、第1のラインおよび第2のラインのシグナリング状態から生成される受信クロック上でパルスを生成し得る。10

#### 【0180】

いくつかの例では、ハートビートワードは、最上位ビットが第1の論理値に設定された20ビットワードのセットの中から選択され得る。マスタデバイスと1つまたは複数のスレーブデバイスとの間で送信されるペイロードデータは、最上位ビットが第2の論理レベルに設定された20ビットワードを含み得る。1つまたは複数のスレーブデバイスは、バスの第1のラインおよび第2のラインの上で応答ワードを送信することによって、割込み要求をアサートするように適合され得る。応答ワードは、ハートビートワードと1ビットだけ異なっていてよく、ハートビートワードの最上位ビットと同一の最上位ビットを有する。20

#### 【0181】

別の例では、1つまたは複数のスレーブデバイスは、バスから受信されたトランスコードされているデータビットを復号するための割込み期間の間、第1のラインを内部的にマスクするように適合され得る。スレーブ識別子スキャン応答期間が提供され得、そのスレーブ識別子スキャン応答期間の間に、バスの第1のラインおよび第2のラインを介してマスタデバイスによって開始されたスレーブ識別子スキャンの一部の中で、バスに結合されている1つまたは複数のスレーブデバイスがそれらの一意の識別子をバスの第1のラインを介して提供することができる。30

#### 【0182】

別の例では、1つまたは複数のスレーブデバイスの各々は、第1のデータラインをマスクするように構成され得る。SIDスキャン応答期間は、バス上のグローバル呼出しの送信の間に提供され得る。1つまたは複数のスレーブデバイスの各々は、グローバル呼出しがバス上で送信された後、応答を送信しているときに第1のデータラインをマスクするように構成され得る。

#### 【0183】

一例では、マスタデバイスは、割込み要求をアサートしているスレーブデバイスを識別するために、バスを介してスレーブデバイスのスキャンを実行し得る。マスタデバイスは、アサートしているスレーブデバイスから第1のラインを介してインジケータを受信し得る。40

#### 【0184】

別の例では、スレーブデバイスは、割込み期間の間に第1のラインをプルダウンすることによって、割込み要求をアサートし得る。スレーブデバイスは、バスを介して受信されたトランスコードされているデータビットを復号するための割込み期間の間、第1のラインを内部的にマスクし得る。いくつかの態様によれば、バスに結合されているすべてのスレーブデバイスはまた、割込み期間の間、第1のラインを内部的にマスクする。

#### 【0185】

別の例では、スレーブ識別子スキャン応答期間が提供され得る。この期間の間、バスに50

結合されている1つまたは複数のスレーブデバイスは、バスの第1のラインおよび第2のラインを介してマスタデバイスによって開始されたスレーブ識別子スキャンの一部の中で、それらの一意の識別子をバスの第1のラインを介して提供することができる。

#### 【0186】

別の例では、マスタデバイスがバスの第2のラインを介してグローバル読取りクロックを送る間に、前に識別されたスレーブデバイスがバスの第1のラインを介してデータを送信することを可能にされる、データ読取り期間が規定され得る。グローバル読取りクロックは、ダブルデータレートクロックであってよい。

#### 【0187】

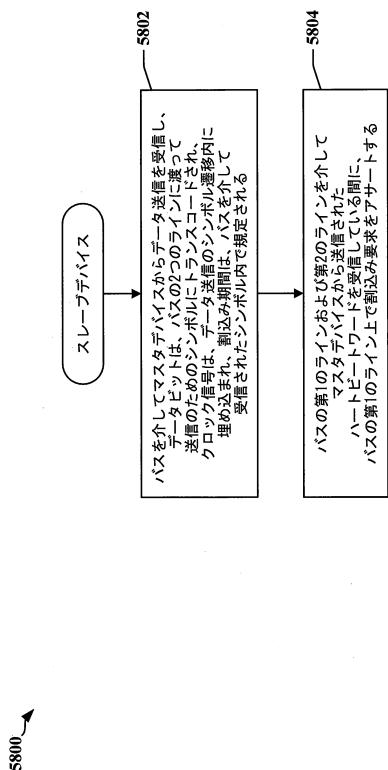

図58は、本明細書で開示するいくつかの態様による、IRQを生成するための方法の例を示すフローチャート5800である。方法は、たとえば、スレーブデバイスによって実施され得る。

10

#### 【0188】

プロック5802において、スレーブデバイスは、バスを介してマスタデバイスからデータ送信を受信し得る。データのデータビットは、バスの2つのラインに渡って送信のためのシンボルにトランスクードされてよい。クロック信号は、データ送信のシンボル遷移内に埋め込まれてよい。割込み期間は、バスを介して受信されたシンボル内で規定され得る。

#### 【0189】

プロック5804において、スレーブデバイスは、バスの第1のラインおよび第2のラインを介してマスタデバイスからハートビート送信を受信している間に、バスの第1のライン上で割込み要求をアサートし得る。割込み要求は、アサートしているスレーブデバイスがマスタデバイスによる何らかのアクションを要求することを望むというインジケータであり得る。割込み要求は、割込み期間の間、第1のラインをプルダウンすることによってアサートされ得る。割込み要求は、割込み期間の間、第1のラインをプルダウンすることによってアサートされ得る。

20

#### 【0190】

一例では、割込み要求は、アサートしているスレーブデバイスがマスタデバイスによる何らかのアクションを要求することを望むというインジケータである。割込み要求は、割込み期間の間、第1のラインをプルダウンすることによってアサートされ得る。

#### 【0191】

別の例では、スレーブデバイスは、ハートビートワードを検出した後、第1のデータラインをマスクし得る。第1のデータラインは、一斉呼出しがバス上で送信された後、ハートビートワードに対する応答を送信している間にマスクされ得る。

30

#### 【0192】

別の例では、スレーブデバイスは、バスの第1のラインおよび第2のラインを介してマスタデバイスからスレーブ識別子スキャン要求を受信し得、スレーブ識別子スキャン要求によって提供されたスレーブ識別子スキャンのスレーブ識別子スキャン応答期間の一部の中で、バスの第1のラインを介して一意のスレーブ識別子を提供し得る。

#### 【0193】

別の例では、マスタデバイスがバスの第2のラインを介してグローバル読取りクロックを送る間に、前に識別されたスレーブデバイスがバスの第1のラインを介してデータを送信することを可能にされる、マスタデバイスによって規定されるデータ読取り期間の間、スレーブデバイスは、バスの第1のラインを介してデータを送り得る。いくつかの事例では、バスに結合されているすべてのスレーブデバイスはまた、グローバルクロック読取り期間の間、SDAラインを内部的にマスクする。

40

#### 【0194】

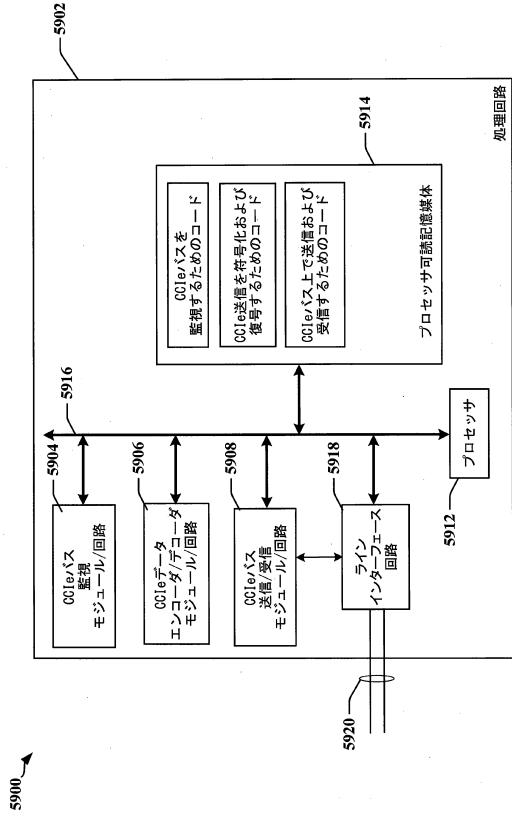

図59は、処理回路5902を採用する装置5900のためのハードウェア実装形態の一例を示す概念図である。この例では、処理回路5902は、バス5916によって概略的に表されるバスアーキテクチャを用いて実装され得る。バス5916は、処理回路5902の特定の適用例および全体的な設計制約に応じて、任意の数の相互接続するバスおよびブリッジを含んでよい。バ

50

ス5916は、プロセッサ5912によって概略的に表される1つまたは複数のプロセッサ、およびプロセッサ可読記憶媒体5914によって概略的に表されるコンピュータ可読媒体を含む様々な回路を互いにリンクする。1つまたは複数のタイマーがバスに接続されてよく、および/またはプロセッサ5912の中で直接アクセス可能であり得るか、またはプロセッサ5912内で実施され得る。バス5916はまた、タイミングソース、タイマー、周辺装置、電圧調整器、および電力管理回路などの様々な他の回路をリンクしてよい。ラインインターフェース回路5912は、処理回路5902を制御データバスに結合する差動ドライバおよびレシーバ、および/または処理回路をIRQバスに結合する回路を含んでよい。装置の性質に応じて、ユーザインターフェースが、キーパッド、ディスプレイ、スピーカー、マイクロフォン、ジョイスティックなどのデバイスをサポートするために設けられてよい。

10

#### 【0195】

プロセッサ5912は、バス5916の管理、およびプロセッサ可読記憶媒体5914に記憶されたソフトウェアの実行を含む一般的な処理を担当する。ソフトウェアは、プロセッサ5912によって実行されるとき、処理回路5902に、任意の特定の装置に対して上記で説明した様々な機能を実行させる。プロセッサ可読記憶媒体5914は、ソフトウェアを実行するとき、プロセッサ5912によって操作されるデータを記憶するために使用されてよい。プロセッサ可読記憶媒体5914はまた、1つまたは複数のリモート管理されるデバイスに関するシステム情報(たとえば、プロファイル)、および装置5900自体に関するシステム情報を記憶するために使用されてよい。

#### 【0196】

一構成では、処理回路5902は、I2C、CCI、および/またはCClバス上のバスマスターとして通信するために適合されたデバイスとしての、1つまたは複数の機能を実行してよい。第2の構成では、処理回路5902は、I2C、CCI、および/またはCClバス上のスレーブマスターとして通信するために適合されたデバイスとしての、1つまたは複数の機能を実行してよい。処理回路5902は、インターフェース回路5918を通じて制御データバス5920に接続されてよい。処理回路5902は、インバンドIRQ信号がアサートされているとき、またはインバンドIRQ信号が少なくとも1つのスレーブデバイスによってアサートされ得るときを確認するために、CClバス5920を監視するように構成されたモジュールまたは回路5904と、CClバス5920上で送信されるデータを符号化または復号するように構成されたモジュールまたは回路5906と、データをCClバス5920を使用して送信および/または受信するように構成されたモジュールまたは回路5908とを含んでよい。

20

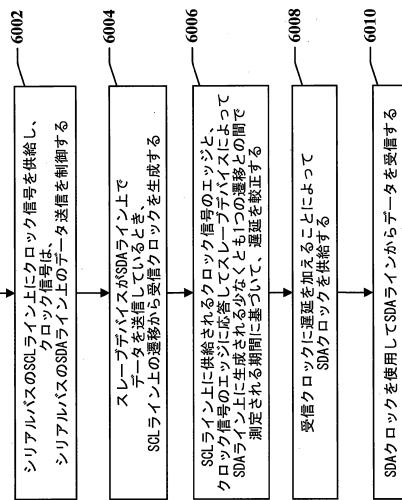

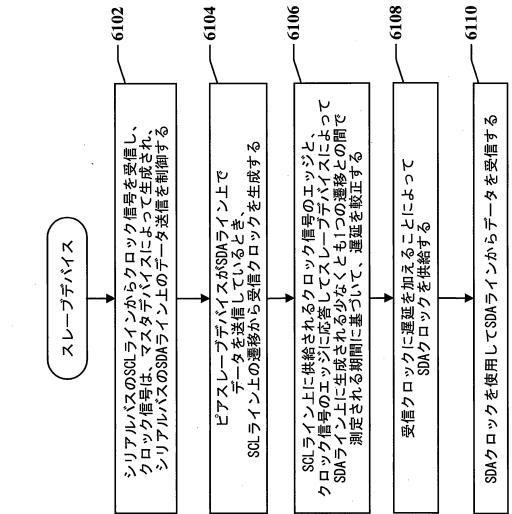

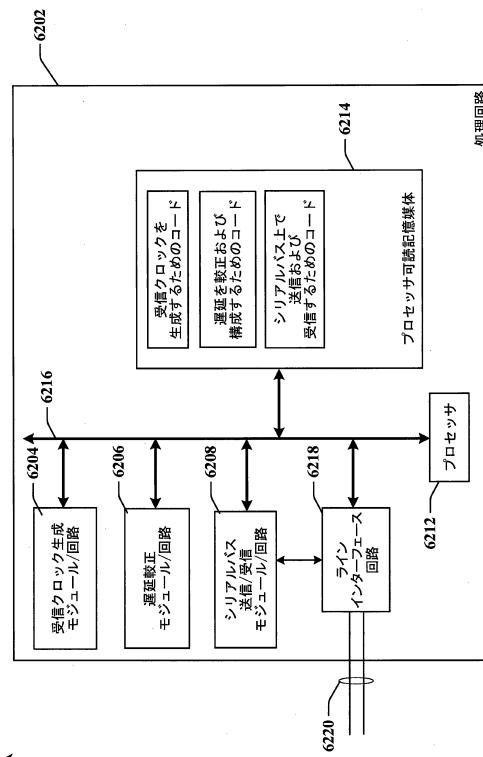

#### 【0197】

図60は、本明細書で開示するいくつかの態様による、受信クロックを較正するための方法の一例を示すフローチャート6000である。方法は、マスタデバイスによって実施されてよく、シリアルバス上で送信されるデータビットに受信クロックを位置合わせるために使用される遅延回路を較正することを含み得る。

#### 【0198】

ブロック6002において、マスタデバイスは、シリアルバスのSCLライン上にクロック信号を供給し得る。クロック信号は、シリアルバスのSDAライン上のデータ送信を制御し得る。SCLライン上に供給されるクロック信号は、SDAライン上のダブルデータレート送信を制御する。

30

#### 【0199】