(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5000293号

(P5000293)

(45) 発行日 平成24年8月15日(2012.8.15)

(24) 登録日 平成24年5月25日(2012.5.25)

(51) Int.Cl.

**H01L 29/792 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 21/336 (2006.01)**

**H01L 27/115 (2006.01)**

**H01L 21/8247 (2006.01)**

F 1

H01L 29/78 371

H01L 27/10 434

請求項の数 7 (全 10 頁)

(21) 出願番号 特願2006-356457 (P2006-356457)

(22) 出願日 平成18年12月28日 (2006.12.28)

(65) 公開番号 特開2007-184612 (P2007-184612A)

(43) 公開日 平成19年7月19日 (2007.7.19)

審査請求日 平成18年12月28日 (2006.12.28)

(31) 優先権主張番号 10-2005-0134385

(32) 優先日 平成17年12月29日 (2005.12.29)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 505087780

マグナチップセミコンダクター有限会社

MAGNACHIP SEMICONDUCTOR LTD

大韓民国忠清北道清州市興徳区香亭洞1

1 Hyangjeong-dong, Heungduk-gu, Cheongju City, Chungcheong Bok-do, Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 ハン イルソク

大韓民国忠清北道清州市興徳区鳳鳴2洞

LGサオンアパート La 棟1001号

最終頁に続く

(54) 【発明の名称】不揮発性半導体メモリ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板に形成された第1活性領域及び第2活性領域と、

前記第1活性領域及び第2活性領域とを分離する素子分離領域と、

前記第1活性領域に第1絶縁膜を媒介として該第1絶縁膜上に形成されるセンス用トランジスタのゲート電極と、

前記第1活性領域に第2絶縁膜を媒介として該第2絶縁膜上に形成される第1キャパシタのトンネリング電極と、

前記第2活性領域内に第3絶縁膜を媒介として該第3絶縁膜上に形成される第2キャパシタのコントロール電極と、

を備え、

前記第2キャパシタのコントロール電極は、前記素子分離領域とはオーバーラップせず

に配置され、寄生キャパシタンスを減らし、

前記センス用トランジスタのゲート電極、前記第1キャパシタのトンネリング電極及び

第2キャパシタのコントロール電極は平面上、互いに分離されており、前記第2キャパシタの

コントロール電極は金属ラインによって、それぞれ前記センス用トランジスタのゲー

ト電極及び前記第1キャパシタのトンネリング電極に電気的に接続されたことを特徴とする

不揮発性半導体メモリ装置。

## 【請求項 2】

前記第1キャパシタのトンネリング電極は、前記第1活性領域上から前記素子分離領域上まで伸び、

前記第1キャパシタのトンネリング電極と前記第2キャパシタのコントロール電極とを接続する前記金属ラインは、前記素子分離領域上で前記第1キャパシタのトンネリング電極に接続されたことを特徴とする請求項1に記載の不揮発性半導体メモリ装置。

**【請求項3】**

前記第1絶縁膜の厚さが、前記第2絶縁膜の厚さより大きいことを特徴とする請求項1に記載の不揮発性半導体メモリ装置。 10

**【請求項4】**

前記第1絶縁膜と前記第3絶縁膜の厚さが、等しいことを特徴とする請求項1に記載の不揮発性半導体メモリ装置。 10

**【請求項5】**

前記第1絶縁膜と前記第3絶縁膜が、同時に形成されることを特徴とする請求項1に記載の不揮発性半導体メモリ装置。 10

**【請求項6】**

前記第1活性領域に第4絶縁膜を媒介として形成された選択トランジスタのゲート電極をさらに備えることを特徴とする請求項1に記載の不揮発性半導体メモリ装置。 10

**【請求項7】**

前記第1キャパシタと前記半導体基板とが共有する前記第1活性領域の接合は、前記センス用トランジスタのドレインを形成し、前記センス用トランジスタのゲート電極を基準に、前記ドレインに対応する前記第1活性領域の接合は、前記センス用トランジスタのソースを形成することを特徴とする請求項1に記載の不揮発性半導体メモリ装置。 20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、不揮発性半導体メモリ装置に関し、さらに詳細には、埋め込み半導体装置で書き込みと消去を繰り返し得る不揮発性メモリ機能を提供する不揮発性半導体メモリ装置に関する。 30

**【背景技術】**

**【0002】**

デジタル機器の使用の増加に伴い、情報を格納するための記憶装置は必須機能として、特に情報の書き込み／消去を繰り返し得る不揮発性半導体メモリ装置は、その使用が次第に増加しつつある。 30

**【0003】**

不揮発性メモリ機能を有する埋め込み(embedded)半導体装置は、メモリ素子とこれを駆動するためのロジック(logic)回路を单一チップで実現したものであり、ロジック半導体製造技術と不揮発性メモリ装置の製造技術を統合して製造される。 30

**【0004】**

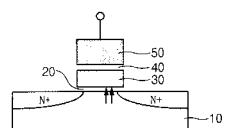

図1は、従来の不揮発性半導体メモリ装置のセル構造を示す断面図である。 40

**【0005】**

図1に示すように、従来の不揮発性半導体メモリ装置は、半導体基板10に第1絶縁膜20のトンネリング酸化膜を媒介としてフローティング電極30が形成されており、フローティング電極30上に第2絶縁膜40を媒介としてコントロール電極50を積層した構造で形成されている。 40

**【0006】**

このように、二重ゲート構造を有するスタッガードゲート型のセル構造を適用した従来の不揮発性半導体メモリ装置が、埋め込み半導体装置の不揮発性メモリとして用いられる場合に、不揮発性メモリセルを形成するために、ロジック回路工程にトンネリング酸化膜形成、フローティング電極30の形成、フローティング電極上に第2絶縁膜40を形成しコン 50

トロール電極 50 を形成するなどの追加工程が必須となる。これにより、工程が複雑となり、原価が増加するという問題がある。

#### 【0007】

また、集積度の増加について、積層した形態の不揮発性メモリセルを使用する場合、トポロジー (topology) の過度な増加により後続工程で平坦化が難しくなり、工程の難易度が増加するという問題がある。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

本発明は、上述の問題点に鑑みてなされたもので、その目的は、積層された電極構造を有さず、かつ、従来のロジック回路製造工程と共に使用することができる不揮発性半導体メモリ装置を提供することにある。10

#### 【課題を解決するための手段】

#### 【0009】

上記の目的を達成すべく、本発明の実施の形態に係る不揮発性半導体メモリ装置は、半導体基板と、前記半導体基板に形成された第1活性領域及び第2活性領域と、前記第1活性領域及び第2活性領域とを分離する素子分離領域と、前記第1活性領域に第1絶縁膜を媒介として該第1絶縁膜上に形成されるセンス用トランジスタのゲート電極と、前記第1活性領域に第2絶縁膜を媒介として該第2絶縁膜上に形成される第1キャパシタのトンネリング電極と、前記第2活性領域内に第3絶縁膜を媒介として該第3絶縁膜上に形成される第2キャパシタのコントロール電極と、を備え、前記第2キャパシタのコントロール電極は、前記素子分離領域とはオーバーラップせずに配置され、寄生キャパシタンスを減らし、前記センス用トランジスタのゲート電極、前記第1キャパシタのトンネリング電極及び第2キャパシタのコントロール電極は平面上、互いに分離されており、前記第2キャパシタのコントロール電極は金属ラインによって、それぞれ前記センス用トランジスタのゲート電極及び前記第1キャパシタのトンネリング電極に電気的に接続されたことを特徴とする。20

#### 【0010】

好ましい実施の形態において、前記第1キャパシタのトンネリング電極は、前記第1活性領域上から前記素子分離領域上まで伸び、前記第1キャパシタのトンネリング電極と前記第2キャパシタのコントロール電極とを接続する前記金属ラインは、前記素子分離領域上で前記第1キャパシタのトンネリング電極に接続されたことを特徴とする。30

#### 【0011】

前記第1絶縁膜と前記第3絶縁膜の厚さが、等しく、前記第1絶縁膜と前記第3絶縁膜が、同時に形成されたことを特徴とする。

#### 【0012】

前記第1活性領域に第4絶縁膜を媒介として形成された選択トランジスタ電極をさらに備えることを特徴とする。

#### 【発明の効果】

#### 【0013】

本発明の不揮発性半導体メモリ装置は、積層された電極構造を有さず、埋め込み半導体装置でロジック回路製造工程と共に同時に製造して、追加の工程なしに製作できるため、製作が容易かつ原価が低減するという効果がある。40

#### 【発明を実施するための最良の形態】

#### 【0014】

以下、本発明の好ましい実施の形態を、添付図面に基づき詳細に説明する。

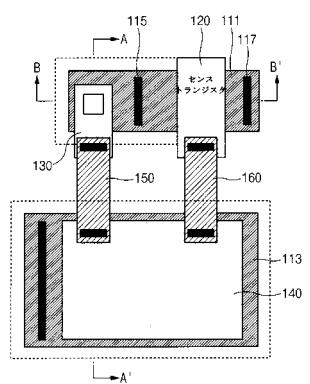

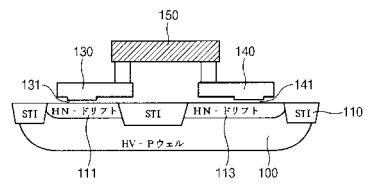

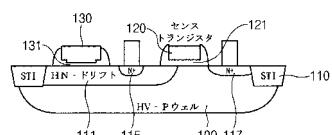

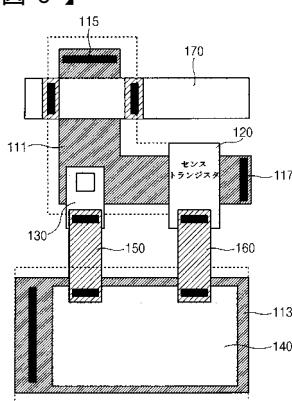

#### 【0015】

図2は、本発明の一実施の形態に係る不揮発性半導体メモリ装置のセルレイアウト (layout) であり、図3は、図2のA-A'線の断面図であり、図4は、図2のB-B50

線の断面図である。

**【0016】**

図2～図4に示すように、本発明の不揮発性半導体メモリ装置は、半導体基板100、素子分離領域110、トランジスタ電極120、第1キャパシタ電極130、及び第2キャパシタ電極140を備える。

**【0017】**

半導体基板100は、電気的素子が形成される基板であって、例えば、シリコン基板のように、半導体特性を有する材質で形成されて、半導体製造工程により電気的素子が形成される支持台の機能を果たす。

**【0018】**

素子分離領域110は、半導体基板100に電気的素子が形成される活性領域を電気的に分離する機能を有し、半導体基板100に形成された素子分離領域110により、第1活性領域111と第2活性領域113とが電気的に分離される。また、半導体素子の集積度が増加するにつれて、素子分離領域110は、STI(Shallow Trench Isolation)工程により形成することが好ましい。

**【0019】**

トランジスタ電極120は、第1活性領域111に形成された第1絶縁膜121を媒介として第1絶縁膜121上に形成されたトランジスタのゲート電極であって、第1活性領域111にトランジスタを形成する。

**【0020】**

第1キャパシタ電極130は、第1活性領域111に形成された第2絶縁膜131を媒介として第2絶縁膜131上に形成されたキャパシタのゲート電極であって、第1活性領域111に第1キャパシタを形成する。このとき、第1絶縁膜121の厚さは、第2絶縁膜131の厚さより厚いものであって、例えば、第1絶縁膜121は、200～1000程度の範囲を有する酸化膜であり、第2絶縁膜131は、60～150程度の範囲を有する酸化膜である。

**【0021】**

そして、第1キャパシタ電極130を形成する工程において、厚さの薄い第2絶縁膜131に損傷を与えないように、第1キャパシタ電極130は、第2絶縁膜131の境界で余裕をおいて伸びた境界を有する。

**【0022】**

そして、第1キャパシタと半導体基板100とが共有する第1活性領域111の接合は、トランジスタのドレイン115を形成し、トランジスタ電極120を基準に、ドレイン115に対応する第1活性領域111の接合は、トランジスタのソース117を形成する。このとき、形成されたトランジスタは、nチャネルトランジスタであって、ドレイン115及びソースも、n型接合を形成することが好ましい。

**【0023】**

第2キャパシタ電極140は、第2活性領域113に形成された第3絶縁膜141を媒介として形成されたキャパシタのゲート電極であって、第2活性領域113に第2キャパシタを形成する。このとき、第2キャパシタ電極140は、トランジスタ電極120及び第1キャパシタ電極130と電気的に接続され、好ましくは、金属ライン150、160により接続される。

**【0024】**

そして、第2キャパシタ電極140は、第2活性領域113の内部に形成されて、素子分離領域110と重ならないように配置して、寄生キャパシタンスを減少させることが好ましい。第3絶縁膜141は、第1絶縁膜121と同時に形成され、第2キャパシタ電極140もトランジスタ電極120と同時に形成されて、製造工程を簡単にすることが好ましい。したがって、第3絶縁膜141の厚さは、第1絶縁膜121の厚さと等しい酸化膜である。

**【0025】**

10

20

30

40

50

そして、トランジスタ電極 120、第1キャパシタ電極 130、及び第2キャパシタ電極 140は、ポリシリコンで形成することが好ましい。

#### 【0026】

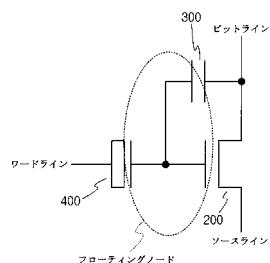

図5は、図2に示す本発明の不揮発性半導体メモリ装置のセルを記号で示す回路図である。

#### 【0027】

図2～図5を参照して、本発明の不揮発性半導体メモリ装置の機能及び動作を説明する。本発明の適用例として、図2に示す本発明の不揮発性半導体メモリ装置は、埋め込み半導体素子の不揮発性メモリのセルとして用いられることが好ましい。この場合、埋め込み半導体素子の製造工程に用いられる工程を利用して、追加工程なしに、本発明の不揮発性半導体メモリ装置を実現し得るという長所がある。

10

#### 【0028】

本発明の不揮発性半導体メモリ装置のセルは、総3個の電気的素子を備えるが、トランジスタは、高電圧のN MOSトランジスタであって、ドレイン及びソースを含むセンス(sense)トランジスタ200として機能し、第1キャパシタ電極130と第2絶縁膜131とで形成された第1キャパシタは、電子のトンネリング(tunneling)ウインドウ(window)として用いられる低電圧ゲート酸化膜を使用した第1MOSキャパシタ(=トンネリングゲート)300である。

#### 【0029】

そして、第2キャパシタ電極140と第3絶縁膜141で形成された第2キャパシタは、書き込み／消去動作の際、コントロールゲート、すなわちn<sup>-</sup>接合(junction)に印加された電圧をカップリング(coupling)させるための高電圧ゲート酸化膜を使用した第2MOSキャパシタ(=コントロールゲート)400であり、コントロールゲートは、高電圧素子のソース／ドレインとして用いられるイオン注入を利用したn<sup>-</sup>接合により接続されて、不揮発性半導体メモリ装置のワードライン(word line)として機能する。

20

#### 【0030】

コントロールゲートのn<sup>-</sup>接合は、メモリセルの書き込み／消去時に印加される電圧を第2MOSキャパシタを利用してカップリングさせ、カップリングされた電圧は、接続された金属ライン150、160を介して低電圧ゲート酸化膜の上端の第1キャパシタ電極130に伝達される。このとき、伝達された電圧は、ドレイン端に印加された電圧に応じて、トンネリング酸化膜(=低電圧ゲート酸化膜)の両端にかかり、セルの書き込み／消去動作を行う。

30

#### 【0031】

書き込み／消去動作時には、ソース117側をフロー・ティングして、センストランジスタ200を介した電流通路は遮断される。以後、読み出し動作時には、書き込み／消去動作により、F-Nトンネリング現象により互いに接続したトランジスタ電極、第1キャパシタ電極及び第2キャパシタ電極であるポリシリコン内に電子が充填されるか、または放出された状態となる。

#### 【0032】

ポリシリコンに充填または放出された電子は、センストランジスタ200のゲートの下のチャネルのポテンシャル差を表し、センストランジスタ200のチャネルを反転(inversion)させる電圧が変化されることにより、書き込み状態と消去状態の2種類の状態を持つようになる。

40

#### 【0033】

例えば、セルの消去動作の場合、n<sup>-</sup>接合に接続したワードラインメタルに10～15Vの高電圧を印加すると、n<sup>-</sup>接合に接続したコントロールゲートの下端n<sup>-</sup>接合は、MOSキャパシタカップリングがおき、カップリングされた電圧は、カップリング比(coupling ratio)により、適正電圧が金属ラインに接続されて、トンネリングゲートである第1キャパシタ電極に伝達される。

50

## 【0034】

カップリング比が約70%の場合、7.0～10.5Vがトンネリング酸化膜の第2絶縁膜131の上端に伝達されるが、このとき、ドレイン115に接続したビットラインにグラウンド電圧(Vss)が外部から伝達され、酸化膜の厚さが約100 存在する場合、約7.0～10.5MeVの電圧がかかる。

## 【0035】

トンネリング酸化膜の両端に垂直方向に電界が印加され、F-Nトンネリング現象により、n<sup>-</sup>接合側にあった電子は、カップリングされた正(positive)電圧に引かれて、ポリシリコンにトンネリングされる。以後、センストランジスタ200を介してセルのしきい(threshold)電圧を測定する場合、ポリシリコンにトンネリングされた電子により、ポリシリコンゲートの下にチャネルを反転させるための電圧がさらに大きくなるため、しきい電圧は高まる。10

## 【0036】

一般的なSTI工程を使用したフィールド(field)の場合、ポリシリコンを利用してフィールドを経るとき、寄生フィールドトランジスタが形成され、このトランジスタの降伏(breakdown)電圧としきい電圧は約12～18V程度で、一般的な用途で使用するため、問題がないが、約20V内外の高い電圧が印加される場合、漏れ電流、カップリング比の減少、降伏電圧の減少(降下)、フィールド反転などの問題が発生する余地がある。20

## 【0037】

したがって、本発明でフローティングされたポリシリコン間の接続は、寄生フィールドトランジスタ特性を向上させるために、トンネリング酸化膜のポリシリコン及びセンストランジスタ200のポリシリコンをフローティングゲートのポリシリコンと金属で接続して、ポリシリコン対比書き込み/消去動作時発生し得る降伏電圧の減少及びフィールド反転という問題を解決する。

## 【0038】

また、メモリセルの接合は、高電圧による接合の降伏を防止するために、n<sup>+</sup>接合の場合、ポリシリコンと一定距離を隔てた構造を使用し、ソースの場合、接地レベルの電圧のみを印加するため、従来の低電圧接合と同じ構造を有する。

## 【0039】

n<sup>+</sup>ドレイン接合の下には、電界を緩和させるためのn<sup>-</sup>接合である高電圧用n<sup>-</sup>イオン注入及びドライブイン(drive-in)熱(thermal)工程を利用したn<sup>-</sup>接合がある。これらの全ての構造は、従来の高電圧素子に使用していた工程をそのまま利用する。30

## 【0040】

コントロールゲートに用いられる第2キャパシタの場合、一般には、フィールド酸化膜側にポリシリコンが伸びるが、本発明では、フィールド酸化膜でポリシリコンとの間で発生される寄生キャパシタンスを減らすために、活性領域内側でポリエッチングされるようになり、トンネリング酸化膜の上端に存在する第1キャパシタ電極は、第2絶縁膜である薄い酸化膜に工程進行時に発生し得るプラズマによる損傷を減らすために、フィールド領域に伸びて金属ラインと接続される。40

## 【0041】

埋め込み半導体装置に本発明の不揮発性半導体メモリ装置が用いられる場合、第1絶縁膜及び第3絶縁膜は、高電圧トランジスタの絶縁膜と同じ工程で形成し、第2絶縁膜は、低電圧トランジスタの絶縁膜と同じ工程で形成されるために、別途の工程を追加せず、本発明の不揮発性半導体メモリ装置を有する埋め込み半導体装置の実現が可能である。

## 【0042】

また、書き込み/消去動作の際、電子のトンネリングを行うトンネリング酸化膜の形成は、従来の埋め込み高電圧工程で高電圧と低電圧用二重ゲートを形成するマスク工程をそのまま使用する。すなわち、ウエハ全面に高電圧用厚いゲート酸化膜(200～100050

)を熱酸化工程の方法で成長させ、以後、マスクを利用した選択的ウェットエッティングを適用して、低電圧領域（低電圧N / PMOS素子）をウエハ表面が露出するように選択的エッティングさせる。このとき、トンネリング酸化膜のトンネリングウィンドウ領域も同時にエッティングされる。

#### 【0043】

以後、薄いゲート酸化膜を熱酸化工程方法で酸化させる。したがって、トンネリングウィンドウ領域及び低電圧素子部分には、例えば60～150ゲート酸化膜が形成され、残りの高電圧素子領域は、既存の薄いゲート酸化膜に薄いゲート酸化工程時にさらに成長される酸化膜が追加される。

#### 【0044】

前記工程により成長されるトンネリング酸化膜は、低電圧酸化膜と等しい厚さを有し、マスクを使用した選択的エッティングの際のトンネリングウィンドウの大きさは、カップリング比を考慮して、横／縦の大きさが、例えば0.4～1.2μm程度になるようとする。

#### 【0045】

以上で説明した工程を参照すると、本発明の不揮発性半導体メモリ装置は、従来の埋め込み半導体装置でロジック回路を製作するのに必要な工程を行うと共に製造されるという長所があるため、不揮発性半導体メモリ装置を製作するための追加工程を必要としない。

#### 【0046】

また、図3及び図4の断面図に示すように、単一層の電極を使用するため、トポロジーが増加しないから、後続の平坦化工程や金属配線工程が容易になる。

#### 【0047】

図5を参照して、本発明の不揮発性半導体メモリ装置の単位セルに対する書き込み／消去／読み出し動作について説明する。

#### 【0048】

まず、消去動作特性は、ワードラインを介して約12～18VのVpp（高電圧）を印加し、印加されたVppは、第2キャパシタであるコントロールキャパシタ400にカップリングされて、第1キャパシタであるトンネリングキャパシタ300の上部に伝達される。このとき、センストランジスタ200のソースノードは、フローティングであるため、トランジスタへの電流通路は形成されない。ドレインノードには、接地電圧、すなわち、0Vが印加されるため、トンネリングキャパシタ300の両端には、垂直方向の電界が発生する。この電界によって、ドレイン端の電子がF-Nトンネリングが発生し、フローティングノードに電子（charge）が格納される。

#### 【0049】

すなわち、フローティングノードに電子が注入される場合、注入された電子により、センストランジスタ200のしきい電圧は高まるため、チャネルを逆転させ難くなり、したがって、読み出し電圧を印加してもソース／ドレイン間セル電流は流れない。

#### 【0050】

書き込み動作の場合、ワードラインを介して接地電圧である0Vが印加され、印加されたVssは、コントロールキャパシタ400にカップリングされて、トンネリングキャパシタ300の上部に伝達される。また、センストランジスタ200のソースノードは、フローティングされるため、トランジスタの電流通路は形成されない。また、ドレインノードには、12～18Vの高電圧を印加し、印加され電圧は、トンネリングキャパシタ300の下端にカップリングされて、トンネリングキャパシタ300の両端には、ワードライン電圧及びドレイン電圧により垂直方向の電界が発生する。この電界により、ポリシリコンに存在する電子がドレイン電圧に引かれて、ビットライン側に放出される。

#### 【0051】

そして、これにより、しきい電圧が低くなつて、読み出し電圧を印加する場合、フローティングゲートの電位がチャネルを十分に反転させ、ソース／ドレイン間電位差により、セル電流が流れるようになる。

**【0052】**

読み出し動作の場合には、一般的なMOSトランジスタの動作と同様に、ビットラインに1.8~5.0VのVdd電圧を印加し、n接合からなるワードラインにも、同じ電圧を印加して、ソース／ドレイン間のセル電流を感知する。

**【0053】**

図6は、本発明の他の実施の形態に係る不揮発性半導体メモリ装置のセルレイアウトである。図6は、図2と実質的に同じ構成と機能を有した構成要素に対しては、同じ参照符号を使用する。

**【0054】**

図6に示すように、本発明の他の実施の形態に係る不揮発性半導体メモリ装置は、一実施の形態の不揮発性半導体メモリ装置で第1活性領域111を伸びて第4絶縁膜を媒介としてポリシリコンで形成された選択トランジスタ電極170をさらに形成した構造を有している。

**【0055】**

このとき、第4絶縁膜を第1絶縁膜と一緒に形成して、工程の追加なしに選択トランジスタ電極170を形成することが好ましい。そして、ソース117に対応する追加された選択トランジスタ電極170の第1活性領域111の接合は、ドレイン115を形成する。選択トランジスタ電極170により選択トランジスタが形成される。

**【0056】**

選択トランジスタは、選択トランジスタ電極170に印加された電圧により、ドレイン115に印加される電圧が、選択的にトンネリングキャパシタに印加されるように調節する。

**【0057】**

このとき、選択トランジスタは、ビットラインを介して印加されるドレイン電圧を選択するスイッチ機能を有するトランジスタであって、特定のバイト選択の機能を有する不揮発性半導体メモリ装置を提供する。他の機能や動作は、上述の本発明の一実施の形態と同じである。

**【0058】**

上述した本発明の好ましい実施の形態は、例示の目的のために開示されたものであり、本発明の属する技術の分野における通常の知識を有する者であれば、本発明の技術的思想を逸脱しない範囲内で、様々な置換、変形、及び変更が可能であり、このような置換、変更などは、特許請求の範囲に属するものである。

**【図面の簡単な説明】****【0059】**

【図1】従来の不揮発性半導体メモリ装置のセル構造を示す断面図である。

【図2】本発明の一実施の形態に係る不揮発性半導体メモリ装置のセルレイアウトである。

【図3】図2のA-A'線の断面図である。

【図4】図2のB-B'線の断面図である。

【図5】図2に示す本発明の不揮発性半導体メモリ装置のセルを記号で示す回路図である。

【図6】本発明の他の実施の形態に係る不揮発性半導体メモリ装置のセルレイアウトである。

**【符号の説明】****【0060】**

100、100 半導体基板

120 トランジスタ電極

130 第1キャパシタ電極

140 第2キャパシタ電極

150、160 金属ライン

10

20

30

40

50

## 170 選択トランジスタ電極

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

審査官 井原 純

- (56)参考文献 特開2004-165182(JP,A)

特開2005-191057(JP,A)

特開平11-111872(JP,A)

特開昭60-057673(JP,A)

特開2000-031395(JP,A)

欧州特許出願公開第00977265(EP,A1)

特表2001-511308(JP,A)

特開平11-087664(JP,A)

特開2004-094922(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792