(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

**(11) N° de publication :**

(à n'utiliser que pour les commandes de reproduction)

**2 540 277**

**(21) N° d'enregistrement national :**

83 01544

(51) Int Cl<sup>3</sup> : G 11 C 8/02.

12

## **DEMANDE DE BREVET D'INVENTION**

A1

22 Date de dépôt : 1<sup>er</sup> février 1983.

71 Demandeur(s) : BRION Alain - EB

### 30 Priorité

⑦2 Inventeur(s) : Alain Brion.

④ Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 31 du 3 août 1984.

**(73) Titulaire(s) :**

**60 Références à d'autres documents nationaux appartenants :**

**(74) Mandataire(s) : Brevatome.**

**54** Mémoire de mots munie d'un circuit de transcodage d'adresses.

(57) Mémoire de mots munie d'un circuit de transcodage d'adresses permettant d'obtenir  $A \times B$  mots, A et B n'étant pas des puissances de deux.

Le circuit de transcodage comprend deux parties CTA X et CTA Y affectées respectivement au trancodeage de deux adresses X et Y. La première partie CTA X comprend un multiplexeur M X qui multiplexe  $r$  éléments binaires de poids fort de X avec un niveau logique prédéterminé. La seconde CTA Y comprend un multiplexeur M Y qui multiplexe  $r$  éléments binaires de poids fort de Y (excepté l'élément binaire de plus fort poids) avec les  $r$  éléments binaires de plus fort poids de X. La commande des multiplexeurs s'effectue par l'élément binaire de plus fort poids de l'une des adresses.

**Application à la constitution de mémoires, notamment pour écrans d'affichage alphanumérique ou graphique.**

La présente invention a pour objet une mémoire de mots munie d'un circuit de transcodage d'adresses.

Les mémoires courantes sont organisées en mots constitués de plusieurs éléments binaires. Le nombre de mots est en général une puissance de deux. Comme on a souvent besoin de mémoires ayant une forme matricielle, la répartition de ces mots correspond à des matrices de  $2^p$  par  $2^q$  mots. Dans ce cas, pour écrire ou lire un mot dans la mémoire, il suffit d'afficher une adresse colonne X sur un premier groupe de p fils d'adresse et une adresse ligne Y sur un second groupe de q fils d'adresse.

Cependant, il est souhaitable parfois de disposer d'une mémoire de AxB mots où les nombres A et B ne sont pas des puissances de 2. C'est le cas notamment avec les mémoires d'écran alphanumérique où l'on a besoin de 80x24 caractères (ou de 80x25) ou avec les mémoires d'écran graphique au format facsimilé à 1728x2288 points dans laquelle les points sont groupés par mots de 64 éléments binaires, ce qui conduit à des mémoires de 27x2288 mots.

Lorsque A et B ne sont pas des puissances de 2, on peut écrire :

$$2^p < A < 2^{p+1} \quad (1)$$

$$2^q < B < 2^{q+1}$$

inégalités où p et q sont les exposants des plus proches puissances de 2 inférieures à A et à B.

En d'autres termes, cela signifie que A s'exprime avec p+1 éléments binaires, et B avec q+1 éléments binaires.

Deux cas peuvent se présenter :

$$- \text{ si } 2^{p+q+1} < AxB < 2^{p+q+2} \quad (2)$$

on est obligé d'utiliser une mémoire de  $2^{p+q+2}$  mots ; il suffit alors de majorer A et B respectivement par  $2^{p+l}$  et  $2^{q+l}$ .

5 - si  $2^{p+q} < AxB < 2^{p+q+1}$  (3)

on pourrait encore prendre une mémoire de  $2^{p+q+2}$  mots, mais elle serait mal utilisée puisque toute la moitié allant de  $2^{p+q+1}$  à  $2^{p+q+2}$  serait inemployée.

10 Le problème que se propose de résoudre l'invention est justement de trouver un moyen permettant d'utiliser une mémoire de capacité  $2^{p+q+1}$  mots, dans le cas particulier où chaque mot est défini par une première adresse à  $p+l$  éléments binaires et une deuxième adresse à 15  $q+l$  éléments binaires.

L'invention résout ce problème par l'adjonction d'un circuit de transcodage d'adresses à  $p+q+2$  entrées et à  $p+q+l$  sorties. Ce circuit comprend deux parties :

20 a) - une première partie constituée par :

- $p+l$  entrées et  $p+l$  sorties, les  $p+l$  entrées recevant  $p+l$  éléments binaires définissant un nombre X inférieur à A, ces éléments binaires étant répartis entre un élément de plus faible poids et un élément de plus fort poids, les  $p+l$  sorties étant reliées à  $p+l$  premières entrées d'adressage de la mémoire,

- $p+l-r$  connexions directes entre les  $p+l-r$  entrées affectées aux  $p+l-r$  éléments binaires de plus faible poids et  $p+l-r$  sorties,

- un premier multiplexeur possédant un premier groupe de r entrées recevant des expressions logiques des r éléments binaires de plus fort poids de X reçus par les r entrées correspondantes, et possédant un second groupe de r entrées portées à un

même niveau logique prédéterminé, ce premier multiplexeur possédant r sorties reliées aux r sorties restantes de cette première partie,

b) - une seconde partie constituée par :

- 5 . q+l entrées et q sorties, les q+l entrées recevant q+l éléments binaires définissant un nombre Y inférieur à B, ces éléments binaires étant répartis entre un élément binaire de plus faible poids et un élément binaire de plus fort poids, les q sorties étant reliées aux q dernières entrées d'adressage de la mémoire,

- 10 . q-r connexions directes entre les q-r entrées affectées aux q-r éléments binaires de plus faible poids de Y et q-r sorties,

- 15 . un second multiplexeur possédant un premier groupe de r entrées recevant des expressions logiques de r éléments binaires de plus fort poids de Y pris après l'élément binaire de Y ayant le plus fort poids et possédant un second groupe de r entrées reliées au premier groupe de r entrées du premier multiplexeur de la première partie, ce second multiplexeur possédant r sorties reliées aux r sorties restantes de cette seconde partie,

- 20 chaque multiplexeur possédant en outre une entrée de commande qui reçoit l'élément binaire de plus fort poids du nombre Y appliquée à l'entrée de plus fort poids de la seconde partie.

Dans ce qui précède, r est un entier vérifiant les relations :

$$30 \quad (2^r - 1) 2^{p+1-r} > A$$

(4)

$$2^q + 2^{q-r} > B$$

Grâce à ce circuit de transcodage, les r entrées d'adressage de la mémoire, qui sont reliées aux

sorties du premier multiplexeur reçoivent, selon la valeur de l'élément binaire de plus fort poids de Y, soit r expressions logiques de r éléments binaires de plus fort poids de X, soit r niveaux logiques prédéterminés ; les r entrées d'adressage de la mémoire qui sont reliées aux sorties du second multiplexeur reçoivent de même, soit les r éléments binaires de plus fort poids de Y pris après l'élément ayant le plus fort poids, soit les r éléments binaires de plus fort poids de X. Il y a donc 10 multiplexage d'adresses sur deux groupes de r entrées d'adressage.

Les caractéristiques de l'invention apparaîtront mieux après la description qui suit, d'exemples de réalisation donnés à titre explicatif et nullement limitatif. Cette description se réfère à des dessins annexés sur lesquels :

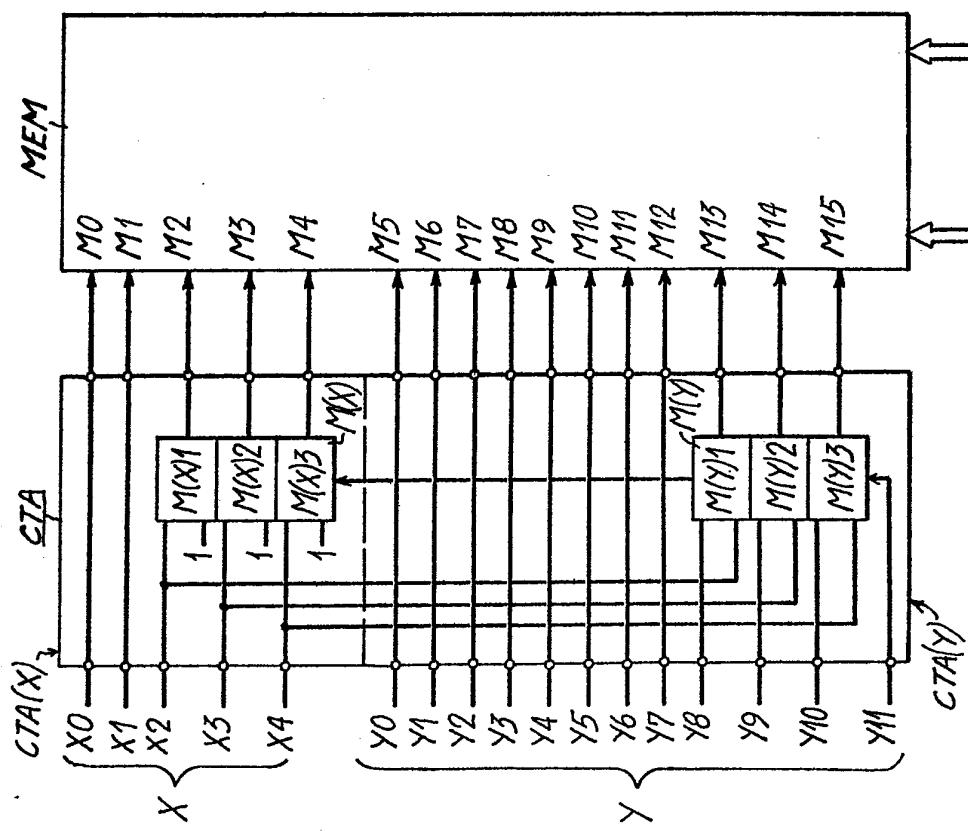

- la figure 1 est un diagramme montrant la place respective des nombres A et B par rapport aux puissances de 2,

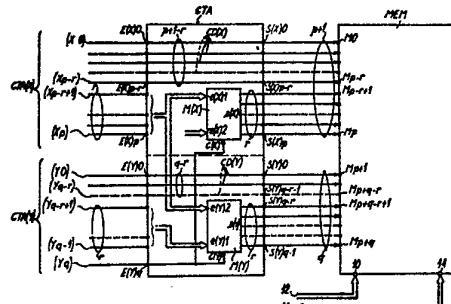

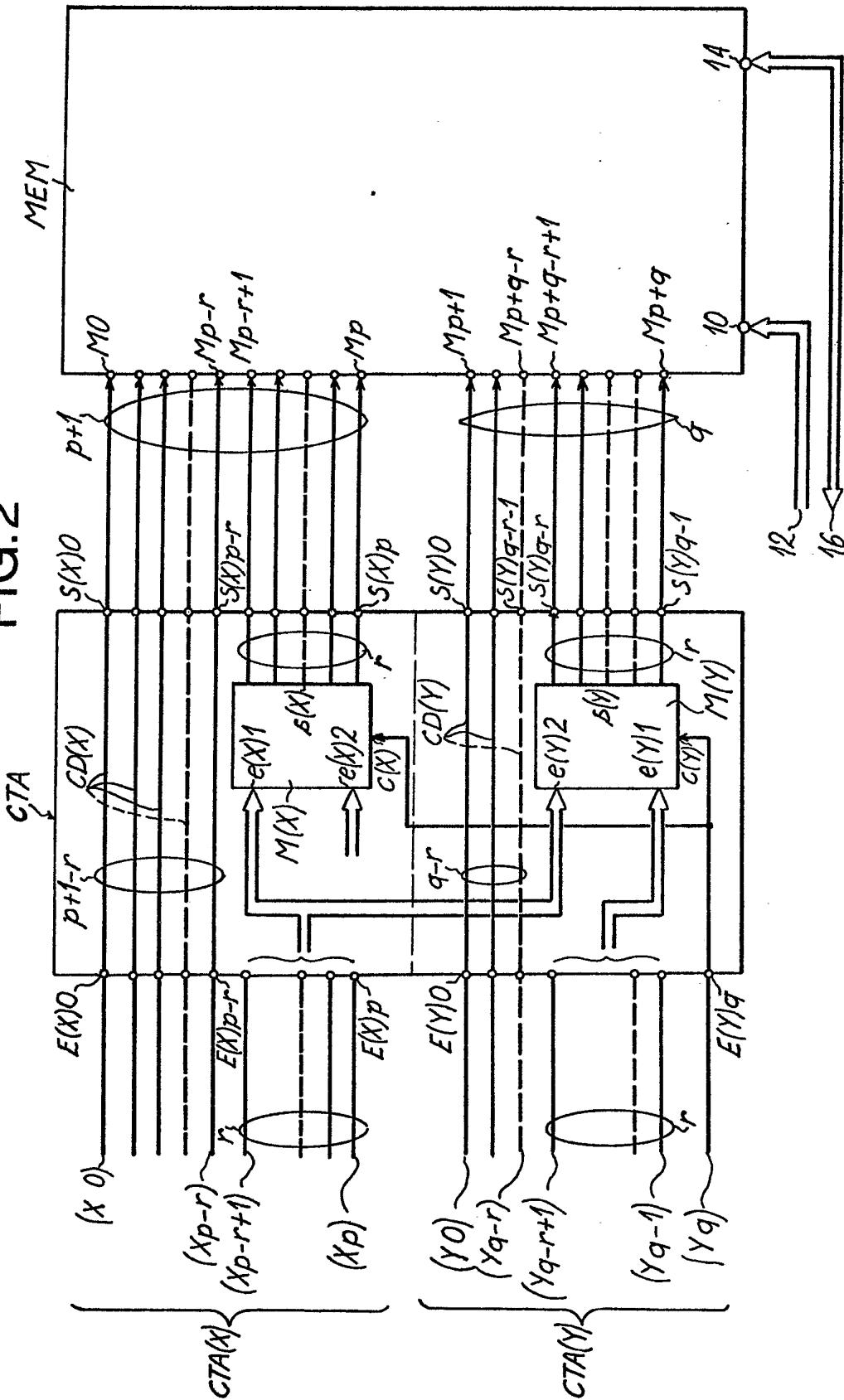

- 20 - la figure 2 est un schéma général d'une mémoire conforme à l'invention,

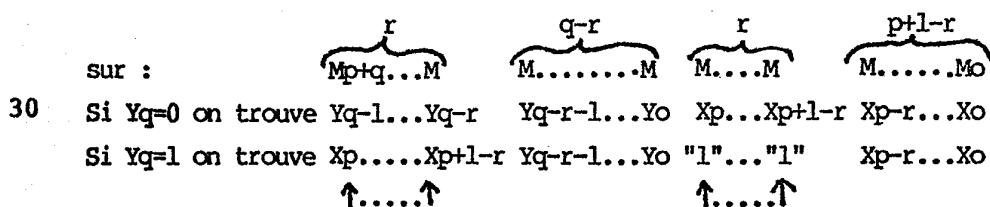

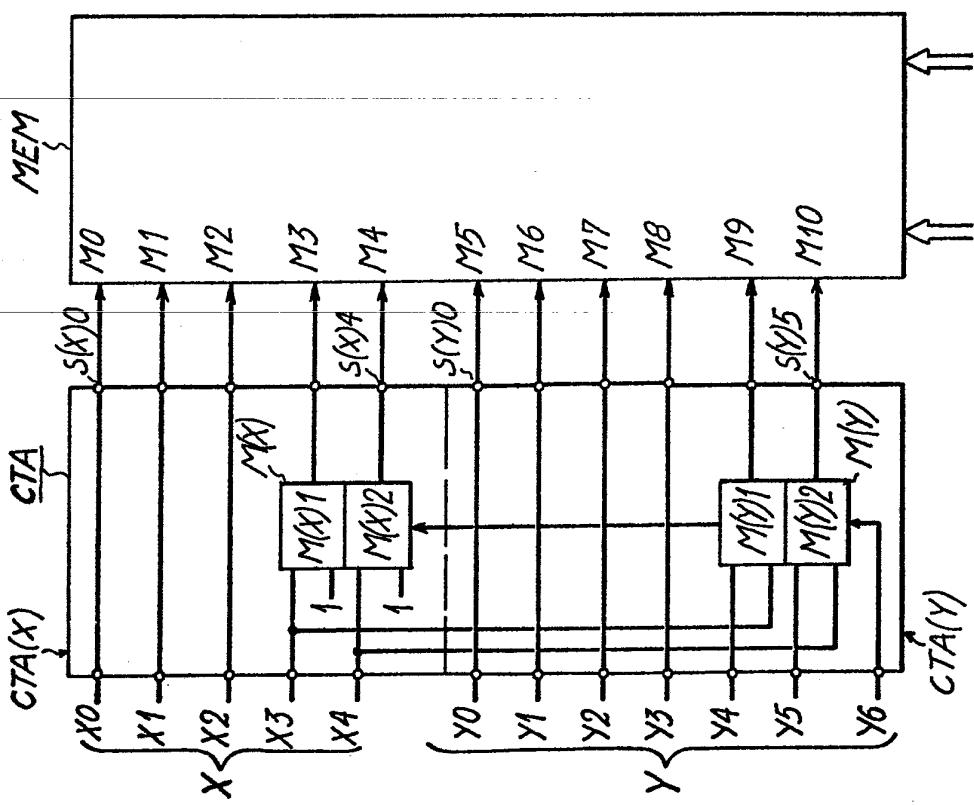

- la figure 3 illustre un mode particulier de réalisation d'une mémoire de 24x80 mots utilisant une mémoire de 2048 mots,

- 25 - la figure 4 illustre un autre mode particulier de réalisation d'une mémoire de 27x2288 mots utilisant une mémoire de 64K mots.

La figure 1 est un diagramme qui permet de préciser graphiquement les places relatives des nombres A et B et du produit AB. Ce dernier est supposé compris entre  $2^{p+q}$  et  $2^{p+q+1}$  et non entre  $2^{p+q+1}$  et  $2^{p+q+2}$  auquel cas, il n'y aurait pas d'autres moyens que d'utiliser une mémoire de capacité  $2^{p+q+2}$ . Le domaine d'application de l'invention correspond donc à la zone hachurée de l'axe.

35 L'idée qui est à la base de l'invention est de multiplexer certaines adresses pour réduire de  $p+q+2$  à

5       $p+q+r$  le nombre d'entrées d'adressage. Ce multiplexage est possible, en faisant intervenir judicieusement deux groupes de  $r$  adresses, le nombre  $r$  étant défini à partir de deux nombres  $A'$  et  $B'$  supérieurs ou égaux à  $A$  et  $B$ , respectivement :

$$\begin{aligned} A' &= 2^{p+1-r} (2^r - 1) \geq A \\ B' &= 2^{q-r} (2^r + 1) \geq B \end{aligned} \quad (4)$$

10

10      Le nombre  $A'$  étant égal à  $2^{p+1} - 2^{p+1-r}$ , il est donc inférieur à  $2^{p+1}$ . Le nombre  $B'$  étant égal à  $2^q + 2^{q-r}$ , il est donc inférieur à  $2^q + 2^q$  donc à  $2^{q+1}$ . Le produit  $A'B'$  est égal à  $2^{p+q+1} - 2^{p+q+1-2r}$ . Il est donc compris entre  $AB$  et  $2^{p+q+1}$ . Autrement dit, une mémoire de  $A'B'$  mots tombe bien dans le domaine de l'invention et présente une capacité supérieure à  $AB$ .

15      Les places respectives de  $A'$ ,  $B'$  et de  $A'B'$  sont marquées sur le diagramme de la figure 1.

20      Le point  $A'B'$  est bien dans la zone hachurée.

20      Au lieu de réaliser une mémoire de  $AB$  mots on va réaliser une mémoire de  $A'B'$  mots en utilisant la forme particulière du produit  $A'B'$ .

25      Lorsque l'élément binaire de plus fort poids de  $Y$  est à 1, ce qui donne à  $Y$  au moins la valeur  $2^q$ , tous les éléments binaires de  $Y$  de poids supérieur à  $q-r$  sont nécessairement nuls sinon  $B'$  excéderait  $2^q + 2^{q-r}$ . Ceci permet de multiplexer les adresses de la manière suivante :

25      -- $p+1-r$  entrées d'adressage vont recevoir en permanence

30      les  $p+1-r$  éléments binaires de poids faible du nombre  $X$  inférieur à  $A$ ,

30      -- $q-r$  entrées d'adressage vont recevoir en permanence les  $q-r$  éléments binaires de poids faible du nombre  $Y$  inférieur à  $B$ ,

--r entrées d'adressage vont recevoir :

- soit les r éléments binaires de poids fort de X quand l'élément binaire de poids fort de Y est à "0",

- 5 - soit "1" (c'est-à-dire un niveau logique prédéterminé) quand l'élément binaire de poids fort de Y est à "1".

--r autres entrées d'adressage vont recevoir :

- soit les r éléments binaires de poids fort de Y (sauf son élément binaire de plus fort poids) quand l'élément binaire de poids fort de Y est à "0",

- 10 - soit les r éléments binaires de poids fort de X quand l'élément binaire de poids fort de Y est à "1".

15 Pour préciser ces questions, on notera  $X_0 \dots X_p$  les  $p+1$  éléments binaires de X ( $X_0$  désignant l'élément binaire de plus faible poids et  $X_p$  l'élément binaire de plus fort poids) ; on notera de même  $Y_0 \dots Y_q$  les  $q+1$  éléments binaires de Y ( $Y_0$  étant l'élément binaire de plus 20 faible poids et  $Y_q$  l'élément binaire de plus fort poids) ; enfin, on notera  $M_0 \dots M_{p+q}$  les  $p+q+1$  entrées d'adressage de la mémoire.

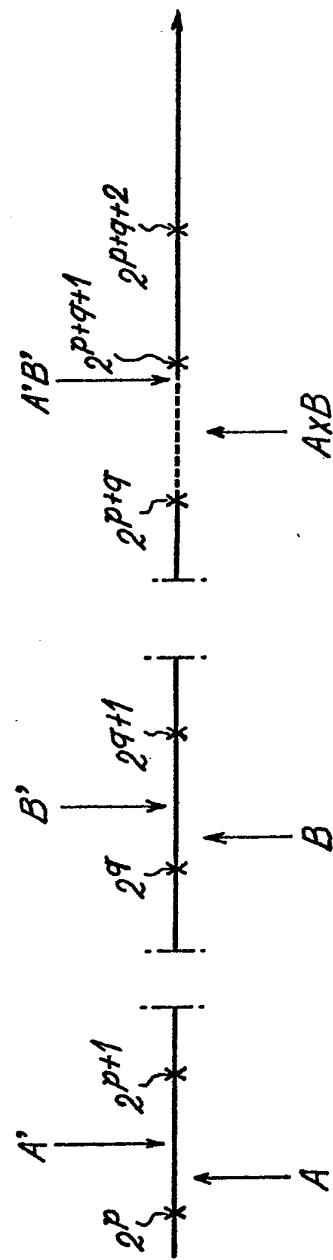

On peut alors écrire la correspondante entre 25 les entrées d'adressage et les éléments binaires d'adresse de la manière suivante :

Les entrées multiplexées sont marquées par des flèches.

Pour trouver l'entier  $r$ , on part des inégalités 35 (4) et on cherche la plus petite puissance de 2 supérieure

re à  $B - 2^q$ , ce qui va donner  $2^{q-r}$ . On en déduit la plus grande valeur de  $r$  possible et on vérifie si cette valeur satisfait la première inéquation des inégalités (4), relative à  $A$ , à savoir  $(2^{r-1}) \cdot 2^{p+1-r} > A$ .

5

Si  $r$  existe, il peut y avoir plusieurs valeurs convenantes. Dans ce cas, on choisit de préférence la plus petite.

Si  $r$  n'existe pas, on renouvelle l'essai en permutant  $A$  et  $B$ .

10

D'un point de vue concret, une mémoire conçue selon l'invention se présente sous la forme illustrée sur la figure 2. La mémoire proprement dite, MEM, comprend  $p+q+1$  entrées d'adressage notées  $M_0$  à  $M_{p+q}$ . Elle est précédée d'un circuit de transcodage d'adresses CTA, comprenant deux parties, respectivement  $CTA(X)$  et  $CTA(Y)$ , chargées de traiter les nombres  $X$  et  $Y$  qui constituent les adresses du mot à désigner parmi les  $A \times B$  mots possibles.

15

La première partie  $CTA(X)$  est constituée par :

- $p+1$  entrées notées  $E(X)_0 \dots E(X)_p$  et  $p+1$  sorties notées

20

- $S(X)_0 \dots S(X)_p$ ; les  $p+1$  entrées reçoivent les  $p+1$  éléments binaires  $X_0, X_1, \dots, X_p$  définissant le nombre  $X$ . Ces éléments binaires sont répartis entre un élément de plus faible poids,  $X_0$ , et un élément de plus fort poids ; les  $p+1$  sorties sont reliées à  $p+1$  premières entrées d'adressage de la mémoire, soit  $M_0$  à  $M_p$ .

- $p+1-r$  connexions directes  $CD(X)$  entre les  $p+1-r$  entrées

25

- $E(X)_0 \dots E(X)_{p-r}$  affectées aux  $p+1-r$  éléments binaires de plus faible poids  $X_0, \dots, X_{p-r}$  et  $p+1-r$  sorties  $S(X)_0 \dots S(X)_{p-r}$ .

30

- un premier multiplexeur  $M(X)$  possédant un premier groupe  $e(X)_1$  de  $r$  entrées recevant des expressions logiques de  $r$  éléments binaires de plus fort poids de  $X$  ( $X_{p-r+1} \dots X_p$ ) reçus par les  $r$  entrées correspondantes  $E(X)_{p-r+1} \dots E(X)_p$ ; le multiplexeur possède un second groupe  $e(X)_2$  de  $r$  entrées portées à un même niveau lo-

35

gique prédéterminé, par exemple à 1 ; ce premier multiplexeur possède enfin r sorties  $s(X)$  reliées aux r sorties restantes,  $S(X)p-r+1...S(X)p$ .

La seconde partie,  $CTA(Y)$ , du circuit de transcodage est constituée par :

- q+1 entrées notées  $E(Y)0...E(Y)q$  et q sorties notées  $S(Y)0...S(Y)q-1$  ; les q+1 entrées reçoivent q+1 éléments binaires, soit  $y_0, y_1, \dots, y_q$ , définissant le nombre Y ; ces éléments binaires sont répartis entre un élément de plus faible poids,  $y_0$ , et un élément de plus fort poids  $y_q$  ; les q sorties  $S(Y)0...S(Y)q-1$  sont reliées aux q dernières entrées d'adressage de la mémoire, soit  $M_p+1...M_p+q$ .

- q-r connexions directes  $CD(Y)$  entre les q-r entrées  $E(Y)0...E(Y)q-r$  affectées aux q-r éléments binaires de plus faible poids de Y et q-r sorties  $S(Y)0...S(Y)q-r-1$ ,

- un second multiplexeur  $M(Y)$  possédant un premier groupe  $e(X)1$  de r entrées recevant des expressions logiques des r éléments binaires  $y_{q-r}...y_{q-1}$  de plus fort poids de Y pris après l'élément binaire  $y_q$  de plus fort poids, et un second groupe  $e(Y)2$  de r entrées reliées au premier groupe de r entrées du premier multiplexeur de la première partie, ce second multiplexeur possédant r sorties  $s(Y)$  reliées aux r sorties restantes de cette seconde partie, soit  $S(Y)q-r...S(Y)q-1$ .

Chaque multiplexeur  $M(X)$ ,  $M(Y)$  possède en outre une entrée de commande, respectivement  $C(X)$ ,  $C(Y)$ , qui reçoit une expression logique de l'élément binaire de plus fort poids du nombre Y soit  $y_q$ , appliquée à l'entrée de plus fort poids  $E(Y)q$  de la seconde partie.

Les r entrées d'adressage  $M_p-r+1...M_p$  de la mémoire qui sont reliées aux sorties du premier multiplexeur  $M(X)$  reçoivent ainsi, selon la valeur de l'élément binaire  $y_q$  de plus fort poids de Y, r expressions

logiques des  $r$  éléments binaires de plus fort poids de  $X$ , soit  $r$  niveaux logiques prédéterminés. De même, les  $r$  entrées d'adressage  $M_p+q-r \dots M_p+q$  de la mémoire, qui sont reliées aux sorties du second multiplexeur, reçoivent soit les  $r$  éléments binaires de plus fort poids de  $Y$  pris après  $Y_q$ , soit les  $r$  éléments binaires de plus fort poids de  $X$ .

En plus de ses entrées d'adressage, la mémoire MEM comprend naturellement une entrée de commande 10 reliée à un bus de commande 12 et une entrée de données 14 reliée à un bus de données 16.

Dans la description qui précède, les entrées des multiplexeurs reçoivent certains éléments binaires mais elles pourraient évidemment recevoir leur complément. Dans ce cas, il suffirait d'ajouter, dans le circuit représenté, un inverseur logique entre l'entrée du circuit de transcodage et l'entrée du multiplexeur. Dans les exemples qui vont suivre, on supposera que les entrées des multiplexeurs reçoivent les éléments binaires eux-mêmes.

En pratique, chaque multiplexeur peut être constitué de  $r$  multiplexeurs élémentaires à deux entrées et une sortie. On peut utiliser par exemple le multiplexeur 74-LS 158 de la Société Texas Instruments.

Deux exemples de réalisation vont maintenant être décrits en référence aux figures 3 et 4.

Le premier exemple correspond à une mémoire d'écran d'affichage alphanumérique de 80x24 mots utilisant une mémoire de 2048 mots.

Avec les notations précédentes, on a  $p=6$  et  $q=4$  ainsi que  $A=80$  et  $B=24$ .

Les relations définissant  $r$  sont alors :

$$A' = (2^r - 1) \times 2^{6+1-r} \gg 80, \text{ et}$$

$$B' = 2^4 + 2^{4-r} \geq 24$$

La deuxième inéquation impose  $2^{4-r} \geq 24 - 16$ ,

soit  $2^{4-r} \geq 8$ , donc  $r=1$ . Il en résulte que  $A'=64$ . Comme

5 A' n'est pas supérieur à A, cette solution ne convient

pas.

On réitère l'essai en permutant les deux nom-

bres A et B. On prend donc cette fois  $p=4$  et  $q=6$  avec  $A=24$

et  $B=80$ .

10 On cherche alors r tel que :

$$A' = (2^r - 1) \times 2^{4+1-r} \geq 24, \text{ et}$$

$$B' = 2^6 + 2^{6-r} \geq 80.$$

15 La deuxième inéquation donne  $2^{6-r} \geq 80 - 64 = 16$ ,

d'où  $r=2$ . Il en résulte que  $A'=24$ , ce qui convient.

La solution est donc  $p=4$ ,  $q=6$ ,  $r=2$ .

Le schéma de multiplexage est alors le suivant,

20 où les fils multiplexés sont encore marqués par une flè-

che :

|        |    |    |    |    |    |    |     |     |    |    |    |

|--------|----|----|----|----|----|----|-----|-----|----|----|----|

| M10    | M9 | M8 | M7 | M6 | M5 | M4 | M3  | M2  | M1 | M0 |    |

| Y6=0 : | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 | X4  | X3  | X2 | X1 | X0 |

| Y6=1 : | X4 | X3 | Y3 | Y2 | Y1 | Y0 | "1" | "1" | X2 | X1 | X0 |

25 ↑ ↑ ↑ ↑

On obtient ainsi un circuit mémoire qui fait

juste  $24 \times 80$  mots et qui est représenté sur la figure 3.

30 Il comprend un premier multiplexeur M(X) constitué de

deux multiplexeurs  $2 \rightarrow 1$ , respectivement M(X)1 et M(X)2

dont les entrées reçoivent X3 et X4 d'une part, et deux

signaux logiques 1 d'autre part. Il comprend un second

multiplexeur M(Y) constitué, lui aussi, de deux multi-

35 plexeurs  $2 \rightarrow 1$ , respectivement M(Y)1 et M(Y)2 dont les en-

trées reçoivent  $Y_4$ ,  $Y_5$  d'une part et  $X_3$ ,  $X_4$  d'autre part. L'élément binaire  $Y_6$  de plus fort poids les commande tous deux. La mémoire MEM comprend 11 entrées d'adressage  $M_0$  à  $M_{10}$ . Le circuit de transcodage CTA possède cinq entrées pour l'adresse  $X$ , soit  $X_0$  à  $X_4$ , six entrées pour l'adresse  $Y$ , soit  $Y_0$  à  $Y_5$  plus l'entrée de commande pour  $Y_6$ , et onze sorties  $S(X)_0$  à  $S(X)_4$  et  $S(Y)_0$  à  $S(Y)_5$ .

Le second exemple correspond à une mémoire d'écran d'affichage graphique de  $27 \times 2288$  mots utilisant une mémoire de  $64K$  mots.

Dans cet exemple, on a  $p=4$  et  $q=11$  ainsi que  $A=27$  et  $B=2288$ .

On cherche  $r$  tel que :

$$15 \quad A' = (2^r - 1) \times 2^{4+1-r} \geq 27, \text{ et}$$

$$B' = 2^{11} + 2^{11-r} \geq 2288.$$

La deuxième inéquation donne  $r=3$ , d'où  $A'=28$ ,

20 solution qui convient. On obtient donc le schéma de multiplexage suivant :

$M_{15} M_{14} M_{13} M_{12} M_{11} M_{10} M_9 M_8 M_7 M_6 M_5 M_4 M_3 M_2 M_1 M_0$

si  $Y_{11}=0$   $Y_{10} Y_9 Y_8 Y_7 Y_6 Y_5 Y_4 Y_3 Y_2 Y_1 Y_0 X_4 X_3 X_2 X_1 X_0$

25 Si  $Y_{11}=1$   $X_4 X_3 X_2 Y_7 Y_6 Y_5 Y_4 Y_3 Y_2 Y_1 Y_0 "1" "1" "1" X_1 X_0$

De cette façon, on obtient une mémoire de  $28 \times 2304$  mots, soit  $1792 \times 2304$  points. Chaque mot peut prendre 64 éléments binaires dans le cas de l'application à l'affichage graphique. La figure 4 représente le circuit obtenu. Le circuit de transcodage d'adresses comprend cinq entrées affectées à  $X$  ( $X_0$  à  $X_4$ ) et douze entrées affectées à  $Y$  ( $Y_0$  à  $Y_{11}$ ). Les multiplexeurs  $M(X)$  et  $M(Y)$  comprennent chacun trois multiplexeurs  $2 \rightarrow 1$ . Le pre-

**2540277**

**12**

mier multiplexe les éléments X2, X3, X4 avec un même niveau logique "1" et le second les éléments Y8, Y9, Y10 avec X2, X3, X4. La commande du multiplexage s'effectue par Y11.

REVENDICATIONS

1. Mémoire destinée à mémoriser  $A \times B$  mots, où A et B sont des nombres qui vérifient les inégalités :

5

$$2^p < A < 2^{p+1}$$

$$2^q < B < 2^{q+1}$$

$$2^{p+q} < A \times B < 2^{p+q+1}$$

- 10 où p et q sont des entiers, caractérisée en ce qu'elle comprend  $p+q+1$  entrées d'adressage reliées à un circuit de transcodage d'adresses (CTA) comprenant deux parties :

- a) - une première partie (CTA)X constituée par :

- $p+1$  entrées  $E(X)0...E(X)p$  et  $p+1$  sorties  $S(X)0...S(X)p$ , les  $p+1$  entrées recevant  $p+1$  éléments binaires ( $X_0...X_p$ ) définissant un nombre X inférieur à A, ces éléments binaires étant répartis entre un élément de plus faible poids ( $X_0$ ) et un élément de plus fort poids ( $X_p$ ), les  $p+1$  sorties étant reliées à  $p+1$  premières entrées d'adressage ( $M_0...M_p$ ) de la mémoire (MEM),

- $p+1-r$  connexions directes  $CD(X)$  entre les  $p+1-r$  entrées affectées aux  $p+1-r$  éléments binaires de X de plus faible poids et  $p+1-r$  sorties,

- un premier multiplexeur  $M(X)$  possédant un premier groupe  $e(X)1$  de r entrées recevant des expressions logiques des r éléments binaires ( $X_{p-r+1}...X_p$ ) de plus fort poids de X reçus par les r entrées correspondantes, et un second groupe  $e(X)2$  de r entrées portées à un même niveau logique prédéterminé, de premier multiplexeur possédant r sorties  $s(X)$  reliées aux r sorties restantes de cette première partie,

b) - une seconde partie CTA(Y) constituée par :

- q+1 entrées  $E(Y)0...E(Y)q$  et q sorties  $S(Y)0...S(Y)q-1$ , les q+1 entrées recevant q+1 éléments binaires  $(Y_0...Y_q)$  définissant un nombre Y inférieur à B, ces éléments binaires étant répartis entre un élément de plus faible poids ( $Y_0$ ) et un élément de plus fort poids ( $Y_q$ ), les q sorties étant reliées aux q dernières entrées d'adressage  $(M_{p+1}...M_{p+q})$  de la mémoire,

- q-r connexions directes  $CD(Y)$  entre les q-r entrées affectées aux q-r éléments binaires de plus faible poids de Y et q-r sorties,

- un second multiplexeur  $M(Y)$  possédant un premier groupe  $e(Y)1$  de r entrées recevant des expressions logiques des r éléments binaires de plus fort poids  $(Y_{q-r+1}...Y_{q-1})$  de Y pris après l'élément binaire de Y ayant le plus fort poids ( $Y_q$ ) et un second groupe  $e(Y)2$  de r entrées reliées au premier groupe de r entrées  $e(X)1$  du premier multiplexeur  $M(X)$  de la première partie, ce second multiplexeur possédant r sorties  $s(Y)$  reliées aux r sorties restantes  $S(X)q-r...S(Y)q-1$  de cette seconde partie,

- chaque multiplexeur possédant en outre une entrée de commande  $C(X)$ ,  $C(Y)$  qui reçoit l'élément binaire ( $Y_q$ ) de plus fort poids du nombre Y appliqué à l'entrée  $E(Y)q$  de plus fort poids de la seconde partie, les r entrées d'adressage  $(M_{p-r+1}...M_p)$  de la mémoire qui sont reliées aux sorties du premier multiplexeur  $M(X)$  recevant ainsi, selon la valeur de l'élément binaire ( $Y_q$ ) de plus fort poids de Y, soit r expressions logiques des r éléments binaires  $(X_{p-r+1}...X_p)$  de plus fort poids de X, soit r niveaux logiques prédéterminés, et les r entrées d'adressage  $(M_{p+q-r+1}...M_{p+q})$  de la mémoire qui sont reliées aux sorties du second multiplexeur

5      M(Y) recevant de même soit les r éléments binaires de plus fort poids de Y pris après l'élément ayant le plus fort poids ( $Y_q=r+1 \dots Y_{q-1}$ ), soit les r éléments binaires de plus fort poids de X ( $X_{p-r+1} \dots X_p$ ), dans ce qui précède, r étant un entier vérifiant les relations :

$$(2^r - 1) 2^{p+1-r} > A$$

$$2^q + 2^{q-r} > B.$$

10

2. Mémoire selon la revendication 1, caractérisée en ce que chaque multiplexeur M(X), M(Y) est constitué de r multiplexeurs 2→1.

15     3. Mémoire selon la revendication 1, caractérisée en ce que lesdites expressions logiques d'éléments binaires sont les éléments binaires eux-mêmes.

20     4. Mémoire selon la revendication 1, caractérisée en ce qu'elle est apte à traiter 24x80 mots et en ce qu'elle comprend une mémoire à onze entrées d'adressage, et un circuit de transcodage d'adresses comprenant :

- une première partie comprenant cinq entrées, cinq sorties, deux multiplexeurs 2→1,

- une seconde partie à six entrées d'adressage plus une entrée de commande et six sorties, et deux multiplexeurs 2→1.

25     5. Mémoire selon la revendication 1, caractérisée en ce qu'elle est apte à traiter 27x2288 mots et en ce qu'elle comprend une mémoire à seize entrées d'adressage et un circuit de transcodage d'adresses comprenant :

- une première partie comprenant cinq entrées, cinq sorties, et trois multiplexeurs 2→1,

- une seconde partie comprenant onze entrées d'adressage, plus une douzième de commande, et onze sorties et trois multiplexeurs 2→1.

2540277

1/3

FIG.1

2/3

FIG. 2

2540277

**FIG.3**

**FIG.4**