(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5489946号

(P5489946)

(45) 発行日 平成26年5月14日(2014.5.14)

(24) 登録日 平成26年3月7日(2014.3.7)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO3F 3/343 (2006.01)  | HO3F 3/343 A    |

| HO1L 29/786 (2006.01) | HO1L 29/78 618B |

| HO3F 3/08 (2006.01)   | HO1L 29/78 618G |

|                       | HO3F 3/08       |

請求項の数 10 (全 73 頁)

(21) 出願番号 特願2010-231402 (P2010-231402)

(22) 出願日 平成22年10月14日 (2010.10.14)

(65) 公開番号 特開2011-109646 (P2011-109646A)

(43) 公開日 平成23年6月2日 (2011.6.2)

審査請求日 平成25年9月2日 (2013.9.2)

(31) 優先権主張番号 特願2009-242853 (P2009-242853)

(32) 優先日 平成21年10月21日 (2009.10.21)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 広瀬 篤志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 津吹 将志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】アナログ回路

## (57) 【特許請求の範囲】

## 【請求項1】

リファレンストランジスタと、ミラートランジスタと、検出器と、を有し、前記リファレンストランジスタは前記検出器と電気的に接続され、前記リファレンストランジスタのドレインとゲートは電気的に接続され、前記リファレンストランジスタのゲートは前記ミラートランジスタのゲートと電気的に接続され、

前記リファレンストランジスタと前記ミラートランジスタは、ドレイン電圧が1V及び10Vの場合において、ゲート電圧が-5Vから-20Vの範囲におけるドレイン電流が $1 \times 10^{-13} A$ 以下である酸化物半導体を有することを特徴とするアナログ回路。

10

## 【請求項2】

請求項1において、

前記ミラートランジスタは、複数の薄膜トランジスタが並列接続されていることを特徴とするアナログ回路。

## 【請求項3】

請求項1または請求項2において、

前記ミラートランジスタのチャネル幅は、前記リファレンストランジスタのチャネル幅よりも大きいことを特徴とするアナログ回路。

## 【請求項4】

請求項1乃至請求項3のいずれか一項において、

20

前記酸化物半導体のチャネル領域のキャリア濃度が $5 \times 10^{14} / \text{cm}^3$ 以下であることを特徴とするアナログ回路。

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、

前記酸化物半導体のチャネル領域の水素濃度が $5 \times 10^{19} \text{ atoms/cm}^3$ 以下であることを特徴とするアナログ回路。

**【請求項 6】**

第1端子が高電源電位に電気的に接続された第1の薄膜トランジスタと、

第1端子が高電源電位に電気的に接続された第2の薄膜トランジスタと、

前記高電源電位と、前記第1の薄膜トランジスタの前記第1端子との間に、検出器と、10を有し、

前記第1の薄膜トランジスタのゲートは、前記検出器と前記第1の薄膜トランジスタの前記第1端子の間に電気的に接続され、

前記第2の薄膜トランジスタのゲートは、前記第1の薄膜トランジスタのゲートと電気的に接続され、

前記第1の薄膜トランジスタの第2端子と、前記第2の薄膜トランジスタの第2端子とは、低電源電位に電気的に接続され、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタは、ドレイン電圧が1V及び10Vの場合において、ゲート電圧が-5Vから-20Vの範囲におけるドレイン電流が $1 \times 10^{-13} \text{ A}$ 以下である酸化物半導体を有することを特徴とするアナログ回路。20

**【請求項 7】**

請求項6において、

前記第2の薄膜トランジスタは、複数の薄膜トランジスタが並列接続されていることを特徴とするアナログ回路。

**【請求項 8】**

請求項6または請求項7において、

前記第2の薄膜トランジスタのチャネル幅は、前記第1の薄膜トランジスタのチャネル幅よりも大きいことを特徴とするアナログ回路。

**【請求項 9】**

請求項6乃至請求項8のいずれか一項において、

前記酸化物半導体のチャネル領域のキャリア濃度が $5 \times 10^{14} / \text{cm}^3$ 以下であることを特徴とするアナログ回路。30

**【請求項 10】**

請求項6乃至請求項9のいずれか一項において、

前記酸化物半導体のチャネル領域の水素濃度が $5 \times 10^{19} \text{ atoms/cm}^3$ 以下であることを特徴とするアナログ回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一形態は、酸化物半導体を用いた電界効果型トランジスタを有するアナログ回路に関する。また、該アナログ回路を有する半導体装置に関する。40

**【0002】**

なお、本明細書において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電気器機は全て半導体装置である。

**【背景技術】**

**【0003】**

絶縁表面を有する基板上に形成された半導体薄膜を用いて薄膜トランジスタ(TFT: Thin Film Transistor)を構成する技術が注目されている。薄膜トランジスタは液晶テレビに代表されるような表示装置に用いられている。薄膜トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が公知であるが、その他の材料とし50

て酸化物半導体が注目されている。

**【0004】**

酸化物半導体の材料としては、酸化亜鉛又は酸化亜鉛を成分とする材料が知られている。そして、電子キャリア濃度が  $10^{18} / \text{cm}^3$  未満である非晶質金属酸化物（酸化物半導体）からなるもので形成された薄膜トランジスタが開示されている（特許文献 1 乃至 3）。

**【先行技術文献】**

**【特許文献】**

**【0005】**

【特許文献 1】特開 2006 - 165527 号公報

10

【特許文献 2】特開 2006 - 165528 号公報

【特許文献 3】特開 2006 - 165529 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

しかしながら、酸化物半導体は薄膜形成工程において化学量論的組成からのずれが生じてしまう。例えば、酸素の過不足によって酸化物半導体の電気伝導度が変化してしまう。また、酸化物半導体の薄膜形成中に混入する水素が酸素（O）-水素（H）結合を形成して電子供与体となり、電気伝導度を変化させる要因となる。さらに O - H は極性分子なので、酸化物半導体によって作製される薄膜トランジスタのような能動デバイスに対して特性の変動要因となる。

20

**【0007】**

電子キャリア濃度が  $10^{18} / \text{cm}^3$  未満としても、酸化物半導体においては実質的には n 型であり、前記特許文献 1 乃至 3 に開示される薄膜トランジスタのオン・オフ比は  $10^3$  しか得られていない。このような薄膜トランジスタのオン・オフ比が低い理由はオフ電流が高いことによるものである。

**【0008】**

オン・オフ比が低い薄膜トランジスタによって構成される回路は、回路動作が不安定になりやすい。また、アナログ回路に用いた場合のダイナミックレンジを十分に得ることができず、オフ電流が高いと、小さな信号の検出感度を高めることができないという問題がある。さらに、オフ電流が高いことにより、無駄に電流が流れ消費電力が増加するという問題がある。

30

**【0009】**

上述した課題に鑑み、本発明の一形態は、酸化物半導体を用いて形成された薄膜トランジスタによって構成される回路の誤動作を低減させることを課題の一とする。

**【0010】**

本発明の一態様は、酸化物半導体を用いて形成された薄膜トランジスタによって構成される回路のダイナミックレンジを高めることを課題の一とする。

**【0011】**

本発明の一態様は、酸化物半導体を用いて形成された薄膜トランジスタによって構成される回路の信号検出感度を高めることを課題の一とする。

40

**【0012】**

本発明の一態様は、酸化物半導体を用いて形成された薄膜トランジスタによって構成される回路の消費電力を低減することを課題の一とする。

**【課題を解決するための手段】**

**【0013】**

本発明の一形態は、酸化物半導体中で電子供与体（ドナー）となる不純物（水素、水分、水素化物、または水酸化物など）を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成される薄膜トランジスタによってアナログ回路を構成する。

50

## 【0014】

具体的には、酸化物半導体に含まれる水素が  $5 \times 10^{19} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{18} / \text{cm}^3$  以下、より好ましくは  $5 \times 10^{17} / \text{cm}^3$  以下として、酸化物半導体に含まれる水素若しくは OH 基を除去し、キャリア濃度を  $5 \times 10^{14} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{12} / \text{cm}^3$  以下とした酸化物半導体でチャネル領域が形成される薄膜トランジスタによってアナログ回路が構成される。

## 【0015】

また、当該酸化物半導体のエネルギーギャップを、 $2 \text{ eV}$  以上、好ましくは  $2.5 \text{ eV}$  以上、より好ましくは  $3 \text{ eV}$  以上として、ドナーを形成する水素等の不純物を極力低減し、キャリア濃度を  $1 \times 10^{14} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{12} / \text{cm}^3$  以下となるようにする。10

## 【0016】

このように高純度化された酸化物半導体は、薄膜トランジスタのチャネル領域に用いることで、チャネル幅が  $10 \text{ mm}$  の場合でさえも、ドレイン電圧が  $1 \text{ V}$  及び  $10 \text{ V}$  の場合において、ゲート電圧が  $-5 \text{ V}$  から  $-20 \text{ V}$  の範囲におけるドレイン電流が  $1 \times 10^{-13} \text{ A}$  以下となるように作用する。

## 【0017】

また、本発明の一態様は、リファレンストランジスタと、ミラートランジスタと、検出器を有し、リファレンストランジスタは検出器と電気的に接続され、リファレンストランジスタのドレインとゲートは電気的に接続され、リファレンストランジスタのゲートはミラートランジスタのゲートと電気的に接続され、リファレンストランジスタとミラートランジスタは、チャネル領域が、水素濃度が  $5 \times 10^{19} \text{ atoms/cm}^3$  以下である酸化物半導体によって構成されていることを特徴とするアナログ回路である。20

## 【0018】

また、本発明の一態様は、第 1 端子が高電源電位に電気的に接続された第 1 の薄膜トランジスタと、第 1 端子が高電源電位に電気的に接続された第 2 の薄膜トランジスタと、高電源電位と第 1 の薄膜トランジスタの第 1 端子の間に検出器を有し、第 1 の薄膜トランジスタのゲートは、検出器と第 1 の薄膜トランジスタの第 1 端子の間に電気的に接続され、第 2 の薄膜トランジスタのゲートは、第 1 の薄膜トランジスタのゲートに電気的に接続され、第 1 の薄膜トランジスタの第 2 端子と、第 2 の薄膜トランジスタの第 2 端子は低電源電位に電気的に接続され、第 1 の薄膜トランジスタと、第 2 の薄膜トランジスタは、チャネル領域が、水素濃度が  $5 \times 10^{19} \text{ atoms/cm}^3$  以下である酸化物半導体によって構成されていることを特徴とするアナログ回路である。30

## 【0019】

なお、本明細書において、濃度は二次イオン質量分析法 (Secondary Ion Mass Spectrometry。以下、SIMSともいう。) によって計測される。ただし、他の計測法が挙げられている場合など、特に記載がある場合にはこの限りではない。

## 【0020】

また、上記のアナログ回路を有する半導体装置も本発明の一態様である。40

## 【発明の効果】

## 【0021】

本発明の一態様によれば、高純度化された酸化物半導体を用いた薄膜トランジスタでアナログ回路を構成することで、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることができる。

## 【0022】

また、高純度化された酸化物半導体を用いた薄膜トランジスタを用いることで、安定して動作し、消費電力が低い半導体装置を得ることができる。

## 【図面の簡単な説明】

## 【0023】

- 【図 1】半導体装置の回路構成を示す図。

- 【図 2】半導体装置の断面構造を示す図。

- 【図 3】半導体装置の上面及び断面構造を示す図。

- 【図 4】半導体装置の作製工程を示す図。

- 【図 5】半導体装置の上面及び断面構造を示す図。

- 【図 6】半導体装置の作製工程を示す図。

- 【図 7】半導体装置の断面構造を示す図。

- 【図 8】半導体装置の作製工程を示す図。

- 【図 9】半導体装置の作製工程を示す図。

- 【図 10】半導体装置の作製工程を示す図。 10

- 【図 11】半導体装置の断面構造を示す図。

- 【図 12】半導体装置を示す図。

- 【図 13】半導体装置の画素等価回路を示す図。

- 【図 14】半導体装置の画素等価回路を示す図。

- 【図 15】半導体装置の断面構造を示す図。

- 【図 16】半導体装置を示す図。

- 【図 17】半導体装置を示す図。

- 【図 18】半導体装置を示す図。

- 【図 19】半導体装置を示す図。

- 【図 20】半導体装置を示す図。 20

- 【図 21】半導体装置を示す図。

- 【図 22】酸化物半導体を用いた逆スタガー型の薄膜トランジスタの縦断面図。

- 【図 23】図 22 に示す A - A' 断面におけるエネルギー・バンド図（模式図）。

- 【図 24】(A) ゲート (G1) に正の電位 (+ VG) が印加された状態を示し、(B) ゲート (G1) に負の電位 (- VG) が印加された状態を示す図。

- 【図 25】真空準位と金属の仕事関数 (M)、酸化物半導体の電子親和力 ( ) の関係を示す図。

#### 【発明を実施するための形態】

##### 【0024】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。 30

##### 【0025】

なお、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

##### 【0026】

また、トランジスタのソース端子及びドレイン端子は、トランジスタの構造や動作条件等によって替わるため、いずれがソース端子又はドレイン端子であるかを特定することが困難である。そこで、本書類においては、ソース端子及びドレイン端子の一方を第1端子、ソース端子及びドレイン端子の他方を第2端子と表記し、区別することとする。 40

##### 【0027】

また、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。また、本明細書にて用いる「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

##### 【0028】

(実施の形態 1 )

本明細書で開示する高純度化された酸化物半導体を用いた薄膜トランジスタは、アナログ回路に適用することができる。アナログ回路の代表例として、例えば、カレントミラー回路が挙げられる。カレントミラー回路を電流増幅回路として用いた場合、電流増幅回路のダイナミックレンジを広げることができ、特に微量電流に対する感度を向上させることができる。

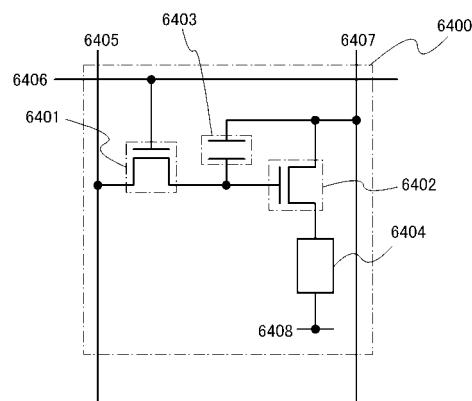

【 0 0 2 9 】

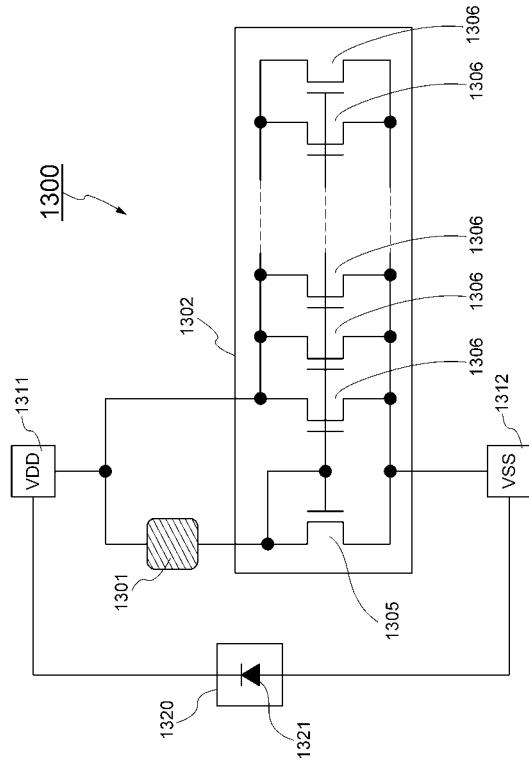

本実施の形態では、高純度化された酸化物半導体を用いた薄膜トランジスタをカレントミラー回路に適用する例として、光検出装置について図 1 を用いて説明する。

【 0 0 3 0 】

図 1 に示す光検出装置 1300 は、検出器 1301、増幅回路 1302、高電源電位 VD D が供給される電源端子 1311、低電源電位 VSS が供給される電源端子 1312、保護回路 1320 を有する。光検出装置 1300 では、電源端子 1312 の電位を接地電位 GND とすることもできる。

【 0 0 3 1 】

保護回路 1320 はダイオード 1321 を有する。ダイオード 1321 は、電源端子 1311 と電源端子 1312 の間に挿入され、ダイオード 1321 のカソードが電源端子 1311 に電気的に接続され、そのアノードが電源端子 1312 に電気的に接続されている。ESD などにより、電源端子 1311 および / または電源端子 1312 に過剰な電圧 (サージ) が印加された場合、ダイオード 1321 により電源端子 1311 と電源端子 1312 が短絡され、増幅回路 1302、および検出器 1301 に過剰な電圧が印加されることを防ぐ。

【 0 0 3 2 】

また、ダイオード 1321 として、ゲート端子とドレイン端子を接続し、ダイオードと同様の特性を持たせた薄膜トランジスタを用いることができる。本明細書で開示する高純度化された酸化物半導体を用いた薄膜トランジスタは、オフ電流値が極めて小さい特徴を有する。本明細書で開示する高純度化された酸化物半導体を有する薄膜トランジスタを用いてダイオードを形成することで、逆方向バイアスが加えられた時の漏れ電流が極めて小さいダイオードを実現することができる。なお、薄膜トランジスタを用いて形成した複数のダイオードを、直列や並列に接続して用いてもよい。

【 0 0 3 3 】

検出器 1301 は、受光した光を電気信号に変換する光電変換素子を用いる。光電変換素子としては、フォトダイオードやフォトトランジスタを用いることができる。増幅回路 1302 は、検出器 1301 の出力電流を増幅するための回路であり、ここでは、カレントミラー回路で構成されている。このカレントミラー回路は、1 つのトランジスタ 1305 と、並列に接続された複数のトランジスタ 1306 とを有する。トランジスタ 1305 とトランジスタ 1306 は、高純度化された酸化物半導体を用いた薄膜トランジスタで形成する。

【 0 0 3 4 】

トランジスタ 1305 は検出器 1301 の出力電流を検出するためのリファレンストランジスタであり、トランジスタ 1306 は、トランジスタ 1305 で検出された電流を反映して動作するミラートランジスタである。

【 0 0 3 5 】

トランジスタ 1306 の数で、電源端子 1311 と電源端子 1312 の間に流れる電流を調節することができる。例えば、トランジスタ 1305 とトランジスタ 1306 を同じ電流電圧特性を持つトランジスタで形成し、電源端子 1311 と電源端子 1312 の間に流れる電流を、検出器 1301 の出力電流の 100 倍とするには、例えば、1 つのトランジスタ 1305 に対して、99 個のトランジスタ 1306 を並列に接続する。このような構成とすることで、カレントミラー回路で構成された増幅回路 1302 を増幅率 100 倍の増幅回路とすることができます、検出器 1301 の出力電流を 100 倍に増幅して検出するこ

10

20

30

40

50

とができる。

【0036】

なお、上述の増幅回路1302を、トランジスタ1305と、トランジスタ1305とチャネル幅以外の構成が同じで、チャネル幅がトランジスタ1305のチャネル幅よりも大きいトランジスタ1306とを用いた構成とすることもできる。例えば、トランジスタ1305のチャネル幅の4.95倍のチャネル幅をもつトランジスタ1306を用い、1つのトランジスタ1305に対して、20個のトランジスタ1306を並列に接続した構成としても、増幅回路1302の増幅率を100倍とすることができます。

【0037】

また、トランジスタ1305と、トランジスタ1305とチャネル幅以外の構成が同じで、トランジスタ1305のチャネル幅の99倍のチャネル幅をもつトランジスタ1306を用い、1つのトランジスタ1305に対して、1つのトランジスタ1306を接続した構成としても、増幅率100倍の増幅回路1302とすることができます。この構成にすると、回路構成を簡潔にできるという利点があるものの、トランジスタ1306の機能が損なわれると、増幅回路1302全体の機能を著しく損なう可能性が高くなる。

【0038】

このため、増幅回路1302は、複数のトランジスタ1306を並列に接続し、冗長性を高めた構成とすることが好ましい。複数のトランジスタ1306を並列に接続する構成とすることにより、複数あるトランジスタ1306の一部の機能が損なわっても、増幅回路1302に与える影響を抑えることができ、安定して動作する信頼性の高い増幅回路1302とすることができます。例えば、トランジスタ1306を10個並列に接続することで、その中の1つのトランジスタ1306の機能が損なわっても、その影響を1/10とすることができる。

【0039】

また、複数のトランジスタ1306を並列に接続する構成とすることにより、トランジスタ1306の特性バラツキを低減させ、安定して動作する信頼性の高い増幅回路1302とすることができます。

【0040】

トランジスタ1306を2個以上、好ましくは5個以上を並列接続することで、信頼性の高い増幅回路1302とすることができます。すなわち、信頼性の高いカレントミラー回路を用いた光検出装置を作製することができます。

【0041】

増幅回路1302に用いる薄膜トランジスタのオフ電流が大きいと、微少光量の検出におけるS/N比を悪くしてしまう。つまり、検出器1301の出力電流に比べてオフ電流が無視できない大きさとなるため、検出器1301の出力電流を正確に得ることができない。

【0042】

非晶質シリコンまたは多結晶シリコンを用いた従来の薄膜トランジスタでは、チャネル幅を小さくする、または、チャネル長を大きくすることで、オフ電流をある程度小さくすることが可能ではあるが、同時にオン電流も低下してしまうという問題があった。このため、微少光量の検出と大光量の検出を両立させることが難しく、広いダイナミックレンジを得ることが難しかった。

【0043】

本明細書で開示する高純度化された酸化物半導体を用いた薄膜トランジスタは、チャネル幅を大きくしても、オフ電流を従来の薄膜トランジスタに比べて十分小さくできるため、微量電流に対する感度が良好で、ダイナミックレンジの広いカレントミラー回路を作製することができる。すなわち、ダイナミックレンジの広い光検出装置を作製することができる。

【0044】

本実施の形態では、検出器1301に光電変換素子を用いた光検出装置について説明した

10

20

30

40

50

が、検出器 1301 は他の様々な検出器を適用することができる。例えば、検出器 1301 に温度センサーを適用することで、温度検出装置とすることができます。また、検出器 1301 に音声センサーを適用し、音声検出装置としてだけでなく、音声増幅装置として用いることもできる。

#### 【0045】

本明細書で開示する高純度化された酸化物半導体を用いた薄膜トランジスタを用いたカレントミラー回路は、本実施の形態で説明した光検出装置に限定されず、他の半導体装置にも適用することができる。

#### 【0046】

##### (実施の形態 2)

10

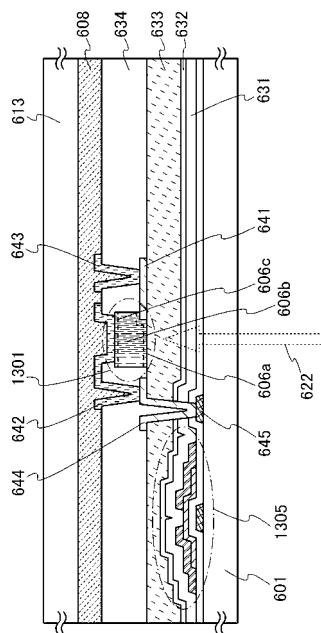

本実施の形態では、実施の形態 1 で説明した光検出装置 1300 の積層構成の一例について説明する。なお、本実施の形態では、検出器 1301 としてフォトダイオードを用いる例について説明する。図 2 は光検出装置 1300 の一部を示す断面図である。

#### 【0047】

図 2 は、フォトセンサにおける検出器 1301 及びトランジスタ 1305 に示す断面図であり、基板 601 上に、センサとして機能する検出器 1301 及びトランジスタ 1305 が設けられている。検出器 1301、トランジスタ 1305 の上には接着層 608 を用いて基板 613 が設けられている。

#### 【0048】

基板 601 に用いられる基板は、透光性を有し、作製工程における加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、アルミニシリケートガラス、バリウムホウケイ酸ガラスやアルミニホウケイ酸ガラスなどのガラス基板を用いることができる。また、プラスチック基板等も適宜用いることができる。

20

#### 【0049】

トランジスタ 1305 上には絶縁層 631、保護絶縁層 632、層間絶縁層 633、層間絶縁層 634 が設けられている。検出器 1301 は、層間絶縁層 633 上に設けられ、層間絶縁層 633 側から順に第 1 半導体層 606a、第 2 半導体層 606b、及び第 3 半導体層 606c を積層した構造を有している。第 1 半導体層 606a は層間絶縁層 633 上に設けられた電極層 641 と電気的に接続し、第 3 半導体層 606c は層間絶縁層 634 上に設けられた電極層 642 と電気的に接続している。

30

#### 【0050】

電極層 641 は、層間絶縁層 634 に形成された導電層 643 と電気的に接続し、電極層 642 は電極層 644 を介してゲート電極層 645 と電気的に接続している。ゲート電極層 645 は、トランジスタ 1305 のゲート電極層と電気的に接続している。すなわち、検出器 1301 はトランジスタ 1305 と電気的に接続している。

#### 【0051】

ここでは、第 1 半導体層 606a として p 型の導電型を有する半導体層と、第 2 半導体層 606b として高抵抗な半導体層 (I 型半導体層)、第 3 半導体層 606c として n 型の導電型を有する半導体層を積層する p-i-n 型のフォトダイオードを例示している。

#### 【0052】

第 1 半導体層 606a は p 型半導体層であり、p 型を付与する不純物元素を含むアモルファスシリコン膜により形成することができる。第 1 半導体層 606a の形成には 13 族の不純物元素（例えばボロン（B））を含む半導体材料ガスを用いて、プラズマ CVD 法により形成する。半導体材料ガスとしてはシラン（SiH<sub>4</sub>）を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub> 等を用いてもよい。また、不純物元素を含まないアモルファスシリコン膜を形成した後に、拡散法やイオン注入法を用いて該アモルファスシリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合にアモルファスシリコン膜を形成する方法としては、LPCVD 法、気相成長法、又はスパッタリング法等を用いればよい。第 1 半導体層 606a の膜厚は 10 nm 以上

40

50

0 nm 以下となるよう形成することが好ましい。

#### 【0053】

第2半導体層 606b は、I型半導体層（真性半導体層）であり、アモルファスシリコン膜により形成する。第2半導体層 606b の形成には、半導体材料ガスを用いて、アモルファスシリコン膜をプラズマCVD法により形成する。半導体材料ガスとしては、シラン（SiH<sub>4</sub>）を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>、SiHC<sub>1</sub><sub>3</sub>、SiC<sub>1</sub><sub>4</sub>、SiF<sub>4</sub>等を用いてもよい。第2半導体層 606b の形成は、LPCVD法、気相成長法、スパッタリング法等により行っても良い。第2半導体層 606b の膜厚は 200 nm 以上 1000 nm 以下となるように形成することが好ましい。なお、真性半導体層は、理想的には、不純物を含まずにフェルミレベルが禁制帯のほぼ中央に位置する半導体層であるが、第2半導体層 606b は、ドナーとなる不純物（例えば、リン（P）など）またはアクセプタとなる不純物（例えば、ボロン（B）など）を添加して、フェルミレベルが禁制帯のほぼ中央に位置するようにした半導体であってもよい。10

#### 【0054】

第3半導体層 606c は、n型半導体層であり、n型を付与する不純物元素を含むアモルファスシリコン膜により形成する。第3半導体層 606c の形成には、15族の不純物元素（例えばリン（P））を含む半導体材料ガスを用いて、プラズマCVD法により形成する。半導体材料ガスとしてはシラン（SiH<sub>4</sub>）を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>、SiHC<sub>1</sub><sub>3</sub>、SiC<sub>1</sub><sub>4</sub>、SiF<sub>4</sub>等を用いてもよい。また、不純物元素を含まないアモルファスシリコン膜を形成した後に、拡散法やイオン注入法を用いて該アモルファスシリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合にアモルファスシリコン膜を形成する方法としては、LPCVD法、気相成長法、又はスパッタリング法等を用いればよい。第3半導体層 606c の膜厚は 20 nm 以上 200 nm 以下となるよう形成することが好ましい。20

#### 【0055】

また、第1半導体層 606a、第2半導体層 606b、及び第3半導体層 606c は、アモルファス半導体ではなく、多結晶半導体を用いて形成してもよいし、微結晶半導体や、セミアモルファス（Semi Amorphous Semiconductor : SAS）半導体を用いて形成してもよい。30

#### 【0056】

微結晶半導体は、ギブスの自由エネルギーを考慮すれば非晶質と単結晶の中間的な準安定状態に属するものである。すなわち、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する。柱状または針状結晶が基板表面に対して法線方向に成長している。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す 520 cm<sup>-1</sup> よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す 520 cm<sup>-1</sup> とアモルファスシリコンを示す 480 cm<sup>-1</sup> の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダングリングボンド）を終端するため水素またはハロゲンを少なくとも 1 原子% またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。40

#### 【0057】

この微結晶半導体膜は、周波数が数十 MHz ~ 数百 MHz の高周波プラズマCVD法、または周波数が 1 GHz 以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>、SiHC<sub>1</sub><sub>3</sub>などの水素化珪素や、SiC<sub>1</sub><sub>4</sub>、SiF<sub>4</sub>などのハロゲン化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。

#### 【0058】

水素化珪素の希釈は、水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。さらには、シリコンを含む気体中に、 $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$ 等の炭化物気体、 $\text{GeH}_4$ 、 $\text{GeF}_4$ 等のゲルマニウム化気体、 $\text{F}_2$ 等を混入させてよい。

#### 【0059】

また、光電効果で発生した正孔の移動度は電子の移動度に比べて小さいため、 $\text{p i n}$ 型のフォトダイオードは $\text{p}$ 型の半導体層側を受光面とする方がよい特性を示す。ここでは、 $\text{p i n}$ 型のフォトダイオードが形成されている基板601の面から検出器1301が受ける光622を電気信号に変換する例を示す。また、受光面とした半導体層側とは逆の導電型を有する半導体層側からの光は外乱光となるため、電極層は遮光性を有する導電膜を用いるとよい。また、 $\text{n}$ 型の半導体層側を受光面として用いることもできる。10

#### 【0060】

基板613は、基板601と同様の基板を用いることができる。また、基板613は受光面の反対側に位置しているため、アルミニウムやステンレスなどの金属基板や、シリコンなどの半導体基板といった、遮光性を有する基板を用いることができる。

#### 【0061】

絶縁層631、保護絶縁層632、層間絶縁層633、層間絶縁層634としては、絶縁性材料を用いて、その材料に応じて、スパッタリング法、スピンドルコート法、ディップティング法、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。20

#### 【0062】

絶縁層631としては、酸化シリコン層、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アルミニウム層などの酸化物絶縁層の単層、又は積層を用いることができる。

#### 【0063】

保護絶縁層632としては、無機絶縁材料としては、窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、又は窒化酸化アルミニウム層などの窒化物絶縁層の単層、又は積層を用いることができる。また $\mu$ 波（2.45GHz）を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。

#### 【0064】

層間絶縁層633、634としては、表面凹凸を低減するため平坦化絶縁膜として機能する絶縁層が好ましい。層間絶縁層633、634としては、例えばアクリル樹脂、ポリイミド、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等の単層、又は積層を用いることができる。30

#### 【0065】

検出器1301に入射する光を検出することによって、被検出物の情報を読み取ることができる。なお、被検出物の情報を読み取る際にバックライトなどの光源を用いることができる。40

#### 【0066】

トランジスタ1305として、上記実施の形態で一例を示したトランジスタを用いることができる。水素、水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、高純度化された酸化物層を含むトランジスタは、トランジスタの電気的特性変動が抑制されており、電気的に安定である。よって、信頼性の高い半導体装置を提供することができる。

#### 【0067】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0068】

10

20

30

40

50

## (実施の形態 3 )

本実施の形態では、実施の形態 1 に示したアナログ回路が有する薄膜トランジスタの一例について示す。

## 【 0 0 6 9 】

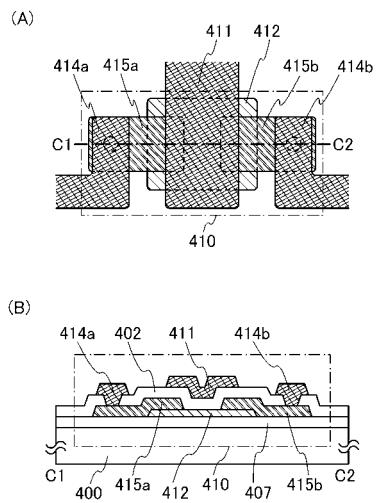

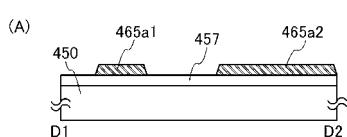

本実施の形態の薄膜トランジスタ及びその作製方法の一形態を、図 3 及び図 4 を用いて説明する。

## 【 0 0 7 0 】

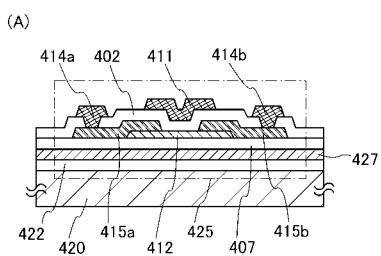

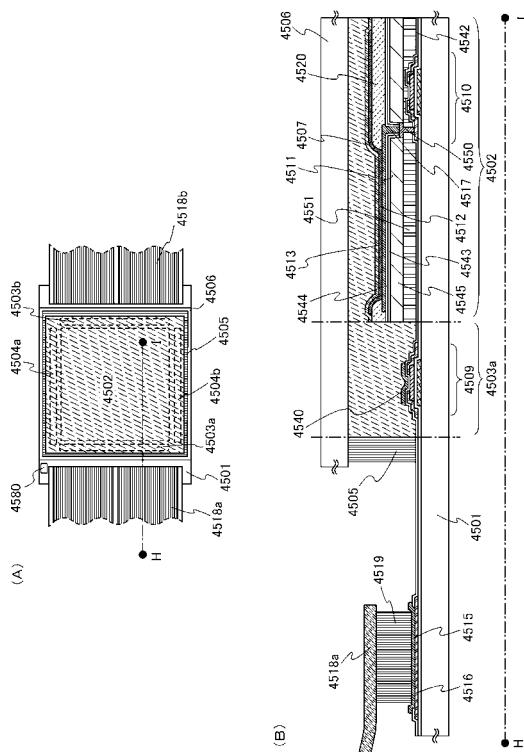

図 3 ( A )、( B )に薄膜トランジスタの上面及び断面構造の一例を示す。図 3 ( A )、( B )に示す薄膜トランジスタ 410 は、トップゲート構造の薄膜トランジスタの一つである。

10

## 【 0 0 7 1 】

図 3 ( A )はトップゲート構造の薄膜トランジスタ 410 の上面図であり、図 3 ( B )は図 3 ( A )の線 C1 - C2 における断面図である。

## 【 0 0 7 2 】

薄膜トランジスタ 410 は、絶縁表面を有する基板 400 上に、絶縁層 407、酸化物半導体層 412、ソース電極層又はドレイン電極層 415a、及びソース電極層又はドレイン電極層 415b、ゲート絶縁層 402、ゲート電極層 411 を含み、ソース電極層又はドレイン電極層 415a、ソース電極層又はドレイン電極層 415b にそれぞれ配線層 414a、配線層 414b が接して設けられ電気的に接続している。

20

## 【 0 0 7 3 】

また、薄膜トランジスタ 410 はシングルゲート構造の薄膜トランジスタを用いて説明したが、必要に応じて、チャネル領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

## 【 0 0 7 4 】

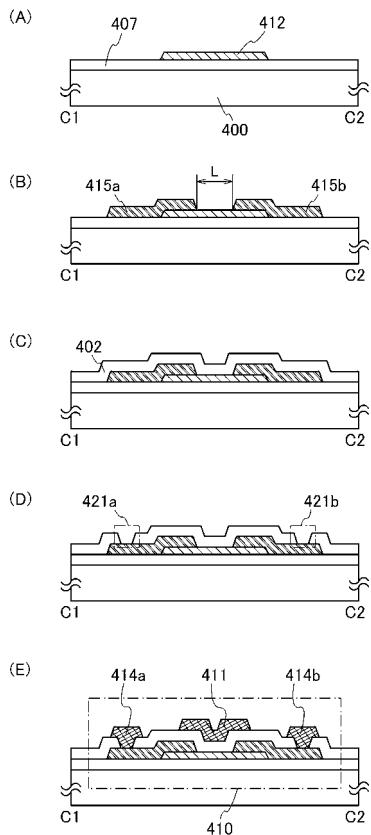

以下、図 4 ( A )乃至 ( E )を用い、基板 400 上に薄膜トランジスタ 410 を作製する工程を説明する。

## 【 0 0 7 5 】

絶縁表面を有する基板 400 に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

30

## 【 0 0 7 6 】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素 ( $B_2O_3$ ) と比較して酸化バリウム ( $BaO$ ) を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$  より  $BaO$  を多く含むガラス基板を用いることが好ましい。

## 【 0 0 7 7 】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。他にも、結晶化ガラスなどを用いることができる。また、プラスチック基板等も適宜用いることができる。

40

## 【 0 0 7 8 】

まず、絶縁表面を有する基板 400 上に下地膜となる絶縁層 407 を形成する。酸化物半導体層 412 と接する絶縁層 407 は、酸化シリコン層、酸化窒化シリコン層、酸化アルミニウム層、または酸化窒化アルミニウム層などの酸化物絶縁層を用いると好ましい。

## 【 0 0 7 9 】

絶縁層 407 の形成方法としては、プラズマ CVD 法又はスパッタリング法等を用いることができるが、絶縁層 407 中に水素が多量に含まれないようにするために、スパッタリング法で絶縁層 407 を成膜することが好ましい。

## 【 0 0 8 0 】

50

本実施の形態では、絶縁層407として、スパッタリング法により酸化シリコン層を形成する。基板400を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて、基板400に絶縁層407として、酸化シリコン層を成膜する。また基板400は室温でもよいし、加熱されていてもよい。

#### 【0081】

例えば、石英（好ましくは合成石英）を用い、基板温度108、基板とターゲットの間の距離（T-S間距離）を60mm、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン（酸素流量25sccm：アルゴン流量25sccm=1:1）雰囲気下でRFスパッタリング法により酸化シリコン層を成膜する。膜厚は100nmとする。なお、石英（好ましくは合成石英）に代えてシリコンターゲットを酸化シリコン層を成膜するためのターゲットとして用いることができる。なお、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

#### 【0082】

この場合において、処理室内の残留水分を除去しつつ絶縁層407を成膜することが好ましい。絶縁層407に水素、水酸基又は水分が含まれないようにするためである。

#### 【0083】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水（H<sub>2</sub>O）など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した絶縁層407に含まれる不純物の濃度を低減できる。

#### 【0084】

絶縁層407を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化合物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。

#### 【0085】

スパッタリング法にはスパッタ用電源に高周波電源を用いるRFスパッタリング法、直流電源を用いるDCスパッタリング法、さらにパルス的にバイアスを与えるパルスDCスパッタリング法がある。RFスパッタリング法は主に絶縁膜を成膜する場合に用いられ、DCスパッタリング法は主に金属膜を成膜する場合に用いられる。

#### 【0086】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

#### 【0087】

また、チャンバー内部に磁石機構を備えたマグネットロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタリング法を用いるスパッタ装置がある。

#### 【0088】

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

#### 【0089】

また、絶縁層407は積層構造でもよく、例えば、基板400側から窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、又は窒化酸化アルミニウムなどの窒化物絶縁層と、上記酸化物絶縁層との積層構造としてもよい。

#### 【0090】

例えば、酸化シリコン層と基板との間に水素及び水分が除去された高純度窒素を含むスパ

10

20

30

40

50

ツタガスを導入しシリコンターゲットを用いて窒化シリコン層を成膜する。この場合においても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成膜することが好ましい。

#### 【0091】

窒化シリコン層を形成する場合も、成膜時に基板を加熱してもよい。

#### 【0092】

絶縁層407として窒化シリコン層と酸化シリコン層とを積層する場合、窒化シリコン層と酸化シリコン層と同じ処理室において、共通のシリコンターゲットを用いて成膜することができる。先に窒素を含むスパッタガスを導入して、処理室内に装着されたシリコンターゲットを用いて窒化シリコン層を形成し、次に酸素を含むスパッタガスに切り替えて同じシリコンターゲットを用いて酸化シリコン層を成膜する。窒化シリコン層と酸化シリコン層とを大気に曝露せずに連続して形成することができるため、窒化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。10

#### 【0093】

次いで、絶縁層407上に、膜厚2nm以上200nm以下の酸化物半導体膜を形成する。。

#### 【0094】

また、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁層407が形成された基板400を予備加熱し、基板400に吸着した水素、水分などの不純物を脱離し排気することができる。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に形成するゲート絶縁層402の成膜前の基板400に行ってもよいし、後に形成するソース電極層又はドレイン電極層415a及びソース電極層又はドレイン電極層415bまで形成した基板400にも同様に行ってもよい。20

#### 【0095】

なお、酸化物半導体膜をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁層407の表面に付着しているゴミを除去することができる。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に高周波電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。30

#### 【0096】

酸化物半導体膜はスパッタリング法により成膜する。酸化物半導体膜は、In-Ga-Zn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Sn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-Ga-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いる。本実施の形態では、酸化物半導体膜をIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体膜は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（代表的にはアルゴン）及び酸素雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、酸化珪素（SiO<sub>x</sub>（X>0））を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。酸化物半導体層に結晶化を阻害する酸化珪素（SiO<sub>x</sub>（X>0））を含ませることで、製造プロセス中において酸化物半導体層の形成後に加熱処理した場合に、結晶化してしまうのを抑制することができる。なお、酸化物半導体層は非晶質な状態であることが好ましく、一部結晶化していくてもよい。40

#### 【0097】

酸化物半導体は、好ましくはInを含有する酸化物半導体、さらに好ましくは、In、及びGaを含有する酸化物半導体である。酸化物半導体層をI型（真性）とするため、後に50

説明する脱水化または脱水素化は有効である。

#### 【0098】

酸化物半導体膜を成膜する際に用いるスパッタガスとして、水素、水、水酸基又は水素化物などの不純物が、濃度 ppm 程度、濃度 ppb 程度まで除去された高純度ガスが好ましい。

#### 【0099】

酸化物半導体膜をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、molar 数比で  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$ 、原子数比で  $In : Ga : Zn = 1 : 1 : 0.5$  の組成を有する In、Ga、及び Zn を含む金属酸化物ターゲットを用いることができる。また、In、Ga、及び Zn を含む金属酸化物ターゲットとして、原子数比で  $In : Ga : Zn = 1 : 1 : 1$ 、または  $In : Ga : Zn = 1 : 1 : 2$  の組成を有するターゲットを用いることもできる。金属酸化物ターゲットの充填率は 90% 以上 100% 以下、好ましくは 95% 以上 99.9% 以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

10

#### 【0100】

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板 400 上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 ( $H_2O$ ) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

20

#### 【0101】

成膜条件の一例としては、基板温度室温、基板とターゲットの間の距離を 60 mm、圧力 0.4 Pa、直流 (DC) 電源 0.5 kW、酸素及びアルゴン（酸素流量 15 sccm : アルゴン流量 30 sccm）雰囲気下の条件が適用される。なお、パルス直流 (DC) 電源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜の膜厚は好ましくは 5 nm 以上 30 nm 以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

30

#### 【0102】

次いで、酸化物半導体膜を第 1 のフォトリソグラフィ工程により島状の酸化物半導体層 412 に加工する（図 4 (A) 参照）。また、島状の酸化物半導体層 412 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

40

#### 【0103】

なお、ここでの酸化物半導体膜のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

#### 【0104】

ドライエッチングに用いるエッティングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素 ( $Cl_2$ )、塩化硼素 ( $BCl_3$ )、塩化珪素 ( $SiCl_4$ )、四塩化炭素 ( $CCl_4$ ) など）が好ましい。

#### 【0105】

また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素 ( $CF_4$ )、弗化硫黄 ( $SF_6$ )、弗化窒素 ( $NF_3$ )、トリフルオロメタン ( $CHF_3$ ) など）、臭化水素 ( $HBr$ )、酸素 ( $O_2$ )、これらのガスにヘリウム ( $He$ ) やアルゴン ( $Ar$ ) などの希ガスを

50

添加したガス、などを用いることができる。

**【0106】**

ドライエッティング法としては、平行平板型 RIE (Reactive Ion Etching) 法や、ICP (Inductively Coupled Plasma: 誘導結合型プラズマ) エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

**【0107】**

ウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO 07N（関東化学社製）を用いてもよい。

10

**【0108】**

また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

**【0109】**

所望の加工形状にエッティングできるように、材料に合わせてエッティング条件（エッティング液、エッティング時間、温度等）を適宜調節する。

**【0110】**

本実施の形態では、エッティング液として磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッティング法により、酸化物半導体膜を島状の酸化物半導体層 412 に加工する。

20

**【0111】**

次に、本実施の形態では、酸化物半導体層 412 に、第 1 の加熱処理を行う。第 1 の加熱処理の温度は、400 以上 750 以下、好ましくは 400 以上 基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下 450 において 1 時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。この第 1 の加熱処理によって酸化物半導体層 412 の脱水化または脱水素化を行うことができる。

**【0112】**

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置等の RTA (Rapid Thermal Anneal) 装置を用いることができる。LRTA 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA 装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

30

**【0113】**

例えば、第 1 の加熱処理として、650 ~ 700 の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出す GRTA を行ってもよい。GRTA を用いると短時間での高温加熱処理が可能となる。

40

**【0114】**

なお、第 1 の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N (99.9999%) 以上、好ましくは 7N (99.99999%) 以上、（即ち不純物濃度を 1 ppm 以下、好ま

50

しくは 0.1 ppm 以下) とすることが好ましい。

#### 【0115】

上述の様にして、酸化物半導体中の不純物を低減させることにより、I型化又は実質的に I型化された酸化物半導体(高純度化された酸化物半導体)を得ることができる。具体的には、酸化物半導体に含まれる水素が  $5 \times 10^{-9} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{-8} / \text{cm}^3$  以下、より好ましくは  $5 \times 10^{-7} / \text{cm}^3$  以下として、酸化物半導体に含まれる水素若しくは OH 基を除去し、キャリア濃度を  $5 \times 10^{-4} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{-2} / \text{cm}^3$  以下とすることで、I型化又は実質的に I型化された酸化物半導体(高純度化された酸化物半導体)を得ることができる。

#### 【0116】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶層または多結晶層となる場合もある。例えば、結晶化率が 90% 以上、または 80% 以上の微結晶の酸化物半導体層となる場合もある。また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体層となる場合もある。また、非晶質の酸化物半導体の中に微結晶部(粒径 1 nm 以上 20 nm 以下(代表的には 2 nm 以上 4 nm 以下)) が混在する酸化物半導体層となる場合もある。

10

#### 【0117】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

20

#### 【0118】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にソース電極及びドレイン電極を積層させた後、ソース電極及びドレイン電極上にゲート絶縁層を形成した後、のいずれで行っても良い。

#### 【0119】

次いで、絶縁層 407 及び酸化物半導体層 412 上に、導電膜を形成する。導電膜をスパッタリング法や真空蒸着法で形成すればよい。導電膜の材料としては、アルミニウム(A1)、クロム(Cr)、銅(Cu)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タンクスチン(W)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン(Mn)、マグネシウム(Mg)、ジルコニウム(Zr)、ベリリウム(Be)、トリウム(Th)のいずれか一または複数から選択された材料を用いてもよい。また、金属導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する3層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タンクスチン、モリブデン、クロム、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、もしくは窒化膜を用いてもよい。

30

#### 【0120】

第2のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層 415a、ソース電極層又はドレイン電極層 415b を形成した後、レジストマスクを除去する(図4(B)参照)。なお、形成されたソース電極層、ドレイン電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。

40

#### 【0121】

本実施の形態ではソース電極層又はドレイン電極層 415a、ソース電極層又はドレイン電極層 415b を形成するための導電膜として、スパッタリング法により膜厚 150 nm のチタン膜を形成する。

#### 【0122】

50

なお、導電膜のエッティングの際に、酸化物半導体層412が除去されて、その下の絶縁層407が露出しないようにそれぞれの材料及びエッティング条件を適宜調節する。

#### 【0123】

本実施の形態では、導電膜としてTi膜を用いて、酸化物半導体層412にはIn-Ga-Zn-O系酸化物半導体を用いて、エッチャントとしてアンモニア過水（アンモニア、水、過酸化水素水の混合液）を用いる。

#### 【0124】

なお、第2のフォトリソグラフィ工程では、酸化物半導体層412は一部のみがエッティングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。10

#### 【0125】

第2のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層412上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第2のフォトリソグラフィ工程でのレジストマスク形成時の露光を行なう。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。20

#### 【0126】

次いで、絶縁層407、酸化物半導体層412、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415b上にゲート絶縁層402を形成する（図4（C）参照）。

#### 【0127】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層402中に水素が多量に含まれないようにするためには、スパッタリング法でゲート絶縁層402を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。30

#### 【0128】

ゲート絶縁層402は、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415b側から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。例えば、第1のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層（SiO<sub>x</sub>（x>0））を形成し、第1のゲート絶縁層上に第2のゲート絶縁層としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン層（SiN<sub>y</sub>（y>0））を積層して、膜厚100nmのゲート絶縁層としてもよい。本実施の形態では、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン（酸素流量25sccm：アルゴン流量25sccm=1:1）雰囲気下でRFスパッタリング法により膜厚100nmの酸化シリコン層を形成する。40

#### 【0129】

次いで、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッティングを行ってゲート絶縁層402の一部を除去して、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bに達する開口421a、開口421bを形成する（図4（D）参照）。50

## 【0130】

次に、ゲート絶縁層402、及び開口421a、421b上に導電膜を形成した後、第4のフォトリソグラフィ工程によりゲート電極層411、配線層414a、414bを形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0131】

また、ゲート電極層411、配線層414a、414bの材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

10

## 【0132】

例えば、ゲート電極層411、配線層414a、414bの2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、または銅層上にモリブデン層を積層した2層構造、または銅層上に窒化チタン層若しくは窒化タンタルを積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タングステン層または窒化タングステンと、アルミニウムとシリコンの合金またはアルミニウムとチタンの合金と、窒化チタンまたはチタン層とを積層した積層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。

20

## 【0133】

本実施の形態ではゲート電極層411、配線層414a、414bとしてスパッタリング法により膜厚150nmのチタン膜を形成する。

## 【0134】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好ましくは200以上400以下、例えば250以上350以下）を行う。本実施の形態では、窒素雰囲気下で250、1時間の第2の加熱処理を行う。また、第2の加熱処理は、薄膜トランジスタ410上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。

## 【0135】

さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

30

## 【0136】

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層412を有する薄膜トランジスタ410を形成することができる（図4（E）参照）。薄膜トランジスタ410は、実施の形態1及び2に示したアナログ回路を構成する薄膜トランジスタとして適用することができる。

## 【0137】

また、薄膜トランジスタ410上に保護絶縁層や、平坦化のための平坦化絶縁層を設けてもよい。例えば、保護絶縁層として酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。

40

## 【0138】

また、平坦化絶縁層としては、ポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンクガラス）、BPSG（リンクボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、平坦化絶縁層を形成してもよい。

50

## 【0139】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成された Si-O-Si 結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

## 【0140】

平坦化絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG 法、スピニコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を用いることができる。

10

## 【0141】

上記のように酸化物半導体膜を成膜する際に、反応雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

## 【0142】

なお、不純物を除去することにより I 型化又は実質的に I 型化された酸化物半導体（高純度化された酸化物半導体）は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁膜との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜（G I）は、高品質化が要求される。

## 【0143】

例えば、μ 波（2.45 GHz）を用いた高密度プラズマ CVD は、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができますからである。もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマ CVD 法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、酸化物半導体との界面特性が改質される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

20

## 【0144】

さらに、85、 $2 \times 10^6$  V/cm、12 時間のゲートバイアス・熱ストレス試験（BT 試験）においては、不純物が酸化物半導体に添加されていると、不純物と酸化物半導体の主成分との結合手が、強電界（B：バイアス）と高温（T：温度）により切断され、生成された結合手がしきい値電圧（Vth）のドリフトを誘発することとなる。これに対して、酸化物半導体の不純物、特に水素や水等を極力除去し、上記のようにゲート絶縁膜との界面特性を良好にすることにより、BT 試験に対しても安定な薄膜トランジスタを得ることを可能としている。

30

## 【0145】

上述した薄膜トランジスタを実施の形態 1 に示したアナログ回路に適用することによって、安定な電気特性を有し信頼性の高いアナログ回路を提供することができる。

40

## 【0146】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

## 【0147】

## (実施の形態 4)

本実施の形態では、実施の形態 1 に示したアナログ回路が有する薄膜トランジスタの一例について示す。なお、実施の形態 3 と同一部分又は同様な機能を有する部分、及び工程は、実施の形態 3 と同様とすればよく、その繰り返しの説明は省略する。また同じ箇所の詳細な説明も省略する。

## 【0148】

本実施の形態の薄膜トランジスタ及びその作製方法の一形態を、図 5 及び図 6 を用いて説

50

明する。

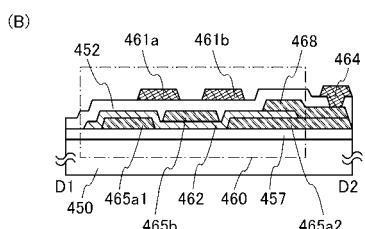

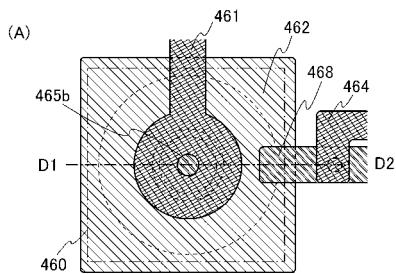

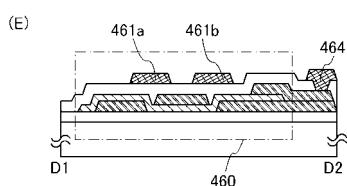

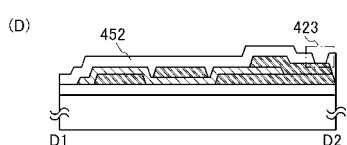

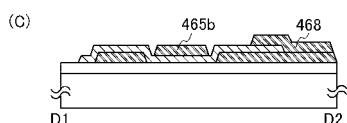

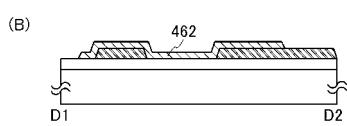

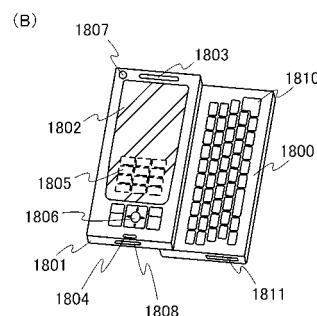

**【0149】**

図5(A)、(B)に薄膜トランジスタの平面及び断面構造の一例を示す。図5(A)、(B)に示す薄膜トランジスタ460は、トップゲート構造の薄膜トランジスタの一つである。

**【0150】**

図5(A)はトップゲート構造の薄膜トランジスタ460の平面図であり、図5(B)は図5(A)の線D1-D2における断面図である。

**【0151】**

薄膜トランジスタ460は、絶縁表面を有する基板450上に、絶縁層457、ソース電極層又はドレイン電極層465a(465a1、465a2)、酸化物半導体層462、ソース電極層又はドレイン電極層465b、配線層468、ゲート絶縁層452、ゲート電極層461(461a、461b)を含み、ソース電極層又はドレイン電極層465a(465a1、465a2)は配線層468を介して配線層464と電気的に接続している。また、図示していないが、ソース電極層又はドレイン電極層465bもゲート絶縁層452に設けられた開口において配線層と電気的に接続する。

**【0152】**

以下、図6(A)乃至(E)を用い、基板450上に薄膜トランジスタ460を作製する工程を説明する。

**【0153】**

まず、絶縁表面を有する基板450上に下地膜となる絶縁層457を形成する。

**【0154】**

本実施の形態では、絶縁層457として、スパッタリング法により酸化シリコン層を形成する。基板450を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタガスを導入しシリコンターゲット又は石英(好ましくは合成石英)を用いて、基板450に絶縁層457として、酸化シリコン層を成膜する。なお、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

**【0155】**

例えば、純度が6Nである石英(好ましくは合成石英)を用い、基板温度108°C、基板とターゲットとの間との距離(T-S間距離)を60mm、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により酸化シリコン層を成膜する。膜厚は100nmとする。なお、石英(好ましくは合成石英)に代えてシリコンターゲットを酸化シリコン層を成膜するためのターゲットとして用いることができる。

**【0156】**

この場合において、処理室内の残留水分を除去しつつ絶縁層457を成膜することが好ましい。絶縁層457に水素、水酸基又は水分が含まれないようにするためである。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜し絶縁層457に含まれる不純物の濃度を低減できる。

**【0157】**

絶縁層457を成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。

**【0158】**

また、絶縁層457は積層構造でもよく、例えば、基板450側から窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、窒化酸化アルミニウム層などの窒化物絶縁層と、上記酸化物絶縁層との積層構造としてもよい。

**【0159】**

例えば、酸化シリコン層と基板との間に水素及び水分が除去された高純度窒素を含むスパ

10

20

30

40

50

ツタガスを導入しシリコンターゲットを用いて窒化シリコン層を成膜する。この場合においても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成膜することが好ましい。

#### 【 0 1 6 0 】

次いで、絶縁層 4 5 7 上に、導電膜を形成し、第 1 のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 を形成した後、レジストマスクを除去する（図 6（A）参照）。ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 は断面図では分断されて示されているが、連続した膜である。なお、形成されたソース電極層、ドレイン電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。

10

#### 【 0 1 6 1 】

ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 の材料としては、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一または複数から選択された材料を用いてよい。また、金属導電膜は、単層構造でも、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する 2 層構造、Ti 膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する 3 層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、又は複数組み合わせた膜、合金膜、もしくは窒化膜を用いてよい。

20

#### 【 0 1 6 2 】

本実施の形態ではソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 としてスパッタリング法により膜厚 1 5 0 nm のチタン膜を形成する。

#### 【 0 1 6 3 】

次いで、絶縁層 4 5 7 及びソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 上に、膜厚 2 nm 以上 2 0 0 nm 以下の酸化物半導体膜を形成する。

#### 【 0 1 6 4 】

次に酸化物半導体膜を第 2 のフォトリソグラフィ工程により島状の酸化物半導体層 4 6 2 に加工する（図 6（B）参照）。本実施の形態では、酸化物半導体膜として In - Ga - Zn - O 系金属酸化物ターゲットを用いてスパッタリング法により成膜する。

30

#### 【 0 1 6 5 】

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板 4 5 0 上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

40

#### 【 0 1 6 6 】

酸化物半導体膜を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度 ppm 程度、濃度 ppb 程度まで除去された高純度ガスが好ましい。

#### 【 0 1 6 7 】

成膜条件の一例としては、基板温度室温、基板とターゲットの間の距離を 6 0 mm、圧力 0 . 4 Pa、直流 (DC) 電源 0 . 5 kW、酸素及びアルゴン（酸素流量 1 5 sccm : アルゴン流量 3 0 sccm）雰囲気下の条件が適用される。なお、パルス直流 (DC) 電

50

源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜の膜厚は好ましくは5 nm以上30 nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

#### 【0168】

本実施の形態では、エッティング液として磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッティング法により、酸化物半導体膜を島状の酸化物半導体層462に加工する。

#### 【0169】

本実施の形態では、酸化物半導体層462に、第1の加熱処理を行う。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。

ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。この第1の加熱処理によって酸化物半導体層462の脱水化または脱水素化を行うことができる。

10

#### 【0170】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、G R T A ( G a s R a p i d T h e r m a l A n n e a l ) 装置、L R T A ( L a m p R a p i d T h e r m a l A n n e a l ) 装置等のR T A ( R a p i d T h e r m a l A n n e a l ) 装置を用いることができる。例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すG R T A を行ってもよい。G R T A を用いると短時間での高温加熱処理が可能となる。

20

#### 【0171】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、（即ち不純物濃度を1 ppm以下、好ましくは0.1 ppm以下）とすることが好ましい。

#### 【0172】

30

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶層または多結晶層となる場合もある。

#### 【0173】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

#### 【0174】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にさらにソース電極又はドレイン電極を積層させた後、ソース電極及びドレイン電極上にゲート絶縁層を形成した後、のいずれで行っても良い。

40

#### 【0175】

次いで、絶縁層457及び酸化物半導体層462上に、導電膜を形成し、第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッティングを行ってソース電極層又はドレイン電極層465b、配線層468を形成した後、レジストマスクを除去する（図6（C）参照）。ソース電極層又はドレイン電極層465b、配線層468はソース電極層又はドレイン電極層465a1、465a2と同様な材料及び工程で形成すればよい。

#### 【0176】

本実施の形態ではソース電極層又はドレイン電極層465b、配線層468としてスパッタリング法により膜厚150 nmのチタン膜を形成する。本実施の形態では、ソース電極

50

層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 とソース電極層又はドレイン電極層 4 6 5 b に同じチタン膜を用いる例のため、ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 とソース電極層又はドレイン電極層 4 6 5 b とはエッチングにおいて選択比がとれない。よって、ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 が、ソース電極層又はドレイン電極層 4 6 5 b のエッチング時にエッチングされないように、酸化物半導体層 4 6 2 に覆われないソース電極層又はドレイン電極層 4 6 5 a 2 上に配線層 4 6 8 を設けている。ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 とソース電極層又はドレイン電極層 4 6 5 b とにエッチング工程において高い選択比を有する異なる材料を用いる場合には、エッチング時にソース電極層又はドレイン電極層 4 6 5 a 2 を保護する配線層 4 6 8 は必ずしも設けなくてもよい。

10

## 【0177】

なお、導電膜のエッチングの際に、酸化物半導体層 4 6 2 は除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

## 【0178】

本実施の形態では、導電膜として Ti 膜を用いて、酸化物半導体層 4 6 2 には In - Ga - Zn - O 系酸化物半導体を用いて、エッチャントとしてアンモニア過水（アンモニア、水、過酸化水素水の混合液）を用いる。

## 【0179】

なお、第 3 のフォトリソグラフィ工程では、酸化物半導体層 4 6 2 は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層 4 6 5 b、配線層 4 6 8 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

20

## 【0180】

次いで、絶縁層 4 5 7、酸化物半導体層 4 6 2、ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2、ソース電極層又はドレイン電極層 4 6 5 b 上にゲート絶縁層 4 5 2 を形成する。

## 【0181】

ゲート絶縁層 4 5 2 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層 4 5 2 中に水素が多量に含まれないようにするために、スパッタリング法でゲート絶縁層 4 5 2 を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

30

## 【0182】

ゲート絶縁層 4 5 2 は、ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2、ソース電極層又はドレイン電極層 4 6 5 b 側から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。本実施の形態では、圧力 0.4 Pa、高周波電源 1.5 kW、酸素及びアルゴン（酸素流量 25 sccm : アルゴン流量 25 sccm = 1 : 1）雰囲気下で RF スパッタリング法により膜厚 100 nm の酸化シリコン層を形成する。

40

## 【0183】

次いで、第 4 のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってゲート絶縁層 4 5 2 の一部を除去して、配線層 4 6 8 に達する開口 4 2 3 を形成する（図 6 (D) 参照）。図示しないが開口 4 2 3 の形成時にソース電極層又はドレイン電極層 4 6 5 b に達する開口を形成してもよい。本実施の形態では、ソース電極層又はドレイン電極層 4 6 5 b への開口はさらに層間絶縁層を積層した後に形成し、電気的に接続する配線層を開口に形成する例とする。

## 【0184】

次に、ゲート絶縁層 4 5 2、及び開口 4 2 3 上に導電膜を形成した後、第 5 のフォトリソ

50

グラフィ工程によりゲート電極層 461(461a、461b)、配線層 464を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0185】

また、ゲート電極層 461(461a、461b)、配線層 464の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0186】

本実施の形態ではゲート電極層 461(461a、461b)、配線層 464としてスパッタリング法により膜厚 150 nm のチタン膜を形成する。

10

#### 【0187】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好ましくは 200 以上 400 以下、例えば 250 以上 350 以下）を行う。本実施の形態では、窒素雰囲気下で 250 、1 時間の第2の加熱処理を行う。また、第2の加熱処理は、薄膜トランジスタ 410 上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。

#### 【0188】

さらに大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

20

#### 【0189】

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層 462 を有する薄膜トランジスタ 460 を形成することができる（図 6 (E) 参照）。

#### 【0190】

また、薄膜トランジスタ 460 上に保護絶縁層や、平坦化のための平坦化絶縁層を設けてもよい。なお、図示しないが、ゲート絶縁層 452 、保護絶縁層や平坦化絶縁層にソース電極層又はドレイン電極層 465b に達する開口を形成し、その開口に、ソース電極層又はドレイン電極層 465b と電気的に接続する配線層を形成する。

30

#### 【0191】

上記のように酸化物半導体膜を成膜する際に、反応雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

#### 【0192】

上述した薄膜トランジスタを実施の形態 1 に示したアナログ回路に適用することによって、安定な電気特性を有し信頼性の高いアナログ回路を提供することができる。

#### 【0193】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【0194】

40

#### (実施の形態 5)

本実施の形態では、実施の形態 1 に示したアナログ回路が有する薄膜トランジスタの一例について示す。なお、他の実施の形態の内容と同一部分または同様な機能を有する部分、及び工程は、他の実施の形態と同様とすればよく、その繰り返しの説明は省略する。また同じ箇所の詳細な説明も省略する。

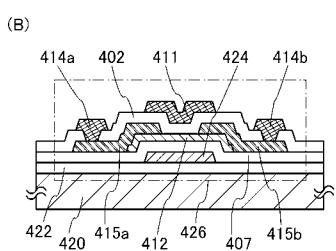

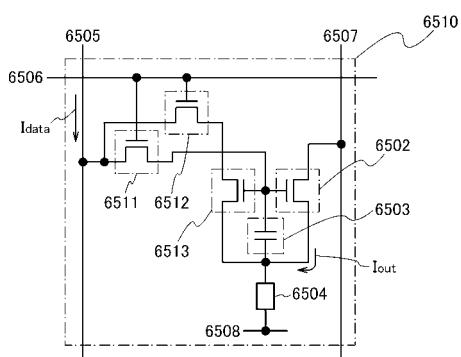

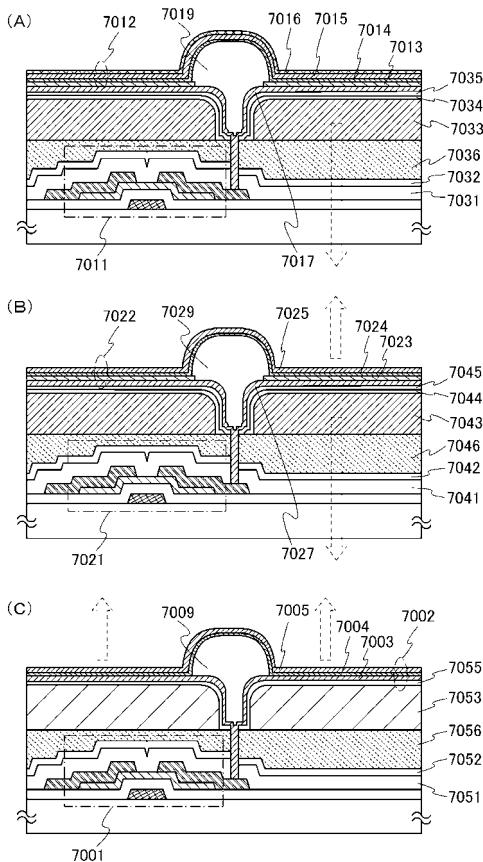

#### 【0195】

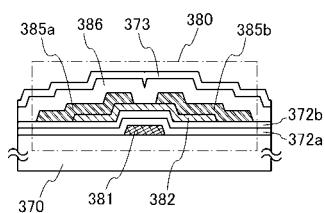

本実施の形態の薄膜トランジスタを、図 7 を用いて説明する。

#### 【0196】

図 7 (A)、(B) に薄膜トランジスタの断面構造の一例を示す。図 7 (A)、(B) に示す薄膜トランジスタ 425 、薄膜トランジスタ 426 は、酸化物半導体層を導電層とゲ

50

ート電極層とで挟んだ構造の薄膜トランジスタの一つである。

**【0197】**

また、図7(A)、(B)において、基板はシリコン基板を用いており、シリコン基板420上に設けられた絶縁層422上に薄膜トランジスタ425、薄膜トランジスタ426がそれぞれ設けられている。

**【0198】**

図7(A)において、シリコン基板420に設けられた絶縁層422と絶縁層407との間に少なくとも酸化物半導体層412全体と重なるように導電層427が設けられている。

**【0199】**

なお、図7(B)は、絶縁層422と絶縁層407との間の導電層が、導電層424のようにエッチングにより加工され、酸化物半導体層412の少なくともチャネル領域を含む一部と重なる例である。

10

**【0200】**

導電層427、導電層424は後工程で行われる加熱処理温度に耐えられる金属材料であればよく、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、スカンジウム(Sc)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物などを用いることができる。また、単層構造でも積層構造でもよく、例えばタングステン層単層、または窒化タングステン層とタングステン層との積層構造などを用いることができる。

20

**【0201】**

また、導電層427、導電層424は、電位が薄膜トランジスタ425、薄膜トランジスタ426のゲート電極層411と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層427、導電層424の電位がGND、0Vという固定電位であってもよく、どこにも接続せず電気的に浮遊した状態(フローティング)としても良い。

**【0202】**

導電層427、導電層424によって、薄膜トランジスタ425、薄膜トランジスタ426の電気特性を制御することができる。

30

**【0203】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【0204】**

ここで、本発明の一形態である酸化物半導体を用いた薄膜トランジスタについて、エネルギー・バンド図を用いて説明しておく。

**【0205】**

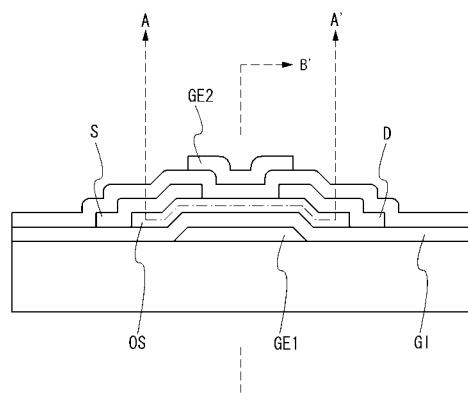

図22は、酸化物半導体を用いた逆スタガー型の薄膜トランジスタの縦断面図を示す。ゲート電極(GE1)上にゲート絶縁膜(GI)を介して酸化物半導体層(OS)が設けられ、その上にソース電極(S)及びドレイン電極(D)が設けられている。

40

**【0206】**

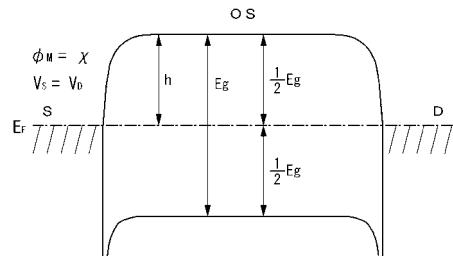

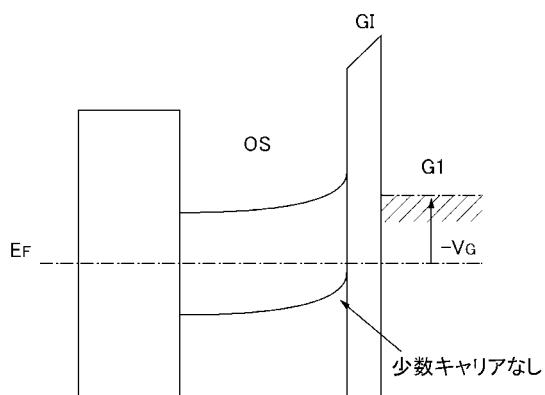

図23は、図22に示すA-A'断面におけるエネルギー・バンド図(模式図)を示す。図23(A)はソースとドレインの間の電圧を等電位(VD=0V)とした場合を示し、図23(B)はソースに対しドレインに正の電位(VD>0)をえた場合を示す。

**【0207】**

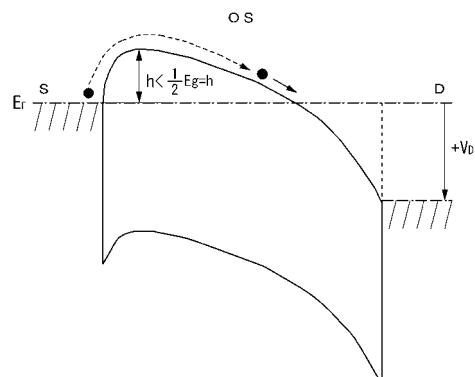

図24は、図22におけるB-B'の断面におけるエネルギー・バンド図(模式図)である。図24(A)はゲート(G1)に正の電位(+VG)が印加された状態であり、ソースとドレイン間にキャリア(電子)が流れるオン状態を示している。また、図24(B)は、ゲート(G1)に負の電位(-VG)が印加された状態であり、オフ状態(少数キャリアは流れない)である場合を示す。

**【0208】**

50

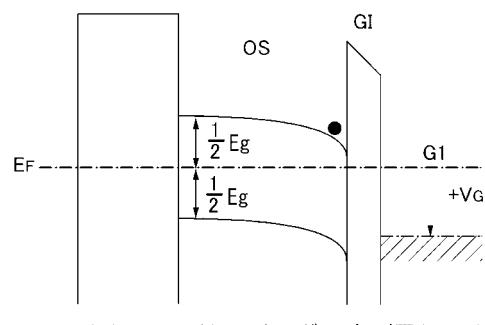

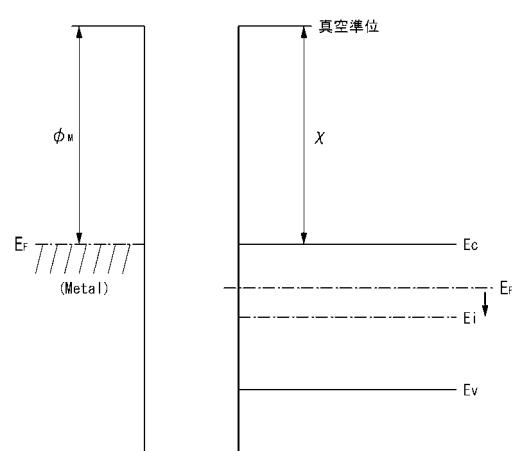

図25は、真空準位と金属の仕事関数( $M$ )、酸化物半導体の電子親和力( $\chi$ )の関係を示す。

#### 【0209】

金属は縮退しているため、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体は一般にn型であり、その場合のフェルミ準位( $E_f$ )は、バンドギャップ中央に位置する真性フェルミ準位( $E_i$ )から離れて、伝導帯寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなりn型化する一つの要因であることが知られている。

#### 【0210】

これに対して本発明に係る酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性(I型)とし、又は真性型とせんとしたものである。すなわち、不純物を添加してI型化するだけでなく、水素や水等の不純物を極力除去したことにより、高純度化されたI型(真性半導体)又はそれに近づけることを特徴としている。そうすることにより、フェルミ準位( $E_f$ )は真性フェルミ準位( $E_i$ )と同じレベルにまですることができる。

#### 【0211】

酸化物半導体のバンドギャップ( $E_g$ )が $3.15\text{ eV}$ である場合、電子親和力( $\chi$ )は $4.3\text{ eV}$ と言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力( $\chi$ )とほぼ等しい。この場合、金属・酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

#### 【0212】

すなわち、金属の仕事関数( $M$ )と酸化物半導体の電子親和力( $\chi$ )が等しい場合、両者が接触すると図23(A)で示すようなエネルギー-band図(模式図)が示される。

#### 【0213】

図23(B)において黒丸( $\bullet$ )は電子を示し、ドレインに正の電位が印加されると、電子はバリア( $h$ )をこえて酸化物半導体に注入され、ドレインに向かって流れる。この場合、バリア( $h$ )の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレイン電圧が印加された場合には、電圧印加のない図23(A)のバリアの高さすなわちバンドギャップ( $E_g$ )の $1/2$ よりもバリアの高さ( $h$ )は小さい値となる。

#### 【0214】

このとき電子は、図24(A)で示すようにゲート絶縁膜と高純度化された酸化物半導体との界面における、ゲート絶縁膜側のエネルギー的に安定な最低部を移動する。

#### 【0215】

また、図24(B)において、ゲート電極(G1)に負の電位(逆バイアス)が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

#### 【0216】

例えば、薄膜トランジスタのチャネル幅Wが $1 \times 10^4\text{ }\mu\text{m}$ でチャネル長が $3\text{ }\mu\text{m}$ の素子であっても、オフ電流が $10^{-13}\text{ A}$ 以下であり、サブスレッショルドスイッチング値(S値)が $0.1\text{ V/d ec.}$ (ゲート絶縁膜厚 $100\text{ nm}$ )が得られる。

#### 【0217】

このように、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより、薄膜トランジスタの動作を良好なものとすることができます。

#### 【0218】

(実施の形態6)

本実施の形態では、実施の形態1に示したアナログ回路が有する薄膜トランジスタの一例について示す。

#### 【0219】

本実施の形態の薄膜トランジスタ及びその作製方法の一形態を図8を用いて説明する。

#### 【0220】

10

20

30

40

50

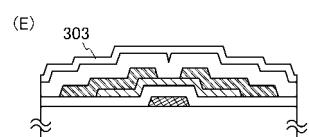

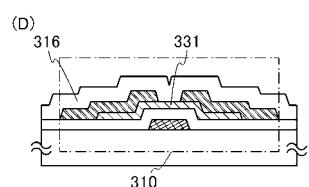

図8(D)に示す薄膜トランジスタ310は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

#### 【0221】

また、薄膜トランジスタ310はシングルゲート構造の薄膜トランジスタを用いて説明したが、必要に応じて、チャネル領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

#### 【0222】

以下、図8(A)乃至(E)を用い、基板300上に薄膜トランジスタ310を作製する工程を説明する。

#### 【0223】

まず、絶縁表面を有する基板300上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層311を形成する。形成されたゲート電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0224】

絶縁表面を有する基板300に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

#### 【0225】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ よりBaOを多く含むガラス基板を用いることが好ましい。

#### 【0226】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。他にも、結晶化ガラスなどを用いることができる。

#### 【0227】

下地膜となる絶縁膜を基板300とゲート電極層311との間に設けてもよい。下地膜は、基板300からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた一又は複数の膜による積層構造により形成することができる。

#### 【0228】

また、ゲート電極層311の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0229】

例えば、ゲート電極層311の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、銅層上にモリブデン層を積層した2層の積層構造、銅層上に窒化チタン層若しくは窒化タンタルを積層した2層の積層構造、窒化チタン層とモリブデン層とを積層した2層の積層構造、又は窒化タングステン層とタングステン層との2層の積層構造とすることが好ましい。3層の積層構造としては、タングステン層または窒化タングステンと、アルミニウムと珪素の合金またはアルミニウムとチタンの合金と、窒化チタンまたはチタン層とを積層した積層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。

#### 【0230】

次いで、ゲート電極層311上にゲート絶縁層302を形成する。

10

20

30

40

50

## 【0231】

ゲート絶縁層302は、プラズマCVD法又はスパッタリング法等を用いて、酸化珪素層、窒化珪素層、酸化窒化珪素層、窒化酸化珪素層、又は酸化アルミニウム層を単層で又は積層して形成することができる。例えば、成膜ガスとして、SiH<sub>4</sub>、酸素及び窒素を用いてプラズマCVD法により酸化窒化珪素層を形成すればよい。ゲート絶縁層302の膜厚は、100nm以上500nm以下とし、積層の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁層と、第1のゲート絶縁層上に膜厚5nm以上300nm以下の第2のゲート絶縁層の積層とする。

## 【0232】

本実施の形態では、ゲート絶縁層302としてプラズマCVD法により膜厚100nm以下の酸化窒化珪素層を形成する。10

## 【0233】

次いで、ゲート絶縁層302上に、膜厚2nm以上200nm以下の酸化物半導体膜330を形成する。

## 【0234】

酸化物半導体膜330は、In-Ga-Zn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Sn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-Ga-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いる。本実施の形態では、酸化物半導体膜330としてIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタ法により成膜する。この段階での断面図が図8(A)に相当する。また、酸化物半導体膜330は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素雰囲気下においてスパッタ法により形成することができる。また、スパッタリング法を用いる場合、酸化珪素(SiO<sub>X</sub>(X>0))を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。20

## 【0235】

酸化物半導体膜をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、mol数比でIn<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1、原子数比でIn:Ga:Zn=1:1:0.5の組成を有するIn、Ga、及びZnを含む金属酸化物ターゲットを用いることができる。また、In、Ga、及びZnを含む金属酸化物ターゲットとして、原子数比でIn:Ga:Zn=1:1:1、またはIn:Ga:Zn=1:1:2の組成を有するターゲットを用いることもできる。金属酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。30

## 【0236】

酸化物半導体膜330を成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。40

## 【0237】

減圧状態に保持された処理室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板300上に酸化物半導体膜330を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例50

えば、水素原子、水（H<sub>2</sub>O）など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0238】

成膜条件の一例としては、基板とターゲットの間の距離を100mm、圧力0.6Pa、直流（DC）電源0.5kW、酸素（酸素流量比率100%）雰囲気下の条件が適用される。なお、パルス直流（DC）電源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜の膜厚は、2nm以上200nm以下、好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。10

#### 【0239】

次いで、酸化物半導体膜330を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0240】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層331を得る（図8（B）参照）。20

#### 【0241】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。30

#### 【0242】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

#### 【0243】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.99999%）以上、（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。40

#### 【0244】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶層または多結晶層となる場合もある。例えば、結晶化率が90%以上、または80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半50

導体層となる場合もある。また、非晶質の酸化物半導体の中に微結晶部（粒径 1 nm 以上 20 nm 以下（代表的には 2 nm 以上 4 nm 以下））が混在する酸化物半導体層となる場合もある。

#### 【 0 2 4 5 】

また、酸化物半導体層の第 1 の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜 330 に行うこともできる。その場合には、第 1 の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

#### 【 0 2 4 6 】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にソース電極及びドレイン電極を積層させた後、ソース電極及びドレイン電極上に保護絶縁膜を形成した後、のいずれで行っても良い。10

#### 【 0 2 4 7 】

また、ゲート絶縁層 302 にコンタクトホールを形成する場合、その工程は酸化物半導体膜 330 に脱水化または脱水素化処理を行う前でも行った後に行ってもよい。

#### 【 0 2 4 8 】

なお、ここでの酸化物半導体膜のエッチングは、ウェットエッチングに限定されずドライエッチングを用いてもよい。

#### 【 0 2 4 9 】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件（エッチング液、エッチング時間、温度等）を適宜調節する。20

#### 【 0 2 5 0 】

次いで、ゲート絶縁層 302、及び酸化物半導体層 331 上に、導電膜を形成する。導電膜をスパッタ法や真空蒸着法で形成すればよい。導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一または複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する 2 層構造、Ti 膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する 3 層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タンクステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、又は複数組み合わせた膜、合金膜、もしくは窒化膜を用いてもよい。30

#### 【 0 2 5 1 】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

#### 【 0 2 5 2 】

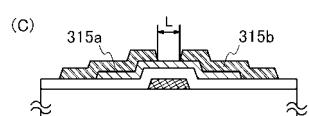

第 3 のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層 315a、ドレイン電極層 315b を形成した後、レジストマスクを除去する（図 8 (C) 参照）。

#### 【 0 2 5 3 】

第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線や KrF レーザ光や ArF レーザ光を用いる。酸化物半導体層 331 上で隣り合うソース電極層 315a の下端部とドレイン電極層 315b の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長 L が決定される。なお、チャネル長 L = 25 nm 未満の露光を行う場合には、数 nm ~ 数 10 nm と極めて波長が短い超紫外線（Extreme UV traviolent）を用いて第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長 L を 10 nm 以上 1000 nm 以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。4050

**【0254】**

なお、導電膜のエッティングの際に、酸化物半導体層331は除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

**【0255】**

本実施の形態では、導電膜としてTi膜を用いて、酸化物半導体層331にはIn-Ga-Zn-O系酸化物半導体を用いて、エッチャントとしてアンモニア過水（アンモニア、水、過酸化水素水の混合液）を用いる。

**【0256】**

なお、第3のフォトリソグラフィ工程では、酸化物半導体層331は一部のみがエッティングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、ソース電極層315a、ドレイン電極層315bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。10

**【0257】**

また、酸化物半導体層331とソース電極層315a及びドレイン電極層315bの間に、酸化物導電層を形成してもよい。酸化物半導体層331とソース電極層315a及びドレイン電極層315bを形成するための金属層は、連続成膜が可能である。酸化物導電層はソース領域及びドレイン領域として機能しうる。

**【0258】**

ソース領域及びドレイン領域として、酸化物導電層を酸化物半導体層とソース電極層及びドレイン電極層との間に設けることで、ソース領域及びドレイン領域の低抵抗化を図ることができ、トランジスタの高速動作をすることができる。20

**【0259】**

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッティング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッティングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッティング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。30

**【0260】**

次いで、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

**【0261】**

プラズマ処理を行った後、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層316を形成する。

**【0262】**

酸化物絶縁層316は、少なくとも1nm以上の膜厚とし、スパッタ法など、酸化物絶縁層316に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。酸化物絶縁層316に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化（N型化）してしまい、寄生チャネルが形成されるおそれがある。よって、酸化物絶縁層316はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。40

**【0263】**

本実施の形態では、酸化物絶縁層316として膜厚200nmの酸化珪素膜をスパッタ法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化珪素膜のスパッタ法による成膜は、希ガス（代表的にはア

ルゴン) 霧囲気下、酸素霧囲気下、または希ガス(代表的にはアルゴン)及び酸素霧囲気下において行うことができる。また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び窒素霧囲気下でスパッタ法により酸化珪素を形成することができる。酸化物半導体層331に接して形成する酸化物絶縁層316は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

#### 【0264】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層316を成膜することが好ましい。酸化物半導体層331及び酸化物絶縁層316に水素、水酸基又は水分が含まれないようにするためである。10

#### 【0265】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層316に含まれる不純物の濃度を低減できる。

#### 【0266】

酸化物絶縁層316を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。20

#### 【0267】

次いで、不活性ガス霧囲気下、または酸素ガス霧囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。例えば、窒素霧囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル領域)が酸化物絶縁層316と接した状態で加熱される。酸化物半導体層331と酸化物絶縁層316とを接した状態で加熱処理を行うと、第1の加熱処理によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を、酸化物絶縁層316より酸化物半導体層331へ供給することができる。よって、酸化物半導体はより高純度化し、電気的にI型(真性)化する。30

#### 【0268】

以上の工程を経ることによって、脱水化または脱水素化により水素、水分、水素化物、水酸化物の濃度が低減され、I型化された酸化物半導体層331を有する薄膜トランジスタ310を形成することができる。(図8(D)参照)。

#### 【0269】

さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。本実施の形態では150で10時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなる薄膜トランジスタを得ることができる。40

#### 【0270】

酸化物絶縁層316上にさらに保護絶縁層303を形成してもよい。例えば、RFスパッタ法を用いて窒化珪素膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜な50

どを用いる。(図8(E)参照)。

【0271】

本実施の形態では、保護絶縁層303として、酸化物絶縁層316まで形成された基板300を100～400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコンターゲットを用いて窒化シリコン膜を成膜する。この場合においても、酸化物絶縁層316と同様に、処理室内の残留水分を除去しつつ保護絶縁層303を成膜することが好ましい。

【0272】

保護絶縁層303上に平坦化のための平坦化絶縁層を設けてもよい。

【0273】

上述した薄膜トランジスタを実施の形態1に示したアナログ回路に適用することによって、安定な電気特性を有し信頼性の高いアナログ回路を提供することができる。

【0274】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0275】

(実施の形態7)

本実施の形態では、実施の形態1に示したアナログ回路が有する薄膜トランジスタの一例について示す。

【0276】

本実施の形態の薄膜トランジスタ及びその作製方法の一形態を、図9を用いて説明する。

【0277】

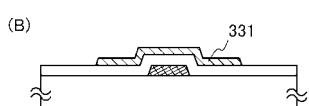

図9(D)に示す薄膜トランジスタ360は、チャネル保護型(チャネルトップ型ともいう)と呼ばれるボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

【0278】

また、薄膜トランジスタ360はシングルゲート構造の薄膜トランジスタを用いて説明したが、必要に応じて、チャネル領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

【0279】

以下、図9(A)乃至(D)を用い、基板320上に薄膜トランジスタ360を作製する工程を説明する。

【0280】

まず、絶縁表面を有する基板320上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層361を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0281】

また、ゲート電極層361は、モリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

【0282】

次いで、ゲート電極層361上にゲート絶縁層322を形成する。

【0283】

本実施の形態では、ゲート絶縁層322としてプラズマCVD法により膜厚100nm以下の酸化窒化珪素層を形成する。

【0284】

次いで、ゲート絶縁層322上に、膜厚2nm以上200nm以下の酸化物半導体膜を形成し、第2のフォトリソグラフィ工程により島状の酸化物半導体層332に加工する。本実施の形態では、酸化物半導体膜としてIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタ法により成膜する。

【0285】

10

20

30

40

50

この場合において、処理室内の残留水分を除去しつつ酸化物半導体膜を成膜することが好ましい。酸化物半導体膜に水素、水酸基又は水分が含まれないようにするためである。

#### 【0286】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水( $H_2O$ )など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0287】

酸化物半導体膜を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。

#### 【0288】

次いで、酸化物半導体層332の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層332に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層332への水や水素の再混入を防ぎ、脱水化または脱水素化された酸化物半導体層332を得る(図9(A)参照)。

#### 【0289】

次いで、 $N_2O$ 、 $N_2$ 、またはArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

#### 【0290】

次いで、ゲート絶縁層322、及び酸化物半導体層332上に、酸化物絶縁層を形成した後、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行って、チャネル保護層として機能する酸化物絶縁層366を形成した後、レジストマスクを除去する。チャネル保護層として酸化物絶縁層366を設けることによって、酸化物半導体層332のチャネル形成領域となる部分に対する、後の工程時におけるエッチング時のプラズマやエッチング剤による膜減りなどのダメージを防ぐことができる。

#### 【0291】

本実施の形態では、酸化物絶縁層366として膜厚200nmの酸化珪素膜をスパッタ法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化珪素膜のスパッタ法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において行うことができる。また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び窒素雰囲気下でスパッタ法により酸化珪素を形成することができる。

#### 【0292】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層366を成膜することが好ましい。酸化物半導体層332及び酸化物絶縁層366に水素、水酸基又は水分が含まれないようにするためである。

#### 【0293】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水( $H_2O$ )など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層366に含まれる不純物の濃度を低減できる。

10

20

30

40

50

**【 0 2 9 4 】**

酸化物絶縁層 3 6 6 を成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度 ppm 程度、濃度 ppb 程度まで除去された高純度ガスが好ましい。

**【 0 2 9 5 】**

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第 2 の加熱処理（好ましくは 200 以上 400 以下、例えば 250 以上 350 以下）を行ってもよい。例えば、窒素雰囲気下で 250 、 1 時間の第 2 の加熱処理を行う。第 2 の加熱処理を行うと、酸化物半導体層の一部（チャネル領域）が酸化物絶縁層 3 6 6 と接した状態で加熱される。

**【 0 2 9 6 】**

次いで、ゲート絶縁層 3 2 2 、酸化物半導体層 3 3 2 、及び酸化物絶縁層 3 6 6 上に、導電膜を形成した後、第 4 のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってソース電極層 3 6 5 a 、ドレイン電極層 3 6 5 b を形成した後、レジストマスクを除去する（図 9 ( C ) 参照）。

**【 0 2 9 7 】**

ソース電極層 3 6 5 a 、ドレイン電極層 3 6 5 b の材料としては、 Al 、 Cr 、 Cu 、 Ta 、 Ti 、 Mo 、 W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、金属導電膜は、単層構造でも、 2 層以上の積層構造としてもよい。第 2 の加熱処理は、ソース電極層 3 6 5 a 、ドレイン電極層 3 6 5 b 形成以降の工程で行っても良い。

**【 0 2 9 8 】**

以上の工程を経ることによって、脱水化または脱水素化により水素、水分、水素化物、水酸化物の濃度が低減され、 I 型化された酸化物半導体層 3 3 2 を有する薄膜トランジスタ 3 6 0 が形成される。

**【 0 2 9 9 】**

さらに大気中、 100 以上 200 以下、 1 時間以上 30 時間以下の加熱処理を行ってもよい。本実施の形態では 150 で 10 時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、 100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなる薄膜トランジスタを得ることができる。

**【 0 3 0 0 】**

また、ソース電極層 3 6 5 a 、ドレイン電極層 3 6 5 b 、酸化物絶縁層 3 6 6 上に保護絶縁層 3 2 3 を形成してもよい。本実施の形態では、保護絶縁層 3 2 3 を、窒化珪素膜を用いて形成する（図 9 ( D ) 参照）。

**【 0 3 0 1 】**

なお、ソース電極層 3 6 5 a 、ドレイン電極層 3 6 5 b 、酸化物絶縁層 3 6 6 上にさらに酸化物絶縁層を形成し、該酸化物絶縁層上に保護絶縁層 3 2 3 を積層してもよい。

**【 0 3 0 2 】**

上述した薄膜トランジスタを実施の形態 1 に示したアナログ回路に適用することによって、安定な電気特性を有し信頼性の高いアナログ回路を提供することができる。

**【 0 3 0 3 】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【 0 3 0 4 】****( 実施の形態 8 )**

本実施の形態では、実施の形態 1 に示したアナログ回路が有する薄膜トランジスタの一例について示す。

**【 0 3 0 5 】**

本実施の形態の薄膜トランジスタ及びその作製方法の一形態を、図 10 を用いて説明する

10

20

30

40

50

。

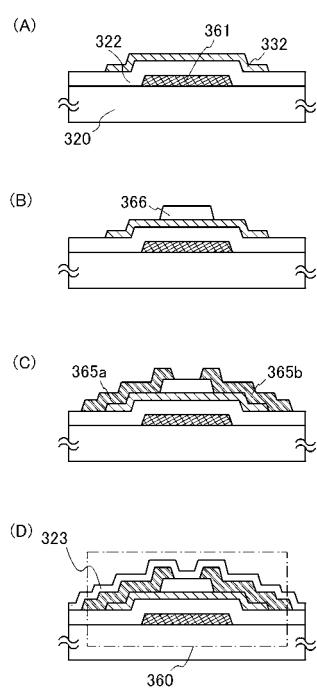

### 【0306】

また、図10(D)に示す薄膜トランジスタ350はシングルゲート構造の薄膜トランジスタを用いて説明するが、必要に応じて、チャネル領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

### 【0307】

以下、図10(A)乃至(D)を用い、基板340上に薄膜トランジスタ350を作製する工程を説明する。

### 【0308】

まず、絶縁表面を有する基板340上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層351を形成する。本実施の形態では、ゲート電極層351として、膜厚150nmのタンゲステン膜を、スパッタ法を用いて形成する。10

### 【0309】

次いで、ゲート電極層351上にゲート絶縁層342を形成する。本実施の形態では、ゲート絶縁層342としてプラズマCVD法により膜厚100nm以下の酸化窒化珪素層を形成する。

### 【0310】

次いで、ゲート絶縁層342に、導電膜を形成し、第2のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層355a、ドレイン電極層355bを形成した後、レジストマスクを除去する(図10(A)参照)。20

### 【0311】

次に、酸化物半導体膜345を形成する(図10(B)参照)。本実施の形態では、酸化物半導体膜345としてIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタ法により成膜する。酸化物半導体膜345を第3のフォトリソグラフィ工程により島状の酸化物半導体層346に加工する。

### 【0312】

この場合において、処理室内の残留水分を除去しつつ酸化物半導体膜345を成膜することが好ましい。酸化物半導体膜345に水素、水酸基又は水分が含まれないようにするためにある。

30

### 【0313】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物半導体膜345に含まれる不純物の濃度を低減できる。

### 【0314】

酸化物半導体膜345を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。

40

### 【0315】

次いで、酸化物半導体層346の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層346に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層346への水や水素の再混入を防ぎ、脱水化または脱水素化された酸化物半導体層346を得る(図10(C)参照)。

### 【0316】

また、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板

50

を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すG R T Aを行ってもよい。G R T Aを用いると短時間での高温加熱処理が可能となる。

### 【0317】

酸化物半導体層346に接する保護絶縁膜となる酸化物絶縁層356を形成する。

### 【0318】

酸化物絶縁層356は、少なくとも1nm以上の膜厚とし、スパッタ法など、酸化物絶縁層356に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。酸化物絶縁層356に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜きが生じ酸化物半導体層のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成されるおそれがある。よって、酸化物絶縁層356はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。10

### 【0319】

本実施の形態では、酸化物絶縁層356として膜厚200nmの酸化珪素膜をスパッタ法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化珪素膜のスパッタ法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において行うことができる。また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び窒素雰囲気下でスパッタ法により酸化珪素を形成することができる。酸化物半導体層346に接して形成する酸化物絶縁層356は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。20

### 【0320】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層356を成膜することが好ましい。酸化物半導体層346及び酸化物絶縁層356に水素、水酸基又は水分が含まれないようにするためである。

### 【0321】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層356に含まれる不純物の濃度を低減できる。30

### 【0322】

酸化物絶縁層356を成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。40

### 【0323】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層が酸化物絶縁層356と接した状態で加熱される。

### 【0324】

以上の工程を経ることによって、脱水化または脱水素化により水素、水分、水素化物、水酸化物の濃度が低減され、I型化された酸化物半導体層346を有する薄膜トランジスタ350が形成される。

### 【0325】

10

20

30

40

50

さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってよい。本実施の形態では150で10時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなる薄膜トランジスタを得ることができる。

#### 【0326】

酸化物絶縁層356上にさらに保護絶縁層を形成してもよい。例えば、RFスパッタ法を用いて窒化珪素膜を形成する。本実施の形態では、保護絶縁層として保護絶縁層343を、窒化珪素膜を用いて形成する(図10(D)参照)。10

#### 【0327】

保護絶縁層343上に平坦化のための平坦化絶縁層を設けてよい。

#### 【0328】

上述した薄膜トランジスタを実施の形態1に示したアナログ回路に適用することによって、安定な電気特性を有し信頼性の高いアナログ回路を提供することができる。

#### 【0329】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【0330】

(実施の形態9)20

本実施の形態では、実施の形態1に示したアナログ回路が有する薄膜トランジスタの一例について示す。

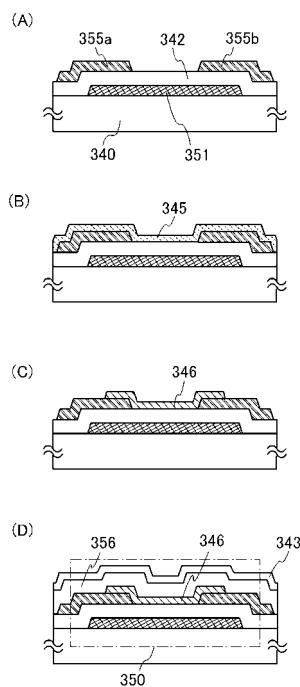

#### 【0331】

本実施の形態では、薄膜トランジスタの作製工程の一部が実施の形態6と異なる例を図11に示す。図11は、図8と工程が一部異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。

#### 【0332】

実施の形態6に従って、基板370上にゲート電極層381を形成し、第1のゲート絶縁層372a、第2のゲート絶縁層372bを積層する。本実施の形態では、ゲート絶縁層を2層構造とし、第1のゲート絶縁層372aに窒化物絶縁層を、第2のゲート絶縁層372bに酸化物絶縁層を用いる。30

#### 【0333】

酸化絶縁層としては、酸化シリコン層、酸化窒化シリコン層、または酸化アルミニウム層、又は酸化窒化アルミニウム層などを用いることができる。また、窒化絶縁層としては、窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、又は窒化酸化アルミニウム層などを用いることができる。

#### 【0334】

本実施の形態では、ゲート電極層381側から窒化シリコン層と酸化シリコン層とを積層した構造とする。第1のゲート絶縁層372aとしてスパッタリング法により膜厚50nm以上200nm以下(本実施の形態では50nm)の窒化シリコン層( $\text{SiN}_y$  ( $y > 0$ ))を形成し、第1のゲート絶縁層372a上に第2のゲート絶縁層372bとして膜厚5nm以上300nm以下(本実施の形態では100nm)の酸化シリコン層( $\text{SiO}_x$  ( $x > 0$ ))を積層して、膜厚150nmのゲート絶縁層とする。40

#### 【0335】

次に、酸化物半導体膜の形成を行い、酸化物半導体膜をフォトリソグラフィ工程により島状の酸化物半導体層382に加工する。本実施の形態では、酸化物半導体膜としてIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタ法により成膜する。

#### 【0336】

この場合において、処理室内の残留水分を除去しつつ酸化物半導体膜を成膜することが好み。酸化物半導体膜に水素、水酸基又は水分が含まれないようにするためである。50

## 【0337】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであつてもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水( $H_2O$ )など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

## 【0338】

酸化物半導体膜を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスが好ましい。10

## 【0339】

次いで、酸化物半導体層382の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上750以下、好ましくは425以上とする。なお、425以上であれば加熱処理時間は1時間以下でよいが、425未満であれば加熱処理時間は、1時間よりも長時間行うこととする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。その後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア(露点が-40以下、好ましくは-60以下)を導入して冷却を行う。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。20

## 【0340】

なお、加熱処理装置は電気炉に限られず、例えば、G R T A (Gas Rapid Thermal Anneal)装置、L R T A (Lamp Rapid Thermal Anneal)装置等のRTA (Rapid Thermal Anneal)装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。また、L R T A 装置、ランプだけでなく、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。G R T A とは高温のガスを用いて加熱処理を行う方法である。ガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性ガスが用いられる。RTA法を用いて、600~750で数分間加熱処理を行ってもよい。30

## 【0341】

また、脱水化または脱水素化を行う第1の加熱処理後に200以上400以下、好ましくは200以上300以下の温度で酸素ガスまたはN<sub>2</sub>Oガス雰囲気下での加熱処理を行ってもよい。40

## 【0342】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

## 【0343】

以上の工程を経ることによって酸化物半導体中の不純物を低減させることにより、全体がI型化又は実質的にI型化された酸化物半導体層382を得ることができる。

## 【0344】

次いで、酸化物半導体層382上に導電膜を形成し、フォトリソグラフィ工程によりレジストマスクを形成し、導電膜を選択的にエッチングしてソース電極層385a、ドレイン50

電極層 385b を形成し、スパッタ法で酸化物絶縁層 386 を形成する。

【0345】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層 386 を成膜することが好ましい。酸化物半導体層 382 及び酸化物絶縁層 386 に水素、水酸基又は水分が含まれないようにするためである。

【0346】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであつてもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水 ( $H_2O$ ) など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層 386 に含まれる不純物の濃度を低減できる。10

【0347】

酸化物絶縁層 386 を、成膜する際に用いるスパッタガスとしては水素、水、水酸基又は水素化物などの不純物が、濃度 ppm 程度、濃度 ppb 程度まで除去された高純度ガスが好ましい。

【0348】

以上の工程で、薄膜トランジスタ 380 を形成することができる。

【0349】

次いで、薄膜トランジスタの電気的特性のばらつきを軽減するため、不活性ガス雰囲気下、または窒素ガス雰囲気下で加熱処理（好ましくは 150 以上 350 未満）を行ってもよい。例えば、窒素雰囲気下で 250 、1 時間の加熱処理を行う。20

【0350】

また、大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行ってもよい。本実施の形態では 150 で 10 時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなる薄膜トランジスタを得ることができる。30

【0351】

酸化物絶縁層 386 上に保護絶縁層 373 を形成する。本実施の形態では、保護絶縁層 373 として、スパッタリング法を用いて膜厚 100 nm の窒化珪素膜を形成する。

【0352】

窒化物絶縁層からなる保護絶縁層 373 及び第 1 のゲート絶縁層 372a は、水分や、水素や、水素化物、水酸化物などの不純物を含まず、これらが外部から侵入することをプロックする効果がある。

【0353】

従って、保護絶縁層 373 形成後の製造プロセスにおいて、外部からの水分などの不純物の侵入を防ぐことができる。また、半導体装置、例えば液晶表示装置としてデバイスが完成した後にも長期的に、外部からの水分などの不純物の侵入を防ぐことができデバイスの長期信頼性を向上することができる。40

【0354】

また、窒化物絶縁層からなる保護絶縁層 373 と、第 1 のゲート絶縁層 372a との間に設けられる絶縁層を除去し、保護絶縁層 373 と、第 1 のゲート絶縁層 372a とが接する構造としてもよい。

【0355】

保護絶縁層 373 と、第 1 のゲート絶縁層 372a とが接する構造とすることで、酸化物半導体層中の水分や、水素や、水素化物、水酸化物などの不純物を究極にまで低減し、かつ該不純物の再混入を防止し、酸化物半導体層中の不純物濃度を低く維持することができ50

る。

**【 0 3 5 6 】**

保護絶縁層 3 7 3 上に平坦化のための平坦化絶縁層を設けてもよい。

**【 0 3 5 7 】**

上述した薄膜トランジスタを実施の形態 1 に示したアナログ回路に適用することによって、安定な電気特性を有し信頼性の高いアナログ回路を提供することができる。

**【 0 3 5 8 】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【 0 3 5 9 】**

( 実施の形態 1 0 )

10

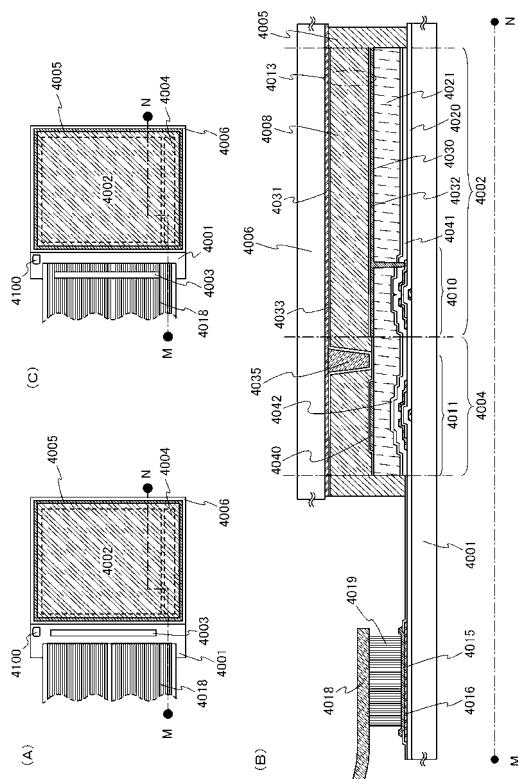

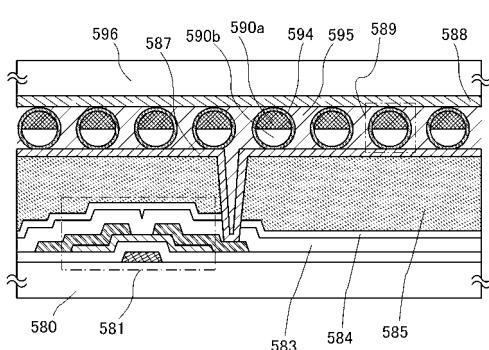

本実施の形態では、実施の形態 1 に示したアナログ回路を有する半導体装置の一例について説明する。具体的には、実施の形態 1 に示した光検出装置を有する液晶表示パネルの外観及び断面について、図 1 2 を用いて説明する。図 1 2 は、薄膜トランジスタ 4 0 1 0 、薄膜トランジスタ 4 0 1 1 、及び液晶素子 4 0 1 3 を、第 1 の基板 4 0 0 1 と第 2 の基板 4 0 0 6 との間にシール材 4 0 0 5 によって封止したパネル上面図であり、図 1 2 ( B ) は、図 1 2 ( A ) または図 1 2 ( C ) の M - N における断面図に相当する。

**【 0 3 6 0 】**

第 1 の基板 4 0 0 1 上に設けられた画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 とを囲むようにして、シール材 4 0 0 5 が設けられている。また、画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 の上に第 2 の基板 4 0 0 6 が設けられている。よって画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 とは、第 1 の基板 4 0 0 1 とシール材 4 0 0 5 と第 2 の基板 4 0 0 6 とによって、液晶層 4 0 0 8 と共に封止されている。また第 1 の基板 4 0 0 1 上のシール材 4 0 0 5 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路 4 0 0 3 が実装されている。

20

**【 0 3 6 1 】**

また、第 1 の基板 4 0 0 1 上のシール材 4 0 0 5 によって囲まれている領域とは異なる領域に、実施の形態 1 で示した光検出装置 4 1 0 0 が設けられている。光検出装置 4 1 0 0 は、第 1 の基板 4 0 0 1 上に画素部と同時に形成してもよいし、別途基板上に作製して第 1 の基板 4 0 0 1 上に実装してもよい。なお、第 1 の基板 4 0 0 1 に透光性基板を用いる場合は、基板側から入射した光を検出する構成として光検出装置 4 1 0 0 を設けることができるが、第 1 の基板 4 0 0 1 に可視光を透過しない基板を用いる場合は、光検出装置の受光部を、基板による遮光の影響を受けない方向となるように配置する必要がある。

30

**【 0 3 6 2 】**

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG 法、ワイヤボンディング法、或いは TAB 法などを用いることができる。図 1 2 ( A ) は、 COG 方法により信号線駆動回路 4 0 0 3 を実装する例であり、図 1 2 ( C ) は、 TAB 方法により信号線駆動回路 4 0 0 3 を実装する例である。

**【 0 3 6 3 】**

また、第 1 の基板 4 0 0 1 上に設けられた画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 は、薄膜トランジスタを複数有しており、図 1 2 ( B ) では、画素部 4 0 0 2 に含まれる薄膜トランジスタ 4 0 1 0 と、走査線駆動回路 4 0 0 4 に含まれる薄膜トランジスタ 4 0 1 1 とを例示している。薄膜トランジスタ 4 0 1 0 、 4 0 1 1 上には絶縁層 4 0 4 1 、保護絶縁層 4 0 4 2 、絶縁層 4 0 2 0 、絶縁層 4 0 2 1 が設けられている。

40

**【 0 3 6 4 】**

薄膜トランジスタ 4 0 1 0 、 4 0 1 1 は、実施の形態 3 乃至実施の形態 9 に示した薄膜トランジスタのいずれか一を適宜用いることができ、同様な工程及び材料で形成することができる。薄膜トランジスタ 4 0 1 0 、 4 0 1 1 の酸化物半導体層は水素や水が低減されている。従って、薄膜トランジスタ 4 0 1 0 、 4 0 1 1 は信頼性の高い薄膜トランジスタである。本実施の形態において、薄膜トランジスタ 4 0 1 0 、 4 0 1 1 は n チャネル型薄膜トランジスタである。

50

## 【0365】

絶縁層4021上において、駆動回路用の薄膜トランジスタ4011の酸化物半導体層のチャネル領域と重なる位置に導電層4040が設けられている。導電層4040を酸化物半導体層のチャネル領域と重なる位置に設けることによって、BT試験前後における薄膜トランジスタ4011のしきい値電圧の変化量を低減することができる。また、導電層4040の電位は、薄膜トランジスタ4011のゲート電極層と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層4040の電位は、GND、0V、或いはフローティング状態であってもよい。なお、当該導電層4040はなくてもよい。

## 【0366】

10

また、液晶素子4013が有する画素電極層4030は、薄膜トランジスタ4010のソース電極層又はドレイン電極層と電気的に接続されている。そして液晶素子4013の対向電極層4031は第2の基板4006上に形成されている。画素電極層4030と対向電極層4031と液晶層4008とが重なっている部分が、液晶素子4013に相当する。なお、画素電極層4030、対向電極層4031はそれぞれ配向膜として機能する絶縁層4032、絶縁層4033が設けられ、絶縁層4032、4033を介して液晶層4008を挟持している。

## 【0367】

20

なお、第1の基板4001、第2の基板4006としては、透光性基板を用いることができる、ガラス、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルム、またはアクリル樹脂フィルムを用いることができる。

## 【0368】

30

また、スペーサ4035は絶縁膜を選択的にエッキングすることで得られる柱状のスペーサであり、画素電極層4030と対向電極層4031との間の距離(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていても良い。また、対向電極層4031は、薄膜トランジスタ4010と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極層4031と共に電位線とを電気的に接続することができる。なお、導電性粒子はシール材4005に含有させる。

## 【0369】

40

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために5重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層4008に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1ms以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることができるとなる。特に、酸化物半導体層を用いる薄膜トランジスタは、静電気の影響により薄膜トランジスタの電気的な特性が著しく変動して設計範囲を逸脱する恐れがある。よって酸化物半導体層を用いる薄膜トランジスタを有する液晶表示装置にブルー相の液晶材料を用いることはより効果的である。

## 【0370】

なお、透過型液晶表示装置の他に、半透過型液晶表示装置でも適用できる。

## 【0371】

50

また、液晶表示装置では、基板の外側(視認側)に偏光板を設け、内側に着色層、表示素子に用いる電極層という順に設ける例を示すが、偏光板は基板の内側に設けてもよい。ま

た、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、表示部以外にブラックマトリクスとして機能する遮光膜を設けてもよい。

### 【0372】

薄膜トランジスタ4011、4010上には、酸化物半導体層に接して絶縁層4041が形成されている。絶縁層4041は他の実施の形態で示した酸化物絶縁層と同様な材料及び方法で形成すればよい。ここでは、絶縁層4041として、スパッタリング法により酸化シリコン層を形成する。また、絶縁層4041上に接して保護絶縁層4042を形成する。また、保護絶縁層4042は他の実施の形態で示した保護絶縁層と同様に形成すればよく、例えば窒化シリコン膜を用いることができる。また、保護絶縁層4042上に薄膜トランジスタの表面凹凸を低減するための平坦化膜として、絶縁層4021が形成されている。10

### 【0373】

また、平坦化膜として機能する絶縁層4021としては、ポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層4021を形成してもよい。

### 【0374】

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタリング法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。絶縁層4021の焼成工程と半導体層のアニールを兼ねることで効率よく半導体装置を作製することが可能となる。20

### 【0375】

画素電極層4030、対向電極層4031は、インジウム錫酸化物(ITO: Indium Tin Oxide)、インジウム亜鉛酸化物(IZO: Indium Zinc Oxide)、酸化インジウムに酸化珪素(SiO<sub>x</sub>(X>0))を混合した導電材料、有機インジウム、有機スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、などの透光性を有する導電性材料を用いることができる。または反射型の液晶表示装置において、透光性を有する必要がない、または反射性を有する必要がある場合は、タンゲステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。30

### 【0376】

また、画素電極層4030、対向電極層4031として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。40

### 【0377】

導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

### 【0378】

また、別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部50

4002に与えられる各種信号及び電位は、FPC4018から供給されている。

【0379】

接続端子電極4015が、液晶素子4013が有する画素電極層4030と同じ導電膜から形成され、端子電極4016は、薄膜トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

【0380】

接続端子電極4015は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

【0381】

また、図12においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているがこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。10

【0382】

また、ブラックマトリクス(遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などは適宜設ける。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

【0383】

アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。20

【0384】

液晶表示装置の動画表示において、液晶分子自体の応答が遅いため、残像が生じる、または動画のぼけが生じるという問題がある。液晶表示装置の動画特性を改善するため、全面黒表示を1フレームおきに行う、所謂、黒挿入と呼ばれる駆動技術がある。

【0385】

また、垂直同期周期数を1.5倍、好ましくは2倍以上にすることで動画特性を改善する、所謂、倍速駆動と呼ばれる駆動技術もある。30

【0386】

また、液晶表示装置の動画特性を改善するため、バックライトとして複数のLED(発光ダイオード)光源または複数のEL光源などを用いて面光源を構成し、面光源を構成している各光源を独立して1フレーム期間内で間欠点灯駆動する駆動技術もある。面光源として、3種類以上のLEDを用いてもよいし、白色発光のLEDを用いてもよい。独立して複数のLEDを制御できるため、液晶層の光学変調の切り替えタイミングに合わせてLEDの発光タイミングを同期させることもできる。この駆動技術は、LEDを部分的に消灯することができるため、特に一画面を占める黒い表示領域の割合が多い映像表示の場合は、消費電力の低減効果が図れる。

【0387】

これらの駆動技術を組み合わせることによって、液晶表示装置の動画特性などの表示特性を従来よりも改善することができる。

【0388】

また、薄膜トランジスタは静電気などにより破壊されやすいため、さらに画素部または駆動回路と同一基板上に保護回路を設けることが好ましい。保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することが好ましい。例えば、保護回路は画素部と、走査線入力端子及び信号線入力端子との間に配設されている。本実施の形態では複数の保護回路を配設して、走査線、信号線及び容量バス線に静電気等によりサーボ電圧が印加され、画素トランジスタなどが破壊されないように構成されている。そのため、保護回路にはサーボ電圧が印加されたときに、共通配線に電荷を逃がすように構成する。また、保護回路4050

は、走査線及び共通配線の間に並列に配置された非線形素子によって構成されている。非線形素子は、ダイオードのような二端子素子又はトランジスタのような三端子素子で構成される。例えば、画素部の薄膜トランジスタと同じ工程で形成することも可能であり、例えばゲート端子とドレイン端子を接続することによりダイオードと同様の特性を持たせることができる。

#### 【0389】

また、液晶表示モジュールには、TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、FFS (Fringe Field Switching) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。10

#### 【0390】

このように、本明細書に開示される半導体装置としては、特に限定されず、TN液晶、OCB液晶、STN液晶、VA液晶、ECB型液晶、GH液晶、高分子分散型液晶、ディスコティック液晶などを用いることができるが、中でもノーマリーブラック型の液晶パネル、例えば垂直配向(VA)モードを採用した透過型の液晶表示装置とすることが好ましい。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASVモードなどを用いることができる。20

#### 【0391】

また、VA型の液晶表示装置にも適用することができる。VA型の液晶表示装置とは、液晶表示パネルの液晶分子の配列を制御する方式の一種である。VA型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。また、画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されているマルチドメイン化あるいはマルチドメイン設計といわれる方法を用いることができる。

#### 【0392】

光検出装置4100により液晶表示装置周辺の照度を検出することで、バックライトの発光輝度を調節して視認性を高めるとともに、省電力化が可能となる。30

#### 【0393】

また、画素部4002内に実施の形態1で示した光検出装置を設け、光学式のタッチセンターとして用いることもできる。

#### 【0394】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【0395】

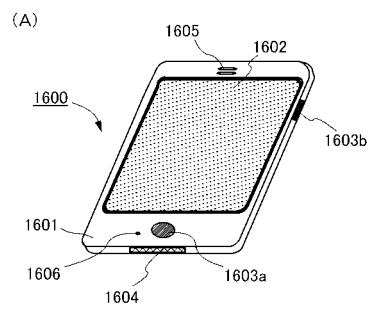

##### (実施の形態11)

本実施の形態では、アクティブマトリクス型の発光表示装置の一例を示す。なお、具体的には、エレクトロルミネッセンスを利用する発光素子を有する発光表示装置の一例について説明する。40

#### 【0396】