## (12)发明专利

(10)授权公告号 CN 102549747 B

(45)授权公告日 2019.03.22

(21)申请号 201080042743.5

(72)发明人 亚历山大·H·欧文斯

(22)申请日 2010.10.15

(74)专利代理机构 北京律盟知识产权代理有限公司 11287

(65)同一申请的已公布的文献号

申请公布号 CN 102549747 A

代理人 沈锦华

(43)申请公布日 2012.07.04

(51)Int.Cl.

(30)优先权数据

12/589,027 2009.10.16 US

H01L 27/092(2006.01)

(85)PCT国际申请进入国家阶段日

2012.03.26

H01L 21/8238(2006.01)

(86)PCT国际申请的申请数据

PCT/US2010/052816 2010.10.15

H01L 29/78(2006.01)

(87)PCT国际申请的公布数据

W02011/047244 EN 2011.04.21

H01L 21/336(2006.01)

(73)专利权人 国家半导体公司

(56)对比文件

地址 美国加利福尼亚州

CN 1667828 A, 2005.09.14,

CN 1667828 A, 2005.09.14,

US 2004/0256700 A1, 2004.12.23,

审查员 曹毓涵

(54)发明名称

权利要求书2页 说明书8页 附图8页

使用结合选择性外延生长的混合定向技术

(HOT)提高迁移率的方法及相关设备

(57)摘要

本发明涉及一种半导体设备，其包括第一衬底(102、202)及第二衬底(106、206)，所述第二衬底位于所述第一衬底的第一部分上且通过掩埋层(104、204)与所述第一衬底分隔。所述半导体设备还包括外延生长层(108、220)，所述外延生长层位于所述第一衬底的第二部分上且与所述第二衬底隔离。所述半导体设备进一步包括至少部分地形成在所述第二衬底中的第一晶体管(116)及至少部分地形成在所述外延生长层中或上的第二晶体管(128)。所述第二衬底及所述外延生长层具有带有不同的电子及空穴迁移率的体性质。所述晶体管中的至少一者经配置以接收至少约5V的一个或一个以上信号。所述第一衬底可具有第一结晶定向，且所述第二衬底可具有第二结晶定向。

B

CN 102549747

1. 一种半导体设备, 其包含:

第一衬底;

第二衬底, 其位于所述第一衬底的第一部分上且通过掩埋层与所述第一衬底分隔;

第一晶体管, 其至少部分地形成在所述第二衬底中;

外延生长层, 其位于所述第一衬底的第二部分上且与所述第二衬底隔离;

罩盖, 其位于所述外延生长层上, 但其中所述第二衬底上没有任何罩盖; 及第二晶体管, 其至少部分地在所述罩盖中及在所述外延生长层上;

其中所述第二衬底及所述外延生长层具有带有不同的电子及空穴迁移率的体性质; 且其中所述晶体管中的至少一者经配置以接收至少约5V的一个或一个以上信号。

2. 根据权利要求1所述的半导体设备, 其中:

所述第一晶体管包含p沟道金属氧化物半导体PMOS晶体管;

所述第二晶体管包括n沟道金属氧化物半导体NMOS晶体管。

3. 根据权利要求1所述的半导体设备, 其中:

所述第一衬底具有第一结晶定向; 且

所述第二衬底具有第二结晶定向。

4. 根据权利要求3所述的半导体设备, 其中所述外延生长层具有所述第一结晶定向。

5. 根据权利要求1所述的半导体设备, 其中所述第一衬底和所述罩盖包含共用半导体材料。

6. 根据权利要求3所述的半导体设备, 其中:

所述第一衬底包含具有(100)结晶定向的p型硅;

所述第二衬底包含具有(110)结晶定向的n型硅; 且

所述罩盖包含p型硅。

7. 根据权利要求1所述的半导体设备, 其中所述外延生长层包含硅锗。

8. 根据权利要求7所述的半导体设备, 其中所述硅锗具有约15%的锗浓度。

9. 一种设备, 其包含:

衬底结构, 其包含:

第一衬底;

第二衬底, 其位于所述第一衬底的第一部分上且通过掩埋层与所述第一衬底分隔;

外延生长层, 其位于所述第一衬底的第二部分上且与所述第二衬底隔离, 其中所述第二衬底具有高于所述外延生长层的空穴迁移率, 其中所述外延生长层具有高于所述第二衬底的电子迁移率, 且其中所述空穴及电子迁移率为体性质; 及

罩盖, 其位于所述外延生长层上, 但其中所述第二衬底上没有任何罩盖;

及

第一及第二晶体管, 所述第一晶体管至少部分地形成在所述第二衬底中, 所述第二晶体管至少部分地形成在所述罩盖中及在所述外延生长层上, 所述晶体管中的至少一者经配置以接收至少约5V的一个或一个以上信号。

10. 根据权利要求9所述的设备, 其中:

所述第一晶体管包含p沟道金属氧化物半导体PMOS晶体管; 且

所述第二晶体管包含n沟道金属氧化物半导体NMOS晶体管。

11. 根据权利要求9所述的设备,其中:

所述第一衬底具有第一结晶定向;且

所述第二衬底具有第二结晶定向。

12. 根据权利要求11所述的设备,其中所述外延生长层具有所述第一结晶定向。

13. 根据权利要求11所述的设备,其中:

所述第一衬底包含具有(100)结晶定向的p型硅;

所述第二衬底包含具有(110)结晶定向的n型硅;且

所述罩盖包含p型硅。

14. 根据权利要求9所述的设备,其中所述外延生长层包含硅锗。

15. 一种方法,其包含:

获得衬底结构,所述衬底结构包含:

第一衬底;

第二衬底,其位于所述第一衬底的第一部分上且通过掩埋层与所述第一衬底分隔;及

外延生长层,其位于所述第一衬底的第二部分上且与所述第二衬底隔离,其中所述第二衬底具有高于所述外延生长层的空穴迁移率,其中所述外延生长层具有高于所述第二衬底的电子迁移率,且其中所述空穴及电子迁移率为体性质;及

罩盖,其位于所述外延生长层上,但其中所述第二衬底上没有任何罩盖;

及

形成第一及第二晶体管,所述第一晶体管至少部分地形成在所述第二衬底中,所述第二晶体管至少部分地形成在所述罩盖中及在所述外延生长层上,所述晶体管中的至少一者经配置以接收至少约5V的一个或一个以上信号。

16. 根据权利要求15所述的方法,其中获得所述衬底结构包含:

移除第二衬底材料的一部分;

在所述第二衬底的一侧上形成间隔物;及

在移除所述第二衬底材料的区域中形成所述外延生长层。

17. 根据权利要求16所述的方法,其中获得所述衬底结构进一步包含:

形成沟槽以隔离所述第二衬底与所述外延生长层。

18. 根据权利要求15所述的方法,其中:

所述第一衬底具有第一结晶定向;且

所述第二衬底具有第二结晶定向。

19. 根据权利要求18所述的方法,其中所述外延生长层具有所述第一结晶定向。

20. 根据权利要求18所述的方法,其中:

所述第一衬底包含具有(100)结晶定向的p型硅;

所述第二衬底包含具有(110)结晶定向的n型硅;

所述外延生长层包含硅锗;且

所述罩盖包含p型硅。

## 使用结合选择性外延生长的混合定向技术 (HOT) 提高迁移率的方法及相关设备

### 技术领域

[0001] 本发明大体上针对集成电路。更特定来说，本发明针对使用结合选择性外延生长的混合定向技术 (HOT) 来提高迁移率的方法及相关设备。

### 背景技术

[0002] 互补型金属氧化物半导体 (CMOS) 电路通常形成在具有 (100) 结晶定向的硅衬底上。混合定向技术 (HOT) 使用单个衬底上的不同的结晶定向。举例来说，混合定向技术可将 (100) 结晶定向衬底与在相同的半导体晶片上的 (110) 结晶定向衬底混合。此通常经进行以帮助提高半导体装置内的空穴及电子迁移率。

### 发明内容

### 附图说明

[0003] 为了对本发明及其特征的更完整的理解，现在参考结合附图进行的以下描述，在附图中：

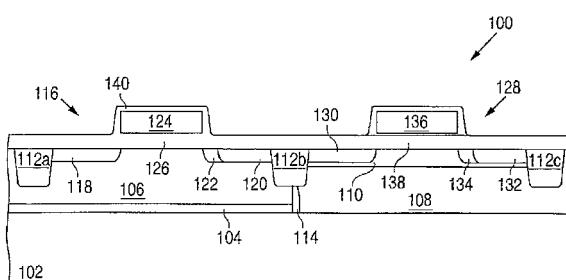

[0004] 图1说明根据本发明的使用结合选择性外延生长的混合定向技术 (HOT) 的实例性集成电路装置；

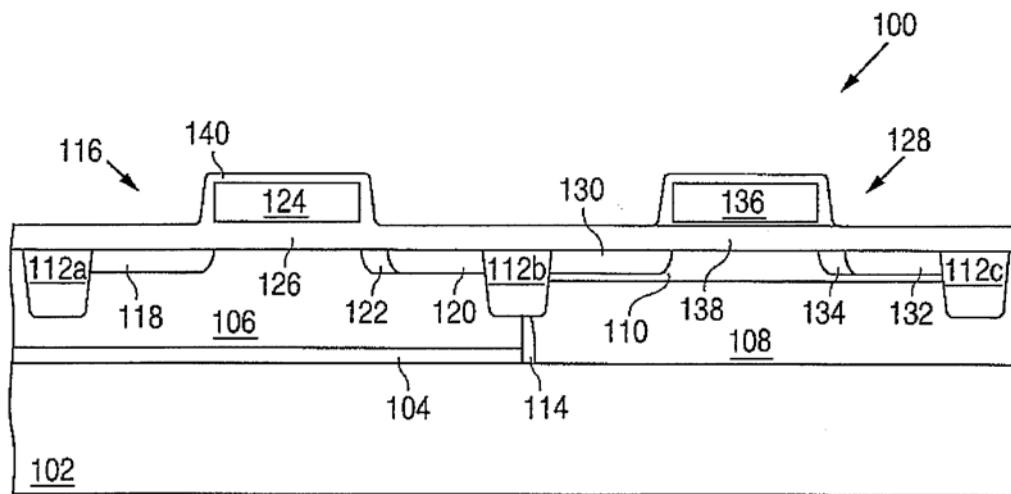

[0005] 图2A至2K说明根据本发明的用于形成使用结合选择性外延生长的HOT的集成电路装置的实例性技术；

[0006] 图3A至3G说明根据本发明的关于集成电路装置中的缺陷的实例性细节；

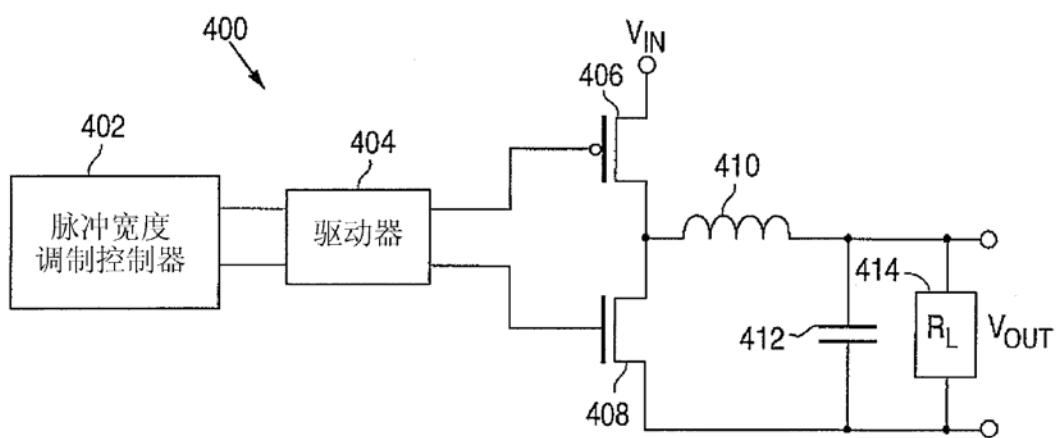

[0007] 图4说明根据本发明的具有使用结合选择性外延生长的HOT而形成的晶体管装置的实例性电路；以及

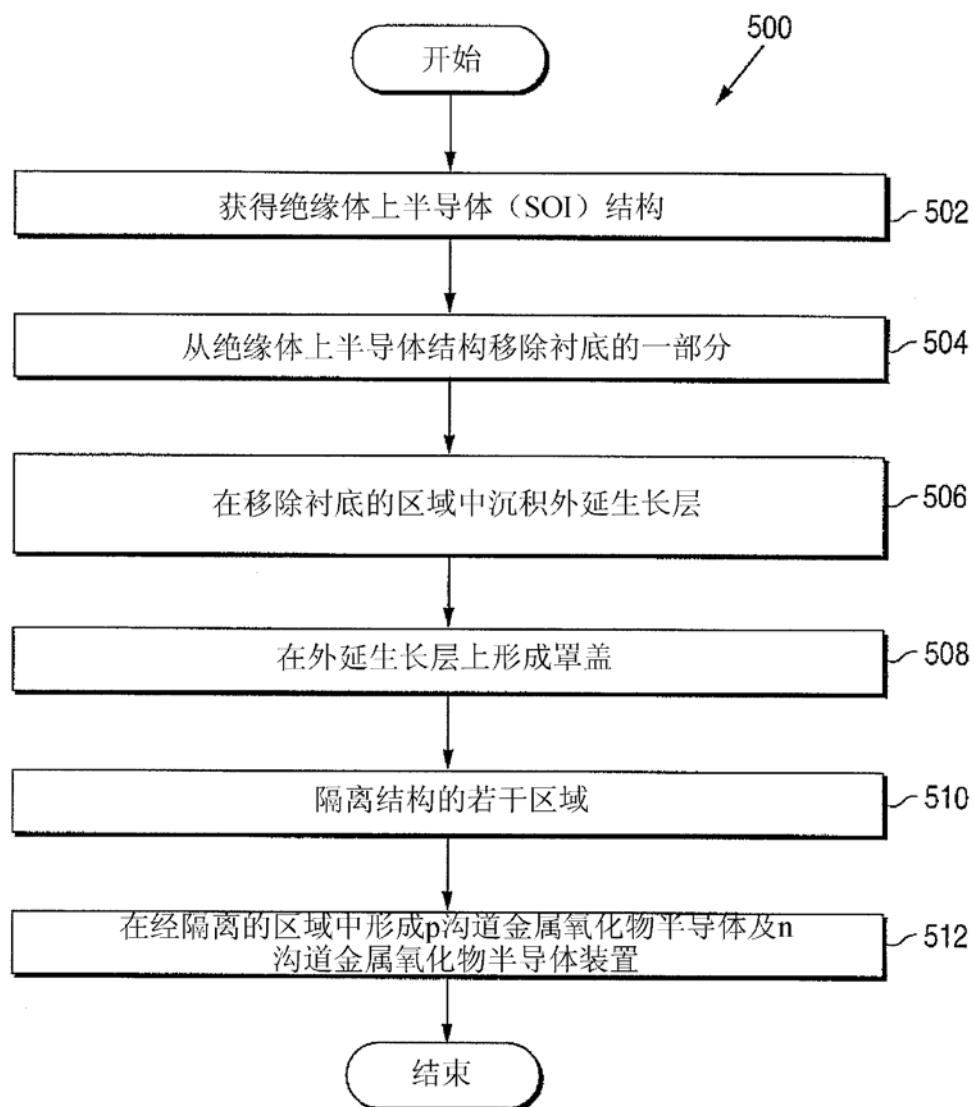

[0008] 图5说明根据本发明的形成使用结合选择性外延生长的HOT的集成电路装置的实例性方法。

### 具体实施方式

[0009] 下述的图1至5及本专利文献中的用于描述本发明的原理的各种实施例是仅作为说明的且不应以任何限制本发明的范围的方式解释。所属领域的技术人员将理解，本发明的原理可在任何类型的经合适地布置的装置或系统中实施。

[0010] 图1说明根据本发明的使用结合选择性外延生长的混合定向技术 (HOT) 的实例性集成电路装置100。图1中展示的集成电路装置100的实施例为仅用于说明的。可在不脱离本发明范围的情况下使用集成电路装置100的其它实施例。

[0011] 如图1中所展示，集成电路装置100包括晶片102。晶片102表示可用于承载或支撑集成电路装置100的其它组件的任何合适的半导体衬底。举例来说，晶片102可表示具有  $30 \Omega /cm$  的 (100) 结晶定向的P型衬底。

[0012] 掩埋层104驻留在晶片102的一部分上。掩埋层104一般表示用于在电性上隔离集成电路装置100的其它组件的氧化物或其它材料的薄层。举例来说,掩埋层104可表示具有约1450Å或2000Å的厚度的氧化硅层或其它氧化物层。

[0013] 衬底106驻留在掩埋层104上。衬底106可表示任何合适的半导体衬底。举例来说,衬底106可表示具有 $30\Omega/cm$ 的(110)结晶定向及在约 $2\mu m$ 与约 $5\mu m$ 之间的厚度的N型衬底。衬底106与晶片102可具有不同的结晶定向,从而实施HOT方法。为了方便起见,晶片102可称为“第一半导体衬底”,且衬底106可称为“第二半导体衬底”。

[0014] 外延生长层108也驻留在晶片102上。外延生长层108可表示任何合适的外延生长材料。举例来说,外延生长层108可由硅锗(例如 $Si_{0.85}Ge_{0.15}$ )形成。可在外延生长层108中使用其它材料,例如硅锡( $SiSn$ )或掺杂碳的硅锗( $SiGeC$ )。在一些实施例中,外延生长层108具有不同于衬底106的定向的结晶定向,例如(100)定向。

[0015] 罩盖110可形成在外延生长层108上。罩盖110可由一种或一种以上半导体衬底材料(例如硅)形成。在特定实施例中,罩盖110可由具有约1000Å的厚度的 $30\Omega/cm$ 的P型硅形成。注意,在其它实施例中,罩盖110可省略。

[0016] 在此实例中,沟槽112a-112c用于帮助在电性上隔离所述结构的不同部分。沟槽112a-112c可表示任何合适的隔离结构,例如浅沟槽隔离(STI)结构。沟槽112a-112c可以任何合适的方式且由任何合适的材料(例如氧化物)形成。同样,间隔物114可将衬底106与外延生长层108分隔。间隔物114可以任何合适的方式且由任何合适的材料(例如氧化物)形成。

[0017] 使用衬底106来形成p沟道金属氧化物半导体(PMOS)装置116。如图1中所展示,PMOS装置116包括源极118、漏极120、偏移122及栅极124。源极118、漏极120及偏移122中的每一者一般表示已使用一种或一种以上合适的掺杂剂掺杂的衬底106的区域。举例来说,源极118及漏极120可包括p+掺杂剂,且偏移122可包括p-掺杂剂。栅极124一般表示可用于控制PMOS装置116的操作的在电性上导电的区域,例如由多晶硅形成的在电性上导电的区域。栅极124通常通过栅极氧化物126与衬底106分隔。这些组件118-126中的每一者可使用任何合适的材料以任何合适的方式形成。

[0018] 使用罩盖110来形成n沟道金属氧化物半导体(NMOS)装置128(虽然在其它实施例中,NMOS装置128形成在外延生长层108中)。NMOS装置128包括源极130、漏极132、偏移134及栅极136。栅极136通过栅极氧化物138与罩盖110分隔。这些组件130-138可与PMOS装置116中的对应组件118-126相同或类似于PMOS装置116中的对应组件118-126,但是在NMOS装置128中使用不同的掺杂。举例来说,源极130及漏极132可包括n+掺杂剂,且偏移134可包括n-掺杂剂。这些组件130-138中的每一者可使用任何合适的材料以任何合适的方式形成。注意,(例如)当使用相同的工艺步骤来形成栅极124及136时,PMOS及NMOS装置116及128中的不同组件的形成可重叠。栅极氧化物126与138可或可不使用相同的工艺步骤来形成。

[0019] 氧化物层140形成在PMOS及NMOS装置116及128上。氧化物层140通常在后续的处理步骤期间保护集成电路装置100的下伏组件。氧化物层140可表示任何合适的氧化物材料且可以任何合适的方式形成。

[0020] 在一些实施例中,PMOS及NMOS装置116及128可表示具有较高的操作电压的装置(例如5V+PMOS及NMOS装置)。此电平的操作电压通常不能使用常规CMOS系统来获得。同样,

此处的集成电路装置100支持使用不同的材料及定向以支持较高的电子迁移率及较高的空穴迁移率两者。举例来说,衬底106的(110)定向可提供较好的空穴迁移率,而具有可调整的锗浓度的外延生长层108可提供较好的电子迁移率。这些结构中的两者可用于相同的集成电路中及相同的晶片上。

[0021] 此外,注意,此处的提高的空穴及电子迁移率为体性质,表示它们为所述结构的固有特性而不是仅由压力引起。这在形成用于应用(例如混合信号模拟应用)中的较高电压装置(例如5V+PMOS及NMOS装置)时是有用的。这些类型的装置通常不使用深亚微米技术来制造,因为那些技术向这些类型的装置提供极少益处,所以那些技术通常限于与低电压装置一起使用。所述较高电压装置通常达不到深亚微米尺寸且因此不通过光刻法而是通过体材料性质来驱动。此外,以此方式形成的装置可具有提高的晶体管导通电阻( $R_{DS_{ON}}$ )及跨导、较小的裸片尺寸及较低的成本。

[0022] 虽然图1说明使用结合选择性外延生长的HOT的集成电路装置100的一个实例,但是可对图1做出各种改变。举例来说,图1中的各种组件的相对尺寸及形状仅用于说明。同样,虽然图1中的某些组件已在上文描述为由特定材料形成,但是图1中的每一组件可由任何合适的材料且以任何合适的方式形成。此外,取决于制造工艺,各种其它层或结构可在集成电路装置100内形成。出于清晰的目的,那些其它层或结构从图1中省略。

[0023] 图2A至2K说明根据本发明的用于形成使用结合选择性外延生长的HOT的集成电路装置的实例性技术。图2A至2K中展示的技术的实施例为仅用于说明的。可在不脱离本发明范围的情况下使用其它技术来形成所述集成电路装置。

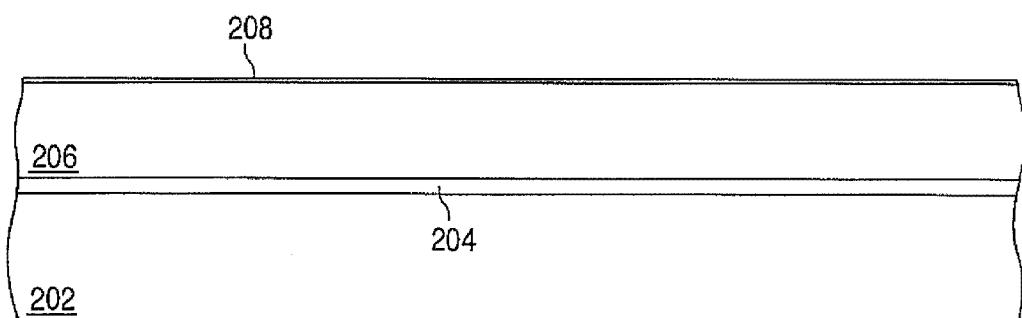

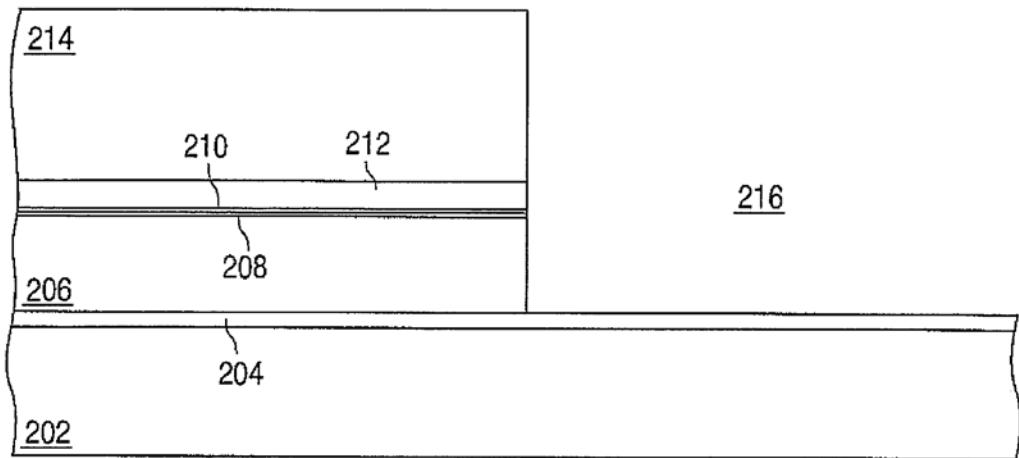

[0024] 如图2A中所展示,形成绝缘体上半导体(SOI)结构或以其它方式获得绝缘体上半导体(SOI)结构。所述结构包括晶片202及跨越晶片202形成的掩埋层204。晶片202可表示具有 $30\Omega/cm$ 的(100)定向的P型衬底。掩埋层204可表示具有约 $1450\text{\AA}$ 或 $2000\text{\AA}$ 的厚度的氧化硅层或其它氧化物层。在掩埋层204上的是衬底206,例如具有 $30\Omega/cm$ 的(110)定向及约 $2\mu\text{m}$ 到约 $5\mu\text{m}$ 的厚度的N型衬底。在特定实施例中,由组件202-206形成的SOI结构可直接从供应商处购买。在其它特定实施例中,SOI结构可以任何合适的方式制造。

[0025] 屏蔽氧化物层208形成在衬底206上。屏蔽氧化物层208的形成可包括屏蔽氧化清洁工艺、氧化衬底206的一部分(例如通过在 $1100^\circ\text{C}$ 下使用干氧化约49分钟)的屏蔽氧化工艺及后氧化操作。在特定实施例中,屏蔽氧化物层208具有 $350\text{\AA}\pm35\text{\AA}$ 的厚度。

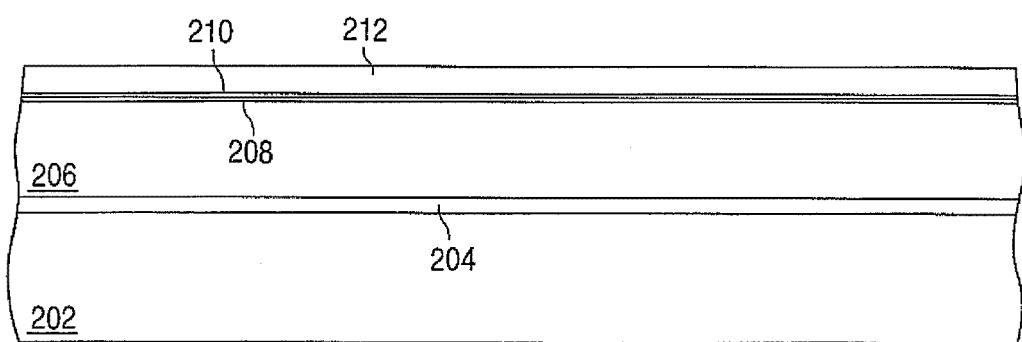

[0026] 如图2B中所展示,垫氧化物层210形成在所述结构上。垫氧化物层210的形成可包括垫氧化预清洁工艺、垫氧化工艺(例如通过在 $920^\circ\text{C}$ 下使用干氧化约40分钟)及后氧化操作。在特定实施例中,垫氧化物层210具有 $110\text{\AA}\pm10\text{\AA}$ 的厚度。氮化物层212形成在垫氧化物层210上。氮化物层212的形成可包括在 $760^\circ\text{C}$ 的温度下使用 $\text{NH}_3/\text{N}_2/\text{DCS}/\text{HCl}$ 约160分钟的氮化物沉积。在特定实施例中,氮化物层212具有 $1625\text{\AA}\pm150\text{\AA}$ 的厚度。

[0027] 如图2C中所展示,光致抗蚀剂掩模214形成在氮化物层212上。光致抗蚀剂掩模214可经图案化以包括将形成NMOS装置的区域上的开口216。光致抗蚀剂掩模214覆盖将形成PMOS装置的区域。可接着发生蚀刻以移除衬底206的一部分。所述蚀刻工艺可表示经设计以在到达掩埋层204之后即刻停止的NMOS光及深硅蚀刻工艺。可在所述蚀刻工艺之后执行抗蚀剂清洁及聚合物移除工艺以移除剩余的光致抗蚀剂掩模214。

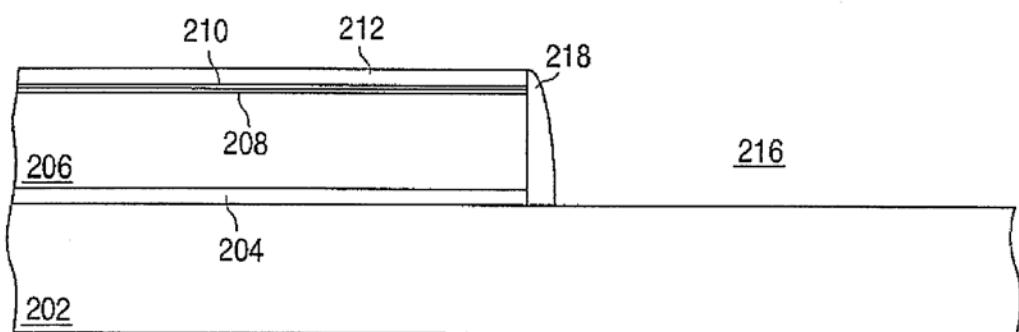

[0028] 如图2D中所展示,氧化物间隔物218抵靠衬底206而形成。氧化物间隔物218的形成

可包括执行间隔物氧化物沉积工艺以在所述结构上沉积氧化物层(例如2000Å或3000Å厚的氧化物层)。接着蚀刻所述氧化物层以形成氧化物间隔物218。所述蚀刻可包括在晶片202处停止的间隔物回蚀刻工艺。替代地,所述蚀刻可包括在掩埋层204处停止的间隔物回蚀刻工艺,接着执行蚀刻(例如HCl湿蚀刻)以移除掩埋层204的经暴露部分且使晶片202显露。

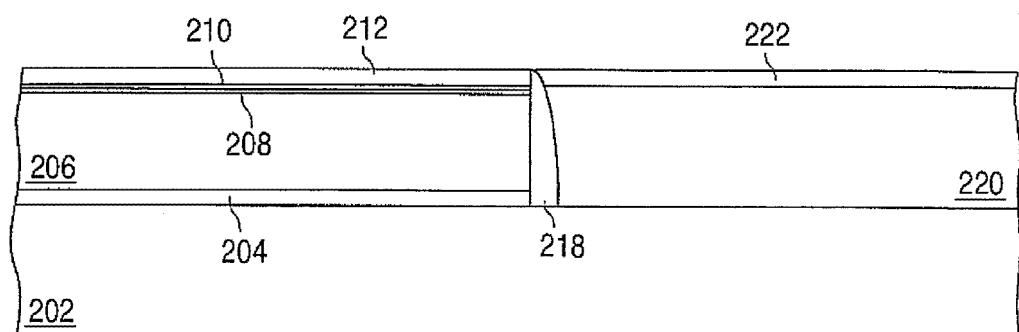

[0029] 如图2E中所展示,(例如)通过使用外延生长沉积工艺来在晶片202的经暴露部分上的开口216中形成外延生长层220。外延生长层220可由分级的硅锗形成,例如具有(100)定向的Si<sub>0.85</sub>Ge<sub>0.15</sub>。外延生长层220可具有约3μm±0.5μm或约5μm±0.2μm的厚度。(例如)当外延生长层220的顶面低于氮化物层212的顶面约2000Å时,外延生长层220可为底部填充的。罩盖222可(例如)通过生长具有约1000Å的厚度的30Ω/cm的P型硅层而形成在外延生长层220上。

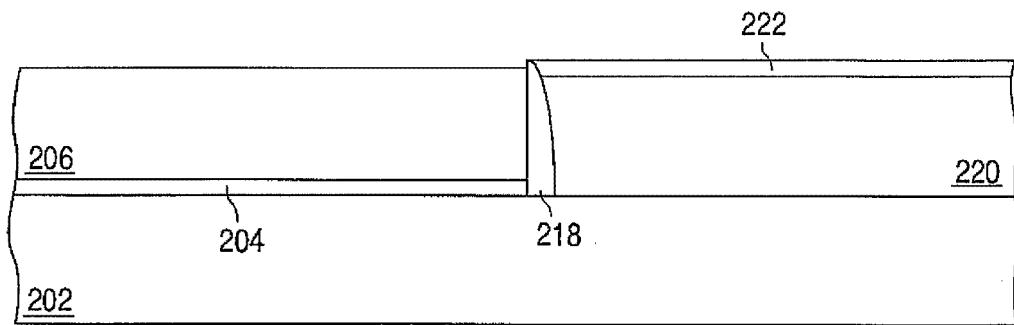

[0030] 如图2F中所展示,移除氮化物层212及氧化物层208-210。举例来说,这可通过剥离所述氮化物及氧化物层以暴露衬底206来发生。

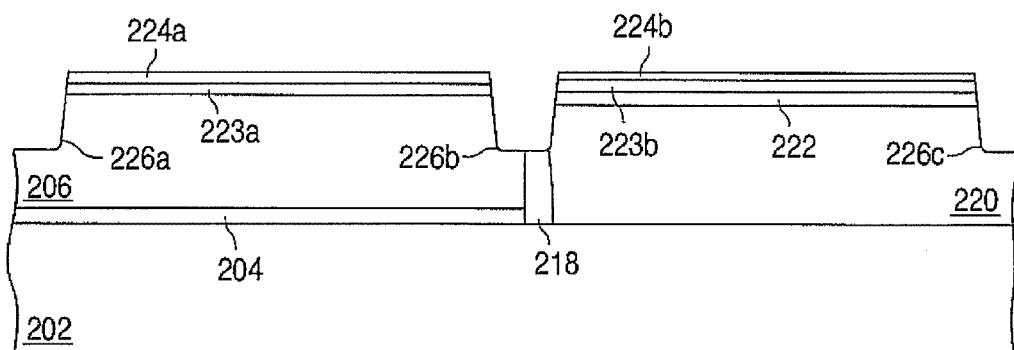

[0031] 如图2G中所展示,垫氧化物层223a-223b形成在所述结构上,且氮化物堆叠224a-224b形成在垫氧化物层223a-223b上。氮化物堆叠224a-224b可包括氮化物层及氮氧化硅(SiON)层。垫氧化物层223a-223b的形成可包括垫氧化预清洁工艺、垫氧化工艺(例如通过在920℃下使用干氧化约40分钟)及后氧化操作。氮化物堆叠224a-224b中的氮化物层的形成可包括在760℃的温度下使用NH<sub>3</sub>/N<sub>2</sub>/DCS/HCl约160分钟的氮化物沉积。氮化物堆叠224a-224b中的SiON层的形成可包括沉积SiON以形成防反射涂覆层。在特定实施例中,垫氧化物层具有110Å±10Å的厚度,氮化物层具有1625Å±150Å的厚度且SiON层具有320Å±32Å的厚度。

[0032] 沟槽226a-226c使用任何合适的技术形成在所述结构中。举例来说,掩模(例如复合掩模)可形成在所述结构上且可经图案化以暴露待形成沟槽226a-226c的区域。显影检查临界尺寸(DICD)工艺可用于检查所述掩模且保证所述掩模是合适的,例如通过保证所述掩模具有带有0.25μm±0.23μm的宽度的开口。蚀刻(例如复合等离子体蚀刻)可用于形成沟槽226a-226c,例如具有5600Å±400Å的深度的沟槽。接着可(例如)通过使用H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub>加上SC1的溶液五分钟来移除所述掩模。最终检查临界尺寸(FICD)工艺可用于检查所得沟槽226a-226c且保证所述沟槽是合适的,例如通过保证所述沟槽具有0.22μm±0.025μm的最小宽度。

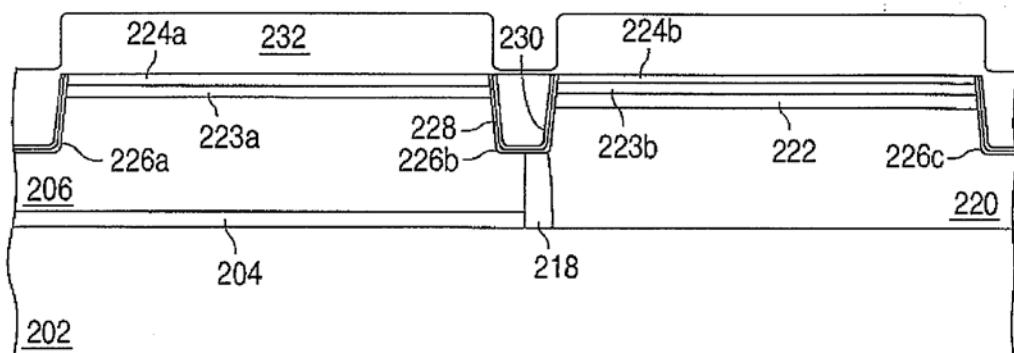

[0033] 如图2H中所展示,沟槽226a-226c经填充以产生隔离沟槽。可执行现场预清洁工艺且沟槽衬垫可形成在每一沟槽中。举例来说,所述沟槽衬垫可使用硅228(例如400Å或600Å硅)的选择性沉积来形成,接着形成沟槽衬垫氧化物230。可使用现场蒸汽生成(ISSG)来形成沟槽衬垫氧化物230以形成具有200Å±20Å的热氧化物层。在衬垫氧化物清理操作之后,可发生或可不发生沟槽退火。氧化物层232形成在所述结构上,其填充沟槽226a-226c的剩余部分。举例来说,可使用高密度等离子体(HDP)STI氧化物沉积工艺来形成氧化物层232。可发生清洁工艺及(可能地)快速热退火(RTA)。氧化物层232可具有5976Å±426Å的厚度。此处使用沟槽衬垫可帮助减少结泄漏且提高氧化物层232的氧化物质量。

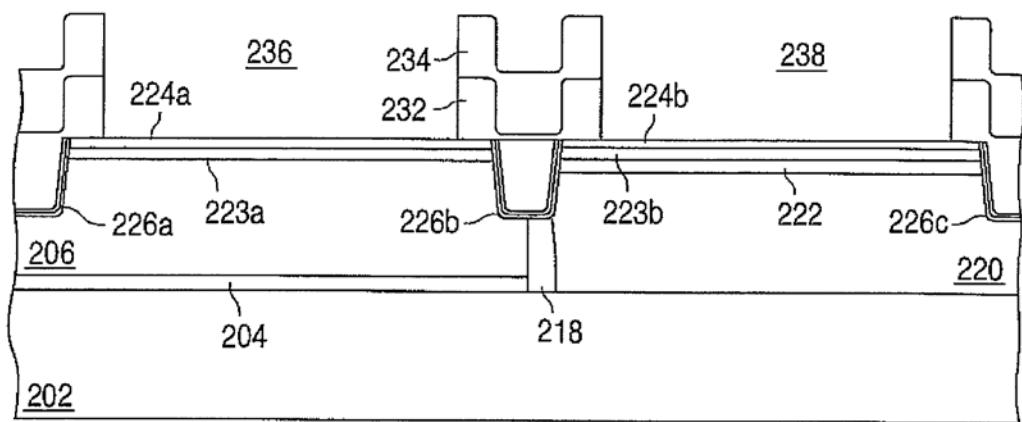

[0034] 如图2I中所展示,反掩模234形成在氧化物层232上且经图案化以形成开口236-238。接着蚀刻反掩模234下的氧化物层232。举例来说,可使用反掩模与反掩模重叠、蚀刻所述反掩模且在250℃下灰化所述反掩模70秒钟来形成反掩模234。在所述蚀刻之后,可在反

掩模清洁期间移除反掩模234，此可使用H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub>加上SC1的溶液十分钟。

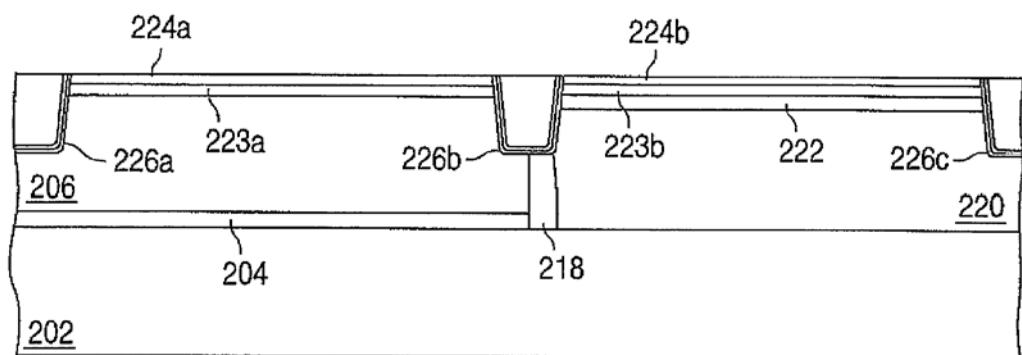

[0035] 如图2J中所展示，移除反掩模234及氧化物层232的剩余在氮化物堆叠224a-224b上的部分。此可牵涉到化学机械抛光 (CMP) 操作的使用。氧化物层232的一部分剩余在沟槽226a-226c中。氧化物层232的此部分可具有4000Å±400Å的厚度。

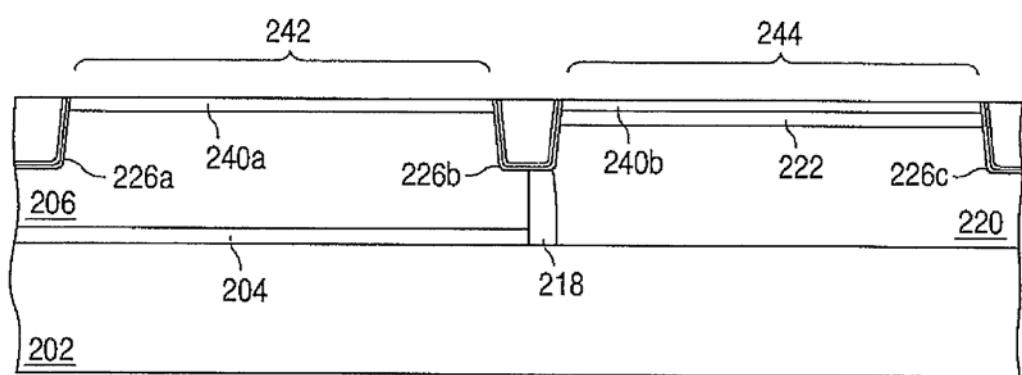

[0036] 如图2K中所展示，移除氮化物堆叠224a-224b及垫氧化物层223a-223b。举例来说，此可通过形成且固化开掩模且接着执行开掩模蚀刻来发生。所述蚀刻可包括2.5分钟的缓冲氧化物蚀刻 (BOE) 及使用H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub>加上SC1十分钟的湿蚀刻以移除SiON层。使用HF1.5分钟及使用H<sub>3</sub>PO<sub>4</sub>加上SC1十分钟的湿蚀刻可用于移除氮化物层。可使用垫氧化物条来移除垫氧化物层，此可或可不在所述结构上留下非常薄的氧化物(例如80Å±50Å)。栅极氧化物层240a-240b形成在所述结构上。举例来说，可使用120A蒸汽工艺来形成栅极氧化物层240a-240b。

[0037] 此时，可在图2K中展示的结构的第一区域242中形成PMOS装置，且可在图2K中展示的结构的第二区域244中形成NMOS装置。第一区域242包括可提供提高的空穴迁移率的具有第一定向(例如(110)定向)的衬底材料。第二区域244包括提供提高的电子迁移率且可能具有第二定向(例如(100)定向)的外延生长材料(例如SiGe)。举例来说，可使用标准CMOS工艺来形成PMOS及NMOS装置。

[0038] 注意，使用绝缘体上半导体结构可引起热消散问题。然而，此可(例如)通过使用对组件的精心布局或通过使用允许热直接消散到晶片202的传导带而在很大程度上减缓或避免。

[0039] 还需注意，衬底引起的应变可用于改变待形成的NMOS装置的迁移率。可使用外延生长层220及罩盖222来产生衬底引起的应变。外延生长层220可表示与在罩盖222中使用的硅或其它材料兼容的应变层。因此，外延生长层220可增加或减少罩盖222的晶格间隔，且取决于用于形成外延生长层220的材料，罩盖222处于拉伸或压缩状态。可在罩盖222中形成NMOS装置的源极及漏极，且罩盖222的拉伸或压缩可影响NMOS装置的操作。

[0040] 此外，可注意到用于形成PMOS及NMOS装置的后续CMOS处理步骤。应变消除可随着热预算、锗含量及罩盖厚度的增加而增加。在后续操作期间，外延生长层220及罩盖222可暴露于高温，例如在氧化物生长或活化退火期间。在一些实施例中，形成外延生长层220及罩盖222之后的所有热循环可保持低于1000°C且为尽可能短的，且可随时使用例如ISSG及快速热处理 (RTP) 等技术。

[0041] 此外，当形成实施此方法的特定装置时，可考虑以下内容。如果除了形成在图2K中展示的结构的区域242-244中的PMOS及NMOS装置外，在集成电路中还需要标准CMOS晶体管，那么那些晶体管可在衬底206中形成。同样，因为与PMOS及NMOS装置的操作相关联的高电流及高密度，所以当设计电路时可考虑电子迁移问题，且可选择合适的材料(例如铜)以用于形成局部互连。此外，如果在PMOS及NMOS装置两者中不能使用共用栅极氧化物，那么双多晶硅-双栅极氧化物 (DP-DGO) 方法可用于形成PMOS及NMOS装置。

[0042] 虽然图2A至2K说明用于形成使用结合选择性外延生长的HOT的集成电路装置的技术的一个实例，但是可对图2A至2K做出各种修改。举例来说，虽然这些图式说明在不同制造阶段的实例性结构，但是各种技术可用于形成所述集成电路装置。因此，可省略、修改或重新布置一个或一个以上步骤且可添加额外步骤。同样，可对图2A至2K中所展示的结构做出

各种修改。此外,虽然某些组件已在上文描述为由特定材料形成,但是每一组件可由任何合适的材料且以任何合适的方式形成。作为特定实例,虽然硅锗描述为用于外延生长层220中,但是可使用其它材料(例如GaN、GaAs、SiC、AlN或金刚石)。此外,组件的相对尺寸及形状为仅用于说明的。

[0043] 图3A至3G说明根据本发明的关于集成电路装置中的缺陷的实例性细节。图3A至3G中所展示的细节为仅用于说明的。在不脱离本发明范围的情况下其它集成电路可具有不同的缺陷特性。

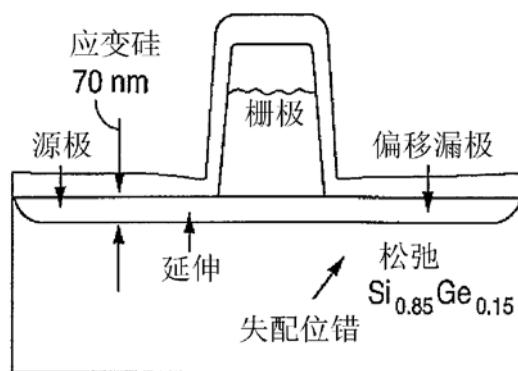

[0044] 图3A说明在集成电路装置中(例如在图2K中展示的结构的区域244中)实施的NMOS装置的横截面图。图3B说明相同的NMOS装置的长度图。如此处所展示,使用松弛的 $Si_{0.85}Ge_{0.15}$ 外延生长层上的70nm的应变硅罩盖来实施NMOS装置。失配位错为可发生在晶体管装置中的常见缺陷。如图3A中所展示,失配位错可在 $Si_{0.85}Ge_{0.15}$ 外延生长层中形成。如图3B中所展示,可沿着NMOS装置的长度形成一系列的失配位错。

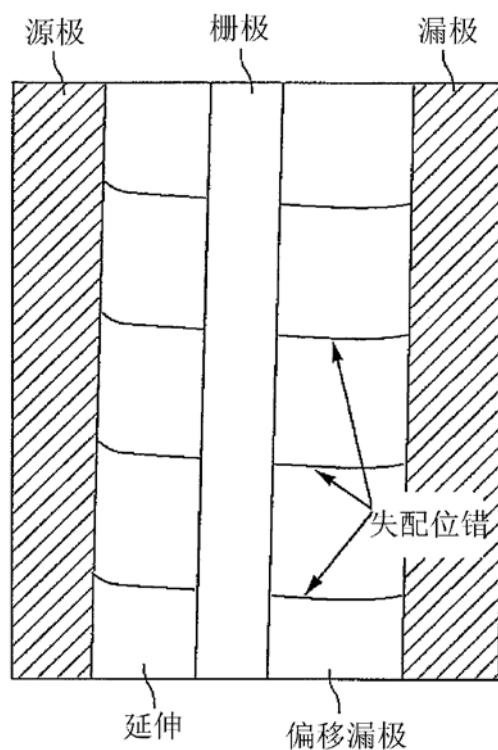

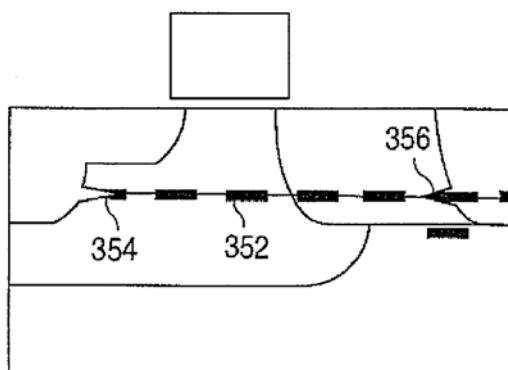

[0045] 图3C说明标准NMOS装置中的失配位错302的影响。此处,失配位错302允许更多的材料扩散到周围衬底中,此导致在晶体管的源极及漏极区域中形成水平峰值304-306。这些峰值304-306导致所述晶体管中的较高的结泄漏。相比之下,图3D说明形成在松弛 $Si_{0.85}Ge_{0.15}$ 外延生长层上的70nm的应变硅罩盖中的NMOS装置中的失配位错352的影响。如图3D中所展示,可仍然在晶体管的源极及漏极区域中形成水平峰值354-356。然而,与图3C中的峰值相比,峰值354-356为较小的且相隔较远。因此,图3D中展示的晶体管遭受较少的结泄漏。

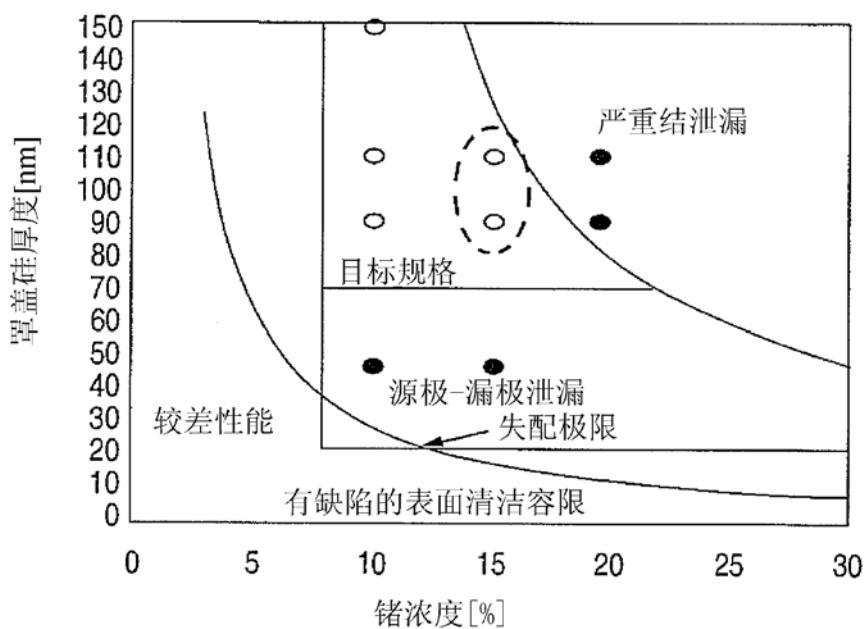

[0046] 如图3E中所展示,可针对与不同的结泄漏相关联的不同的区域绘制外延生长层中的锗浓度与硅罩盖厚度之间的关系。图3E中的开放圈表示较少的泄漏电流,而图3E中的实心圈表示过量的泄漏电流。如此处所展示,针对特定NMOS设计选择硅罩盖厚度及外延生长层锗浓度以实现想要的泄漏电流电平或范围是可能的。注意,可针对使用罩盖中的不同的材料或外延生长层中的不同的材料的装置来构造相同类型的图表。

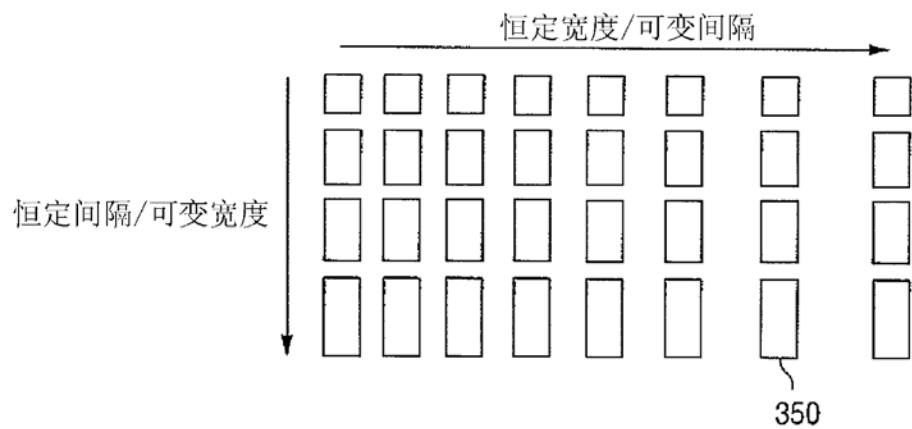

[0047] 返回参考图3B,邻近的失配位置之间的距离可表示为 $\gamma$ 。距离 $\gamma$ 对各种因素敏感,例如锗浓度、硅罩盖厚度及热预算。一种针对给定锗浓度、给定硅罩盖厚度及给定热预算来表征距离 $\gamma$ 的可能的方式展示在图3F中。此处,多个岛状物350(各自表示由硅罩盖覆盖的SiGe外延生长层)可在晶片上形成。岛状物350在晶片的横向上具有恒定宽度及可变间隔,且岛状物350在晶片的纵向上具有可变宽度及恒定间隔。在制造之后,(例如)可使用暗场照明来光学地检查岛状物350以识别最小化失配位错的数目的特定尺寸/间隔组合。以此方式,可识别针对给定锗浓度/硅罩盖厚度/热预算组合的最佳尺寸/间隔组合。此可针对不同的锗浓度/硅罩盖厚度/热预算组合而重复。

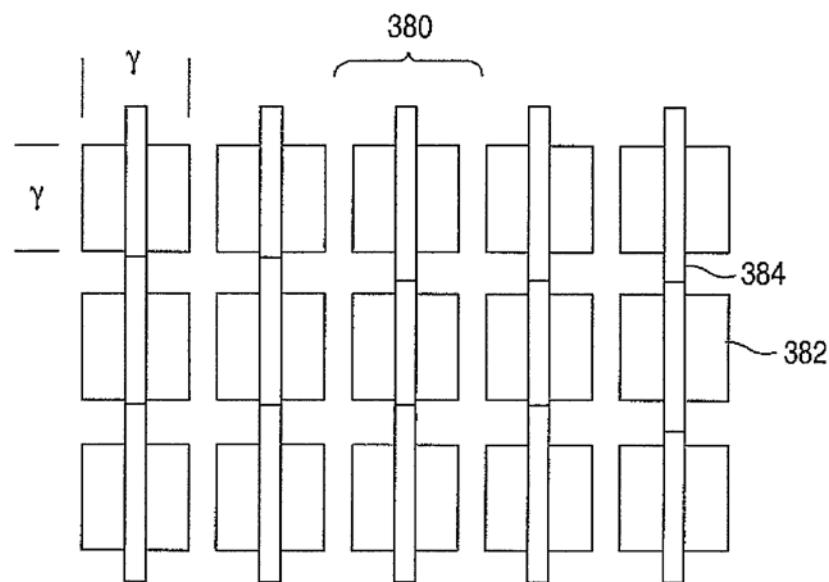

[0048] 一旦针对给定实施方案确定距离 $\gamma$ ,便可如图3G中所示布局电路,其中使用由局部互连384连接的多个岛状物382来形成多个晶体管380中的每一者。岛状物382中的每一者可具有等同于经识别的距离 $\gamma$ 的长度及宽度尺寸。理想地,此可帮助最小化或消除晶体管380中的失配位错。

[0049] 虽然图3A至3G说明关于集成电路装置中的缺陷的实例性细节,但是可对图3A至3G做出各种改变。举例来说,可使用其它技术来识别可接受的距离 $\gamma$ 。同样,可以任何其它合适的方式来形成晶体管380。

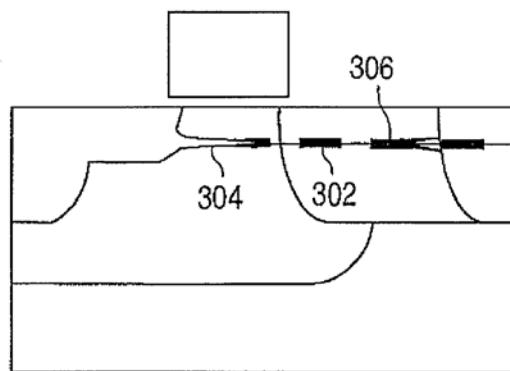

[0050] 图4说明根据本发明的具有使用结合选择性外延生长的HOT而形成的晶体管装置的实例性电路400。图4中展示的电路400的实施例为仅用于说明的。

[0051] 在此特定实例中,电路400表示具有脉冲宽度调制(PWM)控制器402、驱动器404 及两个晶体管406-408的降压调节器。PWM控制器402一般操作以输出具有可调整的脉冲宽度的信号。所述输出信号引起驱动器404将控制信号输出到晶体管406-408的栅极,其重复地接通及切断晶体管406-408。被提供到晶体管406的控制信号中的脉冲可落后于被提供到晶体管408的控制信号中的脉冲。当被接通时,晶体管406将电感器410 耦合到输入电压V<sub>IN</sub>,且晶体管408将电感器410耦合到接地。电感器410耦合到电容器412,且电路400产生用于负载的输出电压V<sub>OUT</sub>。负载电阻414表示为R<sub>L</sub>。晶体管 406-408中的每一者被接通及切断的时间量及因此输出电压V<sub>OUT</sub>的电平是通过由PWM 控制器402输出的信号的脉冲宽度来控制的。

[0052] PWM控制器402包括用于控制信号的脉冲宽度的任何合适的结构,例如同步整流 PWM控制器。驱动器404包括用于驱动晶体管的任何合适的结构。晶体管406-408可分别表示 5V+PMOS及NMOS晶体管。晶体管406-408可如图1中所展示而实施。电感器410、电容器412及负载电阻414可具有任何合适的值。

[0053] 在特定实施例中,电路400接收5V输出电压V<sub>IN</sub>、在5V下驱动晶体管406-408的栅极且产生2.45输出电压V<sub>OUT</sub>。电路400可具有2ns的寂静时间、0.5A的输出电流、50%工作循环和1μF电容器412。电路400可具有50mm的总栅极宽度及1-20MHz的频率范围或10-200mm的宽度范围及6MHz的频率。

[0054] 虽然图4说明具有使用结合选择性外延生长的HOT而形成的晶体管装置的电路400的一个实例,但是可对图4做出各种改变。举例来说,使用结合选择性外延生长的HOT 而形成的晶体管装置可用于任何其它合适的电路中。

[0055] 图5说明根据本发明的用于形成使用结合选择性外延生长的HOT的集成电路装置的实例性方法500。图5中展示的方法500的实施例为仅用于说明的。在不脱离本发明范围的情况下可使用方法500的其它实施例。

[0056] 如图5中所展示,在步骤502处制造或以其它方式获得绝缘体上半导体(SOI)结构。SOI结构可包括第一衬底材料(例如p型材料)、第二衬底材料(例如n型材料)及分隔第一及第二衬底材料的掩埋层。(例如)当第一衬底材料具有(100)定向且第二衬底材料具有(110)定向时,第一及第二衬底材料可具有不同的结晶定向。

[0057] 在步骤504处,从SOI结构移除第二衬底材料的一部分。此可包括(例如)遮蔽 SOI 结构且移除n型衬底的一部分以暴露下伏p型晶片。外延生长层沉积在已在步骤506 处移除第二衬底材料的区域中。此可包括(例如)在p型晶片的经暴露部分上形成分级的硅锗外延生长层。在步骤508处,罩盖在所述外延生长层上形成。此可包括(例如) 在所述硅锗外延生长层上形成硅罩盖。

[0058] 此时,所述结构包括两个不同的区域。一个区域具有原始第二衬底材料,且另一个区域具有外延生长层及罩盖。在步骤510处,隔离所述结构的不同的区域。此可包括(例如)在不同的区域附近及之间形成沟槽。在步骤512处,PMOS及NMOS装置形成在经隔离的区域中。举例来说,PMOS装置可形成在具有原始第二衬底材料的区域中,且 NMOS装置可形成在具有外延生长层及罩盖的区域中。

[0059] 虽然图5说明用于形成使用结合选择性外延生长的HOT的集成电路装置的方法500

的一个实例,但是可对图5做出各种改变。举例来说,虽然展示为一系列的步骤,但是图5中的各个步骤可重叠、并行地发生或以不同的次序发生。

[0060] 阐述已在此专利文献中使用的某些词及短语的定义可为有利的。当参考图式中的结构使用时,术语(例如“上”及“下”)仅指当在特定方向上观察时所述结构的方位。术语“耦合”及其派生物指两个或两个以上组件之间的任何直接或间接联系,不管那些组件是否互相处于物理接触中。术语“包括”及“包含”,以及其派生物表示包括而无限制。术语“或”是包括性的,表示及/或。短语“与...相关联”及“与其相关联”以及其派生物,可表示包括、被包括在内、与...互连、包含、被包含在内、连接到或与...连接、耦合到或与...耦合、可与...连通、与...合作、交叉、并列、接近于、附着到或与...附着、具有、具有...性质、具有到...或与...的关系或类似物。

[0061] 虽然本发明已描述某些实施例及一般相关联的方法,但是对这些实施例及方法的改变及排列对所属领域的技术人员将是显而易见的。因此,对实例性实施例的以上描述不限定或限制本发明。在不脱离如所附权利要求书限定的本发明的精神及范围的情况下其它变化、代替及改变也是可能的。

图1

图2A

图2B

图2C

图2D

图2E

图2F

图2G

图2H

图2I

图2J

图2K

图3A

图3B

图3C

图3D

图3E

图3F

图3G

图4

图5