(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-228807

(P2005-228807A)

(43) 公開日 平成17年8月25日(2005.8.25)

(51) Int.Cl.<sup>7</sup>

H01L 21/822

H01L 27/04

H03H 7/06

F 1

H01L 27/04

H03H 7/06

H01L 27/04

テーマコード(参考)

5 F 038

5 J 024

P

審査請求 未請求 請求項の数 2 O L (全 8 頁)

(21) 出願番号

特願2004-33707 (P2004-33707)

(22) 出願日

平成16年2月10日 (2004.2.10)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100098291

弁理士 小笠原 史朗

(72) 発明者 中野 智至

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

F ターム(参考) 5F038 AC15 AR09 AZ03 BH02 BH03

BH05 BH13 BH19 EZ20

5J024 AA01 BA05 CA20 DA04 EA01

EA08 GA02

(54) 【発明の名称】回路保護装置

## (57) 【要約】

【課題】 カットオフ周波数が変動しない高周波ノイズ除去フィルタとしての機能と、静電気等のサージを吸収する保護回路としての機能とを兼ね備えた回路保護装置を提供する。

【解決手段】 回路保護装置100は、入力電極151、N型埋め込み領域137、P型半導体基板122及び共通電極160でなる定電圧ダイオードと、出力電極152、電極間挿入部140、P型半導体基板122及び共通電極160でなるコンデンサと、抵抗体124とを備えている。入力電極151及び出力電極152は、抵抗体124に電気的に接続されている。定電圧ダイオードは保護回路として、また、抵抗体124とコンデンサとで高周波ノイズ除去用のフィルタとして機能する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

保護すべき回路の入力部と電気的に接続される回路保護装置であって、

第1導電型の半導体基板と、

前記半導体基板の第1主面から表面が露出するように形成され、前記半導体基板にP N

接合された第2導電型の埋め込み部と、

前記第1主面上の、前記埋め込み部が形成されていない領域に設けられ、コンデンサの

電極間充填材として機能する電極間充填部と、

前記第1主面上の、前記埋め込み部及び前記電極間充填部が形成されていない領域を覆

う絶縁膜と、

前記絶縁膜上に設けられた抵抗体と、

前記埋め込み部を覆い、前記抵抗体と電気的に接続された入力電極と、

前記電極間充填部を覆い、前記抵抗体と電気的に接続された出力電極と、

前記半導体基板の第2主面に形成された共通電極とを備えた回路保護装置。

## 【請求項 2】

前記共通電極が金または金を主成分とする材料で形成されていることを特徴とする、請求項1に記載の回路保護装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、集積回路等の入力部に保護回路として設けられる回路保護装置に関する。

## 【背景技術】

## 【0002】

携帯電話やパーソナルコンピュータ等の電子機器の外部接続端子から電子機器内に静電気等のサージ（以下、静電気サージという）が進入し、電子機器内の集積回路に瞬間に大電圧が印加されると、集積回路が破壊されてしまう。静電気サージは、帯電した人や物が外部入力端子や集積回路チップの入力端子に接触した場合など、通常の使用形態でも頻繁に発生する。そのため、集積回路の入力部には、一般的に、静電気サージから集積回路を保護するための保護回路が取り付けられる。

## 【0003】

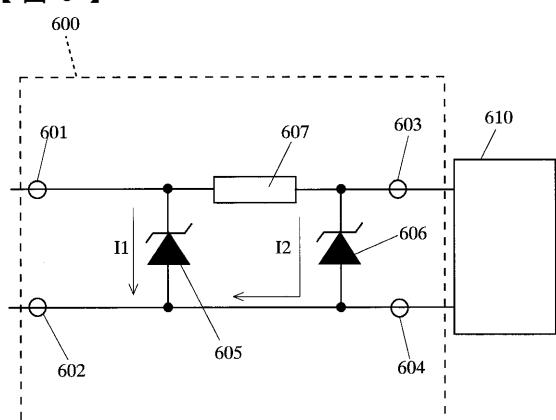

図6は、特許文献1に記載した保護回路600を示す図である。保護回路600は、入力端子601、602と出力端子603、604との間に接続された2つの定電圧ダイオード605、606と、定電圧ダイオード605、606のカソード電極間に接続された抵抗607とで構成されている。定電圧ダイオード605、606のカソード電極側は、それぞれ、入力端子601及び出力端子603と接続されている。

## 【0004】

定電圧ダイオード605、606には、アノード-カソード電極間の電位差が所定値を超えたときにのみ、図中に示すように電流I1、I2が流れる。これにより電圧が降下するため、保護回路600からは、ある一定値以上の電圧は出力されない。よって、保護回路600を設けておけば、保護回路600の後に接続されている集積回路610には大電流が流れ込むことがなく、静電気サージによる回路破壊を防止することができる。

## 【0005】

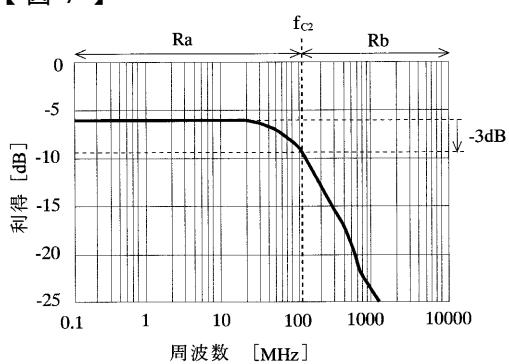

ところで、保護回路600は、高周波ノイズ除去用のパイ型ローパスフィルタとしても機能する。出力端子603がハイインピーダンスである場合、カットオフ周波数f<sub>c2</sub>は、抵抗607の抵抗値R<sub>2</sub>と定電圧ダイオード606におけるP型半導体部とN型半導体部との接合容量C<sub>2</sub>とを用いて、次式(1)のように表される。

$$f_{c2} = 1 / 2 \pi R_2 C_2 \quad \dots (1)$$

## 【0006】

図7は、ローパスフィルタの出力特性を示す図である。図7における横軸は周波数、縦軸は、利得を示している。カットオフ周波数f<sub>c2</sub>は、利得が平坦な部分から3dB低下し

10

20

30

40

50

た位置における周波数と決められている。ローパスフィルタでは、入力信号のうちカットオフ周波数  $f_{c_2}$  以下の周波数帯域（以下、通過帯域  $R_a$  という）の信号は出力されるが、カットオフ周波数  $f_{c_2}$  よりも高いの周波数帯域（以下、阻止帯域  $R_b$  という）の信号は、ほぼ除去されて出力されない。

【特許文献 1】特開平 11 - 168175 号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

ところで、定電圧ダイオード 606 の接合容量  $C_2$  は、定電圧ダイオード 606 を構成する P 型半導体部と N 型半導体部の P-N 接合部に形成される空乏層の幅に反比例するので、入力電圧が変化すると空乏層の幅が変化し、上記式（1）で表されるカットオフ周波数  $f_{c_2}$  も変化してしまう。このようにカットオフ周波数  $f_{c_2}$  が変化すると、通過領域  $R_a$  と阻止領域  $R_b$  とが変動するために、入力信号のうち、回路装置 610 に入力すべき周波数信号を除去してしまったり、除去されるべき周波数信号が後続の回路装置 610 に入力されたりする。このように、従来の保護回路 600 では、入力電圧によってカットオフ周波数  $f_{c_2}$  が変化してしまうため、ローパスフィルタとしての働きは充分ではなかった。

【0008】

それ故に、本発明は、カットオフ周波数が変動しない高周波ノイズ除去フィルタとしての機能と、静電気等によるサージを吸収する保護回路としての機能とを兼ね備えた回路保護装置を提供することを目的としている。

【課題を解決するための手段】

【0009】

本発明に係る回路保護装置は、保護すべき回路の入力部と電気的に接続される回路保護装置であって、第 1 導電型の半導体基板と、半導体基板の第 1 主面から表面が露出するよう形成され、半導体基板に P-N 接合された第 2 導電型の埋め込み部と、第 1 主面上の、埋め込み部が形成されていない領域に設けられ、コンデンサの電極間充填材として機能する電極間充填部と、第 1 主面上の、埋め込み部及び電極間充填部が形成されていない領域を覆う絶縁膜と、絶縁膜上に設けられた抵抗体と、埋め込み部を覆い、抵抗体と電気的に接続された入力電極と、充填部を覆い、抵抗体と電気的に接続された出力電極と、半導体基板の第 2 主面に形成された共通電極とを備える。

【0010】

共通電極は、金または金を主成分とする材料で形成されていてもよい。

【発明の効果】

【0011】

本発明の実施形態に係る回路保護装置は、静電気等のサージを吸収する保護回路としての機能と高周波ノイズを除去するフィルタリング機能とを兼ね備え、かつ、簡単な構造を有している。また、R-C 回路を構成するコンデンサを備えているために、高周波ノイズ除去のカットオフ周波数が変動せず、所望の周波数の入力信号のみを安定して出力することができる。また、本発明に係る回路保護装置を用いれば、回路保護用の回路素子とフィルタリング用の回路素子とを個別に設ける必要が無いため、電子機器における部品点数を削減させることができる。

【発明を実施するための最良の形態】

【0012】

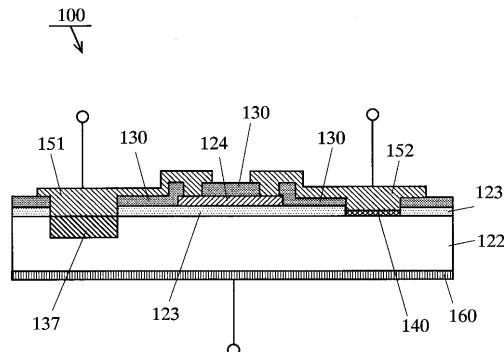

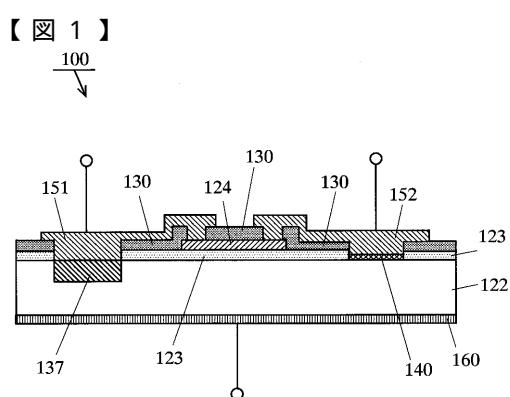

図 1 は、本発明の実施形態に係る回路保護装置 100 の断面図である。図 1 に示す回路保護装置 100 は、図 2 に示す回路 200 を実現するチップ素子であり、保護したい集積回路の入力部に接続される。この回路保護装置 100 は、静電気等によるサージ（以下、静電気サージという。）を吸収することによって集積回路の破壊を防止する回路保護機能と、入力信号から高周波ノイズをカットするフィルタリング機能とを備えている。

【0013】

図 1 に示す回路保護装置 100 は、P 型半導体基板 122、N 型埋め込み領域 137、

10

20

20

30

40

50

電極間挿入部 140、抵抗体 124、入力電極 151、出力電極 152、絶縁膜 123、130 及び共通電極 160 を備えている。

#### 【0014】

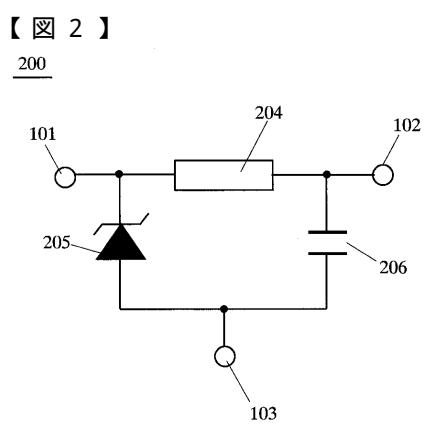

図 2 に示す回路 200 は、入力端子 101、定電圧ダイオード 205、抵抗 204、コンデンサ 206、出力端子 102 及び共通端子 103 を備えている。定電圧ダイオード 205 のカソード電極及びアノード電極は、それぞれ、入力端子 101 及び共通端子 103 に接続されている。コンデンサ 206 の 2 つの電極は、それぞれ、出力端子 102 及び共通端子 103 と接続されている。抵抗 204 は、定電圧ダイオード 205 のカソード電極とコンデンサ 206 の一方の電極とに接続されている。

#### 【0015】

図 1 に示す N 型埋め込み領域 137 と P 型半導体基板 122 とは、P N 接合されて図 2 に示す定電圧ダイオード 205 を構成している。図 1 に示す入力電極 151 は、N 型埋め込み領域 137 の全面を覆うように形成されており、図 2 に示す定電圧ダイオード 205 のカソード電極になっている。また、図 1 に示す共通電極 160 は、図 2 に示す定電圧ダイオード 205 のアノード電極になっている。N 型埋め込み領域 137 の深さは  $7 \mu\text{m}$  程度であり、表面におけるリン濃度は  $3 \times 10^{19} \text{ cm}^{-3}$  程度である。P 型半導体基板 122 の比抵抗は、 $4.5 \cdot \text{m}$  程度になっている。

#### 【0016】

図 1 に示す出力電極 152 は図 2 に示すコンデンサ 206 の一方の電極を構成している。また、P 型半導体基板 122 及び共通電極 160 は、コンデンサ 206 の他方の電極を構成している。電極間挿入部 140 は、厚みが  $50 \text{ nm}$  程度の絶縁膜である。電極間挿入部 140 を形成する材料は、例えば、二酸化シリコン ( $\text{SiO}_2$ ) や窒化シリコン ( $\text{Si}_3\text{N}_4$ ) など、入力電圧に対する容量値の変化が少ない材料であればよい。コンデンサ 206 の容量値は、電極間挿入部 140 のような電極間挿入物の厚みや誘電率で決められる。よって、電極間挿入部 140 として適当な材料を選択し大きさを適当に設計しておけば、所望の容量値を有するコンデンサ 206 を形成することができる。

#### 【0017】

絶縁膜 123 は、P 型半導体基板 122 の表面のうち N 型埋め込み領域 137 と電極間挿入部 140 とが形成されていない領域に形成されている。抵抗体 124 は、絶縁膜 123 上の一部に形成されており、図 2 に示す抵抗 204 を構成している。抵抗体 124 は、ポリシリコン層内にボロンを拡散させることによって所望の導電率になるよう、つまり、所望の抵抗値が得られるよう形成されている。抵抗体 124 の表面におけるボロン濃度は、 $3 \times 10^{19} \text{ cm}^{-3}$  程度であり、シート抵抗値は  $90 / \text{程度}$  である。絶縁膜 130 は、抵抗体 124 の一部のみを露出させて抵抗体 124 と絶縁膜 123 とを覆っている。

#### 【0018】

入力電極 151 の一部は、図 2 に示す定電圧ダイオード 205 のカソード電極と抵抗 204 とを電気的に接続する配線を構成している。また、出力電極 152 の一部は、図 2 に示すコンデンサ 206 の一方の電極と抵抗 204 とを電気的に接続する配線を構成している。また、入力電極 151、出力電極 152 及び共通電極 160 は、それぞれ、図 2 に示す入力端子 101、出力端子 102 及び共通端子 103 を構成している。この回路保護装置 100 は、出力電極 152 と保護対象となる集積回路チップの入力端子とが電気的に接続されるようにマザーボード上に取り付けられる。共通電極 160 は主に接地電極として使用される。

#### 【0019】

なお、上記した濃度や厚み等の値で各構成要素を形成した場合、サージ耐圧が  $25 \text{ kV}$  となり、国際電気標準会議 IEC 61000-4-2 レベル 4 の規格を満たすことができる。また、図 2 に示す回路 200 における、定電圧ダイオード 205 のツェナー電圧値を  $7 \text{ V}$ 、接合容量を  $25 \text{ pF}$  とし、抵抗 204 の抵抗値を  $100 \Omega$ 、コンデンサの容量値を  $25 \text{ pF}$  として、共通端子 103 を接地したときには、カットオフ周波数  $100 \text{ MHz}$ 、サージ耐圧  $25 \text{ kV}$  となる。ただし、上記した設計値は一例に過ぎず、入力する信号や保

護対象となる回路の特性等に合わせて各数値等を調整すればよい。

#### 【0020】

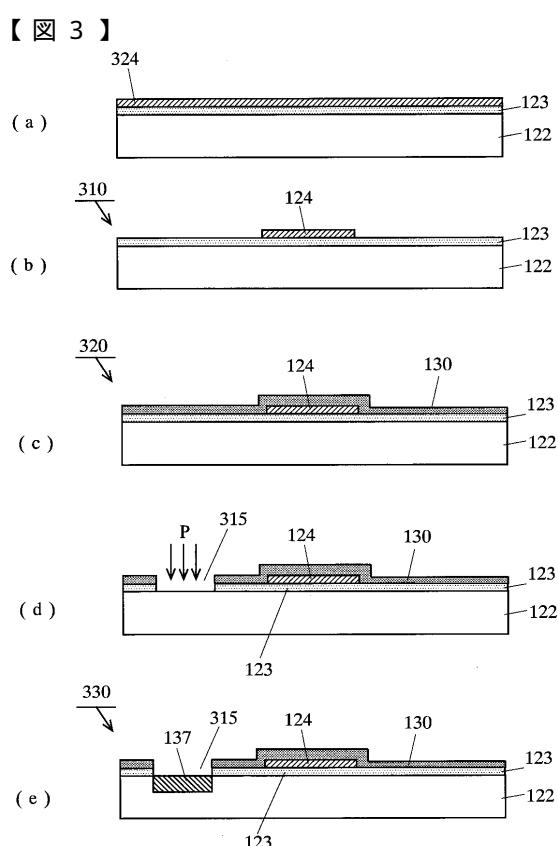

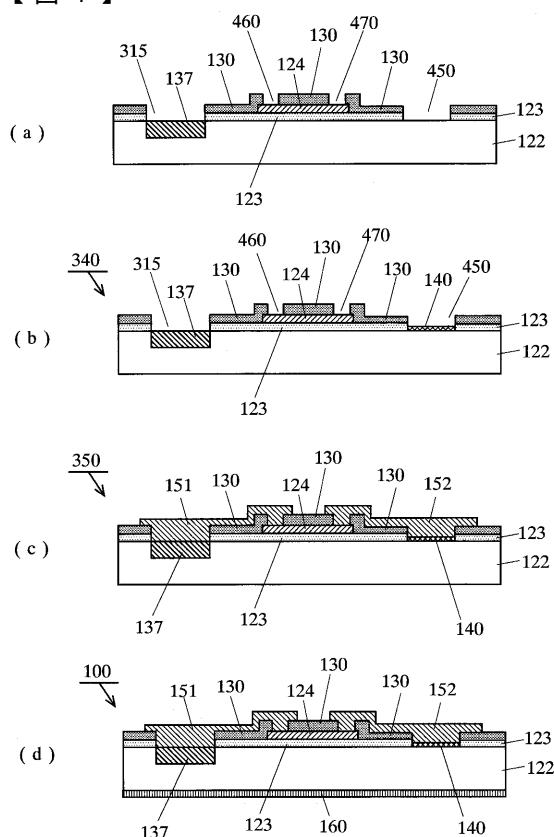

この回路保護装置100の製造方法の一例を、図3及び図4を用いて説明する。まず、図3(a)に示すように、P型半導体基板122の表面を酸化してシリコン酸化膜である絶縁膜123を形成する。絶縁膜123の上には、所望する厚さのポリシリコン膜を形成した後、所望の濃度になるまでボロンを拡散させることによって、抵抗体形成用膜324を形成する。

#### 【0021】

次に、抵抗体形成用膜324を所望の大きさにエッティングすることにより、図3(b)に示す抵抗体124を形成する。図3(b)に示す仕掛け状態の回路保護装置を、仕掛け回路保護装置310という。10

#### 【0022】

次に、図3(c)に示すように、仕掛け回路保護装置310の表面に、CVD(chemical vapor deposition: 化学気相成長)等で酸化シリコンの絶縁膜130を形成する。図3(c)に示す仕掛け状態の回路保護装置を、仕掛け回路保護装置320という。

#### 【0023】

次に、図3(d)に示すように、後にN型埋め込み領域137を形成したい領域上に形成されている絶縁膜123及び絶縁膜130をエッティングして、コンタクト窓315を形成する。コンタクト窓315から露出したP型半導体基板122には、リンを注入して拡散させ、所望する深さと不純物濃度のN型埋め込み領域137を形成する。図3(e)に示す仕掛け状態の回路保護装置を、仕掛け回路保護装置330という。20

#### 【0024】

次に、図4(a)に示すように、後に電極間挿入部140を形成したい領域上の絶縁膜130及び絶縁膜123をエッティングして、コンタクト窓450を形成する。また、抵抗体124を覆っている絶縁膜130の一部もエッティングして、コンタクト窓460、470を形成する。

#### 【0025】

次に、図4(b)に示すように、コンタクト窓450から露出したP型半導体基板122の表面を酸化させて、シリコン酸化膜である電極間挿入部140を形成する。図4(b)に示す仕掛け状態の回路保護装置を仕掛け回路保護装置340という。30

#### 【0026】

次に、仕掛け回路保護装置340の表面に、電子ビーム蒸着法等によりアルミニウムを蒸着して入力電極151、152を形成する。この仕掛け状態の回路保護装置を仕掛け回路保護装置350という。

#### 【0027】

最後に、仕掛け回路保護装置350の裏面に、金などの導電性の高い金属を電子ビーム蒸着法等で蒸着して共通電極160を形成すると、回路保護装置100が完成する。なお、共通電極160は、この工程よりも先の工程で形成しておいてもよい。

#### 【0028】

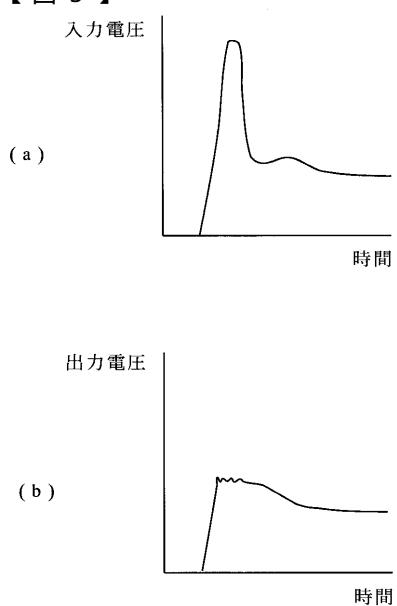

次に、図2に示す回路図を用いて、本実施形態に係る回路保護装置100の機能及び効果を説明する。抵抗204とコンデンサ206とで構成されるRC回路は、入力信号から高周波ノイズを除去する1次のRCローパスフィルタを構成する。出力端子102がハイインピーダンスである場合、コンデンサ206の容量値をC<sub>1</sub>、抵抗204の抵抗値をR<sub>1</sub>とすると、ローパスフィルタのカットオフ周波数f<sub>c1</sub>は、次式(2)で示される。

$$f_{c1} = 1 / 2 \pi R_1 C_1 \quad \dots (2)$$

上述のように電極間挿入部140を形成する材料には、容量値の変動が少ない材料が選ばれているので、入力電圧の変化に対するコンデンサ206の容量値の変動が少ない。よって、入力電圧が変化してもカットオフ周波数f<sub>c1</sub>が変化しないため、カットオフ周波数f<sub>c1</sub>以下の周波数帯域(図7における通過帯域Ra)と、カットオフ周波数f<sub>c1</sub>よりも大40

きな周波数帯域（図7における阻止帯域Rb）とが変動しない。したがって、回路保護装置100によれば、入力信号のうち特定周波数帯域の信号のみを安定して出力することができる。

#### 【0029】

これに加えて本実施形態に係る回路保護装置100は、静電気サージから集積回路を保護する機能も備えている。図2に示す入力端子101と共に端子103との間に、つまり、図1に示す入力電極151と共に電極160との間に、所定値以上の電圧が印加された場合には、定電圧ダイオード205でツェナー降伏が起こり、電圧が降下する。例えば、図5(a)に示すように立ち上がりの鋭いサージ電圧が回路保護装置100に印加されると、図5(b)に示すように所定の閾値以下の電圧のみが出力される。よって、この回路保護装置100の出力端子102に接続された集積回路チップ等には、所定値以上の電圧が印加されないため、静電気サージによる集積回路の破壊を防止することができる。また、共通電極160を金など導電性が非常に高い金属材料で形成しておけば、回路保護装置100を設置するマザー基板との直列抵抗を低減させることができ、サージ吸収効果をさらに向上させられる。10

#### 【0030】

このように回路保護装置100は、保護回路としての機能と、高周波ノイズフィルタとしての機能を兼ね備えている。よって、保護対象となる集積回路が実装されているマザー基板上に、回路保護用素子と高周波フィルタ素子とを個別に実装するよりも、製造工程を簡略化することができる。また、マザー基板上に実装する部品点数を削減することができる。20

#### 【産業上の利用可能性】

#### 【0031】

本発明に係る回路保護装置は、カットオフ周波数が変動しない高周波ノイズ除去フィルタとしての機能と、静電気等のサージを吸収する保護回路としての機能とを兼ね備えているので、半導体集積回路を搭載したマザー基板上に設ける保護回路などのチップ素子等として利用することができる。

#### 【図面の簡単な説明】

#### 【0032】

【図1】本発明の実施形態に係る回路保護装置の断面図30

【図2】図1に示す回路保護装置の回路図

【図3】図1に示す回路保護装置の製造方法を説明する図

【図4】図3の続図

【図5】図1に示す回路保護装置における入力電圧と出力電圧とを説明する図

【図6】従来の保護回路

【図7】ローパスフィルタの特性を示す図

#### 【符号の説明】

#### 【0033】

100 回路保護装置

101 入力端子

102 出力端子

103 共通端子

122 P型半導体基板

123 絶縁膜

124 抵抗体

130 絶縁膜

137 N型埋め込み領域

140 電極間挿入部

151 入力電極

152 出力電極

10

20

30

40

50

## 160 共通電極

【図4】

【図5】

【図6】

【図7】