(19)

(10)

AT 514564 B1 2015-02-15

(12)

# Patentschrift

(21) Anmeldenummer: A 50439/2013

(22) Anmeldetag: 04.07.2013

(45) Veröffentlicht am: 15.02.2015

(51) Int. Cl.: H05K 1/18 (2006.01)

H01L 21/56 (2006.01)

H01L 23/538 (2006.01)

(56) Entgegenhaltungen:

US 2006049530 A1

US 2008116565 A1

US 2010044842 A1

WO 2012100274 A1

(73) Patentinhaber:

AT&S AUSTRIA TECHNOLOGIE &

SYSTEMTECHNIK AKTIENGESELLSCHAFT

8700 LEOBEN (AT)

(72) Erfinder:

Schrittwieser Wolfgang

8605 Kapfenberg (AT)

Morianz Mike Dipl.Ing.

8045 Graz (AT)

Kasper Alexander Dr.

8055 Graz (AT)

Preiner Erich

8770 St. Michael (AT)

Krivec Thomas Dipl.Ing.

8740 Zeltweg (AT)

(74) Vertreter:

PATENTANWALTSKANZLEI MATSCHNIG &

FORSTHUBER OG

WIEN

## (54) Verfahren zum Ankontaktieren und Umverdrahten

(57) Ein Verfahren zum Ankontaktieren und Umverdrahten eines in eine Leiterplatte (2) eingebetteten elektronischen Bauteils (1) ist gekennzeichnet durch die folgenden Schritte:

Auftragen einer ersten Permanentresistschicht (9) auf eine Kontaktseite (8) der Leiterplatte (2),

Strukturieren der ersten Permanentresistschicht (11) zum Herstellen von Freistellungen (10, 12) im Bereich von Kontakten (7) des elektronischen Bauteils (1),

Auftragen einer zweiten Permanentresistschicht (11) auf die strukturierte erste Permanentresistschicht (9),

Strukturieren der zweiten Permanentresistschicht (11) zum Freilegen der Freistellungen (10) im Bereich der Kontakte (7) und zum Herstellen von Freistellungen (12) entsprechend den gewünschten Leiterzügen (15),

Chemisches Beschichten der Freistellungen (10, 12) mit Kupfer,

Galvanisches Auffüllen der Freistellungen (10, 12) mit Kupfer,

Abtragen von Kupferüberschuss in den Bereichen zwischen den Freistellungen (10, 12).

Fig. 1i

## Beschreibung

[0001] Die Erfindung betrifft ein Verfahren zum Ankontakteieren und Umverdrahten eines in eine Leiterplatte eingebetteten elektronischen Bauteils sowie eine entsprechende Leiterplatte.

[0002] Bei Leiterplatten für die Montage und elektrische Verbindung von Halbleiterelementen besteht die Tendenz zu einem immer höheren Grad der Miniaturisierung, wobei die Halbleiterelemente zunehmend platzsparend in die Leiterplatte integriert und nicht auf deren Oberfläche festgelegt werden. Die Halbleiterelemente werden hierbei derart in das elektrisch isolierende Leiterplattenmaterial - in aller Regel ein Prepreg-Material wie zum Beispiel FR4- Material - eingebettet, dass das gesamte Volumen des Halbleiterelements im Querschnitt der Leiterplatte aufgenommen ist und lediglich die Kontakte bzw. Anschlüsse des Halbleiterelements an der Kontaktseite der Leiterplatte im Wesentlichen plan an der Oberfläche der Leiterplatte freiliegen und somit für die Verdrahtung des Halbleiterelements durch auf der Leiterplatte ausgebildete Leiterzüge aus einem elektrisch leitenden Material, wie zum Beispiel Kupfer oder Aluminium, zugänglich sind. Derartige Leiterplatten mit integrierten Halbleiterelementen weisen zumeist eine Vielzahl von einander abwechselnden elektrisch isolierenden und zur Ausbildung von Leiterzügen strukturierten elektrisch leitenden Schichten auf, die in einem sequentiellen Verfahren übereinander laminiert werden, sodass die eingebetteten Halbleiterelemente vor dem Ankontakteieren in der Regel durch eine Vielzahl solcher Schichten überdeckt sind.

[0003] Gemäß den bekannten Vorgehensweisen aus dem Stand der Technik werden die derart verdeckten Kontakte bzw. Anschlüsse der Halbleiterelemente mit einem Laserschneidverfahren freigelegt, bei dem ein Laserstrahl die über den Kontakten bzw. Anschlässen der Halbleiterelemente gelegenen Schichten aus isolierendem Material von der Oberfläche der Leiterplatte bis zum Metall des Kontakts hinunterschneidet, woraufhin die dabei gebildeten Freistellungen mit Kupfer oder einem anderen elektrischen Leiter verfüllt werden, um die Ankontakteierung zu bewerkstelligen.

[0004] Das Laserschneidverfahren ist jedoch insofern nachteilig, als die durch den Laser eingebrachte Wärme bei immer kleineren Halbleiterelementen und folglich immer kleineren Leiterplatten zu Beschädigungen der empfindlichen Halbleiterelemente führen kann.

[0005] Es ist daher Aufgabe der vorliegenden Erfindung, ein Verfahren der eingangs genannten Art anzugeben, mit dem auch bei sehr kleinbauenden Halbleiterelementen und entsprechend dimensionierten Leiterplatten eine präzise Ankontakteierung und Verdrahtung der Halbleiterelemente auf der Leiterplatte erfolgen kann, wobei ein übermäßiger Hitzeeintrag in die Leiterplatte und damit einhergehend eine Schädigung der Halbleiterelemente vermieden werden soll. Diese Aufgabe wird mit einem Verfahren gelöst, welches erfindungsgemäß durch die folgenden Schritte gekennzeichnet ist:

[0006] Auftragen einer ersten Permanentresistschicht auf eine Kontaktseite der Leiterplatte,

[0007] Strukturieren der ersten Permanentresistschicht zum Herstellen von Freistellungen im Bereich von Kontakten des elektronischen Bauteils

[0008] Auftragen zumindest einer zweiten Permanentresistschicht auf die strukturierte erste Permanentresistschicht

[0009] Strukturieren der zweiten Permanentresistschicht zum Freilegen der Freistellungen im Bereich der Kontakte und zum Herstellen von Freistellungen entsprechend den gewünschten Leiterzügen.

[0010] Chemisches Beschichten der Freistellungen mit Kupfer

[0011] Galvanisches Auffüllen der Freistellungen mit Kupfer

[0012] Abtragen von Kupferüberschuss in den Bereichen zwischen den Freistellungen.

[0013] Es ist somit bei dem erfindungsgemäßen Verfahren vorgesehen, die Freistellungen für das Ankontakteieren und Verdrahten der Halbleiterelemente anstatt in herkömmlichen isolieren-

den Schichten aus Prepreg-Material wie zum Beispiel FR4 in Schichten aus Permanentresist auszubilden, sodass keine Notwendigkeit besteht, über den Kontakten bzw. Anschlüssen der Halbleiterelement liegende Schichten durch Laserschneiden zu entfernen, sondern lediglich der Permanentresist durch Belichten, Entwickeln und Entfernen bzw. Strippen der entwickelten Bereiche strukturiert werden muss. Der Fotolack bzw. Permanentresist verbleibt hierbei in den nicht strukturierten Bereichen auf der fertigen Leiterplatte und dient in jenen Lagen der Leiterplatte, in denen die Ankontaktierung und die Verdrahtung bzw. Entflechtung der Halbleiterelemente erfolgt, folglich als Dielektrikum anstelle des herkömmlichen Prepreg-Materials wie zum Beispiel FR4 oder auch Polyimid. Dadurch, dass das Laserschneidverfahren entfallen kann, wird eine Beschädigung der Leiterplatte und der darin eingebetteten Halbleiterelement vermieden.

**[0014]** Um den Platz auf der Leiterplatte besser für die Umverdrahtung von elektronischen Bauelementen wie Halbleiterelementen zu nutzen, ist die Erfindung bevorzugt dahingehend weitergebildet, dass der Schritt des Auftragens zumindest einer zweiten Permanentresistschicht zusätzlich das Auftragen einer Permanentresistschicht auf die der Kontaktseite der Leiterplatte gegenüberliegende Seite der Leiterplatte umfasst. Im darauffolgenden Schritt des Strukturierens der zweiten Permanentresistschicht wird auch diese Permanentresistschicht strukturiert, um auch auf der der Kontaktseite der Leiterplatte gegenüberliegenden Seite der Leiterplatte Leiterzüge auszubilden. Das Resultat dieser bevorzugten Verfahrensführung ist daher eine Leiterplatte mit strukturierten elektrisch leitenden Schichten zu beiden Seiten der Leiterplatte, wobei die elektrisch leitenden Schichten durch Verfüllen der Freistellungen in einem Permanentresist bzw. Fotolack hergestellt sind.

**[0015]** Herkömmlicher Weise werden Permanentresist-Materialien dergestalt belichtet, dass die kontinuierliche Fotolack-Schicht mit einer lichtundurchlässigen Maske bedruckt, danach belichtet und einer chemischen Behandlung unterzogen wird, bei der je nach Art Lacks die unbelichteten oder die belichteten Bereich bestehen bleiben und die verbleibenden Bereiche entfernt werden. Bei den sogenannten Positivlacken bleiben die verdeckten und somit unbelichteten Bereiche bestehen, während bei den sogenannten Negativlacken, die unverdeckten und somit belichteten Bereiche bestehen bleiben. Das Aufdrucken der Maske ist hierbei ein relativ aufwendiger Prozessschritt, weswegen es in Anwendung einer demgegenüber verbesserten und daher bevorzugten Ausführungsform der vorliegenden Erfindung vorgesehen ist, dass das Strukturieren der Permanentresistschichten das Belichten der Permanentresistschichten mit einem Laser umfasst. Hierbei wird ein Laserstrahl entsprechend dem gewünschten Belichtungsbild über die kontinuierliche Permanentresistschicht gelenkt, sodass das Aufbringen einer photolithographischen Maske entfallen kann.

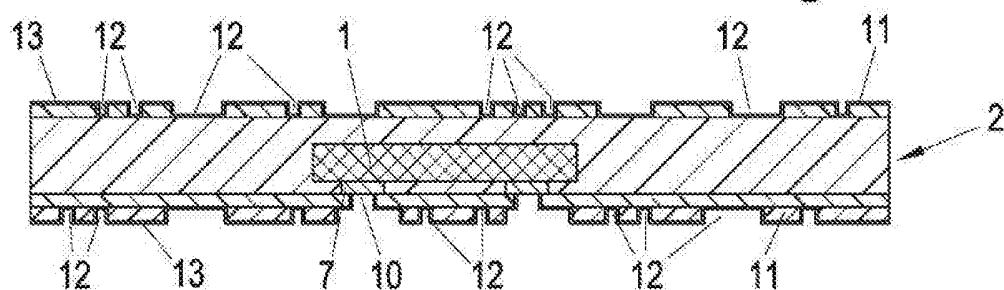

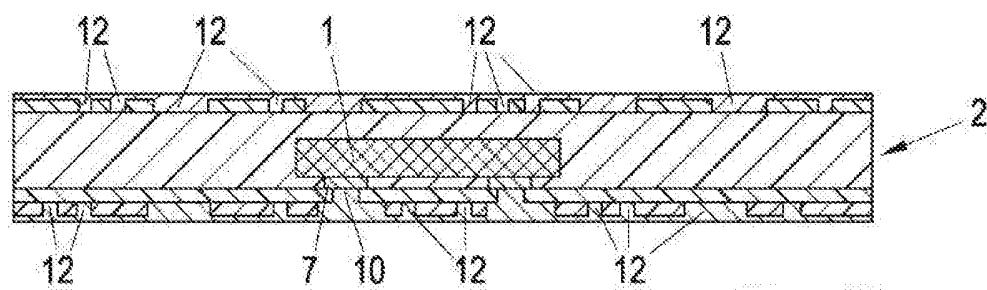

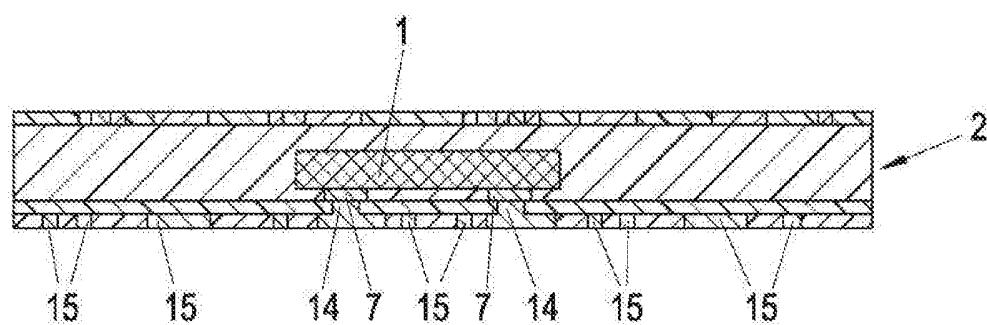

**[0016]** Die Erfindung wird nachfolgend anhand eines in der Zeichnung dargestellten Ausführungsbeispiels näher erläutert. In dieser zeigen die Figuren 1a) bis 1i) schematische Schnittdarstellungen der einzelnen erfindungsgemäßen Verfahrensschritte. Um Wiederholungen zu vermeiden, sind in den Zeichnungen gleiche Teile der Leiterplatte mit gleichen Bezugszeichen versehen.

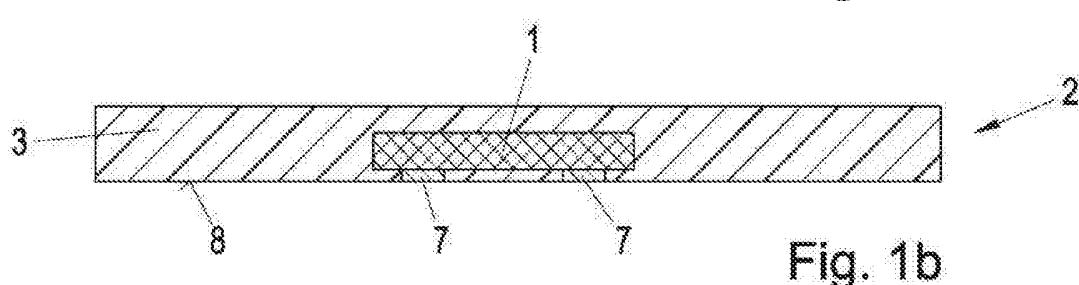

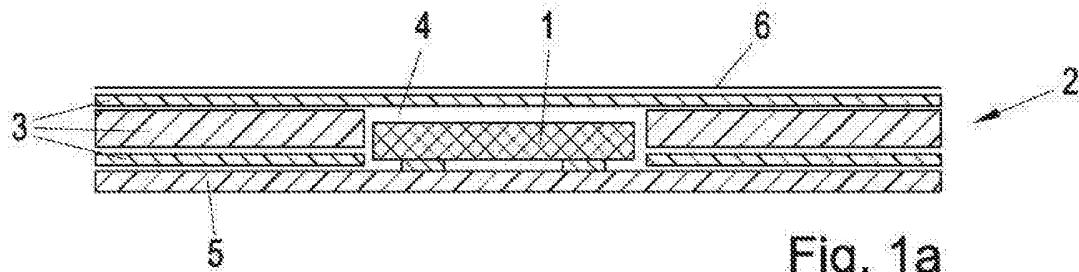

**[0017]** In Fig. 1a) ist ein Halbleiterelement mit 1 bezeichnet. Das Halbleiterelement 1 ist innerhalb des Querschnitts der Leiterplatte 2 aufgenommen. In Fig. 1a) ist die Leiterplatte vor einem Laminierungsschritt dargestellt und es ist zu erkennen, dass die einzelnen Prepreg-Schichten 3 eine Ausnehmung 4 ausbilden, in das Halbleiterelement 1 aufgenommen ist. In dem Zustand in Fig. 1a) ist das Harz der einzelnen Prepreg-Schichten noch nicht verflossen und auch noch nicht ausgehärtet. Da das Halbleiterelement bei diesem speziellen Herstellungsverfahren nicht in bereits gehärtete Prepreg-Schichten eingeklebt, sondern mit diesen durch das Harz der Prepreg-Schichten vergossen wird, ist es notwendig, das Halbleiterelement 1 vor dem Laminieren, bei dem es zum Aushärten der Prepregs kommt, mithilfe eines Klebebandes 5 in der Ausnehmung 4 temporär festzulegen. Zum Laminieren wird zusätzlich eine Folie aufgebracht. Nach dem Laminieren dieses Verbundes und Entfernen des Klebebandes 5 sowie der Folie 6 erhält man das Produkt gemäß Figur 1 b), bei dem die Prepreg-Schichten 3 zu einer praktisch homogenen Prepreg-Schicht 3 verflossen und in der Folge ausgehärtet sind. Das Halbleiterelement 1

definiert mit seinen freiliegenden Kontakten 7 eine Kontaktseite 8 der Leiterplatte 2, auf der das Ankontaktieren und Verdrahten des Halbleiterelements 1 erfolgt.

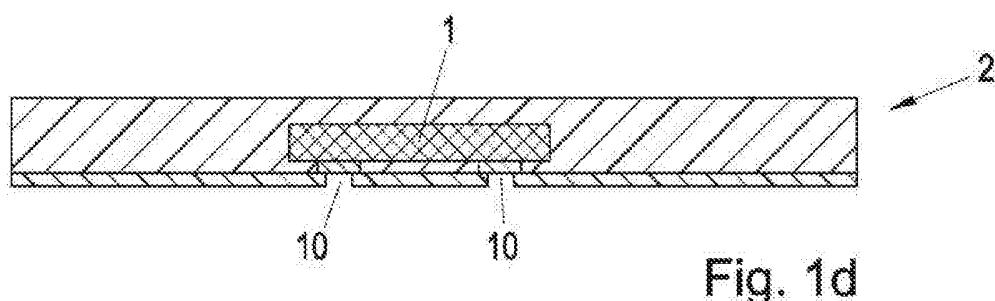

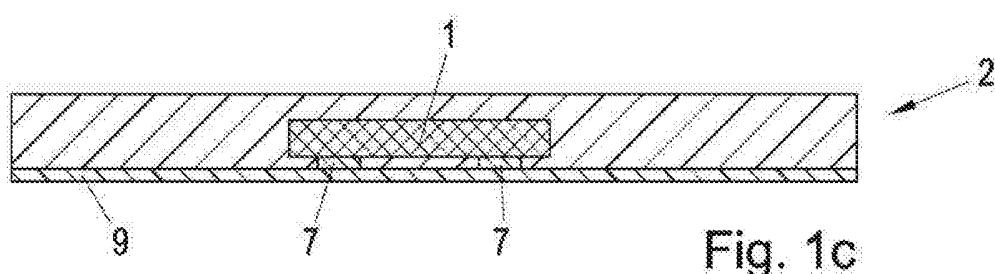

**[0018]** Gemäß der Darstellung in Fig. 1 c) wird nun eine erste Permanentresistschicht 9 auf die Kontaktseite 8 der Leiterplatte 2 aufgebracht und durch Belichten, Entwickeln und Strippen strukturiert, wobei Freistellungen 10 gebildet werden, die die Kontakte 7 für das später erfolgende Ankontaktieren zugänglich machen (Fig. 1 d)). Das Belichten kann hierbei, wie oben beschrieben, mit einem Laser erfolgen. Beim Entwickeln der ersten Permanentresistschicht wird der verbleibende Fotolack chemisch derart verändert, dass nach einer erneuten Belichtung desselben Materials keine Entwicklung mehr erfolgt.

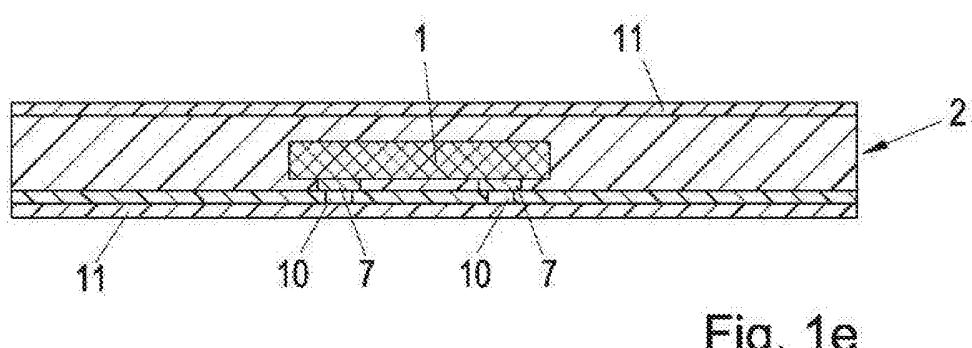

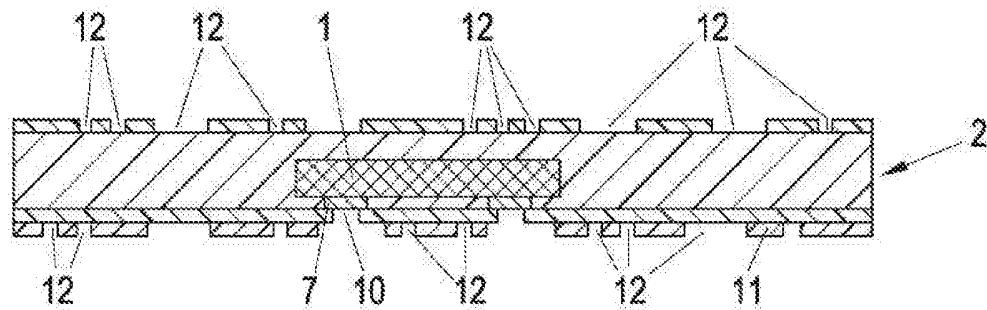

**[0019]** Anschließend wird eine zweite Permanentresistschicht 11 aufgetragen (Fig. 1 e)), die die im oben beschriebenen Schritt gebildeten Freistellungen 10 zwar zumindest teilweise wieder verschließt, jedoch vor allem die Möglichkeit schafft, durch geeignetes Strukturieren dieser frischen, zweiten Permanentresistschicht 11 Freistellungen 12 entsprechend den gewünschten Leiterzügen zu schaffen (Fig. 1 f)), wobei hier hervorgehoben wird, dass in diesem Fall der Schritt des Auftragens einer zweiten Permanentresistschicht 11 zusätzlich das Auftragen einer Permanentresistschicht 11 auf die der Kontaktseite 8 der Leiterplatte 2 gegenüberliegende Seite der Leiterplatte 2 umfasst.

**[0020]** Hierauf erfolgt der Schritt des chemischen Verkupferns der Freistellungen 10 und 12, wobei eine dünne Kupferschicht 13 auf dem Permanentresistmaterial und insbesondere in den Freistellungen 10 und 12 abgelagert wird (Fig. 1 g). Nun kann das galvanische Auffüllen der Freistellungen 10 und 12 mit Kupfer erfolgen, wodurch ein Produkt wie in Fig. 1 h) dargestellt erhalten wird. Schließlich muss das überschüssige Kupfer in den Bereichen zwischen den Freistellungen 10 und 12 abgetragen werden, um die fertige Leiterplatte 2 zu erhalten (Fig. 1 i). Die Ankontakteierungen 14 der Kontakte 7 der Halbleiterelement 1 und die Leiterzüge 15 wurden mit dem erforderlichen Verfahren ausgebildet, ohne das Halbleiterelement 1 übermäßig zu erhitzen.

**[0021]** Es ist selbstverständlich, dass die so erhaltene Leiterplatte weiteren Bearbeitungsschritten unterworfen werden kann, ohne vom Geist der hierin dargelegten Erfindung abzuweichen.

## Patentansprüche

1. Verfahren zum Ankontaktieren und Umverdrahten eines in eine Leiterplatte (2) eingebetteten elektronischen Bauteils (1) **gekennzeichnet durch** die folgenden Schritte:

Auftragen einer ersten Permanentresistschicht (9) auf eine Kontaktseite (8) der Leiterplatte (2),

Strukturieren der ersten Permanentresistschicht (9) zum Herstellen von Freistellungen (10) im Bereich von Kontakten (7) des elektronischen Bauteils (1),

Auftragen einer zweiten Permanentresistschicht (11) auf die strukturierte erste Permanentresistschicht (9),

Strukturieren der zweiten Permanentresistschicht (11) zum Freilegen der Freistellungen (10) im Bereich der Kontakte (7) und zum Herstellen von Freistellungen (12) entsprechend den gewünschten Leiterzügen (15),

Chemisches Beschichten der Freistellungen (10, 12) mit Kupfer,

Galvanisches Auffüllen der Freistellungen (10, 12) mit Kupfer,

Abtragen von Kupferüberschuss in den Bereichen zwischen den Freistellungen (10).

2. Verfahren nach Anspruch 1, **dadurch gekennzeichnet**, dass der Schritt des Auftragens einer zweiten Permanentresistschicht (11) zusätzlich das Auftragen einer Permanentresistschicht (11) auf die der Kontaktseite (8) der Leiterplatte (2) gegenüberliegende Seite der Leiterplatte (2) umfasst.

3. Verfahren nach Anspruch 1 oder 2, **dadurch gekennzeichnet**, dass das Strukturieren der Permanentresistschichten (9, 11) das Belichten der Permanentresistschichten (9, 11) mit einem Laser umfasst.

4. Leiterplatte (2) erhältlich nach einem der Ansprüche 1 bis 3.

Hierzu 2 Blatt Zeichnungen

1/2

2/2

Fig. 1f

Fig. 1g

Fig. 1h

Fig. 1i