**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

|                                                |                                                                          |

|------------------------------------------------|--------------------------------------------------------------------------|

| (51) Int. Cl. <sup>5</sup><br><u>H03K 5/00</u> | (11) 공개번호      특 1993-0011421<br>(43) 공개일자      1993년06월24일              |

| (21) 출원번호                                      | 특 1992-0021739                                                           |

| (22) 출원일자                                      | 1992년 11월 19일                                                            |

| (30) 우선권주장                                     | 795,538 1991년 11월 21일 미국(US)                                             |

| (71) 출원인                                       | 선마이크로시스템즈 인코오퍼레이티드 마이클 에이치. 모리스<br>미합중국 캘리포니아 94043 마운틴 뷰우 가르시아 애비뉴 2550 |

| (72) 발명자                                       | 제임스 테스타<br>미합중국 캘리포니아 마운틴 뷰우 #1 웨스트 미들필드 1555                            |

| (74) 대리인                                       | 라기상, 장용식                                                                 |

**심사청구 : 없음****(54) 스큐를 최소로한 다중클록 수신기용 고속클록 회로****요약**

각 클록출력당 하나씩의 개별구동기를 채용하고, 집적회로침상에 클록회로를 포함하고, 클록칩 내부의 클록신호 트레이스 길이를 일치시키고, 그리고 회로기판 클록신호 트레이스 길이를 일치시킴으로써 데이터 처리시스템내의 클록스큐문제를 해결하는 고속 클록회로가 공개된다. 클록회로는 소스클록 입력신호를 수신하여 소스클록의 1/2 주파수 및 1/4 주파수에서 다중클록출력을 발생시킨다.

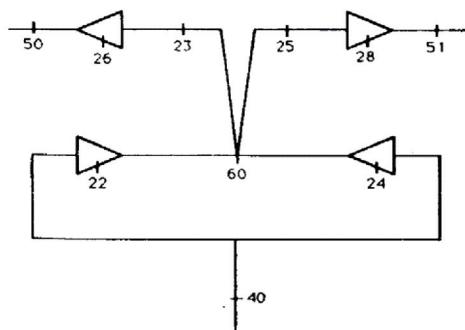

클록분배회로는 버스클록신호를 수신하고 이중구동기를 사용하여 버스클록신호를 집적회로다이상의 공통점으로 전송한다.

각 클록출력당 하나씩의 개별출력구동기가 존재한다.

다이상의 공통점으로부터, 동일한 길이의 트레이스가 각 출력구동기로 이어진다.

각 출력구동기는 출력핀을 통하여 침외의 최종 목적지로 클록출력신호를 전송하는데 필요한 신호강도를 제공한다. 클록칩의 출력핀에서 클록신호의 최종 목적지까지의 트레이스 길이는 회로기판 트레이스의 커패시턴스 및 길이의 차이에 의한 스큐를 감소시키기 위하여 일치하여야 한다.

**대표도****도1****명세서**

[발명의 명칭]

스큐를 최소로한 다중클록 수신기용 고속클록회로

[도면의 간단한 설명]

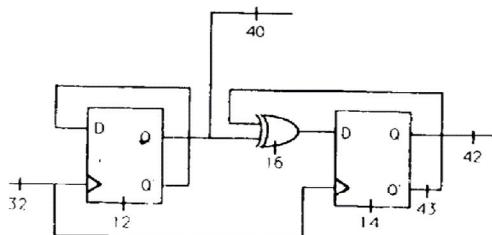

제1도는 소스클록신호를 수신하여 1/2 및 1/4 주파수 클록신호를 발생시키는데 사용되는 회로를 도시한다.

제2도는 단일클록입력으로부터 다중클록출력을 발생시키는데 사용되는 클록분배 회로의 작동을 도시한다.

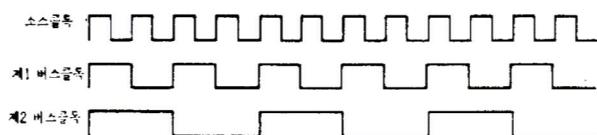

제3도는 소스클록과 제1버스클록 및 제2버스클록의 타이밍을 도시한다.

본 내용은 요구공개 건이므로 전문 내용을 수록하지 않았음

**(57) 청구의 범위****청구항 1**

입력신호의 1/2 및 1/4 주파수에서의 다수의 동기화된 출력신호를 발생시키는 집적회로침상에 제조된 회로에 있어서, 상기 회로는, 상기 입력신호를 수신하는 수신수단, 상기 입력신호에 전기적으로 연결되어, 상기 입력신호를 1/2로 나누어 제1신호를 제공하는 제1분주기 수단, 상기 제1신호에 전기적으로 연결된 각각의 입력과 집적회로침상의 제1공통점에 전기적으로 연결된 각각의 출력을 가진 한쌍의 제1구동수단, 각각 입력과 출력을 가진 다수의 제2구동수단, 상기 제1신호에 전기적으로 연결되어, 상기 제1신호의 주

파수를 1/2로 나누어 제2신호를 제공하는 제2분주기 수단, 상기 제2신호에 전기적으로 연결된 각각의 입력과 집적회로침상의 제2공통점에 전기적으로 연결된 각각의 출력을 가진 한쌍의 제3구동수단, 각각 입력과 출력을 가진 다수의 제4구동수단으로 구성되어, 상기 제2구동수단 각각의 입력은 상기 제1공통점에 전기적으로 연결되어 상기 제1공통점에서 상기 제2구동수단 각각의 입력까지의 전류이동거리가 같고, 상기 제2구동수단의 각각의 출력은 상기 제1신호와 동일한 형태를 가진 신호를 제공하고, 상기 제4구동수단 각각의 입력은 상기 제2공통점에 전기적으로 연결되어 상기 제2공통점에서 상기 제4구동수단 각각의 입력까지의 전류이동거리가 같고, 상기 제4구동수단 각각의 출력은 상기 제2신호와 동일한 형태를 가진 신호를 제공하는 것을 특징으로 하는 회로.

### 청구항 2

입력신호와 동일한 형태의 다수의 동기화된 출력신호를 발생시키는 집적회로침상에 제조된 회로에서, 상기 회로는, 상기 입력신호를 수신하는 수신수단, 상기 입력신호에 전기적으로 연결된 각각의 입력과, 집적회로다이상의 공통점에 전기적으로 연결된 각각의 출력을 가진 한쌍의 제1구동수단, 입력과 출력을 각각 가진 다수의 제2구동수단으로 구성되어, 상기 제2구동수단 각각의 입력은 상기 공통점에 전기적으로 연결되어, 상기 공통점에서 상기 제2구동수단 각각의 입력까지의 전류이동거리가 같고, 상기 제2구동수단 각각의 출력은 상기 입력신호와 동일한 형태를 가진 신호를 제공하는 것을 특징으로 하는 회로.

### 청구항 3

제1항에 있어서, 상기 제1분주기 수단은 제1 D-Q 래치로 구성되고 상기 제2분주기 수단은 제2 D-Q래치로 구성되는 것을 특징으로 하는 회로.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

### 도면

#### 도면1

#### 도면2

#### 도면3