(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6422310号

(P6422310)

(45) 発行日 平成30年11月14日(2018.11.14)

(24) 登録日 平成30年10月26日(2018.10.26)

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| (51) Int.Cl.  | F 1       |        |       |         |

| HO 1 L 29/786 | (2006.01) | HO 1 L | 29/78 | 6 1 6 T |

| HO 1 L 21/336 | (2006.01) | HO 1 L | 29/78 | 6 1 6 U |

| HO 1 L 21/28  | (2006.01) | HO 1 L | 29/78 | 6 1 6 K |

| HO 1 L 29/417 | (2006.01) | HO 1 L | 29/78 | 6 1 8 B |

| GO 2 F 1/1368 | (2006.01) | HO 1 L | 29/78 | 6 1 2 D |

請求項の数 12 (全 19 頁) 最終頁に続く

|           |                              |           |                                                |

|-----------|------------------------------|-----------|------------------------------------------------|

| (21) 出願番号 | 特願2014-229474 (P2014-229474) | (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号     |

| (22) 出願日  | 平成26年11月12日(2014.11.12)      | (74) 代理人  | 100088672<br>弁理士 吉竹 英俊                         |

| (65) 公開番号 | 特開2016-96171 (P2016-96171A)  | (74) 代理人  | 100088845<br>弁理士 有田 貴弘                         |

| (43) 公開日  | 平成28年5月26日(2016.5.26)        | (72) 発明者  | 木稻 貴治<br>熊本県合志市御代志997番地 メルコ・ディスプレイ・テクノロジー株式会社内 |

| 審査請求日     | 平成29年11月8日(2017.11.8)        | 審査官       | 市川 武宜                                          |

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板、その製造方法、及び、液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁基板と、

前記絶縁基板上に配設されたゲート電極と、

前記ゲート電極を覆う第1絶縁膜と、

前記ゲート電極上に前記第1絶縁膜を介して配設された、酸化物半導体からなる半導体膜と、

前記半導体膜を覆う第2絶縁膜と、

前記第2絶縁膜の一端上に配設された、酸化物導電体以外の導電体からなる第1ソース電極と、

前記第2絶縁膜の他端上に配設された、酸化物導電体以外の導電体からなる第1ドレイン電極と、

前記第1ソース電極上に配設され、前記第1ソース電極及び前記第2絶縁膜に設けられた第1コンタクトホールを介して前記半導体膜と接続された、酸化物導電体からなる第2ソース電極と、

前記第1ドレイン電極上に配設され、前記第1ドレイン電極及び前記第2絶縁膜に設けられた第2コンタクトホールを介して前記半導体膜と接続された、酸化物導電体からなる第2ドレイン電極と、

前記第2ドレイン電極の一部を延設して形成された画素電極と、

前記第1絶縁膜と、前記第2ソース電極と、前記第2ドレイン電極と、前記画素電極と

10

20

を覆う第3絶縁膜と

を備える、薄膜トランジスタ基板。

【請求項2】

請求項1に記載の薄膜トランジスタ基板であって、

前記絶縁基板上に配設され、前記第1絶縁膜により覆われる共通配線と、

前記画素電極上に第3絶縁膜を介して配設され、前記第1絶縁膜及び前記第3絶縁膜に

設けられた第3コンタクトホールを介して前記共通配線と接続されるとともに、横方向の

電界を前記画素電極との間に発生することが可能な対向電極と

をさらに備える、薄膜トランジスタ基板。

【請求項3】

請求項1または請求項2に記載の薄膜トランジスタ基板であって、

前記半導体膜は、

平面視において前記ゲート電極の外周よりも内側に配設された、薄膜トランジスタ基板

。

【請求項4】

請求項2に記載の薄膜トランジスタ基板であって、

前記画素電極は、前記第1絶縁膜上に配設され、

前記画素電極の少なくとも一部は、

平面視において前記共通配線の少なくとも一部と重なる、薄膜トランジスタ基板。

【請求項5】

請求項1に記載の薄膜トランジスタ基板と、

前記薄膜トランジスタ基板と対向配置された対向基板とを備え、

前記画素電極と、前記薄膜トランジスタ基板または前記対向基板に配設された対向電極

との間に発生する電界によって液晶を駆動する、液晶表示装置。

【請求項6】

ゲート電極と、前記ゲート電極上に第1絶縁膜を介して酸化物半導体膜とが形成された

絶縁基板を用意する工程と、

前記酸化物半導体膜上に当該酸化物半導体膜を覆うように絶縁層を形成する工程と、

前記絶縁層を介して前記酸化物半導体膜を覆う導電膜を形成する工程と、

少なくとも前記酸化物半導体膜上に一部が残るように前記絶縁層及び前記導電膜を1回

の写真製版でパターニングすることによって、前記酸化物半導体膜上に第2絶縁膜を、前

記第2絶縁膜上に電極体を形成する工程と、

前記電極体を形成する工程後に、前記電極体を分離することによって、前記第2絶縁膜

上で離間する第1ソース電極及び第1ドレイン電極を形成する工程と

を備える、薄膜トランジスタ基板の製造方法。

【請求項7】

請求項6に記載の薄膜トランジスタ基板の製造方法であって、

一回の写真製版の間に、第2ソース電極、第2ドレイン電極及び画素電極をパターニン

グによって形成するとともに前記電極体を分離するパターニングを行うことによって、前

記第1ソース電極及び前記第1ドレイン電極を形成する工程を行う、薄膜トランジスタ基

板の製造方法。

【請求項8】

請求項6または請求項7に記載の薄膜トランジスタ基板の製造方法であって、

前記電極体を形成する工程にて、前記絶縁層及び前記電極体に、前記酸化物半導体膜の

一部を露出する第1及び第2コンタクトホールをエッティングによって形成し、

前記第1ソース電極上から前記第1コンタクトホールを介して前記酸化物半導体膜上に

延在する酸化物導電体からなる第2ソース電極を形成するとともに、前記第1ドレイン電

極上から前記第2コンタクトホールを介して前記酸化物半導体膜上に延在する酸化物導電

体からなる第2ドレイン電極を形成する工程をさらに備える、薄膜トランジスタ基板の製

造方法。

10

20

30

40

50

## 【請求項 9】

請求項 6 に記載の薄膜トランジスタ基板の製造方法であって、

前記電極体を形成する工程において形成される前記電極体は、前記第 1 ソース電極が形成されるソース電極形成領域から前記第 1 ドレイン電極が形成されるドレイン電極形成領域にわたって一体に形成された導電膜からなる、薄膜トランジスタ基板の製造方法。

## 【請求項 10】

請求項 8 に記載の薄膜トランジスタ基板の製造方法であって、

前記第 2 ドレイン電極の形成とともに、前記第 2 ドレイン電極と一体化された酸化物導電体からなる画素電極を形成する、薄膜トランジスタ基板の製造方法。

## 【請求項 11】

10

請求項 6 に記載の薄膜トランジスタ基板の製造方法であって、

前記第 1 ソース電極及び前記第 1 ドレイン電極は、酸化物導電体以外の導電体からなる、薄膜トランジスタ基板の製造方法。

## 【請求項 12】

請求項 7, 8, 10 のうちのいずれか 1 項に記載の薄膜トランジスタ基板の製造方法であって、

前記第 2 ドレイン電極に電気的に接続される画素電極を形成する工程と、前記画素電極上に第 3 絶縁膜を形成し、当該第 3 絶縁膜上に対向電極を形成する工程とをさらに備える、薄膜トランジスタ基板の製造方法。

## 【発明の詳細な説明】

20

## 【技術分野】

## 【0001】

本発明は、薄膜トランジスタ基板、その製造方法、及び、液晶表示装置に関する。

## 【背景技術】

## 【0002】

薄膜トランジスタ (Thin Film Transistor : 以下「TFT」) をスイッチング素子として備えた TFT アクティブマトリックス基板 (薄膜トランジスタ基板 : 以下「TFT 基板」) は、例えば液晶を利用した表示装置 (液晶表示装置) 等の電気光学装置に利用される。TFT 等の半導体装置は、低消費電力で薄型という特徴があり、この特徴を活かして、CRT (Cathode Ray Tube) の代わりに用いられるようになってきており、フラットパネルディスプレイに対する TFT 等の応用が盛んになされている。

30

## 【0003】

液晶表示装置 (Liquid Crystal Display : 以下「LCD」と記すこともある) 用の電気光学素子には、単純マトリックス型 LCD と、TFT をスイッチング素子として備える TFT - LCD とがある。特に TFT - LCD は、携帯性及び表示品位の点で CRT や単純マトリックス型 LCD より優れており、ノート型パソコンや TV などのディスプレイ製品に広く実用化されている。

## 【0004】

40

一般に、TFT - LCD は、アレイ状に配設された複数の TFT を備えた TFT 基板と、カラーフィルタ等を備えた対向基板との間に液晶層が挟持された構造の液晶表示パネルを有している。液晶表示パネルの前面側及び背面側のそれぞれに偏光板が設けられ、さらにそのうちの一方側にはバックライトが設けられる。この構造によって良好なカラー表示が得られる。

## 【0005】

従来の TFT - LCD の視野角を改善した横電界の液晶駆動方式である IPS (In Plane Switching) (登録商標) 方式の LCD は、広視野角という特徴を活かして、表示装置等に広く使用されている。しかし、画素表示部での開口率の低さや透過率の低さといった問題を有しており、明るい表示特性を得ることが困難である。明るい表示特性を困難にする主な理由は、IPS - LCD に用いられる櫛歯形状の画素電極の上方で、液晶を駆動させるための電界が有効に働くかず、画素電極の上方に位置する液晶の一部が駆動しないため

50

であると考えられる。この問題を改善するために、例えば特許文献1に開示されているようなFFS (Fringe Field Switching: フリンジ電界駆動) 方式のLCDが提案されている。

#### 【0006】

さて、従来、液晶表示装置用のTFT基板のスイッチング素子では、活性層（チャネル層）としての半導体膜にアモルファスシリコン（Si）が用いられていた。これに対して、近年では、活性層に酸化物半導体を用いたTFTの開発が盛んになされている。酸化物半導体は、従来のアモルファスシリコンよりも高い移動度を有している。酸化物半導体としては、酸化亜鉛（ZnO）系材料や、酸化亜鉛に酸化ガリウム（Ga<sub>2</sub>O<sub>3</sub>）及び酸化インジウム（In<sub>2</sub>O<sub>3</sub>）を添加した非晶質のInGaZnO系材料が主に用いられている。この技術は、例えば特許文献1, 2及び非特許文献1等に開示されている。

#### 【0007】

酸化物半導体は、透明導電体である非晶質ITO（酸化インジウム（In<sub>2</sub>O<sub>3</sub>）+酸化すず（SnO<sub>2</sub>））や非晶質InZnO（酸化インジウム（In<sub>2</sub>O<sub>3</sub>）+酸化亜鉛（ZnO））のような酸化物導電体と同様に、シュウ酸やカルボン酸のような弱酸系溶液でエッティングすることが可能であり、パターン加工が容易であるという利点がある。

#### 【0008】

しかしながら、酸化物半導体は、TFTのソース電極やドレイン電極となる一般的な金属膜のエッティング加工に用いられる酸系溶液によってエッティングダメージを受け、その特性が劣化してしまうことがある。あるいは、酸化物半導体の材料の種類によっては、これらの酸系溶液に溶けてしまうことがある。したがって、例えば特許文献3のような、酸化物半導体膜の上層にソース電極やドレイン電極を配設したTFT（一般的にバックチャネル（BCE）型と呼ばれる）を製造する場合は、ソース電極やドレイン電極を加工するときに酸系溶液によってチャネル層の酸化物半導体膜がダメージを受け、TFTの特性が劣化してしまうことがあった。さらには、ソース電極やドレイン電極となる金属膜を成膜するときの界面での酸化還元反応によりチャネル層の酸化物半導体膜がダメージを受け、TFTの特性を劣化させてしまうことがあった。

#### 【0009】

この問題を解決するためには、特許文献4や特許文献5のような、半導体層の上層に半導体層を保護する保護層が配設されたTFT構造を適用することが考えられる。このようなTFT構造は、ソース電極及びドレイン電極の金属膜をエッティング加工するときの酸化物半導体膜のダメージやエッティングによる消失を抑制することができる。なお、この構造は、この作用に鑑みて、一般的にエッティングストッパーまたはエッチストッパー（ES）型TFTと呼ばれる。

#### 【先行技術文献】

##### 【特許文献】

##### 【0010】

【特許文献1】特開2001-56474号公報

【特許文献2】特開2005-77822号公報

【特許文献3】特開2007-281409号公報

【特許文献4】特開昭62-235784号公報

【特許文献5】国際公開第2011/077607号

##### 【非特許文献】

##### 【0011】

【非特許文献1】Kenji Nomura, et al, 「Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors」、Nature、2004年、第432巻、p. 488-492

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0012】

10

20

30

40

50

しかしながら、特許文献1などに開示された一般的なFFS-LCDのTFTをエッチストッパー型のTFT構造にする場合には、酸化物半導体層の上に保護層を形成するための専用の写真製版工程を新たに追加する必要がある。つまり、当該写真製版工程を製造工程に追加する必要があることから、生産能力を低下させ、製造コストの増加を招くといった問題がある。なお、このエッチストッパー型のTFT構造を採用することによる製造コストの増加は、FFS-LCDのみならず、酸化物半導体を活性層とするTFTをスイッチング素子に用いたLCDに共通する課題である。

#### 【0013】

また、スパッタリング法や真空蒸着法により、ソース電極及びドレイン電極となる一般的な金属膜を酸化物半導体膜の上に直接形成する場合、半導体膜のチャネル層（領域）がエッチストッパー層で保護された状態であっても、半導体膜のうち、ソース電極及びドレイン電極と電気的に接続されるソース領域及びドレイン領域において、界面反応（酸化還元反応）が生じることがある。この場合、酸化物半導体膜における還元反応の影響が、チャネル領域を含む半導体層全体に波及してTFTの特性が劣化してしまうこともある。

10

#### 【0014】

そこで、本発明は、上記のような問題点を鑑みてなされたものであり、薄膜トランジスタの特性を高めることが可能な技術を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0015】

本発明に係る薄膜トランジスタ基板は、絶縁基板と、前記絶縁基板上に配設されたゲート電極と、前記ゲート電極を覆う第1絶縁膜と、前記ゲート電極上に前記第1絶縁膜を介して配設された、酸化物半導体からなる半導体膜と、前記半導体膜を覆う第2絶縁膜とを備える。また、前記薄膜トランジスタ基板は、前記第2絶縁膜の一端上に配設された、酸化物導電体以外の導電体からなる第1ソース電極と、前記第2絶縁膜の他端上に配設された、酸化物導電体以外の導電体からなる第1ドレイン電極と、前記第1ソース電極上に配設され、前記第1ソース電極及び前記第2絶縁膜に設けられた第1コンタクトホールを介して前記半導体膜と接続された、酸化物導電体からなる第2ソース電極と、前記第1ドレイン電極上に配設され、前記第1ドレイン電極及び前記第2絶縁膜に設けられた第2コンタクトホールを介して前記半導体膜と接続された、酸化物導電体からなる第2ドレイン電極とを備える。また、前記薄膜トランジスタ基板は、前記第2ドレイン電極の一部を延設して形成された画素電極と、前記第1絶縁膜と、前記第2ソース電極と、前記第2ドレイン電極と、前記画素電極とを覆う第3絶縁膜とを備える。

20

#### 【発明の効果】

#### 【0016】

本発明によれば、酸化物導電体からなる第2ソース電極が、第1ソース電極上に配設されて、第1ソース電極及び第2絶縁膜に設けられた第1コンタクトホールを介して半導体膜と接続されており、酸化物導電体からなる第2ドレイン電極が、第1ドレイン電極上に配設されて、第1ドレイン電極及び第2絶縁膜に設けられた第2コンタクトホールを介して半導体膜と接続されている。これにより、薄膜トランジスタの特性を高めることができる。

30

40

#### 【図面の簡単な説明】

#### 【0017】

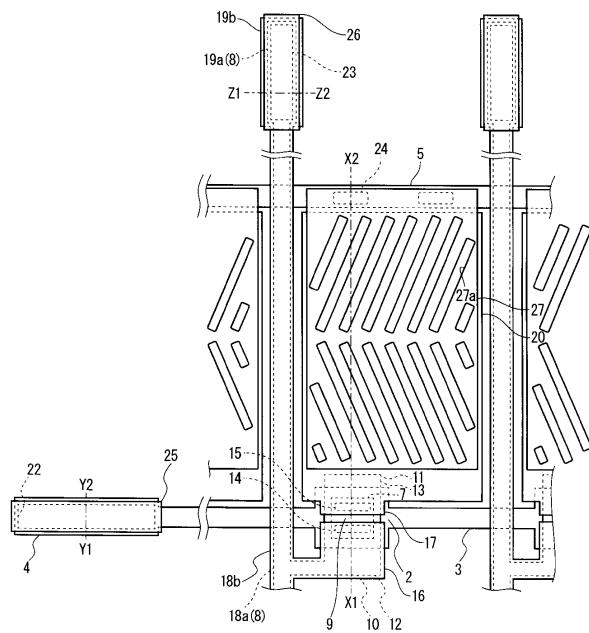

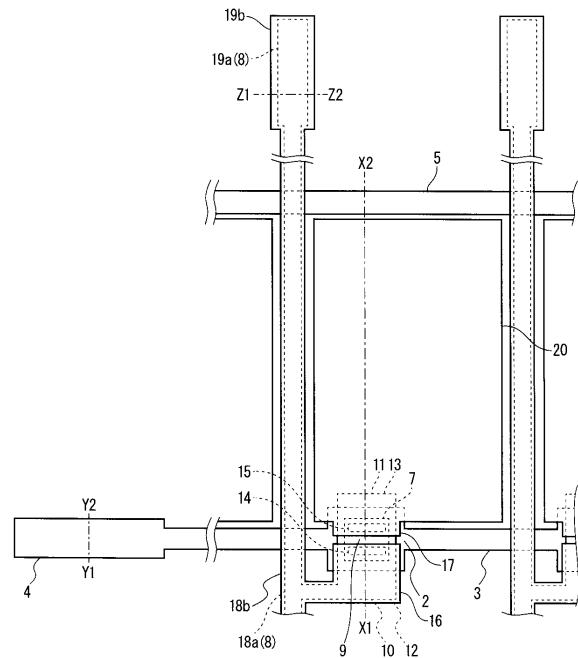

【図1】実施の形態に係るTFT基板の構成を示す平面図である。

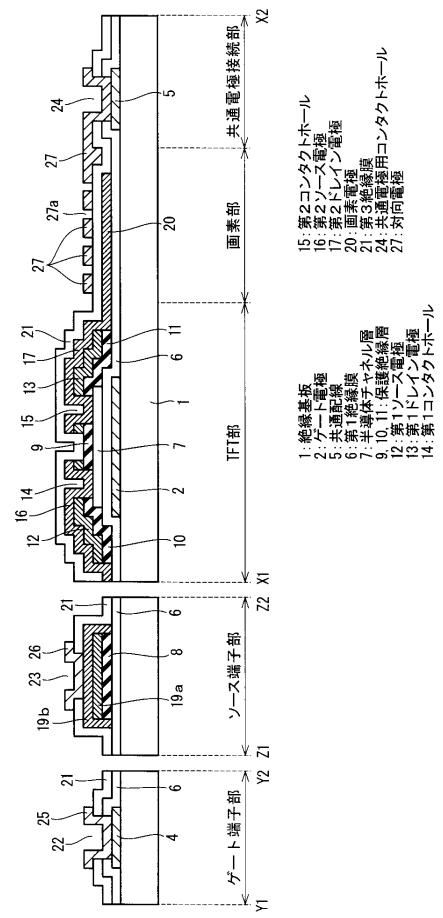

【図2】実施の形態に係るTFT基板の構成を示す断面図である。

【図3】実施の形態に係るTFT基板の第1回目の写真製版工程後の構成を示す平面図である。

【図4】実施の形態に係るTFT基板の第1回目の写真製版工程後の構成を示す断面図である。

【図5】実施の形態に係るTFT基板の第2回目の写真製版工程後の構成を示す平面図である。

50

【図6】実施の形態に係るTFT基板の第2回目の写真製版工程後の構成を示す断面図である。

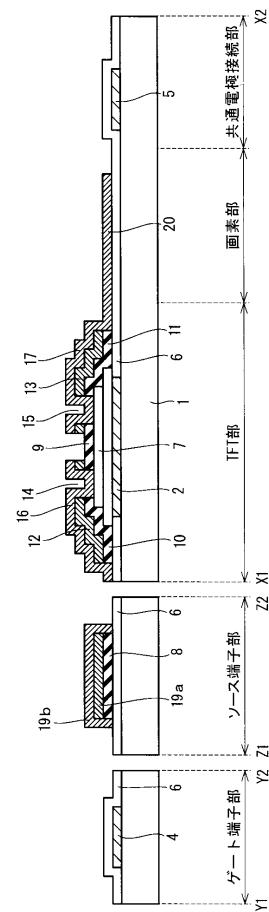

【図7】実施の形態に係るTFT基板の第3回目の写真製版工程後の構成を示す平面図である。

【図8】実施の形態に係るTFT基板の第3回目の写真製版工程後の構成を示す断面図である。

【図9】実施の形態に係るTFT基板の第4回目の写真製版工程後の構成を示す平面図である。

【図10】実施の形態に係るTFT基板の第4回目の写真製版工程後の構成を示す断面図である。

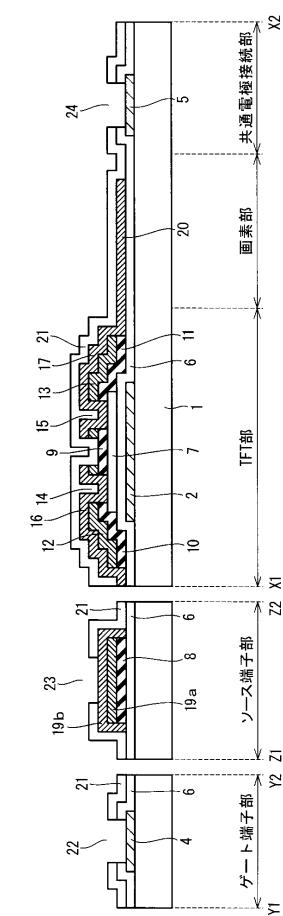

10

【図11】実施の形態に係るTFT基板の第5回目の写真製版工程後の構成を示す平面図である。

【図12】実施の形態に係るTFT基板の第5回目の写真製版工程後の構成を示す断面図である。

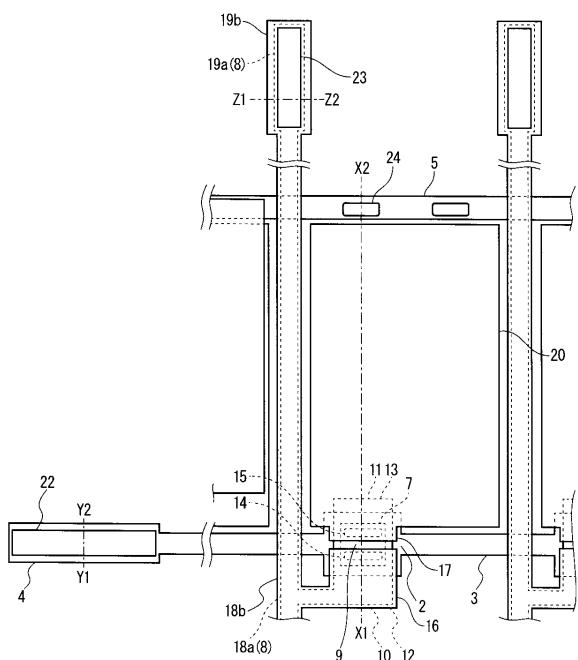

【図13】変形例に係るTFT基板の構成を示す平面図である。

【図14】変形例に係るTFT基板の構成を示す断面図である。

【発明を実施するための形態】

【0018】

<実施の形態>

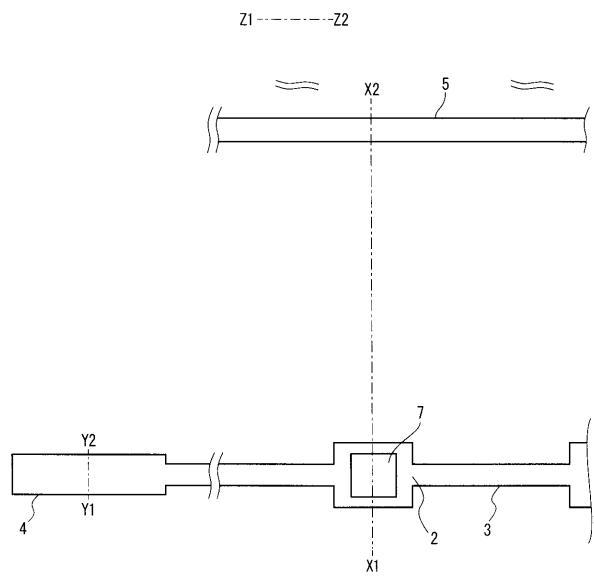

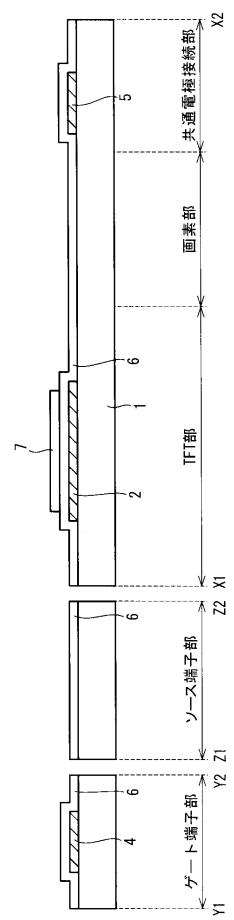

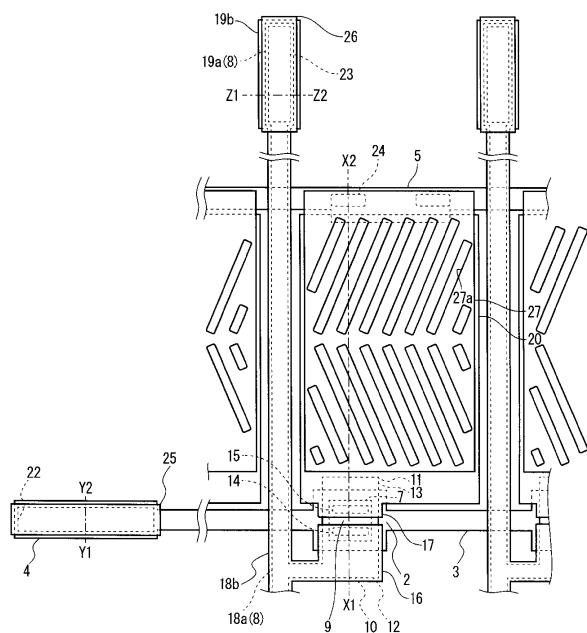

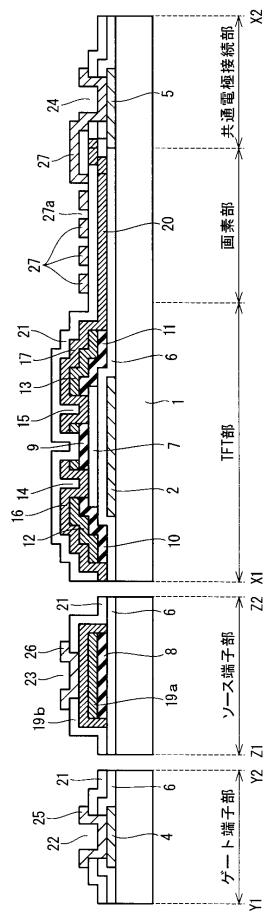

図1及び図2を参照して、本実施の形態に係るTFT基板の構成について説明する。図1は、FFS方式のTFT基板における画素部、及び、画素部（画素表示領域）外側のゲート端子部及びソース端子部の平面構成を示す図であり、図2は、その断面構成を示す図である。図2では、図1に示すX1-X2線、Y1-Y2線及びZ1-Z2線に沿った断面が示されている。X1-X2線に沿った断面は、画素の配設領域（画素部）に対応する。Y1-Y2線に沿った断面は、ゲート配線3（図2には図示せず）にゲート信号を供給するためのゲート端子4及びゲート端子パッド25の配設領域（ゲート端子部）に対応する。Z1-Z2線に沿った断面は、ソース配線18a, 18b（図2には図示せず）に表示信号を印加するためのソース端子19a, 19b及びソース端子パッド26の配設領域（ソース端子部）に対応する。

20

【0019】

30

図2に示すように、画素部は、X1-X2に沿って、TFTの配設領域である「TFT部」と、画素電極20及び対向電極27の配設領域である「透過画素部」と、対向電極27と共に接続される「共通電極接続部」とを含んでいる。

【0020】

さて、本実施の形態に係るTFT基板は、絶縁基板1と、ゲート電極2と、共通配線5と、第1絶縁膜6と、半導体膜である半導体チャネル層7と、第2絶縁膜である保護絶縁層9, 10, 11と、第1ソース電極12と、第1ドレイン電極13と、第2ソース電極16と、第2ドレイン電極17と、画素電極20と、第3絶縁膜21と、対向電極27とを備えている。以下、本実施の形態に係るTFT基板の、これら構成要素と、これら以外の構成要素（ゲート配線3等）について説明する。

40

【0021】

絶縁基板1には、例えばガラス等の透明性絶縁基板が用いられる。絶縁基板1上には、ゲート電極2、ゲート配線3、ゲート端子4及び共通配線5が配設されている。第1絶縁膜6は、ゲート電極2、ゲート配線3、ゲート端子4及び共通配線5を覆う。第1絶縁膜6は、TFT部ではゲート絶縁膜として機能するため、以下では「ゲート絶縁膜6」と記すこともある。

【0022】

なお、図1に示されるように、ゲート配線3は横方向に延在しており、ゲート電極2及びゲート端子4と電気的に接続されている。ここでは、ゲート配線3におけるTFT部の部分（ゲート配線3の一部分）がゲート電極2となっており、ゲート電極2は、ゲート配

50

線 3 の他の部分よりも幅が広くなっている。また、ゲート配線 3 におけるゲート端子部の部分（ゲート配線 3 の端部）がゲート端子 4 となっている。共通配線 5 は、ゲート配線 3 と平行に延在している。なお、図 1 及びこれ以降の平面図では、第 1 絶縁膜 6、第 3 絶縁膜 21 の図示を適宜省略する。

【 0 0 2 3 】

図 1 及び図 2 に示されるように、本実施の形態に係る TFT 基板の TFT 部では、ゲート電極 2 と、ゲート絶縁膜 6（第 1 絶縁膜 6）と、半導体チャネル層 7 と、保護絶縁層 9 と、第 1 ソース電極 12 と、第 1 ドレイン電極 13 と、第 2 ソース電極 16 と、第 2 ドレイン電極 17 を備える。このうち、ゲート電極 2 及びゲート絶縁膜 6 については上述のとおりである。

10

【 0 0 2 4 】

半導体膜である半導体チャネル層 7 は、ゲート電極 2 上にゲート絶縁膜 6 を介して配設されている。なお、本実施の形態では、半導体チャネル層 7 は、平面視においてゲート電極 2 の外周よりも内側に配設されている。

【 0 0 2 5 】

ここでは、半導体チャネル層 7 は、酸化物半導体からなる。半導体チャネル層 7 の酸化物半導体には、例えば、酸化亜鉛（ZnO）系の酸化物半導体や、酸化亜鉛に酸化インジウム（In<sub>2</sub>O<sub>3</sub>）及び酸化すず（SnO<sub>2</sub>）を添加したInZnSnO系の酸化物半導体、または、酸化亜鉛系の酸化物半導体もしくは酸化亜鉛に酸化ガリウム（Ga<sub>2</sub>O<sub>3</sub>）及び酸化インジウム（In<sub>2</sub>O<sub>3</sub>）を添加したInGaZnO系の酸化物半導体などを用いることができる。半導体チャネル層 7 が酸化物半導体で構成されることにより、半導体チャネル層 7 にアモルファスシリコンを用いた構成よりも移動度を高めることができる。

20

【 0 0 2 6 】

第 2 絶縁膜である保護絶縁層 9、10、11 は、半導体チャネル層 7 を覆う。ここでは、保護絶縁層 10 は半導体チャネル層 7 の一端の上部及び側部に設けられ、保護絶縁層 11 は半導体チャネル層 7 の他端の上部及び側部に設けられ、保護絶縁層 9 は、保護絶縁層 10、11 の間の半導体チャネル層 7 上に設けられている。なお、以下では、保護絶縁層 9 は、保護絶縁層 10、11 と連接されているものとして説明するが、保護絶縁層 10、11 と離間されてもよい。

【 0 0 2 7 】

30

第 1 ソース電極 12 は、保護絶縁層 10、及び、保護絶縁層 9 の保護絶縁層 10 側の端部上、つまり第 2 絶縁膜の一端上に配設されている。第 1 ドレイン電極 13 は、保護絶縁層 11、及び、保護絶縁層 9 の保護絶縁層 11 側の端部上、つまり第 2 絶縁膜の他端上に配設されている。

【 0 0 2 8 】

第 1 ソース電極 12 及び第 1 ドレイン電極 13 は、酸化物導電体以外の導電体からなるとともに、互いに離間している。本実施の形態では、第 1 ソース電極 12 及び第 1 ドレイン電極 13 の導電体に、金属または合金（例えばモリブデン（Mo）及びアルミニウム（Al）のそれぞれに他の元素を微量に添加してなる合金）が用いられる。

【 0 0 2 9 】

40

第 2 ソース電極 16 は、第 1 ソース電極 12 上に配設され、第 1 ソース電極 12 及び保護絶縁層 9、10、11 に設けられた第 1 コンタクトホール 14 を介して半導体チャネル層 7 と接続されている。第 2 ソース電極 16 は、酸化物導電体（例えばIn<sub>2</sub>O<sub>3</sub>とSnO<sub>2</sub>とを含むITO膜）からなる。なお、本実施の形態では、第 1 コンタクトホール 14 は、保護絶縁層 9 と保護絶縁層 10 との間に設けられている。

【 0 0 3 0 】

同様に、第 2 ドレイン電極 17 は、第 1 ドレイン電極 13 上に配設され、第 1 ドレイン電極 13 及び保護絶縁層 9、10、11 に設けられた第 2 コンタクトホール 15 を介して半導体チャネル層 7 と接続されている。第 2 ドレイン電極 17 は、酸化物導電体（例えばIn<sub>2</sub>O<sub>3</sub>とSnO<sub>2</sub>とを含むITO膜）からなる。なお、本実施の形態では、第 2 コン

50

タクトホール 15 は、保護絶縁層 9 と保護絶縁層 11 との間に設けられている。

【0031】

次に、TFT 基板の TFT 部以外の構成要素についても説明する。

【0032】

図 1 に示されるように、第 1 ソース電極 12 は、ソース配線 18a から分岐して設けられている。そして、同様に、第 1 ソース電極 12 上の第 2 ソース電極 16 は、ソース配線 18a 上のソース配線 18b から分岐して設けられており、第 1 ソース電極 12 下の保護絶縁層 10 は、ソース配線 18a 下の保護絶縁層 8 から分岐して設けられている。そして、ソース配線 18a, 18b の端部には、それぞれソース端子 19a, 19b が設けられている。

10

【0033】

図 2 に示されるように、画素電極 20 は、第 2 ドレイン電極 17 と接続されており、第 1 絶縁膜 6 上に配設されている。本実施の形態では、画素電極 20 は、第 2 ドレイン電極 17 の一部を側方に延設して形成されている。

【0034】

第 3 絶縁膜 21 は、共通配線 5 上の第 1 絶縁膜 6 と、第 2 ソース電極 16 と、第 2 ドレイン電極 17 と、画素電極 20 とを覆う。本実施の形態では、第 3 絶縁膜 21 は、これら以外にも、ゲート端子 4 上の第 1 絶縁膜 6 や、保護絶縁層 9 なども覆う。

【0035】

ゲート端子パッド 25 は、第 1 絶縁膜 6 及び第 3 絶縁膜 21 に設けられたゲート用コンタクトホール 22 を介してゲート端子 4 と電気的に接続されている。ソース端子パッド 26 は、第 3 絶縁膜 21 に設けられたソース用コンタクトホール 23 を介してソース端子 19a, 19b と電気的に接続されている。

20

【0036】

対向電極 27 は、画素電極 20 上に第 3 絶縁膜 21 を介して配設されている。そして、対向電極 27 は、第 1 絶縁膜 6 及び第 3 絶縁膜 21 に設けられた共通電極用コンタクトホール 24 (第 3 コンタクトホール) を介して共通配線 5 と接続されている。この対向電極 27 には、スリット開口部 27a が設けられている。これにより、画素電極 20 と対向電極 27 との間に電圧が印加されると、対向電極 27 は、対向電極 27 上方に横方向の電界を画素電極 20 との間に発生することが可能となっている。

30

【0037】

< 製造方法 >

次に、本実施の形態に係る TFT 基板の製造方法について、図 3 ~ 図 14 を参照しつつ説明する。なお、図 3 ~ 図 14 では、図 1 及び図 2 に示した構成要素に対応する構成要素に、それと同一符号が付されている。

【0038】

まず、絶縁基板 1 を洗浄液または純水を用いて洗浄する。本実施の形態では、厚さが 0.5 mm であるガラス基板を絶縁基板 1 として用いた。そして、洗浄された絶縁基板 1 の一方の主面全面に、ゲート電極 2 及びゲート配線 3 などの材料である第 1 の導電膜を成膜する。

40

【0039】

第 1 の導電膜としては、例えば、クロム (Cr)、モリブデン (Mo)、チタン (Ti)、銅 (Cu)、タンタル (Ta)、タンゲステン (W)、アルミニウム (Al) などの一般的な金属やこれらの金属元素を主成分として他の元素を 1 種類以上添加した合金等を用いることができる。ここで、主成分の元素とは、合金を構成する元素のうち、含有量が最も多い元素であることを意味する。また、これらの金属または合金を 2 層以上含む積層構造としてもよい。これらの金属または合金を用いることによって、比抵抗値が 50  $\mu$  cm 以下の低抵抗な導電膜を得ることができる。本実施の形態では、アルゴン (Ar) ガスを用いたスパッタリング法により、第 1 の導電膜として、厚さが 200 nm であるアルミニウム (Al) 合金膜を成膜した。

50

## 【0040】

その後、A1合金膜上にレジスト材を塗布し、第1回目の写真製版工程で当該レジスト材からフォトレジストパターンを形成し、当該フォトレジストパターンをマスクとして、A1合金膜を選択的にエッチングすることによりパターニングする。ここでエッチングには、例えばリン酸、酢酸及び硝酸を含む溶液(PAN薬液)によるウェットエッチング法を用いることができる。その後、フォトレジストパターンを除去する。

## 【0041】

以上の結果、図3及び図4に示すように、絶縁基板1上のゲート電極2、ゲート配線3、ゲート端子4及び共通配線5が、上記第1の導電膜のパターニングによって形成される。

10

## 【0042】

次に、絶縁基板1の上面全体に、第1絶縁膜6の材料である第1被加工絶縁膜を成膜する。本実施の形態では、第1被加工絶縁膜として、酸化シリコン(SiO)膜と窒化シリコン(SiN)膜とを、化学的気相成膜(CVD)法を用いて形成した。ここでは、厚さが50nmである酸化シリコン膜、及び、厚さが400nmである窒化シリコン膜を成膜した。なお、酸化シリコン膜は、水分(H<sub>2</sub>O)、水素(H<sub>2</sub>)、ナトリウム(Na)及びカリウム(K)のようなTFTの特性に影響を及ぼす不純物元素に対するバリア性(遮断性)が弱いので、第1被加工絶縁膜は、SiOの下層に例えばバリア性に優れるSiNなどを設けた積層構造とした。この第1被加工絶縁膜の大部分は、第1絶縁膜6及びゲート絶縁膜6となることから、以下、第1被加工絶縁膜を、ゲート絶縁膜6または第1絶縁膜6と記して説明する。

20

## 【0043】

その後、第1絶縁膜6上に、半導体チャネル層7の材料である酸化物半導体膜を成膜する。本実施の形態では、その膜の酸化物半導体としてInとGaとZnとを含む酸化物(例えばInGaZnO)を用いる。その一例として、In:Ga:Zn:Oの原子組成比が1:1:1:4であるIn-Ga-Zn-Oターゲット[In<sub>2</sub>O<sub>3</sub>·Ga<sub>2</sub>O<sub>3</sub>·(ZnO)<sub>2</sub>]を用いたスパッタリング法により、InGaZnO酸化物半導体膜を成膜した。ただし、以上によって成膜された酸化物半導体膜では、通常、酸素の原子組成比が化学量論組成よりも少ないので、酸素イオン欠乏状態(上記の例ではOの組成比が4未満)となってしまう。このため、Arガスに酸素(O<sub>2</sub>)ガスを混合させてスパッタリングする方が好ましい。本実施の形態では、Arガスに対して分圧比で10%のO<sub>2</sub>ガスを添加した混合ガスを用いてスパッタリングし、厚さが50nmであるInGaZnO膜を成膜した。このように形成されたInGaZnO膜は、非晶質構造を有する。また、非晶質構造のInGaZnO膜は、一般的に結晶化温度が500以上であり、常温では膜中の大部分が非晶質構造のままで安定する。

30

## 【0044】

次に、第2回目の写真製版工程でフォトレジストパターンを形成し、これをマスクとして、酸化物半導体膜を選択的にエッチングすることによりパターニングする。ここでエッチングには、例えばカルボン酸を含む薬液によるウェットエッチング法を用いることができる。カルボン酸を含む薬液としては、例えばシュウ酸を1~10wt%の範囲で含むものが好ましい。本実施の形態では、シュウ酸5wt%と水とからなるシュウ酸系薬液を用いて酸化物半導体膜をエッチングした。その後、フォトレジストパターンを除去する。

40

## 【0045】

以上の結果、図5及び図6に示すように、ゲート電極2上に第1絶縁膜6を介して配設された半導体チャネル層7が、上記酸化物半導体膜のパターニングによって形成される。なお、第1絶縁膜6のうち、ゲート電極2と半導体チャネル層7とに挟まれた部分はゲート絶縁膜6として機能する。

## 【0046】

次に、第1絶縁膜6及び半導体チャネル層7上に保護絶縁層8, 9, 10, 11の材料である第2被加工絶縁膜を成膜する。本実施の形態では、第2被加工絶縁膜として、例え

50

ば厚さが 100 nm である SiO 膜を、 CVD 法を用いて形成した。

【 0047 】

次いで、第 2 被加工絶縁膜上に第 2 の導電膜を成膜する。本実施の形態では、第 2 の導電膜として、モリブデン (Mo) 及びアルミニウム (Al) のそれぞれに他の元素を微量に添加して得られる合金を積層させることによって積層構造を形成した。

【 0048 】

次に、第 3 回目の写真製版工程でフォトレジストパターンを形成し、これをマスクとして、第 2 の導電膜 (ここでは Al 合金と Mo 合金との積層膜) を選択的にエッチングすることによりパターニングする。ここでのエッチングには、例えばリン酸、酢酸及び硝酸を含む溶液 (PAN 薬液) によるウェットエッチング法を用いることができる。本実施の形態では、リン酸 70 wt % と、酢酸 7 wt % と、硝酸 5 wt % と、水とからなる PAN 薬液を用いてエッチングを行った。この段階では、下層の半導体チャネル層 7 は、第 2 被加工絶縁膜により保護されているので薬液によるダメージを受けない。

10

【 0049 】

その後、まだ除去されていないフォトレジストパターンと、上記パターニングが施された第 2 の導電膜とをマスクとして、第 2 被加工絶縁膜を選択的にエッチングすることによりパターニングする。ここでのエッチングには、例えばフッ素を含むガスを用いたドライエッチング法を用いることができる。本実施の形態では、六フッ化硫黄 (SF<sub>6</sub>) に酸素 (O<sub>2</sub>) を加えたガスを用いてドライエッチングした。O<sub>2</sub> ガスを添加することによって、エッチング時の下層の半導体チャネル層 7 の還元反応によるダメージを抑制することができる。その後、フォトレジストパターンを除去する。

20

【 0050 】

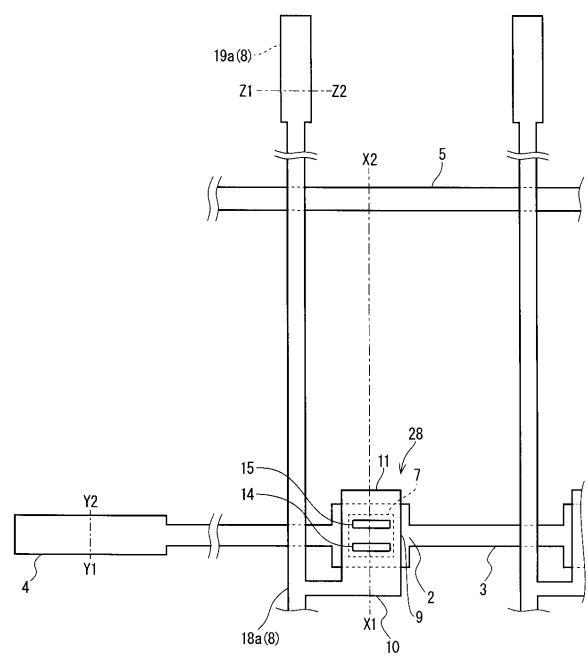

以上の結果、図 7 及び図 8 に示すように、一回の写真製版 (ここでは第 3 回目の写真製版) の間に、半導体チャネル層 7 上の保護絶縁層 9, 10, 11 と、保護絶縁層 8 とが、上記第 2 被加工絶縁膜のパターニングによって形成されるとともに、電極体 28 と、ソース配線 18a と、ソース端子 19a とが、上記第 2 の導電膜のパターニングによって形成される。また、上記第 2 被加工絶縁膜のパターニングによって、半導体チャネル層 7 のソース領域上には第 1 コンタクトホール 14 が形成され、半導体チャネル層 7 のドレイン領域上には第 2 コンタクトホール 15 が形成される。

30

【 0051 】

なお、上述の電極体 28 とは、保護絶縁層 10、及び、保護絶縁層 9 の保護絶縁層 10 側の端部上に配設された第 1 ソース電極 12 と、保護絶縁層 11、及び、保護絶縁層 9 の保護絶縁層 11 側の端部上に配設された第 1 ドレイン電極 13 とが、保護絶縁層 9 上にて繋がった構造体である。なお、図 8 に示されるように、電極体 28 のうち、第 1 ソース電極 12 及び第 1 ドレイン電極 13 に対応する部分は、半導体チャネル層 7 上に直接的に配設されておらず、保護絶縁層 9, 10, 11 を介して半導体チャネル層 7 上に間接的に配設される。

【 0052 】

その後、半導体チャネル層 7 と、第 1 ソース電極 12 及び第 1 ドレイン電極 13 を電気的に接続する第 2 ソース電極 16 及び第 2 ドレイン電極 17 の材料である第 3 の導電膜を成膜する。本実施の形態では、第 3 の導電膜として、光透過性の酸化物系導電膜である ITO 膜 (例えば、混合比が In<sub>2</sub>O<sub>3</sub> の重量 % : SnO<sub>2</sub> の重量 % = 90 : 10) を用いる。ITO 膜は一般的に、常温中では結晶質 (多結晶) 構造が安定であるが、ここではスパッタリング法で、アルゴン (Ar) に水素 (H) を含むガス、例えば、水素 (H<sub>2</sub>) ガスまたは水蒸気 (H<sub>2</sub>O) などを混合したガスを用いて成膜することにより、厚さが 100 nm であり、非晶質状態を有する ITO 膜を形成する。

40

【 0053 】

次に、第 4 回目の写真製版工程でフォトレジストパターンを形成し、これをマスクとして、第 3 の導電膜 (非晶質 ITO 膜) を選択的にエッチングすることによりパターニングする。ここでのエッチングには、例えばシウ酸 5 wt % と水とからなるシウ酸系薬液

50

によるウェットエッティング法を用いることができる。

【0054】

その後、まだ除去されていないフォトレジストパターンと、上記パターニングが施された第3の導電膜とをマスクとして、電極体28を選択的にエッティングする。これにより、電極体28のうち第1ソース電極12及び第1ドレイン電極13を繋いでいた、保護絶縁層9上の部分が除去される。つまり、ソース電極（第1及び第2ソース電極12, 16）とドレイン電極（第1及び第2ドレイン電極13, 17）とが電気的に分離する。なお、ここでのエッティングには、例えばPAN薬液によるウェットエッティング法を用いることができる。その後、フォトレジストパターンを除去する。

10

【0055】

以上の結果、図9及び図10に示すように、一回の写真製版（ここでは第4回目の写真製版）の間に、第2ソース電極16及び第2ドレイン電極17と、第2ドレイン電極17の画素表示領域に対応する部分である画素電極20と、ソース配線18bと、ソース端子19bとが、上記第3の導電膜のパターニングによって形成されるとともに、第1ソース電極12及び第1ドレイン電極13が、上記電極体28のパターニングによって形成される。

【0056】

なお、ITOなどからなる酸化物導電体からなる第2ソース電極16及び第2ドレイン電極17は、それぞれ第1コンタクトホール14及び第2コンタクトホール15を介して下層の半導体チャネル層7に直接接続されている。このような構成によれば、酸化物導電体以外の導電体からなる第1ソース電極12及び第1ドレイン電極13が半導体チャネル層7に直接接続される構成よりも、半導体チャネル層7のソース領域及びドレイン領域における還元反応を抑制することができる。この結果、半導体チャネル層7の特性劣化を抑制することができる。

20

【0057】

以上によって第2ソース電極16、第2ドレイン電極17及び画素電極20を形成した後、絶縁基板1の上面全体に、第3絶縁膜21の材料である第3被加工絶縁膜を成膜する。本実施の形態では、第3被加工絶縁膜として、厚さが200nmである酸化シリコン（SiO）膜と、厚さが100nmである窒化シリコン（SiN）膜とを、この順にCVD法を用いて成膜した。

30

【0058】

そして、第5回目の写真製版工程でフォトレジストパターンを形成し、これをマスクとして、第3被加工絶縁膜及び第1絶縁膜6を選択的にエッティングすることによりパターニングする。ここでのエッティングには、例えばフッ素を含むガスを用いたドライエッティング法を用いることができる。本実施の形態では、六フッ化硫黄（SF<sub>6</sub>）に酸素（O<sub>2</sub>）を加えたガスを用いてドライエッティングした。その後、フォトレジストパターンを除去する。

【0059】

以上の結果、図11及び図12に示すように、ゲート端子部のゲート用コンタクトホール22、ソース端子部のソース用コンタクトホール23、及び、共通配線接続部の共通電極用コンタクトホール24が設けられた第3絶縁膜21が、上記第3被加工絶縁膜のパターニングによって形成される。

40

【0060】

その後、ゲート用コンタクトホール22を介してゲート端子4と電気的に接続されたゲート端子パッド25と、ソース用コンタクトホール23を介してソース端子19a, 19bと電気的に接続されたソース端子パッド26と、共通電極用コンタクトホール24を介して共通配線5と電気的に接続された対向電極27との材料である第4の導電膜を成膜する。本実施の形態では、第4の導電膜として透光性導電膜を成膜する。透光性導電膜としては、ITO膜（例えは、混合比がIn<sub>2</sub>O<sub>3</sub>の重量% : SnO<sub>2</sub>の重量% = 90 : 10

50

)を用いる。ITO膜は一般的に、常温中では結晶質(多結晶)構造が安定であるが、ここではスパッタリング法で、アルゴン(Ar)に水素(H)を含むガス、例えば、水素(H<sub>2</sub>)ガスまたは水蒸気(H<sub>2</sub>O)などを混合したガスを用いて成膜することにより、厚さが100nmであり、非晶質状態を有するITO膜を形成する。

#### 【0061】

そして、第6回目の写真製版工程でフォトレジストパターンを形成し、これをマスクとして、第4の導電膜(非晶質ITO膜)を選択的にエッティングすることによりパターニングする。ここでエッティングには、例えばシュウ酸5wt%と水とからなるシュウ酸系薬液によるウェットエッティング法を用いることができる。その後、フォトレジストパターンを除去する。

10

#### 【0062】

以上の結果、図1及び図2に示すように、ゲート用コンタクトホール22を介してゲート端子4と電気的に接続されたゲート端子パッド25と、ソース用コンタクトホール23を介してソース端子19a, 19bと電気的に接続されたソース端子パッド26と、共通電極用コンタクトホール24を介して共通配線5と電気的に接続された対向電極27とが、上記第4の導電膜のパターニングによって形成される。なお、当該パターニングによって、対向電極27にはスリット開口部27aが設けられる。以上により、図1及び図2に示したFFS-LCD用のTFT基板が完成する。

#### 【0063】

液晶表示パネルの組み立ての際は、完成したTFT基板の表面に配向膜やスペーサを形成する。配向膜は、液晶を配列させるための膜であり、ポリイミド等で構成される。また、別途作製したカラーフィルタや配向膜を備えた対向基板を、本実施の形態に係るTFT基板と対向配置させて貼り合わせる。このとき、スペーサによってTFT基板と対向基板との間に隙間が形成され、その隙間に液晶層を形成して封止することによって、FFSモードの液晶表示パネルが形成される。これにより、当該液晶表示パネルを備える液晶表示装置は、対向電極27と画素電極20との間に発生する電界のうち、対向電極27に関して画素電極20と逆側に発生する横方向の電界によって、液晶を駆動することが可能となつている。

20

#### 【0064】

最後に、液晶表示パネルの外側に偏光板、位相差板及びバックライトユニット等を配設することによって液晶表示装置が完成する。

30

#### 【0065】

##### <実施の形態のまとめ>

以上のような本実施の形態に係るTFT基板及び液晶表示装置によれば、酸化物半導体からなる半導体チャネル層7上に、保護絶縁層9, 10, 11を介して、酸化物導電体以外の導電体(例えば金属層または合金層)からなる第1ソース電極12及び第1ドレイン電極13が配設される。このような構成によれば、ソース電極及びドレイン電極を形成する加工プロセスの際ににおける、半導体チャネル層7のダメージを抑制することができる。したがって、TFTの特性及び信頼性を高めることができる。

#### 【0066】

40

また、本実施の形態では、酸化物導電体からなる第2ソース電極16及び第2ドレイン電極17が、半導体チャネル層7と、酸化物導電体以外の導電体からなる第1ソース電極12及び第1ドレイン電極13との間を接続する。このような構成によれば、従来技術では、半導体チャネル層7と第1ソース電極12及び第1ドレイン電極13との間に生じていた還元反応を抑制することができる。これにより、当該界面でのコンタクト特性を向上させることができ、オン電流値や移動度の値が向上するので、TFTの特性及び信頼性を高めることができる。

#### 【0067】

なお、仮に、半導体チャネル層7が、平面視においてゲート電極2の外周(端部)からはみ出して配設されている場合には、ゲート電極2の厚さにより当該ゲート電極2の外周

50

に形成される段差部で耐圧が悪くなったり、段差部上方に形成されるソース電極及びドレイン電極の段切れ（段差部に起因する断線や断裂）が発生したりする可能性がある。

【0068】

これに対して、本実施の形態では、半導体チャネル層7は、平面視においてゲート電極2の外周よりも内側に配設されている。これにより、ゲート電極2の上記段差部上方には、第1絶縁膜6と、保護絶縁層10, 11が形成されることになるので、ゲート電極2と、ソース電極及びドレイン電極との間の耐圧を向上させることができる。また、半導体チャネル層7を覆うように保護絶縁層9, 10, 11が形成されることにより、ゲート電極2と第1ソース電極12との間の電気的ショート（短絡）不良を抑制することができる。また、ソース電極及びドレイン電極のカバレッジ特性（被覆性）を高めることができるので、上記段差部に起因するソース電極及びドレイン電極の段切れ不良の発生を抑制することができる。

【0069】

また、本実施の形態に係るTFT基板の製造方法によれば、一回の写真製版の間に、保護絶縁層9, 10, 11と、第1ソース電極12及び第1ドレイン電極13となる電極体28とを形成し、一回の写真製版の間に第2ソース電極16、第2ドレイン電極17及び画素電極20と、第1ソース電極12及び第1ドレイン電極13とを形成する。このような製造方法によれば、半導体チャネル層7を保護する保護絶縁層9, 10, 11を形成するための専用の写真製版を行わなくて済むことから、生産能力の低下を抑制することができるとともに、写真製版のマスク枚数の増加に伴う製造コストの増加を抑制することができる。

【0070】

以上のように、本実施の形態によれば、酸化物半導体からなる半導体チャネル層7上に、保護絶縁層9, 10, 11を介して、酸化物導電体以外の導電体からなる第1ソース電極12及び第1ドレイン電極13が配設される。これにより、第1ソース電極12及び第1ドレイン電極13を形成する際の成膜及びエッチングによる、半導体チャネル層7へのダメージを抑制することができるのでTFTの特性及び信頼性を高めることができる。また、TFTの半導体チャネル層7に、移動度の高い酸化物半導体膜を用いることにより、動作速度の速いTFTの基板、及びそれを用いた液晶表示装置を、高い歩留まりで製造することができる。つまり、高性能のTFT基板及び液晶表示装置を、生産性良く製造することができる。

【0071】

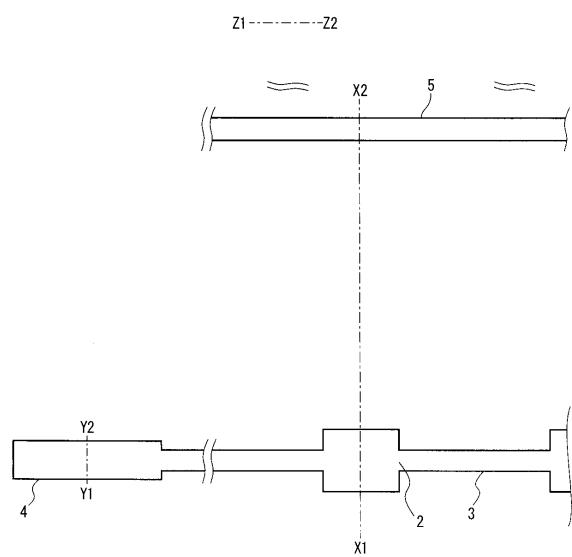

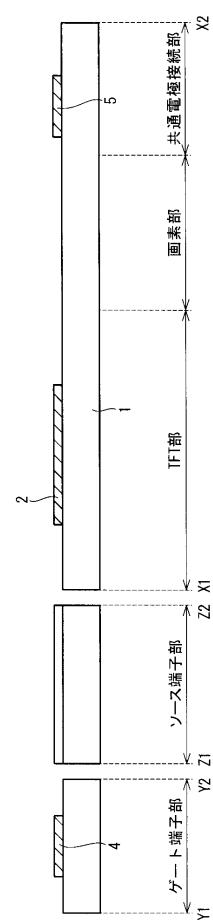

<変形例>

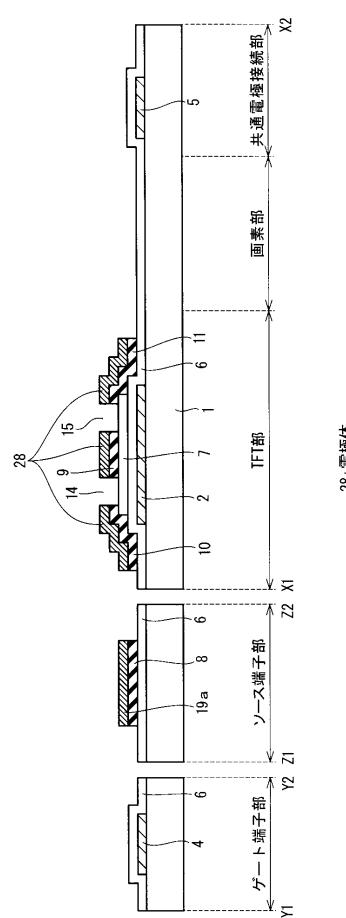

図13及び図14を参照して、本実施の形態の変形例に係るTFT基板の構成について説明する。図13は、本変形例に係るFFS方式のTFT基板における画素部、及び、画素部（画素表示領域）外側のゲート端子部及びソース端子部の平面構成を示す図であり、図14は、その断面構成を示す図である。図14では、図13に示すX1-X2線、Y1-Y2線及びZ1-Z2線に沿った断面が示されている。X1-X2線に沿った断面は、画素の配設領域（画素部）に対応する。Y1-Y2線に沿った断面は、ゲート配線3（図14には図示せず）にゲート信号を供給するためのゲート端子4及びゲート端子パッド25の配設領域（ゲート端子部）に対応する。Z1-Z2線に沿った断面は、ソース配線18a, 18b（図14には図示せず）に表示信号を印加するためのソース端子19a, 19b及びソース端子パッド26の配設領域（ソース端子部）に対応する。

【0072】

本変形例では、実施の形態1の共通配線5及び画素電極20の少なくともいずれか一方のパターンを一部変更して、画素電極20の少なくとも一部が、平面視において共通配線の少なくとも一部と重なるように構成されている。このような重なり領域を形成することによって、画素電極20には液晶容量に加えて補助容量が形成されるため、画素電極20に書き込まれた映像信号の電荷の保持特性が向上する。したがって、輝度ムラのような表示不良を抑制することができ、さらに高い表示品質を有するFFSモードの液晶表示パネ

10

20

30

40

50

ル（液晶表示装置）を実現することができる。

【0073】

なお、上記の実施の形態1及び変形例においては、本発明をFFSモードの液晶表示パネル（液晶表示装置）へ適用した場合を例示して説明を行った。しかし、TFT部と当該TFT部に接続される画素電極20に関する構造については、FFS-LCDに限らず、酸化物導電体を画素電極に用いたLCDであれば、例えば、TN（Twisted Nematic）モードの透過型LCDにも適用することができる。

【0074】

TNモードの透過型LCDに適用した場合においては、実施の形態1のTFT部の基本的な構成と画素電極20との接続構造までは同様の構成を用いることができ、TFT基板上に配設される共通配線5及び対向電極27の構成が省略される。そして、TFT基板上に配設される対向電極27に代えて、カラーフィルタや配向膜を備えた対向基板上に画素表示領域全面にわたってITO膜などの酸化物導電体により形成される対向電極が配設される。そのような構成において、TFT基板上に配設される画素電極20と、対向基板上に配設される対向電極との間に発生する電界によって液晶を駆動するように部分的に変更するとよい。

10

【0075】

このように変更した構成においても、実施の形態1において得られる基本的な効果が得られる。つまり、第1ソース電極12及び第1ドレイン電極13を形成する際の成膜及びエッチングによる、半導体チャネル層7へのダメージを抑制することができるので、TFTの特性及び信頼性を高めることができる効果が得られる。あるいは、TFTの半導体チャネル層7に、移動度の高い酸化物半導体膜を用いることにより、動作速度の速いTFTの基板、及びそれを用いた液晶表示装置を、高い歩留りで製造することができる効果が得られる。つまり、高性能のTFT基板及び液晶表示装置を、生産性良く製造することができる効果について同様に得ることができる。

20

【0076】

なお、本発明は、その発明の範囲内において、実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0077】

30

1 絶縁基板、2 ゲート電極、5 共通配線、6 第1絶縁膜、7 半導体チャネル層、9, 10, 11 保護絶縁層、12 第1ソース電極、13 第1ドレイン電極、14 第1コンタクトホール、15 第2コンタクトホール、16 第2ソース電極、17 第2ドレイン電極、20 画素電極、21 第3絶縁膜、24 共通電極用コンタクトホール、27 対向電極、28 電極体。

【図1】

【図2】

- 1:絶縁基板

2:ゲート電極

3:共通配線

4:第2ソース電極

5:半導体チャネル層

6:第2ドレイン電極

7:半導体チャネル層

9,10,11:保護絶縁層

12:第1ソース電極

13:第1ドレイン電極

14:第1コントラクトホール

15:第2コントラクトホール

16:第2ソース電極

17:第2ドレイン電極

20:画面部

21:画面部

24:共通電極接続部

25:ソース端子部

26:ゲート端子部

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(51)Int.Cl.

F I

|        |        |         |

|--------|--------|---------|

| H 01 L | 29/78  | 6 2 7 C |

| H 01 L | 21/28  | 3 0 1 B |

| H 01 L | 21/28  | 3 0 1 R |

| H 01 L | 29/50  | M       |

| G 02 F | 1/1368 |         |

(56)参考文献 国際公開第2012/060362 (WO, A1)

特開2014-036189 (JP, A)

米国特許出願公開第2014/0319515 (US, A1)

特開2014-215485 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |             |

|--------|-------------|

| H 01 L | 2 9 / 7 8 6 |

| G 02 F | 1 / 1 3 6 8 |

| H 01 L | 2 1 / 2 8   |

| H 01 L | 2 1 / 3 3 6 |

| H 01 L | 2 9 / 4 1 7 |