(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5016118号

(P5016118)

(45) 発行日 平成24年9月5日(2012.9.5)

(24) 登録日 平成24年6月15日(2012.6.15)

(51) Int.CI.

HO3M 1/66 (2006.01)

F 1

HO3M 1/66

C

請求項の数 21 (全 21 頁)

(21) 出願番号 特願2010-546069 (P2010-546069)

(86) (22) 出願日 平成21年2月6日 (2009.2.6)

(65) 公表番号 特表2011-511604 (P2011-511604A)

(43) 公表日 平成23年4月7日 (2011.4.7)

(86) 國際出願番号 PCT/US2009/033463

(87) 國際公開番号 WO2009/100379

(87) 國際公開日 平成21年8月13日 (2009.8.13)

審査請求日 平成22年10月6日 (2010.10.6)

(31) 優先権主張番号 12/027,132

(32) 優先日 平成20年2月6日 (2008.2.6)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】適応可能な高次のデジタル・アナログ変換

## (57) 【特許請求の範囲】

## 【請求項1】

1次または高次のホールドでデジタル／アナログ変換を実行するための装置であって

アナログ入力信号を受信しアナログ出力信号を供給するように構成されたアナログ回路

(370, 570, 770)と、

前記アナログ回路からの前記アナログ出力信号および第1のデジタル回路を受信し、第2のデジタル信号を供給するように構成されたフィードバック回路(330)と、

前記フィードバック回路に結合され、前記第2のデジタル信号を受信し、前記アナログ回路のための前記アナログ入力信号を供給するためのゼロ次のホールド(ZOH)回路(360)と、なお、前記フィードバック回路、前記ZOH回路、アナログ回路は、1次またはより高次のホールドでデジタル／アナログ変換を実行する

前記フィードバック回路に結合され、デジタル入力信号を受信し、前記第1のデジタル信号を供給するように構成された逆モデル回路(310)と

を備え、前記逆モデル回路は、前記ZOH回路および前記アナログ回路の組み合された伝達回路の逆数に基づいて決定される伝達関数を有する、装置。

## 【請求項2】

前記フィードバック回路は、前記アナログ出力回路に基づいて低周波数ノイズ・フィルタリングを実行するように構成される、

請求項1に記載の装置。

## 【請求項3】

前記フィードバック回路は、前記アナログ回路の伝達関数に基づいて決定される伝達関数を有するモデル回路(340, 540, 740)を備える、

請求項1に記載の装置。

【請求項4】

前記モデル回路の前記伝達関数は、前記ZOH回路の伝達関数にさらにに基づいて決定される、

請求項3に記載の装置。

【請求項5】

前記フィードバック回路は、前記アナログ回路の少なくとも1つのパラメータを推定するように構成された適応回路(790)をさらに備え、前記モデル回路の前記伝達関数は、前記少なくとも1つの推定されたパラメータに基づく、

請求項3に記載の装置。

【請求項6】

前記フィードバック回路は、前記アナログ回路のポール周波数および利得を推定するように構成された適応回路(790)をさらに備え、前記モデル回路の前記伝達関数は、前記推定されたポール周波数および利得に基づく、

請求項3に記載の装置。

【請求項7】

前記フィードバック回路は、第1のデジタル信号を受信し、モデル出力信号を供給するように構成されたモデル回路(340, 540, 740)と、

前記モデル出力信号とデジタル化された出力信号との差をとり、エラー信号を供給するように構成された第1の加算器(342, 542, 742)と、

前記エラー信号をフィルタにかけ、フィルタにかけられた信号を供給するように構成されたループ・フィルタ(350, 550, 750)と、

前記フィルタにかけられた信号と前記第1のデジタル信号との和を取り、前記第2のデジタル信号を供給するように構成された第2の加算器(352, 552, 752)と、

を備える請求項1に記載の装置。

【請求項8】

前記ループ・フィルタは、前記第1のデジタル信号の帯域幅より小さな帯域幅でノイズ・フィルタリングを実行するように構成される、

請求項7に記載の装置。

【請求項9】

前記フィードバック回路は、前記アナログ出力信号をデジタル化し、前記デジタル化された出力信号を供給するように構成されたアナログ/デジタル変換器(ADC)(380, 780)をさらに備え、

前記ADCは、ノイズ形成変調器を備える、

請求項7に記載の装置。

【請求項10】

前記フィードバック回路は、

前記第1のデジタル信号のための広域変調パスと、

前記第1のデジタル信号のための低域変調パスとを備える、請求項1に記載の装置。

【請求項11】

前記アナログ回路は、少なくとも1つのポールを備える、請求項1に記載の装置。

【請求項12】

前記アナログ回路は、

## 【数1】

$$G(s) = \frac{b}{s + a},$$

の s - ドメイン伝達関数 G ( s ) を有し、

ここで、 a は、前記アナログ回路のポール周波数であり、 b は、前記アナログ回路の利得であり、前記ポール周波数は、好ましくは前記第 1 のデジタル信号のサンプリング周波数より少なくとも 10 倍小さい、

請求項 1 に記載の装置。

## 【請求項 1 3】

1 次またはより高次のホールドでデジタル / アナログ変換を実行するための方法 ( 900 ) であって、前記方法は、

第 2 のデジタル信号を取得するためにアナログ回路からのアナログ出力信号および第 1 のデジタル回路を処理すること ( 914 ) と、

前記アナログ回路のためのアナログ入力信号を取得するためにゼロ次のホールドでデジタルからアナログに前記第 2 のデジタル信号を変換すること ( 916 ) と、

前記アナログ出力信号を取得するために前記アナログ回路を前記アナログ入力信号が通過すること ( 918 ) と、

前記第 1 のデジタル信号を得るために、前記ゼロ次のホールド及び前記アナログ回路の伝達関数の組み合わせの逆数に基づいて決定された伝達関数でデジタル入力信号を処理すること ( 912 ) と、

を備える方法。

## 【請求項 1 4】

前記フィードバック回路で前記アナログ出力信号と前記第 1 のデジタル信号を前記処理することは、

モデル出力信号を取得するためにモデル回路で前記第 1 のデジタル信号を処理すること ( 1012 ) と、

エラー信号を取得するために前記モデル出力信号とデジタル化された出力信号との差をとること ( 1014 , 1016 ) と、

フィルタにかけられた信号を取得するためにループ・フィルタで前記エラー信号をフィルタリングすること ( 1018 ) と、

前記第 2 のデジタル信号を取得するために前記第 1 のデジタル信号と前記フィルタにかけられた信号との和をとること ( 1020 ) と、

を備える請求項 1 3 に記載の方法。

## 【請求項 1 5】

アナログ回路の少なくとも 1 つのパラメータを推定することと、

前記少なくとも 1 つの推定されたパラメータに基づいて前記モデル回路の伝達関数を実施することと、

をさらに備える請求項 1 4 に記載の方法。

## 【請求項 1 6】

前記アナログ回路のポール周波数および利得を推定することと、

前記推定されたポール周波数および利得に基づいてモデル回路の伝達関数をインプリメントすることと、

をさらに備える請求項 1 4 に記載の方法。

## 【請求項 1 7】

1 次またはより高次のホールドでデジタル / アナログ変換を実行するための装置であつて、前記装置は、

10

20

30

40

50

第2のデジタル信号を取得するためにアナログ回路からのアナログ出力信号および第1のデジタル回路を処理するための手段と、

前記アナログ回路のためのアナログ入力信号を取得するためにゼロ次のホールドでデジタルからアナログに前記第2のデジタル信号を変換するための手段と、

前記アナログ出力信号を取得するために前記アナログ回路を前記アナログ入力信号が通過するための手段と、

前記第1のデジタル信号を得るために、前記ゼロ次のホールド及び前記アナログ回路の伝達関数の組み合わせの逆数に基づいて決定された伝達関数でデジタル入力信号を処理するための手段と、

を備える装置。

10

【請求項18】

前記フィードバック回路で前記アナログ出力信号と前記第1のデジタル信号を前記処理するための手段は、

モデル出力信号を取得するためにモデル回路で前記第1のデジタル信号を処理するための手段と、

エラー信号を取得するために前記モデル出力信号とデジタル化された出力信号との差を取るための手段と、

フィルタにかけられた信号を取得するためにループ・フィルタで前記エラー信号をフィルタリングするための手段と、

前記第2のデジタル信号を取得するために前記第1のデジタル信号と前記フィルタにかけられた信号との和をとるための手段と、

20

備える請求項17に記載の装置。

【請求項19】

アナログ回路の少なくとも1つのパラメータを推定するための手段と、

前記少なくとも1つの推定されたパラメータに基づいて前記モデル回路の伝達関数をインプリメントするための手段と、

をさらに備える請求項18に記載の装置。

【請求項20】

前記アナログ回路のポール周波数および利得を推定するための手段と、

前記推定されたポール周波数および利得に基づいてモデル回路の伝達関数を実施するための手段と

30

をさらに備える請求項18に記載の装置。

【請求項21】

コンピュータ可読記憶媒体を備えるコンピュータ・プログラムであって、

前記コンピュータ可読記憶媒体は、

少なくとも1つのコンピュータに、請求項13乃至16のいずれか1項に記載の方法を実行させるためのコードを備える、

コンピュータ・プログラム。

【発明の詳細な説明】

【技術分野】

40

【0001】

本開示は、一般に電子装置に関し、特に、デジタル・アナログ変換を実行するための技術に関する。

【背景技術】

【0002】

デジタル・アナログ変換器(DAC)は、デジタル信号を受信し、アナログ信号を出力する回路である。DACは、デジタル回路とアナログ回路との間のインターフェースを提供するために様々な電子デバイスで一般に使用される。例えば、携帯電話のようなワイヤレス通信デバイスは、送信機、音声出力回路、ビデオ出力回路、などであるインターフェースに対する1つ又は複数のDACを含み得る。

50

## 【0003】

DACは、DACからアナログ信号をフィルタにかけるために、再構成フィルタのようなアナログ回路と組み合わされて典型的に使用される。アナログ回路は、比較的複雑であり、DACを使用する電子デバイスの複雑性及びコストを増大させ得る。複雑性とコストを低減するために単純なアナログ回路を使用して、デジタル・アナログ変換を実行することが望まれている。

## 【発明の概要】

## 【0004】

第1次又はより高次のホールドを備えたデジタル・アナログ変換を実行するための技術が、ここで説明される。技術は、信号再構成のための単純なアナログ回路を利用し、アナログ回路の低周波の動作を改善し且つ良い性能を達成するためにフィードバック制御技術を採用する。

10

## 【0005】

1つの設計において、デジタル／アナログ変換回路は、逆モデル回路（inverse model circuit）、フィードバック回路、ゼロ次のホールド（ZOH：zero-order hold）回路及びアナログ回路を含む。逆モデル回路は、デジタル入力信号を処理し、第1のデジタル信号を供給する。フィードバック回路は、第1のデジタル信号及びアナログ回路からのアナログ出力信号を受信し、低周波ノイズ・フィルタリングを実行し、第2のデジタル信号を供給する。ZOH回路は、ゼロ次のホールドでデジタルからアナログに第2のデジタル信号を変換し、アナログ回路のためにアナログ入力信号を供給する。アナログ回路は、アナログ入力信号上で作動し、アナログ出力信号を供給する。アナログ回路は、1つ又は複数のポールを有する単純な回路であり得る。

20

## 【0006】

1つの設計において、フィードバック回路は、モデル回路、第1と第2の加算器、ループ・フィルタ、及びアナログ／デジタル変換器（ADC）を含む。モデル回路は、伝達関数  $M(s)$  に基づいて第1のデジタル信号上で作動し、モデル出力信号を供給する。ADCは、アナログ出力信号をデジタル化し、デジタル化された出力信号を供給する。第1の加算器は、モデル出力信号とデジタル化された出力信号との差をとり、エラー信号を供給する。ループ・フィルタは、エラー信号をフィルタにかけ、フィルタにかけられた信号を供給する。第2の加算器は、フィルタにかけられた信号及び第1のデジタル信号との和をとり、第2のデジタル信号を供給する。フィードバック回路は、第1のデジタル回路を最小の影響にすると同時に、アナログ回路の低周波の動作を改善するためにノイズ・フィルタリングを実行する。

30

## 【0007】

モデル回路の伝達関数  $M(s)$  は、アナログ回路の伝達関数  $G(s)$  及びZOH回路の伝達関数  $Z(s)$  に基づいて適応的に決定され得る。適応回路は、アナログ回路の少なくとも1つのパラメータ（例えば、ポール周波数および利得）を推定し得る。その後、モデル回路の伝達関数  $M(s)$  は、推定されたパラメータに基づいて改善され得る。逆モデル回路は、モデル回路の伝達関数  $M(s)$  の逆数である、 $M^{-1}(s)$  の伝達関数を有し得る。

40

## 【0008】

説明の様々な態様及び特徴は、さらに以下に詳細に説明される。

## 【図面の簡単な説明】

## 【0009】

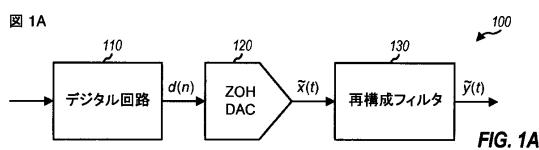

【図1A】図1Aは、従来のデジタル／アナログ変換を示す。

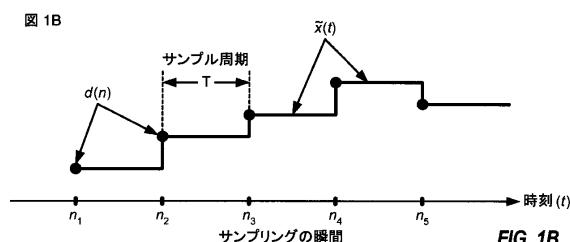

【図1B】図1Bは、デジタル入力信号及びアナログ入力信号を示す。

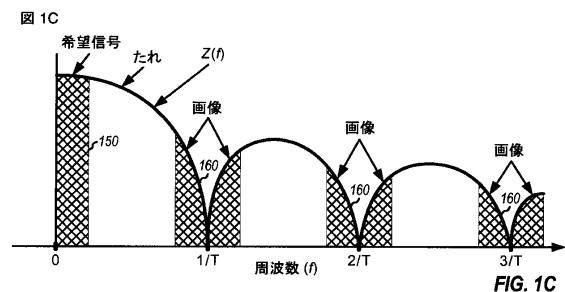

【図1C】図1Cは、アナログ入力信号のスペクトル応答を示す。

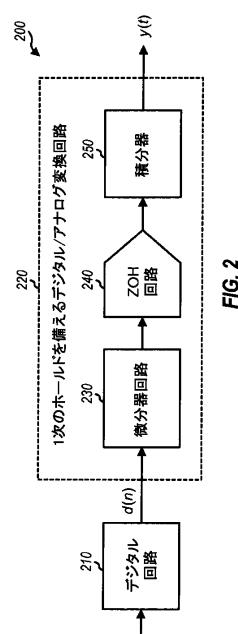

【図2】図2は、1次のホールドを備えるデジタル／アナログ変換を示す。

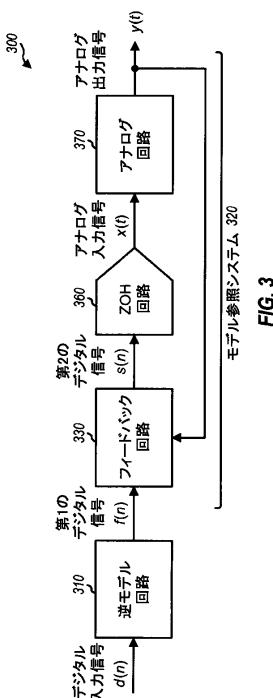

【図3】図3は、1次又はより高次のホールド及びネガティブ・フィードバックを備えたデジタル／アナログ変換回路の設計を示す。

50

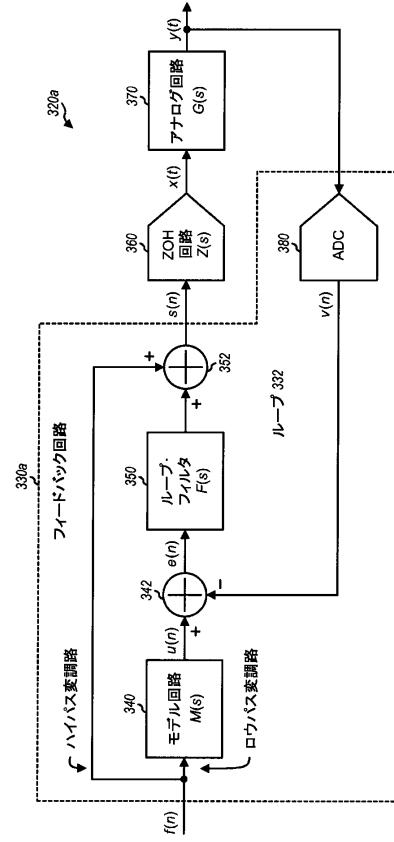

【図4】図4は、デジタル／アナログ変換回路内のフィードバック回路を示す。

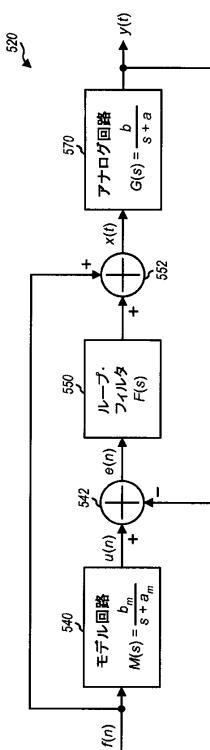

【図5】図5は、デジタル／アナログ変換回路のためのモデル参照システムを示す。

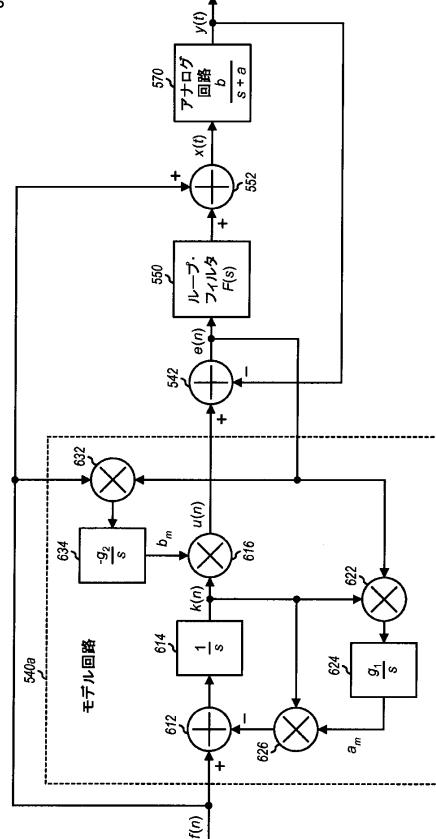

【図6】図6は、フィードバック回路内のモデル回路を示す。

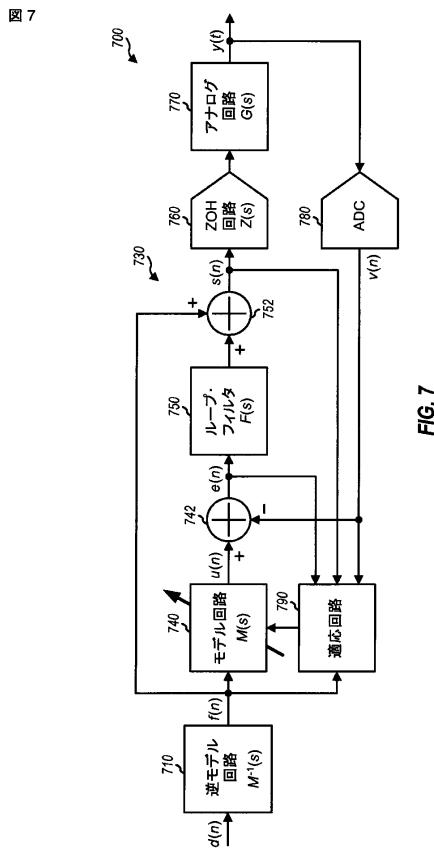

【図7】図7は、1次の又はより高次のホールド及びネガティブ・フィードバックを備えたデジタル／アナログ変換回路の別の設計を示す。

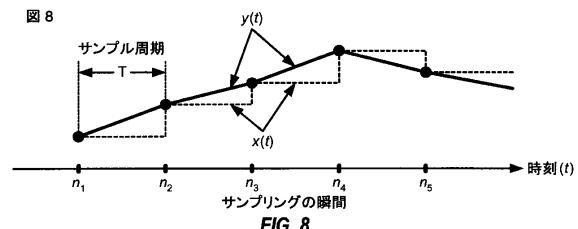

【図8】図8は、1次のホールドを備えたアナログ出力信号を示す。

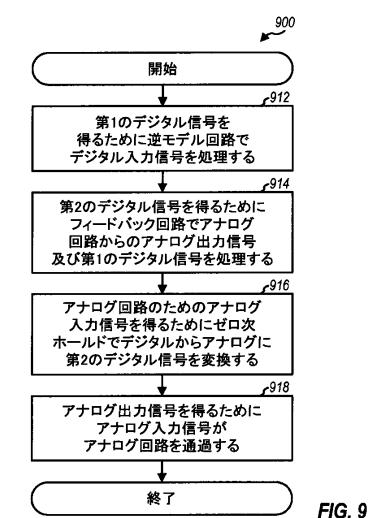

【図9】図9は、デジタル／アナログ変換を実行するプロセスを示す。

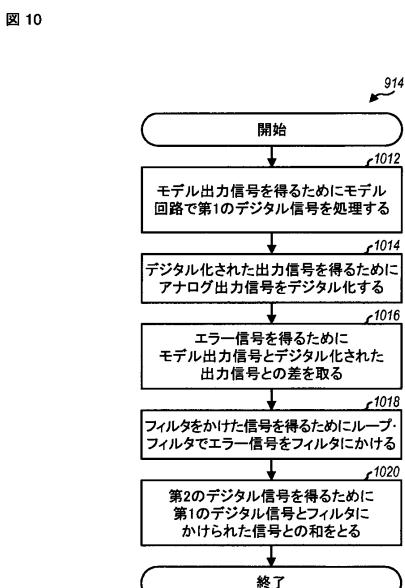

【図10】図10は、デジタル／アナログ変換のためのフィードバック処理のためのプロセスを示す。

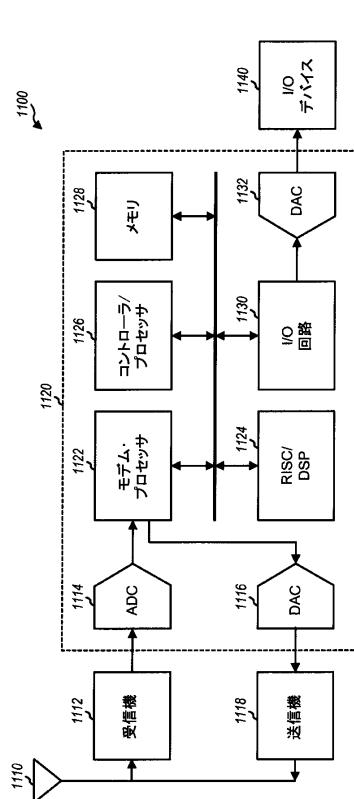

【図11】図11は、ワイヤレス通信デバイスのブロック図を示す。

10

【発明を実施するための形態】

【0010】

図1Aは、従来の方法でデジタル／アナログ変換を実行するデバイス100のブロック図を示す。デバイス100内で、デジタル回路110は、デジタル・データを受信し、処理し、且つデジタル入力信号d(n)を供給する。ここで、nは、サンプル・インデックスである。DAC120は、ゼロ次のホールドでデジタルからアナログに信号を変換し、アナログ入力信号

【数1】

$\tilde{x}(t)$

20

【0011】

を供給する。ここで、tは、連続時間に対する変数である。再構築フィルタ130は、アナログ入力信号をフィルタにかけ、アナログ出力信号

【数2】

$\tilde{y}(t)$

【0012】

を供給する。フィルタ130は、デジタル／アナログ変換によって生じる画像の減衰、ゼロ次のホールドによる周波数応答のたれに対する補償、などの様々な様々な機能を実行し得る。

30

【0013】

図1Bは、図1Aのデジタル入力信号d(n)及びアナログ入力信号

【数3】

$\tilde{x}(t)$

【0014】

のタイミング図を示す。デジタル入力信号は、離散時間のある瞬間n1、n2などにおけるデジタル値を含む。DAC120は、サンプル周期Tの全持続時間に対する各デジタル値を出力し、保持することによって、アナログ入力信号

40

【数4】

$\tilde{x}(t)$

【0015】

を生成する。アナログ入力信号は、サンプリングの瞬間(sampling instant)においてそのサンプリングの瞬間にに対する新しいデジタル値に変化する。

【0016】

50

図1Cは、ゼロ次のホールドによる時間領域ステップ関数の周波数応答Z(f)を示す。D A C 1 2 0によるゼロ次ホールドは、サンプル周期Tによって決定されているヌルの位置で、サイン(x)/x(sine(x)/x)の形を有する周波数応答Z(f)をもたらす。アナログ入力信号

【数5】

$$\tilde{x}(t)$$

【0017】

は、源(origin)(それはたれによってフィルタにかけられる)における所望の信号コンポーネント150のほかに1/Tの倍数(それはサイン(x)/xのノッチによってフィルタにかけられる)において画像160を含む。単純性のために、正の周波数コンポーネントのみが、図の1Cに示される。再構成フィルタ130は、1/Tより高い周波数で画像を減衰するように試み得る。さらに、再構成フィルタ130は、サイン(x)/x応答によりパスバンド内のたれに対して補償することを試み得る。再構成フィルタ130の複雑性は、信号の帯域幅、サンプル・レート、所望の画像減衰の量、所望のパスバンド応答、などの様々な要因に依存し得る。比較的複雑な再構成フィルタは、適用可能な必要条件を満たすために使用され、デバイス100の複雑性及びコストを増大させ得る。

【0018】

よい性能を実現すると同時に単純なアナログ回路を使用してデジタル/アナログ変換を実行することが望ましい。これは、1次又はより高次のホールドでデジタル/アナログ変換を実行することによって達成され得る。一般的に、ここで説明される技法は、ゼロ次のホールドより高い任意の次数に対して使用され得る。明瞭さのために、技法のある態様は、1次のホールド(F O H)に対して以下で詳細に説明される。

【0019】

図2は、1次のホールドでデジタル/アナログ変換を実行するデバイス200の設計のブロック図を示す。デバイス200内で、デジタル回路210は、デジタル・データを受信し、処理し、且つ、デジタル/アナログ変換回路220にデジタル入力信号d(n)を供給する。変換回路220内で、微分器230は、デジタル入力信号を微分し、微分された信号を供給する。ZOH回路240は、ゼロ次のホールドでデジタルからアナログに微分された信号を変換し、アナログ入力信号を供給する。積分器250は、アナログ入力信号を積分し、アナログ出力信号y(t)を供給する。

【0020】

変換回路220の全体の伝達関数は、以下のように表現され得る：

【数6】

$$H(s) = \left[ \frac{1 - z^{-1}}{T} \right]_{z=e^{j\omega T}} \frac{1 - e^{-sT}}{sT} \frac{1}{s} = \left( \frac{1 - e^{-sT}}{sT} \right)^2 \quad \text{式(1)}$$

ここで、 $s=j\omega$ であり、 $\omega$ は、弧度における周波数であり、 $z^{-1}$ は、1つのサンプル周期の遅延を示す。

【0021】

式(1)で示されるように、ゼロ次のホールドは、

## 【数7】

$$\frac{1-e^{-sT}}{sT}$$

## 【0022】

伝達関数を有する。一般において、L次のホールドは、

## 【数8】

$$\left(\frac{1-e^{-sT}}{sT}\right)^{L+1}$$

10

## 【0023】

の伝達関数を有する。ここで、L=0である。式(1)は、1次のホールドが図2で示された微分器230、ZOH回路240、および積分器250の組み合わせで達成され得る。

## 【0024】

デジタル／アナログ変換回路220は、いくつかの理由のために実施するために困難又は非現実的となり得る。第1に、理想／純粹な積分器は、一般的に実現不可能であり、低周波でポールを備えた回路によって近似され得る。第2に、ポールを備えた回路および積分器の両方は、アナログ出力信号の品質を大幅に低減するような、低周波ノイズ、ドロフト、かく乱の影響を受けやすい。

20

## 【0025】

1つの態様において、デジタル／アナログ変換回路は、1つ又は複数のポールを有する単純なアナログ回路、およびアナログ回路の低周波の振る舞いを改善するデジタル・フィードバック回路を含む。変換回路は、1次またはより高次のホールドでデジタル／アナログ変換を実行し、よりスムーズにアナログ出力信号を再構成し得る。1次またはより高次のホールドは、フィードバック制御技術を使用して、アナログ回路からのアナログ出力信号をガイドすることによって達成され得る。

30

## 【0026】

図3は、1次またはより高次のホールドおよびネガティブ・フィードバックを備えるデジタル／アナログ変換300の設計のブロック図を示す。変換回路300内で、逆モデル回路310は、以下で説明されるようにデジタル入力信号d(n)を受信し、処理し、第1のデジタル信号f(n)を供給する。フィードバック回路330は、第1のデジタル信号およびアナログ出力信号y(t)を受信し、所望のアナログ出力信号を供給する第2のデジタル信号s(n)を生成する。ZOH回路360は、ゼロ次のホールドでデジタルからアナログに第2のデジタル信号を変換し、アナログ入力信号x(t)を供給する。アナログ回路370は、アナログ入力信号で作動し、アナログ出力信号y(t)を供給する。アナログ回路370は、単一のポールで積分器を近似する、または複数のポールで高次のフィルタを改善し得る。

40

## 【0027】

フィードバック回路330は、いくつかの機能を実行する。第1に、フィードバック回路330は、アナログ回路370の低周波の振る舞いを改善することを試みる。第2に、フィードバック回路330は、第1のデジタル信号の信号コンテンツをバスすることを試みる。モデル参照システム320を形成する、フィードバック回路330、ZOH回路360、およびアナログ回路370の組み合わされた伝達関数は、ZOH回路360およびアナログ回路370の組み合わされた伝達関数と厳密に一致するように設計され得る。逆モデル回路310は、変換回路300の全体の応答が広帯域幅にわたってフラットになるように、モデル参照システム320の伝達関数の逆数となる伝達関数を有し得る。

50

## 【0028】

図4は、モデル参照システム320aおよびフィードバック回路330aのブロック図を示す。これらは、図3のモデル参照システム320およびフィードバック回路330の1つの設計である。単純性のために、図4は、s-ドメインの様々な回路の伝達関数を示す。それは、連続時間の中でアナログ回路および信号のために一般に使用される。フィードバック回路330aは、第1のデジタル信号 $f(n)$ およびアナログ出力信号 $y(t)$ を受信し、第2のデジタル信号 $s(n)$ を生成する。

## 【0029】

フィードバック回路330a内で、モデル回路340は、第1のデジタル信号 $f(n)$ を受信し、モデル出力信号 $u(n)$ を供給する。ADC380は、アナログ出力信号 $y(t)$ を受信してデジタル化し、デジタル化された出力信号 $v(n)$ を供給する。加算器342は、モデル出力信号とデジタル化された出力信号との差をとり、エラー信号 $e(n)$ を供給する。ループ・フィルタ350は、エラー信号をフィルタにかけ、フィルタにかけられた信号を供給する。加算器352は、フィルタにかけられた信号および第1のデジタル信号を合計し、第2のデジタル信号 $s(n)$ を供給する。

10

## 【0030】

フィードバック回路330a、ZOH回路360およびアナログ回路370は、モデル参照適応制御システムを形成し、適応制御技術を使用して分析され得る。ループ・フィルタ350は、適応制御システムのノイズ・フィルタリングおよびループ・ダイナミクスを決定する。1つの設計において、ループ・フィルタ350の伝達関数 $F(s)$ は、以下のように表現され得る：

20

## 【数9】

$$F(s) = \frac{1}{s + p} \quad \text{式(2)}$$

ここで、 $p$ は、ループ・フィルタのポールの周波数である。

## 【0031】

伝達関数 $F(s)$ は、加算器342および352、ループ・フィルタ350、ZOH回路360、アナログ回路370およびADC380によって形成されたループ332の閉ループ帯域幅を決定する。ループ・フィルタ350のための狭帯域幅は、より大きなノイズ・フィルタリングを供給するが、伝達に対してより遅い応答をも供給し得る。反対に、ループ・フィルタ350のための広帯域幅は、より小さいノイズ・フィルタリングを供給するが、伝達に対してより速い応答をも供給し得る。ループ・フィルタ350の帯域幅は、所望のノイズ・フィルタリングおよびループ・ダイナミクスを達成するために選択され得る。

30

## 【0032】

フィードバック回路330aは、アナログ出力信号のための広帯域変調を達成するために2ポイントまたはデュアル・ポート変調を実施する。フィードバック回路330aの内で、第1のデジタル信号 $f(n)$ は、広域変調パス(`highpass modulation path`)および低域変調パス(`lowpass modulation path`)の両方に供給される。広域変調パスにおいて、第1のデジタル信号は、フィードバック回路330aの入力から加算器352に直接供給される。低域変調パスにおいて、第1のデジタル信号は、モデル回路340、加算器342およびループ・フィルタ350を経由して加算器352に供給される。低域変調パスの帯域幅は、モデル回路340およびループ・フィルタ350によって決定され、比較的狭くなり得る。別々の広域および低域変調パスを経由して第1のデジタル信号を適用することによって、適応制御システムは、第2のデジタル信号に適応制御システムの閉ループ帯域幅より広い信号帯域幅を供給することができる。

40

50

## 【0033】

モデル回路340は、M(s)の伝達関数を有し、ZOH回路360は、Z(s)の伝達関数を有し、アナログ回路370は、s-ドメイン内のG(s)の伝達関数を有する。モデル回路340の伝達関数は、以下のようにZOH回路360およびアナログ回路370の組み合わされた伝達関数と一致することが定義され得る：

## 【数10】

$$M(s) = Z(s) \cdot G(s) \quad \text{式(3)}$$

10

## 【0034】

式(3)が達成される場合、フィードバック回路330a、ZOH回路360およびアナログ回路370の組み合わされた伝達関数は、Z(s)・G(s)に等しいだろう。この場合、フィードバック回路330aは、低周波の振る舞いを改善する一方で全体の伝達関数に最小限の影響を及ぼす。

## 【0035】

図5は、モデル参照制御システム520のブロック図を示す。それは、図3のモデル参照システム320の1つのモデルである。単純性のために、図4のZOH回路360およびADC380は、システム520から省略されている。システム520において、モデル回路540、加算器542、ループ・フィルタ550および加算器552は、図4のモデル回路340、加算器342、ループ・フィルタ350および加算器352、それぞれと同じ方法で結合される。アナログ回路570は、加算器552の出力に直接結合される。

20

## 【0036】

1次のホールドに対して、アナログ回路570の伝達関数G(s)およびモデル回路540の伝達関数M(s)は、以下のように表現され得る：

## 【数11】

$$G(s) = \frac{b}{s+a}, \text{ および} \quad \text{式(4)} \quad \text{30}$$

$$M(s) = \frac{b_m}{s+a_m} \quad \text{式(5)}$$

ここで、aは、アナログ回路570のポールの周波数であり、

bは、アナログ回路570の利得であり、

$a_m$ は、モデル回路540のポールの周波数であり、

$b_m$ は、モデル回路540の利得である。

40

## 【0037】

式(4)の伝達関数G(s)は、レジスタ(R)およびコンデンサ(C)、受動RCフィルタ、スイッチ・キャパシタ・フィルタ、等と並列の電流ソースでインプリメントされ得る。ポール周波数aは、レジスタとコンデンサの値によって決定され得る。利得bは、電流ソースおよび/またはレジスタとコンデンサを駆動する他の能動回路の利得に依存し得る。

## 【0038】

モデル参照制御システム520において、アナログ回路570は、制御されることになっているプラント(plant)である。用語「プラント」は、出力が適切な入力を適用することにより制御されることになっているブロックのための制御システム内で一般に使

50

用される。モデル参照制御システム 520 のために、(式(4)の伝達関数  $G(s)$  を備えたアナログ回路 570 である) プラントは、(式(5)の伝達関数  $M(s)$  を備えたモデル回路 540 である) モデルの後に続くことが推奨される。モデル回路 540 のポール周波数  $a_m$  および利得  $b_m$  がアナログ回路のポール周波数  $a$  および利得  $b$  と一致する場合、システム 520 全体の伝達関数は、モデル回路 540 の伝達関数と同じである。

#### 【0039】

アナログ回路 570 のポール周波数および利得は、所望の値にセットされ得る。しかしながら、コンポーネントの許容範囲および／または他の要因により、アナログ回路 570 のポール周波数および利得が、所望の値と異なる、および／または既知でなくなり得る。この場合、アナログ回路 570 のポール周波数および利得は、適応的に決定され得る。

10

#### 【0040】

図 6 は、モデル回路 540a のブロック図を示す。それは、図 5 のモデル回路 540 の 1 つの設計である。この設計において、モデル回路 540a は、アナログ回路 570 のパラメータ  $a$  および  $b$  を適応的に推定し、その伝達関数  $M(s)$  のために推定されたパラメータ  $a_m$  および  $b_m$  を適用する。

#### 【0041】

モデル回路 540a 内で、加算器 612 は、乗算器 626 の出力を受信し、第 1 のデジタル信号  $f(n)$  とこの出力との差をとる。累算器 614 は、加算器 612 の出力を累算し、累算された信号  $k(n)$  を供給する。乗算器 616 は、累算された信号と回路 634 からの  $b_m$  との積をとり、モデル出力信号  $u(n)$  を供給する。

20

#### 【0042】

乗算器 622 は、加算器 542 から累算された信号  $k(n)$  とエラー信号  $e(n)$  との積をとる。回路 624 は、利得  $g_1$  で乗算器 622 の出力をスケールし、スケールされた結果を累算し、アナログ回路のポール周波数の推定値である、 $a_m$  を供給する。乗算器 626 は、累算された信号  $k(n)$  と  $a_m$  との積をとり、加算器 612 にその出力を供給する。

#### 【0043】

乗算器 632 は、第 1 のデジタル信号  $f(n)$  とエラー信号  $e(n)$  との積をとる。回路 634 は、利得  $-g_2$  で乗算器 632 の出力をスケールし、スケールされた結果を累算し、アナログ回路の利得  $b$  の推定値である、 $b_m$  を供給する。

30

#### 【0044】

回路 624 の利得  $g_1$  は、パラメータ  $a_m$  の適応レートを決定し、回路 634 の利得  $g_2$  は、パラメータ  $b_m$  の適応レートを決定する。利得  $g_1$  および  $g_2$  は、 $a_m$  および  $b_m$  それぞれのための所望の適応レートを達成するために選択され得る。一旦、適応が収束していると、 $a_m$  は、 $a$  と厳密に一致し、 $b_m$  は、 $b$  と厳密に一致するべきである。その後、モデル回路 540a は、式(5)で示された伝達関数  $M(s)$  をインプリメント (implement) することになる。

#### 【0045】

図 6 は、アナログ回路 570 のパラメータを適応的に推定し、モデル回路 540 に推定されたパラメータを適用するための設計の 1 つを示す。さらに、アナログ回路 570 のパラメータは、他の方法で推定され得る。

40

#### 【0046】

図 7 は、1 次あるいはより高い次数のホールドおよびネガティブ・フィードバックを備えるデジタル／アナログ変換回路 700 の設計のブロック図を示す。変換回路 700 は、逆モデル回路 710、フィードバック回路 730、ZOH 回路 760 およびアナログ回路 770 を含む。それは、図 3 の逆モデル回路 310、フィードバック回路 330、ZOH 回路 360 およびアナログ回路 370 それぞれと同じ方法で結合される。

#### 【0047】

図 7 に示される設計において、フィードバック回路 730 は、モデル回路 340、加算器 342、ループ・フィルタ 350、加算器 352 および ADC 380 それぞれと同じ方

50

法で連結される、モデル回路 740、加算器 742、ループ・フィルタ 750、加算器 752 および ADC 780 を含む。フィードバック回路 730 は、適応回路 790 をさらに含む。適応回路 790 は、第 1 のデジタル信号  $f(n)$ 、エラー信号  $e(n)$ 、第 2 のデジタル信号  $s(n)$ 、および / またはデジタル化された出力信号  $v(n)$  を受信し得る。適応回路 790 は、ZOH 回路 760 の伝達関数  $Z(s)$  および / またはアナログ回路 770 の伝達関数  $G(s)$  のパラメータを推定し得る。モデル回路 740 の伝達関数  $M(s)$  は、ZOH 回路 760 およびアナログ回路 770 の組み合わされた伝達関数と一致するために推定されたパラメータに基づいて定義され得る。1 次のホールドのために、適応回路 790 は、図 6 に示されるように実施され得る。より高い次数のホールドのために、適応回路 790 は、ランダウ、Y.D. 著、1979 年、マーセル・デッカー社、「適応制御、モデル参照アプローチ」(Landau, Y.D., "Adaptive Control, The Model Reference Approach," Marcel Dekker, Inc., 1979) によって説明されるフィードバック制御技術を使用して実施され得る。逆モデル回路 710 は、モデル回路 740 の伝達関数  $M(s)$  の逆数である、伝達関数を有する。

#### 【0048】

デジタル / アナログ変換回路 700 は、1 次またはより高い次数のホールドを実施し得る。正確な  $L$  次のホールドのために、プラントは、カスケードで結合された  $L$  個の積分器を含む。ここで、 $L$  は、1 又はそれより大きい。これら  $L$  個の積分器は、十分高い周波数における  $L$  個のポールで近似され得る。 $L$  次のホールドのために、アナログ回路 770 は、 $L$  個の積分器を近似するために  $L$  個のポールを含み得る。例として、2 次のホールドに対して、アナログ回路 770 は、2 つのポールを含み、以下の伝達関数を有し得る：

#### 【数 12】

$$G(s) = \left( \frac{b_1}{s + a_1} \right) \cdot \left( \frac{b_2}{s + a_2} \right) \quad \text{式(6)}$$

ここで、 $a_1$  および  $a_2$  は、2 つのポールの周波数であり、

$b_1$  および  $b_2$  は、2 つのポールに関連する利得である。

#### 【0049】

任意の与えられた次数  $L$  に対して、モデル回路 740 は、ZOH 回路 760 およびアナログ回路 770 の組み合わされた伝達関数を有する。

#### 【0050】

明瞭さのために、図 5 および図 6 は、図 4 の ZOH 回路 360 および ADC 380 を省略する。更に、図 4 乃至図 7 は、 $s$  - ドメインの様々な回路の伝達関数を示す。それは、連続時間内の信号およびアナログ回路のために一般的に使用される。実際の実施において、アナログ回路、および ZOH 回路と ADC の一部だけがアナログ / 連続的であり、残りの回路は、デジタル / 離散時間的である。したがって、ZOH 回路および ADC の左側の全ての回路は、デジタル回路で実施され得る。

#### 【0051】

モデル回路が離散時間でデジタルに実施されるので、アナログ回路は、サンプル化の瞬間にに対応する離散時間でのみ制御され得る。サンプル化の瞬間の間、アナログ出力信号  $y(t)$  は、アナログ回路の連続時間応答に依存する。ZOH 回路は、第 2 のデジタル信号  $s(n)$  を受信し、例えば図 1B で示さるような、第 2 のデジタル信号の各サンプルに対してアナログ回路にステップ応答を供給する。サンプル化の瞬間の間のアナログ出力信号は、アナログ回路のステップ応答によって決定される。

#### 【0052】

1 次のホールドのために、式 (4) で示される単一ポールの伝達関数  $G(s)$  を備えるアナログ回路のステップ応答  $g(t)$  は、以下のように表現され得る：

10

20

30

40

## 【数13】

$$g(t) = \frac{b}{a} \cdot (1 - e^{-at}) = \frac{b}{a} \cdot \left( a \cdot t - \frac{(a \cdot t)^2}{2!} + \frac{(a \cdot t)^3}{3!} + \dots \right) \quad \text{式(7)}$$

ここで「!」は、階乗を示す。

## 【0053】

式(7)において、 $b/a$ は、DCでの利得であり、スケーリング・ファクタである。ステップ応答は、式(7)の第2の等号の右において異なる次数の一連の項で近似され得る。第1の項  $a \cdot t$  は、傾き  $a$  の直線である。後の項は、直線に対する誤差と見なされ得る。ポール周波数がサンプリング周波数より非常に低い、又は  $a << 1/T$  である場合、 $g(t)$  は、サンプルとの間でほとんど線形である。例えば、ポール周波数は、キロヘルツ(kHz)のオーダであり得るが、サンプリング周波数は、メガヘルツ(MHz)のオーダであり得る。ポール周波数  $a$  が比較的低い場合、アナログ出力信号は、近接区分的線形補間になり、デジタル/アナログ変換回路は、1次のホールドに接近するだろう。

10

## 【0054】

図8は、1次のホールドを備えるデジタル/アナログ変換回路300または700のZOH回路からアナログ入力信号  $x(t)$  およびアナログ回路からのアナログ出力信号  $y(t)$  のタイミング図を示す。アナログ入力信号  $x(t)$  は、点線で示され、各サンプル化の瞬間  $n_1, n_2, \dots$  などでステップ応答を有する。アナログ出力信号  $y(t)$  は、式(4)で示される単一のポールの伝達関数  $G(s)$  によりサンプル化の瞬間の間に近似的に直線的に変化する。実際には、図8のFOH応答は、必要な処理のための時間を割り当てるために少なくとも1つのサンプルで遅延することになる。

20

## 【0055】

図9は、ここで説明された技術に基づいてデジタル/アナログ変換を実行するプロセス900の設計を示す。デジタル入力信号は、デジタル信号を得るために、逆モデル回路で処理され得る(ブロック912)。第1のデジタル信号およびアナログ回路からのアナログ出力信号は、第2のデジタル信号を得るために、フィードバック回路で処理され得る(ブロック914)。第2のデジタル信号は、アナログ回路のためのアナログ入力信号を得るために、ゼロ次のホールドでデジタルからアナログに変換され得る(ブロック916)。アナログ入力信号は、アナログ出力信号を得るために、アナログ回路を通過し得る(ブロック918)。

30

## 【0056】

アナログ回路は、1つ又は複数のポールを備え得る。1次のホールドに対して、アナログ回路は、式(4)で示される伝達関数を有する。2次のホールドに対して、アナログ回路は、式(6)で示される伝達関数を有する。アナログ回路の各ポール周波数は、第1のデジタル信号のサンプリング周波数より非常に低い(例えば、少なくとも10倍より低い)ことになり得る。

40

## 【0057】

図10は、図9内のブロック914の設計を示す。第1のデジタル信号は、モデル出力信号を得るために、モデル回路で処理され得る(ブロック1012)。アナログ出力信号は、デジタル化された出力信号を得るために、ADCでデジタル化され得る(ブロック1014)。デジタル化された出力信号は、エラー信号を得るために、モデル出力信号から引かれ得る(ブロック1016)。エラー信号は、フィルタにかけられた信号を得るために、ループ・フィルタでフィルタにかけられ得る(ブロック1018)。フィルタにかけられた信号は、第2のデジタル信号を得るために、第1のデジタル信号との和をとり得る(ブロック1020)。

## 【0058】

モデル回路は、ZOH回路およびアナログ回路の伝達関数に基づいて伝達関数を決定し

50

得る。適応回路は、アナログ回路の少なくとも1つのパラメータを推定し、モデル回路の伝達関数は、推定された1つ又は複数のパラメータに基づいて実施され得る。例えば、適応回路は、アナログ回路のポール周波数および利得を推定し、モデル回路の伝達関数は、推定されたポール周波数および利得に基づいて実施され得る。ループ・フィルタは、ノイズ・フィルタリングを実行し、第1のデジタル信号の帯域幅よりはるかに小さい帯域幅を有し得る。

【0059】

図4乃至7に示される設計において、主なノイズ・ソースは、アナログ回路からのフリッカー・ノイズ及びホワイト・ノイズとフィードバック・パスのADCからのフィードバック・ノイズである。ホワイト・ノイズは、大部分はループ帯域幅の外側にあり、そのため、制御又は緩和されない。アナログ回路は、ホワイト・ノイズの許容可能なレベルを達成するために設計され得る。フリッカー・ノイズは、低周波で支配的であり、ループ帯域幅が十分に高い場合、ループによって抑制され得る。ループの最小の帯域幅は、フリッカー・ノイズの（例えば、より大きな）コーナー周波数に依存し得る。ループの最大の帯域幅は、フィードバック・パスのADCによって注入されたノイズに依存し得る。ループ帯域幅は、抑制すべきフリッcker・ノイズの量（より大きなループ帯域幅がより良い）と、抑制すべきフィードバック・ノイズの量（より小さいループ帯域幅がより良い）との間のトレードオフに基づいて選択され得る。

【0060】

ノイズ形成コンバータは、フィードバック・ノイズを緩和するためにフィードバック・パス内のADCのために使用され得る。ノイズ形成コンバータは、大部分の量子化ノイズが例えば、ループ・フィルタの阻止帯域の、高周波数にブッシュされるようなアナログ出力信号をデジタル化することができる。ここで説明されるDACが、直交アップコンバータの同相(I)および直交(Q)ブランチの各々で使用される場合、および1次のシグマ・デルタ

【数14】

( $\Sigma\Delta$ )

【0061】

が各DACのフィードバック・パスで使用される場合、エラー・ベクトルの大きさは、以下のように表現され得る：

【数15】

$$EVM = 100 \cdot \left( \frac{\pi^2}{3} q^2 \frac{(2/2^N)^2}{12} \frac{1}{OSR^3} \right)^{1/2} \quad \text{式(8)}$$

ここで、 $q$ は、IまたはQ信号のピーク対二乗平均(rms)比であり、

$N$ は、各 $\Sigma\Delta$ 変調器からのビットの数であり、

OSRは、信号のバンド幅(例えば、この例のループ・バンド幅)で除算されたサンプリング周波数であるオーバーサンプリング率である。

【0062】

例えば、1ビットの1次

【数16】

$\Sigma\Delta$

【0063】

10

20

30

40

50

変調器は、4倍のチップ・レートでサンプリングされた広帯域符号分割多元接続（W C D M A）信号のためのIとQのD A Cで使用され得る。この場合、50 K H zのループ帯域に対して

【数17】

$$q \approx 2, \text{ および } EVM \approx 0.06\%$$

【0064】

である。この低いE V Mは、無視し得る。

【0065】

一般的に、ループは、ループ帯域幅未満のコーナー周波数でフリッカー・ノイズを拒絶することができる。より高いループ帯域幅は、フリッcker・ノイズのためのより高いコーナー周波数に有効であるように使用され得る。しかしながら、A D Cからのフィードバック・ノイズは、過度の低下を回避するために対応する量によってより小さくなるべきである。

10

【0066】

ここで説明されるデジタル／アナログ変換回路は、Z O H回路のダイナミック・レンジ要求を低減し得る。図3および図7に示されるように、デジタル／アナログ変換回路は、逆モデル回路を含み得る。逆モデル回路は、微分器の近似であり得る。この場合、Z O H回路に供給される第2のデジタル信号s(n)は、デジタル入力信号d(n)の導関数であり、この導関数は、離散時間の隣接したサンプルの間の差である。デジタル入力信号d(n)は、典型的にスムーズであり、オーバーサンプルされる。そのため、デジタル入力信号内の隣接したサンプルとの間のピーク差は、デジタル入力信号それ自身のピークよりはるかに小さいことになり得る。したがって、Z O H回路の入力ダイナミック・レンジは、低減され得る。例として、W C D M Aについて、1次のホールドは、2以上のビットでZ O H回路の入力ダイナミック・レンジを低減し、2次のホールドは、4以上のビットで入力ダイナミック・レンジを低減し得る。

20

【0067】

ここで説明されるデジタル／アナログ変換回路は、（例えば、1つ又は複数のポールを備えた、）単純なアナログ回路を利用し、サンプル・データ制御技法でアナログ回路の出力をガイドする。一般的に、アナログ回路の順序（ひいては複雑性）は、アナログ出力信号の再構成を円滑に決定することになる。再構成フィルタは、アナログ回路の後に必要又は不必要であり得る、またはデジタル／アナログ変換回路および出力信号要求の設計に依存して単純化され得る。

30

【0068】

ここで説明されたデジタル／アナログ変換回路は、いくつかの利点を提供し得る。第1に、アナログ回路は、比較的単純、例えば1つのポール、になり得る。単純なアナログ回路は、回路パラメータ（例えば、ポール周波数aおよび利得b）がより容易に識別され、その後デジタル処理で修正されることを意味し得る。第2に、サンプル・レートは、アナログ回路を制御する必要性のみに基づいて判定され、単にデジタル画像の周波数によって判定されない。より低いサンプリング・レートは、電力デジタル入力信号に使用され得る。それは電力消費量を低減する。第3に、Z O H回路の入力ダイナミック・レンジは、フィードバック回路より前に逆モデル回路によって低減され得る。

40

【0069】

以上で説明された利点は、フィードバック回路のより大きな複雑性の費用において高次のホールドに対してより大きな利点がある。例えば、高次のホールドは、よりスムーズな信号再構成、Z O H回路のためのより小さい入力ダイナミック・レンジ、より小さいサンプル・レート、などを供給し得る。例として、2次のホールドを備えたW C D M Aについて、サンプル・レートは、8倍と同程度、例えば32倍のチップ・レート（チップ×32（chip×32））から4倍のチップ・レート（チップ×4（chip×4））、まで

50

低減され得る。

【0070】

ここで説明されるデジタル／アナログ変換回路は、通信、計算、ネットワーキング（networking）、個人電子機器、などの様々なアプリケーションに使用され得る。例えば、デジタル／アナログ変換回路は、ワイヤレス通信デバイス、携帯電話、携帯情報端末（PDA）、ハンドヘルド・デバイス、ゲーミング・デバイス、コンピューティング・デバイス、ラップトップ・コンピュータ、家庭用電子デバイス、パソコン、コードレス・ホン、などに使用され得る。ワイヤレス通信デバイスのデジタル／アナログ変換回路の例示的な使用が以下で説明される。

【0071】

図11は、無線通信システムのためのワイヤレス通信デバイス1100の設計のブロック図を示す。ワイヤレス・デバイス1100は、携帯電話、端末、ハンドセット、ワイヤレス・モデム、などであり得る。無線通信システムは、cdma2000システム、WC D M Aシステム、グローバル・システム・フォー・モバイル・コミュニケーションズ（GSM）システム、などであり得る。

【0072】

ワイヤレス・デバイス1100は、受信バスおよび送信バスを介して双方向通信を供給することができる。受信バスにおいて、（図示されていない）基地局によって送信された信号が、アンテナ1110によって受信され、受信機1112に供給される。受信機1112は、受信信号を条件付け、セクション1120内のADC1114に入力ベースバンド信号を供給する。送信バスにおいて、DAC1116が、送信されるデータを受信し、送信機1118に出力ベースバンド信号を供給する。DAC1116は、ここで説明されるデジタル／アナログ変換回路と共に実施され得る。送信機1118は、ベースバンド出力信号を処理し、条件付け、変調された信号を生成する。それは、基地局にアンテナ1110を介して送信される。受信機1112および送信機1116は、cdma2000、WC D M A、GSM、などをサポートし得る。

【0073】

セクション1120は、例えば、モデム1122、縮小命令セット・コンピュータ／デジタル・シグナル・プロセッサ（RISC/DSP）1124、コントローラ／プロセッサ1126、メモリ1128、および入力／出力（I/O）回路1130のような様々な処理、インターフェース、メモリ・ユニットを含む。モデム・プロセッサ1122は、（例えば、符号化、変調、復調、復号化、などの）データ送信およびデータ受信のための処理を実行し得る。RISC/DSP1124は、ワイヤレス・デバイス1100のため的一般的および特定の処理を実行し得る。コントローラ／プロセッサ1126は、セクション1120の様々なユニットの操作を命令し得る。メモリ1128は、セクション1120の様々なユニットのためのデータおよび／または命令を格納し得る。I/O回路1130は、DAC1132を介して外部のI/Oデバイス1140と通信し得る。それは、ここで説明されたデジタル／アナログ変換回路で実施され得る。

【0074】

ここで説明されたデジタル／アナログ変換回路は、様々な手段によって実施され得る。例えば、デジタル／アナログ変換回路は、ハードウェア、ファームウェア、ソフトウェア、又はそれらの組み合わせで実施され得る。ハードウェアの実施について、デジタル／アナログ変換回路の様々な回路は、集積回路（IC）、アナログIC、無線周波数IC（RFIC）、混合信号IC、特定用途向け集積回路（ASIC）、デジタル・シグナル・プロセッサ（DSP）、デジタル信号処理デバイス（DSPD）、プログラム可能な論理回路（PLD）、フィールドプログラム可能なゲートアレイ（FPGA）、プロセッサ、コントローラ、マイクロ・コントローラ、マイクロプロセッサー、電子デバイス、ここで説明された機能を実施するように設計された他の電子ユニット、コンピュータ、あるいはこれらの組み合わせ上で実施され得る。

【0075】

10

20

30

40

50

さらに、デジタル／アナログ変換回路は、相補型金属酸化膜半導体（C M O S）、N-チャネルM O S（N-M O S）、P-チャネルM O S（P-M O S）、バイポーラ接合トランジスタ（B J T）、バイポーラC M O S（B i C M O S）、シリコン・ゲルマニウム（S i G e）、ガリウム・アルセニド（G a A s）、などの様々な様々なI Cプロセス技法で製造され得る。

【0076】

デジタル／アナログ変換回路のある部分は、ここで説明された機能を実施する、ファームウェアおよび／またはソフトウェア・コード（例えば、手順、関数、モジュール、命令、など）で実施され得る。一般的に、ファームウェアおよび／またはソフトウェア・コードを明確に具体化する任意のコンピュータ／プロセッサ可読媒体は、ここで説明された技法を実施するのに使用され得る。例えば、ファームウェアおよび／またはソフトウェア・コードは、メモリ（例えば、図11のメモリ1128）に格納され、プロセッサ（例えば、プロセッサ1126）によって実行され得る。メモリは、プロセッサの内部又はプロセッサの外部でインプリメントされ得る。

【0077】

ファームウェアおよび／またはソフトウェア・コードは、コンピュータ可読媒体上に格納されるか、又はそれを通じて送信され得る。コンピュータ可読媒体は、ある場所から別の場所にコンピュータ・プログラムの転送を容易にする任意の媒体を含むコンピュータ記憶媒体と通信媒体との両方を含む。記憶媒体は、コンピュータによってアクセスされることができる任意の利用可能な媒体であり得る。例として、そして限定ではなく、そのようなコンピュータ可読媒体は、ランダム・アクセス・メモリ（R A M）、読み出し専用メモリ（R O M）、不揮発性ランダム・アクセス・メモリ（N V R A M）、プログラマブル読み出し専用メモリ（P R O M）、電子的に消去可能・書き込み可能なP R O M（E E P R O M）、F L A S Hメモリ、または他の光ディスク・ストレージ、磁気ディスク・ストレージまたは他の磁気ストレージデバイス、あるいは命令またはデータ構造の形態で望ましいプログラムコードを搬送し、または記憶するために使用されることができ、そしてコンピュータによってアクセスされることができる他の任意の媒体、を備えることができる。また、任意の接続は、コンピュータ可読媒体と適切に名づけられることもある。例えば、ソフトウェアが、同軸ケーブル、光ファイバケーブル、ツイストペア（twisted pair）、デジタル加入者回線（D S L）、または赤外線、無線、マイクロ波などのワイヤレス技術を使用して、ウェブサイト、サーバ、または他のリモートソースから送信される場合、そのときには同軸ケーブル、光ファイバケーブル、ツイストペア、D S L、または赤外線、無線、マイクロ波などのワイヤレス技術は、媒体の定義の中に含まれる。ここにおいて使用されるようなディスク（Disk）およびディスク（disc）は、コンパクトディスク（C D：compact disc）、レーザーディスク（登録商標）（laser disc）、光ディスク（optical disc）、デジタル多用途ディスク（D V D：digital versatile disc）、フロッピー（登録商標）ディスク、およびブルーレイディスク（blu-ray disc）を含み、ここでディスク（disks）は通常、データを磁気的に再生するが、ディスク（discs）は、レーザを用いて光学的にデータを再生する。上記の組み合わせもまた、コンピュータ可読媒体の範囲内に含められるべきである。

【0078】

ここに記述されたデジタル／アナログ変換回路をインプリメントする装置は、スタンド・アロンのデバイスかもしれないし、あるいは大型装置の一部かもしれない。デバイスは、（i）スタンド・アロンI C（i i）データおよび／または命令を格納するためのメモリI Cを含む、1つ又は複数のI Cのセット、（i i i）R F受信機（R F R）あるいはR F送信機／受信機（R T R）のようなR F I C、（i v）移動局モデム（M S M）のようなA S I C、（v）他のデバイス内に埋め込まれ得るモジュール、（v i）受信機、携帯電話、ワイヤレス・デバイス、ハンドセット、あるいはモバイル・ユニット、（v i i）などであり得る。

【0079】

10

20

30

40

50

本開示の前の説明は、当業者が本開示を行なえるまたは使用することができるために提供される。本開示に対する様々な修正は、当業者に容易に明白になり、ここに定義された一般的な原理は、本開示の範囲から外れずに、他の変形として適用され得る。したがって、本開示は、ここに説明した例示及び設計に制限されるように意図したものではなく、ここに開示された原理および新規な特徴と一致する最も広い範囲が許容されることになる。

【図 1 A】

【図 1 B】

【図 1 C】

【図 2】

【図3】

図3

FIG. 3

【図4】

図4

FIG. 4

【図5】

図5

FIG. 5

【図6】

図6

FIG. 6

【図 7】

FIG. 7

【図 8】

FIG. 8

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

---

フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 バランタイン、ゲイリー・ジョン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 柳下 勝幸

(56)参考文献 特開昭63-211921(JP, A)

特開平05-259910(JP, A)

特表2002-519925(JP, A)

特開平06-177842(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M1/00-1/88