(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년08월29일

(11) 등록번호 10-0855083

(24) 등록일자 2008년08월22일

(51) Int. Cl.

H01L 21/20 (2006.01)

(21) 출원번호 10-2003-7006179

(22) 출원일자 2003년05월03일

심사청구일자 2006년09월19일

번역문제출일자 2003년05월03일

(65) 공개번호 10-2003-0051782

(43) 공개일자 2003년06월25일

(86) 국제출원번호 PCT/FR2001/003401

국제출원일자 2001년11월05일

(87) 국제공개번호 WO 2002/37556

국제공개일자 2002년05월09일

(30) 우선권주장

00/14170 2000년11월06일 프랑스(FR)

(56) 선행기술조사문헌

US05391257 A1

전체 청구항 수 : 총 23 항

심사관 : 이시근

(54) 타겟 기판에 결합된 박막을 구비하는 적층 구조의 제조 방법

### (57) 요약

본 발명은 타겟 기판에 결합된 적어도 하나의 박막을 구비하는 적층 구조를 제조하는 방법에 관한 것으로, 다음의 단계를 포함한다.

- 제 1 콘택면이라 불리우는 자유면을 갖는 박막을 최초 기판으로부터 형성하는 단계;

- 상기 자유면을 중간 서포트의 면과 결합 접촉시켜, 얻은 구조가 상기 최초 기판을 씌우는 이 후의 단계와 양립할 수 있도록 하는 단계;

- 상기 최초 기판을 씌우하여, 제 2 콘택면이라 불리우고 상기 제 1 콘택면과 대향하는 상기 박막의 자유면을 노출시키는 단계;

- 상기 중간 서포트의 적어도 일부를 제거하여 상기 적층 구조를 얻는 단계;

**대표도** - 도5

(72) 발명자

잘라기에에릭

프랑스에프-38410쌩-마르땡-뒤리아쥬레쁘네슈맹데

루205

르페르트르파브리스

프랑스에프-38000그르노블깨종킨드33

(81) 지정국

국내특허 : 아랍에미리트, 안티구와바부다, 알바니아, 아르메니아, 오스트리아, 오스트레일리아, 아제르바이잔, 보스니아 헤르체고비나, 바베이도스, 불가리아, 브라질, 벨라루스, 벨리즈, 캐나다, 스위스, 리히텐슈타인, 중국, 콜롬비아, 코스타리카, 쿠바, 체코, 독일, 덴마크, 도미니카, 알제리, 에쿠아도르, 에스토니아, 스페인, 핀란드, 영국, 그라나다, 그루지야, 가나, 감비아, 크로아티아, 헝가리, 인도네시아, 이스라엘, 인도, 아이슬랜드, 일본, 케냐, 키르키즈스탄, 북한, 대한민국, 카자흐스탄, 세인트루시아, 스리랑카, 리베이라, 레소토, 리투아니아, 룩셈부르크, 라트비아, 모로코, 몰도바, 마다가스카르, 마케도니아공화국, 몽고, 말라위, 멕시코, 모잠비크, 노르웨이, 뉴질랜드, 오만, 필리핀, 폴란드, 포르투칼, 루마니아, 러시아, 수단, 스웨덴, 싱가포르, 슬로베니아, 슬로바키아, 시에라리온, 타지키스탄, 투르크맨, 터어키, 트리니아드토바고, 탄자니아, 우크라이나, 우간다, 미국, 우즈베키스탄, 베트남, 세르비아 앤 몬테네그로, 남아프리카, 짐바브웨

AP ARIPO특허 : 가나, 감비아, 케냐, 레소토, 말라위, 모잠비크, 수단, 시에라리온, 스와질랜드, 탄자니아, 우간다, 짐바브웨

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탄, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크맨

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 리히텐슈타인, 사이프러스, 독일, 덴마크, 스페인, 핀란드, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 터어키

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 적도 기니, 기니 비사우, 말리, 모리타니, 니제르, 세네갈, 차드, 토고

## 특허청구의 범위

### 청구항 1

타겟 기판(15)에 결합된 적어도 하나의 박층을 구비하는 적층 구조를 제조하기 위한 방법에 있어서,

a) 최초 기판의 잔여 부분으로부터 막(6)을 분리하는 약화된 층(5)을 형성하기 위하여, 상기 최초 기판 내부로 가스종을 도입하는 단계를 포함하는, 제 1 콘택면(8)이라 불리는 자유면을 갖는 박층(7)의 형성 단계,

b) 상기 제 1 콘택면을 중간 서포트(10)의 면(11)과 결합 접촉(9)시켜, 얻은 구조가 후속되는 상기 최초 기판의 씨닝(thinning)을 가능하도록 하는 단계,

c) 상기 약화된 층(5)에서 상기 최초 기판(1) 내에 과쇄를 얻기 위한 바람직한 처리를 행하고, 제 2 콘택면(14)이라 불리우고 상기 제 1 콘택면(8)과 대향하는 상기 박층의 자유면을 노출시킴으로써 상기 최초 기판(1)을 씨닝하는 단계,

d) 타겟 기판(15)의 면을 상기 제 2 콘택면(14)의 적어도 일부분과 결합 접촉시켜, 여기서 얻은 구조가 후속되는 상기 중간 서포트의 전부 또는 일부의 제거를 가능하도록 하는 단계,

e) 상기 적층 구조를 얻기 위하여 상기 중간 서포트(10)의 적어도 일부분을 제거하는 단계를 포함하고,

단계 c)의 씨닝을 수행하는 동안 결합 결합을 피할 수 있도록 단계 a)에서 박층(7)을 형성함으로써 단계 b)에서 상기 구조가 얻어지는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서, 상기 박층과 접촉하는 상기 중간 서포트 및/또는 상기 타겟 기판의 성질은 상기 얻어진 구조의 재료의 상변화에 관한 불양립성을 방지하도록 선택되는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 6

제 1 항에 있어서, 상기 박층과 접촉하는 상기 중간 서포트 및/또는 상기 타겟 기판의 성질은 상기 얻어진 구조의 재료의 불균일성에 관한 불양립성을 방지하도록 선택되는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 7

제 1 항에 있어서, 상기 박층과 접촉하는 상기 중간 서포트 및/또는 상기 타겟 기판의 성질은 상기 중간 서포트 및/또는 상기 타겟 기판, 및 상기 박층의 열팽창계수 사이의 차이와 관련된 불양립성을 방지하도록 선택되는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 8

제 1 항에 있어서, 상기 박층, 상기 중간 서포트 및 상기 타겟 기판의 적어도 하나는 하나 또는 그 이상의 콘택면을 갖는 적어도 하나의 추가적인 층을 구비하는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 9

제 8 항에 있어서, 단계 d) 전에 구성 요소의 적어도 일부가 상기 추가적인 층 내에 제공되는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 10**

제 8 항에 있어서, 상기 추가적인 층은 산화물 또는 다결정 실리콘 또는 비정질 실리콘으로 이루어진 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 11**

제 1 항에 있어서, 단계 a) 및 단계 c)는 상기 박층의 제 1 콘택면 및/또는 상기 중간 서포트의 거칠기가 상기 타겟 기판 및/또는 상기 박층의 제 2 콘택면의 거칠기보다 더 낮은 상태로 행하여지고, 단계 d)에서 상기 제 2 콘택면이 상기 박층과 결합 접촉되고 상기 중간 서포트가 제거되는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 12**

제 1 항에 있어서, 단계 b) 및/또는 단계 d)에서 상기 박층의 상기 제 1 콘택면 및/또는 상기 제 2 콘택면의 결합 접촉은 결합 접촉을 가능하게 하는 처리를 사용한 결과인 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 13**

제 12 항에 있어서, 상기 결합 접촉을 위해 사용되는 상기 처리는 기계적 화학적 및/또는 이온 연마, 상기 박층의 콘택면과 이에 대응하는 상기 중간 서포트 또는 상기 타겟 기판 사이의 중간층의 삽입, 열처리 및 화학적 처리 중에서 하나 선택되거나 이들의 조합에서 선택되는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 14**

제 1 항에 있어서, 단계 b) 및/또는 단계 d)에서의 상기 결합 접촉은 문자 결합에 의해 이루어지는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 15**

제 1 항에 있어서, 상기 박층의 상기 제 1 콘택면의 표면 극성 (이 표면상의 원자의 성질에 관련된 극성)은 상기 제 2 콘택면의 극성과 다르고, 단계 d)에서 상기 박층의 상기 제 2 콘택면이 상기 타겟 기판과 결합 접촉되고, 상기 중간 서포트가 상기 박층의 상기 제 1 콘택면으로부터 제거됨으로써 제 1 콘택면이 자유면이 되는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 16**

제 1 항에 있어서, 상기 박층의 상기 제 2 콘택면과 상기 타겟 기판과의 결합 콘택이, 단계 e) 이후 상기 타겟 기판의 제거를 가능하게 하는 결합 에너지와 함께, 단계 d)에서 생성되는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 17**

제 1 항에 있어서, 단계 c) 와 단계 d) 사이에, 상기 박층의 상기 제 2 콘택면 및/또는 상기 타겟 기판 내에 구성 요소를 제조하는 단계로 이루어지는 중간 단계가 수행되고, 단계 d) 후에 얻어지는 구조는 상기 구성 요소의 존재와 양립하는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 18**

제 1 항에 있어서, 단계 d) 전에, 상기 제 2 콘택면의 적어도 일 영역을 분리하기 위한 트리밍 작업으로 이루어진 중간 단계가 수행되고, 단계 d)에서 이러한 영역 중 적어도 하나를 상기 타겟 기판과 결합 접촉시키는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 19**

제 1 항에 있어서, 단계 a)는 적어도 하나의 재료의 층(3)으로 피복된 기판(1)으로부터 시작하여 행하여지는 것을 특징으로 하는 적층 구조의 제조 방법.

**청구항 20**

제 19 항에 있어서, 단계 e) 후에, 단계 a)에서 상기 기판(1)을 피복하는 재료의 층(3)을 제거하는 단계로 이루

어지는 단계를 포함하는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 21

제 19 항 또는 제 20 항에 있어서, 상기 최초 기판(1)은 실리콘으로 제조되고, 이를 피복하는 상기 재료의 층(3)은 실리콘 산화물로 제조된 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 22

삭제

### 청구항 23

제 1 항에 있어서, 단계 b) 이후 상기 박층을 통해, 또는 중간 서포트의 콘택면을 상기 박층의 상기 제 1 콘택면과 결합 접촉시킨 후 또는 그 전에 상기 중간 서포트의 상기 콘택면을 통해 가스 화합물을 도입시키고, 이렇게 가스 화합물을 부가함으로써 상기 중간 서포트의 전부 또는 일부의 제거를 가능하게 하는 약화된 층을 형성함으로써 상기 중간 서포트의 적어도 일부가 제거되는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 24

제 1 항에 있어서, 단계 e)의 종료시에 얻어진 상기 적층 구조가 상기 제 1 콘택면 쪽 상에서 씌닝되는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 25

제 1 항에 있어서, 단결정 실리콘으로 제조된 최초 기판, 단결정 실리콘으로 제조된 중간 서포트, 상기 최초 기판 내의 실리콘보다 품질이 더 낮은 다결정 또는 단결정 실리콘으로 제조된 타겟 기판을 사용하는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 26

제 1 항에 있어서, SiC 또는 GaAs 최초 기판, SiC 또는 GaAs 중간 서포트, 상기 최초 기판 재료보다 품질이 더 낮은 SiC 또는 GaAs 타겟 기판을 사용하고, 상기 박층은 상기 최초 기판으로부터 유래된 SiC 또는 GaAs 를 포함하는 것을 특징으로 하는 적층 구조의 제조 방법.

### 청구항 27

제 1 항에 있어서, 상기 박층은 Si, GaN, SiC, LiNbO<sub>3</sub>, Ge, GaAs, InP, 사파이어 및 다른 반도체로부터 선택된 재료층인 것을 특징으로 하는 적층 구조의 제조 방법.

## 명세서

### 기술분야

<1>

본 발명은 타겟 기판에 결합된 박막을 구비하는 적층 구조(stacked structure)를 제조하기 위한 방법에 관한 것이다. 본 발명은 특히 반도체 분야에 적용될 수 있다.

### 배경기술

<2>

(미국특허 제 5 374 564호에 대응하는) 문헌 FR-A-2 681 472는 반도체 재료로 만들어진 박막을 제조하는 공정을 개시하고 있다. 이 문헌은 반도체 재료로 만들어진 기판 내에 희유 가스(rare gas) 및/또는 수소를 주입함으로써 주입 이온의 평균 관통 깊이와 거의 동일한 깊이에 미세 공동(micro-cavities) 또는 미세 기포(micro-bubbles) (또는 작은 판)을 포함할 수 있는 약화된 층을 형성할 수 있다는 것을 개시하고 있다. 이 기판의 주입된 면은 스티프너(stiffener)로 기능하는 서포트(support)와 접촉하게 된다. 또한, 반도체 기판을 2 부분, 즉, 상기 스티프너와 결합된 반도체 박막, 및 기증 기판 (donating substrate) 또는 서포트로 재생될 수 있는 반도체 기판의 나머지 부분으로 분리(separation) 또는 파쇄(fracture)시키는 미세 공동 또는 미세 기포 사이의 상호작용(또는 융합)을 일으키도록 충분히 높은 온도에서 열처리를 가할 수 있다. 이러한 분리는 미세 공동 또는 미세 기포가 존재하는 위치에서, 즉 미세 공동층을 따라 발생한다. 열처리를 행함으로써, 주입에 의해 형성

된 미세 기포 또는 미세 공동 사이의 상호작용은 박막과 기판의 잔여 부분 간의 분리를 일으키도록 한다. 따라서, 최초 기판으로부터 박막에 대한 서포트로 기능하는 스티프너로 박막을 전달하게 된다.

<3> 이온 주입은 미리 정의된 화합물들을 단독으로 또는 조합으로 도입하는 어떤 수단을 말한다. 예를 들어, 이온 충격(ionic bombardment), 확산 등이 있다.

<4> 또한, 이 공정은 반도체 재료 이외의 결정 또는 비결정인 고체 재료(도체 또는 유전체 재료)로 만들어진 박막을 제조하는 데에 적용될 수 있다. 이러한 막은 단일층 또는 다층일 수 있다(예를 들어, 문헌 FR-A-2 748 850을 참조).

<5> 이 공정은 작은 판(platelets) 예를 들어, 산화물층으로 피복된 실리콘 기판 상으로 실리콘막을 전달함으로써 전자소자급 SOI 웨이퍼를 저비용으로 제조하는 데에 사용될 수 있다.

<6> H. MORICEAU 등에 의해 E.C.S. Proc. Vol. 99-3, p. 173에 발표된 논문 "A new characterization process used to quality SOI films"은 이러한 종류의 공정에 따라 제조된 SOI 웨이퍼가 산화된 실리콘 기판 상에 결합될 수 있다는 것을 개시하고 있다. (예를 들어, HF에 기초한) 선택적 화학적 작용(selective chemical attack)에 의해 실리콘 기판이 SOI 웨이퍼 및 그 산화물층으로부터 제거된 후의 결과물은 반전된 실리콘막 (inverted silicon film)을 갖는 또하나의 SOI 웨이퍼가 되는데, 이는 그 막의 자유면(free face)이 최초 SOI 웨이퍼의 매립된 산화물층에 결합되었기 때문이다. 실리콘 막 내에 결함을 조사할 수 있었기 때문에, 이러한 공정 절차를 사용하였다. 이 연구의 목적은 새로운 구조를 제조하는 것이 아니라, 그 막의 두께 내에 있는 결함의 위치를 확인하는 것이었다.

<7> M. SUDOU 등에 의해 E.C.S. Proc. Vol. 97-23, p. 119에 발표된 논문 "Evaluation of defects in surface Si near Si/BOX interface in SIMOX platelets" 및 A.J. AUBERTON-HERVE 등에 의해 E.C.S. Proc. Vol. 95-7, p. 12에 발표된 논문 "SIMOX technology and applications to wafer bonding"은 SIMOX 공정을 사용하여 얻은 SOI 웨이퍼를 실리콘 기판 또는 순수 실리카 기판 상에 직접 결합하는 실험을 개시하고 있다. 이 공정은 단일 결합(single bonding) 단계 및 그 후의 SOI 웨이퍼로부터 기판을 제거하는 단계를 포함한다. 이 실험의 목적으로 또한 실리콘막 내에 있는 결함을 조사하는 것이었다. 유사한 접근 방법이 F. FOURNEL 등에 의해 Materials Science and Engineering, B 73 (2000), 페이지 42 내지 46에 발표된 논문 "Ultra thin silicon films directly bonded onto silicon wafers"에서, 박막과 단결정 실리콘 기판이 접촉할 때 정의된 계면 내에 전위망(dislocation network)를 만들기 위해 사용되었다. 이 논문은 본 발명에 의해 설명되는 바와 같은 적층 구조 내에 박층을 얻는 수단에 대한 어떠한 정보도 제공하고 있지 않다.

<8> (미국특허 제 5 863 830 호에 대응하는) 문헌 FR-A-2 725 074는 타겟 기판에 결합된 반도체 박막을 구비하는 구조를 제조하기 위한 공정을 개시하고 있다. 우선, 박막이 제 1 결합 에너지에 의해 최초 기판에 결합된다. 그 후, 제 1 결합 에너지를 극복하도록 박막을 벗기는 힘을 가하고 타겟 기판 상에 박막을 결합시킴으로써 박막은 최초 기판으로부터 타겟 기판으로 전달된다. 벗김(tearing off)에 의해 박막으로부터 분리되는 중간 기판 (intermediate or manipulator substrate)에 의해 박막이 전달될 수 있다. 이 공정은, 박막과 관련된 서로 다른 결합 계면들에서의 결합 에너지가 연속적인 벗김을 가능하게 하도록 잘 제어되어야 한다는 것을 요한다.

<9> BESOI로 알려진 방법은 가스 화합물의 주입에 의한 박막의 분리를 사용하지 않는다. 그 주요한 특징들 중의 하나는, 통상 실리콘으로 제조되는 단결정층을 지지하면서 화학적(선택적) 작용을 가능하게 하는 결정 저지층(crystalline stop layer)을 사용하는 것이다. 이 저지층은 단결정층 또는 에피택셜층이다. 그것은 도핑된 실리콘층, 박막의 성질과 다른 성질을 갖는 결정 재료의 에피택시에 의해 얻은 층(예를 들어,  $Si_xGe_{1-x}$ ), 실리콘 기판의 단단한 부분으로부터 형성된 다공성으로 된 실리콘의 단결정층일 수 있다. 이 방법은 이 저지층 상에 단결정막을 증착하는 것이 요구될 경우, 비정질의 저지층을 사용할 수 없다. 그것은 중간 기판의 사용에 대한 어떠한 정보도 제공하고 있지 않다.

<10> 직접 공정(direct process)으로 불리우는, 박층 구조를 제조하기 위한 알려진 공정은 FR-A-2 681 472에 설명되어 있는 바, 수소 주입, 최종 서포트와의 분자 결합 및 주입된 영역 내에서의 분리 및/또는 주입된 영역 근방에서의 분리에 기초한 것으로서, 특정 특성을 갖는 구조를 얻기가 어렵고 또는 이러한 구조를 충분한 품질로 얻을 수 없다. 다음의 경우에는 직접 공정을 쉽게 적용할 수 없으며, 본 발명에서 설명하는 바와 같이 제공되는 기술적 해결 방법은 직접 공정의 단순한 변경이 아니다.

<11> 첫번째 경우는 비정질층의 표면 상에 존재하는 결정층을 갖는 얇은 및/또는 매우 얇은 적층막의 구조를 제조하는 것에 관한 것이다. 첫번째 예는 수십 나노미터 미만의 두께를 가진 막, 예를 들어 단단한 실리콘 서포트에

결합된 20 nm 두께의  $\text{SiO}_2$  막 상에 20 nm 두께의 실리콘막을 제조하는 것이다. 직접 공정에서의 분리 단계 동안에 결합 결함(bonding defects)이 자주 나타나게 되는데, 이는 그 공정이 낮은 온도의 열처리 (예를 들어, 500 °C 미만) 를 포함하는 분리 단계를 사용하는 경우에 나타내 보일 수 있다. 이 분리 단계는 기계적인 도움을 받을 수도 있고 그렇지 않을 수도 있다. 두번째 예는, 사용된 기판들 중 하나를 (예를 들어, 직접 공정에 의한 씨닝(thinning)을 사용하여) 씨닝하는 동안에 또는 씨닝한 후에 미리 가해진 열처리의 온도를 넘는 온도에서 특정 특성을 갖는 박막 구조가 열처리를 받게 되는 경우이다. 예를 들어, 가스로 팽창된 기포 등의 결합 결함은 상기 구조의 품질에 대한 손상의 원인으로 나타나게 된다.

<12> 두번째 경우는 직접 공정을 사용하는 분리 단계 전의 결합력이 매우 낮은 구조를 제조하는 것에 관한 것이다. 예를 들어, 접촉 전의 어떤 표면 준비 조건에 대해서 (클리닝(cleaning), 주어진 표면 거칠기(surface roughness)를 발생시키는 구성 요소 제조 공정의 레벨), 최종 서포트와 전달된 막의 발생판(generating plate) 사이의 결합은 매우 낮은 에너지를 가진다. 그러면, 이 직접 공정에서의 분리 단계는 불가능하게 된다.

<13> 세번째 경우는 열팽창계수가 너무 다른 재료들의 적층 구조를 제조하는 것에 관한 것이다. 전달될 막을 이루는 재료와 최종 서포트의 재료의 열팽창계수 사이의 차이가 너무 높으면, 열처리를 그 결합에 가하는 경우 직접 공정에 의한 분리 전에 그 결합이 파손될 것이다. 예를 들어, 열팽창계수 사이의 비가 2 인, 실리콘과 사파이어의 경우에 그러하다.

<14> 네번째 경우는 직접 공정을 사용하는 분리 단계 후의 결합력이 낮거나 매우 낮은 구조를 제조하는 것에 관한 것이다. 이후에 결합 계면에서 분리될 수 있도록, 직접 공정을 사용하는 분리 단계 후에 적층 구조의 결합 에너지는 낮은 상태로, 어쩌면 분리에 필요한 결합력보다 훨씬 더 낮은 상태로, 유지되는 것이 바람직할 수 있다. 이는 특히 몇몇 처리가 결합 계면을 강화할 수 있는 경우에 적용될 수 있다. 예를 들어, 재사용될 수 있도록 제거될 수 있는 타겟 기판에 대응하는 첫번째 예에서, SOI 구조의 실리콘 표면막을 950 °C에서 희생 산화(sacrificial oxidation)시킴으로써 씨닝하면,  $1 \text{ J/m}^2$  보다 더 큰 결합 에너지의 증가를 초래하여, 이 후의 타겟 기판 적층 구조의 분리로 전도되지 않게된다. 두번째 예에서, 모든 층 또는 일부 층을 처리하기 위해 화합물의 열 확산, 국부 산화 등이 필요할 수 있는데, 이러한 처리는 결합력을 강화하는 데에 관여하기 때문에 적층 구조의 분리에 긍정적이지 못하다. 또한, 예를 들어 적층 구조의 모든 부분 또는 일부 및 기판에 비하여 매우 큰 응력을 받는 중착물을 그 구조 위에 제조하는 것이 요구되는 경우에, 최종 구조 내에 매우 낮은 결합 에너지를 갖는 것이 바람직할 수 있다. 이러한 약한 계면은 응력 조절 영역(stress accommodation area)으로 작용하게 된다. 이것은 서포트 컴플라이언스(support compliance) 응용이다.

<15> 다섯번째 경우는 이종 재료로 만들어진 적층 구조의 제조에 관한 것이다. 서로 다른 성질들을 갖는 재료, 예를 들어 실리콘 또는 열 산화물 (다양한 유전체, 금속 재료, 반도체, 초전도체, 등등)을 사용하면, 직접 공정에서 나타나는 결합 결함을 초래할 수 있다. 예를 들어, 실리콘 질화물막 자체에 의해 피복된 실리콘 막의 결합은, 직접 공정에서 분리 단계 동안에 쉽게 나타나는 결합 결함을 자주 발생시킨다. 이 경우, 막은 기판 또는 막 또는 상기 막에 의해 표면상에 피복된 적층 구조이다.

<16> 여섯번째 경우는, 상변화 또는 재료의 성질 변화가 발생할 수 있는 적층 구조를 제조하는 것에 관한 것이다. 예를 들어, 어떤 재료는 열수지(thermal budgets)와의 불양립성으로 인해 직접 공정에서 사용될 수 없다. 따라서, 실리콘막, 팔라듐막 및 실리콘 웨이퍼로 이루어진 적층 구조는 양호한 결합을 이룰수 있는 실리사이드를 200 °C 이상의 온도에서 형성한다. 더 높은 온도, 예를 들어, 두께를 감소시키기 위해 실리콘막을 산화시키는 데에 통상 사용되는 온도인 900 °C 이상의 온도에서 그 결합은 열화된다. 다른 예는 금속 미러(mirror)가 분자 결합에 의해 실리콘 시트(silicon sheet)에 부가되는 광학적인 응용 분야에 적용된다. 이 금속 미러는 수십 °C 이상의 온도로 가열할 수 없어서, 분리 공정에 사용될 수 있는 열수지가 불가능하게 된다.

<17> 직접 공정은 전면(front face)이라고 불리우는 특정 표면의 보존을 포함하는 적층막 구조를 제조하는 데에 항상 사용될 수 있는 것은 아니다.

<18> 이러한 점에서, 첫번째 예로서, 얇어진 표면을 연마하는 것이 어려운 적층 구조를 제조하는 것에 유의한다. 예를 들어, 분리 단계 후에 씨닝된 구조의 표면 거칠기는 예정된 용도에 따라 감소될 필요가 있을 것이다. 실리콘의 경우에, 이러한 거칠기의 감소는 화학적 기계적 연마 (CMP)에 의해 얻을 수 있다. 예를 들어, "견고한" 재료 등 많은 재료에 대해서, 이러한 연마는 적절하지 못하거나(효과적이지 못하거나) 너무 긴 시간(더 높은 생산 비용)이 소요된다. 예를 들어, 사파이어,  $\text{SiC}$  또는 다이아몬드막을 사용하는 표면에서 종결되는 직접 공정을 사용하여 씨닝되는 구조에서 그러하다. "견고한" 막 표면의 미세 거칠기(micro-roughness)는, 요구되는 용

도를 만족시키기 위해 감소되어야 한다. 이러한 종류의 재료에 대해서, CMP에 의한 연마는 매우 긴 실행 시간이 소요되고 그 구조 상의 연마 균일성을 제어하기가 매우 어렵다. 따라서, 에피택셜같은(epi-ready) 형태의 품질을 달성하고자 한다면, 관련되는 추가 비용이 매우 높게 된다.

<19> 또한, 2 면 상에 서로 다른 특성을 갖는 하나의 막이 제공되는 적층 구조를 제조하는 것을 언급할 수 있다. 분리 단계 후에 직접 공정에 의해 얻어진 구조가 예정된 용도와 양립하지 않는 면을 구비하는 경우에 그러하다. 예를 들어, 극성으로 인하여, 단결정 SiC 막은 일면의 표면(Si형 표면이라고 함)이 그 일면 상에 주로 실리콘 원자로 이루어져 있고, 다른 면의 표면(C형 표면이라고 함)은 주로 탄소 원자로 이루어져 있는 특성을 가지고 있다. SiC 상에 에피택시로 계속해서 성장시키는 것은 자유 Si형 표면(free Si type surface)이 이용될 수 있다는 것을 가정한 것이다. 그러나, 예를 들어 직접 공정을 사용하여 SiC막을 전달하는 것은, 전복(turing over)으로 인하여 표면 성질의 변화를 수반하게 된다. Si형 표면이 SiC로 연마되기 쉽고 분자 결합에 의해 결합되기 쉽기 때문에, 최초의 자유 표면은 Si형이다. 따라서, 직접 공정에 의해 전달된 후의 자유면은 C형이 된다. GaN층에 대해서도 마찬가지이다.

### 발명의 상세한 설명

<20> 본 발명은 종래 기술의 단점을 극복하고 몇가지 특정 특성을 갖는 막 또는 특정 특성을 갖는 적어도 하나의 표면을 갖는 막을 구비하는 적층 구조를 제조하는 수단을 제공한다.

<21> 본 발명은 발명자가 발견한 놀라운 사실, 즉, 박층을 타겟 기판에 결합한 후 씨닝하는 직접 공정과 달리, 박층을 타겟 기판에 결합하기 전에 최초 기판을 씨닝하는 경우에는 전술한 모든 결함을 방지할 수 있다는 사실에 근거한 것이다. 이러한 결합 단계 및 씨닝 단계를 역전시키기 위하여 하나 또는 몇개의 중간 서포트를 사용할 필요가 있다.

<22> 따라서, 본 발명의 목적은 타겟 기판에 결합된 적어도 하나의 박층을 구비하는 적층 구조를 제조하기 위한 방법을 제공하는 것이며, 이 방법은 다음의 단계들을 포함한다.

a) 최초 기판으로부터 제 1 콘택면이라 불리우는 자유면을 갖는 박층을 형성하는 단계,

<24> b) 상기 제 1 콘택면을 중간 서포트의 면과 결합 접촉시켜, 얻은 구조가 상기 최초 기판을 씨닝하는 이후의 단계와 양립할 수 있도록 하는 단계,

<25> c) 상기 최초 기판을 씨닝하여, 제 2 콘택면이라 불리우고 상기 제 1 콘택면과 대향하는 상기 박층의 자유면을 노출시키는 단계,

<26> d) 타겟 기판의 면을 상기 제 2 콘택면의 적어도 일부와 결합 접촉시켜, 얻은 구조가 상기 중간 서포트 전부 또는 일부를 제거하는 이후의 단계와 양립할 수 있도록 하는 단계,

<27> e) 상기 중간 서포트의 적어도 일부를 제거하여 상기 적층 구조를 얻는 단계.

<28> 단계 c)에서의 씨닝 또는 단계 e)에서의 제거는 최초 기판 또는 중간 서포트를 제거할 수 있는 어떠한 방법도 사용할 수 있다. 특히, (가스 화합물의 도입에 의해 약화된 영역의 형성에 의한)파쇄, 분리, 기계적 및/또는 화학적 작용을 예로 들 수 있다. 씨닝 및 제거 형태에 따라, 기판 및 서포트를 재사용할 수도 있다.

<29> 일 실시예에 따르면, 타겟 기판은 박층을 위한 임시적인 서포트일 뿐이며, 상기 공정에서의 단계들은 완전히 또는 부분적으로 반복되고, 타겟 기판은 최초 기판 또는 중간 서포트로서 다루게 된다.

<30> 따라서, 본 발명에 따른 공정은 박층을 하나의 서포트로부터 다른 서포트로 필요한 만큼 여러 번 전달하여 요구되는 특성을 갖는 적층 구조 및 특히, 기술적인 구성 요소 레벨을 갖는 적층물을 얻는 데에 이용될 수 있다.

<31> 단계 c)에서의 씨닝 및 단계 e)에서의 제거 동안에 결합 결함을 방지하기 위해, 단계 a)에서 박층을 형성함으로써 단계 b) 및/또는 단계 d)에서의 상기 구조의 양립성(compatibility)을 각각 달성할 수 있다. 이러한 양립성은 박층의 완성된 두께 및/또는 상기 박층을 이루는 재료 또는 재료들 때문일 것이다. 중간 서포트 및/또는 박층과 접촉하는 타겟 기판의 성질은 결과물로서 얻은 구조 내의 재료의 상변화와 관련된 임의의 불양립성을 방지하도록 선택될 수 있다. 중간 서포트 및/또는 박층과 접촉하는 타겟 기판의 성질은 중간 서포트와 박층의 열팽계수 사이의 차이에 관련된 임의의 불양립성을 방지하도록 선택될 수 있다. 이러한 양립성을 가능하게 하기 위해, 박층 및/또는 중간 서포트 및/또는 타겟 기판은 콘택면(들)을 갖는 적어도 하나의 추가적인 층을 구비할 수 있다. 이 경우, 단계 d) 전에, 추가적인 층에

는 적어도 하나의 구성 요소의 전부 또는 일부가 제공될 수 있다. 추가적인 층은 산화물 또는 다결정 실리콘 또는 비정질 실리콘으로 이루어질 수 있다.

<32> 단계 a) 및 c)는 박층의 제 1 콘택면 또는/및 중간 서포트의 거칠기가 각각 제 2 콘택면 및/또는 타겟 기판의 거칠기보다 더 작게 되도록 하고, 단계 d)에서의 구조의 양립성은 박층의 제 2 콘택면을 결합 접촉시키고 중간 서포트를 제거함으로써 얻어진다.

<33> 단계 b) 및 단계 d)에서의 상기 양립성을 달성하는 박층의 제 1 콘택면 및/또는 제 2 콘택면의 결합 접촉은 결합 접촉을 가능하게 하는 처리 방법의 사용으로부터 기인한다. 결합 접촉을 가능하게 하는 처리 방법은 기계적 화학적 또는 이온 연마, 박층의 해당 콘택면과 중간 서포트 또는 타겟 기판 사이의 중간층의 삽입, 또는 열처리 또는 화학적 처리, 또는 이러한 처리들의 조합이 적용될 수 있다. 그 처리 방법은 구조의 양립성으로 인해 고온에서 적용될 수 있다.

<34> 유리하게는, 단계 b) 및/또는 단계 d)는 문자 결합에 의해 결합 접촉할 수 있다.

<35> 박층의 제 1 콘택면의 (표면상의 원자의 성질과 관련된) 표면 극성은 제 2 콘택면의 표면 극성과 다를 수 있고, 단계 d)의 구조의 양립성은 박층의 제 2 콘택면을 타겟 기판과 결합 접촉시키고 박층의 제 1 콘택면으로부터 중간 서포트를 제거함으로써(이와 같이 제거함으로써 제 1 콘택면은 자유면이 됨) 얻을 수 있다. 단계 d)에서 달성되는 구조 양립성은 박층의 제 2 콘택면을 (단계 e) 후에 타겟 기판을 제거하기에 적절한 결합 에너지를 갖는) 타겟 기판과 결합 접촉시킴으로써 얻을 수 있다. 유리하게는, 이러한 결합 에너지는 낮다. 단계 c)와 단계 d) 사이에, 박층의 제 2 콘택면 및/또는 타겟 기판에 소자를 제조하는 것으로 이루어진 중간 단계가 삽입될 수 있으며, 단계 d) 후에 얻은 구조는 상기 소자의 존재와 양립된다. 이러한 소자는 캐비티(cavity) 또는 구성 요소 (마이크로 전자소자, 광전소자 등)의 모든 부분 또는 일부일 수 있고, 일정한 표면 토폴로지(surface topology)를 가지고 만들어 진다. 단계 d)전에, 제 2 콘택면의 적어도 일 영역을 분리하기 위해 트리밍 작업 (trimming operation)으로 이루어진 중간 단계가 제공될 수 있으며, 단계 d)는 이러한 영역중의 적어도 하나를 타겟 기판과 결합 접촉시킨다. 트리밍 작업은 단계 a) 전에 일어날 수도 있다. 제거 단계 e) 후에, 타겟 기판과 결합 접촉하지 않은 층의 영역(들)은 중간 서포트 상에 남아있고 나중에 전달된다.

<36> 단계 a)는 적어도 1층의 재료가 피복된 기판으로부터 실시될 수 있다. 이 경우, 단계 e) 후에, 본 공정은 단계 a)에서 기판을 피복하는 층의 재료를 제거하는 것으로 이루어진 단계를 포함할 수 있다.

<37> 바람직한 일 실시예에 따르면:

<38> - 단계 a)는 상기 제 1 콘택면에 대응하는 최초 기판의 면들중 1 면을 통하여 그 최초 기판으로 가스 화합물을 도입하는 것을 포함하여, 최초 기판의 잔여 부분으로부터 상기 막을 분리시키는 약화된 층을 형성한다.

<39> - 단계 c)는 상기 약화된 층에서 최초 기판 내에 파쇄를 얻기위해 바람직하게 처리하는 것으로 이루어진다.

<40> 이러한 처리는 열적 및/또는 기계적일 수 있다. 최초 기판은 단층 또는 다층일 수 있다. 특히, 그것은 에피택 층층을 구비할 수 있다. 타겟 기판 및 중간 서포트에 대해서도 마찬가지이다.

<41> 바람직한 일 실시예에 따르면, 중간 서포트의 적어도 일부는, 그것을 박층의 제 1 콘택면과 결합 접촉시키기 전 또는 후에, 콘택 형성 후 박층을 통한 또는 중간 서포트의 콘택면을 통한 가스 화합물의 도입에 의해 제거될 수 있으며, 이렇게 가스 화합물을 더해줌으로써 (박층의 막으로 피복될 수 있는) 중간 층의 모든 부분 또는 일부를 파쇄에 의해 제거할 수 있는 약화된 층을 형성한다. 이 경우, 중간 서포트는 예를 들어 새로운 서포트로서 재 사용될 수 있다.

<42> 단계 e)의 종료로 얻은 적층 구조는 제 1 콘택면측 위에서 씌우 될 수 있다.

<43> 본 공정은, 예를 들어 300 mm 직경 단결정 실리콘과 같은 매우 좋은 품질을 갖는 값비싼 최초 기판, 예를 들어  $\text{SiO}_2$  산화막에 의해 피복된 단결정 실리콘 기판과 같은 단계 b)의 의미에서 최초 기판과 양립되는 중간 서포트, 예를 들어 최초 기판으로부터 유래된 단결정 실리콘 상에 실리콘 산화물을 구비하는 박층과 같은 최초 기판 내의 실리콘보다 품질이 더 낮은 단결정 실리콘의 단결정으로 제조된 타겟 기판을 사용할 수 있다. 마찬가지로, 타겟 기판은 실리콘의 다른 것일 수 있다. 공정 종료시에, 타겟 기판 상에 얻어진 막은 매우 품질이 좋다. 또한, 최초 기판이 제조될 수 있고, 중간 기판은 그 품질 또는 가격에 따라 재사용되거나 희생(sacrificial)될 수 있다. 또한,  $\text{SiC}$  또는  $\text{GaAs}$  최초 기판,  $\text{SiC}$  또는  $\text{GaAs}$  중간 서포트, 또는 최초 기판보다 품질이 더 낮은  $\text{SiC}$  또는  $\text{GaAs}$  타겟 기판이 사용될 수 있고, 박층은 최초 기판으로부터 유래된  $\text{SiC}$  또는  $\text{GaAs}$ 를 포함할 수

있다.

<44> 또한, 박막은 Si, GaN, SiC, LiNbO<sub>3</sub>, Ge, GaAs, InP, 사파이어 및 반도체로부터 선택된 재료로 된 층일 수 있다.

<45> 본 발명은 다음과 같은 점들을 포함하여 많은 이점을 제공한다:

<46> - 좋은 결정 품질을 갖는 단결정이 전달될 수 있되, 중간 서포트를 씌우기 위한 저지층(stop layer)은 비정질 층이다.

<47> - 중간 기판의 가격 (품질, 성질 등)이 높다면, 예를 들어, 결합 에너지를 검사함으로써 재생 이용 가능한 중간 서포트가 사용될 수 있다. 따라서, 다결정 SiC 중간 서포트가 고가(高價) 및/또는 고품질 단결정 SiC 막을 전달하도록 다결정 SiC 중간 서포트가 사용될 수 있다. 예를 들어, 결합 에너지는 박층 상에 또는 중간 서포트 상에 증착된 SiO<sub>2</sub>의 추가적인 층의 거칠기를 검사함으로써 제어될 수 있다. 중간 서포트의 결합 에너지를 제어하기 위한 다른 방법으로서, 재생 이용하기 위해 이 중간 서포트의 표면 상에 소모될 수 있는 막(예를 들어, 산화물)을 사용할 수도 있다(리프트 오프(lift-off) 기법).

<48> - 최종 매립 산화물 또는 중간층(유전체, 금속 등)의 두께를 선택하기 용이하다.

<49> - 본 발명의 원리는 적층 구조 내의 막들중 적어도 하나가 실리콘 이외의 다른 단결정 재료로 제조된 층에 적용될 수 있다. 특히, 본 공정은 임의의 서포트 상으로 사파이어, SiC, GaN, LiNbO<sub>3</sub>, Ge, GaAs, InP 막을 도포하기 위해 사용될 수 있다.

<50> - 이와 동일한 원리는 예를 들어 석영 또는 임의의 다른 기판 등 실리콘 이외의 다른 타겟 기판 형태에 적용될 수 있고, 유리하게는 저가의 기판(유리, 플라스틱, 세라믹 등)에 적용될 수 있다.

<51> - 이 공정은 어떠한 형태의 반도체막에도 적용될 수 있는데, 예를 들어 III-V, II-VI 및 IV 반도체 또는 다이아몬드 또는 질화막 또는 다른 임의의 형태의 막에 적용될 수 있고, 예를 들어, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, SrTiO<sub>3</sub>, LaAlO<sub>3</sub>, MgO, Yba<sub>x</sub>Cu<sub>y</sub>O<sub>z</sub>, SiO<sub>x</sub>N<sub>y</sub>, RuO<sub>2</sub> 또는 다른 재료 등의 산화물에 적용될 수 있고, 특히, 압전 재료, 초전도체, 절연체, 금속, 초전 재료(pyroelectric), 단결정 및 다른 재료에 적용될 수 있다.

<52> - 이 공정은 극성을 가진 표면이 있는 재료에 적용될 수 있다.

<53> - 이 공정은, 예를 들어 복합 다층 구조를 얻기 위해, 재료들에 반복적으로 적용될 수 있다.

<54> - 예를 들어 최종 서포트 상의 단결정 등 단일한 단결정 막에 대한 제조 원리는, 최종 서포트가 적어도 한번 처리되거나 처리되지 않은 층을 갖는 구조로 된 적용예에서 유리하게 사용될 수 있다. 전달된 실리콘의 이러한 단결정막은 그 자체로 구성 요소를 형성하기 위한 기술적 단계의 주제가 된다. 이 원리는, 반복된다면, 기술적 구성 요소 레벨의 3D 적층용으로 사용될 수 있다.

<55> - 본 발명에 따른 공정은 특정 제품에서의 몇가지 형태의 불양립성을 보완할 수 있다. 한개 또는 수개의 중간 서포트가 이를 달성하는 데에 사용될 수 있다.

<56> - 최초 기판, 타겟 기판 및 중간 서포트는 적층 구조일 수 있다.

## 실시 예

<64> 본 발명의 실시예들을 설명한다. 이러한 실시예들은 본 발명의 실시에 대한 공정 상의 변형이 있으므로, 도 1 내지 도 6 을 참조하여 일 실시예를 사용하여 본 공정을 간단히 설명함으로써 시작한다.

<65> 도 1은 최초 기판을 형성하는 725  $\mu\text{m}$ 의 두께와 200 nm의 직경을 갖는 웨이퍼(1)의 단면도를 나타낸다. 최초 기판(1)의 면(2)은 열처리에 의해 400 nm의 두께로 산화되어 산화물층(3)을 형성한다(도 2 참조). 기판(1)으로서 다층(multi-layer)이 사용될 수도 있다.

<66> 다음 단계로, 도 2에 도시된 바와 같이, 면(2)을 통과하고 따라서 산화물층(3)을 또한 통과하는 가스 화합물(4)에 의해 최초 기판(1)에 이온 주입을 행한다. 예를 들어, 가스 화합물(4)은 75 keV의 에너지로써 약  $6 \times 10^{16}$  원자/cm<sup>2</sup> 의 도우즈(dose)로 주입되는 수소 이온일 수 있다. 이에 따라, 이 단계는 면(2)에 평행한 평면 내에 약화된 층(5)을 생기게 한다.

- <67> 면(2)과 약화된 층(5) 사이의 기판(1) 부분은 막(6)을 형성한다. 막(6) 및 산화물층(3)을 적층하여 형성된 어셈블리(assembly)는 박막(7)을 형성한다. 박막(7)은 제 1 콘택면이라 불리우는 자유면(free face; 8)을 가진다.

- <68> 제 1 콘택면(8)은 예를 들어 충분히 친수성이 되도록 의도된 조제물에 의해 클리닝되어 분자 결합에 적합하게 되도록 하고, 도 3에 도시된 바와 같이, 중간 서포트라 불리우는 다른 실리콘 웨이퍼(10)의 면(11)과 분자 결합에 의해 접촉된다. 다른 응용예에서는, 중간 서포트와의 결합을 일으킬 수 있는 (접착성, 용해성 층 등의) 층이 상기 서포트에 결합하도록 가해질 수 있다.

- <69> 최초 기판(1)의 잔여 부분(9)으로부터 파쇄에 의해 막(6)을 분리하기 위해, 최초 기판(1) 및 중간 서포트(10)로 이루어진 어셈블리는, 예를 들어 열처리 등의 분리 처리(separation treatment)를 받게 된다(도 4 참조). 막(6)은 중간 서포트(10)에 부착된 상태로 남아 있고, 자유면(12)을 가진다.

- <70> 유리하게는, 박막(7)은 서포트(10) 상으로 결합되고 고온 열처리에 의해 강화된다. 온도에 따라, 이 두 부분 사이의 분자 결합 에너지는 예를 들어  $1.5 \text{ J/m}^2$ 정도일 수 있다.

- <71> 그 후, 막(6)의 자유면(12)은 예를 들어 기계적 화학적 연마, 또는 부분적이거나 전체적인 수소 분위기 하에서의 가능한 어닐링, 막(6)의 전부 또는 일부를 제거하기 위한 분리되거나 놓축된 이온에 의한 충격 또는 화학적 작용 등의 표면 처리에 의해 평탄화되어, 층(3)이 중간 기판에 대하여 충분히 선택적인 경우에는 막(3)의 면은 자유면이 된다. 여기에 막(13)이 피복되어 다층이 될 수 있고, 그 자유면은 제 2 콘택면(14)을 형성한다(도 5 참조). 막(13)은 증착, 열처리, 화학적 처리 등에 의해 얻어질 수 있다.

- <72> 제 2 콘택면(14)이 클리닝된 후에, 그 면은 타겟 기판(15)과 접촉 결합한다. 이 결합은 고온 열처리에 의해 강화될 수 있다.

- <73> 그 후, 중간 서포트(10)가 예를 들어 화학적 작용과 함께 그라인딩에 의해 제거된다. 또한, 산화물층(3)도 제거되어 도 6에 도시된 바와 같이 타겟 기판(15), 막(13) 및 막(6)으로 이루어진 적층 구조를 얻을 수 있다.

- <74> 제 1 실시예에 따르면, 막(13)은 막(6)의 표면(12) 상에서 열적으로 제조된 20 nm 두께의 산화물일 수 있다. 타겟 기판(15)은 실리콘으로 제조될 수 있고 그 표면 상에서 산화되거나(예를 들어 20 nm 이상) 또는 산화되지 않을 수 있다. 이 경우, 타겟 기판(15) 상의 막(13)의 결합은 1100 °C에서의 열처리 또는 분자 형태 결합에 의해 강화될 수 있다. 전술한 바와 같이, 결합은 접착성 또는 용해성 재료 또는 다른 임의의 형태의 재료를 사용하여 이루어질 수 있다. 이것은 고품질의 적층 구조를 만들면서 결합 계면에서의 기포의 발생을 방지한다. 중간 서포트(10)는 그라인딩을 행한 후 테트라에틸암모늄 수산화물 (TMAH) 또는 칼륨 용액 (potash solution)에서 화학적 작용을 행함으로써 제거되고, 산화물층(3)은 실리콘에 대한 화학적 에칭 저지층의 역할을 한다. 이 산화물층(3)은 염산계 용액을 사용하여 제거된다. 막(6)의 최종 두께는, 예를 들어 희생 산화를 사용하여 씨닝에 의해 적합하게 변경된다. 매우 좋은 균일성을 갖는 50 nm의 최종 두께를 얻을 수 있다.

- <75> 제 2 실시예에 따르면, 최초 기판(1) 상에 형성된 산화물층(3)은 400 nm의 두께를 가진다. 수소 원자가 전술한 바와 동일한 조건에서 주입된다. 최초 기판(1)의 잔여 부분(9)으로부터 실리콘막(6)을 분리한 후, 막(6)은 예를 들어 희생 산화에 의해 30 nm로 씨닝되고, 50 nm 두께의 산화물(13)에 의해 피복된다. 제 2 콘택면(14)은 타겟 기판(15)에 결합된다. 그래서, 결합 계면에서 기포가 발생되는 위험을 야기하지 않고서 고온을 요하는 처리가 가해질 수 있게 된다.

- <76> 제 3 실시예는 타겟 기판 상에 더 낮은 에너지의 결합 계면을 만들어 낸다. 이를 달성하기 위해, 최초 기판의 잔여 부분(9)로부터 막(6)을 분리시킴으로써(도 4 참조) 노출된 막(6)의 표면(12)은, 예를 들어 기계적 화학적 연마에 의해 평탄화된다. 이것은 1000nm 두께를 갖는 산화막(13)을 열적으로 형성시킨다(도 5 참조). 그 후, 막(13)의 자유면은, 예를 들어 10 % 불산(hydrofluoric acid) 용액을 사용하여 12 분간 에칭함으로써 0.6 nm와 동일한 평균 RMS값으로 거칠게 된다. 클리닝 후, 제 2 접촉면(14)은 타겟 기판(15)에 결합된다. 이 타겟 기판은, 예를 들어 1000 nm의 깊이로, 상기 표면 상에서 산화된 실리콘 기판이다. 그 표면은 막(13)에 대해 사용된 것과 동일한 화학적 처리를 사용하여 0.6 nm의 평균 RMS 값으로 거칠게 될 수 있다. 결합 에너지는 열처리 및 야기된 거칠기의 합수로서 융통성을 가지고 있다. 이 단계에서, 결합 에너지는, 문턱 결합 에너지(threshold bonding energy)라고 불리우는, 직접 공정의 만족할 만한 실시에 필요한 에너지보다 더 낮을 수 있다.

- <77> 그 후, 실리콘 중간 서포트(10)가, 예를 들어 TMAH 또는 칼륨 용액에서의 화학적 작용과 함께 그라인딩을 행함

으로써 제거되고, 산화물층(3)은 예청 저지층의 역할을 한다. 이 산화물층(3)은 불산 용액을 사용하여 예청함으로써 제거되고, 막(6)의 최종 두께는 예를 들어 희생 산화에 의해 씨닝함으로 적합하게 변경된다.

<78> 이 실시예는 약 200 nm 의 두께를 갖고 매우 좋은 균일성을 갖는 최종 막(6)을 만들어 낼 수 있다. 그 막은 타겟 기판(15)과의 결합 에너지는 낮아서, 본 공정의 종료시 타겟 기판으로부터의 분리에 의해 회수될 수 있다. 유리하게는, 막이 회수되기 전에, 예를 들어 마이크로 전자소자, 광전 소자, 광전지 소자 또는 센서용 등의 구성 요소 전부 또는 일부를 제조할 수 있다. 유리하게는, 다른 적용예에 따르면, 이런 형태의 낮은 결합 에너지를 갖는 적층 구조는 막 증착 또는 전달을 하는 데에 사용될 수 있다. 이러한 다른 적용예는 고가의 기판에 관련된 것이다.

<79> 다른 실시예에 따르면, 최초 및 중간 기판을 재사용하려고 한다. 이 실시예에 따르면, 최초 웨이퍼는, 예를 들어, 300 mm 직경을 갖는 웨이퍼 등의 고품질 및/또는 고가의 단결정 실리콘으로 제조된 것일 수 있다. 타겟 서포트는 단결정 실리콘 또는 더 낮은 품질의 단결정 실리콘 또는 저가의 다결정 실리콘으로 제조된 것일 수 있다. 본 공정을 사용하여 극복되는 장애물들은 직접 공정에서의 관찰 가능한 기포의 발생 또는 결합 결함을 포함한다. 첫번째 예로서, 제 1 단계 d)에서 박막의 자유면은, 예를 들어 도전성 결합을 요하는 경우에 타겟 기판과 직접 결합될 수 있다. 두번째 예로서, 단계 d)에서 박막 또는 타겟 기판의 자유면은 산화막으로 피복되어, 예를 들어 저가의 타겟 기판 상에서의 결합을 가능하게 한다. 후자의 예에서, 산화물은 결합될 표면을 평탄화시킬 수 있고 타겟 기판은 다결정 실리콘으로 제조될 수 있다.

<80> 이 실시예에서, 중간 실리콘 기판은 예를 들어 다결정 등의 저가일 수 있다. 유리하게는, 예를 들어 SiO<sub>2</sub>로 제조된 표면 평탄화를 위한 추가적인 층이 중간 기판 상에 증착될 것이다.

<81> 또한, 이 실시예에서, 중간 기판은 고품질 실리콘으로 제조될 수 있다. 따라서, 예를 들어 리프트 오프 기법을 사용하거나 가스 화합물의 주입 후 분리에 의해, 또는 예를 들어 분리를 가능하게 하는 매우 낮은 결합 에너지에 기초한 단계 b) 후의 기법에 의해, 예를 들어 기계적 또는 공기압적인 방법 등에 의해 그 중간 기판을 회수하는 것이 유리하다.

<82> 이러한 실시예의 모든 경우에 있어, 유리하게는 예를 들어 300 mm 직경의 실리콘 등 고품질 및/또는 고가인 최초 기판은, 단계 a)에서 가스 화합물 주입을 사용하고 단계 c)에서 최초 기판의 잔여 부분으로부터 분리함으로써 회수될 것이다.

<83> 제 4 실시예는, 막이 방출되고 타겟 기판이 회수될 수 있도록 타겟 기판 상에 낮은 에너지의 결합 계면을 제공할 수 있다. 이전의 실시예와 공통된 점을 많이 가지고 있는 이 실시예는, 타겟 기판에 고정된 막에 다수의 처리, 예를 들어 고온 열처리를 포함한 전자소자를 제조하기 위한 기술적 단계를 행할 수 있게 한다. 직접 공정을 사용하고서는 이 열처리는 막을 분리하는 것을 거의 불가능하게 한다.

<84> 타겟 기판 상의 막의 낮은 에너지 결합, 예를 들어  $0.5 \text{ J/m}^2$  의 에너지를 달성할 수 있다는 것을 알 수 있다. 이런 형태의 결합 에너지는 900 °C를 초과하는 온도에서의 열처리에도 불구하고, 접촉하기 전에 RMS 값이 확실히 0.6 nm 보다 더 크도록 표면 거칠기에 대한 제어를 유지함으로써 달성될 수 있다. 이 에너지는 양립하므로, 구성 요소를 제조하는 기술적 단계의 적용 후에 "처리된" 막은 타겟 기판의 분리에 의해 방출될 수 있다. 타겟 기판을 회수하는 것이 가능하므로, 그 비용면에서 유리하다.

<85> 고가인 타겟 기판의 예로서 300 mm 직경 실리콘 기판을 고려해보자. 기판의 막 부분만이 구성 요소를 위해 재사용될 수 있고, 최초 기판 및/또는 중간 서포트 및/또는 타겟 기판을 회수하는 것이 중요하다.

<86> 제 5 실시예는 최초 기판 내에서 경계가 정하여진 막(6)의 자유면이, 예를 들어 접촉될 2 면 중 적어도 1 면 위의 거칠기로 인하여, 타겟 기판 상의 직접 결합이 매우 약하게 되도록 하는 경우에 적용될 수 있다. 따라서, 직접 공정을 사용하고서는 타겟 기판 상의 결합 에너지는 막을 분리할 수 있도록 하기에는 불충분하다.

<87> 이러한 문제점은 제 1 콘택면(8)을 마련하여, 예를 들어 이온 주입 단계 후의 희생막의 증착 및 추가적인 스무싱(smoothing) 또는 평탄화에 의해, 결합에 적합하게 함으로써 해결된다. 본 발명에 따르면, 중간 서포트, 예를 들어 산화물(예를 들어 100 nm 두께의 산화물)로 피복되고 약간 거칠게 된 콘택면(예를 들어 0.2 nm 와 동일한 평균 RMS 값을 갖는 콘택면)을 갖는 실리콘 기판이 사용된다. 낮은 거칠기를 가진 표면 상에 결합이 가해진다는 사실은 충분히 높은 결합 에너지로 귀결되어, 막(6)이 최초 기판으로부터 분리되는 단계가 이후에 가능하게 된다.

<88> 일단 분리가 이루어지면, 예를 들어 결합을 강화하기 위해 또는 타겟 적용에 필요한 작업의 함수로서(주입된 원

소의 확산, 이후의 산화막 증착, 등등) 고온 열처리가 가해질 수 있다. 표면 처리, 예를 들어 기계적 화학적 연마는 최초 기판으로부터 분리된 막의 노출된 표면의 전부 또는 일부를 평탄화한다.

<89> 클리닝 후에, 제 2 콘택면이라 불리우는, 막(6) 또는 추가적인 막(13)의 자유면은 예를 들어 약 1000 nm 두께의 산화막으로 피복된 실리콘 타겟 기판 상으로 결합되며, 그 표면은 화학적 처리에 의해 거칠게 된다. 결합은 열처리에 의해 변화되지만, 낮은 상태로 남아 있다. 이 단계에서, 막(6) 또는 막(13)과 타겟 기판(15) (또는 그 표면) 사이의 결합 에너지는 막이 최초 기판의 잔여 부분으로부터 분리되는 단계의 평탄화 실행에 필요한 에너지보다 더 낮다. 그 후, 중간 서포트(10)가 예를 들어 그라인딩 및 화학적 작용에 의해 제거되고, 산화물층(3)이 화학적 작용에 의해 제거된다. 막(6)의 최종 두께는 예를 들어 희생 산화에 의해 씨딩된다. 이 두께는 50 nm 이고 매우 좋은 균일성을 가진다.

<90> 유리하게는, 면(2) 또는 면(8)의 최초 표면 거칠기가 최초 기판 상의 또는 최초 박층 상의 또는 타겟 기판 상의 예칭된 토플로지에 해당하는 경우에 이러한 제 5 실시예가 사용될 것이다. 1000 nm의 두께를 갖는 산화막(13)(도 5참조)은 막(6)의 표면 상에서 예를 들어 열적으로 제조될 수 있다. 처음에 직접 공정을 가능하게 하지 못하는 표면 모폴로지는 예를 들어 화학적 예칭 처리에 의해 이 단계에서 재생될 수 있다. 일 적용예로서 타겟 기판과의 결합 계면에 위치하고 유체의 순환에 의해 그 구조를 냉각할 수 있는 덕트(ducts)의 경우가 있다. 다른 분야의 다른 예로서 광전지 응용을 위한 텍스처(texture)의 생산이 있다. 또한, 이 모폴로지는 타겟 기판 내에서 유일하게 또는 부분적으로 만들어질 수 있고, 추가적인 층으로 피복되거나 피복되지 않을 수 있다.

<91> 제 6 실시예는 중간 서포트가 회수될 수 있다는 점에서 이전의 실시예와 다르다. 중간 서포트는 막의 분리를 가능하게 하는 특정 성질을 가진 구성 요소이고 그 비용이 높을 수 있기 때문에, 이러한 해결 방법은 매력적이다. 예를 들어, 본 발명에 따른 공정은 유리하게는 중간 서포트 상으로의 최초 기판의 결합 에너지가 최초 기판으로부터 막을 분리하기 위해 필요한 문턱 에너지보다 더 높은 값과 동일하게 되도록 유지할 수 있다. 최초 기판과 중간 서포트의 결합 에너지는, 분리 처리에 더하여 표면 거칠기 및 사용된 열처리를 검사함으로써 제어될 수 있다. 중간 서포트가 재생될 수 있다는 것을 생각하면, 비싼 기판을 (본 적용과 양립하는)서포트로 사용할 수 있고, 제 1 결합 계면에서의 분리를 용이하게 하도록 특별히 마련된 기판조차도 서포트로 사용할 수 있다. 중간 서포트는 타겟 기판에 결합된 후 "리프트 오프" 기법을 사용하거나, 기계적 및/또는 공기압적인 분리에 의해, 또는 가스 주입과 조합한 공정을 사용하여 회수될 수 있으며, 이러한 기법들은 서로 조합될 수 있다.

<92> 제 7 실시예는 특히, 최초 기판으로부터 분리된 막의 자유면이 연마하기 어렵거나 직접 공정 후에 그 평탄화 품질이 충분하지 못할 때 적용될 수 있다. 직접 공정에 의해 얻어진 막의 표면 거칠기는, 분리 단계 후에, 예정된 용도에 따라 자주 감소되어야 한다. 종래에는, 기계적 화학적 연마가 가능하다. 그러나, 많은 재료들, 예를 들어 "견고한" 재료 (사파이어, SiC, 다이아몬드 등)에 대해서는, 이러한 연마는 실제로 적절하지 못하거나 (이러한 연마는 큰 형태로 된 동일한 재료에 대해 발전되었기 때문에, 또는 그 품질이 충분하지 못하기 때문에, 또는 두께 균일성의 결함이 있다면, 견고한 재료의 막을 연마하기에 효과적이지 않다), 너무 긴 시간을 요한다 (이는 제조 비용을 증가시킨다). 본 발명은 이러한 문제점을 해결한다.

<93> [1-102] 방향을 갖는 단결정 사파이어의 웨이퍼에 의해 형성되고 표면 상에서 연마되어 에피택셜 품질을 갖는 최초 기판(1)을 고려해 보자. 웨이퍼는 실리콘 산화물의 층으로 다시 피복될 수 있다. 최초 기판(1)은 예를 들어 수소 등의 가스 화합물에 의해 주입된다. 산화물층이 없다면, 주입 에너지는  $2 \times 10^{17}$  원자/cm<sup>2</sup>의 도우즈에 대해 60 keV 일 것이다. 산화물이 존재하는 경우에는, 주입 에너지는 이 산화물의 두께를 고려하여 증가된다. 주입된 면 (제 1 콘택면)을 마련한 후, 최초 기판은 분자 결합에 의해 중간 서포트와 접촉하게 된다. 사파이어 막은 약화된 층 내에서 또는 이 약화된 층 근방에서 분리된다.

<94> 이렇게 분리한 후, 낮은 미세 거칠기(micro-roughness)를 갖는 사파이어 막을 얻는 것이 바람직하다. 기계적 화학적 연마는 이러한 형태의 재료에 대해 적용하기에는 시간이 매우 오래 걸리고, 막과 연마의 품질과 균일성을 제어하기 어렵다. 표면 품질이 에피택셜 형태가 아니거나 수반되는 비용이 높기 때문에, 직접 공정은 적용될 수 없다. 사파이어 최초 기판은 이미 에피택셜 품질로 된 면을 갖는 상태로 웨이퍼 공급자에 의해 판매되는데, 결국 본 발명은 자유면(또는 전면(front face))이 에피택셜 품질을 갖는 이러한 최초의 면이 되는 막을 구비하는 적층 구조를 얻는 데에 사용될 수 있다.

<95> 따라서, 최초 기판을 추가적인 최초 막을 통해 중간 서포트 상에 결합 접촉시킨 후에, 막과 최초 기판의 잔여 부분 사이의 분리 단계가 실시된다. 분리 후에, 사파이어 막의 자유면은 특정 거칠기를 가진다. 예를 들어

$\text{SiO}_2$  층 등의 재료층이 자유면 상에 중착되어, 기계적 화학적 연마가 그 표면의 평탄화를 가능하게 한다. 이러한 표면 및 (예를 들어 실리콘으로 제조된) 타겟 기판의 대응하는 표면을 마련한 후, 결합 접촉을 형성하는 제2 단계가 이루어진다. 중간 서포트를 제거하면, 사파이어막 또는 추가적인 최초 막의 최초 전면을 노출시키게 된다. 이러한 추가적인 최초 막은 유리하게는 실리콘 산화막이다. 이 경우, 그것은 화학적 반응에 의해 제거되어 사파이어막의 최초 전면을 방출할 수 있다. 이 전면이 산화물층에 의해 피복되어 있다면, 이 층은 화학적 반응에 의해 제거될 수 있다.

<96> 제 8 실시예는 막에 다른 특성을 가진 면이 제공되는 경우에 적용될 수 있다. 이것은, 예를 들어  $\text{SiC}$  또는  $\text{GaN}$ 으로 제조된 막(6) 상에 에피택시에 의한 연속된 성장에 대해 종래 기술의 상태로 이미 설명한 경우이다.

<97> 예를 들어, 최초  $\text{SiC}$  기판은 약 400 nm 두께의 산화물층으로 피복된다. 최초 기판은 120 keV 의 에너지를 가진 수소 원자에 의해  $8 \times 10^{16}$  원자/ $\text{cm}^2$  의 도우즈로 상기 산화물층을 통해 주입된다. 그 후 주입된 표면은 친수성으로 되며, 예를 들어 1  $\mu\text{m}$  두께의 산화물층으로 피복된 중간 기판의 일면과 분자 결합을 위해 접촉하게 된다. 분리 처리는 최초 기판의 잔여 부분으로부터 막을 분리한다. 그 후,  $\text{SiC}$  막은 산화물층을 통해 중간 서포트에 결합한다. (예를 들어, 기계적 화학적 연마 또는 평탄화를 가능하게 하는 막의 중착 등의) 표면 처리는  $\text{SiC}$  막의 새로운 자유면이 이 후의 결합에 적합하게 되도록 한다. 이러한 자유면은 친수성으로 되고 타겟 기판의 대응하는 면과 분자 결합을 위한 접촉을 하게 된다. 결합을 강화시키도록 하는 고온 열처리 후에, 분자 결합 에너지의 값은 1  $\text{J/m}^2$  이상일 수 있다.

<98> 그 후, 중간 서포트(10)가 예를 들어 그라인딩 후 화학적 반응에 의해 제거되며, 산화물층(3)은 에칭 저지층의 역할을 한다. 마지막으로, 산화물층(3)이 불산계의 용액을 사용한 반응에 의해 제거된다. 막의 최종 두께는, 예를 들어 씨닝 열처리를 사용하여 적합하게 변경된다.

<99> 이 실시예에서는, 100 nm 와 동일한 막(6)의 최종 두께가 기판의 대부분에 걸쳐 매우 좋은 균일성을 갖고 얻어진다. 막의 방출된 표면은 에피택시에 의한 연속된 성장에 적합한 표면에 대응한다.

<100> 제 9 실시예는 중간 서포트를 회수하는 것이 바람직하고 막(또는 여러 막들 중 하나)이 서로 다른 특성의 면을 갖는 경우에 적용될 수 있다. 이 실시예는 이전 실시예의 특별한 경우이다.

<101> 최초 기판의 잔여 부분(9)으로부터 막(6)을 분리하는 것으로 이루어진 단계(도 4 참조) 후에, 이온 주입 단계가 표면(12)을 통해 수행되어, 성질에 따라, 중간 기판 내에 또는 중간 기판이나 박층(7) 상에 중착된 추가적인 층들 중 한 층 내에 약화된 영역을 발생시킨다. 그것은 140 keV 의 에너지를 가지고  $8 \times 10^{16}$  원자/ $\text{cm}^2$  의 도우즈로 중간 기판 내에 주입되는 수소 주입일 수 있으며, 그 재료는 예를 들어, 제 8 실시예에서 설명된 재료이고, 중간 기판은  $\text{SiC}$ 로 제조된 것이다.

<102> 타겟 기판은 제 2 콘택면과 결합 접촉한다. 그 후, 중간 서포트는 적층 구조로부터 분리되고 재생될 수 있다. 실리콘 타겟 기판 상에  $\text{SiC}$  막을 제조하기 위한 공정의 경우에, 중간  $\text{SiC}$  서포트를 회수한다는 것은 경제적으로 매우 매력적인 것이다. 산화물층(13)은 불산 용액을 사용한 에칭에 의해 제거된다. 최종 막(6) 두께는 예를 들어 희생 산화에 의해 씨닝함으로서 적합하게 변경된다.

<103> 제 10 실시예는, 막 및 타겟 기판이 직접 공정으로는 양립되는 않는 적어도 하나의 특성을 갖는 경우에, 적용된다. 예를 들어, 막 및 타겟 기판을 형성하는 재료의 열팽창계수 사이의 차이가 너무 큰 경우에 이 실시예가 적용된다. 예를 들어, 실리콘과 석영, 실리콘과 사파이어, 실리콘과 갈륨비소,  $\text{Si}$  와  $\text{InP}$ ,  $\text{Si}$  와  $\text{LiNbO}_3$  가 그러하다. 직접 공정에 의한 분리 단계 동안에 또는 그 분리 단계 전에 사용된 열처리는 접촉 계면에서 분리를 일으키거나 결합 접촉된 2 개의 구성 요소 중 하나의 파손을 일으킨다.

<104> 예를 들어, 400 nm 두께의 산화물층(3)으로 피복된 실리콘 웨이퍼로 이루어진 최초 기판을 출발점으로 할 수 있다. 약화된 층(5)은 75 keV 의 에너지에서  $6 \times 10^{16}$  원자/ $\text{cm}^2$  의 도우즈로 수소 주입에 의해 형성된다. 콘택면(8)은, 양립되는 열팽창계수를 가진 중간 서포트(10)에 결합된다. 이 중간 서포트는 200 nm 두께의 산화물층으로 피복된 다른 실리콘 웨이퍼일 수 있다. 그 후, 열처리를 가할 수 있다. 이 열처리는 결합 에너지를 증가시킬 수 있어, 막과 최초 기판의 잔여부분 사이의 고품질의 분리를 일으킬 것이다. 일단 분리가 이루어지면, 도 4 에 도시된 적층 구조를 얻을 수 있다. 표면 처리는 막(6)의 표면 미세 거칠기를 최소화한다. 필요한 경우 표면을 처리한 후에, 상기 구조는 예를 들어 석영 또는 사파이어 판 등으로 된 타겟 기판(상기 타겟 기판의 열팽창계수는 최초 기판의 열팽창계수와 매우 다를 수 있음) 상으로 결합되고, 예를 들어 그라인딩, 화학적 에칭,

리프트 오프, 등등에 의해 중간 서포트가 제거된다.

<105> 이러한 제 10 실시예의 다른 예는, 에너지가 적어도 문턱 에너지(이 문턱 에너지 아래에서는 단계 c)가 발생할 수 없음)에 상당하는 단계 b)에서 결합을 일으키는 것으로 이루어진다. 단계 d) 전에, 예를 들어 수소 등의 이온 주입이 중간 기판 내에서 또는 이 중간 기판 내의 추가적인 층들 중 한 층에서 면(12)을 통해 행하여 진다. 이 주입은 이 기판 내에 약화된 층을 발생시켜, 단계 e) 동안에 이 약화된 층에서 분리가 일어날 것이다. 그 후, 중간 기판은 회수되어 재사용될 수 있다.

<106> 타겟 기판이 박층의 열산화물로 피복된 실리콘 웨이퍼라 할 지라도, 그 자체로 적층 구조로 이루어진 최초 기판, 예를 들어 질화물층으로 피복된 실리콘 웨이퍼에 대해 유사한 예들을 얻을 수 있다. 질화막의 열팽창계수는  $4 \times 10^{-6}/\text{k}$  보다 더 클 수 있는 반면, 산화막의 열팽창계수는  $10^{-6}/\text{k}$  보다 작다. 예를 들어 희생 산화에 의해 실리콘막을 씨딩하기 위해, 직접 공정 동안에 또는 직접 공정 후에 사용된 고온 열처리는 질화막과 실리카막 사이의 어떤 결합 에너지 조건에 대해 양립하지 않는다. 이 경우에, 본 발명에 따른 공정은 이러한 문제점을 해결한다. 단계 c) 후에, 박층을 고온에서 처리하여 희생 산화에 의해 실리콘을 씨딩한다. 단계 d) 후에, 추가적인 질화물층( $\text{Si}_3\text{N}_4$ )이 박층의 자유면 상에 제조되고 타겟 기판은 산화막( $\text{SiO}_2$ )으로 피복된다. 이 2개 층들은 박층의 자유면 상에 또는 타겟 기판 상에 중착될 수도 있다. 최종 적층 구조는 매우 다른 열팽창계수를 가진 2 개의 막에 의해 지지된 실리콘의 씨딩된 층에 해당한다.

<107> 제 11 실시예에 따르면, 직접 공정으로는 양립할 수 없게 하는 특성은 막 내에서 일어나는 상변화이다. 예를 들어, 실리콘 기판과 접촉된 팔라듐막은  $200\text{ }^\circ\text{C}$  를 넘는 온도에서의 열처리로 인해 실리사이드를 형성함으로써 결합을 가능하게 한다. 그러나,  $900\text{ }^\circ\text{C}$  에서, 이 실리사이드는 열화되어, 예를 들어 직접 공정으로  $900\text{ }^\circ\text{C}$  에서 희생 산화 단계를 실행할 수 없게 한다. 본 발명은 이러한 문제점을 해결한다.

<108> 중간 서포트(10) 상에 실리콘막(6)을 구비하는 박층(7)을 형성한 후, 실리콘막은 희생 산화에 의해  $900\text{ }^\circ\text{C}$  에서 씨딩되고, 그 후, 자유면(12)을 평탄화시키는 단계 후에, 팔라듐막이 중착되고 막(13)의 전부 또는 일부를 형성한다. 그 후, 타겟 기판과의 결합을 형성하는 열처리가  $870\text{ }^\circ\text{C}$  미만의 온도에서 실행되어 양질의 결합이 형성되고 정확한 두께의 실리콘막이 형성된다.

### 도면의 간단한 설명

<57> 첨부된 도면을 참조하여, 비한정적인 예로서 제시되는 이하의 설명에 의해 본 발명을 더 잘 이해할 수 있을 것 이고 다른 이점 및 특징들은 더 분명해질 것이다.

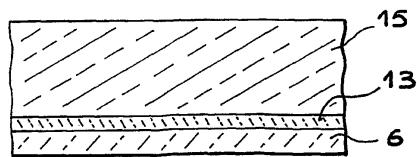

<58> 도 1은 본 발명이 적용되는 최초 기판이라 불리우는 기판의 단면도를 나타낸다.

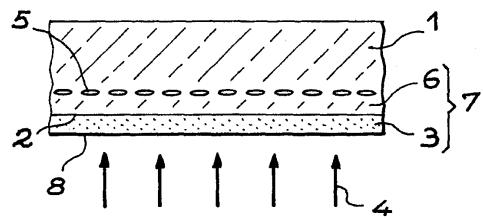

<59> 도 2는 재료층이 피복된 최초 기판의 단면도를 나타내는 단면도로서, 본 발명에 따른 공정의 실시 동안에 이온 주입 단계가 이 기판에 가해진다.

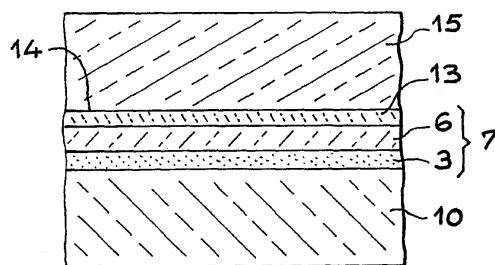

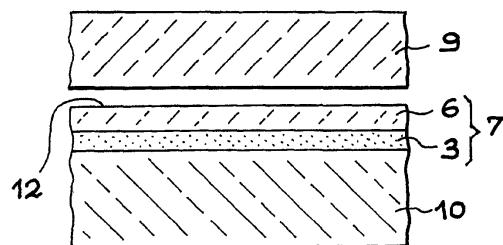

<60> 도 3은 본 발명에 따라 최초 기판이 상기 재료층을 통해 중간 서포트와 결합 접촉하는 단계를 나타낸다.

<61> 도 4는 본 발명에 따라 최초 기판의 적어도 일부가 제거되는 단계를 나타낸다.

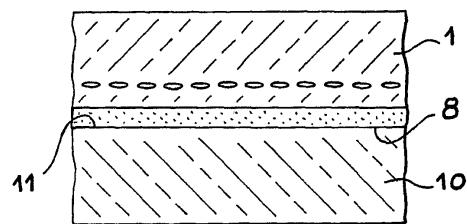

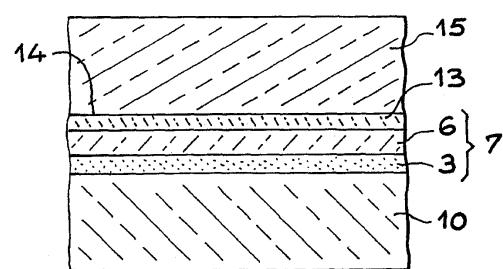

<62> 도 5는 본 발명에 따라 가능한 층을 통해 타겟 기판의 면과의 결합 접촉을 이루는 단계를 나타낸다.

<63> 도 6은 본 발명에 따른 공정에 의해 얻어진 적층 구조를 나타낸다.

### 도면

#### 도면1

도면2

도면3

도면4

도면5

도면6