(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-126526

(P2004-126526A)

(43) 公開日 平成16年4月22日(2004.4.22)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

**G09G 3/30**

G09G 3/30

J

3K007

**G09F 9/30**

G09F 9/30

338

5C080

**G09G 3/20**

G09F 9/30

365Z

5C094

**H01L 29/786**

G09G 3/20

611H

5F110

**H05B 33/14**

G09G 3/20

624B

審査請求 未請求 請求項の数 23 O L (全 16 頁) 最終頁に続く

(21) 出願番号

特願2003-198139(P2003-198139)

(22) 出願日

平成15年7月16日(2003.7.16)

(31) 優先権主張番号

特願2002-223160(P2002-223160)

(32) 優先日

平成14年7月31日(2002.7.31)

(33) 優先権主張国

日本国(JP)

(71) 出願人

000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人

100095728

弁理士 上柳 雅善

(74) 代理人

100107076

弁理士 藤綱 英吉

(74) 代理人

100107261

弁理士 須澤 修

(72) 発明者

宮澤 貴士

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA00

最終頁に続く

(54) 【発明の名称】電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び電子機器

## (57) 【要約】

【課題】トランジスタの閾値電圧のばらつきを低減することができる電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び電子機器を提供する。

【解決手段】駆動用トランジスタTrd、第1及び第2のスイッチング用トランジスタTr1, Tr2、調整用トランジスタTrc、カップリング用コンデンサC1及び保持用キャパシタC2での画素回路20を構成した。そして、調整用トランジスタTrcの閾値電圧が駆動用トランジスタTrdのゲートに印加されるようにした。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、

第3の端子と第4の端子と第2の制御用端子とを備え、前記第1の制御用端子に前記第3

の端子が接続された第2のトランジスタと、

第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された

容量素子と、

第5の端子と第6の端子とを備え、前記第2の電極に前記第5の端子が接続された第3の

トランジスタと、を含み

前記第2の制御用端子が前記第3の端子に接続されていることを特徴とする電子回路。 10

**【請求項 2】**

請求項1に記載の電子回路において、

第7の端子と第8の端子とを備え、前記第4の端子に前記第7の端子が接続された第4の

トランジスタを含むことを特徴とする電子回路。

**【請求項 3】**

請求項1または2に記載の電子回路において、

前記第1の端子には電子素子が接続されていることを特徴とする電子回路。

**【請求項 4】**

請求項3に記載の電子回路において、

前記電子素子は、電流駆動素子であることを特徴とする電子回路。 20

**【請求項 5】**

複数の第1の信号線と、複数の第2の信号線と、複数の電源線と、複数の単位回路を含む

電子回路であって、

前記複数の単位回路の各々は、

第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、

第3の端子と第4の端子と第2の制御用端子とを備え、前記第1の制御用端子に前記第3

の端子が接続された第2のトランジスタと、

第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された

容量素子と、

第5の端子と第6の端子と第3の制御用端子とを備え、前記第2の電極に前記第5の端子

が接続された第3のトランジスタと、を含み、

前記第2の制御用端子が前記第3の端子に接続され、

前記第3の制御用端子が前記複数の第1の信号線のうちの一つに接続されていることを特

徴とする電子回路。 30

**【請求項 6】**

請求項5に記載の電子回路において、

第7の端子と第8の端子と第4の制御用端子とを備え、前記第4の端子に前記第7の端子

が接続され、前記第4の制御用端子が前記複数の第2の信号線のうちの一つに接続された

第4のトランジスタを含むことを特徴とする電子回路。 40

**【請求項 7】**

請求項5または6に記載の電子回路において、

前記第1の端子には電子素子が接続されていることを特徴とする電子回路。

**【請求項 8】**

請求項7に記載の電子回路において、

前記電子素子は、電流駆動素子であることを特徴とする電子回路。

**【請求項 9】**

信号を電荷として保持する保持手段と、

前記保持手段への前記信号の伝送を制御する第1のスイッチング用トランジスタと、

前記保持手段に保持された電荷に基づいて導通状態が設定される駆動用トランジスタと、

前記保持手段への前記信号の伝送に先立って前記駆動用トランジスタの制御用端子を所定 50

の電位に設定する調整用トランジスタと

を備えたことを特徴とする電子回路。

【請求項 10】

請求項 9 に記載の電子回路において、

前記調整用トランジスタと所定電位との電気的接続又は電気的切断を制御する第 2 のスイ

ッチング用トランジスタを含むことを特徴とする電子回路。

【請求項 11】

請求項 9 または 10 に記載の電子回路において、

前記駆動用トランジスタには電子素子が接続されていることを特徴とする電子回路。

【請求項 12】

請求項 11 に記載の電子回路において、

前記電子素子は、電流駆動素子であることを特徴とする電子回路。

【請求項 13】

第 1 の端子と第 2 の端子と第 1 の制御用端子とを備えた第 1 のトランジスタと、

第 3 の端子と第 4 の端子とを備え、前記第 1 の制御用端子に前記第 3 の端子が接続された

第 2 のトランジスタと、

第 1 の電極と第 2 の電極とを備え、前記第 1 の制御用端子に前記第 1 の電極が接続された

容量素子と

を含む電子回路の駆動方法であって、

前記第 4 の端子を所定電位に電気的に接続するとともに前記第 1 の制御用端子を第 1 の電

位に設定する第 1 のステップと、

前記第 4 の端子を前記所定電位から電気的に切断した状態で、前記容量素子の第 2 の電極

の電位を第 2 の電位から第 3 の電位に変化させることにより前記第 1 の制御用端子を前記

第 1 の電位から変化させる第 2 のステップと

を含むことを特徴とする電子回路の駆動方法。

【請求項 14】

請求項 13 に記載の電子回路の駆動方法において、

少なくとも前記第 1 のステップを行っている期間は前記第 2 の電極の電位を前記第 2 の電

位に設定した状態で行うことを行なうことを特徴とする電子回路の駆動方法。

【請求項 15】

複数の走査線と、複数のデータ線と、複数の電源線と、電気光学素子を有する複数の単位

回路を含む電気光学装置であって、

前記複数の単位回路の各々は、

第 1 の端子と第 2 の端子と第 1 の制御用端子とを備えた第 1 のトランジスタと、

前記第 1 の端子と接続された電気光学素子と、

第 3 の端子と第 4 の端子と第 2 の制御用端子とを備え、前記第 1 の制御用端子に前記第 3

の端子が接続された第 2 のトランジスタと、

第 1 の電極と第 2 の電極とを備え、前記第 1 の制御用端子に前記第 1 の電極が接続された

容量素子と、

第 5 の端子と第 6 の端子と第 3 の制御用端子とを備え、前記第 2 の電極に前記第 5 の端子

が接続された第 3 のトランジスタと、

第 7 の端子と第 8 の端子とを備え、前記第 7 の端子が前記第 4 の端子に接続された第 4 の

トランジスタと、を含み、

前記第 2 の制御用端子が前記第 3 の端子に接続され、

前記第 3 の制御用端子が前記複数の走査線のうちの一つに接続され、

前記第 6 の端子が前記複数のデータ線のうちの一つに接続されていることを特徴とする電

気光学装置。

【請求項 16】

請求項 15 に記載の電気光学装置において、

前記電気光学素子は、有機 E L 素子であることを特徴とする電気光学装置。

10

20

30

40

50

**【請求項 17】**

複数の走査線と、複数のデータ線と、複数の電源線と、電気光学素子を有する複数の単位回路とを備えた電気光学装置であって、

前記複数の単位回路の各々は、

前記複数の走査線のうち対応する一つの走査線を介して供給される走査信号に応じて導通状態が制御される第1のスイッチング用トランジスタと、

前記複数のデータ線の一つのデータ線と前記第1のスイッチング用トランジスタとを介して供給されるデータ信号を電荷として蓄積する保持手段と、

前記保持手段に蓄積された電荷量に基づいて導通状態が設定され、前記導通状態に応じた電流レベルを有する電流を前記電気光学素子に供給する駆動用トランジスタと、

前記保持手段へ前記データ信号を伝送するのに先立って前記駆動用トランジスタの制御用端子を所定の電位に設定する調整用トランジスタと

を備えたことを特徴とする電気光学装置。

**【請求項 18】**

請求項17に記載の電気光学装置において、

前記複数の単位回路の各々は、前記調整用トランジスタと所定電位との電気的接続又は電気的切断を制御する第2のスイッチング用トランジスタを含むことを特徴とする電気光学装置。

**【請求項 19】**

請求項17または18に記載の電気光学装置において、

前記電気光学素子は、有機EL素子であることを特徴とする電気光学装置。

**【請求項 20】**

第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、

第3の端子と第4の端子とを備え、前記第1の制御用端子に前記第3の端子が接続された第2のトランジスタと、

第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された容量素子と

を含む複数の単位回路と、複数の走査線と、複数のデータ線と、複数の電源線とを含む電気光学装置の駆動方法であって、

前記第4の端子を所定電位に電気的に接続するとともに前記第1の制御用端子を第1の電位に設定する第1のステップと、

一端が前記第2の電極に接続された第3のトランジスタを前記複数の走査線を介して走査信号を供給することによりオン状態とした後、前記第4の端子を前記所定電位から電気的に切断した状態で、前記複数のデータ線からデータ信号に対応する電圧を前記第3のトランジスタを介して前記第2の電極に印加し、前記第2の電極の電位を第2の電位から第3の電位に変化させることにより前記第1の制御用端子の電位を前記第1の電位から変化させる第2のステップと

を含むことを特徴とする電気光学装置の駆動方法。

**【請求項 21】**

請求項20に記載の電気光学装置の駆動方法において、

少なくとも前記第1のステップを行っている期間は前記容量素子の第2の電極の電位を前記第2の電位に設定した状態で行うことを特徴とする電気光学装置の駆動方法。

**【請求項 22】**

請求項1～12に記載の電子回路を実装したことを特徴とする電子機器。

**【請求項 23】**

請求項15～19に記載の電気光学装置を実装したことを特徴とする電子機器。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び

10

20

30

40

50

電子機器に関するものである。

【0002】

【従来の技術】

例えば、液晶素子、有機EL素子、電気泳動素子、電子放出素子等の電気光学素子を備えた電気光学装置の駆動方式の一つにアクティブマトリクス駆動方式がある。アクティブマトリクス駆動方式の電気光学装置は、その表示パネル部に複数の画素回路がマトリクス状に配置されている。前記複数の画素回路の各々は、電気光学素子と、その電気光学素子に駆動電力を供給する駆動用トランジスタとを備えている。

中でも、有機EL素子等の電流で駆動される電流駆動素子（特許文献1）の輝度は、電流レベルに依存するため、精度良く画素回路を駆動する必要がある。

10

【特許文献1】国際公開番号WO98/36407号のパンフレット

【発明が解決しようとする課題】

ところで、各画素回路は、前記駆動用トランジスタの閾値電圧などの特性にばらつきがあるため、同じ階調に対応するデータ信号が供給されても電気光学素子の輝度が各画素毎に異なってしまう場合がある。特に、前記駆動用トランジスタとして薄膜トランジスタを用いた場合は、その閾値電圧のばらつきが顕著であるため、所望の表示品位が得られないことがある。

【0003】

本発明は上記問題点を解決するためになされたものであって、その目的は、トランジスタの閾値電圧のばらつきを低減することができる電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び電子機器を提供することにある。

20

【0004】

【課題を解決するための手段】

本発明における電子回路は、第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、第3の端子と第4の端子と第2の制御用端子とを備え、前記第1の制御用端子に前記第3の端子が接続された第2のトランジスタと、第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された容量素子と、第5の端子と第6の端子とを備え、前記第2の電極に前記第5の端子が接続された第3のトランジスタと、を含み前記第2の制御用端子が前記第3の端子に接続されている。

【0005】

これによれば、第1のトランジスタの製造ばらつきによる閾値電圧を補償する電子回路を提供することができる。

30

【0006】

この電子回路において、第7の端子と第8の端子とを備え、前記第2のトランジスタの前記第4の端子に前記第7の端子が接続された第4のトランジスタを含む。

【0007】

これによれば、前記第4のトランジスタの導通状態を制御することにより前記第1の制御用端子の電位を所望の電位に設定し、維持することができる。

【0008】

上記の電子回路において、前記第1の端子には電子素子が接続されるようにしても良い。

【0009】

上記の電子回路において、前記電子素子としては、例えば、電流駆動素子であっても良い。

【0010】

本発明における電子回路は、複数の第1の信号線と、複数の第2の信号線と、複数の電源線と、複数の単位回路を含む電子回路であって、前記複数の単位回路の各々は、第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、第3の端子と第4の端子と第2の制御用端子とを備え、前記第1の制御用端子に前記第3の端子が接続された第2のトランジスタと、第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された容量素子と、第5の端子と第6の端子と第3の制御用端子とを

40

50

備え、前記第2の電極に前記第5の端子が接続された第3のトランジスタと、を含み、前記第2の制御用端子が前記第3の端子に接続され、前記第3の制御用端子が前記複数の第1の信号線のうちの一つに接続されている。

【0011】

これによれば、第1のトランジスタの製造ばらつきによる閾値電圧を補償することができる電子回路を提供することができる。

【0012】

この電子回路において、第7の端子と第8の端子と第4の制御用端子とを備え、前記第4の端子に前記第7の端子が接続され、前記第4の制御用端子が前記複数の第2の信号線のうちの一つに接続された第4のトランジスタを含む。

10

【0013】

これによれば、前記第4のトランジスタの導通状態を制御することにより前記第1の制御用端子の電位を所望の電位に設定し、維持することができる。

【0014】

上記の電子回路において、前記第1の端子には電子素子が接続されるようにしても良い。

【0015】

上記の電子回路において、前記電子素子としては、例えば、電流駆動素子であっても良い。

【0016】

本発明における電子回路は、信号を電荷として保持する保持手段と、前記保持手段への前記信号の伝送を制御する第1のスイッチング用トランジスタと、前記保持手段に保持された電荷に基づいて導通状態が設定される駆動用トランジスタと、前記保持手段への前記信号の伝送に先立って前記駆動用トランジスタの制御用端子を所定の電位に設定する調整用トランジスタとを備えた。

20

【0017】

これによれば、第1のスイッチング用トランジスタのオン・オフ制御によって駆動用トランジスタの閾値電圧を補償することができる電子回路を提供することができる。

【0018】

上記の電子回路において、前記調整用トランジスタと所定電位との電気的接続又は電気的切断を制御する第2のスイッチング用トランジスタを含んでいることが好ましい。

30

【0019】

上記の電子回路において、前記駆動用トランジスタには電子素子が接続されるようにしても良い。

【0020】

上記の電子回路において、電子素子としては、例えば、電流駆動素子などが挙げられる。

【0021】

本発明における電子回路の駆動方法は、第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、第3の端子と第4の端子とを備え、前記第1の制御用端子に前記第3の端子が接続された第2のトランジスタと、第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された容量素子とを含む電子回路の駆動方法であって、前記第4の端子を所定電位に電気的に接続するとともに前記第1の制御用端子を第1の電位に設定する第1のステップと、前記第4の端子を前記所定電位から電気的に切断した状態で、前記容量素子の第2の電極の電位を第2の電位から第3の電位に変化させることにより前記第1の制御用端子を前記第1の電位から変化させる第2のステップとを含む。

40

【0022】

これによれば、前記第1のトランジスタ製造ばらつきによる閾値電圧を補償する電子回路を駆動させることができる。

【0023】

上記の電子回路の駆動方法において、前記第1のステップは前記第2の電極の電位を前記

50

第2の電位に設定した状態で行うことが好ましい。

【0024】

本発明における電気光学装置は、複数の走査線と、複数のデータ線と、複数の電源線と、電気光学素子を有する複数の単位回路を含む電気光学装置であって、前記複数の単位回路の各々は、第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、前記第1の端子と接続された電気光学素子と、第3の端子と第4の端子と第2の制御用端子とを備え、前記第1の制御用端子に前記第3の端子が接続された第2のトランジスタと、第1の電極と第2の電極とを備え、前記第1の制御用端子に前記第1の電極が接続された容量素子と、第5の端子と第6の端子と第3の制御用端子とを備え、前記第2の電極に前記第5の端子が接続された第3のトランジスタと、第7の端子と第8の端子とを備え、前記第7の端子が前記第4の端子に接続された第4のトランジスタと、を含み、前記第2の制御用端子が前記第3の端子に接続され、前記第3の制御用端子が前記複数の走査線のうちの一つに接続され、前記第6の端子が前記複数のデータ線のうちの一つに接続されている。10

【0025】

これによれば、第1のトランジスタの製造ばらつきによる閾値電圧を補償することができる。その結果、電気光学素子の輝度階調を精度良く制御することができるため、従来の電気光学装置と比較してその表示品位の向上を図ることができる。

【0026】

上記の電気光学装置において、前記電気光学素子としては、例えば、有機EL素子が挙げられる。20

【0027】

本発明における電気光学装置は、複数の走査線と、複数のデータ線と、複数の電源線と、電気光学素子を有する複数の単位回路とを備えた電気光学装置であって、前記複数の単位回路の各々は、前記複数の走査線のうち対応する一つの走査線を介して供給される走査信号に応じて導通状態が制御される第1のスイッチング用トランジスタと、前記複数のデータ線の一つのデータ線と前記第1のスイッチング用トランジスタとを介して供給されるデータ信号を電荷として蓄積する保持手段と、前記保持手段に蓄積された電荷量に基づいて導通状態が設定され、前記導通状態に応じた電流レベルを有する電流を前記電気光学素子に供給する駆動用トランジスタと、前記保持手段へ前記データ信号を伝送するのに先立つて前記駆動用トランジスタの制御用端子を所定の電位に設定する調整用トランジスタとを備えた。30

【0028】

これによれば、駆動用トランジスタの製造ばらつきによる閾値電圧を補償することができる。その結果、電気光学素子の輝度階調を精度良く制御することができるため、従来の電気光学装置と比較してその表示品位の向上を図ることができる。

【0029】

この電気光学装置において、前記複数の単位回路の各々は、前記調整用トランジスタと所定電位との電気的接続又は電気的切断を制御する第2のスイッチング用トランジスタを含む。40

【0030】

これによれば、第2のスイッチング用トランジスタのオン・オフ制御に応じて第1のトランジスタの閾値電圧を補償することができる。

【0031】

上記の電気光学装置において、前記電気光学素子としては、例えば、有機EL素子である。

【0032】

本発明における電気光学装置の駆動方法は、第1の端子と第2の端子と第1の制御用端子とを備えた第1のトランジスタと、第3の端子と第4の端子とを備え、前記第1の制御用端子に前記第3の端子が接続された第2のトランジスタと、第1の電極と第2の電極とを

50

備え、前記第1の制御用端子に前記第1の電極が接続された容量素子とを含む複数の単位回路と、複数の走査線と、複数のデータ線と、複数の電源線とを含む電気光学装置の駆動方法であって、前記第4の端子を所定電位に電気的に接続するとともに前記第1の制御用端子を第1の電位に設定する第1のステップと、一端が前記第2の電極に接続された第3のトランジスタを前記複数の走査線を介して走査信号を供給することによりオン状態とした後、前記第4の端子を前記所定電位から電気的に切断した状態で、前記複数のデータ線からデータ信号に対応する電圧を前記第3のトランジスタを介して前記第2の電極に印加し、前記第2の電極の電位を第2の電位から第3の電位に変化させることにより前記第1の制御用端子の電位を前記第1の電位から変化させる第2のステップとを含む。

10

#### 【0033】

これによれば、第1のトランジスタの閾値電圧を補償する電気光学装置を駆動させることができる。

#### 【0034】

少なくとも前記第1のステップを行っている期間は前記容量素子の第2の電極の電位を前記第2の電位に設定した状態で行う。

#### 【0035】

上記の電気光学装置の駆動方法において、前記第1のステップは前記容量素子の第2の電極の電位を前記第2の電位に設定した状態で行うことが好ましい。

#### 【0036】

本発明の電子機器は、上記の電子回路を実装したことを特徴とする。

20

#### 【0037】

上記の電子機器は、上記の電子回路を備えているので、電流の精密な制御が可能である。

#### 【0038】

本発明の第2の電子機器は、上記の電気光学装置を実装したことを特徴とする。

#### 【0039】

これによれば、表示品質が優れた表示ユニットを有した電子機器を提供することができる。

#### 【0040】

#### 【発明の実施の形態】

30

##### (第1実施形態)

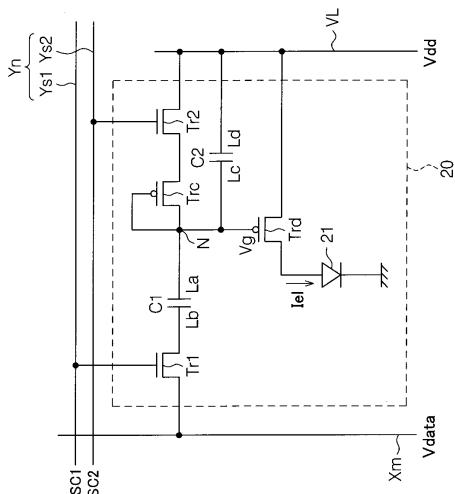

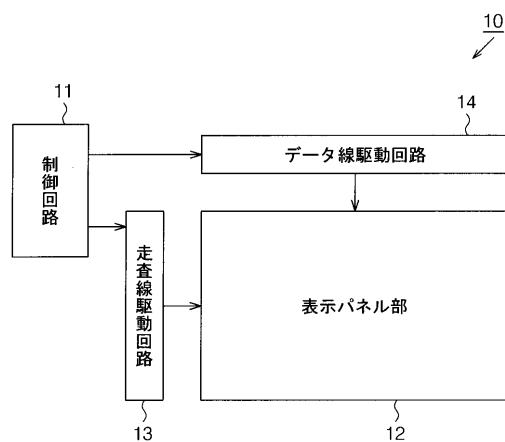

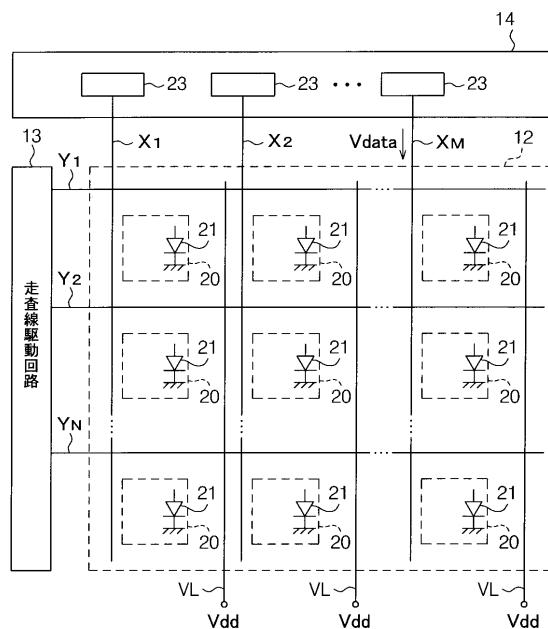

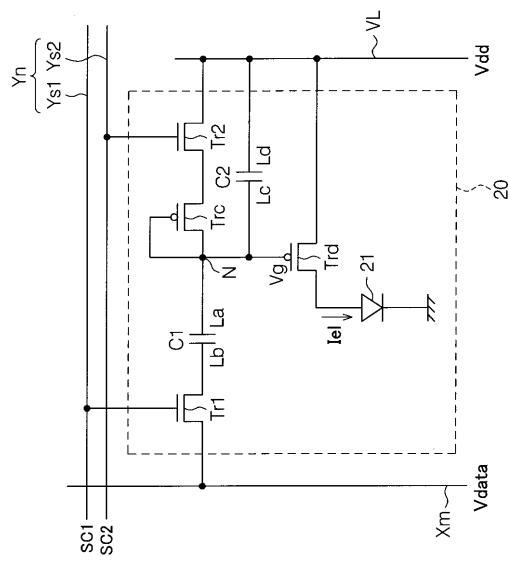

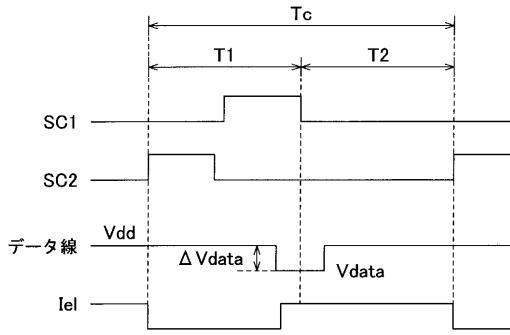

以下、本発明の一つの実施の態様として有機ELディスプレイを例に挙げ、図1～4を用いて説明する。図1は、電気光学装置としての有機ELディスプレイの制御系の構成を示すである。図2は、表示パネル部及びデータ線駆動回路の内部回路構成を示すブロック回路図である。図3は画素回路の回路図である。図4は、画素回路の駆動方法を説明するためのタイミングチャートである。

#### 【0041】

有機ELディスプレイ10は、図1に示すように、制御回路11、表示パネル部12、走査線駆動回路13及びデータ線駆動回路14を備えている。

#### 【0042】

有機ELディスプレイ10の制御回路11、走査線駆動回路13及びデータ線駆動回路14は、それぞれが独立した電子部品によって構成されていてもよい。例えば、制御回路11、走査線駆動回路13及びデータ線駆動回路14が、各々1チップの半導体集積回路装置によって構成されていてもよい。又、制御回路11、走査線駆動回路13及びデータ線駆動回路14の全部若しくは一部がプログラマブルなICチップで構成され、その機能がICチップに書き込まれたプログラムによりソフトウェア的に実現されてもよい。

#### 【0043】

制御回路11は、図示しない外部装置からの画像データに基づいて表示パネル部12に画像を表示するための走査制御信号及びデータ制御信号を作成する。そして、制御回路11は、走査制御信号を走査線駆動回路13に出力するとともに、データ制御信号をデータ線

40

50

駆動回路 14 に出力する。

【 0 0 4 4 】

表示パネル部 12 は、図 2 に示すように、列方向に沿って延びる M 本のデータ線 X<sub>m</sub> ( m = 1 ~ M ; m は整数 ) と、行方向に沿って延びる N 本の走査線 Y<sub>n</sub> ( n = 1 ~ N ; n は整数 ) との交差部に対応する位置に配設された複数の電子回路又は単位回路としての画素回路 20 を有している。つまり、各画素回路 20 は、その列方向に沿って延びるデータ線 X<sub>m</sub> と、行方向に沿って延びる走査線 Y<sub>n</sub> とにそれぞれ接続されることによりマトリクス状に配列されている。又、走査線 Y<sub>n</sub> は、後記する第 1 の副走査線 Y<sub>s1</sub> と第 2 の副走査線 Y<sub>s2</sub> ( 図 3 参照 ) とから構成されている。

【 0 0 4 5 】

画素回路 20 は、図 2 に示すように、電子素子又は電気光学素子としての有機 E L 素子 21 を有する。又、各画素回路 20 は、それぞれ列方向に沿って延びる電源線 V<sub>L</sub> と接続されて、その電源線 V<sub>L</sub> を介して電源電位としての駆動電圧 V<sub>dd</sub> が供給されるようになっている。尚、本実施形態では各画素回路 20 内に配置形成される後記するトランジスタは、ここでは TFT ( 薄膜トランジスタ ) で構成されているが、これに限定されることはなく、たとえば、MOS トランジスタで構成されていても良い。

【 0 0 4 6 】

走査線駆動回路 13 は、制御回路 11 から出力される走査制御信号に基づいて、表示パネル部 12 に配置された複数の走査線 Y<sub>n</sub> のうち、1 本の走査線を選択し、その選択された走査線に走査信号を出力する。

【 0 0 4 7 】

データ線駆動回路 14 は、図 2 に示すように、複数の單一ラインドライバ 23 を備えている。单一ラインドライバ 23 は、表示パネル部 12 に配設されたデータ線 X<sub>m</sub> と接続されている。

【 0 0 4 8 】

詳しくは、データ線駆動回路 14 は、制御回路 11 から出力されたデータ制御信号に基づいて、それぞれのデータ信号としてのデータ電圧 V<sub>data</sub> を生成する。そして、その生成されたデータ電圧 V<sub>data</sub> は前記データ線 X<sub>m</sub> を介して各画素回路 20 に供給される。そして、前記画素回路 20 は、このデータ電圧 V<sub>data</sub> に応じて同画素回路 20 の内部状態が設定されることで、有機 E L 素子 21 に流れる駆動電流 I<sub>e1</sub> ( 図 3 参照 ) が制御されるようになっている。また、データ線駆動回路 14 は、後記するデータ書き込み期間 T<sub>1</sub> において、前記データ電圧 V<sub>data</sub> を供給する前に駆動電圧 V<sub>dd</sub> を各画素回路 20 に供給するようになっている。

【 0 0 4 9 】

このように構成された有機 E L ディスプレイ 10 を構成する画素回路 20 について図 3 に基づいて以下に説明する。

【 0 0 5 0 】

画素回路 20 は、図 3 に示すように、駆動用トランジスタ T<sub>rd</sub> 、調整用トランジスタ T<sub>rc</sub> を備えている。又、画素回路 20 は、第 1 のスイッチング用トランジスタ T<sub>r1</sub> 及び第 2 のスイッチング用トランジスタ T<sub>r2</sub> を備えている。更に、画素回路 20 は、容量素子又は保持手段としてのカップリング用コンデンサ C<sub>1</sub> と保持用キャパシタ C<sub>2</sub> を備えている。

【 0 0 5 1 】

尚、特許請求の範囲における第 1 のトランジスタ及び駆動用トランジスタ、第 1 の端子、第 2 の端子、第 1 の制御用端子及び制御用端子は、それぞれ、本実施形態においては、駆動用トランジスタ T<sub>rd</sub> 、駆動用トランジスタ T<sub>rd</sub> のドレイン、駆動用トランジスタ T<sub>rd</sub> のソース、駆動用トランジスタ T<sub>rd</sub> のゲートに対応している。また、第 2 のトランジスタ及び調整用トランジスタ、第 3 の端子、第 4 の端子、第 2 の制御用端子及び制御用端子は、それぞれ、調整用トランジスタ T<sub>rc</sub> 、調整用トランジスタ T<sub>rc</sub> のドレイン、調整用トランジスタ T<sub>rc</sub> のソース、調整用トランジスタ T<sub>rc</sub> のゲートに対応している

10

20

30

40

50

。さらに、第3のトランジスタ、第5の端子、第6の端子、第3の制御用端子は、それぞれ、第1のスイッチング用トランジスタTr1、第1のスイッチング用トランジスタTr1のドレイン、第1のスイッチング用トランジスタTr1のソース、第1のスイッチング用トランジスタTr1のゲートに対応している。また、第4のトランジスタ、第7の端子、第8の端子、第4の制御用端子は、それぞれ、第2のスイッチング用トランジスタTr2、第2のスイッチング用トランジスタTr2のソース、第2のスイッチング用トランジスタTr2のドレイン、第2のスイッチング用トランジスタTr2のゲートに対応している。

#### 【0052】

駆動用トランジスタTrd及び調整用トランジスタTrcの導電型は、それぞれ、p型(pチャネル)で構成されている。又、第1及び第2のスイッチング用トランジスタTr1、Tr2の導電型は、それぞれ、n型(nチャネル)で構成されている。10

#### 【0053】

駆動用トランジスタTrdは、ドレインが有機EL素子21の陽極に接続されている。有機EL素子21の陰極は接地されている。駆動用トランジスタTrdのソースは前記電源線VLに接続されている。駆動用トランジスタTrdのゲートは、カップリング用コンデンサC1と、保持用キャパシタC2と、調整用トランジスタTrcとにそれぞれ接続されている。カップリング用コンデンサC1の静電容量はCaである。又、保持用キャパシタC2の静電容量はCbである。

#### 【0054】

詳しくは、カップリング用コンデンサC1は、その第1の電極Laが前記駆動用トランジスタTrdのゲートに接続されるとともに、第2の電極Lbが第1のスイッチング用トランジスタTr1のドレインに接続されている。保持用キャパシタC2は、その第3の電極Lcが前記駆動用トランジスタTrdのゲートに接続されるとともに、第4の電極Ldが前記電源線VLに接続されている。20

#### 【0055】

又、第1のスイッチング用トランジスタTr1のゲートは、前記走査線Ynを構成する第1の信号線としての第1の副走査線Ys1に接続されている。

#### 【0056】

調整用トランジスタTrcは、ノードNにて、そのゲートがドレインに接続されるとともに、前記駆動用トランジスタTrdのゲートに接続されている。又、調整用トランジスタTrcは、そのソースが第2のスイッチング用トランジスタTr2のソースに接続されている。第2のスイッチング用トランジスタTr2のドレインは電源線VLに接続されている。又、第2のスイッチング用トランジスタTr2のゲートは、走査線Ynを構成する第2の信号線としての第2の副走査線Ys2に接続されている。そして、前記第1の副走査線Ys1と第2の副走査線Ys2とで走査線Ynを構成する。30

#### 【0057】

又、前記調整用トランジスタTrcは、その閾値電圧Vth2が前記駆動用トランジスタTrdの閾値電圧Vth1とほぼ等しくなるように設定されている。尚、前記調整用トランジスタTrcの閾値電圧Vth2は、その駆動条件に応じて適宜設定してもよい。又、前記駆動電圧Vddはデータ電圧Vdataと比べて十分高くなるように予め設定されている。40

#### 【0058】

次に、前記のように構成された有機ELディスプレイ10の画素回路20の動作について図4に従って説明する。なお、図4において、Tc、T1及びT2は、それぞれ、駆動周期、第1及び第2のステップとしてのデータ書き込み期間及び発光期間を表している。駆動周期Tcは、データ書き込み期間T1と発光期間T2とから構成されている。駆動周期Tcは、前記有機EL素子21の輝度階調が1回ずつ更新される周期を意味しており、所謂、フレーム周期と同じものである。

#### 【0059】

50

20

30

40

50

まず、データ書き込み期間 T<sub>1</sub>において、前記走査線駆動回路 13 から第 2 の副走査線 Y<sub>s2</sub>を介して第 2 のスイッチング用トランジスタ T<sub>r2</sub>のゲートに同第 2 のスイッチング用トランジスタ T<sub>r2</sub>をオン状態にする第 2 の走査信号 S<sub>C2</sub>が印加される。すると、第 2 のスイッチング用トランジスタ T<sub>r2</sub>がオン状態になる。その結果、調整用トランジスタ T<sub>rc</sub>のソースには前記電源線 V<sub>L</sub>を介して駆動電圧 V<sub>dd</sub>が供給される。また、このとき、走査線駆動回路 13 から第 1 の副走査線 Y<sub>s1</sub>を介して第 1 のスイッチング用トランジスタ T<sub>r1</sub>のゲートに同第 1 のスイッチング用トランジスタ T<sub>r1</sub>をオフ状態にする第 1 の走査信号 S<sub>C1</sub>が印加されている。

## 【0060】

このことによって、調整用トランジスタ T<sub>rc</sub>のソースの電位は駆動電圧 V<sub>dd</sub>になる。

そして、前記ノード N での電位 V<sub>n1</sub>は、駆動電圧 V<sub>dd</sub>から調整用トランジスタ T<sub>rc</sub>の閾値電圧 V<sub>th2</sub>分の値とが減算された値 (V<sub>n1</sub> = V<sub>dd</sub> - V<sub>th2</sub>) となるとともに、その電位 V<sub>n1</sub>が初期電位 V<sub>c1</sub>として保持用キャパシタ C<sub>2</sub>に保持される。また、前記電位 V<sub>n1</sub>が駆動用トランジスタ T<sub>rd</sub>のゲートに供給される。その結果、前記したように、調整用トランジスタ T<sub>rc</sub>の閾値電圧 V<sub>th2</sub>は、駆動用トランジスタ T<sub>rd</sub>の閾値電圧 V<sub>th1</sub>とほぼ等しいので、前記駆動用トランジスタ T<sub>rd</sub>はその閾値電圧 V<sub>th1</sub>が補償された状態になる。

## 【0061】

その後、走査線駆動回路 13 から第 2 の副走査線 Y<sub>s2</sub>を介して第 2 のスイッチング用トランジスタ T<sub>r2</sub>のゲートに同第 2 のスイッチング用トランジスタ T<sub>r2</sub>をオフ状態にする第 2 の走査信号 S<sub>C2</sub>が印加される。すると、第 2 のスイッチング用トランジスタ T<sub>r2</sub>がオフ状態になる。続いて、走査線駆動回路 13 から第 1 の副走査線 Y<sub>s1</sub>を介して第 1 のスイッチング用トランジスタ T<sub>r1</sub>のゲートに同第 1 のスイッチング用トランジスタ T<sub>r1</sub>をオン状態にする第 1 の走査信号 S<sub>C1</sub>が印加される。すると、第 1 のスイッチング用トランジスタ T<sub>r1</sub>がオン状態になる。

## 【0062】

そして、まず、前記データ線 X<sub>m</sub>を介して画素回路 20 に駆動電圧 V<sub>dd</sub>が供給される。その後、直ちに前記データ線駆動回路 14 の單一ラインドライバ 23 からデータ線 X<sub>m</sub>を介してデータ電圧 V<sub>data</sub>が供給される。

## 【0063】

このことによって、前記初期電位 V<sub>c1</sub>は、カップリング用コンデンサ C<sub>1</sub>の静電容量 C<sub>a</sub>及び保持用キャパシタ C<sub>2</sub>の静電容量 C<sub>b</sub>を用いると、以下の式で表わす値に変化する。

## 【0064】

$$V_{c1} = V_{dd} - V_{th2} + C_a / (C_a + C_b) \cdot V_{data}$$

ここで、V<sub>data</sub>は、前記駆動電圧 V<sub>dd</sub>とデータ電圧 V<sub>data</sub>との電位差 (= V<sub>dd</sub> - V<sub>data</sub>) である。そして、この V<sub>dd</sub> - V<sub>th2</sub> + C<sub>a</sub> / (C<sub>a</sub> + C<sub>b</sub>) · V<sub>data</sub>が最終電位 V<sub>c2</sub>として駆動用トランジスタ T<sub>rd</sub>のゲートに供給される。

## 【0065】

前記最終電位 V<sub>c2</sub>に応じて、駆動用トランジスタ T<sub>rd</sub>の導通状態が設定され、その導通状態に応じた駆動電流 I<sub>e1</sub>が有機 EL 素子 21 に供給される。この電流 I<sub>e1</sub>は、その駆動用トランジスタ T<sub>rd</sub>のゲート電圧とソース電圧との電圧差を V<sub>gs</sub>で表すと、以下のように表される。

## 【0066】

$$I_{e1} = (1/2) (-V_{gs} - V_{th1})^2$$

ここで、- は利得係数であって、キャリアの移動度を μ、ゲート容量を A、チャネル幅を W、チャネル長を L で表すと、利得係数 - は、= (μ A W / L) となる。なお、駆動用トランジスタ T<sub>rd</sub>のゲート電圧 V<sub>g</sub>は前記最終電位 V<sub>c2</sub>である。つまり、駆動用トランジスタ T<sub>rd</sub>のゲート電圧とソース電圧との電圧差 V<sub>gs</sub>は以下のように表される。

## 【0067】

10

20

30

40

50

$$V_{g s} = V_{d d} - [V_{d d} - V_{t h 2} + C_a / (C_a + C_b) \cdot V_{data}]$$

従って、駆動用トランジスタ  $T_{rd}$  の駆動電流  $I_{e1}$  は以下のように表される。

#### 【0068】

$$I_{e1} = (1/2) [V_{t h 2} - C_a / (C_a + C_b) \cdot V_{data} - V_{t h 1}]^2$$

ここで、前記調整用トランジスタ  $T_{rc}$  の閾値電圧  $V_{t h 2}$  は、前記したように、駆動用トランジスタ  $T_{rd}$  の閾値電圧  $V_{t h 1}$  とほぼ等しくなるように設定してあるので、駆動電流  $I_{e1}$  は以下のように表される。

#### 【0069】

$$I_{e1} = (1/2) [V_{t h 2} - C_a / (C_a + C_b) \cdot V_{data} - V_{t h 1}]^2$$

$$= (1/2) [C_a / (C_a + C_b) \cdot V_{data}]^2$$

従って、上式に示されるように、前記駆動電流  $I_{e1}$  は、前記駆動用トランジスタ  $T_{rd}$  の閾値電圧  $V_{t h 1}$  に依存することなく、データ電圧  $V_{data}$  に対応した大きさの電流となる。そして、この駆動電流  $I_{e1}$  が前記有機EL素子  $Z_1$  に供給され、同有機EL素子  $Z_1$  が発光することとなる。

10

#### 【0070】

次に、前記データ書き込み期間  $T_1$  終了後、発光期間  $T_2$  にて、前記走査線駆動回路  $1_3$  から第1の副走査線  $Y_{s1}$  を介して第1のスイッチング用トランジスタ  $T_{r1}$  のゲートに同第1のスイッチング用トランジスタ  $T_{r1}$  をオフ状態にする第1の走査信号  $S_{C1}$  が印加される。すると、第1のスイッチング用トランジスタ  $T_{r1}$  がオフ状態になる。

20

#### 【0071】

この発光期間  $T_2$  においては、前記最終電位  $V_{c2}$  に応じて設定された駆動用トランジスタ  $T_{rd}$  の導通状態に応じた駆動電流  $I_{e1}$  が有機EL素子  $Z_1$  に供給されることとなる。

#### 【0072】

以上のことより、各画素回路  $2_0$  の駆動用トランジスタ  $T_{rd}$  の閾値電圧  $V_{t h 1}$  が製造ばらつきによって相違しても駆動電流  $I_{e1}$  はデータ電圧  $V_{data}$  のみで決定される。このことから、有機EL素子  $Z_1$  は、データ電圧  $V_{data}$  に基づいて精度良く輝度階調が制御されることとなる。その結果、表示品質の良い有機ELディスプレイ  $1_0$  を提供することができる。

30

#### 【0073】

前記実施形態の有機ELディスプレイ  $1_0$  及び画素回路  $2_0$  によれば、以下のような特徴を得ることができる。

#### 【0074】

(1) 上記の実施形態では、駆動用トランジスタ  $T_{rd}$ 、第1及び第2のスイッチング用トランジスタ  $T_{r1}, T_{r2}$ 、調整用トランジスタ  $T_{rc}$ 、カップリング用コンデンサ  $C_1$  及び保持用キャパシタ  $C_2$  で画素回路  $2_0$  を構成した。そして、駆動用トランジスタ  $T_{rd}$  には、同駆動用トランジスタ  $T_{rd}$  の閾値電圧  $V_{t h 1}$  を補償する補償電圧を生成する調整用トランジスタ  $T_{rc}$  の閾値電圧  $V_{t h 2}$  が前記駆動用トランジスタ  $T_{rd}$  のゲートに印加されるようにした。このようにすることによって、駆動用トランジスタ  $T_{rd}$  の閾値電圧  $V_{t h 1}$  を補償することができる。このことから、各画素回路  $2_0$  の駆動用トランジスタ  $T_{rd}$  の閾値電圧  $V_{t h 1}$  のばらつきを低減することができるので、前記データ線  $X_m$  を介してデータ線駆動回路  $1_4$  から供給されるデータ電圧  $V_{data}$  に対応した駆動電流  $I_{e1}$  を精度良く制御することができる。従って、有機EL素子  $Z_1$  は、データ電圧  $V_{data}$  に基づいて精度良く輝度階調が制御されることとなる。その結果、表示品質の良い有機ELディスプレイ  $1_0$  を提供することができる。

40

#### 【0075】

尚、上記の実施形態において、駆動用トランジスタ  $T_{rd}$ 、第1及び第2のスイッチング用トランジスタ  $T_{r1}, T_{r2}$ 、及び調整用トランジスタ  $T_{rc}$  はそれぞれ、p型トランジスタ、n型トランジスタ、n型トランジスタ及びp型トランジスタを用いたが、特に限定されず、適宜、トランジスタの導電型は選択することができる。例えば、駆動用トラン

50

ジスタ T<sub>r d</sub> 及び調整用トランジスタ T<sub>r c</sub> として n 型トランジスタを使用することも可能である。また、第 1 及び第 2 のスイッチング用トランジスタ T<sub>r 1</sub>, T<sub>r 2</sub> を共に n 型トランジスタとしてもよい。

また、第 1 及び第 2 のスイッチング用トランジスタ T<sub>r 1</sub>, T<sub>r 2</sub> として互いに導電型の異なるトランジスタを使用することができる。その場合、第 1 及び第 2 のスイッチング用トランジスタ T<sub>r 1</sub>, T<sub>r 2</sub> のゲートを共通の信号線、例えば、走査線に接続し、相補的に動作させるようにすれば、配線に要する面積を低減することも可能となる。

#### 【0076】

画素回路 20 を構成するトランジスタは、例えば、単結晶シリコン、多結晶シリコン、微結晶シリコン、あるいは、アモルファスシリコンのいずれかにより形成されていることが好ましい。10

#### (第 2 実施形態)

次に、第 1 実施形態で説明した電気光学装置としての有機 EL ディスプレイ 10 の電子機器の適用について図 5 及び図 6 に従って説明する。有機 EL ディスプレイ 10 は、モバイル型のパーソナルコンピュータ、携帯電話、デジタルカメラ等種々の電子機器に適用できる。

#### 【0077】

図 5 は、モバイル型パーソナルコンピュータの構成を示す斜視図を示す。図 5 において、パーソナルコンピュータ 50 は、キーボード 51 を備えた本体部 52 と、前記有機 EL ディスプレイ 10 を用いた表示ユニット 53 とを備えている。この場合においても、有機 EL ディスプレイ 10 を用いた表示ユニット 53 は前記実施形態と同様な効果を発揮する。この結果、表示品質の良い有機 EL ディスプレイ 10 を備えたモバイル型パーソナルコンピュータ 50 を提供することができる。20

#### 【0078】

図 6 は、携帯電話の構成を示す斜視図を示す。図 6 において、携帯電話 60 は、複数の操作ボタン 61、受話口 62、送話口 63、前記有機 EL ディスプレイ 10 を用いた表示ユニット 64 を備えている。この場合においても、有機 EL ディスプレイ 10 を用いた表示ユニット 64 は前記実施形態と同様な効果を発揮する。この結果、表示品質の良い有機 EL ディスプレイ 10 を備えた携帯電話 60 を提供することができる。

#### 【0079】

尚、発明の実施形態は、上記実施形態に限定されるものではなく、以下のように実施してもよい。30

#### 【0080】

前記実施形態では、単位回路として有機 EL 素子を備えた画素回路に具体化したが、有機 EL 素子以外の、例えば液晶素子、電気泳動素子、電子放出素子、無機 EL 素子、LED、FED 等の種々の電気光学素子を駆動する単位回路に具体化してもよい。RAM 等の記憶装置に具体化してもよい。

#### 【0081】

前記実施形態では、1 色からなる有機 EL 素子の画素回路を設けた有機 EL ディスプレイであったが、赤色、緑色及び青色の 3 色あるいはそれ以上の種類の色の光を発する有機 EL 素子に対して各色用の画素回路を設けた EL ディスプレイに応用しても良い。40

#### 【図面の簡単な説明】

【図 1】第 1 実施形態の有機 EL ディスプレイの回路構成を示すブロック回路図である。

【図 2】表示パネル部及びデータ線駆動回路の内部回路構成を示すブロック回路図である。40

【図 3】第 1 実施形態の画素回路の回路図である。

【図 4】第 1 実施形態の画素回路の動作を説明するためのタイミングチャートである。

【図 5】第 2 実施形態を説明するためのモバイル型パーソナルコンピュータの構成を示す斜視図である。

【図 6】第 2 実施形態を説明するための携帯電話の構成を示す斜視図である。50

## 【符号の説明】

- C 1 容量素子又は保持手段としてのカップリング用コンデンサ

L a 第1の電極

L b 第2の電極

T r d 第1のトランジスタとしての駆動用トランジスタ

T r c 第2のトランジスタとしての調整用トランジスタ

T r 1 第3のトランジスタとしての第1のスイッチング用トランジスタ

T r 2 第4のトランジスタとしての第2のスイッチング用トランジスタ

V d a t a データ信号としてのデータ電圧

V d d 電源電位としての駆動電圧

Y n 走査線

X m データ線

1 0 電気光学装置としての有機ELディスプレイ

2 0 単位回路又は電子回路としての画素回路

2 1 電子素子又は電流駆動素子としての有機EL素子

5 0 電子機器としてのモバイル型パーソナルコンピュータ

6 0 電子機器としての携帯電話

10

【図1】

【図2】

【 図 3 】

【 図 4 】

【図5】

【図6】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 1 D |

| G 0 9 G | 3/20  | 6 4 2 A |

| H 0 5 B | 33/14 | A       |

| H 0 1 L | 29/78 | 6 1 4   |

F ターム(参考) 5C080 AA06 AA07 AA10 AA13 BB05 CC03 DD05 EE29 FF01 FF07

FF11 HH09 JJ02 JJ03 JJ04 JJ06 KK01 KK07 KK43 KK47

5C094 AA04 AA23 AA43 AA53 AA55 BA03 BA29 CA19 DB01

5F110 AA30 BB02 GG02 GG12 GG13 GG14 GG15 NN73