(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5779162号

(P5779162)

(45) 発行日 平成27年9月16日(2015.9.16)

(24) 登録日 平成27年7月17日(2015.7.17)

(51) Int.Cl.

F 1

H02M 7/12 (2006.01)

H03D 1/18 (2006.01)H02M 7/12

H03D 1/18A

B

請求項の数 8 (全 28 頁)

(21) 出願番号 特願2012-218785 (P2012-218785)

(22) 出願日 平成24年9月28日 (2012.9.28)

(65) 公開番号 特開2014-73028 (P2014-73028A)

(43) 公開日 平成26年4月21日 (2014.4.21)

審査請求日 平成26年4月8日 (2014.4.8)

前置審査

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100111121

弁理士 原 拓実

(74) 代理人 100125667

弁理士 小林 幹雄

(74) 代理人 100138601

弁理士 山下 正成

(74) 代理人 100151323

弁理士 泉 剛司

(74) 代理人 100149629

弁理士 柏 周作

(74) 代理人 100200229

弁理士 矢作 徹夫

最終頁に続く

(54) 【発明の名称】整流回路とこれを用いた無線通信装置

(57) 【特許請求の範囲】

## 【請求項1】

電界効果トランジスタと、バイアス電圧発生回路とを有する整流回路であつて、前記電界効果トランジスタは、

制御端子と、

第1の電流入出力端子と、

前記第1の電流入出力端子に接続され、P型拡散層を有するソース領域と、

第2の電流入出力端子と、

前記第2の電源入出力端子に接続され、N型拡散層を有するドレイン領域とを備え、

前記バイアス電圧発生回路は、前記制御端子と前記第2の電流入出力端子との間に直流電圧を印加することを特徴とする整流回路。

10

## 【請求項2】

前記第1の電流入出力端子は、前記整流回路の正側の端子に接続され、前記第2の電流入出力端子は、前記整流回路の負側の端子に接続されることを特徴とする請求項1に記載の整流回路。

## 【請求項3】

前記第2の電流入出力端子にAC入力電圧が入力され、前記第1の電流入出力端子からDC電流を出力することを特徴とする請求項1または2に記載の整流回路。

## 【請求項4】

AC入力電圧が入力されるキャパシタと、

20

第1の電界効果トランジスタと、

第2の電界効果トランジスタと、

バイアス電圧発生回路とを有する整流回路であって、

前記第1の電界効果トランジスタは、

第1の制御端子と、

第1の電流入出力端子と、

前記第1の電流入出力端子に接続され、P型拡散層を有する第1のソース領域と、

第2の電流入出力端子と、

前記第2の電流入出力端子に接続され、N型拡散層を有する第1のドレイン領域を備え、前記第2の電流入出力端子が前記キャパシタに接続され、

前記第2の電界効果トランジスタは、

第2の制御端子と、

第3の電流入出力端子と、

前記第3の電流入出力端子に接続され、P型拡散層を有する第2のソース領域と、

第4の電流入出力端子と、

前記第4の電流入出力端子に接続され、N型拡散層を有する第2のドレイン領域を備え、前記第3の電流入出力端子が前記キャパシタに接続され、

前記バイアス電圧発生回路は、前記第1の制御端子と前記第2の電流入出力端子との間および前記第2の制御端子と前記第4の電流入出力端子との間に直流電圧を印加することを特徴とする整流回路。

#### 【請求項5】

差動信号が入力される第1および第2のキャパシタと、

第1の電界効果トランジスタと、

第2の電界効果トランジスタと、

第3の電界効果トランジスタと、

バイアス電圧発生回路とを有する整流回路であって、

前記第1の電界効果トランジスタは、

第1の制御端子と、

第1の電流入出力端子と、

前記第1の電流入出力端子に接続され、P型拡散層を有する第1のソース領域と、

第2の電流入出力端子と、

前記第2の電流入出力端子に接続され、N型拡散層を有する第1のドレイン領域とを備え、前記第2の電流入出力端子が前記第1のキャパシタに接続され、

前記第2の電界効果トランジスタは、

第2の制御端子と、

第3の電流入出力端子と、

前記第3の電流入出力端子に接続され、P型拡散層を有する第2のソース領域と、

第4の電流入出力端子と、

前記第4の電流入出力端子に接続され、N型拡散層を有する第2のドレイン領域とを備え、前記第3の電流入出力端子が前記第1のキャパシタに接続され、前記第4の電流入出力端子が前記第2のキャパシタに接続され、

前記第3の電界効果トランジスタは、

第3の制御端子と、

第5の電流入出力端子と、

前記第5の電流入出力端子に接続され、P型拡散層を有する第3のソース領域と、

第6の電流入出力端子と、

前記第6の電流入出力端子に接続され、N型拡散層を有する第3のドレイン領域とを備え、前記第5の電流入出力端子が前記第2のキャパシタに接続され、

前記バイアス電圧発生回路は、前記第1の制御端子と前記第2の電流入出力端子との間および前記第2の制御端子と前記第4の電流入出力端子との間、および前記第3の制御端

10

20

30

40

50

子と前記第6の電流入出力端子との間に直流電圧を印加することを特徴とする整流回路。

【請求項6】

前記バイアス電圧発生回路によって、前記制御端子と前記第2の電流入出力端子との間に印加される直流電圧の値は、可変であることを特徴とする請求項1乃至3のいずれか1項に記載の整流回路。

【請求項7】

前記バイアス電圧発生回路によって、前記第1の制御端子と前記第2の電流入出力端子との間及び前記第2の制御端子と前記第4の電流入出力端子との間に印加される直流電圧の値は、可変であることを特徴とする請求項4または請求項5に記載の整流回路。

【請求項8】

10

請求項1乃至7のいずれか1項に記載の整流回路と、

前記整流回路に信号を入力するアンテナと、

前記整流回路から出力された信号を増幅するベースバンド回路と、

前記ベースバンド回路から出力された信号をデジタルに変換するADCと、

前記ADCから出力された信号の判別を行い、規定の信号と一致した場合に制御信号を出力する信号処理部とを有することを特徴とする無線通信装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は整流回路とこれを用いた無線通信装置に関する。

20

【背景技術】

【0002】

無線信号を受信検波して信号を処理する無線装置に用いられる整流回路に、MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) を用いた整流回路がある。これは、MOSFETのゲート端子とソース端子を接続し、ドレイン端子を正側、ソース端子を負側として、数段直列に接続したものである。MOSFETの接続部分にキャパシタの一端を接続し、キャパシタの他端を信号入力端子に接続する。この信号入力端子にAC電圧信号が入力され、その包絡線信号を電流信号として正側から出力する。

【0003】

MOSFETは、閾値電圧が設定されており、ゲート・ソース間に印加される電圧がこの閾値電圧を超えたときにソース・ドレイン間に電流が流れ、閾値電圧以下であると電流が流れない。そこで、閾値電圧を超えない微弱なAC電圧信号が信号入力端子に入力された場合でも電流信号を出力するために、ゲート・ソース間にMOSFETの閾値電圧とほぼ等しい電圧を印加する。これによって、閾値電圧が見かけ上は0Vとなり、入力されるAC電圧信号がプラス側波形の場合には、見かけ上の閾値電圧を超え、マイナス側波形の場合には見かけ上の閾値電圧以下となるため、脈流電流が生成され、正側から出力される。

30

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006-34085号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、見かけ上の閾値電圧が0Vに近くなるようにゲート・ソース間に電圧を印加すると、AC電圧信号マイナス側波形の場合に、リーク電流として負側の電流が発生する。整流電流は、正負の電流の差によって生成するため、正負電流の差が少なくなると信号の検出ができなくなる。

【0006】

本発明は、微弱なAC電圧信号が入力された場合でも、信号検出が可能な整流回路と、

50

これを用いた無線通信装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明の実施形態による整流回路は、電界効果トランジスタと、バイアス電圧発生回路とを有する整流回路であって、前記電界効果トランジスタは、制御端子と、P型拡散層を電極とした第1の電流入出力端子と、N型拡散層を電極とした第2の電流入出力端子を備え、前記バイアス電圧発生回路は、前記制御端子と前記第2の電流入出力端子との間に直流電圧を印加することを特徴としている。

【図面の簡単な説明】

【0008】

10

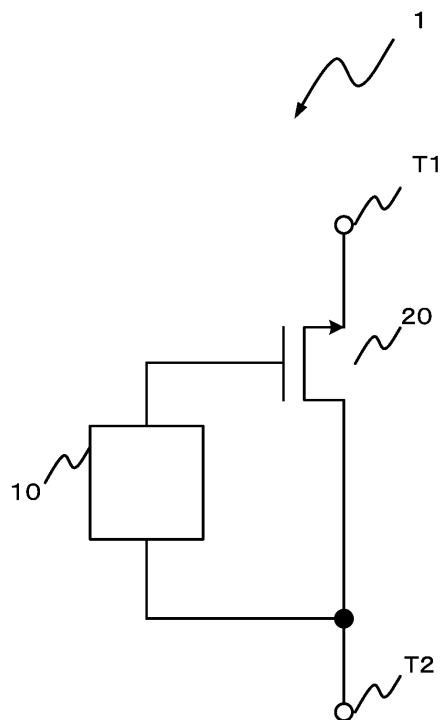

【図1】本発明の第1の実施形態に係る整流回路の回路図。

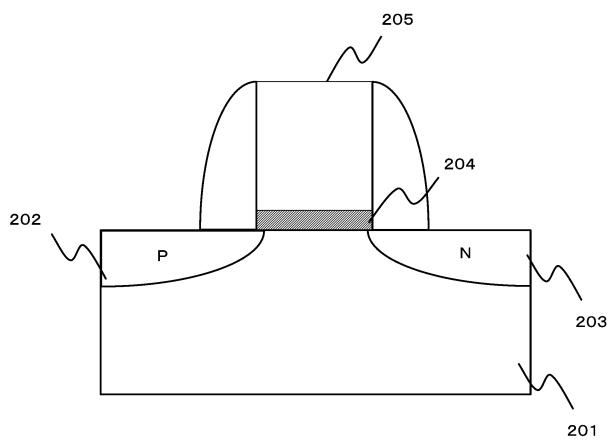

【図2】本発明の第1の実施形態に係る整流回路のトンネルFETの断面図。

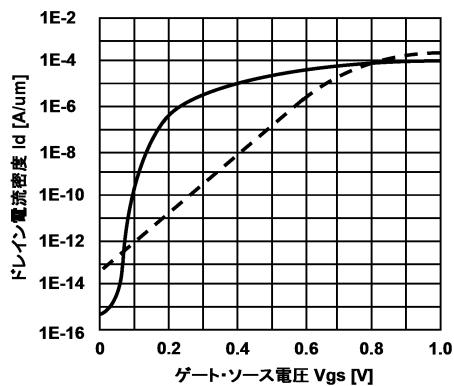

【図3】トンネルFETとMOSFETのゲート・ソース間電圧V<sub>gs</sub>に対するドレイン電流特性の一例を示す図。

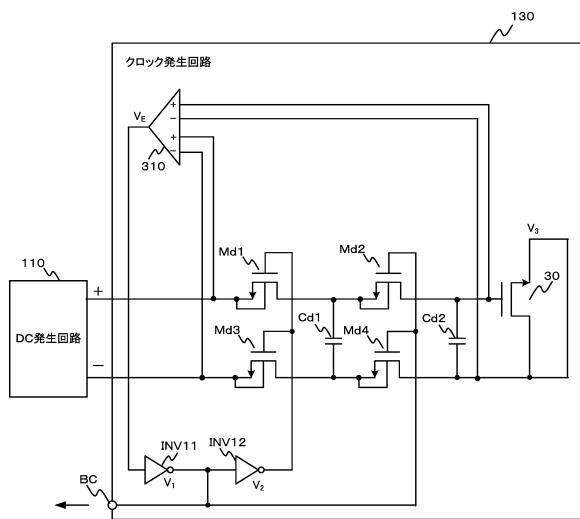

【図4】本発明の第1の実施形態に係る整流回路のバイアス電圧発生回路の構成例を示す回路図。

【図5】本発明の第1の実施形態に係る整流回路のクロック発生回路130を示す回路図である。

【図6】本発明の第1の実施形態に係る整流回路のクロック発生回路の動作を表わすタイミングチャート。

20

【図7】本発明の第1の実施形態に係る整流回路のDC発生回路の一例を示す回路図。

【図8】本発明の第1の実施形態に係る整流回路のDC発生回路の一例を示す回路図。

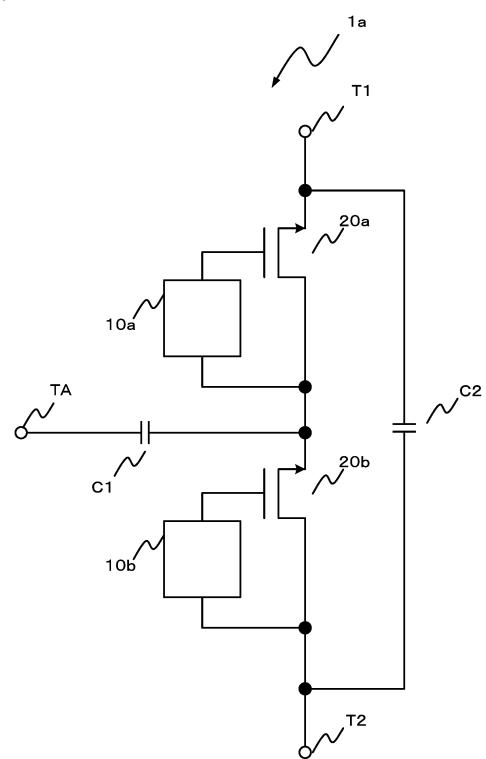

【図9】本発明の第2の実施形態に係る整流回路の回路図。

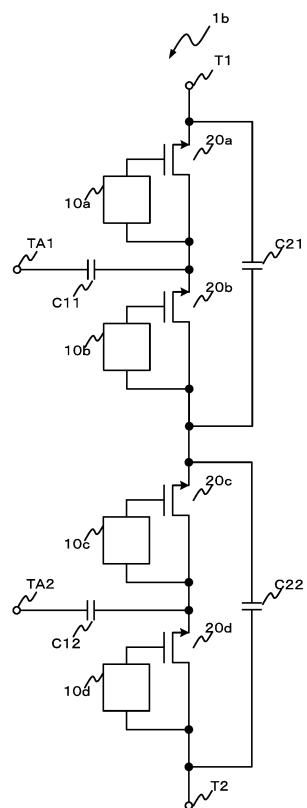

【図10】本発明の第2の実施形態に係る整流回路の回路図の変形例。

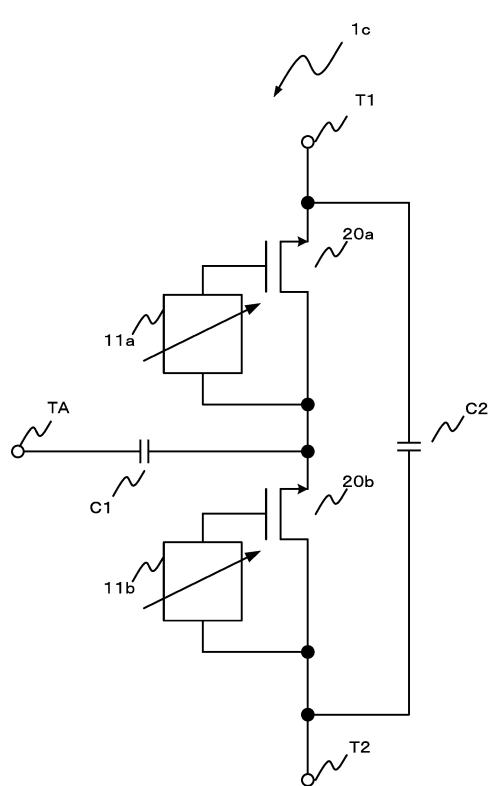

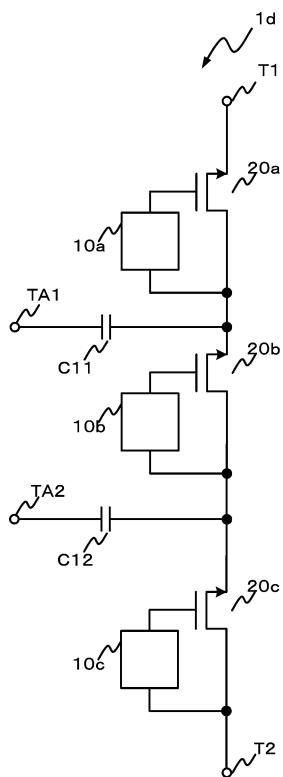

【図11】本発明の第3の実施形態に係る整流回路の回路図。

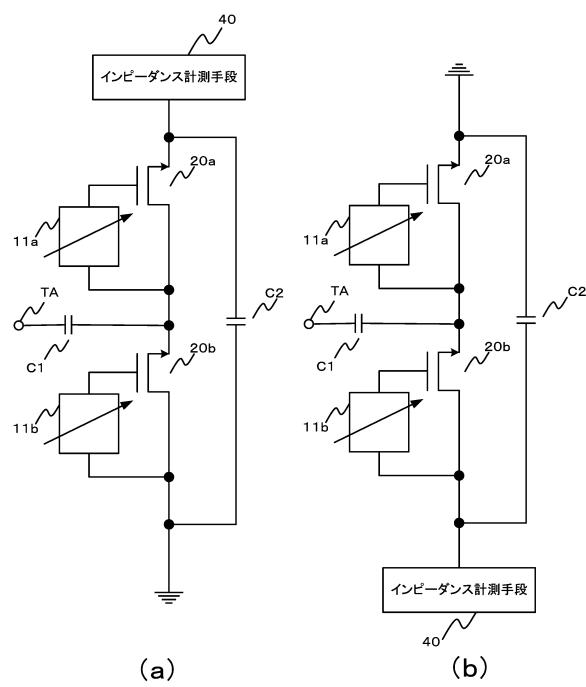

【図12】本発明の第3の実施形態に係る整流回路の回路図。

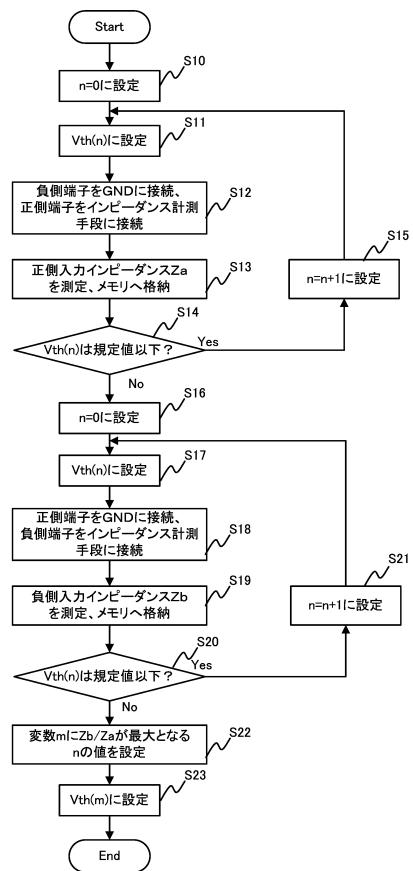

【図13】本発明の第3の実施形態に係る整流回路のバイアス電圧を調整する際のフローチャート。

【図14】本発明の第4の実施形態に係る整流回路の回路図。

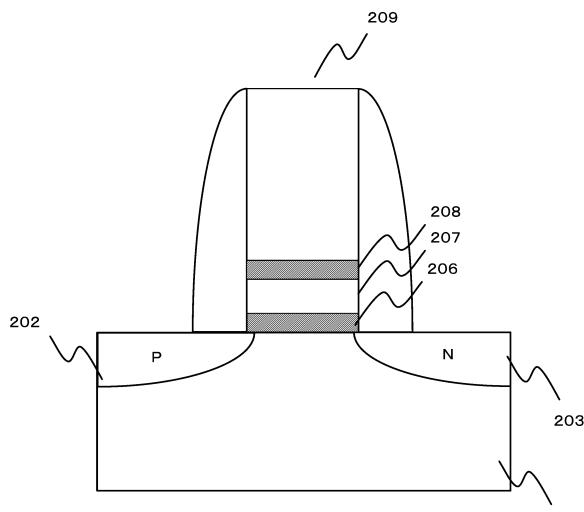

【図15】本発明の第5の実施形態に係る整流回路のトンネルFETの断面図。

30

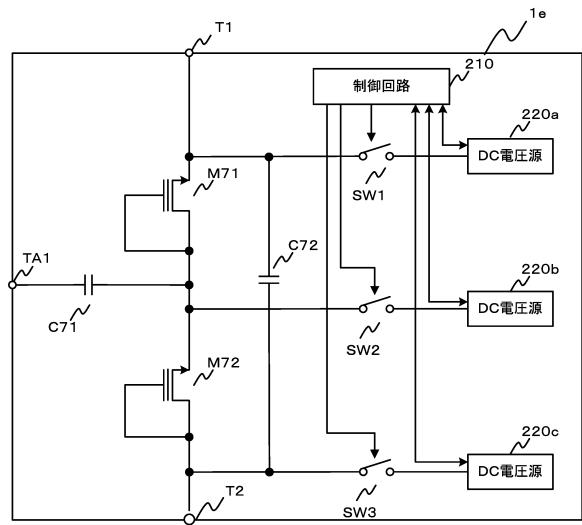

【図16】本発明の実施の形態5にかかる整流回路を示す回路図。

【図17】本発明の実施の形態5にかかる整流回路のDC電圧源の回路図。

【図18】本発明の実施の形態5にかかる整流回路の昇圧回路の一例を示す回路図。

【図19】本発明の実施の形態5にかかる整流回路のフローティングゲートの制御方法を示すフローチャート。

【図20】チャージ量検出工程を示すフローチャート。

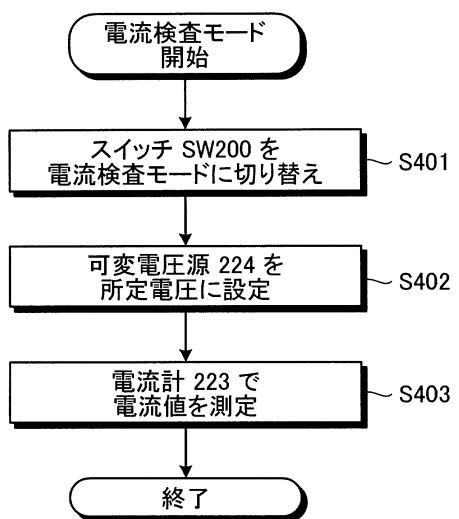

【図21】DC電圧源の電流検査モードの動作を示すフローチャート。

【図22】チャージ量設定工程を示すフローチャート。

【図23】DC電圧源の電圧設定モードの動作を示すフローチャート。

【図24】本発明の実施の形態6にかかる整流回路の回路図。

40

【図25】本発明の実施の形態7に整流回路を示す回路図。

【図26】本発明の実施の形態8に整流回路を示す回路図

【図27】本発明の実施の形態に係る無線受信装置を示すブロック図。

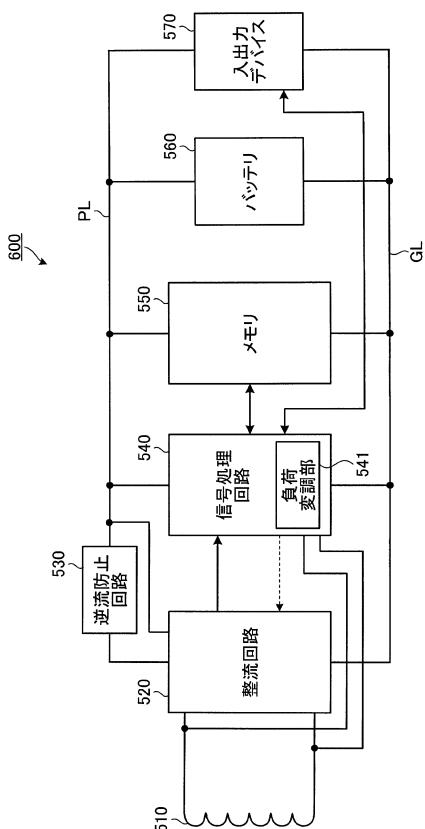

【図28】本発明の実施の形態に係るRFIDタグを示すブロック図。

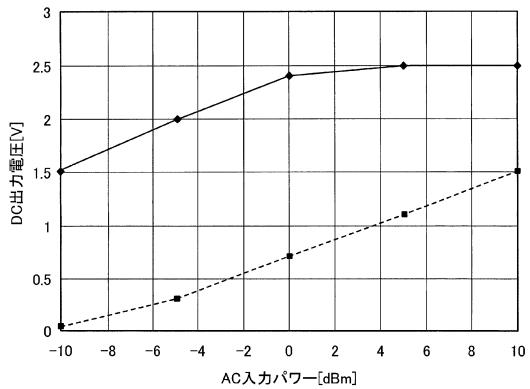

【図29】本発明の実施の形態に係るRFIDタグの整流特性（実線）と、従来のRFIDタグの整流特性（破線）を示したグラフ

【図30】本発明の実施の形態に係るRFIDタグに入出力デバイスを搭載した構成を示すブロック図。

【発明を実施するための形態】

【0009】

50

## (実施の形態 1)

以下、本発明の実施形態について図面を参照して説明する。図1は、本発明の第1の実施形態に係る整流回路の回路図である。整流回路1は、急峻なS値を有する電界効果トランジスタを有する。本実施形態では、急峻なS値を有する電界効果トランジスタとして、トンネル型電界効果トランジスタ(トンネルFET)を例に説明する。

## 【0010】

整流回路1は、バイアス電圧発生回路10とトンネルFET20を有する。トンネルFET20は、ソース電極が正側端子T1、ドレイン電極が負側端子T2に接続される。バイアス電圧発生回路10は、一端が負側端子T2およびトンネルFET20のドレイン電極に接続され、他端がトンネルFET20のゲート電極に接続される。

10

## 【0011】

バイアス発生回路10は、トンネルFET20のゲート・ドレイン間に、トンネルFET20が整流特性を示すのに必要な閾値電圧未満の電圧(以下、バイアス電圧と称する)を印加する。このバイアス電圧は、好ましくはトンネルFETの閾値電圧とほぼ等しい電圧を印加する。これによって、トンネルFETの閾値電圧が見かけ上は0Vとなり、負側端子T2から入力されるAC電圧信号がプラス側波形の場合には、見かけ上の閾値電圧を超えて、AC電圧信号がマイナス側波形の場合には見かけ上の閾値電圧以下となるため、半端整流された信号が正側端子T1から出力される。

## 【0012】

図2は、トンネルFET20の断面図である。トンネルFET20は、半導体基板201上に離間してソース領域202とドレイン領域203が形成されている。ソース領域とドレイン領域は伝導型が異なり、それぞれP型の拡散層とN型の拡散層である。ソース領域202とドレイン領域203の間の領域(チャネル)の上部には絶縁膜204が形成され、絶縁膜204の上部にはゲート電極が形成される。チャネルは、真性半導体を用いても良いし、P型やN型の半導体を用いても良い。トンネルFET20は、ゲート・ソース間に電圧が印加されると、トンネル電流が流れる。ソース・チャネル接合におけるBTBT(Band To Band Tunneling)が電流駆動能力を決定するため、駆動電流を向上させるには、ソース・チャネル接合において不純物濃度が高濃度かつ急峻な接合を形成して、トンネルバリアを薄膜化する。一方、オフリーク電流はドレイン・チャネル接合でのBTBTによって決定されるため、オフリーク電流を低減させるには、ドレイン・チャネル領域において不純物濃度が低濃度かつ緩やかな接合を形成してトンネルバリアを厚膜化する。

20

30

## 【0013】

図3にトンネルFETとMOSFETのゲート・ソース間電圧Vgsに対するドレイン電流特性の一例を示す。図中の実線と破線はそれぞれトンネルFETとMOSFETの特性を示す。MOSFETと比較してトンネルFETは、Vgsが閾値電圧以下の弱反転領域で急峻な電流/電圧特性を有する。つまり、トンネルFETは、MOSFETよりも、ゲート・ソース間の微弱な変動に対して大きくドレイン電流を変化させることができる。

## 【0014】

例えば、図1に示す整流回路のトンネルFET20をMOSFETとした場合、ゲート・ソース間電圧を0.4Vとして、負側端子T2に振幅0.1VのAC電圧信号を入力すると、入力波形がプラス側では電流が10倍となる。しかしながら、入力波形がマイナス側では1/10のリーク電流が発生する。これに対して、図1に示す回路では、ゲート・ソース間電圧を0.1Vとし、負側端子T2に振幅0.1VのAC電圧信号を入力すると、入力波形がプラス側では電流が1000倍以上となり、入力波形がマイナス側では1/1000のリーク電流が発生する。このように、トンネルFETを用いることで、整流回路に入力されるAC電圧信号がマイナス側波形の場合にリーク電流として発生する負側の電流を抑えて、正負電流の差を大きくし、高感度かつ高効率に整流することができる。

40

## 【0015】

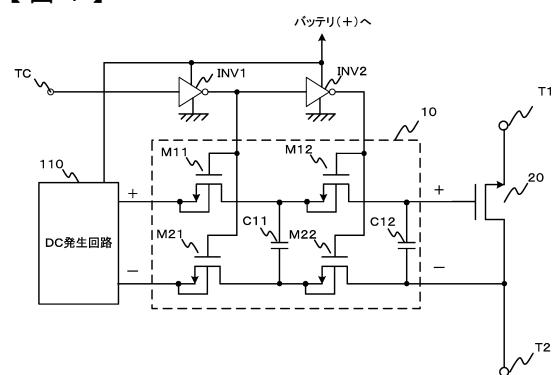

図4は、図1に示す整流回路1のバイアス電圧発生回路10の構成例を示す回路図であ

50

る。バイアス電圧発生回路 10 は、直列に接続された 2 つの NMOS トランジスタ M11 と M12 を備えている。これらの NMOS トランジスタは、それぞれトランジスタとして機能し、プラスのライン上に配置されている。同様に、バイアス電圧発生回路 10 は、マイナスのライン上に直列に接続された NMOS トランジスタ M21 と M22 を備える。M21 と M22 もトランジスタとして機能する。NMOS トランジスタ M11 、 M21 のゲート端子は互いに接続され、NMOS トランジスタ M12 、 M22 のゲート端子も互いに接続されている。NMOS トランジスタ M11 のドレイン端子と NMOS トランジスタ M12 のソース端子とを接続するラインと、NMOS トランジスタ M21 のドレイン端子と NMOS トランジスタ M22 のソース端子とを接続するラインとの間には、キャパシタ C11 が接続されている。さらに、NMOS トランジスタ M12 のドレイン端子と NMOS トランジスタ M22 のドレイン端子との間にはキャパシタ C12 が接続されている。

#### 【 0016 】

バイアス電圧発生回路 10 には、周辺回路として、DC 発生回路 110 とインバータ INV1 、 INV2 とが接続されている。DC 発生回路 110 は、本実施の形態にかかる整流回路が搭載される装置の主電源から上記ダイオードバイアス電圧に相当する直流電圧を生成する。DC 発生回路 110 の具体例については後述する。DC 発生回路 110 によって生成された直流電圧は、バイアス電圧発生回路 10 のプラスラインとマイナスラインとの間に印加される。

#### 【 0017 】

インバータ INV1 の入力端子は、クロック入力端子 TC に接続されており、一定の周波数のクロック信号が入力される。このクロック信号は、例えば、後述するクロック発生回路によって生成される。インバータ INV1 の出力端子は、NMOS トランジスタ M11 および M21 の各ゲート端子に接続され、インバータ INV2 の入力端子にも接続されている。インバータ INV2 の出力端子は、NMOS トランジスタ M12 および M22 の各ゲート端子に接続されている。

#### 【 0018 】

クロック入力端子 TC から入力されたクロック信号が、論理レベル “ L ” である場合、インバータ INV1 は論理レベル “ H ” を出力し、インバータ INV2 は論理レベル “ L ” を出力する。従って、NMOS トランジスタ M11 および M21 は ON となり、キャパシタ C11 は、DC 発生回路 110 から供給される直流電圧によって充電される。また、NMOS トランジスタ M12 および M22 は OFF となり、キャパシタ C12 にはどの直流電圧も印加されない。

#### 【 0019 】

一方、クロック入力端子 TC から入力されたクロック信号が、論理レベル “ H ” である場合、インバータ INV1 は論理レベル “ L ” を出力し、インバータ INV2 は論理レベル “ H ” を出力する。従って、NMOS トランジスタ M11 および M21 は OFF となり、NMOS トランジスタ M12 および M22 は ON となるので、キャパシタ C11 に充電された電荷は、キャパシタ C12 に供給される。キャパシタ C12 の両端は、バイアス電圧発生回路 10 の出力端子に接続されているため、このキャパシタ C12 の両端の電圧が、ダイオードバイアス電圧として、ダイオード接続されたトンネル FET20 のゲート端子とドレイン端子との間に印加される。

#### 【 0020 】

最終的に、キャパシタ C12 の両端の電圧がトンネル FET20 のダイオードバイアス電圧となればよく、DC 発生回路 110 によって供給される直流電圧がダイオードバイアス電圧と同じである必要はない。例えば、NMOS トランジスタ M11 、 M12 、 M21 、 M22 のスイッチング動作を PWM ( Pulse Width Modulation : パルス幅変調 ) 制御によって行なうことで、キャパシタ C12 の電圧を任意の値に固定することもできる。この場合、DC 発生回路 110 を排除し、プラスライン L1 とマイナスライン L2 との間に主電源を接続してもよい。

10

20

30

40

50

## 【0021】

なお、バイアス電圧発生回路10を構成するトランスマジックゲートとしてNMOSトランジスタを用いたが、PMOSトランジスタを用いても良い。また、図4において、インバータINV2を排除し、NMOSトランジスタM12とM22をPMOSトランジスタに変更しても良い。

## 【0022】

図5は、クロック入力端子TCに入力されるクロック信号を生成するクロック発生回路130を示す回路図である。クロック発生回路130は、ダミー整流部とダミースイッチング部と誤差増幅部310とから構成される。ダミー整流部は、トンネルFET30で構成される。トンネルFET30は、ソース端子とドレイン端子はともにマイナスラインに接続されていると共に、所定の電位V<sub>3</sub>に吊られている。また、トンネルFET30のゲート端子とドレイン端子との間に、キャパシタCd2が接続されている。

10

## 【0023】

ダミースイッチング部は、NMOSトランジスタMd1～Md4と、キャパシタCd1,Cd2と、インバータINV11,INV12とで構成される。NMOSトランジスタMd1～Md4およびキャパシタCd1,Cd2は、バイアス電圧発生回路10と同じ構成である。

## 【0024】

具体的には、NMOSトランジスタMd1,Md2は、直列に接続され、それぞれトランスマジックゲートとして機能し、プラスライン上に配置されている。NMOSトランジスタMd3,Md4もまた、直列に接続され、それぞれトランスマジックゲートとして機能し、マイナスライン上に配置されている。NMOSトランジスタMd1のゲート端子とNMOSトランジスタMd3のゲート端子はともに、インバータINV12の出力端子に接続される。インバータINV12の入力端子は、インバータINV11の出力端子に接続されている。NMOSトランジスタMd2のゲート端子とNMOSトランジスタMd4のゲート端子はともに、インバータINV11の出力端子に接続されている。NMOSトランジスタMd1のドレイン端子とNMOSトランジスタMd2のソース端子とを接続するラインと、NMOSトランジスタMd3のドレイン端子とNMOSトランジスタMd4のソース端子とを接続するラインとの間には、キャパシタCd1が接続されている。さらに、NMOSトランジスタMd2のドレイン端子とNMOSトランジスタMd4のドレイン端子との間にはキャパシタCd2が接続されている。

20

## 【0025】

NMOSトランジスタMd1のソース端子とNMOSトランジスタMd3のソース端子は、バイアス電圧発生回路10と同様に、それぞれDC発生回路110のプラス端子とマイナス端子に接続されている。誤差増幅部310は、キャパシタCd2の両端の電圧と参照電圧との差電圧を適当な利得で増幅したベースクロック電圧V<sub>E</sub>を出力する。この参照電圧は、DC発生回路110から供給される直流電圧V<sub>T</sub>から所定の電圧V<sub>x</sub>（例えば50mV）だけ低い電圧V<sub>T</sub>-V<sub>x</sub>として表される。換言すれば、誤差増幅部310は、キャパシタCd2の電圧を監視し、その監視結果に基づいてベースクロック電圧V<sub>E</sub>を生成する。

30

## 【0026】

誤差増幅部310の出力端子は、インバータINV11の入力端子に接続されている。インバータINV11の出力端子はまた、クロック発生回路130の出力端子BCに接続されている。この出力端子BCがクロック入力端子TCに接続される。これにより、誤差増幅部310から出力されたベースクロック電圧V<sub>E</sub>が所定レベル以上になった際に、インバータINV11から論理レベル“L”的信号が出力され、ベースクロック電圧V<sub>E</sub>が所定レベル未満になった際に、インバータINV11から論理レベル“H”的信号が出力される。

40

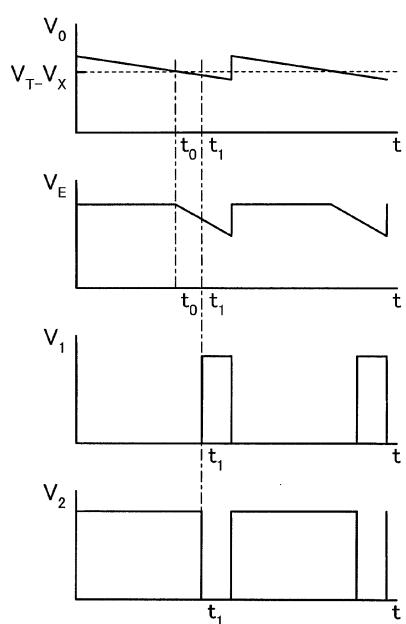

## 【0027】

図6は、キャパシタCd2の一端の電位V<sub>0</sub>と、誤差増幅部310から出力される差電

50

圧  $V_E$  と、インバータ IN V 1 1 の出力電位  $V_1$  と、インバータ IN V 1 2 出力電位  $V_2$  との各タイミングチャートを示す図である。

【0028】

電位  $V_0$  が参照電圧  $V_T - V_x$  よりも大きい期間（時間  $t_0$  まで）においては、誤差増幅部 310 は所定値に飽和した正の差電圧  $V_E$  を出力する（第1フェーズ）。この正の差電圧  $V_E$  は、インバータ IN V 1 1 にとって論理レベル “H” の入力信号である。よって、その期間においては、インバータ IN V 1 1 の出力電位  $V_1$  は論理レベル “L” を示し、インバータ IN V 1 2 の出力電位  $V_2$  は論理レベル “H” を示す。これにより、NMOSトランジスタ Md 1 および Md 3 が ON となり、DC発生回路 110 の直流電圧  $V_T$  がキャパシタ Cd 1 に印加される。

10

【0029】

キャパシタ Cd 2 はトンネル FET 30 のリーク電流によって放電されるため、その電位  $V_0$  は徐々に低下し、ついには参照電圧  $V_T - V_x$  よりも小さくなる（第2フェーズ）。すなわち、誤差増幅部 310 から出力される差電圧  $V_E$  は、正に飽和した値から徐々に低下し、最終的にインバータ IN V 1 1 にとって論理レベル “L” の入力信号となる（時間  $t_1$ ：第3フェーズ）。これにより、インバータ IN V 1 1 の出力電位  $V_1$  は論理レベル “H” を示し、インバータ IN V 1 2 の出力電位  $V_2$  は論理レベル “L” を示す。これにより、NMOSトランジスタ Md 2 および Md 4 が ON となり、キャパシタ Cd 1 の電荷がキャパシタ Cd 2 に与えられる。すなわち、キャパシタ Cd 2 の電位  $V_0$  は、参照電圧  $V_T - V_x$  よりも大きい電位  $V_T$  にほぼ一致し、上記した第1フェーズの状態となる。以降、上記第1～第3フェーズが繰り返される。

20

【0030】

この繰り返しフェーズにおいて、出力電位  $V_1$  は、定期的に発生するパルスとなっている。この出力電位  $V_1$  がクロック信号としてクロック入力端子 TC に入力される。特に、このクロック信号は、上述したようにクロック発生回路 130 がバイアス電圧発生回路 10 およびその周辺回路を模擬していることから、バイアス電圧発生回路 10 内のキャパシタ C 1 1、C 1 2 に無駄なく充電することができる最適なタイミングを示す。換言すれば、これにより、トンネル FET 20 が常に一定値以上の電圧でバイアスされる。

【0031】

なお、クロック発生回路 130 に使用する MOSトランジスタとして、PMOSトランジスタを用いても良い。

30

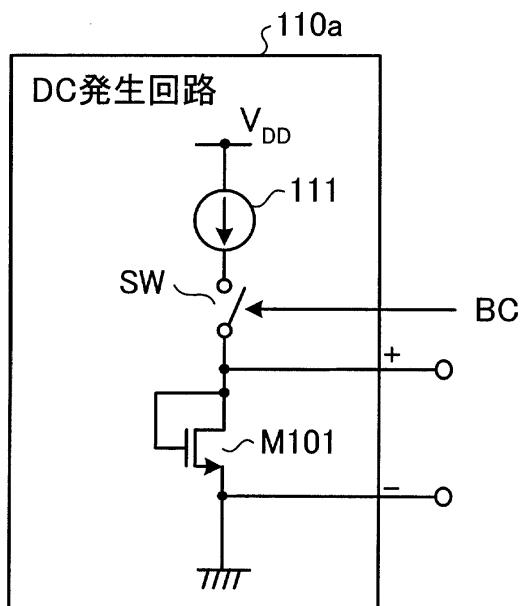

【0032】

バイアス電圧発生回路 10 およびクロック発生回路 130 はともに、DC発生回路 110 から供給される一定の直流電圧を利用している。ところが、この直流電圧は、DC発生回路 110 を構成する電子素子の製造ばらつきなどによって所望の値を示さない可能性がある。しかしながら、本実施の形態にかかるDC発生回路 110 は、以下のような構成を有することで、そのような製造ばらつきに依存しない直流電圧を生成することができる。

【0033】

図 7 は、DC発生回路 110 の一例を示す回路図である。図 7 に示す DC 発生回路 110 a は、ゲート端子とドレイン端子とが接続されたトンネル FET M101 と、電源電圧  $V_{DD}$  から定電流を生成する定電流源 111 とを備える。定電流源 111 の出力端子とトンネル FET M101 のドレイン端子とは、スイッチ SW を介して接続されている。トンネル FET M101 のソース端子は接地されており、トンネル FET M101 のゲート - ソース間電圧がこの DC 発生回路 110 a が output する直流電圧  $V_T$  に相当する。

40

【0034】

スイッチ SW が ON となっている場合、定電流源 111 からある一定の電流がトンネル FET M101 へ供給され、トンネル FET M101 はこの電流値に応じてゲート - ソース間に電圧を発生する。定電流源 111 から供給される電流が非常に微小な場合、例えば  $1 \mu A$  以下の場合、トンネル FET M101 は、ON と OFF との境の状態となっている。すなわち、トンネル FET M101 のゲート - ソース間電圧は閾値電圧と同等

50

な電圧を示す。これは、一般に、MOSトランジスタの特性が  $I_D = (V_{GS} - V_{th})^2$  と表され、電流  $I_D$  を小さくすると、ゲート - ソース間電圧  $V_{GS}$  はほぼ閾値電圧  $V_{th}$  となるという理論に基いている。よって、この電圧を、バイアス電圧発生回路 10 のダイオードバイアス電圧として利用することができる。

#### 【0035】

DC発生回路 110a は、スイッチ SW によって間欠的に動作される。DC発生回路 110a から直流電圧を出力する必要の無い時間帯は、スイッチ SW を OFF として電流の消費を少なくする。このスイッチ SW の ON / OFF 制御のために、上記したクロック発生回路 130 から出力されるクロック信号を利用することができる。例えば、クロック発生回路 130 の出力端子 BC にスイッチ SW の制御端子を接続し、且つスイッチ SW が論理レベル “H” の入力に対して ON となる場合に、バイアス電圧発生回路 10 およびクロック発生回路 130 が一定の直流電圧  $V_T$  を要求するタイミングに合わせて、DC発生回路 110a はその直流電圧  $V_T$  を出力することができる。

10

#### 【0036】

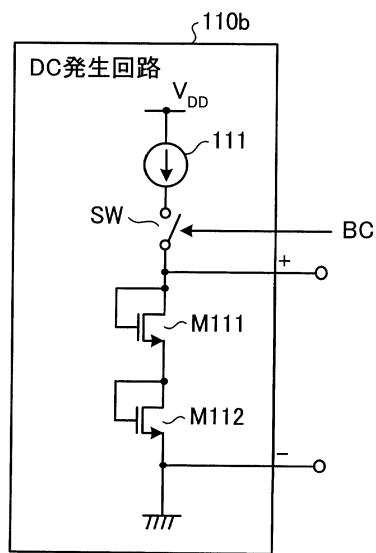

なお、スイッチ SW は、そこに入力されるクロック信号が論理レベル “H” の間中、常に ON となっている必要は必ずしも無い。クロック信号が論理レベル “H” を示す期間中のある期間のみスイッチ SW が ON となってもよい。

#### 【0037】

図 8 は、DC発生回路 110 の他の例を示す回路図である。図 8 に示す DC 発生回路 110b は、ゲート端子とドレイン端子とが接続された 2 つのトンネル FET M111 および M112 と、定電流を生成する定電流源 111 とを備えている。トンネル FET M111 および M112 は縦続接続されている。また、定電流源 111 の出力端子とトンネル FET M111 のドレイン端子とは、スイッチ SW を介して接続されている。トンネル FET M112 のゲート - ソース間電圧とトンネル FET M111 のゲート - ソース間電圧との和が、この DC 発生回路 110b が output する直流電圧  $V_T$  に相当する。

20

#### 【0038】

DC 発生回路 110b では、トンネル FET M111 および M112 の各閾値電圧は、整流回路 1 のトンネル FET 20 やクロック発生回路 130 のトンネル FET 30 の各閾値電圧よりも小さく、上記したゲート - ソース間電圧の和が直流電圧  $V_T$  と一致するような値である。このように、閾値電圧が小さいトンネル FET を用いた電圧源であっても、製造ばらつきに影響されない DC 発生回路 110 として利用することができる。

30

#### 【0039】

以上のように形成された DC 発生回路 110 は、整流回路 1 で用いるトンネル FET 20 と同一のチップ内に集積化することが望ましい。一般にトンネル FET の閾値電圧のばらつきはロット間、ウェハ間では  $+/-100\text{mV}$  程度あり、異なるチップで DC 発生回路 110 と整流回路 1 を形成すると、DC 発生回路 110 で発生する閾値電圧と整流回路 1 内のトンネル FET 20 の閾値電圧とでは  $100\text{mV}$  ずれる可能性がある。これに対して、同一チップ内でのトンネル FET の閾値電圧のばらつきは  $+/-10\text{mV}$  程度であり、DC 発生回路 110 で発生する閾値電圧と整流回路 1 のトンネル FET 20 の閾値電圧との差はほとんど無くなる。

40

#### 【0040】

以上に説明したように、実施の形態 1 にかかる整流回路によれば、バイアス回路によって、トンネル FET 20 のゲートとドレインとの間に、このトンネル FET 20 が整流特性を発現するのに要する閾値電圧未満であって好ましくはその閾値電圧近傍の定電圧を印加することができるので、閾値電圧未満の実効値を有する交流信号をも整流することができる。

#### 【0041】

##### (実施の形態 2)

図 9 は、本発明の第 2 の実施形態に係る整流回路の回路図である。整流回路 1a は、急

50

峻な S 値を有する電界効果トランジスタ（例えばトンネル F E T ）を用いて構成される。本実施形態では、整流回路 1 a は、バイアス電圧発生回路 1 0 a、1 0 b とトンネル F E T 2 0 a、2 0 b を有するとして説明する。バイアス電圧発生回路 1 0 a、1 0 b やトンネル F E T 2 0 a、2 0 b は、第 1 の実施形態にて説明したバイアス電圧発生回路 1 0 やトンネル F E T 2 0 と同様の構成である。

【 0 0 4 2 】

トンネル F E T 2 0 a のソース電極は、正側端子 T 1 に接続される。トンネル F E T 2 0 b のドレイン電極は、負側端子 T 2 に接続される。トンネル F E T 2 0 a のドレイン電極とトンネル F E T 2 0 b のソース電極は互いに接続されており、その接続ラインにキャパシタ C 1 の一端が接続される。キャパシタ C 1 の他端は、信号入力端子 T A に接続される。キャパシタ C 1 は、結合容量として機能する。本実施の形態にかかる整流回路を R F I D タグにおいて使用する場合には、キャパシタ C 1 は、ループアンテナに接続され、直列共振キャパシタとしても機能する。

【 0 0 4 3 】

トンネル F E T 2 0 a のゲート電極は、バイアス電圧発生回路 1 0 a を介してドレイン電極に接続されており、トンネル F E T 2 0 b のゲート電極は、バイアス電圧発生回路 1 0 b を介してドレイン電極に接続されている。バイアス電圧発生回路 1 0 a、1 0 b は、トンネル F E T 2 0 a、2 0 b のゲート・ドレイン間にバイアス電圧を印加する。

【 0 0 4 4 】

トンネル F E T 2 0 a のソース電極とトンネル F E T 2 0 b のドレイン電極との間には、キャパシタ C 2 が接続される。トンネル F E T 2 0 a、2 0 b のそれぞれによって半波整流された信号は、キャパシタ C 2 によって平滑される。これにより、信号入力端子 T A から信号を入力して、正側端子 T 1 と負側端子 T 2 とから直流電圧を取りだすことができる。

【 0 0 4 5 】

このようにトンネル F E T 2 0 a、2 0 b を直列に接続して全波整流を行うと、第 1 の実施形態の整流回路と比較して、効率や感度を向上させることができる。なお、図 1 0 に示すように、整流回路 1 a の正側端子 T 1 や負側端子 T 2 にさらに整流回路 1 a と同様な回路を接続しても良い。図 1 0 に示す整流回路 1 b でも、整流回路 1 a と同様の効果を得ることができる。さらに、図 1 0 では、整流回路 1 a を 2 つ縦積みした場合を示したが、3 つ以上縦積みした構成を取ることもできる。

【 0 0 4 6 】

（実施の形態 3 ）

図 1 1 は、本発明の第 3 の実施形態に係る整流回路の回路図である。整流回路 1 c では、可変バイアス電圧発生回路 1 1 a、1 1 b を用いる。その他の構成は、第 2 の実施形態にて説明した整流回路 1 b と同様であるため、説明を省略する。

【 0 0 4 7 】

可変バイアス電圧発生回路 1 1 a、1 1 b は、トンネル F E T の閾電圧のばらつきや温度特性等による変動に応じて、電流源 1 1 1 を調整することによってバイアス電圧を調整することができる。また、任意のバイアス電位を供給できることから、信号検出の感度を適応的に調整することができる。具体的には、微弱な信号が入力された場合でも高感度に信号検出ができるよう要求される場合には、バイアス電圧を適切な電圧とするのに対して、低感度な信号検出が要求される場合には、バイアス電圧を高感度時よりも低く設定することができる。

【 0 0 4 8 】

可変バイアス電圧発生回路 1 1 a、1 1 b のバイアス電圧をトンネル F E T の閾電圧に応じて調整する場合には、図 1 2 に示すように、インピーダンス計測手段 4 0 を接続して、正側と負側のインピーダンスを計測してバイアス電圧を調整する。インピーダンス計測手段 4 0 は、例えばカレントミラーによる電流源と、そのカレントミラー出力部の電位をモニタする A D 変換器等で構成することができる。

10

20

30

40

50

## 【0049】

図12(a)は、整流回路1cのリーク電流を測定するときの接続である。整流回路1cの正側端子にインピーダンス計測手段40を接続し、負側端子は接地する。図12(b)は、整流回路1cの整流電流を測定するときの接続である。整流回路1cの負側端子にインピーダンス計測手段40を接続し、正側端子は接地する。整流回路1cは、図示しない制御回路の制御に従って、整流回路1cのリーク電流と整流電流を測定し、バイアス電圧を調整することができる。

## 【0050】

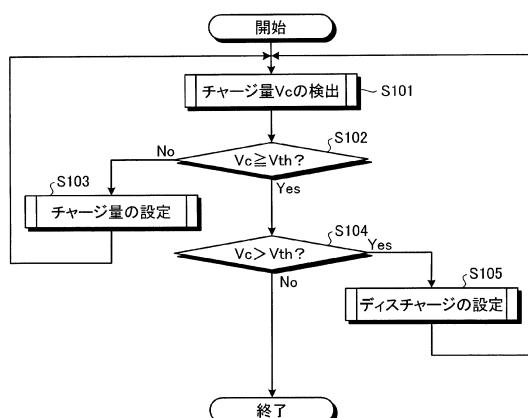

図13は、高感度な信号検出が要求される場合に、可変バイアス電圧発生回路11a、11bのバイアス電圧を適切に調整する際の手順の一例を示すフローチャートである。なお、予めメモリにバイアス電圧の設定値が複数( $Vth(0) \sim Vth(n-1)$ )のn個)記憶されているものとして説明する。 $Vth(0) \sim Vth(n-1)$ は、電圧値が小さい順に0~(n-1)の番号が割り振られている。

10

## 【0051】

まず、変数nを0に設定し(S10)、変数nの表す $Vth(n)$ すなわち $Vth(0)$ を可変バイアス電圧発生回路11a、11bのバイアス電圧として設定する(ステップS11)。そして、図12(a)のように、整流回路1cの負側端子を接地し、正側端子をインピーダンス計測手段40に接続する(ステップS12)。そして、バイアス電圧 $Vth(n)$ における正側の入力インピーダンス $Za$ を測定し、入力インピーダンス $Za$ をメモリに格納する(ステップS13)。そして、 $Vth(n)$ が予め定めた規定電圧値以下であれば(ステップS14のYes)、変数nをインクリメントし(ステップS15)、ステップS11~S14の処理を繰り返す。ステップS14で、 $Vth(n)$ が予め定めた規定電圧値を超える(ステップS14のNo)、変数nを再度0に設定し(ステップS16)、変数nの表す $Vth(n)$ すなわち $Vth(0)$ を可変バイアス電圧発生回路11a、11bのバイアス電圧として設定する(ステップS17)。そして、図12(b)のように、整流回路1cの正側端子を接地し、負側端子をインピーダンス計測手段40に接続する(ステップS18)。そして、バイアス電圧 $Vth(n)$ における負側の入力インピーダンス $Zb$ を測定し、入力インピーダンス $Zb$ をメモリに格納する(ステップS19)。そして、 $Vth(n)$ が予め定めた規定電圧値以下であれば(ステップS20のYes)、変数nをインクリメントし(ステップS21)、ステップS17~S20の処理を繰り返す。ステップS20で、 $Vth(n)$ が予め定めた規定電圧値を超える(ステップS20のNo)、変数n毎に記憶された正側と負側の入力インピーダンス $Za$ 、 $Zb$ を読み出し、n毎に $Zb/Za$ を算出する。そして、 $Zb/Za$ の値が最大となるnの値を変数mに設定する(ステップS22)。そして、この変数mの表わす設定値 $Vth(m)$ を可変バイアス電圧発生回路11a、11bのバイアス電圧として設定する(ステップS23)。これによって整流電流が大きく、リーク電流が小さくなるように、可変バイアス電圧発生回路11a、11bのバイアス電圧を設定することができる。

20

## 【0052】

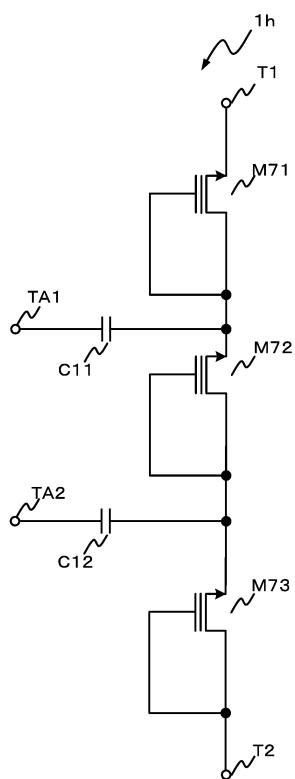

## (実施の形態4)

図14は、本発明の第4の実施形態に係る整流回路の回路図である。本実施形態のトンネルFET20a、20b、20cやバイアス電圧発生回路10a、10b、10cは、第1の実施形態にて説明したものと同様である。トンネルFET20aのソース電極が正側端子T1に接続され、トンネルFET20aのドレイン電極にトンネルFET20bのソース電極が接続され、トンネルFET20bのドレイン電極にトンネルFET20cのソース電極が接続され、トンネルFET20cのドレイン電極が負側端子T2に接続される。トンネルFET20a、20b、20cのゲート電極はそれぞれバイアス電圧発生回路10a、10b、10cを介してドレイン電極と接続される。入力端子TA1、TA2には、差動のAC信号が入力される。入力された差動信号は、キャパシタC11、C12を介して、トンネルFET20b、20cのソース電極にそれぞれ入力される。このようにトンネルFET20a、20b、20cを直列に接続し、差動信号を入力端子TA1、

30

40

50

T A 2 に入力することにより、第 1 の実施形態の整流回路と比較して、振幅が倍の信号が入力されるため、整流効率や感度を向上させることができる。なお、本実施形態の整流回路においても、第 2 の実施形態と同様に整流回路 1 d を複数縦積みした構成とすることもできる。すなわち、図 1 4 に示す整流回路 1 d の正側端子 T 1 または負側端子 T 2 に整流回路 1 d と同様の回路を接続しても良い。

【 0 0 5 3 】

( 実施の形態 5 )

実施の形態 5 にかかる整流回路は、整流素子として、ダイオード接続されたフローティングゲートトンネル型電界効果トランジスタを使用し、そのフローティングゲートに、このフローティングゲートトンネル型電界効果トランジスタが整流特性を発現するのに要する閾値電圧未満であって好ましくはその閾値電圧近傍の定電圧がチャージされていることを特徴としている。

【 0 0 5 4 】

図 1 5 は、フローティングゲートトンネル型電界効果トランジスタの断面図である。フローティングゲートトンネル型電界効果トランジスタは、半導体基板 2 0 1 上に離間してソース領域 2 0 2 とドレイン領域 2 0 3 が形成されている。ソース領域 2 0 2 とドレイン領域 2 0 3 は伝導型が異なり、それぞれ P 型の拡散層と N 型の拡散層である。ソース領域 2 0 2 とドレイン領域 2 0 3 の間の領域（チャネル）の上部には第 1 の絶縁膜 2 0 6 が形成され、第 1 の絶縁膜 2 0 6 の上部にフローティングゲート 2 0 7 が形成され、フローティングゲート 2 0 7 の上部に第 2 の絶縁膜 2 0 8 が形成され、第 2 の絶縁膜 2 0 8 の上部にコントロールゲート 2 0 9 が形成される。チャネルは、真性半導体を用いても良いし、P 型や N 型の半導体を用いても良い。

【 0 0 5 5 】

図 1 6 は、実施の形態 5 にかかる整流回路を示す回路図である。図 1 6 において、フローティングゲートトンネル型電界効果トランジスタ M 7 1 は、制御ゲート端子とドレイン端子とが接続され、ソース端子が正側端子 T 1 に接続されている。入力端子 T A から入力される入力信号の正負によって、ゲート・ソース間のスイッチをオン／オフさせるためにゲート端子とドレイン端子とが接続される。

【 0 0 5 6 】

フローティングゲートトンネル型電界効果トランジスタ M 7 1 のフローティングゲートには、フローティングゲートトンネル型電界効果トランジスタ M 7 1 が整流特性を示すのに必要な電圧（ダイオードバイアス電圧）がチャージされている。ここでは、このダイオードバイアス電圧は、フローティングゲートトンネル型電界効果トランジスタ M 7 1 の閾値電圧と一致しているものとする。これにより、フローティングゲートトンネル型電界効果トランジスタ M 7 1 の閾値電圧を等価的にゼロとすることができます、閾値電圧以下の実効値を有する交流信号を含めたすべての交流信号を整流することができる。

【 0 0 5 7 】

同様に、フローティングゲートトンネル型電界効果トランジスタ M 7 2 は、制御ゲート端子とドレイン端子とが接続され、ドレイン端子がマイナス端子 T 2 に接続されている。また、フローティングゲートトンネル型電界効果トランジスタ M 7 2 のフローティングゲートには、ダイオードバイアス電圧がチャージされている。このフローティングゲートトンネル型電界効果トランジスタ M 7 2 もまた、フローティングゲートトンネル型電界効果トランジスタ M 7 1 と同様に機能な整流特性を有する。

【 0 0 5 8 】

フローティングゲートトンネル型電界効果トランジスタ M 7 1 のドレイン端子とフローティングゲートトンネル型電界効果トランジスタ M 7 2 のソース端子とは互いに接続されており、その接続ラインに、キャパシタ C 7 1 の一端が接続されている。キャパシタ C 7 1 の他端は、信号入力端子 T A に接続されている。このキャパシタ C 7 1 は、結合容量として機能する。本実施の形態にかかる整流回路 1 e を R F I D タグにおいて使用する場合には、キャパシタ C 7 1 は、ループアンテナに接続され、直列共振キャパシタとしても機

10

20

30

40

50

能する。

【0059】

フローティングゲートトンネル型電界効果トランジスタM71のドレイン端子とフローティングゲートトンネル型電界効果トランジスタM72のソース端子との間には、キャパシタC72が接続されている。フローティングゲートトンネル型電界効果トランジスタM71およびM72によって半波整流された信号は、このキャパシタC72によって平滑される。この平滑により、キャパシタC72の両端、すなわち正側端子T1と負側端子T2との間から直流電圧を取り出すことができる。

【0060】

特に、これらフローティングゲートトンネル型電界効果トランジスタM71およびM72とキャパシタC71およびC72とからなるダイオード回路は、従来整流が困難であった振幅100mV程度の小信号の交流信号も整流することができる。したがって、この整流回路をRFIDタグへ用いた場合、微弱な電波を整流することが可能となる。即ち、基地局から距離が離れたタグでも整流が可能となり、長距離通信が可能となる。

10

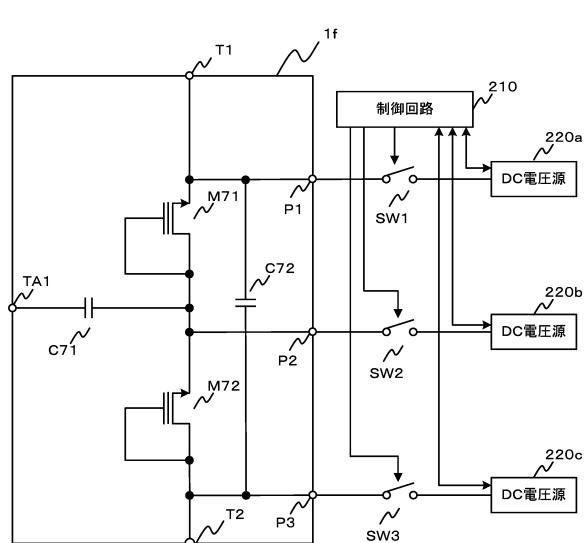

【0061】

整流回路1eはまた、スイッチSW1, SW2, SW3と、制御回路210と、DC電圧源220a, 220b, 220cとを備えている。これら構成要素は、フローティングゲートトンネル型電界効果トランジスタM71およびM72に対するチャージおよびディスチャージを行うためのものである。スイッチSW1の一端は、フローティングゲートトンネル型電界効果トランジスタM71のソース端子に接続され、他端はDC電圧源220aの出力端子に接続されている。スイッチSW2の一端は、フローティングゲートトンネル型電界効果トランジスタM72のソース端子に接続され、他端はDC電圧源220bの出力端子に接続されている。スイッチSW3の一端は、フローティングゲートトンネル型電界効果トランジスタM72のドレイン端子に接続され、他端はDC電圧源220cの出力端子に接続されている。スイッチSW1, SW2, SW3は、制御回路210にも接続されており、この制御回路210によって、ON/OFF制御される。DC電圧源220a, 220b, 220cもまた制御回路210に接続されており、この制御回路210から出力される制御信号に従って、各種動作モードの選択や出力電位を決定する。

20

【0062】

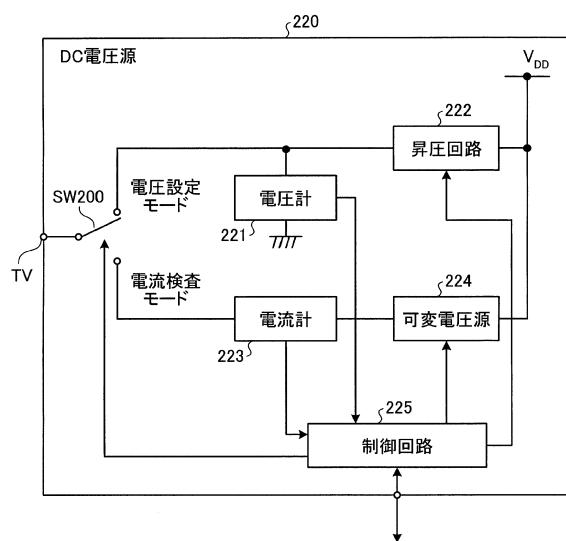

図17は、DC電圧源220a, 220b, 220cの代表として示されたDC電圧源220の回路図である。図17において、DC電圧源220は、2つの動作モードである、電圧設定モードと電流検査モードとの間の切換を行うスイッチSW200を備えている。また、DC電圧源220は、電圧計221、昇圧回路222、電流計223、可変電圧源224、および制御回路225を備えている。電圧設定モードに対応するスイッチSW200の端子には、電圧計221と昇圧回路222とが接続され、電流検査モードに対応するスイッチSW200の端子には電流計223を介して可変電圧源224が電気的に接続されている。制御回路225は、制御回路210から出力される制御信号に従って、スイッチSW200と、昇圧回路222および可変電圧源224に設定される電圧とを制御するとともに、電圧計221および電流計223でそれぞれ検出された電圧値および電流値を示す信号を制御回路210に送信する。

30

【0063】

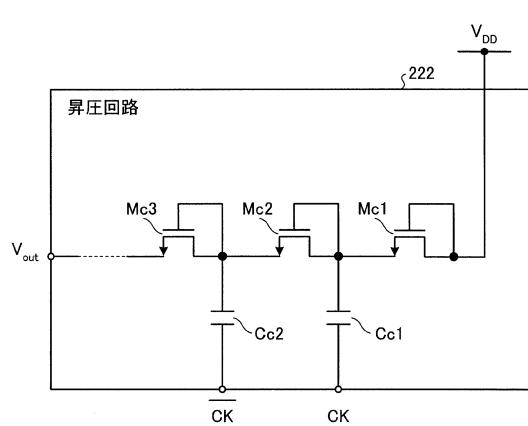

図18は、DC電圧源220の昇圧回路222の一例を示す回路図である。この昇圧回路222は、一般的なチャージポンプ回路を示している。トランジスタM<sub>c</sub>1とM<sub>c</sub>2との間のキャパシタC<sub>c</sub>1を介してクロック信号CKが入力され、トランジスタM<sub>c</sub>2とM<sub>c</sub>3との間のキャパシタC<sub>c</sub>2を介して逆相のクロック信号/C<sub>K</sub>が入力される。点線で記載した部分はこれら構成の繰り返しを意味する。クロック信号の入力によって電源電圧V<sub>DD</sub>は出力端子V<sub>OUT</sub>側に昇圧しながら移動して行く。トランジスタがN個ある場合、出力端子V<sub>OUT</sub>に出力される電圧は(N+1)(V<sub>DD</sub>-V<sub>th</sub>)で表わされる。V<sub>th</sub>は、トランジスタM<sub>c</sub>1～M<sub>c</sub>3の閾値電圧である。この昇圧回路222によって10V程度の電圧をフローティングゲート設定用に供給することができる。

40

50

## 【0064】

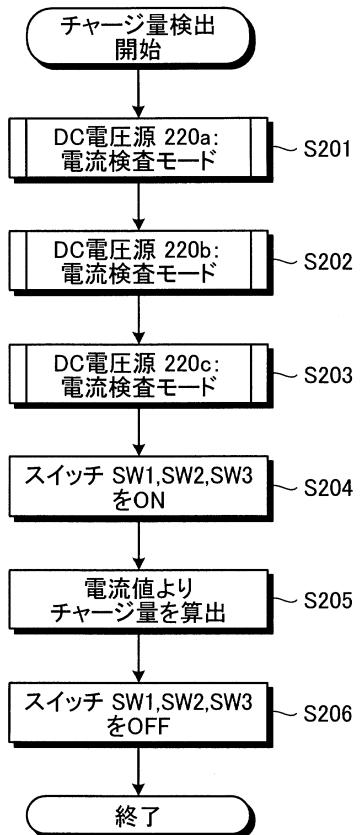

以下に、フローティングゲートトンネル型電界効果トランジスタM71およびM72のフローティングゲートの制御方法を説明する。図19は、フローティングゲートの制御方法を示すフローチャートである。まず、フローティングゲートトンネル型電界効果トランジスタM71およびM72の各フローティングゲートのチャージ量を検出する（ステップS101）。図20は、チャージ量検出工程を示すフローチャートである。整流回路1eの制御回路210は、チャージ量の検出に先がけ、DC電圧源220a～220cの各制御回路225に対し、動作モードを電流検査モードに切り替えることと各可変電圧源224に設定する電圧とが示された制御信号を送信する（ステップS201～S203）。また、制御回路210は、スイッチSW1～SW3をONにする（ステップS204）。 10

## 【0065】

図21は、DC電圧源220の電流検査モードの動作を示すフローチャートである。DC電圧源220の制御回路225は、制御回路210から上記制御信号を受けて、スイッチSW200を電流検査モードに切り替え（ステップS401）、可変電圧源224に上記電圧を設定する（ステップS402）。例えば、フローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートのチャージ量を調べる場合、DC電圧源220aの可変電圧源224を1Vに設定し、DC電圧源220bの可変電圧源224を0Vに設定する。続いて、各DC電圧源220の電流計223によって電流値が測定される（ステップS403）。なお、この電流値の測定は実際には、上記したステップS204の後に行われる。 20

## 【0066】

制御回路210は、DC電圧源220a, 220b, 220cにおいて測定された各電流値を受け取ると、それら電流値からチャージ量に相当する電圧 $V_c$ を算出し（ステップS205）、スイッチSW1～SW3をOFFにする（ステップS206）。

## 【0067】

続いて、制御回路210は、算出された電圧 $V_c$ が閾値電圧 $V_{th}$ 以上であるかを判定する（ステップS102）。この判定は、上記した電圧の設定例（DC電圧源220aの可変電圧源224: 1V, DC電圧源220bの可変電圧源224: 0V）のように、フローティングゲートトンネル型電界効果トランジスタのソース端子に与える電圧をドレイン端子に与える電圧よりも高く設定することにより可能となる。例えば、フローティングゲートトンネル型電界効果トランジスタM71のソース-ドレイン間に電流が流れた場合、すなわち、DC電圧源220aから得られた電流値が大きな値を示す場合、フローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートの電圧 $V_c$ はフローティングゲートトンネル型電界効果トランジスタM71の閾値電圧 $V_{th}$ 以上であると判定される。電圧 $V_c$ が閾値電圧 $V_{th}$ 未満である場合、すなわち、DC電圧源220aから得られた電流値がゼロか十分に小さい値を示す場合には（ステップS102: No）、フローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートをチャージする（ステップS103）。このチャージ設定に先駆けて、フローティングゲートの電圧と閾値電圧との差電圧を算出する。この差電圧の算出は、上記したチャージ量検出処理を繰り返すことにより行う。例えば、フローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートの電圧と閾値電圧との差電圧を算出する場合、DC電圧源220aの可変電圧源224を0Vに設定し、DC電圧源220bの可変電圧源224を0.5Vに設定する。次にスイッチSW1, SW2をONとし、DC電圧源220bから得られた電流値を調べる。 30

## 【0068】

この場合、フローティングゲートトンネル型電界効果トランジスタM71のチャネルに印加されるゲート電圧 $V_g$ はフローティングゲートの電圧値を $V_f$ とすると $V_g = V_f + 0.5$ と表される。この状態のとき、DC電圧源220bに流れる電流値は $(V_g - V_{th})^2 = (V_f + 0.5 - V_{th})^2$ に比例する。このときの電流値が、大きな値を示す場合にはDC電圧源220bの可変電圧源224を0.5Vより低く設定し、電流値がゼロか小さい値 40

10

20

30

40

50

を示す場合にはDC電圧源220bの可変電圧源224を0.5Vより高く設定する。こうして電流の境界状態の電圧値を読み取ることでフローティングゲートの電圧値と閾値電圧との電圧差が求められる。この電圧差に基づいて、電圧設定モードで与えられる電圧、すなわちDC電圧源220の昇圧回路222に設定する電圧を決定する。

#### 【0069】

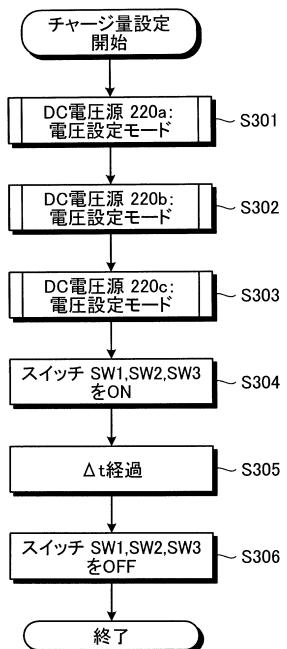

図22は、チャージ量設定工程を示すフローチャートである。制御回路210は、DC電圧源220a～220cの各制御回路225に対し、動作モードを電圧設定モードに切り替えることと、各昇圧回路222に設定する電圧とが示された制御信号を送信する（ステップS301～S303）。また、制御回路210は、スイッチSW1～SW3をONにする（ステップS304）。

10

#### 【0070】

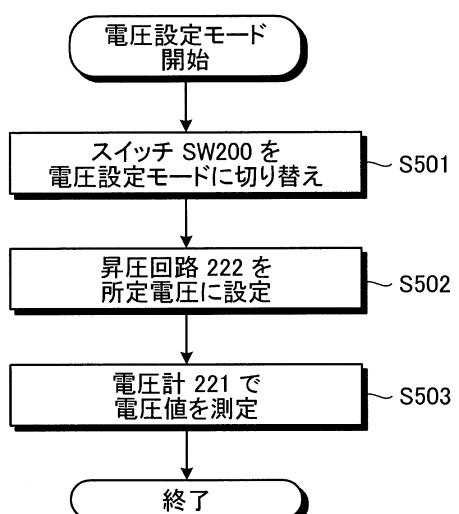

図23は、DC電圧源220の電圧設定モードの動作を示すフローチャートである。DC電圧源220の制御回路225は、制御回路210から上記制御信号を受けて、スイッチSW200を電圧設定モードに切り替え（ステップS501）、昇圧回路222に上記電圧を設定する（ステップS502）。例えば、フローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートをチャージする場合、DC電圧源220aの昇圧回路222を高電圧に設定し、DC電圧源220bの昇圧回路222を0Vに設定する。フローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートの電圧値は、各DC電圧源220の電圧計221によって測定される（ステップS503）。なお、この電圧値の測定は実際には、上記したステップS304の後に行われる。

20

#### 【0071】

制御回路210は、昇圧回路222によってフローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートに高電圧を、所定の時間tの間印加した後（ステップS305）、スイッチSW1～SW3をOFFにする（ステップS306）。この時間tは、フローティングゲートへチャージができ、かつ飽和しない程度の時間を選択する。

#### 【0072】

上記したステップS102において、電圧 $V_C$ が閾値電圧 $V_{th}$ 以上である場合、すなわち、DC電圧源220aから得られた電流値が大きい値を示す場合には（ステップS102：Yes）、電圧 $V_C$ が閾値電圧 $V_{th}$ より大きいか否かが判定される（ステップS104）。電圧 $V_C$ が閾値電圧 $V_{th}$ より大きい場合には（ステップS104：Yes）、フローティングゲートトンネル型電界効果トランジスタM71は常にオン状態となっているため、整流効率が低下する。これを避けるため、フローティングゲートをディスチャージする（ステップS105）。

30

#### 【0073】

ディスチャージの設定は、図22に示したチャージ量設定工程と同様な処理により実現できる。具体的には、例えばフローティングゲートトンネル型電界効果トランジスタM71のフローティングゲートをディスチャージする場合、DC電圧源220aを0Vに設定し、DC電圧源220bを高電圧に設定した後、スイッチSW1, SW2をONとする。これにより、フローティングゲートトンネル型電界効果トランジスタM71のソース端子に存在する電子はフローティングゲート中に注入され、フローティングゲートのチャージを減らすことができる。

40

#### 【0074】

ステップS104において、電圧 $V_C$ が閾値電圧 $V_{th}$ より大きくない場合（ステップS104：No）、すなわち、電圧 $V_C$ と閾値電圧 $V_{th}$ とが等しい場合には、フローティングゲートの制御を終了する。

#### 【0075】

以上の説明では、フローティングゲートトンネル型電界効果トランジスタM71を例示したが、フローティングゲートトンネル型電界効果トランジスタM72についても同様で

50

ある。なお、各フローティングゲートトンネル型電界効果トランジスタの閾値電圧を高い電位に設定することも可能である。この場合、微弱な無線信号は整流できなくなる。特に、本整流回路 1 e を R F I D タグに適用した場合、基地局の近くにある R F I D タグだけが整流動作がされることになる。このように、フローティングゲートへのチャージの量で通信距離を制御することも可能であり、セキュリティやプライバシーが問題となる条件と長距離での通信が必要な場合で、R F I D タグの性能を変えることが可能となる。

#### 【0076】

以上に説明したように、本実施の形態にかかる整流回路によれば、ダイオード接続されたフローティングゲートトンネル型電界効果トランジスタのフローティングゲートに、このフローティングゲートトンネル型電界効果トランジスタが整流特性を発現するのに要する閾値電圧程度の定電圧が保持されているので、閾値電圧未満の実効値を有する交流信号をも整流することができる。

#### 【0077】

##### (実施の形態 6)

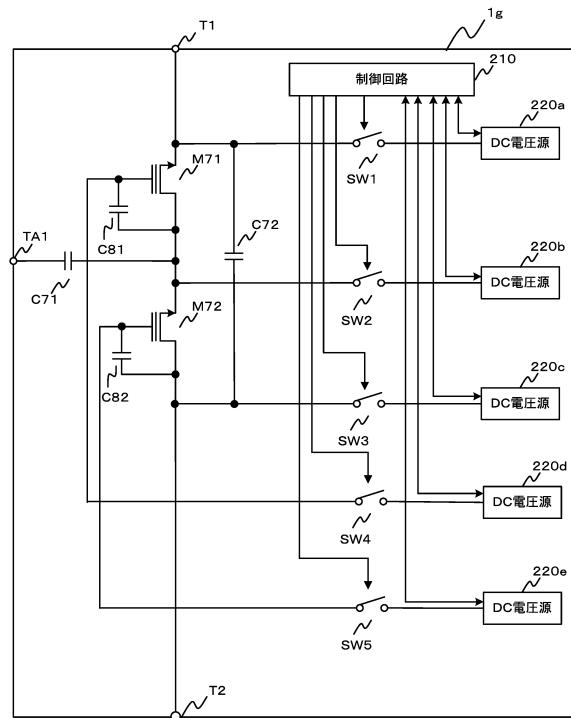

実施の形態 6 にかかる整流回路は、実施の形態 5 にかかる整流回路 1 e の変形例であり、スイッチ SW 1 ~ SW 3 と、制御回路 210 と、DC 電圧源 220a ~ 220c からなる構成が外部装置として提供されることを特徴としている。図 24 は、実施の形態 6 にかかる整流回路を示す回路図である。図 24 に示す整流回路 1 f において、図 16 と共に通する部分には同一の符号を付しており、ここではそれらの説明を省略する。

#### 【0078】

整流回路 1 f は、図 16 に示した整流回路 1 e の構成要素のうち、フローティングゲートトンネル型電界効果トランジスタ M71, M72 と、キャパシタ C71, C72 のみを備えている。整流回路 1 f は、IC チップとして提供され、フローティングゲートトンネル型電界効果トランジスタ M71 の ソース 端子に接続された電極パッド P1 と、フローティングゲートトンネル型電界効果トランジスタ M72 の ソース 端子に接続された電極パッド P2 と、フローティングゲートトンネル型電界効果トランジスタ M72 の ドレイン 端子に接続された電極パッド P3 とを備えている。電極パッド P1, P2, P3 は、それぞれ上記したスイッチ SW1, SW2, SW3 の一端に接続することができる。

#### 【0079】

これにより、整流回路 1 f は、例えば、工場出荷時に一度だけ、電極パッド P1 ~ P3 を介して、フローティングゲートトンネル型電界効果トランジスタ M71, M72 のフローティングゲートに対して上記したフローティングゲートの制御方法（図 19 参照）を実行する。フローティングゲートは絶縁体で覆われているため、通常一度設定したチャージは長い間放出されることなく、同じ状態を保持することが可能である。例えば、フローティングゲートを用いた EEPROM のメモリセルの場合、記憶保持期間は 10 年間が保証されている。したがって、本実施の形態の場合も、一度フローティングゲートにチャージを設定すれば数年に渡る使用に再調整なしで用いることが可能である。

#### 【0080】

すなわち、この整流回路 1 f を R F I D タグに適用する場合、工場出荷時に一度フローティングゲートへのチャージを設定すれば、ユーザは一般的な R F I D タグと同様な使用方法で利用ができ、かつ長距離通信が可能な R F I D タグを供給することができる。

#### 【0081】

##### (実施の形態 7)

実施の形態 7 にかかる整流回路もまた、実施の形態 5 にかかる整流回路の変形例であり、フローティングゲートトンネル型電界効果トランジスタ M71, M72 の制御ゲート端子とソース端子との間にそれぞれキャパシタを設け、このキャパシタの保持電圧を制御することができることを特徴としている。

#### 【0082】

図 25 は、実施の形態 7 に整流回路を示す回路図である。図 25 に示す整流回路 1 g において、図 16 と共に通する部分には同一の符号を付しており、ここではそれらの説明を省

10

20

30

40

50

略する。図25において、整流回路1gは、図16に示す整流回路1eの構成要素に対して、フローティングゲートトンネル型電界効果トランジスタM71の制御ゲート端子とドレイン端子との間に接続されたキャパシタC81と、フローティングゲートトンネル型電界効果トランジスタM72の制御ゲート端子とドレイン端子との間に接続されたキャパシタC82と、DC電圧源220d, 220eとをさらに備えている。また、フローティングゲートトンネル型電界効果トランジスタM71の制御ゲート端子とDC電圧源220dの出力端子との間にはスイッチSW4が接続され、フローティングゲートトンネル型電界効果トランジスタM72の制御ゲート端子とDC電圧源220eの出力端子との間にはスイッチSW5が接続されている。DC電圧源220d, 220eおよびスイッチSW4, SW5は、他のDC電圧源220a~220cおよびスイッチSW4, SW5と同様に制御回路210によって制御される。また、DC電圧源220d, 220eは、図17に示したDC電圧源220と同じ構成である。

#### 【0083】

この構成によって、フローティングゲートトンネル型電界効果トランジスタM71, M72の各制御ゲート端子に、様々な入力電圧を個別に与えることができ、フローティングゲートトンネル型電界効果トランジスタM71, M72がONとなるのに必要な入力信号電圧、換言すれば、フローティングゲートトンネル型電界効果トランジスタM71, M72が整流特性を示すのに必要な入力信号電圧を任意の大きさに調整することができる。

#### 【0084】

##### (実施の形態8)

図26は、本発明の第4の実施形態に係る整流回路の回路図である。本実施形態のフローティングゲートトンネル型電界効果トランジスタM71, M72, M73は、実施の形態5で説明したフローティングゲートトンネル型電界効果トランジスタと同様である。フローティングゲートトンネル型電界効果トランジスタM71のソース電極が正側端子T1に接続され、フローティングゲートトンネル型電界効果トランジスタM71のドレイン電極にフローティングゲートトンネル型電界効果トランジスタM72のソース電極が接続され、フローティングゲートトンネル型電界効果トランジスタM72のドレイン電極にフローティングゲートトンネル型電界効果トランジスタM73のソース電極が接続され、フローティングゲートトンネル型電界効果トランジスタM73のドレイン電極が負側端子T2に接続される。フローティングゲートトンネル型電界効果トランジスタM71, M72, M73のゲート電極はそれぞれドレイン電極と接続される。入力端子TA1, TA2には、差動のAC信号が入力される。入力された差動信号は、キャパシタC11, C12を介して、トンネルFET20b, 20cのソース電極にそれぞれ入力される。このようにフローティングゲートトンネル型電界効果トランジスタM71, M72, M73を直列に接続し、差動信号を入力端子TA1, TA2に入力することにより、第5の実施形態の整流回路と比較して、振幅が倍の信号が入力されるため、整流効率や感度を向上させることができる。なお、本実施形態の整流回路においても、整流回路1hを複数縦積みした構成とすることもできる。すなわち、図26に示す整流回路1hの正側端子T1または負側端子T2に整流回路1hと同様の回路を接続しても良い。

#### 【0085】

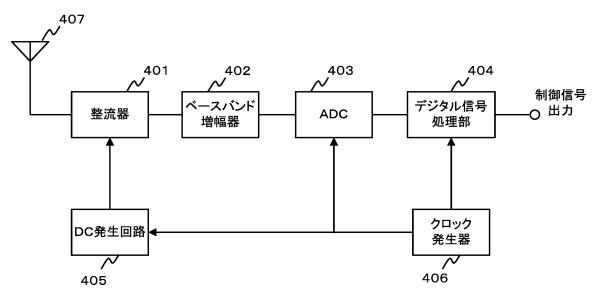

##### (実施の形態9)

図27は、実施の形態1~8のいずれかに記載の整流回路を用いた無線受信装置を示すプロック図である。この無線受信装置は、整流回路401、ベースバンド増幅器402、ADC(analog to digital converter)403、デジタル信号処理部404、DC発生回路405、クロック発生器406、アンテナ407を用いて構成される。整流回路401は、実施の形態1~7のいずれかに記載の整流回路である。DC発生回路405は、例えば図4のDC発生回路110に相当する。整流回路401は、アンテナ407から入力された信号を自乗検波して信号の包絡線をベースバンド信号として出力する。ベースバンド増幅器402は、入力されたベースバンド信号を増幅する。ADC403は、クロック発生器406から出力されるクロックに応じて動作し、入力された信号をデジタル信号へ

10

20

30

40

50

変換する。デジタル信号処理部 404 は、クロック発生器 406 から出力されるクロックに応じて動作し、入力された信号から I D 等の所定のデータを抽出し、これらのデータが規定の信号と一致する場合には、制御信号を出力する。

#### 【 0 0 8 6 】

実施の形態 1 ~ 4 に記載のように、トンネル F E T を用いて整流回路 401 を構成する場合、整流回路 401 にはトンネル F E T を用いるが、ベースバンド増幅器 402、A D C 403、デジタル信号処理部 404、バイアス発生器 405、クロック発生器 406 には、トンネル F E T ではなく C M O S 回路を用いる。

#### 【 0 0 8 7 】

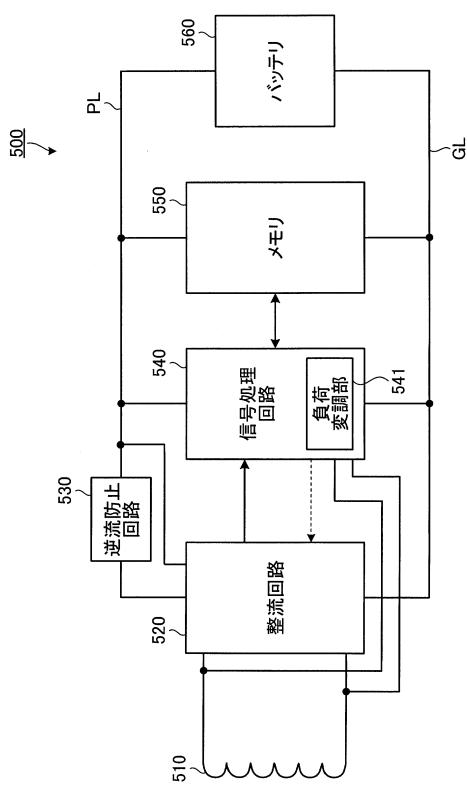

( 実施の形態 10 )

10

図 28 は、実施の形態 1 ~ 8 のいずれかに記載の整流回路を用いて構成された R F I D タグを示すブロック図である。図 28 に示す R F I D タグ 500 は、ループアンテナ 510 と、実施の形態 1 ~ 8 のいずれか一つに示した整流回路と同じ構成の整流回路 520 と、逆流防止回路 530 と、信号処理回路 540 と、メモリ 550 と、二次電池であるバッテリ 560 とを備えて構成される。特に、この R F I D タグ 500 は、バッテリ 560 による電源電圧によって駆動する R F I D タグであり、その動作において、整流回路 520 から電源電圧を生成することを必須要件としない。すなわち、整流回路 520 と、逆流防止回路 530 と、信号処理回路 540 と、メモリ 550 は、バッテリ 560 から引き伸ばされた電源ライン P L および接地ライン G L にそれぞれ接続されている。

#### 【 0 0 8 8 】

20

ループアンテナ 510 は、リーダ / ライタ ( 図示せず ) によって与えられる磁束変化に応じて、そのアンテナ線に交流電流を誘起する。この交流電流は、整流回路 520 の信号入力端子に入力される。整流回路 520 は、バッテリ 560 から供給される電源電圧によって駆動する。よって、整流回路 520 内の D C 発生回路は、バッテリ 560 から供給される電源電圧によって駆動するとともに、バッテリ 560 から供給される電源電圧から所望の直流電圧を生成する。すなわち、整流回路 520 は、ループアンテナ 510 から交流電流が入力されるか否かに關係なく、ダイオード回路を構成する各トンネル F E T のゲートとソースとの間には常に上記したダイオードバイアス電圧が印加されている。あるいは、外部トリガによってダイオードバイアス電圧が印加される。よって、整流回路 520 は、実施の形態 1 ~ 5 に示したように、ループアンテナ 510 において誘起された 0.7 V 程度未満の実効値を有する微弱な交流電流をも整流することができる。すなわち、ループアンテナ 510 が受け取った微弱なデータ信号を復調することができる。この復調されたデータ信号は、信号処理回路 540 へと入力される。また、整流回路 520 によって得られた直流電圧は、充電用電力として、逆流防止回路 530 を介して、バッテリ 560 にも供給される。

30

#### 【 0 0 8 9 】

信号処理回路 540 は、整流回路 520 から受け取ったデータ信号に基づき、メモリ 550 に格納されたデータ ( 代表的なものとしてはタグ識別情報 ) の取り出しやメモリ 550 へのデータの書き込みを行なう。信号処理回路 540 は、ループアンテナ 510 に接続された負荷変調部 541 を備えており、メモリ 550 から取り出されたデータは、この負荷変調部 541 によるループアンテナ 510 の電流の変調によって、リーダ / ライタに送信される。具体的には、負荷変調部 541 は、ループアンテナ 510 に反磁界を発生させ、この反磁界は、リーダ / ライタのアンテナを流れる電流を微小に変化させる。この微小な変化が、リーダ / ライタによって検出され、データ信号として認識される。なお、図 5 に示したようなクロック発生回路 130 は、信号処理回路 540 に設けてもよいし、整流回路 520 内に設けてもよい。

40

#### 【 0 0 9 0 】

図 29 は、本実施の形態にかかる R F I D タグの整流特性 ( 実線 ) と、従来の R F I D タグの整流特性 ( 破線 ) を示したグラフである。本実施の形態にかかる R F I D タグでは、-10 dBm の微小な交流信号 ( A C 入力パワー ) が入力された場合であっても 1.5

50

Vの直流電圧（DC出力電圧）を発生することができる。この-10dBmの信号は、リーダ／ライタとRFIDタグとの間の距離に換算すると、10m程度に相当する。なお、グラフにおいて、AC入力パワーが大きくなるとDC出力電圧が一定値となるのは回路内部の電圧リミッタが働いているためである。一方で、従来のRFIDタグでは-10dBmのAC信号に対して0.05Vの直流電圧しか発生することができず、整流回路として機能していないことがわかる。

#### 【0091】

以上に説明したように、実施の形態10にかかるRFIDタグによれば、実施の形態1～7のいずれか一つにかかる整流回路を搭載しているので、従来において整流対象となり得なかつた微小信号をも認識することができる。これは、RFIDタグの認識に必要なRFIDタグとリーダ／ライタとの間の距離を大幅に拡大させることを意味し、そのRFIDシステムの応用分野を格段に広げることができる。例えば、一つのリーダ／ライタによって、数十m～数100mの範囲に分散された多数のRFIDタグをほぼ同時に認識することができる。これにより、RFIDタグを家畜に付与することによって放牧状態の家畜を管理したり、RFIDタグを幼児や徘徊老人に付与することによって迷子を防止することができる。

#### 【0092】

また、本実施の形態にかかるRFIDタグは、バッテリを備えているために、RFIDタグに温度センサ、スピーカ、マイク、発光素子などの種々の入出力デバイス570を搭載することも容易である。その場合、RFIDタグのさらなる応用の拡大を図ることが可能となる。例えば、RFIDタグにセンサを搭載する場合は、図30のような構成になる。図30に示すRFIDタグ600において、図28と同一の構成には同一の参照符号を附している。入出力デバイス570の電源系はバッテリ560からのPLラインとGLラインに接続されている。入出力デバイス570への信号の送受は信号処理回路540との間で行う。入出力デバイス570の一例として、温度センサを搭載したRFIDタグの例を説明する。リーダ／ライタ（図示せず）からの送信が無いとき、温度センサはスリープ状態であり、電流を消費しない。リーダ／ライタから送信信号があり、当該センサ付RFIDタグへの信号送信の指令が有った場合、温度センサは起動し、温度を検知、データを信号処理回路へ送出する。この信号データと、RFIDタグの固有データを合わせた信号データをRFIDタグからリーダ／ライタへ返信する。他の温度センサの実施方法として、ある一定時間ごとに信号処理回路が温度センサへ温度データの出力の指令を行い、温度センサからのデータはメモリブロックへ蓄積される。リーダライタからの指令が有った場合、蓄積された温度データは、記録時間データと共に送出される。また、温度センサの起動手段として、振動、音、光等の刺激があった場合に温度センサが起動し、データをメモリに蓄積する方法もある。

#### 【0093】

以上のとおり、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0094】

1, 1a, 1b, 1c, 1d, 1e, 1f, 1g, 1h... . . . 、整流回路、 10, 10a, 10b, 10c, 10d...バイアス電圧発生回路、 20, 20a, 20b, 20c, 20d...トンネルFET、 T1...正側端子、 T2...負側端子、 201...半導体基板、 202...ソース領域、 203...ドレイン領域、 204...絶縁膜、 10...バイアス電圧発生回路、 M11, M12, M21, M22...NMOSトランジスタ、 C1, C12...キャパシタ、 INV1, INV2...インバータ、 110...DC発生回路

10

20

30

40

50

、 T C ... クロック入力端子、 1 3 0 ... クロック発生回路、 M d 1 , M d 2 , M d 3 , M d 4 ... NMOSトランジスタ、 C d 1 , C d 2 , C 1 , C 2 , C 2 1 , C 2 2 ... キヤパシタ、 I N V 1 1 , I N V 1 2 ... インバータ、 3 1 0 ... 誤差増幅部、 B C ... 出力端子、 1 1 0 a ... DC発生回路、 1 1 1 ... 定電流源、 M 1 0 1 ... トンネルF E T 、 S W ... スイッチ、 1 1 0 b ... DC発生回路、 M 1 1 1 , M 1 1 2 ... トンネルF E T 、 T A 1 , T A 2 ... 入力端子、 1 1 a , 1 1 b ... 可変バイアス電圧発生回路、 4 0 ... インピーダンス計測手段、 2 0 6 ... 第1の絶縁膜、 2 0 7 ... フロー・ティイングゲート、 2 0 8 ... 第2の絶縁膜、 2 0 9 ... コントロールゲート、 M 7 1 , M 7 2 , M 7 3 ... フロー・ティイングゲート・トンネル型電界効果トランジスタ、 2 1 0 ... 制御回路、 2 2 0 , 2 2 0 a , 2 2 0 b , 2 2 0 c ... DC電圧源、 S W 1 , S W 2 , S W 3 ... スイッチ、 C 7 1 , C 7 2 ... キヤパシタ、 2 2 1 ... 電圧計、 2 2 2 ... 昇圧回路、 2 2 3 ... 電流計、 2 2 4 ... 可変電圧源、 2 2 5 ... 制御回路、 M c 1 , M c 2 , M c 3 ... トランジスタ、 C c 1 , C c 2 ... キヤパシタ、 P 1 , P 2 , P 3 ... 電極パッド、 4 0 1 ... 整流器、 4 0 2 ... ベースバンド増幅器、 4 0 3 ... A D C 、 4 0 4 ... デジタル信号処理部、 4 0 5 ... DC発生回路、 4 0 6 ... クロック発生器、 4 0 7 ... アンテナ、 5 0 0 ... R F I Dタグ、 5 1 0 ... ループアンテナ、 5 2 0 ... 整流回路、 5 3 0 ... 逆流防止回路、 5 4 0 ... 信号処理回路、 5 4 1 ... 負荷変調部、 5 5 0 ... メモリ、 5 6 0 ... バッテリ、 P L ... 電源ライン、 G L ... 接地ライン

【図1】

【 図 2 】

【図3】

【図5】

【図4】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

(a)

(b)

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

## 【図25】

### 【図26】

## 【図27】

【図28】

【図29】

【図30】

---

フロントページの続き

(72)発明者 梅田 俊之

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 大高 章二

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 安食 泰秀

(56)参考文献 特開2006-034085(JP, A)

特開平05-190847(JP, A)

国際公開第2011/121663(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H 02 M 7 / 12

H 03 D 1 / 18