(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5547594号

(P5547594)

(45) 発行日 平成26年7月16日(2014.7.16)

(24) 登録日 平成26年5月23日(2014.5.23)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| H05K 1/02    | (2006.01) |

| H05K 3/00    | (2006.01) |

| H05K 3/46    | (2006.01) |

|              | HO5K 1/02 |

|              | HO5K 3/00 |

|              | HO5K 3/46 |

|              | R         |

|              | P         |

|              | Z         |

請求項の数 8 (全 19 頁)

(21) 出願番号 特願2010-216614 (P2010-216614)

(22) 出願日 平成22年9月28日 (2010.9.28)

(65) 公開番号 特開2012-74443 (P2012-74443A)

(43) 公開日 平成24年4月12日 (2012.4.12)

審査請求日 平成25年6月12日 (2013.6.12)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100105957

弁理士 恩田 誠

(72) 発明者 村松 茂次

長野県長野市小島田町80番地 新光電気

工業 株式会社 内

(72) 発明者 春原 聰

長野県長野市小島田町80番地 新光電気

工業 株式会社 内

審査官 井上 信

最終頁に続く

(54) 【発明の名称】配線基板、半導体装置及び配線基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

最上層配線と、前記最上層配線を覆う絶縁層とを含む配線基板であって、

前記最上層配線は、平面形状が認識マークの所望の形状となるように形成され、上面の

全てが前記絶縁層から露出されることで前記認識マークとなる第1の配線層を有し、

前記絶縁層は、前記第1の配線層の上面を全て露出させるための凹部を有し、

前記絶縁層は、前記第1の配線層の側壁を被覆して前記認識マークの周囲を被覆し、

前記凹部の底面には、前記認識マークの端部から前記凹部の側壁部に向かって湾曲状に

凹む湾曲部が形成されていることを特徴とする配線基板。

## 【請求項 2】

前記凹部の底面の表面粗度は、前記認識マークの表面粗度よりも高く、前記凹部の縁部

の表面粗度よりも高いことを特徴とする請求項1に記載の配線基板。

## 【請求項 3】

前記最上層配線は、少なくとも一部がパッドとして前記絶縁層から露出される第2の配

線層を含み、

前記第1の配線層と前記第2の配線層とは同じ厚さで形成されていることを特徴とする

請求項1又は2に記載の配線基板。

## 【請求項 4】

前記凹部は、その側壁部が傾斜面となっていることを特徴とする請求項1～3のいずれ

か1つに記載の配線基板。

10

20

## 【請求項 5】

請求項 1 ~ 4 のいずれか 1 つに記載の配線基板を含むことを特徴とする半導体装置。

## 【請求項 6】

絶縁層から露出される認識マークを有する配線基板の製造方法であって、

平面形状が前記認識マークの所望の形状となるように第 1 の配線層を形成する配線層形成工程と、

前記第 1 の配線層を覆う前記絶縁層を形成する絶縁層形成工程と、

前記第 1 の配線層に対向する領域であって、前記第 1 の配線層の平面形状よりも大きい領域の前記絶縁層を薄化することにより、前記絶縁層に凹部を形成するとともに、前記第 1 の配線層の上面の全てを前記絶縁層から露出して前記認識マークを形成する薄化工程とを含み、

前記薄化工程では、前記凹部の底面に、前記認識マークの端部から前記凹部の側壁部に向かって湾曲状に凹む湾曲部が形成されるように、前記絶縁層を薄化し、

前記薄化工程は、

前記絶縁層の上に、前記凹部に対応する領域を開口する開口部を有するマスクを形成する工程と、

前記マスクの開口部を通じて前記絶縁層にサンドブラスト処理を施すブラスト工程と、を含むことを特徴とする配線基板の製造方法。

## 【請求項 7】

前記認識マークをエッチングする工程を含むことを特徴とする請求項 6 に記載の配線基板の製造方法。

## 【請求項 8】

前記配線層形成工程では、前記第 1 の配線層と同じ厚さの第 2 の配線層を形成し、

前記絶縁層形成工程では、前記第 1 の配線層と前記第 2 の配線層とを覆うように前記絶縁層を形成し、

前記薄化工程では、前記認識マークを形成するとともに、前記第 2 の配線層に対向する領域の前記絶縁層を薄化することにより、前記第 2 の配線層の少なくとも一部を前記絶縁層から露出してパッドを形成することを特徴とする請求項 6 又は 7 に記載の配線基板の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、配線基板、半導体装置及び配線基板の製造方法に関するものである。

## 【背景技術】

## 【0002】

半導体チップ等の実装部品を配線基板に実装する場合には、配線基板の最表層がソルダレジストと呼ばれる絶縁材料によってはんだの付着や汚染等から保護される。この場合、実装部品との接続に必要なパッドを形成するために、ソルダレジストの下層に形成された配線層を露出させるための開口部が形成される。この開口部の形成は、フォトリソグラフィ法、スクリーン印刷法やレーザ加工法などにより行われる。

## 【0003】

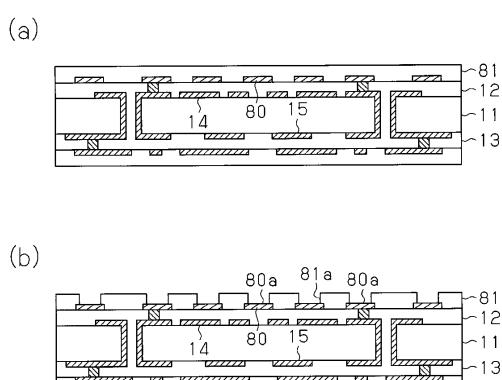

フォトリソグラフィ法では、図 12 (a) に示すように、まず、コア基板 11 上に必要な数の下層配線 14, 15 とそれを覆う絶縁層 12, 13 を形成後、最上層の配線層 80 とその配線層 80 を覆う絶縁層 (ソルダレジスト層) 81 を形成する。続いて、フォトリソグラフィによりソルダレジスト層 81 を露光・現像して、図 12 (b) に示す所定パターンの開口部 81a を形成し、最上層の配線層 80 の一部をパッド 80a として露出する。

## 【0004】

また、スクリーン印刷法では、印刷マスクを使用して、必要な部分のみに絶縁材料 (ソルダレジスト) を印刷する。レーザ加工法では、全面に絶縁材料 (ソルダレジスト) を塗

10

20

30

40

50

布してから、露出させる領域（開口部に対応する領域）の絶縁材料をレーザ光照射により除去する。

#### 【0005】

上述のように、フォトリソグラフィ法では、ソルダレジストとして感光性樹脂を用い、露光と現像によるパターン化が行われる。しかし、感光性樹脂は一般的に耐熱性や耐薬品性が低いという問題がある。一方、スクリーン印刷法やレーザ加工法では、ソルダレジストとして感光性樹脂よりも信頼性の高い熱硬化性樹脂等の非感光性樹脂を採用することができるものの、ファインパターンの形成が困難、製造コストが高いといった問題がある。

#### 【0006】

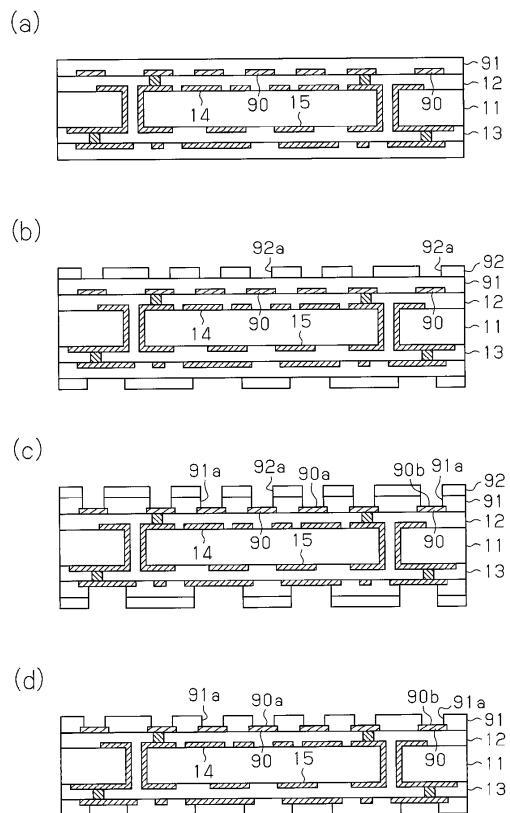

そこで、パッドを露出させるための開口部を形成する別 の方法として、プラスト法が提案されている。例えばサンドブラスト法では、図13(a)に示すように、まず、コア基板11上に必要な数の下層配線14, 15とそれを覆う絶縁層12, 13を形成後、最上層の配線層90とその配線層90を覆う絶縁層（ソルダレジスト層）91を形成する。続いて、図13(b)に示すように、ソルダレジスト層91の上にサンドブラスト保護用のドライフィルムレジスト（DFR）92を貼り付け、露光・現像により所定パターンの開口部92aを形成する。次に、図13(c)に示すように、DFR92の開口部92aに砥粒を吹き付けて絶縁樹脂を除去し、ソルダレジスト層91に開口部91aを形成するとともに、最上層の配線層90の一部をパッド90aや認識マーク90bとして露出する。その後、図13(d)に示すように、DFR92を除去する。

#### 【0007】

なお、上記従来技術に関連する先行技術として、特許文献1, 2が開示されている。

#### 【先行技術文献】

##### 【特許文献】

##### 【0008】

【特許文献1】特開平05-267802号公報

【特許文献2】特開2008-227309号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0009】

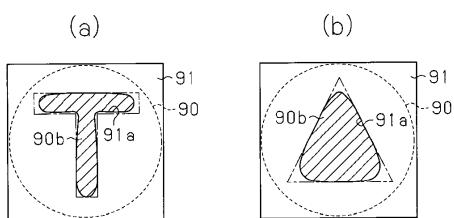

ところが、プラスト法による絶縁層（ソルダレジスト層）の開口では、図14に示すように、絶縁層91の開口部91aの形状がT字形状や三角形状などの鋭角や直角な角を有する形状である場合には、以下のような問題が発生する。すなわち、鋭角や直角な角を有する部分には絶縁層91に吹き付ける砥粒が入り込みにくいため、このような形状の開口部91aをプラスト法で形成すると、図15(a)、(b)に示すように、鋭角や直角な角を有する部分が丸まって形成されてしまう。このため、プラスト法で絶縁層91に開口部91aを形成することによって認識マーク90b（実装や露光時等の位置合わせマークや管理上必要な文字や数字など）を形成する場合には、その認識マーク90bのエッジが丸まることになる。これに起因して、認識マーク90bの認識性が低下するという問題が発生する。

##### 【0010】

本発明は上記問題点を解決するためになされたものであって、その目的は、認識マークの認識性の低下を抑制することのできる配線基板、半導体装置及び配線基板の製造方法を提供することにある。

#### 【課題を解決するための手段】

##### 【0011】

本発明の一観点によれば、最上層配線と、前記最上層配線を覆う絶縁層とを含む配線基板であって、前記最上層配線は、平面形状が認識マークの所望の形状となるように形成され、上面の全てが前記絶縁層から露出されることで前記認識マークとなる第1の配線層を有し、前記絶縁層は、前記第1の配線層の上面を全て露出させるための凹部を有し、前記絶縁層は、前記第1の配線層の側壁を被覆して前記認識マークの周囲を被覆し、前記凹部

10

20

30

40

50

の底面には、前記認識マークの端部から前記凹部の側壁部に向かって湾曲状に凹む湾曲部が形成されている。

【0012】

この構成によれば、絶縁層から露出される第1の配線層の上面の形状(平面形状)が認識マークの形状となる。ここで、第1の配線層は、その所望の平面形状が鋭角や直角な角を有する形状であっても、例えばフォトリソグラフィ法などによってその所望の平面形状に容易に形成することができる。したがって、このような第1の配線層の上面が全て露出されれば、プラスト法によって認識マークを露出させるための凹部が所望の形状に形成できない場合であっても、認識マークを所望の形状に精度良く形成することができる。この結果、認識マークの認識性の低下を抑制することができる。

10

【0013】

また、認識マークを露出させるための凹部をプラスト法によって形成することもできるため、絶縁層として非感光性樹脂を採用することができ、絶縁層の信頼性の低下も抑制することができる。

【0014】

本発明の一観点によれば、絶縁層から露出される認識マークを有する配線基板の製造方法であって、平面形状が前記認識マークの所望の形状となるように第1の配線層を形成する配線層形成工程と、前記第1の配線層を覆う前記絶縁層を形成する絶縁層形成工程と、前記第1の配線層に対向する領域であって、前記第1の配線層の平面形状よりも大きい領域の前記絶縁層を薄化することにより、前記絶縁層に凹部を形成するとともに、前記第1の配線層の上面の全てを前記絶縁層から露出して前記認識マークを形成する薄化工程とを含み、前記薄化工程では、前記凹部の底面に、前記認識マークの端部から前記凹部の側壁部に向かって湾曲状に凹む湾曲部が形成されるように、前記絶縁層を薄化し、前記薄化工程は、前記絶縁層の上に、前記凹部に対応する領域を開口する開口部を有するマスクを形成する工程と、前記マスクの開口部を通じて前記絶縁層にサンドプラスト処理を施すプラスト工程と、を含む。

20

【0015】

この方法によれば、絶縁層が薄化されることによって、所望の平面形状に形成された第1の配線層の上面の全てが絶縁層から露出されて認識マークが形成される。このため、絶縁層から露出される第1の配線層の上面の形状(平面形状)が認識マークの形状となる。ここで、第1の配線層は、その所望の平面形状が鋭角や直角な角を有する形状であっても、例えばフォトリソグラフィ法などによってその所望の平面形状に容易に形成することができる。したがって、このような第1の配線層の上面が全て露出されれば、薄化される絶縁層の領域が所望の形状にならない場合であっても、認識マークを所望の形状に精度良く形成することができる。この結果、認識マークの認識性の低下を抑制することができる。

30

【発明の効果】

【0016】

本発明の一観点によれば、認識マークの認識性の低下を抑制することができるという効果を奏する。

40

【図面の簡単な説明】

【0017】

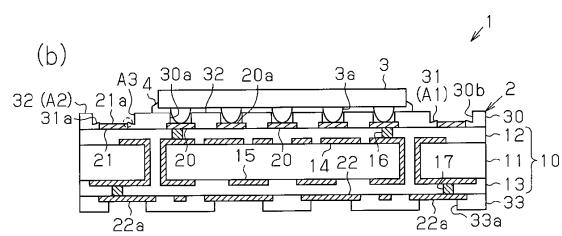

【図1】(a)は第1実施形態の半導体装置を示す概略平面図、(b)は第1実施形態の半導体装置を示す概略断面図。

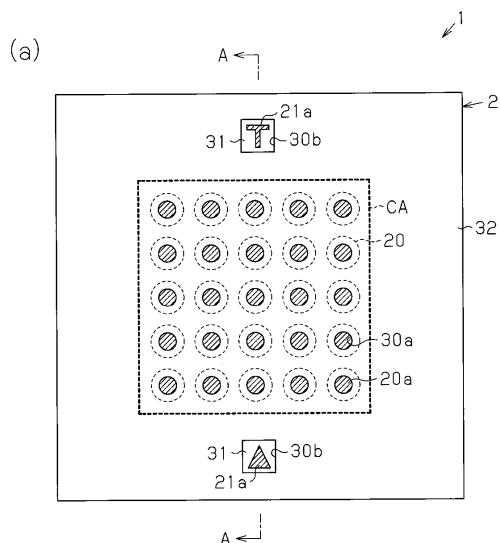

【図2】第1実施形態の半導体装置を示す概略斜視図。

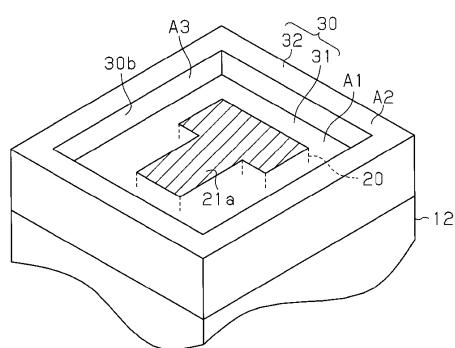

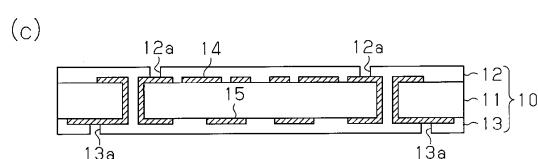

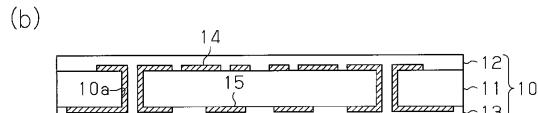

【図3】(a)～(d)は、第1実施形態の半導体装置の製造方法を説明するための概略断面図。

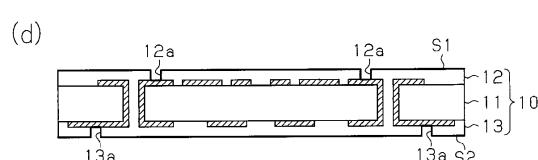

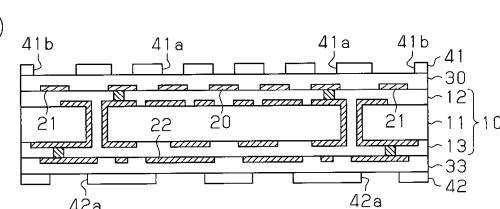

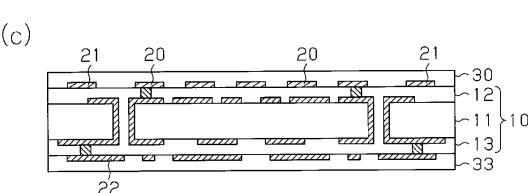

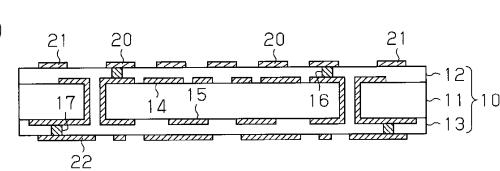

【図4】(a)～(d)は、第1実施形態の半導体装置の製造方法を説明するための概略断面図。

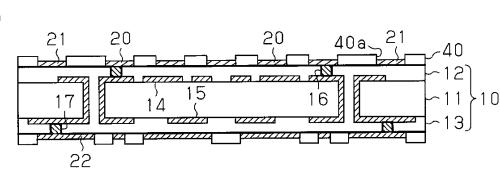

【図5】(a)～(d)は、第1実施形態の半導体装置の製造方法を説明するための概略断面図。

50

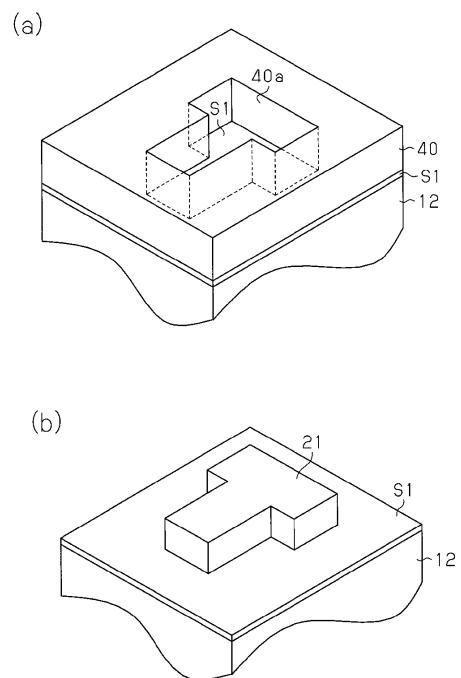

【図6】(a)、(b)は、第1実施形態の半導体装置の製造方法を説明するための概略斜視図。

【図7】第2実施形態の半導体装置を示す概略平面図。

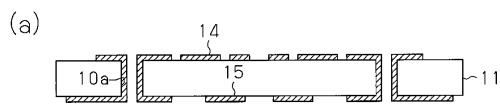

【図8】(a)～(c)は第2実施形態の半導体装置を示す概略断面図。

【図9】変形例の半導体装置を示す概略断面図。

【図10】変形例の半導体装置を示す概略断面図。

【図11】変形例の半導体装置を示す概略断面図。

【図12】(a)、(b)は、従来の配線基板の製造方法を説明するための概略断面図。

【図13】(a)～(d)は、従来の配線基板の製造方法を説明するための概略断面図。

【図14】従来の配線基板を示す概略斜視図。

【図15】(a)、(b)は、従来の配線基板を示す概略平面図。

【発明を実施するための形態】

【0018】

以下、添付図面を参照して各実施形態を説明する。尚、添付図面は、構造の概略を説明するためのものであり、実際の大きさを表していない。

(第1実施形態)

以下、第1実施形態を図1～図6に従って説明する。なお、本実施形態において、先の図12～図15で示した従来と同様な構成部分については同一符号を付して説明する。

【0019】

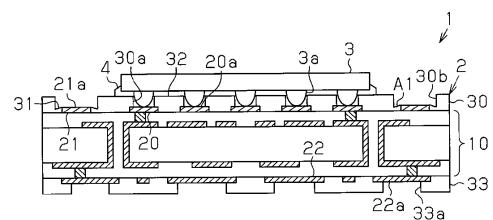

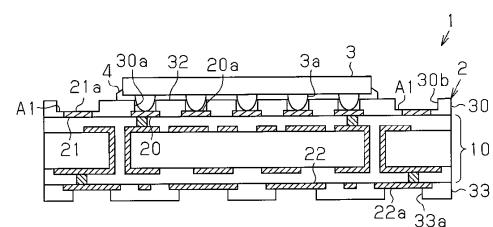

図1(a)は、本実施形態の半導体装置1の概略平面図であり、図1(b)は、図1(a)に示す半導体装置1のA-A概略断面図である。図2は、半導体装置1の一部を示す概略斜視図である。

【0020】

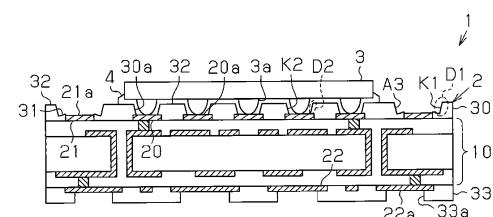

図1(a)及び図1(b)に示すように、本実施形態の半導体装置1は、配線基板2と、半導体チップ3と、アンダーフィル樹脂4とを有する。

図1(b)に示すように、配線基板2は、基板本体10と、最上層の配線パターン20, 21(最上層配線)と、最下層の配線パターン22と、ソルダレジスト層30, 33とを有する。なお、この配線基板2に実装される半導体チップ3は、その回路形成面(図1(b)において下面)に、マトリクス状に配設された複数のバンプ3aを備えている。

【0021】

基板本体10は、コア基板11と、複数の絶縁層12, 13と、複数の絶縁層12, 13に形成された配線14, 15及びビア16, 17等から構成されている。基板本体10に設けられた配線14, 15及びビア16, 17は、配線パターン20及び配線パターン22を電気的に接続している。なお、配線14, 15やビア16, 17の材料としては、例えば銅(Cu)を用いることができる。また、絶縁層12, 13の材料としては、例えばエポキシ系樹脂やポリイミド系樹脂の絶縁樹脂を用いることができる。

【0022】

配線パターン20は、基板本体10のチップ実装面側(図1(b)において上面側)に設けられている。この配線パターン20は、半導体チップ3のバンプ3aが接続されるパッド20aを有する。この配線パターン20の平面形状は、例えば円形状に形成されている(図1(a)参照)。

【0023】

配線パターン21は、基板本体10のチップ実装面側に設けられている。この配線パターン21は、その上面の全てがソルダレジスト層30から露出されることで認識マーク21aとなるパターンである。また、配線パターン21(認識マーク21a)の平面形状は、図1(a)に示すように、例えばT字状や三角形状に形成されている。この配線パターン21と上記配線パターン20とは、同じ厚さで形成されている。これら配線パターン20, 21の材料としては、例えば銅を用いることができる。なお、配線パターン20, 21は、銅層の表面に所要のめっき(例えば、ニッケルめっきや金めっき等)を施して形成するようにしてもよい。

## 【0024】

図1(b)に示すように、配線パターン22は、基板本体10のチップ実装面と反対側(図1(b)において下面側)に設けられている。この配線パターン22は、マザーボード等の実装基板と接続される外部接続端子を配設するための外部接続用パッド22aを有する。なお、配線パターン22の材料としては、例えば銅を用いることができる。

## 【0025】

ソルダレジスト層30は、配線パターン20, 21を覆うように基板本体10のチップ実装面側に設けられている。ソルダレジスト層30の材料としては、例えばエポキシ系の絶縁性樹脂を用いることができる。このソルダレジスト層30には、上記パッド20aとなる配線パターン20の一部を露出させるための複数の開口部30aが形成されるとともに、配線パターン21の上面の全てを露出させるための凹部30bが形成されている。また、このソルダレジスト層30は、凹部30bに対応する領域に形成されたソルダレジスト層31と、凹部30b以外の領域に形成されたソルダレジスト層32とを含む。換言すると、ソルダレジスト層30は、図1及び図2に示すように、凹部30bの底面A1となるソルダレジスト層31と、凹部30bの縁部A2となるソルダレジスト層32とを含む。これらソルダレジスト層31とソルダレジスト層32とは一体に形成されている。

10

## 【0026】

ここで、上記開口部30aの形状について図1に従って説明する。まず、本実施形態では半導体チップ3のバンプ3aがマトリクス状に配設されているため、その配設形態に応じてパッド20aも配線基板2のチップ実装領域CAにマトリクス状に配列されている(図1(a)参照)。このため、複数の開口部30aもチップ実装領域CA内にマトリクス状に形成されている。また、各開口部30aの平面形状は、配線パターン20と同様に、円形状に形成されている。さらに言うと、各開口部30aの平面形状は、配線パターン20の一部を露出させるように、配線パターン20の平面形状よりも小さく形成されている。そして、このような開口部30aによって、配線パターン20の一部がパッド20aとしてソルダレジスト層30から露出されている。

20

## 【0027】

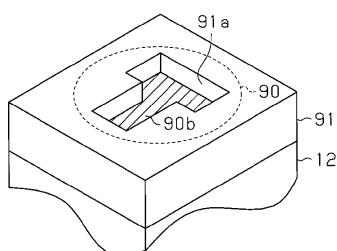

続いて、上記凹部30bの形状について以下に説明する。まず、本実施形態の認識マーク21aは、ソルダレジスト層30の下層の配線パターン21によってその形状が所望の形状に形成されている。すなわち、認識マーク21aの所望の形状がT字状である場合には、配線パターン21の平面形状がT字状に形成されている。また、認識マーク21aの所望の形状が三角形状である場合には、配線パターン21の平面形状が三角形状に形成されている。そして、上記凹部30bは、図1及び図2に示すように、この配線パターン21の上面の全てを露出させるように、その平面形状が配線パターン21の平面形状よりも大きく形成されている。具体的には、凹部30bの平面形状は、配線パターン21の平面形状よりも大きな面積を有する四角形状に形成されている。

30

## 【0028】

このような形状の凹部30bでは、配線パターン21の上面の全てが認識マーク21aとして露出されるとともに、認識マーク21a以外の部分にはソルダレジスト層31が形成されている。このため、配線パターン21の平面形状が認識マーク21aの形状となる。ここで、配線パターン21は、その所望の平面形状が鋭角や直角な角を有する形状であっても、フォトリソグラフィ法などによってその所望の平面形状に容易に形成することができる。したがって、このような配線パターン21の上面が全て露出されれば、プラスト法によって凹部30bが所望の形状に形成できない場合であっても、認識マーク21aを所望の形状に形成することができる。

40

## 【0029】

また、上記凹部30bでは、配線パターン21の側壁に接するようにソルダレジスト層31(ソルダレジスト層30)が形成されている。換言すると、認識マーク21aの周囲はソルダレジスト層31(ソルダレジスト層30)によって覆われている。そして、このソルダレジスト層31の上面(凹部30bの底面A1)には、認識マーク21aの端部か

50

ら凹部 30b の側壁部 A3 に向かって湾曲状に凹む湾曲部 31a が形成されている。このような湾曲部 31a によって、認識マーク 21a の認識性を向上させることができる。例えば、認識マーク 21a は、一定強度の光が認識マーク 21a やソルダレジスト層 31 等の表面に照射され、その表面で反射されて受光部に入射される光の強度（反射光強度）に応じて検出される。この場合において、認識マーク 21a の表面では反射光が特定の方向（受光部に向かう方向）に効率良く反射されるために受光部での反射光強度が強くなるのに対し、上記湾曲部 31a では反射光が特定の方向に反射されないために受光部での反射光強度が弱くなる。これにより、認識マーク 21a とソルダレジスト層 31 における反射光強度の差が大きくなるため、認識マーク 21a とソルダレジスト層 31 との境界部分（図 1 (b) の破線枠参照）が強調される。したがって、認識マーク 21a の輪郭（形状）が認識し易くなるため、認識マーク 21a の認識性を向上させることができる。10

#### 【0030】

さらに、凹部 30b と認識マーク 21a の関係について詳述すると、凹部 30b の底面 A1（ソルダレジスト層 31 の上面）は、認識マーク 21a の上面よりも高く形成されるとともに、凹部 30b の縁部 A2（ソルダレジスト層 32 の上面）よりも低く形成されている。また、凹部 30b の底面 A1 の表面粗度（ソルダレジスト層 31 の上面の表面粗度）は、認識マーク 21a の上面の表面粗度よりも高く、凹部 30b の縁部 A2 の表面粗度（ソルダレジスト層 32 の上面の表面粗度）よりも高くなっている。このようなソルダレジスト層 31 と認識マーク 21a との表面粗度の違いによっても、認識マーク 21a の認識性を向上させることができる。すなわち、表面粗度が高い部分では照射された光が乱反射されて反射光強度が弱くなるため、上記表面粗度の違いによって、ソルダレジスト層 31 と認識マーク 21a における反射光強度の差が大きくなる。これにより、認識マーク 21a の輪郭（形状）が認識し易くなるため、認識マーク 21a の認識性を向上させることができる。20

#### 【0031】

図 1 (b) に示すように、外部接続用パッド 22a は、基板本体 10 の下面側に形成されたソルダレジスト層 33 の開口部 33a から配線パターン 22 の一部が露出されることで形成されている。

#### 【0032】

半導体チップ 3 は、このように構成された配線基板 2 にフリップチップ接合される。すなわち、半導体チップ 3 は、回路形成面に配設されたバンプ 3a を介して、配線基板 2 のパッド 20a と電気的に接続される。30

#### 【0033】

アンダーフィル樹脂 4 は、配線基板 2 と半導体チップ 3 との隙間を充填するように設けられている。このアンダーフィル樹脂 4 は、バンプ 3a とパッド 20a との接続部分の接続強度を向上させると共に、配線パターン 20 の腐食やエレクトロマイグレーションの発生を抑制し、配線パターン 20 の信頼性の低下を防ぐための樹脂である。なお、アンダーフィル樹脂 4 の材料としては、例えばエポキシ樹脂を用いることができる。

#### 【0034】

次に、このように構成された半導体装置 1 の製造方法を図 3 ~ 図 6 に従って説明する。40

まず、配線基板 2 の製造方法について説明する。図 3 ~ 図 5 (b) に示す配線基板 2 の製造方法では、図 3 (a) に示すコア基板 11 を用いる。なお、このコア基板 11 は、例えば銅張積層板（Copper Clad Laminated : CCL）にスルーホール 10a を形成し、スルーホール 10a の側面にめっきを施すことで両面を導通させた後、サブトラクティブ法により配線 14, 15 を形成することによって製造される。

#### 【0035】

このコア基板 11 の両面側に、図 3 (b) に示すように絶縁層 12, 13 を形成する。次に、図 3 (c) に示すように、配線 14, 15 の端部が露出されるように、絶縁層 12, 13 の所定箇所にそれぞれ開口部 12a, 13a を、例えばレーザによって形成する。

#### 【0036】

10

20

30

40

50

続いて、デスマニア処理後、図3(d)に示すように、絶縁層12及び配線14を覆うようにシード層S1を形成するとともに、絶縁層13及び配線15を覆うようにシード層S2を形成する。これらシード層S1, S2は、無電解銅めっき又はスパッタリングによって形成される。

#### 【0037】

次に、図4(a)に示すように、例えばセミアディティブ法により配線パターン20, 21, 22及びビア16, 17を形成する(配線層形成工程)。すなわち、シード層S1上に配線パターン20, 21の形状に対応した開口パターン40aを有するドライフィルムレジスト(DFR)40をフォトリソグラフィ法により形成し、上記シード層S1を給電層とする電解銅めっきによって配線パターン20, 21及びビア16を形成する。これにより、所望の形状(本例では、円形状)の配線パターン20と、所望の形状(本例では、T字状及び三角形状)の配線パターン21が形成される。このとき、図6(a)に示すように、配線パターン21の形状を決定するDFR40の開口パターン40aはフォトリソグラフィ法によって形成されるため、配線パターン21の所望の形状が鋭角な角を有する形状であっても、その形状に対応した開口パターン40aを精度良く形成することができる。すなわち、配線パターン21の所望の平面形状がT字状である場合には、平面形状がT字状の開口パターン40aを精度良く形成することができる。したがって、図6(b)に示すように、配線パターン21の形状を所望の形状に精度良く形成することができる。なお、配線パターン22やビア17も、上記配線パターン20, 21及びビア16と同様に形成される。

10

20

#### 【0038】

このように配線パターン20, 21, 22及びビア16, 17が形成されると、図4(b)に示すように、DFR40及び不要なシード層S1, S2が除去される。

次に、図4(c)に示すように、基板本体10の上面側に形成された配線パターン20, 21を覆うようにソルダレジスト層30を形成するとともに(絶縁層形成工程)、基板本体の下面側に形成された配線パターン22を覆うようにソルダレジスト層33を形成する。これらソルダレジスト層30, 33は、液状レジストを用いる場合には、スクリーン印刷法、スプレーコート法やロールコート法などの方法により形成することができる。また、フィルム状のソルダレジストを基板本体10の上面及び下面にラミネートすることで、上記ソルダレジスト層30, 33を形成することもできる。なお、このときのソルダレジスト層30, 33の厚さは、例えば25μmとすることができます。また、配線パターン20, 21の材料として銅を用いた場合には、配線パターン20, 21の厚さは、例えば15μmとすることができます。

30

#### 【0039】

次に、図4(d)に示すように、ソルダレジスト層30上に貼り付けたドライフィルムレジストを露光・現像によりパターニングして、上記開口部30aに対応する開口部41aと、上記凹部30bに対応する開口部41bを持つサンドブラスト保護用のマスク41を形成する。すなわち、パッド20aと対向する位置に形成される、開口部30aと同様の平面形状(円形状)の開口部41aと、配線パターン21と対向する位置に形成される、凹部30bと同様の平面形状(四角形状)の開口部41bとを持つマスク41を形成する。このため、各開口部41aの平面形状は配線パターン20の平面形状よりも小さく形成され、各開口部41bの平面形状は配線パターン21の平面形状よりも大きく形成される。これにより、ソルダレジスト層30のうち、配線パターン21と対向する領域であって、配線パターン21の平面形状よりも大きい領域のソルダレジスト層30を薄化するための開口部41bを有するマスク41が形成される。また、ソルダレジスト層33上に貼り付けたドライフィルムレジストを露光・現像によりパターニングして、上記開口部33aに対応する開口部42aを持つサンドブラスト保護用のマスク42を形成する。

40

#### 【0040】

続いて、図5(a)に示すように、マスク41の開口部41a, 41bを通じてソルダレジスト層30にサンドブラスト法を施す(ブラスト工程)。すなわち、マスク41の開

50

口部 4 1 a , 4 1 b に砥粒 4 3 を吹き付けてソルダレジスト層 3 0 (ソルダレジスト層 3 1) を所定の厚さまで薄化する。具体的には、図 5 (a) に示すように、マスク 4 1 の開口部 4 1 a に対向するソルダレジスト層 3 0 が除去されるまでソルダレジスト層 3 0 にサンドブラスト法を施す。これにより、ソルダレジスト層 3 0 に開口部 3 0 a が形成されるとともに、その開口部 3 0 a から配線パターン 2 0 の一部がパッド 2 0 a として露出される。

#### 【 0 0 4 1 】

また、薄化されるソルダレジスト層 3 1 の上面が配線パターン 2 1 (認識マーク 2 1 a) の上面よりも低くなるように、マスク 4 1 の開口部 4 1 b を通じてソルダレジスト層 3 1 を削る。このソルダレジスト層 3 1 の薄化が進み、配線パターン 2 1 の上面がソルダレジスト層 3 1 から露出されると、この配線パターン 2 1 にも砥粒 4 3 が吹き付けられる。このとき、配線パターン 2 1 は金属であり、ソルダレジスト層 3 1 よりも硬いため、ソルダレジスト層 3 1 よりも削られにくい。但し、配線パターン 2 1 は、砥粒の噴射によってその表面がダメージを受けて広がる。このため、配線パターン 2 1 付近のソルダレジスト層 3 1 は、配線パターン 2 1 から離れたソルダレジスト層 3 1 よりも削られにくくなる。これにより、薄化されたソルダレジスト層 3 1 には、配線パターン 2 1 端部からソルダレジスト層 3 1 , 3 2 間の境界部分に向かって湾曲状に凹む湾曲部 3 1 a が形成される。換言すると、このサンドブラスト処理では、ソルダレジスト層 3 1 に上記湾曲部 3 1 a が形成されるまでソルダレジスト層 3 1 が薄化される。そして、このような薄化工程 (図 4 (d) 及び図 5 (a) 参照) によって、ソルダレジスト層 3 0 に凹部 3 0 b が形成されるとともに、その凹部 3 0 b から配線パターン 2 1 の上面の全てが認識マーク 2 1 a として露出される。さらに、配線パターン 2 1 の側壁 (周囲) に薄化されたソルダレジスト層 3 1 が形成されるとともに、そのソルダレジスト層 3 1 の上面の表面粗度 (凹部 3 0 b の底面 A 1 の表面粗度) がソルダレジスト層 3 2 の上面の表面粗度 (凹部 3 0 b の縁部 A 2 の表面粗度) よりも高くなる。例えば、薄化されていないソルダレジスト層 3 2 の表面粗度は 5 0 nm 程度であるのに対し、薄化後のソルダレジスト層 3 1 の表面粗度は 4 0 0 nm 程度になる。

#### 【 0 0 4 2 】

なお、基板本体 1 0 の下面側に形成されたソルダレジスト層 3 3 に対しても同様に、マスク 4 2 の開口部 4 2 a を通じてサンドブラスト法を施す。具体的には、マスク 4 2 の開口部 4 2 a に対向するソルダレジスト層 3 3 が除去されるまでソルダレジスト層 3 3 にサンドブラスト法を施す。これにより、ソルダレジスト層 3 3 に開口部 3 3 a が形成されるとともに、その開口部 3 3 a から配線パターン 2 2 の一部が外部接続用パッド 2 2 a として露出される。

#### 【 0 0 4 3 】

その後、図 5 (b) に示すように、マスク 4 1 , 4 2 を除去し、パッド 2 0 a , 2 2 a 及び配線パターン 2 1 の表面を、ソフトエッチング (例えば C u ソフトエッチング) することにより清浄にする (エッチング工程)。このとき、配線パターン 2 1 の上面が凹部 3 0 b の底面 A 1 (配線パターン 2 1 の側壁に接するソルダレジスト層 3 1 の上面) よりも低くなるまで配線パターン 2 1 をエッチングする。これにより、ソルダレジスト層 3 1 から露出される認識マーク 2 1 a が形成される。なお、この表面処理後の認識マーク 2 1 a の上面の表面粗度は、例えば 3 0 0 nm 程度となり、ソルダレジスト層 3 1 の上面の表面粗度よりも低くなる。以上の製造工程により、本実施形態の配線基板 2 を製造することができる。

#### 【 0 0 4 4 】

次に、上述のように製造された配線基板 2 に半導体チップ 3 を実装する方法を説明する。図 5 (c) に示すように、配線基板 2 のパッド 2 0 a 上に、半導体チップ 3 のバンプ 3 a をフリップチップ接合する。続いて、図 5 (d) に示すように、フリップチップ接合された半導体チップ 3 と配線基板 2 との間に、アンダーフィル樹脂 4 を充填し、そのアンダーフィル樹脂 4 を硬化する。以上の製造工程により、本実施形態の半導体装置を製造する

10

20

30

40

50

ことができる。

【0045】

以上説明した本実施形態によれば、以下の効果を奏することができる。

(1) ソルダレジスト層30から上面の全てが露出されることで認識マーク21aとなる配線パターン21と、その配線パターン21の上面を全て露出させるための凹部30bを有するソルダレジスト層30とを形成するようにした。これにより、ソルダレジスト層30から露出される配線パターン21の上面の形状(平面形状)が認識マーク21aの形状となる。ここで、配線パターン21は、その所望の平面形状が鋭角や直角な角を有する形状であっても、フォトリソグラフィ法などによってその所望の平面形状に容易に形成することができる。したがって、このような配線パターン21の上面が全て露出されれば、プラスト法によって凹部30bが所望の形状(四角形状)に形成できない場合、つまり凹部30bの四隅が丸まった形状になった場合であっても、認識マーク21aを所望の形状に形成することができる。この結果、認識マーク21aの認識性が低下することを抑制することができる。

【0046】

また、認識マーク21aを露出させるための凹部30bをプラスト法によって形成することができるため、ソルダレジスト層30として非感光性樹脂(熱硬化性樹脂等)を採用することができる。このため、ソルダレジスト層30における耐熱性や耐薬品性といった信頼性を、ソルダレジスト層30として感光性樹脂を採用する場合に比べて向上させることができる。

【0047】

(2) 凹部30bの底面A1の表面粗度(ソルダレジスト層31の上面の表面粗度)を、認識マーク21aの上面の表面粗度よりも高くなるようにした。これにより、例えば認識マーク21a等の表面で反射される反射光強度によって認識マーク21aを検出する場合に、認識マーク21aとソルダレジスト層31とにおける反射光強度の差を大きくすることができる。この結果、認識マーク21aとソルダレジスト層31との境界部分、すなわち認識マーク21aの輪郭が強調されるため、認識マーク21aの認識性を向上させることができる。

【0048】

(3) 凹部30bの底面A1(ソルダレジスト層31の上面)に、認識マーク21aの端部から凹部30bの側壁部A3に向かって湾曲状に凹む湾曲部31aを形成するようにした。これにより、例えば認識マーク21a等の表面で反射される反射光強度によって認識マーク21aを検出する場合に、認識マーク21aとソルダレジスト層31とにおける反射光強度の差を大きくすることができる。この結果、認識マーク21aとソルダレジスト層31との境界部分、すなわち認識マーク21aの輪郭が強調されるため、認識マーク21aの認識性を向上させることができる。

【0049】

(4) 認識マーク21aを、その上面が凹部30bの底面A1よりも低くなるように形成した。例えばソルダレジスト層30に凹部30bを形成する際に、図5(a)に示すように、サンドブラスト処理による加工ダメージ等によって配線パターン21の上面が変形し、その配線パターン21の平面形状が所望の形状よりも大きくなる場合がある。このような配線パターン21を認識マーク21aとすると、その認識マーク21aの認識性が低下してしまう。これに対し、上述のように認識マーク21aの上面を凹部30bの底面A1よりも低く形成することにより、加工ダメージ等によって配線パターン21が変形しても、図5(b)に示すように配線パターン21の平面形状を所望の形状に戻すことができる。したがって、認識マーク21aの認識性が低下することを抑制することができる。

【0050】

(5) パッド20aとなる配線パターン20と、認識マーク21aとなる配線パターン21と同じ厚さで形成するようにした。これにより、配線パターン20, 21を同一工程で同時に形成することができ(図4(a)参照)、さらにパッド20aと認識マーク2

10

20

30

40

50

1 a とを同一工程で形成することができる（図 5 ( a )、( b )参照）。

【0051】

（第 2 実施形態）

以下、第 2 実施形態を図 7 及び図 8 に従って説明する。なお、先の図 1 ~ 図 6 に示した部材と同一の部材にはそれぞれ同一の符号を付して示し、それら各要素についての詳細な説明は省略する。

【0052】

上記第 1 実施形態では、マトリクス状に配設されたパッド 20 a を有する配線基板 2 について説明した。これに対し、本実施形態では、ペリフェラル状に配設されたパッドを有する配線基板について説明する。

10

【0053】

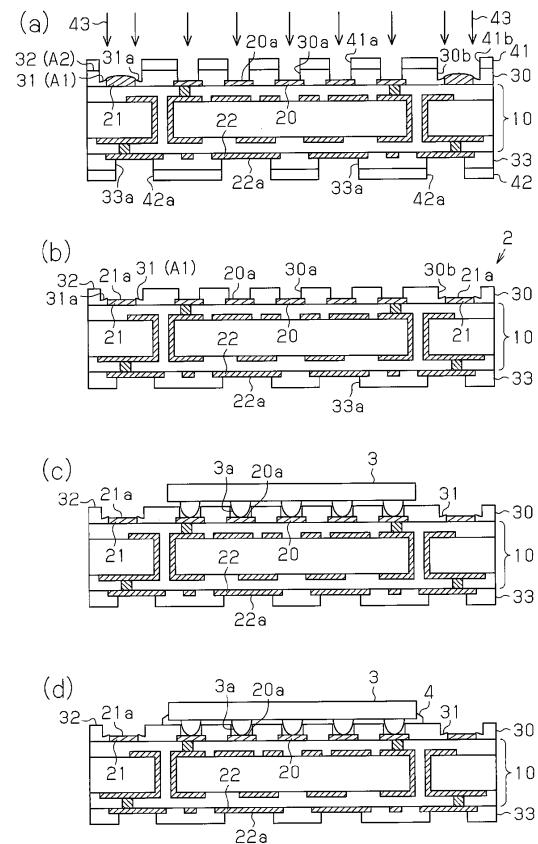

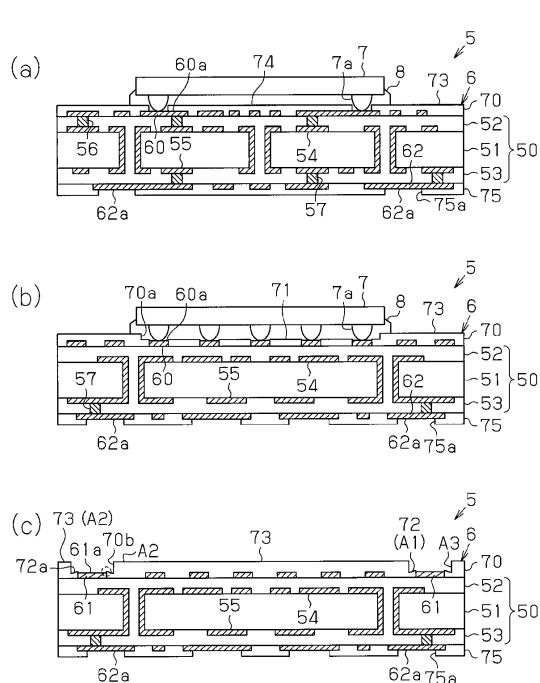

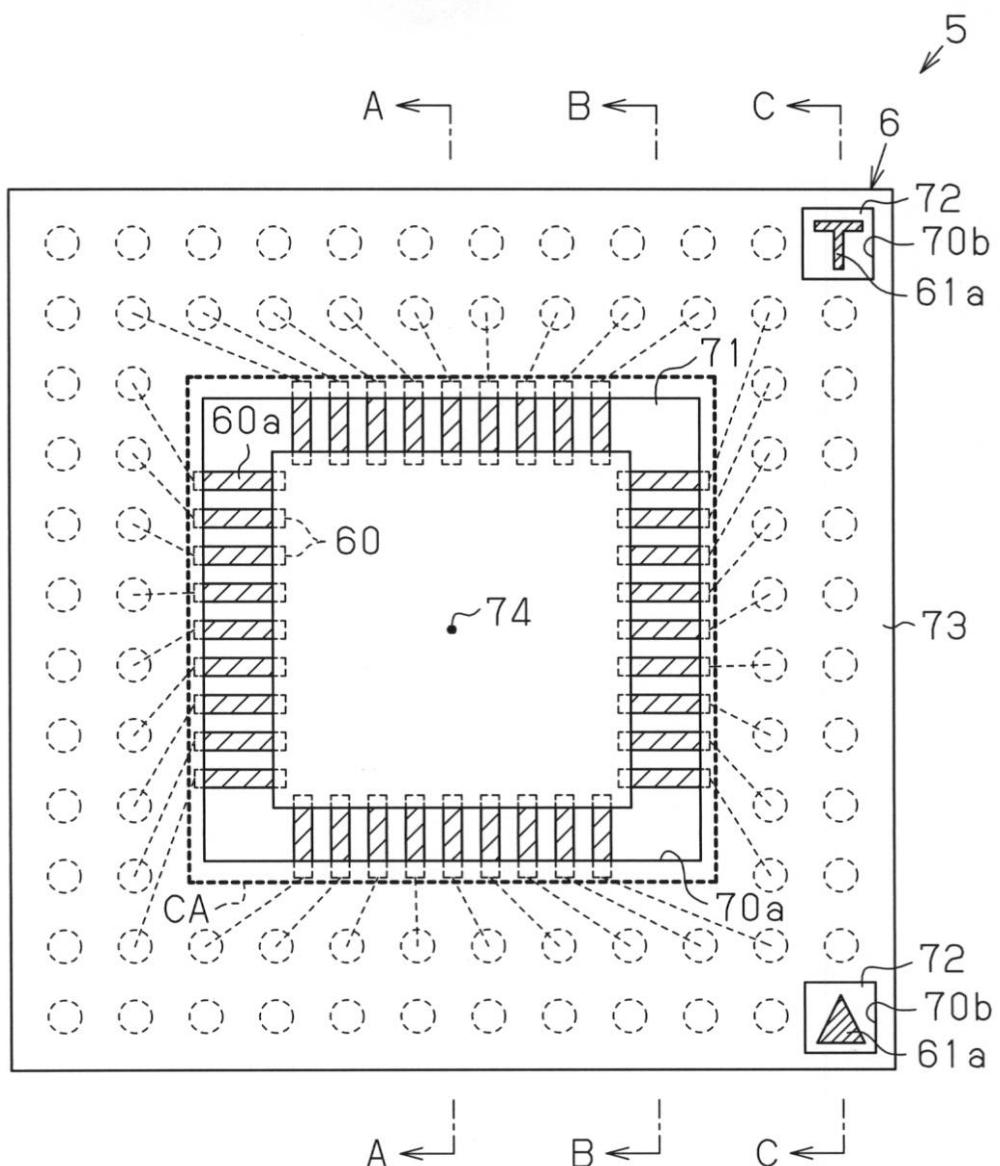

図 7 は、本実施形態の半導体装置 5 の概略平面図である。また、図 8 ( a ) は、図 7 に示す半導体装置 5 の A - A 概略断面図であり、図 8 ( b ) は、図 7 に示す半導体装置 5 の B - B 概略断面図であり、図 8 ( c ) は、図 7 に示す半導体装置 5 の C - C 概略断面図である。

【0054】

図 7 及び図 8 ( a ) ~ ( c ) に示すように、本実施形態の半導体装置 5 は、配線基板 6 と、半導体チップ 7 と、アンダーフィル樹脂 8 とを有する。

図 8 ( a ) ~ ( c ) に示すように、配線基板 6 は、基板本体 50 と、最上層の配線パターン 60, 61 (最上層配線) と、最下層の配線パターン 62 と、ソルダレジスト層 70, 75 とを有する。なお、この配線基板 6 に実装される半導体チップ 7 は、その回路形成面（図 8 において下面）に、ペリフェラル状（チップ外周に沿った環状の形態）に配設された複数のバンプ 7 a を備えている（破線参照）。

20

【0055】

基板本体 50 は、コア基板 51 と、複数の絶縁層 52, 53 と、複数の絶縁層 52, 53 に形成された配線 54, 55 及びビア 56, 57 等から構成されている。基板本体 50 に設けられた配線 54, 55 及びビア 56, 57 は、配線パターン 60 及び配線パターン 62 を電気的に接続している。なお、配線 54, 55 やビア 56, 57 の材料としては、例えば銅 (Cu) を用いることができる。また、絶縁層 52, 53 の材料としては、例えばエポキシ系樹脂やポリイミド系樹脂の絶縁樹脂を用いることができる。

30

【0056】

配線パターン 60 は、基板本体 50 のチップ実装面側（図 8 ( a ) において上面側）に設けられている。この配線パターン 60 は、半導体チップ 7 のバンプ 7 a が接続されるパッド 60 a を有する。この配線パターン 60 の平面形状は、例えば矩形状に形成されている（図 7 参照）。

【0057】

配線パターン 61 は、基板本体 50 のチップ実装面側に設けられている。この配線パターン 61 は、その上面の全てがソルダレジスト層 70 から露出されることで認識マーク 61 a となるパターンである。また、配線パターン 61 (認識マーク 61 a) の平面形状は、図 7 に示すように、例えば T 字状や三角形状に形成されている。この配線パターン 61 と上記配線パターン 60 とは、同じ厚さで形成されている。これら配線パターン 60, 61 の材料としては、例えば銅を用いることができる。なお、配線パターン 60, 61 は、銅層の表面に所要のめっき（例えば、ニッケルめっきや金めっき等）を施して形成するようにしてよい。

40

【0058】

図 8 に示すように、配線パターン 62 は、基板本体 50 のチップ実装面と反対側（図 8 において下面側）に設けられている。この配線パターン 62 は、マザーボード等の実装基板と接続される外部接続端子を配設するための外部接続用パッド 62 a を有する。なお、配線パターン 62 の材料としては、例えば銅を用いることができる。

【0059】

50

ソルダレジスト層70は、配線パターン60, 61を覆うように基板本体50のチップ実装面側に設けられている。ソルダレジスト層70の材料としては、例えばエポキシ系の絶縁性樹脂を用いることができる。このソルダレジスト層70には、上記パッド60aとなる配線パターン60の一部を露出させるための凹部70aが形成されるとともに、配線パターン61の上面の全てを露出させるための凹部70bが形成されている。また、このソルダレジスト層70は、凹部70aに対応する領域に形成されたソルダレジスト層71と、凹部70bに対応する領域に形成されたソルダレジスト層72と、凹部70aよりも外側領域に形成されたソルダレジスト層73と、凹部70aよりも内側領域に形成されたソルダレジスト層74とを含む。換言すると、ソルダレジスト層72は凹部70bの底面A1となり、ソルダレジスト層73は凹部70bの縁部A2となる。これらソルダレジスト層71とソルダレジスト層72とソルダレジスト層73とソルダレジスト層74とは一体に形成されている。

#### 【0060】

ここで、上記凹部70aの形状について以下に説明する。まず、本実施形態では半導体チップ7のバンプ7aがペリフェラル状に配設されているため、その配設形態に応じて配線基板6に形成されるパッド60aも配線基板6の外周に沿って環状に配列されている(図7参照)。すなわち、上記パッド形成領域がチップ実装領域CAに沿って環状に形成されている。このため、上記凹部70aもチップ実装領域CAに沿って環状に形成され、且つ帯状に形成されている。この凹部70aは、例えば第1実施形態の開口部30aの形成方法と同様にサンドブラスト法によって、凹部70aに対応する部分のソルダレジスト層71が、その他の部分のソルダレジスト層73, 74よりも薄化されることで形成されている。

#### 【0061】

このような凹部70aでは、配線パターン60の一部がパッド60aとして露出されるとともに(図8(a)参照)、パッド60a以外の部分にはソルダレジスト層71が形成されている(図8(b)参照)。このため、図8(b)に示すように、隣接するパッド60a間にはソルダレジスト層71が形成されている。さらに言うと、このソルダレジスト層71は、図8(b)に示すように、その上面がパッド60aの上面よりも高く形成されている。その一方で、ソルダレジスト層71は、その上面がソルダレジスト層73, 74の上面よりも低く形成されている。

#### 【0062】

続いて、上記凹部70bの形状について以下に説明する。まず、本実施形態の認識マーク61aは、ソルダレジスト層70の下層の配線パターン61によってその形状が所望の形状に形成されている。すなわち、認識マーク61aの所望の形状がT字状である場合には、配線パターン61の平面形状がT字状に形成されている。また、認識マーク61aの所望の形状が三角形状である場合には、配線パターン61の平面形状が三角形状に形成されている。そして、上記凹部70bは、図7に示すように、この配線パターン61の上面の全てを露出させるように、その平面形状が配線パターン61の平面形状よりも大きく形成されている。具体的には、凹部70bの平面形状は、配線パターン61の平面形状よりも大きな面積を有する四角形状に形成されている。この凹部70bは、上記凹部70aと同様に、例えばサンドブラスト法によって、凹部70bに対応する部分のソルダレジスト層72が、その他の部分のソルダレジスト層73よりも薄化されることで形成されている。

#### 【0063】

このような凹部70bでは、配線パターン61の上面が認識マーク61aとして露出されるとともに、認識マーク61a以外の部分にはソルダレジスト層72が形成されている。このため、配線パターン61の平面形状が認識マーク61aの形状となる。また、配線パターン61の側壁に接するようにソルダレジスト層72(ソルダレジスト層70)が形成されている。換言すると、認識マーク61aの周囲はソルダレジスト層72(ソルダレジスト層70)によって覆われている。そして、このソルダレジスト層72(凹部70b

10

20

30

40

50

の底面 A 1 ) には、認識マーク 6 1 a の端部から凹部 7 0 b の側壁部 A 3 に向かって湾曲状に凹む湾曲部 7 2 a が形成されている。

【 0 0 6 4 】

さらに、凹部 7 0 b と認識マーク 6 1 a の関係について詳述すると、凹部 7 0 b の底面 A 1 ( ソルダレジスト層 7 2 の上面 ) は、認識マーク 6 1 a の上面よりも高く形成されるとともに、凹部 7 0 b の縁部 A 2 ( ソルダレジスト層 7 3 の上面 ) よりも低く形成されている。また、凹部 7 0 b の底面 A 1 の表面粗度 ( ソルダレジスト層 7 2 の上面の表面粗度 ) は、認識マーク 6 1 a の上面の表面粗度よりも高く、凹部 7 0 b の縁部 A 2 の表面粗度 ( ソルダレジスト層 7 3 の上面の表面粗度 ) よりも高くなっている。

【 0 0 6 5 】

図 8 に示すように、外部接続用パッド 6 2 a は、基板本体 5 0 のチップ実装面と反対側 ( 図 8 において下面側 ) に形成されたソルダレジスト層 7 5 から露出するように設けられている。この外部接続用パッド 6 2 a は、マザーボード等の実装基板と接続される外部接続端子を配設するためのパッドである。

【 0 0 6 6 】

図 8 ( a ) 、 ( b ) に示すように、半導体チップ 7 は、このように構成された配線基板 6 にフリップチップ接合される。すなわち、半導体チップ 7 は、回路形成面に配設されたバンプ 7 a を介して、配線基板 6 のパッド 6 0 a と電気的に接続される。

【 0 0 6 7 】

アンダーフィル樹脂 8 は、配線基板 6 と半導体チップ 7 との隙間を充填するように設けられている。なお、アンダーフィル樹脂 8 の材料としては、例えばエポキシ樹脂を用いることができる。

【 0 0 6 8 】

以上説明した本実施形態によれば、上記第 1 実施形態と同様の効果を奏する。

( 他の実施形態 )

なお、上記実施形態は、これを適宜変更した以下の態様にて実施することもできる。

【 0 0 6 9 】

・上記各実施形態では、認識マーク 2 1 a , 6 1 a の上面を凹部 3 0 b , 7 0 b の底面 A 1 よりも低くなるように形成した。これに限らず、例えば図 9 に示されるように、認識マーク 2 1 a の上面を凹部 3 0 b の底面 A 1 と面一になるように形成するようにしてもよい。

【 0 0 7 0 】

・上記各実施形態では、凹部 3 0 b の底面 A 1 に湾曲部 3 1 a を形成するようにし、凹部 7 0 b の底面 A 1 に湾曲部 7 2 a を形成するようにした。これに限らず、例えば図 1 0 に示されるように、凹部 3 0 b の底面 A 1 における湾曲部 3 1 a の形成を省略してもよい。

【 0 0 7 1 】

・図 1 1 に示されるように、上記第 1 実施形態におけるソルダレジスト層 3 1 , 3 2 によって形成される段差部 D 1 が傾斜部 K 1 を有するように形成してもよい。すなわち、凹部 3 0 b の側壁部 A 3 が傾斜面となるように形成してもよい。さらに、上記傾斜部 K 1 が曲面を有するように段差部 D 1 を形成するようにしてもよい。なお、パッド 2 0 a とソルダレジスト層 3 2 によって形成される段差部 D 2 についても、傾斜部 K 2 を有するように形成してもよい。また、上記第 2 実施形態についても同様である。

【 0 0 7 2 】

・上記各実施形態における認識マーク 2 1 a , 6 1 a を形成するための凹部 3 0 b , 7 0 b の平面形状は、配線パターン 2 1 , 6 1 の上面の全てを露出させることのできる形状であれば特に制限されない。例えば、凹部 3 0 b , 7 0 b の平面形状を円形状としてもよい。

【 0 0 7 3 】

・上記各実施形態では、サンドブラスト処理によりソルダレジスト層 3 0 , 7 0 の薄化

10

20

30

40

50

(除去)を行ったが、これに限定されない。例えばサンドブラスト処理以外の各種ブラスト処理(ウェットブラスト処理等)によりソルダレジスト層30,70の薄化を行うようにしてもよい。また、例えば樹脂エッチングやレーザ加工法などによりソルダレジスト層30,70の薄化を行うようにしてもよい。

【0074】

・上記各実施形態におけるパッド20a,60aを形成するための開口部30a及び凹部70aの形状については特に制限されない。例えば配線パターン20,60の全てをパッド20a,60aとして露出させるように開口部30a及び凹部70aを形成するようにしてもよい。

【0075】

・上記第1実施形態では、ソルダレジスト層30上に貼り付けたドライフィルムレジストを露光・現像によりパターニングして、開口部41a,41bを持つサンドブラスト保護用のマスク41を形成するようにした。これに限らず、例えばマスク41として金属マスクを用いてもよい。また、金属箔を上記ドライフィルムレジストと同様にパターニングしてマスク41を形成するようにしてもよい。

【0076】

・上記各実施形態では、配線基板2,6に半導体チップ3,7をそれぞれ実装する場合について説明したが、被実装体としては半導体チップ3,7に制限されない。例えば配線基板2,6の上に別の配線基板を積み重ねる構造を有するフリップチップ実装タイプのパッケージ(パッケージ・オン・パッケージ)にも、本発明を適用することが可能である。

【0077】

・上記各実施形態において、配線パターン20,60の下層の構造については特に限定されない。例えばコア基板11,51の構造及び材質は特に限定されない。また、コア基板11,51上に形成される下層配線(例えば、上記第1実施形態では配線14,15)とそれを覆う絶縁層(例えば、上記第1実施形態では絶縁層12,13)の層数についても特に限定されない。すなわち、コア基板11,51上に所定数の下層配線とそれを覆う絶縁層を形成してもよい。なお、配線パターン20,60のパターン形状についても特に限定されない。

【0078】

・上記各実施形態における配線パターン20,21(配線パターン60,61)上に形成されるのは、ソルダレジスト層30,70に限定されず、絶縁層であればよい。

【符号の説明】

【0079】

1,5 半導体装置

2,6 配線基板

3,7 半導体チップ

20,60 配線パターン(第2の配線層)

21,61 配線パターン(第1の配線層)

21a,61a 認識マーク

30,70 ソルダレジスト層(絶縁層)

31,72 ソルダレジスト層

32,73 ソルダレジスト層

30b,70b 凹部

A1 凹部の底面

A2 凹部の縁部

A3 凹部の側壁部

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図7】

---

フロントページの続き

(56)参考文献 特開平5-267802(JP,A)

特開2003-258416(JP,A)

特開2004-119947(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 05 K 1 / 02