(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6323938号

(P6323938)

(45) 発行日 平成30年5月16日(2018.5.16)

(24) 登録日 平成30年4月20日(2018.4.20)

(51) Int.Cl.

F 1

|                     |                  |        |         |       |

|---------------------|------------------|--------|---------|-------|

| <b>H03K 19/003</b>  | <b>(2006.01)</b> | H 03 K | 19/003  | 2 3 0 |

| <b>H01L 21/822</b>  | <b>(2006.01)</b> | H 01 L | 27/04   | H     |

| <b>H01L 27/04</b>   | <b>(2006.01)</b> | H 03 K | 19/0175 | 2 2 0 |

| <b>H03K 19/0175</b> | <b>(2006.01)</b> |        |         |       |

請求項の数 4 (全 21 頁)

(21) 出願番号

特願2013-233602 (P2013-233602)

(22) 出願日

平成25年11月12日 (2013.11.12)

(65) 公開番号

特開2014-103664 (P2014-103664A)

(43) 公開日

平成26年6月5日 (2014.6.5)

審査請求日 平成28年11月2日 (2016.11.2)

(31) 優先権主張番号 13/682,604

(32) 優先日 平成24年11月20日 (2012.11.20)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

エヌエックスピー ユーエスエイ インコ

ーポレイテッド

N X P U S A, I n c .

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 マイケル エイ. ストッキンガー

アメリカ合衆国 78750 テキサス州

オースティン ハイビュー ドライブ

11503

審査官 白井 亮

最終頁に続く

(54) 【発明の名称】過渡電磁波耐性を向上させるためのトリガ回路および方法

## (57) 【特許請求の範囲】

## 【請求項1】

方法であって、

集積回路上の過渡電圧増大を検出することと;

前記過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することとを含み、

前記検出することは、検出用の第1の時間値および第2の時間値に依存し、検出用の前記第1の時間値は、前記集積回路の非給電状態に適用可能であり、検出用の前記第2の時間値は、前記集積回路の給電状態に適用可能であり、

検出用の前記第1の時間値および前記第2の時間値は、共通の容量性素子の容量値に応じて決まり、 10

前記制御することは、制御用の第1の時間値および第2の時間値に依存し、前記制御することは、前記クランプデバイスのアクティブ期間にわたって行われ、前記アクティブ期間は、前記集積回路の前記非給電状態について制御用の前記第1の時間値に応じて決まり、前記集積回路の前記給電状態については制御用の前記第2の時間値に応じて決まる、方法。

## 【請求項2】

方法であって、

集積回路上の過渡電圧増大を検出することと;

前記過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することと 20

を含み、

前記検出することは、検出用の第1の時間値および第2の時間値に依存し、

検出用の前記第1の時間値は、前記集積回路の非給電状態に適用可能であり、

検出用の前記第2の時間値は、前記集積回路の給電状態に適用可能であり、

検出用の前記第1の時間値および前記第2の時間値は、共通の容量性素子の容量値に応じて決まり、

前記制御することは、制御用の第1の時間値および第2の時間値に依存し、

前記制御することは、前記クランプデバイスのアクティブ期間にわたって行われ、

前記アクティブ期間は、前記集積回路の前記非給電状態については制御用の前記第1の時間値に応じて決まり、前記集積回路の前記給電状態については制御用の前記第2の時間値に応じて決まり、 10

前記検出することは、過渡電圧増大の速度が検出範囲内にあることに応答して行われ、

前記検出範囲は、前記集積回路の前記非給電状態については検出用の前記第1の時間値に応じて決まり、前記集積回路の前記給電状態については検出用の前記第2の時間値に応じて決まる、方法。

#### 【請求項3】

方法であって、

集積回路上の過渡電圧増大を検出することと；

前記過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することと

20

を含み、

前記検出することは、検出用の第1の時間値および第2の時間値に依存し、

検出用の前記第1の時間値は、前記集積回路の非給電状態に適用可能であり、

検出用の前記第2の時間値は、前記集積回路の給電状態に適用可能であり、

検出用の前記第1の時間値および前記第2の時間値は、共通の容量性素子の容量値に応じて決まり、

前記制御することは、制御用の第1の時間値および第2の時間値に依存し、

前記制御することは、前記クランプデバイスのアクティブ期間にわたって行われ、

前記アクティブ期間は、前記集積回路の前記非給電状態については制御用の前記第1の時間値に応じて決まり、前記集積回路の前記給電状態については制御用の前記第2の時間値に応じて決まり、 30

前記方法はさらに、前記集積回路の前記非給電状態および前記給電状態に応答する信号に基づいて検出用の前記第1の時間値と前記第2の時間値との間で選択することを含む、方法。

#### 【請求項4】

方法であって、

集積回路上の過渡電圧増大を検出することと；

前記過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することと

20

を含み、

前記検出ことは、検出用の第1の時間値および第2の時間値に依存し、

検出用の前記第1の時間値は、前記集積回路の非給電状態に適用可能であり、

検出用の前記第2の時間値は、前記集積回路の給電状態に適用可能であり、

検出用の前記第1の時間値および前記第2の時間値は、共通の容量性素子の容量値に応じて決まり、

前記制御することは、制御用の第1の時間値および第2の時間値に依存し、

前記制御することは、前記クランプデバイスのアクティブ期間にわたって行われ、

前記アクティブ期間は、前記集積回路の前記非給電状態については制御用の前記第1の時間値に応じて決まり、前記集積回路の前記給電状態については制御用の前記第2の時間値に応じて決まり、

前記方法はさらに、前記集積回路の前記非給電状態および前記給電状態に応答する信号に基づいて検出用の前記第1の時間値と前記第2の時間値との間で選択することを含み、 50

前記過渡電圧増大を制限するために前記クランプデバイスの前記導電状態を前記制御することは、

前記給電状態における前記過渡電圧増大に応答することを含む、方法。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本願は、参照によりその全体が本明細書に組み込まれる、2010年5月3日に提出された「集積回路のための過電圧保護回路(OVERVOLTAGE PROTECTION CIRCUIT FOR AN INTEGRATED CIRCUIT)」と題する同時係属の米国特許出願第12/772,769号(代理人整理番号AC50291HC)に関連する。 10

【0002】

本開示は、概して集積回路(IC)に関し、より具体的には、集積回路のための過渡電磁波耐性に関する。

【背景技術】

【0003】

電子回路は、制限された電圧範囲にわたって動作するように設計される。これらの制限された電圧範囲を超える電圧にさらされることによって、これらの回路が損傷または破壊される可能性がある。この問題は、非常に小さい尺度で作製される回路に接続される多くの外部端子を有することが多い集積回路に特に顕著である。 20

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国公開特許第2007/0247772号明細書

【特許文献2】米国公開特許第2011/0267723号明細書

【特許文献3】米国公開特許第2007/0115600号明細書

【特許文献4】米国公開特許第2009/0040671号明細書

【特許文献5】米国公開特許第2007/0285854号明細書

【特許文献6】米国公開特許第2007/0067104号明細書 30

【非特許文献】

【0005】

【非特許文献1】A.GERDEMANNら。「When Good Trigger Circuits Go Bad: A Case History」, IEEE 33rd Electrical Overstress/Electrostatic Discharge Symposium; 11-16 September 2011; 6 pages

【発明の概要】

【発明が解決しようとする課題】

【0006】

集積回路のための過渡電圧抑制回路は存在するが、それらは非給電過渡事象(すなわち、集積回路が通常動作のために電源投入されていないときに発生する過渡事象)および給電過渡事象(すなわち、通常動作のために集積回路に電力が加えられているときに発生する過渡事象)の両方に対しては良好に機能しない傾向にある。 40

【課題を解決するための手段】

【0007】

本開示は、添付の図面を参照することによってよりよく理解されることができ、その多数の特徴および利点が当業者に明らかとなる。

【図面の簡単な説明】

【0008】

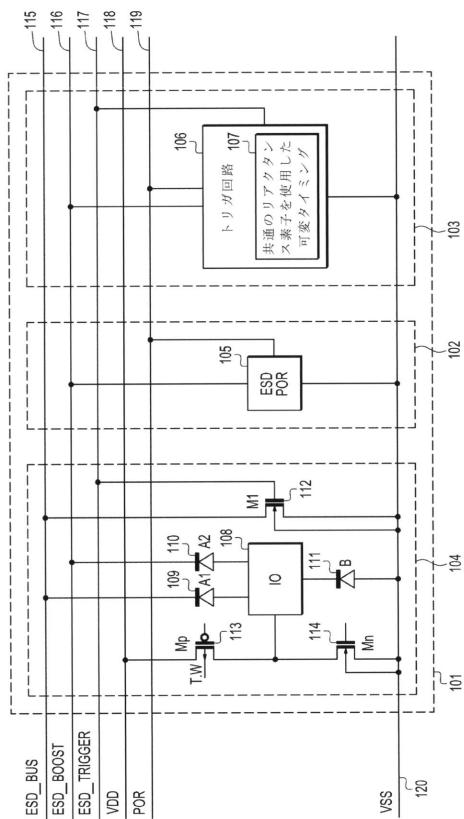

【図1】少なくとも1つの実施形態に応じた、複数の時間値を提供するために共通のリアクタンス素子を使用する可変タイミングブロックを有するトリガ回路を備える過渡抑制システムを示すブロック図。

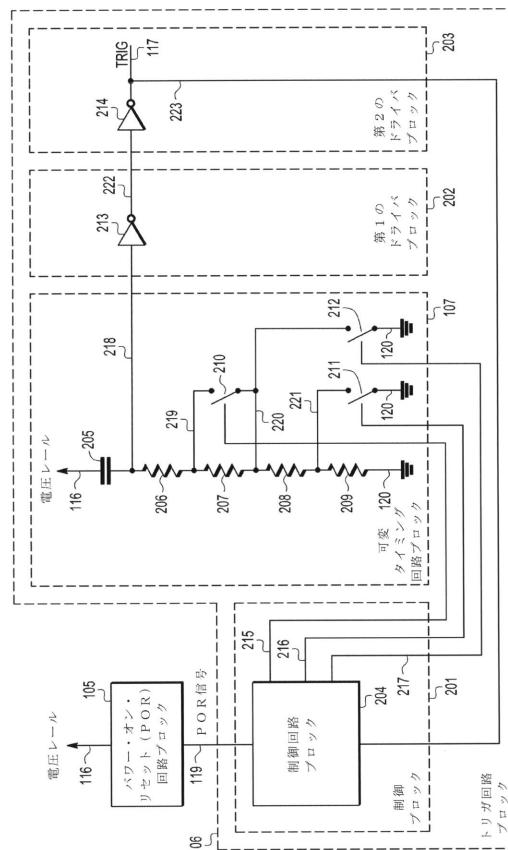

【図2】少なくとも1つの実施形態に応じた、複数の時間値を提供するための切り替え可能抵抗素子および共通の容量性素子を有するトリガ回路を示す簡略化された概略図。

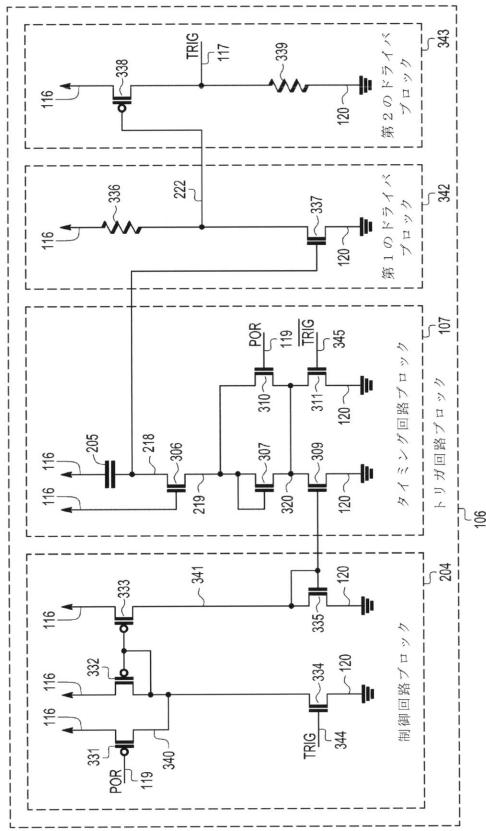

【図3】少なくとも1つの実施形態に応じた、トリガ回路の相補型金属酸化膜半導体(CMOS)の実施態様を示す概略図。

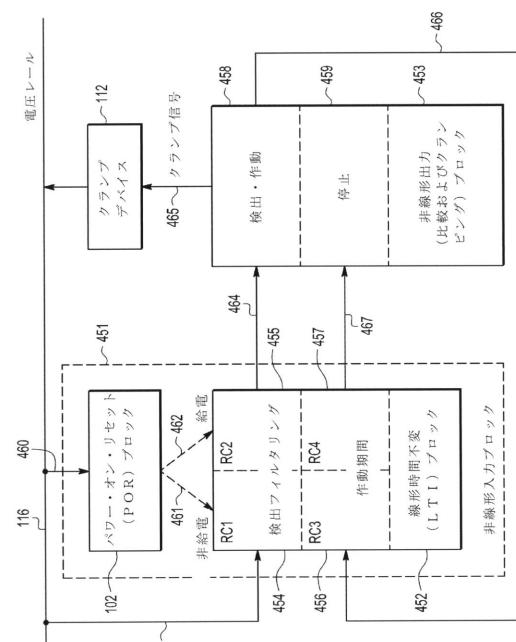

【図4】少なくとも1つの実施形態に応じた、複数の時間値を提供するための線形時不变( LTI )ブロックを有するトリガ回路を備える過渡抑制システムを示すブロック図。

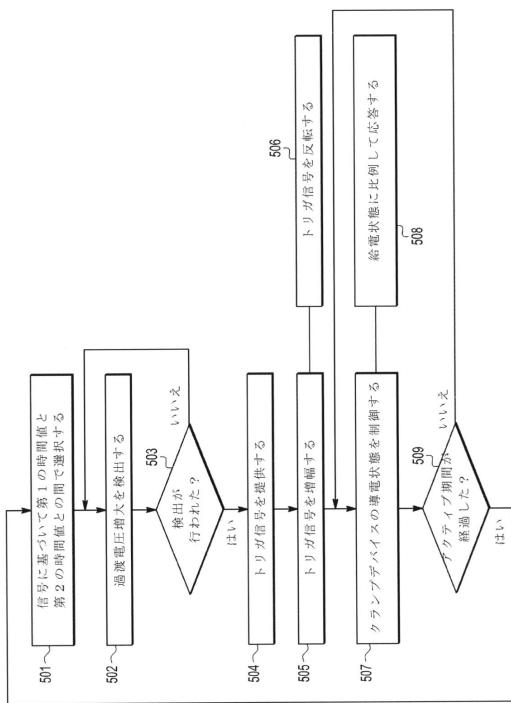

【図5】少なくとも1つの実施形態に応じた、過渡電圧増大を検出し、クランプデバイスの導電状態を制御するための方法を示すフローチャート。 10

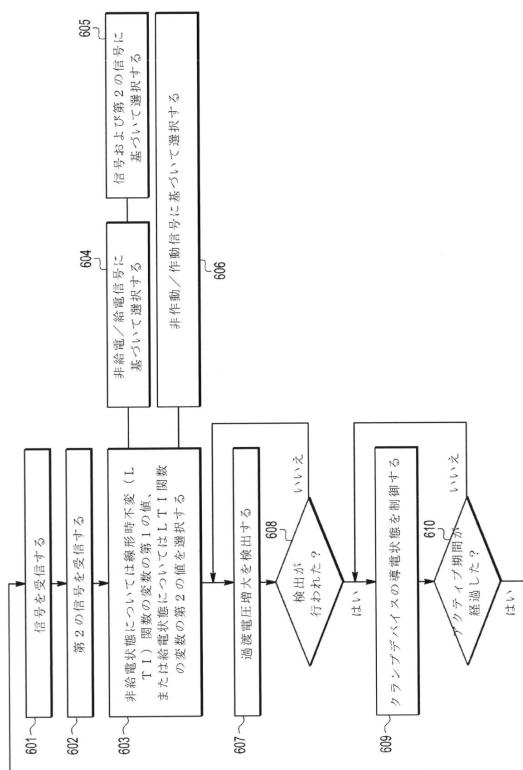

【図6】少なくとも1つの実施形態に応じた、過渡電圧増大を検出し、クランプデバイスの導電状態を制御するための方法を示すフローチャート。

#### 【0009】

異なる図面において同じ参照符号が使用されている場合、これは、類似または同一の項目であることを示す。

#### 【発明を実施するための形態】

#### 【0010】

過渡電磁波耐性(transient immunity)を向上させるためのトリガ回路(TC)が提供される。トリガ回路は、当該トリガ回路がその上に作製される集積回路上の過渡電圧増大(transient voltage increase)を検出する。トリガ回路は、過渡電圧増大を制限するために集積回路上のクランプデバイスの導電状態を制御する。トリガ回路は、或る容量値を有する共通の容量性素子を備え、第1の時間値および第2の時間値がこの共通の容量性素子の容量値に応じて決まり、第1の時間値は集積回路の非給電状態に適用可能であり、第2の時間値は集積回路の給電状態に適用可能である。第1の時間値および第2の時間値は、その範疇にある過渡電圧増大の速度が、トリガ回路をアクティブにする検出範囲、または、クランプデバイスの導電状態の制御のアクティブ期間がそれに応じて決まる「オン」時間を含んでもよいトリガ回路パラメータを制御する。 20

#### 【0011】

図1は、少なくとも1つの実施形態に応じた、複数の時間値を提供するために共通のリアクタンス素子(reactive element)を使用する可変タイミングブロックを有するトリガ回路を備える過渡抑制システム(transient suppression system)を示すブロック図である。過渡抑制システム101は、静電放電(ESD)パワー・オン・リセット(POR)モジュール102と、トリガ回路モジュール103と、入出力(IO)モジュール104とを備える。過渡抑制システム101は、複数の電圧レールおよび信号伝達バス、ならびに過渡抑制バスをも備える。たとえば、過渡抑制システム101は、正電圧レールVDD118および負電圧レールVSS120と、ESD電圧レールESD\_BOOST116と、信号伝達バスPOR119およびESD\_TRIGGER117と、過渡抑制バスESD\_BUS115とを備える。正電圧レールVDD118および負電圧レールVSS120は、過渡抑制システム101によって保護されるシステム構成要素に、そのようなシステム構成要素の通常動作のための電力を提供し、負電圧レールVSS120は概して、他の電圧がそれに対して参照されるグランド基準電位と考えられる。ESD電圧レールESD\_BOOST116は、過渡事象によってエネルギー付与され、過渡抑制システム101の要素に電力を提供して、それらがアクティブに動作して過渡事象を検出および制御することを可能にする。信号伝達バスPOR119は、PORモジュール102からPOR信号を受信し、そのPOR信号をトリガ回路モジュール103に提供する。信号伝達バスESD\_TRIGGER117は、トリガ回路モジュール103からトリガ信号TRIGを受信し、そのトリガ信号TRIGをIOモジュール104に提供する。過渡抑制バスESD\_BUS115は、過渡事象を抑 40

制する結果として生じる大きい電流が、正電圧レールV D D 1 1 8のような通常の電圧レールをバイパスすることを可能にし、正電圧レールV D D 1 1 8において正供給電圧が大きく偏位することが防止される。

#### 【0012】

E S D P O R モジュール1 0 2は、E S D P O R回路ブロック1 0 5を備える。E S D P O R回路ブロック1 0 5の正供給端子は、E S D電圧レールE S D \_ B O O S T 1 1 6に接続されている。E S D P O R回路ブロック1 0 5の負供給端子は、電圧レールV S S 1 2 0に接続されている。E S D P O R回路ブロック1 0 5のP O R出力は、信号伝達バスP O R 1 1 9に接続されている。トリガ回路モジュール1 0 3は、トリガ回路ブロック1 0 6を備える。トリガ回路ブロック1 0 6は、可変タイミング回路ブロック1 0 7を備え、当該ブロックは、複数の時間値(m u l t i p l e t i m e v a l u e s)を提供するのに使用される共通のリアクタンス素子を備える。トリガ回路ブロック1 0 6の正供給端子は、E S D電圧レールE S D \_ B O O S T 1 1 6に接続されている。トリガ回路ブロック1 0 6の負供給端子は、負電圧レールV S S 1 2 0に接続されている。トリガ回路ブロック1 0 6のP O R入力端子は、信号伝達バスP O R 1 1 9に接続されている。トリガ回路ブロック1 0 6のトリガ出力は、信号伝達バスE S D \_ T R I G G E R 1 1 7に接続されている。10

#### 【0013】

I Oモジュール1 0 4は、I Oパッド1 0 8と、ダイオード1 0 9と、ダイオード1 1 0と、ダイオード1 1 1と、クランプデバイス1 1 2と、正出力ドライバ1 1 3と、負出力ドライバ1 1 4とを備える。I Oパッド1 0 8は、その上に過渡抑制システム1 0 1が作製される集積回路の外部端子(たとえば、ピン、ポール、バンプ、ランドなど)に対する導電性接続を提供する。ダイオード1 0 9、1 1 0、および1 1 1は、電流がダイオード1 0 9、1 1 0、および1 1 1の電流 - 電圧(I - V)曲線に基づくノードまたはバス間の電圧関係を維持するための経路を提供する。その間で電圧関係を維持するためにダイオードが使用されるそのようなノードまたはバスは、I Oパッド1 0 8、過渡抑制バスE S D \_ B U S 1 1 5、E S D電圧レールE S D \_ B O O S T 1 1 6、正電圧レールV D D 1 1 8、および負電圧レールV S S 1 2 0を含んでもよい。たとえば、I Oモジュール1 0 4のダイオード1 0 9、1 1 0、および1 1 1と同様に構成される追加のダイオードが、正電圧レールV D D 1 1 8のためにV D Dパッドセル内で使用されてもよい。それゆえ、過渡抑制バスE S D \_ B U S 1 1 5は、I Oパッド・セル・モジュール1 0 4のダイオード1 0 9と類似のV D Dパッド・セル・ダイオードによって、少なくとも、正電圧レールV D D 1 1 8の電圧を下回るダイオードドロップまでプルアップされる。従って、正電圧レールV D D 1 1 8の電圧は、過渡抑制バスE S D \_ B U S 1 1 5の電圧を決定するにあたって大きな役割を果たす傾向にある。I Oが負電圧レールV S S 1 2 0と正電圧レールV D D 1 1 8との間の範囲内で切り替わっている場合(たとえば、通常チップ動作の間)、過渡抑制バスE S D \_ B U S 1 1 5の電圧は、I Oモジュール内のダイオード1 0 9、1 1 0、1 1 1、またはV D Dパッドセル内でそれらに対応するもののようなダイオードが存在することによって影響を受けるべきではない。同様に、I Oモジュール1 0 4のダイオード1 1 0と同様のV D Dパッドセル内のダイオードは、E S D電圧レールE S D \_ B O O S T 1 1 6を、正電圧レールV D D 1 1 8の電圧を下回るダイオードドロップに予備調整する役割を果たし、負電圧レールV S S 1 2 0と正電圧レールV D D 1 1 8との間の範囲内で切り替わっている(たとえば、通常チップ動作の間)I Oについて、E S D電圧レールE S D \_ B O O S T 1 1 6の電圧は、I Oモジュール1 0 4内のダイオード1 0 9、1 1 0、1 1 1、またはV D Dパッドセル内のそれらに対応するもののようなダイオードが存在することによって影響を受けるべきではない。ダイオード1 0 9は、正電圧オーバーストレス事象(p o s i t i v e v o l t a g e o v e r s t r e s s e v e n t)がI Oパッド1 0 8に加わっているときは、I Oパッド1 0 8と過渡抑制バスE S D \_ B U S 1 1 5との間に電流を通す。たとえば、I Oパッド1 0 8における電圧が過渡抑制バスE S D \_ B U S 1 1 5の電圧を上回る1つのダイオードドロップを超えるま20304050

でに上昇すると、ダイオード 109 は、導通することになる。ダイオード 110 は、IO パッド 108 において正電圧オーバーストレス事象が発生すると、IO パッド 108 と ESD 電圧レール ESD\_BOOST116との間に電流を通す。たとえば、IO パッド 108 における電圧が ESD 電圧レール ESD\_BOOST116 の電圧を上回る 1 つのダイオードドロップを超えるまでに上昇すると、ダイオード 110 は導通することになる。

ダイオード 111 は、IO パッド 108 上に負電圧オーバーストレス事象 (negative voltage overstress event) が存在する場合に負電圧レール VSS120 から IO パッド 108 までの電流路を提供する。たとえば、IO パッド 108 における電圧が負電圧レール VSS120 の電圧を下回る 1 つのダイオードドロップを超えるまでに下降すると、ダイオード 111 は、導通することになる。たとえば、N チャネル金属酸化膜半導体電界効果トランジスタ (MOSFET) であってもよいクランプデバイス 112 は、過渡抑制バス ESD\_BUS115 に接続されている第 1 の端子 (たとえば、ドレイン端子) と、負電圧レール VSS120 に接続されている第 2 の端子 (たとえば、ソース端子) と、信号伝達バス ESD\_TRIGGER117 に接続されている制御端子 (たとえば、ゲート端子) と、負電圧レール VSS120 に接続されているボディ端子とを有する。たとえば、P チャネル MOSFET であってもよい正出力ドライバ 113 は、正電圧レール VDD118 に接続されている第 1 の端子 (たとえば、ソース端子) と、IO パッド 108 に接続されている第 2 の端子 (たとえば、ドレイン端子) と、正出力ドライバ 113 に IO パッド 108 をハイ論理レベルに駆動させるための出力ドライバ回路に接続されている制御端子 (たとえば、ゲート端子) と、トラッキングウェル制御回路 (tracking well control circuit) に接続されているボディ端子とを有する。トラッキングウェル制御回路は、電流が IO パッド 108 から正電圧レール VDD118 へと注入されることが可能になることを回避するために、正出力ドライバ 113 のボディ端子を正電圧レール VDD118 の電圧と、IO パッド 108 の電圧とのうちの高い方に維持する。たとえば、N チャネル MOSFET であってもよい負出力ドライバ 114 は、IO パッド 108 に接続されている第 1 の端子 (たとえば、ドレイン端子) と、負電圧レール VSS120 に接続されている第 2 の端子 (たとえば、ソース端子) と、負出力ドライバ 114 に IO パッド 108 をロー論理レベルに駆動させるための出力ドライバ回路に接続されている制御端子 (たとえば、ゲート端子) と、負電圧レール VSS120 に接続されているボディ端子とを有する。

#### 【0014】

一例として、図 1 の過渡抑制システム 101 は、複数の IO パッド 108 が 1 つのトリガ回路を共有することができる場合のような、パッドライングのシナリオに適用されてもよい。たとえば、トリガ回路モジュール 103 は、IO モジュール 104 と T/C モジュール 103 との特定の比 (たとえば、8 : 1) で配置されてもよい。また、複数の IO モジュール 104 を備える IO セグメントの役割が、単一の ESD POR モジュール 102 によって果たされてもよい。単一の ESD POR モジュール 102 が複数のトリガ回路モジュール 103 に結合されてもよく、当該複数のトリガ回路モジュールは、信号伝達バス ESD\_TRIGGER117 を介して IO セグメントの複数の IO モジュール 104 にトリガ信号 TRIG を提供してもよい。従って、ESD POR モジュール 102、トリガ回路モジュール 103 および IO モジュール 104 は、1 : 1 : n の比において実装されてもよく、n は、1 よりも大きい。代替的に、ESD POR モジュール 102、トリガ回路モジュール 103 および IO モジュール 104 は、1 : 1 : 1 の比、1 : x : x の比、ここで、x は 1 よりも大きい、または 1 : x : y の比、ここで、x は 1 よりも大きく y は x よりも大きい、において実装されてもよい。

#### 【0015】

図 2 は、少なくとも 1 つの実施形態に応じた、複数の時間値を提供するための切り替え可能抵抗素子および共通の容量性素子を有するトリガ回路を示す簡略化された概略図である。トリガ回路ブロック 106 は、制御ブロック 201 と、可変タイミング回路ブロック 107 と、第 1 のドライバブロック 202 と、第 2 のドライバブロック 203 とを備える

10

20

30

40

50

。制御ブロック 201 は、制御回路ブロック 204 を備える。ESD 電圧レール ESD\_BOOST116 のような電圧レールが、ESD POR 回路ブロック 105 に接続されている。ESD POR 回路ブロック 105 は、信号伝達バス POR119 を介して、トリガ回路ブロック 106 の制御ブロック 201 の制御回路ブロック 204 に POR 信号を提供する。制御回路ブロック 204 は、スイッチ 210 を制御するためにスイッチ 210 の制御端子に接続される第 1 のスイッチ制御出力 215 と、スイッチ 211 を制御するためにスイッチ 211 の制御端子に接続される第 2 のスイッチ制御出力 216 と、スイッチ 212 を制御するためにスイッチ 212 の制御端子に接続される第 3 のスイッチ制御出力 217 とを提供する。制御回路ブロック 204 は、第 2 のドライバブロック 203 からトリガ信号 TRIG を受信する。制御回路ブロック 204 は、POR 信号の状態およびトリガ信号 TRIG の状態に応答して、それぞれスイッチ 210、211、および 212 を制御するために、第 1 のスイッチ制御出力 215、第 2 のスイッチ制御出力 216、および第 3 のスイッチ制御出力 217 をアサートする。

#### 【0016】

可変タイミング回路ブロック 107 は、共通の容量性素子 205 と、抵抗素子 206 と、抵抗素子 207 と、抵抗素子 208 と、抵抗素子 209 と、スイッチ 210 と、スイッチ 211 と、スイッチ 212 とを備える。共通の容量性素子 205 は、たとえば、金属酸化膜半導体電界効果トランジスタ (MOSFET) として、バラクタダイオードとして、金属 - 絶縁体 - 金属 (MIM) キャパシタとして、または、適切な値のキャパシタンスを提供する任意の他の適切な素子として実装されてもよい。抵抗素子 206、207、208、および 209 は、たとえば、抵抗器として、所望の「オン」抵抗を提供するように構成される MOSFET として、所望の抵抗に対応する電流を提供するように構成されるバイポーラトランジスタとして、または、適切な値の抵抗を提供するための任意の他の適切な素子として実装されてもよい。ESD 電圧レール ESD\_BOOST116 のような電圧レールが、共通の容量性素子 205 の第 1 の端子に接続されている。共通の容量性素子 205 の第 2 の端子はノード 218 に接続されており、当該ノードは抵抗素子 206 の第 1 の端子および第 1 のドライバブロック 202 のインバータ 213 の入力に接続されている。抵抗素子 206 の第 2 の端子はノード 219 に接続されており、当該ノードは抵抗素子 207 の第 1 の端子およびスイッチ 210 の第 1 の端子に接続されている。抵抗素子 207 の第 2 の端子はノード 220 に接続されており、当該ノードはスイッチ 210 の第 2 の端子、抵抗素子 208 の第 1 の端子、およびスイッチ 212 の第 1 の端子に接続されている。抵抗素子 208 の第 2 の端子は、抵抗素子 209 の第 1 の端子およびスイッチ 211 の第 1 の端子に接続されている。抵抗素子 209 の第 2 の端子は、負電圧レール VSS120 に接続されている。スイッチ 211 の第 2 の端子は、負電圧レール VSS120 に接続されている。スイッチ 212 の第 2 の端子は、負電圧レール VSS120 に接続されている。

#### 【0017】

POR 信号、トリガ信号 TRIG、スイッチ 210、スイッチ 211、およびスイッチ 212 の対応する状態、ならびに、抵抗素子 206、抵抗素子 207、抵抗素子 208、および抵抗素子 209 の対応する直列結合に関する真理値表は、下記表 1 に示されている。

10

20

30

40

【表1】

|                                 | T R I G = 1 (たとえば、クランピングのアクティブ継続時間<br>を制御するためのもの)   | T R I G = 0 (たとえば、検出<br>範囲を制御するためのもの)                      |

|---------------------------------|-----------------------------------------------------|------------------------------------------------------------|

| P O R = 1<br><br>(たとえば、非給電状態の間) | スイッチ 2 1 0 = 1                                      | スイッチ 2 1 0 = 1                                             |

|                                 | スイッチ 2 1 1 = 1                                      | スイッチ 2 1 1 = X                                             |

|                                 | スイッチ 2 1 2 = 0                                      | スイッチ 2 1 2 = 1                                             |

|                                 | (抵抗素子 2 0 6 + 抵抗素子 2 0 8)                           | (抵抗素子 2 0 6)<br><br>(たとえば、約 100 ナノ秒の<br>時間値)               |

|                                 | (たとえば、約 5 マイクロ秒の<br>時間値)                            |                                                            |

| P O R = 0<br><br>(たとえば、給電状態の間)  | スイッチ 2 1 0 = 0                                      | スイッチ 2 1 0 = 0                                             |

|                                 | スイッチ 2 1 1 = 0                                      | スイッチ 2 1 1 = X                                             |

|                                 | スイッチ 2 1 2 = 0                                      | スイッチ 2 1 2 = 1                                             |

|                                 | (抵抗素子 2 0 6 + 抵抗素子 2 0 7 + 抵抗素子 2 0 8 + 抵抗素子 2 0 9) | (抵抗素子 2 0 6 + 抵抗素子 2 0 7)<br><br>(たとえば、約 10 マイクロ秒の<br>時間値) |

|                                 | (たとえば、約 20 ミリ秒の時間値)                                 |                                                            |

表1：スイッチ状態および抵抗素子結合

表1において、P O R信号およびトリガ信号T R I Gについて、0はロー論理レベルを示し、1はハイ論理レベルを示す。スイッチ2 1 0、2 1 1、および2 1 2について、0は開スイッチを示し、1は閉スイッチを示し、「X」は結果生じる抵抗値に影響を及ぼさない、開または閉のいずれであってもよいスイッチを示す。抵抗素子について、プラス記号は、それらが直列結合において組み合わされるときの、それらの抵抗値の合計を示す。少なくとも1つの実施形態に応じて、反対の論理レベルが使用されてもよく、異なるスイッチ命名法が使用されてもよく、または、異なる構成の抵抗素子が使用されてもよい。一例として、並列結合の抵抗素子が使用されてもよく、または、直列結合と並列結合とが組み合わされた抵抗素子が使用されてもよい。少なくとも1つの実施形態に応じて、抵抗素子2 0 6は、共通の容量性素子2 0 5と組み合わされて、約100ナノ秒の時間値(たとえば、抵抗容量(R C)時定数)を提供し、抵抗素子2 0 6および抵抗素子2 0 8から成る直列結合は、共通の容量性素子2 0 5と組み合わされて、約5マイクロ秒の時間値(たとえば、R C時定数)を提供し、抵抗素子2 0 6および抵抗素子2 0 7から成る直列結合は、共通の容量性素子2 0 5と組み合わされて、約10マイクロ秒の時間値(たとえば、R C時定数)を提供し、抵抗素子2 0 6、抵抗素子2 0 7、抵抗素子2 0 8、および抵抗素子2 0 9から成る直列結合は、共通の容量性素子2 0 5と組み合わされて、約20ミリ秒の時間値(たとえば、R C時定数)を提供する。

## 【0018】

第1のドライバブロック2 0 2は、インバータ2 1 3を備える。インバータ2 1 3は、低インバタスイッチ点(たとえば、正電圧レールV D D 1 1 8と負電圧レールV S S 1 2 0との間の差の50%よりも低い)を有するように構成されてもよく、ロー論理レベルからのわずかな電圧の増大が、ハイ論理レベルとして解釈され、インバータをハイ論理レベル出力の提供からロー論理レベル出力の提供へと切り替えることが可能である。第2のドライバブロック2 0 3は、インバータ2 1 4を備える。インバータ2 1 3およびインバ

10

20

30

40

50

ータ214は、不安定性および揺らぎを回避するために制限された利得を提供するように構成される。たとえば、インバータ213およびインバータ214は、図3に示すようにそれぞれ抵抗素子336および339を使用して、または、適切に制限された利得を提供するように構成された他のインバータを使用して実装されてもよい。ノード218は、インバータ213の入力に接続されている。インバータ213の出力はノード222に接続されており、当該ノードは第2のドライバブロック203のインバータ214の入力に接続されている。第2のドライバブロックの出力は、制御ブロック201の制御回路ブロック204のトリガ入力に接続されているノード223において、トリガ信号TRIGを提供する。トリガ信号TRIGはまた、クランプデバイスの導電状態を制御するのに使用されてもよい。ノード223におけるトリガ信号TRIGの通信は、信号伝達バスESD\_TRIGGER117を介して提供されてもよく、当該バスはノード223に接続されてもよい。トリガ回路ブロック106内でのノード223におけるトリガ信号TRIGのフィードバックは、トリガ回路ブロック106内の内部導体を介して達成されてもよい。

#### 【0019】

たとえば、集積回路の非給電状態の間に使用されてもよいオン／オフスタイルのトリガモードを提供するために、上記表1に示すように、POR信号は1の値を有し、トリガ信号TRIGは0の値を有する。制御回路ブロック204は、共通の容量性素子205と組み合わさせて、ESD電圧レールESD\_BOOST116の過渡的電圧増大の速度の検出範囲を制御するための（たとえば、約100ナノ秒の）時間値を決定するために、スイッチ210、211、および212が、抵抗素子206だけを選択するようにする。ESD電圧レールESD\_BOOST116上の電圧が相対的に遅く増大する（たとえば、集積回路に電力が印加されESD電圧レールESD\_BOOST116の電圧が増大するときにそうなり得るように）ことによって、抵抗素子206は、共通の容量性素子205を充電するのに十分な電流を提供し、ESD電圧レールESD\_BOOST116上の電圧が上昇するにつれて共通の容量性素子205にわたる電圧を増大させることが可能になり、ノード218における電圧が負電圧レールVSS120に対して実質的に上昇しないようになる。従って、ESD電圧レールESD\_BOOST116の電圧の遅い増大は、トリガ回路をトリガするには十分でなかったため、第1のドライバブロック202および第2のドライバブロック203は変化しないままであり、ノード223におけるトリガ信号TRIGは変化しないままである。しかしながら、ESD電圧レールESD\_BOOST116上の電圧が非常に急速に増大する（たとえば、ESD事象のような過渡電圧ストレス事象の間にそうなり得るように）ことによって、ノード218は、非常に急速に電圧を引き上げられる。ノード218における電圧が非常に急速に増大することによってNチャネルMOSFET337の制御端子（たとえば、ゲート端子）における電圧が増大し、それによって、第1のドライバブロック202および第2のドライバブロック203がノード223におけるトリガ信号TRIGを迅速に作動し、当該信号はクランプデバイスの作動を開始するためにクランプデバイスに提供され、クランプデバイスの作動の作動期間を決定するために制御回路ブロック204にフィードバックされる。

#### 【0020】

たとえば、集積回路の非給電状態の間に使用されてもよい相対的に短い作動期間を提供するために、上記表1に示すように、POR信号は1の値を有し、トリガ信号TRIGは1の値を有する。制御回路ブロック204は、スイッチ210、211、および212に、共通の容量性素子205と協同してクランプデバイスの作動の作動期間を制御するための（たとえば、約5マイクロ秒の）時間値を決定するために抵抗素子206および208から成る直列結合を選択させる。その後、ESD電圧レールESD\_BOOST116上の電圧は、抵抗素子206および208から成る直列結合を通じて共通の容量性素子205を充電する。共通の容量性素子205がノード218における電圧を抑制するのに十分で、第1のドライバブロック202および第2のドライバブロック203の状態を変化させるのに十分に高い電圧まで充電されると、ノード223におけるトリガ信号TRIGが停止され、それによって制御されているいかなるクランプデバイスも停止する。

10

20

30

40

50

## 【0021】

たとえば、集積回路の給電状態の間に使用されてもよい電圧調整モードを提供するために、上記表1に示すように、POR信号は0の値を有し、トリガ信号TRIGは0の値を有する。制御回路ブロック204は、スイッチ210、211、および212に、共通の容量性素子205と協同してESD電圧レールESD\_BOOST116の過渡電圧増大の速度の検出範囲を制御するための（たとえば、約10マイクロ秒の）時間値を決定するために抵抗素子206および207から成る直列結合を選択させる。ESD電圧レールESD\_BOOST116上の電圧が相対的に遅く増大することによって、抵抗素子206および207から成る直列結合は、共通の容量性素子205を充電するのに十分な電流を提供し、ESD電圧レールESD\_BOOST116上の電圧が上昇するにつれて共通の容量性素子205にわたる電圧を増大させることができになり、ノード218における電圧が負電圧レールVSS120に対して実質的に上昇しないようになる。従って、ESD電圧レールESD\_BOOST116の電圧の遅い増大はトリガ回路をトリガするには十分でなかったため、第1のドライバブロック202および第2のドライバブロック203は変化しないままであり、ノード223におけるトリガ信号TRIGは変化しないままである。しかしながら、抵抗素子206および207から成る直列結合の高い抵抗（たとえば、非給電状態における抵抗素子206だけのより低い抵抗と比較して）が、共通の容量性素子205の電荷（および、従って共通の容量性素子205にわたる電圧）が急速に変化することを妨げるため、ESD電圧レールESD\_BOOST116上の電圧が非常に急速に増大することによって、ノード218は、およそESD\_BOOST電圧の変化に比例して電圧を引き上げられる。ノード218において電圧が増大することによって、NチャネルMOSFET337の制御端子（たとえば、ゲート端子）における電圧がおよそESD\_BOOST電圧の増大に比例して増大し、これは第1のドライバブロック202のインバータ213の利得によって増幅される。第2のドライバブロック203は、第1のドライバブロックの出力を反転させて、ノード223においてトリガ信号TRIGを提供し、当該信号は、クランプデバイスの作動を開始するためにクランプデバイスに提供され、クランプデバイスの作動の作動期間を決定するために制御回路ブロック204にフィードバックされる。

## 【0022】

たとえば、集積回路の給電状態の間に使用されてもよい相対的に長い作動期間を提供するために、上記表1に示すように、POR信号は0の値を有し、トリガ信号TRIGは1の値を有する。制御回路ブロック204は、スイッチ210、211、および212に、共通の容量性素子205と協同してクランプデバイスの作動の作動期間を制御するための（たとえば、約20ミリ秒の）時間値を決定するために抵抗素子206、207、208、および209から成る直列結合を選択させる。その後、ESD電圧レールESD\_BOOST116上の電圧が、抵抗素子206、207、208、および209から成る直列結合を通じて共通の容量性素子205を充電する。共通の容量性素子205が、第1のドライバブロック202および第2のドライバブロック203の状態を変化させるのに十分にノード218における電圧を抑制するのに十分に高い電圧まで充電されると、ノード223におけるトリガ信号TRIGが停止され、それによって制御されているいかなるクランプデバイスも停止する。充電時間は、抵抗素子206および208から成る直列結合のより低い抵抗の場合よりもはるかに遅いため、抵抗素子206および208から成る直列結合のより低い抵抗の場合よりも長い作動期間が提供される。

## 【0023】

図3は、少なくとも1つの実施形態に応じた、トリガ回路の相補型金属酸化膜半導体(CMOS)の実施態様を示す概略図である。トリガ回路ブロック106は、制御回路ブロック204と、可変タイミング回路ブロック107と、第1のドライバブロック342と、第2のドライバブロック343とを備える。制御回路ブロック204は、PチャネルMOSFET331と、PチャネルMOSFET332と、PチャネルMOSFET333と、NチャネルMOSFET334と、NチャネルMOSFET335とを備える。ES

10

20

30

40

50

D電圧レールE S D \_ B O O S T 1 1 6のような電圧レールが、PチャネルMOSFET 3 3 1のソース端子、PチャネルMOSFET 3 3 2のソース端子、およびPチャネルMOSFET 3 3 3のソース端子に接続されている。POR信号は、たとえば、信号伝達バスP O R 1 1 9を介してPチャネルMOSFET 3 3 1のゲート端子に接続される。PチャネルMOSFET 3 3 1のドレン端子がノード3 4 0に接続されており、当該ノードは、PチャネルMOSFET 3 3 2のドレン端子、PチャネルMOSFET 3 3 2のゲート端子、PチャネルMOSFET 3 3 3のゲート端子、およびNチャネルMOSFET 3 3 4のドレン端子に接続されている。ノード3 4 4におけるトリガ信号T R I Gは、NチャネルMOSFET 3 3 4のゲート端子に接続される。NチャネルMOSFET 3 3 4のソース端子は、負電圧レールV S S 1 2 0に接続されている。PチャネルMOSFET 3 3 3のドレン端子は、ノード3 4 1に接続されており、当該ノードは、NチャネルMOSFET 3 3 5のドレン端子、NチャネルMOSFET 3 3 5のゲート端子、および可変タイミング回路ブロック1 0 7のNチャネルMOSFET 3 0 9のゲート端子に接続されている。NチャネルMOSFET 3 3 5のソース端子は、負電圧レールV S S 1 2 0に接続されている。

10

#### 【0024】

可変タイミング回路ブロック1 0 7は、共通の容量性素子2 0 5と、NチャネルMOSFET 3 0 6と、NチャネルMOSFET 3 0 7と、NチャネルMOSFET 3 0 9と、NチャネルMOSFET 3 1 0と、NチャネルMOSFET 3 1 1とを備える。E S D電圧レールE S D \_ B O O S T 1 1 6のような電圧レールは、共通の容量性素子2 0 5の第1の端子およびNチャネルMOSFET 3 0 6のゲート端子に接続されている。共通の容量性素子2 0 5の第2の端子は、ノード2 1 8に接続されており、当該ノードは、NチャネルMOSFET 3 0 6のドレン端子、および第1のドライバブロック3 4 2のNチャネルMOSFET 3 3 7のゲート端子に結合されている。NチャネルMOSFET 3 0 6のソース端子は、ノード2 1 9に接続されており、当該ノードは、NチャネルMOSFET 3 0 7のドレン端子、NチャネルMOSFET 3 0 7のゲート端子、およびNチャネルMOSFET 3 1 0のドレン端子に接続されている。POR信号は、たとえば、信号伝達バスP O R 1 1 9を介してNチャネルMOSFET 3 1 0のゲート端子に接続される。NチャネルMOSFET 3 0 7のソース端子は、ノード3 2 0に接続されており、当該ノードは、NチャネルMOSFET 3 0 9のドレン端子、NチャネルMOSFET 3 1 0のソース端子、およびNチャネルMOSFET 3 1 1のドレン端子に接続されている。

20

30

#### 【0025】

第1のドライバブロック3 4 2は、抵抗素子3 3 6およびNチャネルMOSFET 3 3 7を備える。E S D電圧レールE S D \_ B O O S T 1 1 6のような電圧レールは、抵抗素子3 3 6の第1の端子に接続されている。抵抗素子3 3 6の第2の端子は、NチャネルMOSFET 3 3 7のドレン端子、および第2のドライバブロック3 4 3のPチャネルMOSFET 3 3 8のゲート端子に接続されている。NチャネルMOSFET 3 3 7のソース端子は、負電圧レールV S S 1 2 0に接続されている。

40

#### 【0026】

第2のドライバブロック3 4 3は、PチャネルMOSFET 3 3 8および抵抗素子3 3 9を備える。E S D電圧レールE S D \_ B O O S T 1 1 6のような電圧レールは、PチャネルMOSFET 3 3 8のソース端子に接続されている。PチャネルMOSFET 3 3 8のドレン端子は、抵抗素子3 3 9の第1の端子、および、たとえば、信号伝達バスE S D \_ T R I G G E R 1 1 7を介して通信されてもよいトリガ出力に接続されている。抵抗素子3 3 9の第2の端子は、負電圧レールV S S 1 2 0に接続されている。

50

## 【0027】

ノード344におけるトリガ信号TRIGがハイ論理状態にある場合、NチャネルMOSFET334は、ノード340から負電圧レールVSS120へと電流を伝導する。この電流は、2つの電流ミラーを介してノード320に提供される。PチャネルMOSFET332およびPチャネルMOSFET333は、トランジスタチャネルの幅対長さの比の差によって、固有の減衰比( attenuation ratio)を有する第1の電流ミラーを形成する。たとえば、そのような減衰比は約20:1であってもよい。NチャネルMOSFET335およびNチャネルMOSFET309は、トランジスタチャネルの幅対長さの比の差によって、固有の減衰比を有する第2の電流ミラーを形成する。たとえば、そのような減衰比は約20:1であってもよい。電流ミラーの組み合わされた減衰比は、約4,000:1の、NチャネルMOSFET309によって提供される電流を制御するための最終的な減衰比をもたらしてもよい。信号伝達バスPOR119のPOR信号がロー論理レベルにある場合、PチャネルMOSFET331は、ESD電圧レールESD\_BOOST116からノード340へと電流を伝導する。この電流は、第1の電流ミラーに提供される総電流を効果的にさらに低減し、それゆえ、NチャネルMOSFET309によって提供される電流をも低減する。一例において、POR信号のロー論理レベルの間にNチャネルMOSFET309によって提供される電流の低減は、4,000分の1であってもよい。

## 【0028】

図3におけるMOSFET間の所望の相互作用は、MOSFETチャネルの幅対長さの比を、異なる複数のMOSFETの間で異なるように定義することによって達成されることができる。一例として、NチャネルMOSFET334、306、および307は、たとえば、PチャネルMOSFET333またはNチャネルMOSFET309よりも長いチャネルを有するロングチャネルMOSFETとして実装されてもよい。別の例として、PチャネルMOSFET331、PチャネルMOSFET332、およびNチャネルMOSFET335は、たとえば、PチャネルMOSFET333またはNチャネルMOSFET309よりも広いチャネルを有するワイドチャネルMOSFETとして実装されてもよい。

## 【0029】

トリガ回路によって使用される信号はそれら自体が過渡的事象(transient event)によって影響を受ける場合があり、そのような信号は、それらの値をESD事象の前に記憶するために、且つそれらの信号に対する過渡的事象の影響がトリガ回路の動作に悪影響を及ぼすことを防止するために、ラッチまたはバッファリングされてもよい。たとえば、POR信号は、ESD事象が発生しはじめる前にPOR信号とはどのようなものであったかを記憶するためにラッチまたはバッファリングされてもよい。

## 【0030】

図4は、少なくとも1つの実施形態に応じた、複数の時間値を提供するための線形時不变(LTI)ブロックを有するトリガ回路を備える過渡抑制システムを示すブロック図である。過渡抑制システムは、ESD電圧レールESD\_BOOST116のような電圧レールと、非線形入力ブロック451と、非線形(比較およびクランプ)出力ブロック453と、クランプデバイス112とを備える。非線形出力ブロック453は、検出・作動部458と、停止部(deactivation portion)459とを備える。非線形入力ブロック451は、ESD PORモジュール102と、線形時不变(LTI)ブロック452とを備える。LTIBロック452は、それぞれ変数RC1、RC2、RC3、およびRC4を使用する4つの四半部454、455、456、および457に分割されているものとして示されている。四半部454および455は検出フィルタリングに関連し、四半部456および457は作動期間に関連する。四半部454および456は、その上に過渡抑制システムが作製されている集積回路の非給電状態に関連し、四半部455および457は、その上に過渡抑制システムが作製されている集積回路の給電状態に関連する。電圧レールは、四半部454および455の入力463に接続されており、

L T I ブロック 4 5 2 が過渡電圧増大について電圧レールを監視することが可能になっている。電圧レールは、E S D P O R モジュール 1 0 2 の入力 4 6 0 に接続されており、E S D P O R モジュール 1 0 2 が、集積回路が給電されていない場合には四半部 4 5 4 の変数 R C 1 もしくは四半部 4 5 6 の変数 R C 3 を L T I ブロック 4 5 2 が使用するための選択 4 6 1 、または集積回路が給電されている場合には四半部 4 5 5 の変数 R C 2 もしくは四半部 4 5 7 の変数 R C 4 を L T I ブロック 4 5 2 が使用するための選択 4 6 2 を行うことが可能である。

### 【 0 0 3 1 】

入力 4 6 3 に応答して、非給電状態について四半部 4 5 4 の変数 R C 1 または給電状態について四半部 4 5 5 の変数 R C 2 を適用して、L T I ブロック 4 5 2 は、非線形出力ブロック 4 5 3 の検出・作動部 4 5 8 に出力 4 6 4 を提供する。検出・作動部 4 5 8 は、非給電状態について四半部 4 5 4 の変数 R C 1 または給電状態について四半部 4 5 5 の変数 R C 2 を使用して L T I ブロック 4 5 2 によってフィルタリングされているものとしての入力 4 6 3 が、そのためにクランピングが作動されるべきである（たとえば、クランピング作動のスルーレート基準を満たす）過渡電圧増大であるか否かを検出し、そうである場合には、クランプ出力 4 6 5 においてクランプ信号をアサートし、当該信号はクランプデバイス 1 1 2 の入力に接続され、当該クランプデバイスは電圧レールに接続されており、電圧レール上の電圧をクランピングする。非線形出力ブロック 4 5 3 の検出・作動部はトリガ出力 4 6 6 を提供し、当該出力は、L T I ブロック 4 5 2 が非給電状態については四半部 4 5 6 の変数 R C 3 、または給電状態については四半部 4 5 7 の変数 R C 4 に基づいてクランプ信号の作動期間の制御を開始することを可能にするために、L T I ブロック 4 5 2 の作動期間四半部 4 5 6 および 4 5 7 に接続される。適切な変数値に基づく作動期間が経過した後、L T I ブロック 4 5 2 は出力 4 6 7 をアサートし、当該出力は非線形出力ブロック 4 5 3 の停止部 4 5 9 に接続される。出力 4 6 7 によって提供される停止信号を受信すると、停止部 4 5 9 はクランプ出力 4 6 5 におけるクランプ信号を停止し、それによって、クランプデバイス 1 1 2 に電圧レールにおける電圧のクランピングを停止させる。

### 【 0 0 3 2 】

図 5 は、少なくとも 1 つの実施形態に応じた、過渡電圧増大を検出し、クランプデバイスの導電状態を制御するための方法を示すフローチャートである。方法、はブロック 5 0 1 において、信号に基づいて第 1 の時間値と第 2 の時間値との間で選択することによって開始する。ブロック 5 0 1 から、方法はブロック 5 0 2 へと継続する。ブロック 5 0 2 において、存在する場合には、過渡電圧増大の検出が行われる。ブロック 5 0 2 から、方法は判断ブロック 5 0 3 へと継続する。判断ブロック 5 0 3 において、過渡電圧増大の検出が行われたか否かについて判断が為される。そうでない場合、方法はブロック 5 0 2 に戻る。そうである場合、方法はブロック 5 0 4 へと継続する。ブロック 5 0 4 において、トリガ信号の提供が行われる。ブロック 5 0 4 から、方法はブロック 5 0 5 へと継続する。ブロック 5 0 5 において、トリガ信号の増幅が行われる。ブロック 5 0 6 によって示されているように、ブロック 5 0 5 のトリガ信号の増幅は、トリガ信号の反転を含んでもよい。ブロック 5 0 5 から、方法はブロック 5 0 7 へと継続する。ブロック 5 0 7 において、クランプデバイスの導電状態の制御が行われる。ブロック 5 0 8 によって示されているように、クランプデバイスの導電状態の制御は、集積回路が給電状態にあるときは比例的に応答することを含んでもよく、これによって、電圧レールが損壊すること、およびリセットが発生することを防止することができる。ブロック 5 0 7 から、方法は判断ブロック 5 0 9 へと継続し、アクティブ期間が超過したか否かについて判断が為される。そうでない場合、方法はブロック 5 0 7 に戻る。そうである場合、方法はブロック 5 0 1 に戻る。

### 【 0 0 3 3 】

図 6 は、少なくとも 1 つの実施形態に応じた、過渡電圧増大を検出し、クランプデバイスの導電状態を制御するための方法を示すフローチャートである。方法はブロック 6 0 1 において、信号を受信することによって開始する。ブロック 6 0 1 から、方法はブロック

10

20

30

40

50

602へと継続する。ブロック602において、第2の信号の受信が行われる。ブロック602から、方法はブロック603へと継続する。ブロック603において、集積回路が非給電状態にあるか、または給電状態にあるかに応じて、非給電状態については線形時不变(LTI)関数の変数の第1の値、または給電状態についてはLTI関数の変数の第2の値の選択が行われる。ブロック604によって示されているように、ブロック603の動作は、非給電状態または給電状態を表す非給電／給電信号に基づいて実行されてもよい第1の値または第2の値を選択することを含んでもよい。ブロック605によって示されているように、ブロック604の動作は、上記信号および第2の信号に基づいて第1の値または第2の値を選択することを含んでもよい。選択は、上記信号および第2の信号に基づいて第1の値、第2の値、第3の値、および第4の値の間で選択することを含んでもよい。ブロック606によって示されているように、ブロック603の動作は、非作動／作動信号に基づいて選択することを含んでもよい。非作動／作動信号は、クランプデバイスの導電状態の制御の非作動状態または作動状態を表し得る。ブロック603から、方法はブロック607へと継続する。ブロック607において、存在する場合には、過渡電圧増大の検出が行われる。ブロック607から、方法は判断ブロック608へと継続する。判断ブロック608において、過渡電圧増大の検出が行われたか否かについて判断が為される。そうでない場合、方法はブロック607に戻る。そうである場合、方法はブロック609へと継続する。ブロック609において、クランプデバイスの導電状態の制御が行われる。ブロック609から、方法は判断ブロック610へと継続する。判断ブロック610において、クランピングのアクティブ期間が経過したか否かについて判断が為される。そうでない場合、方法はブロック609に戻る。そうである場合、方法はブロック601に戻る。

#### 【0034】

少なくとも1つの実施形態に応じて、トリガ回路のトリガの感応性(triggering sensitivity)は、たとえば、電圧レールまたは過渡抑制が所望される任意の回路内の任意の他のノードであってもよい回路ノードにおける電圧の変化の速度に関する比較の根拠としての第1の時間値または第2の時間値に依存する。トリガ回路は、変化の速度が第1の時間値または第2の時間値に対応する変化の速度よりも大きいときはクランプ要素をトリガし、変化の速度が第1の時間値および第2の時間値に対応する変化の速度よりも小さいときはクランプ要素をトリガしない。

#### 【0035】

立ち上がり時間検出器、および、ESDが検出されるときにレールクランプを完全にオンにするラッチを有するCMOS製品のための既存のESD保護ネットワークであって、アクティブなレールクランプは全くオンにならないか、または完全にオンになるかのいずれかであるため給電過渡事象(すなわち、システムレベルストレス)に良好に応答しない場合があり、それによって、正電圧レールVDDを損壊させ、チップをリセット状態にする可能性がある、既存のESD保護ネットワークとは異なり、少なくとも1つの実施形態は、非給電ESDと給電過渡事象とを区別し、給電過渡事象の間はラッチされたクランプをオンにするモードではなく、電圧調整モードに入る。この調整モードにおいて、トリガ回路は、供給電圧増大に比例してオンになり、それによって損壊させる供給が回避される。

#### 【0036】

少なくとも1つの実施形態は、比例トリガ方式に基づいて、遠隔した電圧基準回路の必要を回避する。そのような遠隔した基準電圧(Vref)生成器は、相当量のダイ面積を占有する場合があり、機能的問題(たとえば、電源投入中の直流電流(DC)漏れ、近傍の電流注入に感應する、など)が発生しやすい場合があり、TCから遠隔して配置されることによって、たとえば、電力バス上の電圧降下に起因して信号伝達問題および性能問題を引き起こす場合がある。集積回路の導体はディスクリート回路の導体と比較して小型で抵抗性である傾向にある。電流が相対的に抵抗の高いIC電力バスのような集積回路導体を流れる結果として電圧降下が生じる可能性があり、電圧降下は、オームの法則に従つて

10

20

30

40

50

、導体を通じて流れる電流に導体の抵抗を乗算した値に等しい。さらに、複数の T C がともに接続されてそれらのうちの少なくとも 1 つが大きい電圧降下を受ける状況においては、その 1 つの T C が誤ってトリガされる結果として、機能不全が広範囲に拡散して生じる可能性がある。独立型の V r e f 生成器の必要をなくすことによって、相対的に抵抗性の集積回路導体からの独立が達成することができ、T C の誤ったトリガが回避されることができる。従って、ダイ面積（たとえば、コスト）の節約、チップの機能的信頼性の増大、過渡ストレス事象の間の E S D クランプ応答の改善（たとえば、E S D 応答性能の改善）が実現されることがある。

### 【 0 0 3 7 】

少なくとも 1 つの実施形態に応じて、非給電チップ動作と給電チップ動作とを区別することによって複数の異なる E S D クランプトリガ応答を提供することができるトリガ回路（T C ）が提供される。そのような T C は、その区別を行うための P O R （「パワー・オン・リセット」）信号を受信し、P O R 信号は、たとえば、パッドリング内に（たとえば、V S S パッド内に）含まれている小型 E S D P O R 回路によって提供されることがある。そのような T C は、別個の電圧基準（V r e f ）生成回路を必要とすることなく機能することができる。P O R 信号およびトリガ回路出力ノードの論理状態に基づいて R C 検出段内の抵抗器値（r e s i s t o r v a l u e ）を切り替えることによって、T C において複数の異なる E S D 応答が達成される。選択可能な抵抗器値と、すべての選択可能な抵抗器値について同じままであることができる共通のキャパシタ値との組み合わせが、抵抗容量（R C ）時間値を提供し、それによって、共通のキャパシタ値と組み合わさったいくつかの選択可能な抵抗器値が、いくつかの R C 時間値を提供することが可能になり、これは、P O R 信号およびトリガ信号に応じていくつかの E S D 応答を提供するために利用される。給電過渡ストレス事象（p o w e r e d t r a n s i e n t s t r e s s e v e n t s ）の間の比例トリガモードは、大きい R 値を選択することによって達成される。それゆえ、初期供給電圧が、T C のための内部基準電圧を提供するキャパシタ C 上に蓄積され、それによって、遠隔した電圧基準回路の必要が回避され、遠隔した電圧基準回路に依存するトリガ回路に関連する問題が回避される。

### 【 0 0 3 8 】

少なくとも 1 つの実施形態に応じて、トリガ回路は、R C フィルタ段を備え、制御信号に応じて R \* C 値が切り替えられることができる。少なくとも 1 つの実施形態に応じて、トリガ回路は、R C フィルタ段の出力信号を検出および增幅するための 1 以上のインバータ段を備え、インバータ段（複数の場合もあり）の出力（T C 出力）は 1 以上のレール・クランプ・デバイスのゲート端子を駆動する。少なくとも 1 つの実施形態に応じて、トリガ回路は、P O R 回路によって監視されている（たとえば、E S D \_ B O O S T 電圧レール上の）ノードまたはバスにおける 0 ボルトから始まる電圧の増大（すなわち、電圧ランプ）があるときはいつでもハイ論理レベルにあり、チップが完全に給電されたときはロー論理レベルにある P O R 信号を受信する。たとえば、P O R 信号は、電源投入（すなわち、電力が最初に集積回路に印加されるとき）または非給電 E S D 事象の間はハイ論理レベルにあり、チップが完全に給電されているとき（たとえば、給電 E S D 事象の間）はロー論理レベルにある。少なくとも 1 つの実施形態に応じて、トリガ回路は、R \* C 値を変更することによって T C の動作モードを設定する制御ロジックを備える。P O R 信号および T C 出力（トリガ）信号は制御ロジックに対する入力として役割を果たす。少なくとも 1 つの実施形態に応じて、トリガ回路は、R C 要素に基づいて 4 つの異なる時間値を提供する。たとえば、集積回路が非給電状態にある（たとえば、P O R 信号 = 1 ）とき、トリガ回路は、過渡事象検出のための約 1 0 0 n s の時間値、および、アクティブなクランプ応答のオン時間のために約 5 μ s の時間値を提供し、集積回路が給電状態にある（たとえば、P O R 信号 = 0 ）とき、トリガ回路は、過渡事象検出のための約 1 0 μ s の時間値、および、アクティブなクランプ応答のオン時間のために約 2 0 m s の時間値を提供する。

### 【 0 0 3 9 】

少なくとも 1 つの実施形態に応じて、集積回路の非給電状態に関する検出範囲を制御す

10

20

30

40

50

るための時間値は、10ナノ秒～1マイクロ秒である。少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する検出範囲を制御するための時間値は、20ナノ秒～50ナノ秒である。少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する検出範囲を制御するための時間値は、50ナノ秒～200ナノ秒である。

#### 【0040】

少なくとも1つの実施形態に応じて、集積回路の給電状態に関する検出範囲を制御するための時間値は、1マイクロ秒～100マイクロ秒である。少なくとも1つの実施形態に応じて、集積回路の給電状態に関する検出範囲を制御するための時間値は、2マイクロ秒～50マイクロ秒である。少なくとも1つの実施形態に応じて、集積回路の給電状態に関する検出範囲を制御するための時間値は、5マイクロ秒～20マイクロ秒である。

10

#### 【0041】

少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する作動期間を制御するための時間値は、500ナノ秒～50マイクロ秒である。少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する作動期間を制御するための時間値は、1マイクロ秒～20マイクロ秒である。少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する作動期間を制御するための時間値は、2マイクロ秒～10マイクロ秒である。

#### 【0042】

少なくとも1つの実施形態に応じて、集積回路の給電状態に関する作動期間を制御するための時間値は、2ミリ秒～200ミリ秒である。少なくとも1つの実施形態に応じて、集積回路の給電状態に関する作動期間を制御するための時間値は、5ミリ秒～100ミリ秒である。少なくとも1つの実施形態に応じて、集積回路の給電状態に関する作動期間を制御するための時間値は、10ミリ秒～50ミリ秒である。

20

#### 【0043】

少なくとも1つの実施形態に応じて、検出範囲を制御するための時間値は、集積回路の給電状態に関しては、集積回路の非給電状態に関するものよりも約100倍大きい。少なくとも1つの実施形態に応じて、検出範囲を制御するための時間値は、集積回路の給電状態に関しては、集積回路の非給電状態に関するものよりも50～200倍大きい。

#### 【0044】

少なくとも1つの実施形態に応じて、作動期間を制御するための時間値は、集積回路の給電状態に関しては、集積回路の非給電状態に関するものよりも約4,000倍大きい。少なくとも1つの実施形態に応じて、作動期間を制御するための時間値は、集積回路の給電状態に関しては、集積回路の非給電状態に関するものよりも1,000～10,000倍大きい。

30

#### 【0045】

少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する作動期間を制御するための時間値は、集積回路の非給電状態に関する検出範囲を制御するための時間値よりも約50倍大きい。少なくとも1つの実施形態に応じて、集積回路の非給電状態に関する作動期間を制御するための時間値は、集積回路の非給電状態に関する検出範囲を制御するための時間値よりも20～100倍大きい。

#### 【0046】

少なくとも1つの実施形態に応じて、集積回路の給電状態に関する作動期間を制御するための時間値は、集積回路の給電状態に関する検出範囲を制御するための時間値よりも約2,000倍大きい。少なくとも1つの実施形態に応じて、集積回路の給電状態に関する作動期間を制御するための時間値は、集積回路の給電状態に関する検出範囲を制御するための時間値よりも500～10,000倍大きい。

40

#### 【0047】

少なくとも1つの実施形態に応じて、2つのモード、すなわち、(非給電過渡ストレス事象のための)正規オン／オフ・スタイル・トリガ・モードおよび(給電過渡ストレス事象のための)比例調整モードにおいて動作することができるE S D T Cが提供される。そのようなE S D T Cは、別個の電圧基準回路(V r e f)を必要としない。2つの動

50

作モード（非給電対給電）を達成するのに、過渡 E S D トリガ回路内の検出 R C 時間値の切り替えが利用される。給電動作モードは、過渡電圧増大に比例的に応答し、電圧レール上の供給電圧を損なうことを回避し、システムの意図しないリセットが引き起こされるのを回避することを可能にする。

#### 【 0 0 4 8 】

少なくとも 1 つの実施形態に応じて、I / O パッドレイアウト面積要件がより小さいことに起因して、ダイサイズ低減が達成されることができる。少なくとも 1 つの実施形態に応じて、C M O S 半導体製品について、過渡電磁波耐性性能の改善をもたらすことができる。

#### 【 0 0 4 9 】

少なくとも 1 つの実施形態に応じて、集積回路において過渡電圧増大を検出するためのトリガ回路は、耐電圧回路設計ライブラリにおいて定義されてもよい。そのような耐電圧回路設計ライブラリは、正電圧レール V D D 1 1 8 を上回る電圧が発生し得る集積回路 I O ピンを実装するために使用されてもよい。

#### 【 0 0 5 0 】

少なくとも 1 つの実施形態に応じて、集積回路において過渡電圧増大を検出するためのトリガ回路は、複数のローカルなトリガ回路を遠隔して配置することを可能にし、複数のローカルなトリガ回路がそれらのトリガ信号を互いに通信するか、または複数のローカルなトリガ回路のうちの他者のトリガ信号を認識するように構成される場合であっても、複数のローカルなトリガ回路の間でトリガ回路が競合することを回避する。

#### 【 0 0 5 1 】

少なくとも 1 つの実施形態に応じて、方法は、集積回路上の過渡電圧増大を検出することと、過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することとを含む。検出することおよび制御することのうちの少なくとも一方は、第 1 の時間値および第 2 の時間値に依存する。第 1 の時間値は集積回路の非給電状態に適用可能であり、第 2 の時間値は集積回路の給電状態に適用可能である。第 1 の時間値および第 2 の時間値は共通の容量性素子の容量値に応じて決まる。少なくとも 1 つの実施形態に応じて、検出することは第 1 の時間値および第 2 の時間値に依存し、検出することは、過渡電圧増大の速度が検出範囲内にあることに応答して行われ、検出範囲は集積回路の非給電状態については第 1 の時間値に応じて決まり、集積回路の給電状態については第 2 の時間値に応じて決まる。30

。少なくとも 1 つの実施形態に応じて、制御することは第 1 の時間値および第 2 の時間値に依存し、制御することはアクティブ期間にわたって行われ、アクティブ期間は集積回路の非給電状態については第 1 の時間値に応じて決まり、集積回路の給電状態については第 2 の時間値に応じて決まる。少なくとも 1 つの実施形態に応じて、方法は、集積回路の非給電状態および給電状態に応答する信号に基づいて第 1 の時間値と第 2 の時間値との間で選択することをさらに含む。少なくとも 1 つの実施形態に応じて、過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することは、給電状態の以前から存在している電圧に対する過渡電圧増大に比例して、給電状態における過渡電圧増大に応答することを含む。少なくとも 1 つの実施形態に応じて、方法は、過渡電圧増大の検出に応答してトリガ信号を提供することと、トリガ信号を增幅することとをさらに含む。少なくとも 1 つの実施形態に応じて、トリガ信号を增幅することは、トリガ信号を反転することを含む。40

。少なくとも 1 つの実施形態に応じて、検出することは第 1 の時間値および第 2 の時間値に依存し、制御することは第 3 の時間値および第 4 の時間値に依存し、第 3 の時間値および第 4 の時間値は共通の容量性素子の容量値に応じて決まる。少なくとも 1 つの実施形態に応じて、検出することは、過渡電圧増大の速度が検出範囲内にあることに応答して行われ、検出範囲は集積回路の非給電状態については第 1 の時間値に応じて決まり、集積回路の給電状態については第 2 の時間値に応じて決まり、制御することはアクティブ期間にわたって行われ、アクティブ期間は集積回路の非給電状態については第 3 の時間値に応じて決まり、集積回路の給電状態については第 4 の時間値に応じて決まる。少なくとも 1 つの実施形態に応じて、第 1 の時間値は第 2 の時間値に等しくない。

10

20

30

40

50

## 【0052】

少なくとも1つの実施形態に応じて、集積回路は、クランプデバイスと、集積回路上の過渡電圧増大を検出するためのトリガ回路とを備える。トリガ回路は、過渡電圧増大を制限するためにクランプデバイスの導電状態を制御する。トリガ回路は、或る容量値を有する共通の容量性素子を備える。第1の時間値および第2の時間値は共通の容量性素子の容量値に応じて決まる。第1の時間値は集積回路の非給電状態に適用可能であり、第2の時間値は集積回路の給電状態に適用可能である。第1の時間値および第2の時間値は、その範疇にある過渡電圧増大の速度が、トリガ回路をアクティブにする検出範囲、および、クランプデバイスの導電状態の制御のアクティブ期間がそれに応じて決まる「オン」時間から成る群から選択されるトリガ回路パラメータを制御する。少なくとも1つの実施形態に応じて、第1の時間値は集積回路の非給電状態に関する検出範囲を決定し、第2の時間値は集積回路の給電状態に関する検出範囲を決定する。少なくとも1つの実施形態に応じて、トリガ回路は、共通の容量性素子に結合されている入力を有するドライバ回路を備え、ドライバ回路は、入力においてフィルタリングされた信号を検出および增幅し、クランプデバイスの制御端子を駆動するためのトリガ回路出力信号を提供するための1以上のインバータ段を備える。少なくとも1つの実施形態に応じて、トリガ回路は、集積回路が非給電状態にあるときはより高い導電性を提供し、集積回路が給電状態にあるときは電圧調整を提供するために制御されたより低い導電性を提供するように制御する。少なくとも1つの実施形態に応じて、トリガ回路は、集積回路の非給電状態の間はより高い導電性のアクティブ期間を決定するための第3の時間値を有し、集積回路の給電状態の間は制御されたより低い導電性のアクティブ期間を決定するための第4の時間値を有し、第3の時間値および第4の時間値は共通の容量性素子の容量値に応じて決まる。10

## 【0053】

少なくとも1つの実施形態に応じて、方法は、集積回路の非給電状態については線形時不变(LETI)関数の変数の第1の値、および、集積回路の給電状態については線形時不变(LETI)関数の変数の第2の値を選択することであって、第1の値および第2の値は共通のリアクタンス素子に応じて決まる、選択することと、集積回路上の過渡電圧増大を検出することと、過渡電圧増大を制限するためにクランプデバイスの導電状態を制御することとを含み、検出することおよび制御することのうちの少なくとも一方はLETI関数に依存する。少なくとも1つの実施形態に応じて、検出することはLETI関数に依存し、検出することは、過渡電圧増大の速度が検出範囲内にあることに応答して行われ、検出範囲はLETI関数に応じて決まる。少なくとも1つの実施形態に応じて、制御することはLETI関数に依存し、制御することはアクティブ期間にわたって行われ、アクティブ期間はLETI関数に応じて決まる。20

少なくとも1つの実施形態に応じて、方法は、集積回路の非給電状態および給電状態に応答する信号を受信することをさらに含み、選択することは、当該信号に基づいてLETI関数の変数の第1の値と第2の値との間で選択することをさらに含む。少なくとも1つの実施形態に応じて、方法は第2の信号を受信することをさらに含み、第2の信号は、当該第2の信号の第1の状態においてはクランプデバイスの導電状態の制御の非作動状態を表し、当該第2の信号の第2の状態においてはクランプデバイスの導電状態の制御の作動状態を表し、LETI関数の変数の第1の値と第2の値との間で選択することは、上記信号および第2の信号に基づいて、集積回路の非給電状態についての検出のためにはLETI関数の変数の第1の値、集積回路の給電状態についての検出のためにはLETI関数の変数の第2の値、集積回路の非給電状態についての制御のためにはLETI関数の変数の第3の値、および、集積回路の給電状態についての制御のためにはLETI関数の変数の第4の値を選択することを含み、第1の値、第2の値、第3の値、および第4の値は共通のリアクタンス素子に応じて決まる。30

少なくとも1つの実施形態に応じて、信号はパワー・オン・リセット(POR)信号である。少なくとも1つの実施形態に応じて、方法は、クランプデバイスの導電性の制御の非作動状態および作動状態に応答する信号を受信することをさらに含み、選択することは、信号に基づいてLETI関数の変数の第1の値および第2の値を検出または制御のいずれに適用すべきかを選択することを含む。40

50

## 【0054】

本明細書において、具体的な実施形態を参照して本発明を説明したが、添付の特許請求の範囲に明記されているような本発明の範囲から逸脱することなくさまざまな改変および変更を為すことができる。従って、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明の範囲内に含まれることが意図されている。本明細書において具体的な実施形態に関して記載されているいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるようには意図されていない。

## 【0055】

さらに、上述の動作の機能間の境界は例示にすぎないことを当業者は認識しよう。複数の動作の機能を单一の動作に組み合わせてもよく、かつ／または単一の動作の機能を追加の動作に分散させてもよい。その上、代替的な実施形態は、特定の動作の複数のインスタンスを含んでもよく、動作の順序はさまざまな他の実施形態においては変更してもよい。

10

## 【0056】

利益、他の利点、および問題に対する解決策が具体的な実施形態に関連して上記で説明された。しかしながら、利益、利点、問題に対する解決策、および、任意の利益、利点、または解決策を発生させまたはより明白にする任意の特徴（複数の場合もあり）は、特許請求項のいずれかまたはすべての決定的な、必要とされる、または必須の特徴であると解釈されるべきではない。

【図1】

【図2】

【 四 3 】

【 四 4 】

【 义 5 】

【 四 6 】

---

フロントページの続き

(56)参考文献 米国特許出願公開第2008/007882(US,A1)

米国特許出願公開第2011/222196(US,A1)

特表2013-526079(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| H 03 K | 19 / 003  |

| H 01 L | 21 / 822  |

| H 01 L | 27 / 04   |

| H 03 K | 19 / 0175 |