(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6094819号

(P6094819)

(45) 発行日 平成29年3月15日(2017.3.15)

(24) 登録日 平成29年2月24日(2017.2.24)

(51) Int.Cl.

F 1

H01L 33/14 (2010.01)

H01L 33/36 (2010.01)H01L 33/14

H01L 33/36

請求項の数 13 (全 36 頁)

(21) 出願番号 特願2013-258350 (P2013-258350)

(22) 出願日 平成25年12月13日 (2013.12.13)

(65) 公開番号 特開2015-115543 (P2015-115543A)

(43) 公開日 平成27年6月22日 (2015.6.22)

審査請求日 平成28年8月5日 (2016.8.5)

早期審査対象出願

(73) 特許権者 000102212

ウシオ電機株式会社

東京都千代田区丸の内一丁目6番5号

(74) 代理人 110000729

特許業務法人 ユニアス国際特許事務所

(72) 発明者 井上 隆博

兵庫県姫路市別所町佐土1194番地 ウシオ電機株式会社内

(72) 発明者 月原 政志

兵庫県姫路市別所町佐土1194番地 ウシオ電機株式会社内

(72) 発明者 三好 晃平

兵庫県姫路市別所町佐土1194番地 ウシオ電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体発光素子及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、p型半導体層、発光層及びn型半導体層を含む半導体層を有してなる半導体発光素子であって、

前記半導体層の一部上面に接触して形成され、電流供給線と連結される電流供給部を含む第一電極と、

前記電流供給部の非形成領域の鉛直下方の一部領域に形成され、前記半導体層の一部底面に接触し、前記発光層からの射出光を反射させる材料で形成された第二電極と、

前記電流供給部の鉛直下方を含む領域に形成され、前記半導体層の一部底面に接触する第一電流遮断層とを有し、

前記第一電流遮断層と前記半導体層との接触箇所における接触抵抗が、前記第二電極と前記半導体層との接触箇所における接触抵抗よりも高く、

前記基板面に平行な方向に関して前記第一電流遮断層の形成箇所よりも前記電流供給部から遠い位置において、前記第一電極の形成領域の鉛直下方を含む領域に形成され、前記半導体層の一部底面に接触する第二電流遮断層を有し、

前記第二電流遮断層と前記半導体層との接触箇所における接触抵抗が、前記第二電極と前記半導体層との接触箇所における接触抵抗よりも高く、前記第一電流遮断層と前記半導体層との接触箇所における接触抵抗よりも低いことを特徴とする半導体発光素子。

## 【請求項 2】

前記基板の上層に形成された導電層を有し、

10

20

前記第二電極、前記第一電流遮断層、及び前記第二電流遮断層の底面が前記導電層の上面に接触していることを特徴とする請求項1に記載の半導体発光素子。

【請求項3】

前記第一電流遮断層及び前記第二電流遮断層は、前記発光層からの射出光を反射させる材料で構成されることを特徴とする請求項1又は2に記載の半導体発光素子。

【請求項4】

前記第一電流遮断層及び前記第二電流遮断層が、Ag、Al、Ni、Ti、又はPtを含有する金属材料で構成されていることを特徴とする請求項3に記載の半導体発光素子。

【請求項5】

前記導電層は、最上層に前記発光層からの射出光を反射させる材料で形成された反射層を有し、10

前記第一電流遮断層及び前記第二電流遮断層は、前記発光層からの射出光を透過させる材料で構成されていることを特徴とする請求項2に記載の半導体発光素子。

【請求項6】

前記第一電流遮断層及び前記第二電流遮断層がITOを含有する材料で構成されていることを特徴とする請求項5に記載の半導体発光素子。

【請求項7】

前記基板面に平行な方向に関し、前記電流供給部の幅をd、前記第一電流遮断層の幅をDとしたとき、20

1.1d D 3d

の関係を満たすことを特徴とする請求項1～6のいずれか1項に記載の半導体発光素子。20

【請求項8】

請求項1に記載の半導体発光素子の製造方法であって、

成長基板上に前記半導体層を形成する工程(a)と、

前記半導体層の第一面上の所定の領域に前記第二電極を形成するための材料膜を成膜した後、コンタクトアニールを施して前記第二電極を形成する工程(b1)と、30

前記工程(b1)の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない所定の領域に前記第一電流遮断層を形成するための材料膜を成膜した後、前記工程(b1)よりも低温度でコンタクトアニール処理を行って前記第一電流遮断層を形成する工程(b2)と、30

前記工程(b2)の実行後、前記成長基板とは別の前記基板を、前記成長基板とは反対側から貼り合わせた後、前記成長基板を剥離する工程(e)と、

前記工程(e)の実行後、前記半導体層の前記第一面とは反対側の第二面上に前記第一電極を形成する工程(c)と、

前記第一電極上において、前記基板の面に垂直な方向に関して前記第一電流遮断層に対向する領域の一部に前記電流供給線を連結して前記電流供給部を形成する工程(d)とを有することを特徴とする半導体発光素子の製造方法。

【請求項9】

前記工程(a)及び(b1)の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない所定の領域に前記第二電流遮断層を形成するための材料膜を成膜した後、前記工程(b1)よりも低温度且つ前記工程(b2)よりも高温度でコンタクトアニール処理を行って前記第二電流遮断層を形成する工程(b3)を有し、40

前記工程(b2)は、前記工程(b3)の実行後、前記半導体層の前記第一面上であって前記第二電極及び前記第二電流遮断層が形成されていない箇所に前記第一電流遮断層を形成するための材料膜を成膜した後、前記工程(b1)及び前記工程(b3)よりも低温度でコンタクトアニール処理を行って前記第一電流遮断層を形成する工程であることを特徴とする請求項8に記載の半導体発光素子の製造方法。

【請求項10】

前記工程(b1)、前記工程(b2)、及び前記工程(b3)で成膜される材料膜が同50

一の金属材料で構成されることを特徴とする請求項 8 又は 9 に記載の半導体発光素子の製造方法。

【請求項 1 1】

前記工程 (b 1) で成膜される材料膜が金属材料であり、前記工程 (b 2) 及び前記工程 (b 3) で成膜される材料膜がITOであり、

前記工程 (b 2) の実行後、前記第二電極、前記第一電流遮断層、及び前記第二電流遮断層に跨るように、金属材料膜を成膜後、前記工程 (b 2) と同等以下の温度でコンタクトアニール処理を行って反射層を形成する工程 (b 4) を有し、

前記工程 (b 4) の実行後に、前記工程 (c) を実行することを特徴とする請求項 8 又は 9 に記載の半導体発光素子の製造方法。

10

【請求項 1 2】

請求項 1 に記載の半導体発光素子の製造方法であって、

成長基板上に前記半導体層を形成する工程 (a) と、

前記半導体層の第一面上の所定の領域に、最上層に  $P_t$  を含む多層構造を有する材料膜を成膜した後、コンタクトアニールを施して前記第二電極を形成する工程 (b 1) と、

前記工程 (b 1) の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない箇所に、 $P_t$  の膜厚を前記工程 (b 1) よりも薄膜として、最上層に  $P_t$  を含む多層構造を有する前記材料膜を成膜した後、コンタクトアニール処理を行って前記第一電流遮断層を形成する工程 (b 2) と、

前記工程 (b 2) の実行後、前記成長基板とは別の前記基板を、前記成長基板とは反対側から貼り合わせた後、前記成長基板を剥離する工程 (e) と、

20

前記工程 (e) の実行後、前記半導体層の前記第一面とは反対側の第二面上に前記第一電極を形成する工程 (c) と、

前記第一電極上において、前記基板の面に垂直な方向に関して前記第一電流遮断層に対向する領域の一部に前記電流供給線を連結して前記電流供給部を形成する工程 (d) とを有することを特徴とする半導体発光素子の製造方法。

【請求項 1 3】

前記工程 (a) 及び (b 1) の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない所定の領域に、 $P_t$  の膜厚を前記工程 (b 1) より薄膜で且つ前記工程 (b 2) より厚膜として前記材料膜を成膜した後、コンタクトアニール処理を行って前記第二電流遮断層を形成する工程 (b 3) を有し、

30

前記工程 (b 2) は、前記工程 (b 3) の実行後、前記半導体層の前記第一面上であって前記第二電極及び前記第二電流遮断層が形成されていない箇所に、 $P_t$  の膜厚を前記工程 (b 1) 及び前記工程 (b 3) よりも薄膜として前記材料膜を成膜した後、コンタクトアニール処理を行って前記第一電流遮断層を形成する工程であることを特徴とする請求項 1 2 に記載の半導体発光素子の製造方法。

【発明の詳細な説明】

【技術分野】

40

【0001】

本発明は、基板上に、p型半導体層、発光層及びn型半導体層を含む半導体層を有してなる半導体発光素子に関する。また、本発明はこのような半導体発光素子の製造方法に関する。

【背景技術】

【0002】

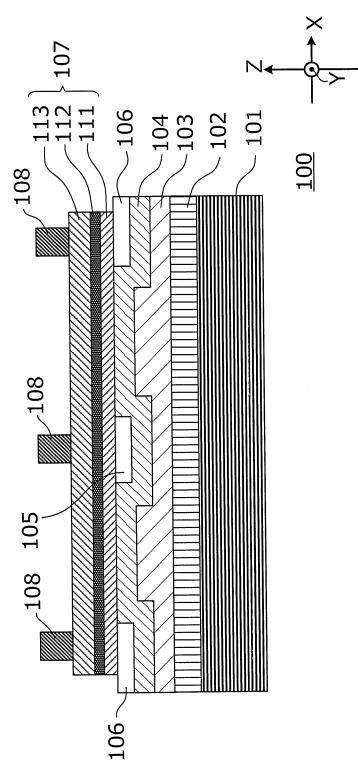

従来の半導体発光素子として、例えば下記特許文献 1 には、図 9 に示す構造が開示されている。

【0003】

図 9 は、特許文献 1 に開示された半導体発光素子の断面図を模式的に示したものである

50

。従来の半導体発光素子100は、支持基板101上に、ボンディング層102、反射電極103、オーミック接触層104、電流遮断層105、アイソレーション層106、半導体層107及びn側電極108を備えて構成される。半導体層107は、p型半導体層111、発光層112及びn型半導体層113が下からこの順に積層されて構成されている。

【0004】

以下では、支持基板101の基板面に平行な平面をX-Y平面とし、この平面に垂直な方向をZ方向と規定する。なお、図9に示す半導体発光素子100は、紙面上向き(Z方向)に光が取り出される素子である。

【0005】

ボンディング層102は、支持基板101と反射電極103を貼り合わせる際に、両者の密着性を高めるために設けられた導電性材料であり、例えばハンダ等で構成される。反射電極103は、高い反射率を有する金属又は合金で形成されており、発光層112から支持基板101側(紙面下向き)に射出された光を当該反射電極103上で反射させることで、n側電極108側に形成された光取り出し面に導く。これにより、光取り出し効率を高める効果が得られる。

【0006】

電流遮断層105は、n側電極108の鉛直下方の位置において、半導体層107の底面に接触するように形成されており、絶縁性材料又は半導体層107との間でショットキー接觸を形成する材料で形成される。特許文献1によれば、この電流遮断層105としては、例えば、 $\text{SiO}_2$ 、 $\text{SiO}_x$ 、 $\text{SiO}_x\text{N}_y$ 、 $\text{Si}_3\text{N}_4$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{TiO}_x$ 、 $\text{Ti}$ 、 $\text{Al}$ 、 $\text{Cr}$ のうちの少なくとも1つを含む構成であればよいという記述がされている。

【0007】

アイソレーション層106は、隣接する半導体層107を素子単位で分離したときの、隣接素子間の絶縁性を確保する目的で設けられた絶縁層であり、例えば、 $\text{SiO}_2$ 、 $\text{SiN}$ 、又は $\text{Al}_2\text{O}_3$ 等で形成される。

【0008】

オーミック接触層104は、ITO等の光透過性を有した導電性酸化膜で構成される。オーミック接触層104は、反射電極103の上層に形成されており、上面の一部が半導体層107の底面に接觸している。より詳細には、オーミック接触層104は、n側電極108の鉛直下方の位置においては半導体層107と接觸せずにアイソレーション層106又は電流遮断層105と接觸しており、鉛直上方にn側電極108が形成されていない領域の一部においては半導体層107と接觸している。オーミック接触層104は、半導体層107と接觸する箇所において、半導体層107との間でオーミック接觸が形成されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2012-244158号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0010】

図9に示すように、半導体発光素子100は、n側電極108の鉛直下方の領域において、反射電極103やオーミック接触層104よりも高抵抗を示す電流遮断層105又はアイソレーション層106を半導体層107の底面に接觸させている。これによって、n側電極108の鉛直下方に位置する半導体層107の領域内において、鉛直方向(Z方向)に電流が集中的に流れるのを緩和でき、発光層112内を流れる電流を水平方向(X-Y平面に平行な方向)に拡げて、発光層112内の広範囲で発光させて光出力を高める効果が得られる。

50

## 【0011】

ところで、近年、半導体発光素子は従来よりも更に高い光出力が要求されるようになってきており、これに伴って、高い電流を供給しても安定的に高出力の光を発光する素子が求められている。

## 【0012】

本発明者の鋭意研究により、従来の構成では、高い電流を注入した場合、電流供給線（ボンディングワイヤ等）が連結されるn側電極108上の箇所（以下、「電流供給部」と呼ぶ。）の付近に電流が集中し、温度が上昇することが分かった。そして、このような高電流注入を一定時間継続すると、電流供給部の近傍に形成されたn型半導体層113に対して、劣化、割れ又は溶融等が生じ、素子寿命が短くなることが分かった。この課題は、10本発明者の鋭意研究によって見出されたものである。

## 【0013】

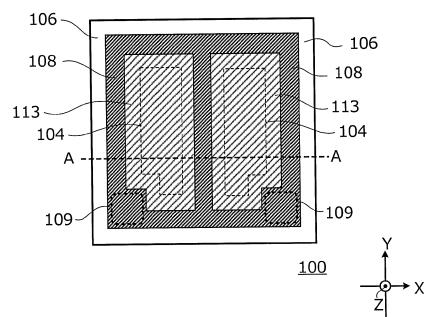

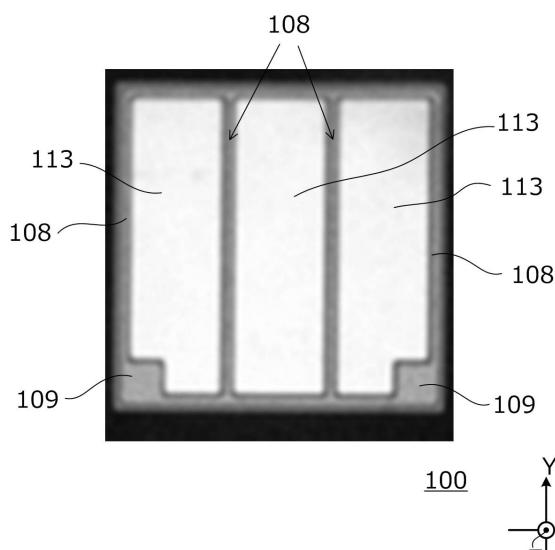

図10は、図9に示す従来の半導体発光素子100を上から見たときの模式図である。図11は、図10の構成を有する素子の上面視の写真である。なお、図9は、図10におけるA-A線（X方向に平行な線）における模式的な断面図に相当する。

## 【0014】

図10に示すように、電流供給部109はn側電極108の一部領域に相当する。なお、図10では、電流供給部109の配置位置がY方向に偏りを有している場合を想定している。また、図10において、オーミック接触層104は半導体層107よりも下層にあるため、上面から見た場合には半導体層107に隠れて見えないが、理解のために破線によって表示している。20

## 【0015】

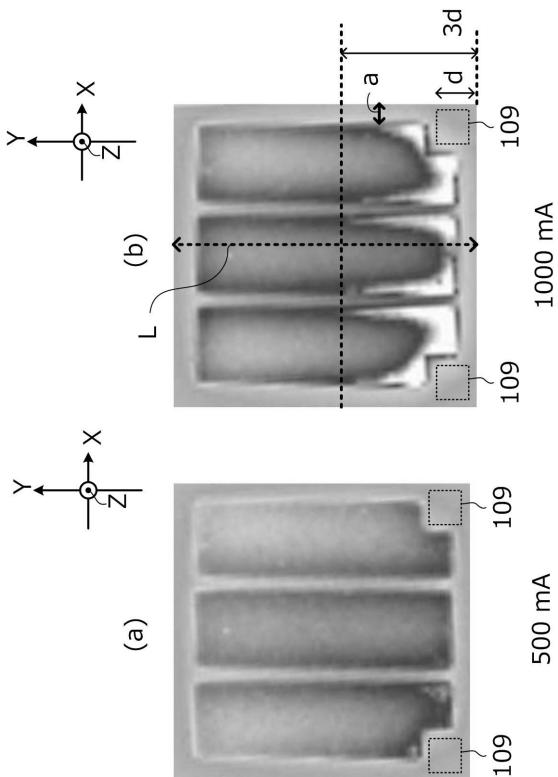

図12は、電流供給部109に対して500mA、1000mAを供給したときの半導体発光素子100の上面の温度分布を示す写真である。図12(a)に示すように、供給電流が500mA程度である場合には、電流供給部109近傍が他の箇所と比べて大きな温度差が生じるということはない。しかし、図12(b)に示すように、供給電流を1000mAという高電流にした場合、電流供給部109の近傍が白っぽくなっている。これは当該領域が極めて高温になっていることを示している。すなわち、図12(b)において、Y方向に関し、電流供給部109の近傍と、電流供給部109から離れた箇所との間には大きな温度差が生じていることが示されている。30

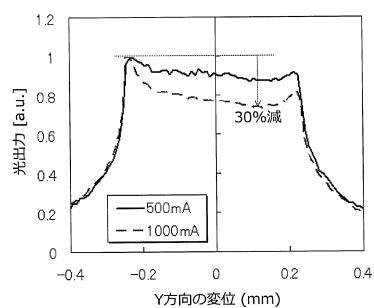

## 【0016】

図13は、素子上のY方向に係る位置に応じた光出力の分布を示すグラフであり、より詳細には、同一のY座標に関してX方向に光出力を積分して得られた値の分布として示したものである。図13では、素子中央の位置を基準として、+Y方向及び-Y方向に関する基準位置からの変位量をもって横軸としている。また、縦軸は光出力の相対値である。1000mAという高電流を供給した場合には、電流供給部109の近傍に比べて、電流供給部109から離れた箇所の光出力が70%程度に留まっており、電流供給部109近傍に高電流が集中していることが示唆される。

## 【0017】

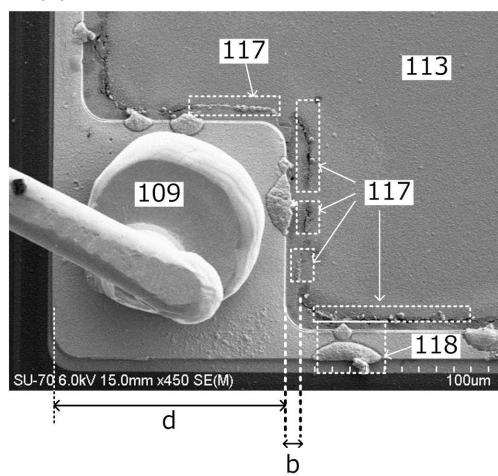

更に、図14は、従来の半導体発光素子100に対して、電流供給部109から1000mAの高い電流を20時間供給した後の上面の写真であり、走査電子顕微鏡によって撮影されたものである。n型半導体層113に割れ117や溶融118が生じていることが確認できる。40

## 【0018】

上記の課題に鑑み、本発明は、高電流を供給した場合であっても、電流供給部近傍の領域に電流が集中することが防止された半導体発光素子を実現することを目的とする。

## 【課題を解決するための手段】

## 【0019】

本発明は、基板上に、p型半導体層、発光層及びn型半導体層を含む半導体層を有してなる半導体発光素子であって、50

前記半導体層の一部上面に接触して形成され、電流供給線と連結される電流供給部を含む第一電極と、

前記電流供給部の非形成領域の鉛直下方の一部領域に形成され、前記半導体層の一部底面に接触し、前記発光層からの射出光を反射させる材料で形成された第二電極と、

前記電流供給部の鉛直下方を含む領域に形成され、前記半導体層の一部底面に接触する第一電流遮断層とを有し、

前記第一電流遮断層と前記半導体層との接触箇所における接触抵抗が、前記第二電極と前記半導体層との接触箇所における接触抵抗よりも高いことを特徴とする。

#### 【0020】

上記の構成によれば、第一電極の一部を構成する電流供給部の鉛直下方において半導体層と接触する第一電流遮断層は、電流供給部が形成されていない領域の鉛直下方において半導体層と接触する第二電極よりも、半導体層との間の接触抵抗が高くなるように形成される。このため、電流供給部に対して供給された電流は、接触抵抗の高い第一電流遮断層の形成領域、すなわち電流供給部の鉛直下方又はその近傍に向かっては流れにくくなり、接触抵抗の低い第二電極の形成領域に向かって流れやすくなる。この結果、電流供給部に供給された電流は、半導体層内を基板面に平行な方向に沿って流れやすくなる。

10

#### 【0021】

上記の内容は、本発明者の鋭意研究によって、駆動時に、第一電極のうちの特に電流供給部の近傍に電流が集中しやすいことを突き止めたことで見出されたものであり、特に電流供給部の鉛直下方を含む領域に高抵抗の第一電流遮断層を設けたことで、当該電流供給部の近傍に電流が集中することが防止される。この結果、電流供給部近傍の温度上昇が緩和され、高い電流を供給した場合であっても、素子の長寿命化が実現できる。

20

#### 【0022】

ここで、第二電極は、少なくとも電流供給部の非形成領域の鉛直下方の一部領域に形成されていればよく、第二電極の一部分が第一電極の鉛直下方に位置しているものとしても構わない。

#### 【0023】

上記半導体発光素子は、前記基板面に平行な方向に関して前記第一電流遮断層の形成箇所よりも前記電流供給部から遠い位置において、前記第一電極の形成領域の鉛直下方を含む領域に形成され、前記半導体層の一部底面に接触する第二電流遮断層を有し、

30

前記第二電流遮断層と前記半導体層との接触箇所における接触抵抗が、前記第二電極と前記半導体層との接触箇所における接触抵抗よりも高く、前記第一電流遮断層と前記半導体層との接触箇所における接触抵抗よりも低いものとしても構わない。

#### 【0024】

上記の構成によれば、第一電極の形成領域の鉛直下方の領域のうち、電流供給部の鉛直下方の領域には第一電流遮断層が形成され、電流供給部から遠い箇所には第二電流遮断層が形成される。第二電流遮断層は、第二電極よりは半導体層との接触抵抗が高く、第一電流遮断層よりは半導体層との接触抵抗が低くなるように形成されている。このため、第一電極の鉛直下方の領域に関していえば、第二電極よりも高抵抗の層が半導体層と接触しているため、第一電極から鉛直方向に電流が流れにくくなり、電流を水平方向に拡げる効果が実現される。更に、電流供給部の近傍と比較して、電流供給部から離れた箇所において半導体層との接触抵抗を低く設定しているため、電流供給部から供給された電流を、電流供給部から離れた箇所に向かって流しやすくなる。これにより、電流供給部の近傍における電流集中を防止しつつ、半導体層に流れる電流を水平方向に更に拡げる効果が得られる。つまり、光取り出し効率を高めつつ、高電流供給時における長寿命化が図られる。

40

#### 【0025】

上記半導体発光素子は、前記基板の上層に形成された導電層を有し、

前記第二電極、前記第一電流遮断層、及び前記第二電流遮断層の底面が前記導電層の上面に接触している構成としても構わない。

#### 【0026】

50

また、上記半導体発光素子は、前記第一電流遮断層及び前記第二電流遮断層を前記発光層からの射出光を反射させる材料で構成することもできる。より具体的には、前記第一電流遮断層及び前記第二電流遮断層を、Ag、Al、Ni、Ti、又はPtを含有する金属材料で構成することができる。

【0027】

上記構成によれば、発光層から基板側に向かって射出された光は、第二電極のみならず、第一電流遮断層及び第二電流遮断層の形成箇所でも、取り出し面側すなわち第一電極側に向かって反射させることができる。これにより、光取り出し効率を更に高めることができる。

【0028】

また、上記半導体発光素子において、前記導電層は、最上層に前記発光層からの射出光を反射させる材料で形成された反射層を有し、

前記第一電流遮断層及び前記第二電流遮断層は、前記発光層からの射出光を透過させる材料で構成されていても構わない。このとき、具体的な例として、前記第一電流遮断層及び前記第二電流遮断層は、ITOを含有する材料で構成することができる。

【0029】

上記構成によれば、発光層から基板側に向かって射出された光は、半導体層と接触している第二電極の形成箇所においては当該第二電極で反射され、半導体層と接触している第一電流遮断層及び第二電流遮断層の形成箇所においては、各電流遮断層を透過した後、その下層に形成されている反射層で反射される。これにより、取り出し面側すなわち第一電極側に光の進行方向を変えることができる。よって、この構成においても、光取り出し効率を更に高めることができる。

【0030】

また、上記半導体発光素子において、前記基板面に平行な方向に関し、前記電流供給部の幅をd、前記第一電流遮断層の幅をDとしたとき、

1.1d D 3d

の関係を満たす構成としても構わない。

【0031】

上記構成とすることで、電流供給部の近傍に電流が集中するのを緩和する効果を最大限発揮できる。

【0032】

また、本発明は、上記構成を有した半導体発光素子の製造方法であって、

基板上に前記半導体層を形成する工程(a)と、

前記半導体層の第一面上の所定の領域に前記第二電極を形成するための材料膜を成膜した後、コンタクトアニールを施して前記第二電極を形成する工程(b1)と、

前記工程(b1)の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない所定の領域に前記第一電流遮断層を形成するための材料膜を成膜した後、前記工程(b1)よりも低温度でコンタクトアニール処理を行って前記第一電流遮断層を形成する工程(b2)と、

前記工程(b2)の実行後、前記半導体層の前記第一面とは反対側の第二面上に前記第一電極を形成する工程(c)と、

前記第一電極上において、前記基板の面に垂直な方向に関して前記第一電流遮断層に対向する領域の一部に前記電流供給線を連結して前記電流供給部を形成する工程(d)とを有することを特徴とする。

【0033】

コンタクトアニールを行う際、オーミック接触を形成する場合と比較してアニール温度を低くすることで、オーミック接触時よりも半導体層との接触抵抗を高くすることができる。このため、上記方法のように、工程(b2)において、第二電極を形成する工程(b1)よりもアニール温度を低くしてコンタクトアニールを実行することで、半導体層との接触抵抗が第二電極よりも高い第一電流遮断層が形成される。そして、工程(c)におい

10

20

30

40

50

て第一電極を形成した後に、工程 (d) において、第一電極の形成領域のうち、基板の面に垂直な方向に関して第一電流遮断層と対向する領域の一部に、電流供給線を連結して電流供給部を形成することで、電流供給部の鉛直下方に第一電流遮断層が形成される。これによって、電流供給部への電流集中が緩和された半導体発光素子が製造できる。

【0034】

また、上記製造方法に加えて、前記工程 (a) 及び (b1) の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない所定の領域に前記第二電流遮断層を形成するための材料膜を成膜した後、前記工程 (b1) よりは低温度且つ前記工程 (b2) よりは高温度でコンタクトアニール処理を行って前記第二電流遮断層を形成する工程 (b3) を有し、

10

前記工程 (b2) は、前記工程 (b3) の実行後、前記半導体層の前記第一面上であって前記第二電極及び前記第二電流遮断層が形成されていない箇所に前記第一電流遮断層を形成するための材料膜を成膜した後、前記工程 (b1) 及び前記工程 (b3) よりも低温度でコンタクトアニール処理を行って前記第一電流遮断層を形成する工程とすることができる。

【0035】

上述したように、コンタクトアニールを行う際、アニール温度によって半導体層との間の接触抵抗を制御することができる。よって、工程 (b3) において、第二電極を形成する工程 (b1) よりはアニール温度を低く、且つ工程 (b2) よりはアニール温度を高くしてコンタクトアニールを実行することで、第二電極よりは接触抵抗が高く、第一電流遮断層よりは接触抵抗の低い第二電流遮断層が形成される。その後、工程 (b2) において、工程 (b1) 及び (b3) より低温度でコンタクトアニール処理を行うことで第一電流遮断層が形成され、工程 (c) 及び (d) を経て第一電流遮断層に対して前記基板の面に垂直な方向に関して対向する位置に電流供給部が形成される。

20

【0036】

つまり、上記方法によれば、第一電極の鉛直下方に位置する領域に関して、電流供給部の近傍では接触抵抗の高い第一電流遮断層が半導体層と接触し、電流供給部から離れた位置では接触抵抗が第一電流遮断層よりも低い第二電流遮断層が半導体層と接触する。そして、第一電極が形成されていない領域の鉛直下方においては、接触抵抗が第一電流遮断層及び第二電流遮断層よりも低い第二電極が半導体層と接触する。

30

【0037】

これにより、第一電極の鉛直下方の領域に関していえば、第二電極よりも高抵抗の層が半導体層と接触しているため、第一電極から鉛直方向に電流が流れにくくなり、電流を水平方向に拡げる効果が実現される。更に、電流供給部の近傍と比較して、電流供給部から離れた箇所において半導体層との接触抵抗が低く設定されるため、電流供給部から供給された電流を電流供給部から離れた箇所に向かって流しやすくなる。これにより、電流供給部の近傍における電流集中を防止しつつ、半導体層に流れる電流を水平方向に更に拡げる効果を有した半導体発光素子が実現される。

【0038】

上記方法において、工程 (b1)、前記工程 (b2)、及び前記工程 (b3) で成膜される材料膜を同一の金属材料で構成しても構わない。この場合、第二電極のみならず、電流遮断層においても反射機能を実現することができる。

40

【0039】

また、上記製造方法に加えて、前記工程 (b1) で成膜される材料膜が金属材料であり、前記工程 (b2) 及び前記工程 (b3) で成膜される材料膜がITOであり、

前記工程 (b2) の実行後、前記第二電極、前記第一電流遮断層、及び前記第二電流遮断層に跨るように、金属材料膜を成膜後、前記工程 (b2) と同等以下の温度でコンタクトアニール処理を行って反射層を形成する工程 (b4) を有し、

前記工程 (b4) の実行後に、前記工程 (c) を実行するものとしても構わない。

【0040】

50

上述したように、コンタクトアニールを行う際、オーミック接触を形成する場合と比較してアニール温度を低くすることで、オーミック接触時よりも半導体層との接触抵抗を高くすることができるが、これは金属材料の場合のみならずITOにおいても同様である。

【0041】

従って、上記方法においても、第一電極の鉛直下方に位置する領域に関して、電流供給部の近傍では接触抵抗の高い第一電流遮断層が半導体層と接触し、電流供給部から離れた位置では接触抵抗が第一電流遮断層よりも低い第二電流遮断層が半導体層と接触する。このため、電流供給部の近傍と比較して、電流供給部から離れた箇所において半導体層との接触抵抗が低く設定されるため、電流供給部から供給された電流を電流供給部から離れた箇所に向かって流しやすくなる。

10

【0042】

更に、上記方法によれば、第一電流遮断層及び第二電流遮断層の下層に反射層を形成することができる。このため、第一電流遮断層及び第二電流遮断層として、光透過性を有するITOで形成した場合であっても、発光層から基板側に向かって射出された光は、半導体層と接触している第一電流遮断層及び第二電流遮断層の形成箇所において、各電流遮断層を透過した後、その下層に形成されている反射層で反射される。よって、光取り出し効率を向上しながら、電流供給部の近傍に電流が集中することが緩和された半導体発光素子が製造できる。

【0043】

また、本発明は、上記構成を有した半導体発光素子の製造方法であって、

基板上に前記半導体層を形成する工程(a)と、

20

前記半導体層の第一面上の所定の領域に、最上層にPtを含む多層構造を有する材料膜を成膜した後、コンタクトアニールを施して前記第二電極を形成する工程(b1)と、

前記工程(b1)の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない箇所に、Ptの膜厚を前記工程(b1)よりも薄膜として、最上層にPtを含む多層構造を有する前記材料膜を成膜した後、コンタクトアニール処理を行って前記第一電流遮断層を形成する工程(b2)と、

前記工程(b2)の実行後、前記半導体層の前記第一面とは反対側の第二面上に前記第一電極を形成する工程(c)と、

前記第一電極上において、前記基板の面に垂直な方向に関して前記第一電流遮断層に対向する領域の一部に前記電流供給線を連結して前記電流供給部を形成する工程(d)とを有することを特徴とする。

30

【0044】

本発明者の鋭意研究により、最上層にPtを含む金属材料膜を形成してコンタクトアニールを行う場合、オーミック接触を形成する場合と比較してPtの膜厚を薄くすることで、オーミック接触時よりも半導体層との接触抵抗を高くできることが分かった。このため、上記方法のように、工程(b2)において、第二電極を形成する工程(b1)よりもPtの膜厚を薄膜として材料膜を成膜した後、コンタクトアニールを実行することで、半導体層との接触抵抗が第二電極よりも高い第一電流遮断層を形成できる。そして、工程(c)において第一電極を形成した後に、工程(d)において第一電極の形成領域のうち、基板の面に垂直な方向に関して第一電流遮断層と対向する領域の一部に、電流供給線を連結して電流供給部を形成することで、電流供給部の鉛直下方に第一電流遮断層が形成される。これによって、電流供給部への電流集中が緩和された半導体発光素子が製造できる。

40

【0045】

また、上記製造方法に加えて、前記工程(a)及び(b1)の実行後、前記半導体層の前記第一面上であって前記第二電極が形成されていない所定の領域に、Ptの膜厚を前記工程(b1)より薄膜で且つ前記工程(b2)より厚膜として前記材料膜を成膜した後、コンタクトアニール処理を行って前記第二電流遮断層を形成する工程(b3)を有し、

前記工程(b2)は、前記工程(b3)の実行後、前記半導体層の前記第一面上であって前記第二電極及び前記第二電流遮断層が形成されていない箇所に、Ptの膜厚を前記工

50

程 (b 1) 及び前記工程 (b 3) よりも薄膜として前記材料膜を成膜した後、コンタクトアニール処理を行って前記第一電流遮断層を形成する工程とすることができます。

【0046】

上述したように、最上層の  $P_t$  の膜厚を制御することで、コンタクトアニールを行う対象となる金属材料膜と半導体層との間の接触抵抗を制御することができる。よって、工程 (b 3) において、第二電極を形成する工程 (b 1) よりは薄膜で、且つ工程 (b 2) よりは厚膜とした  $P_t$  を最上層に含む材料膜を成膜した後にコンタクトアニール処理を実行することで、第二電極よりは半導体層との接触抵抗が高く、第一電流遮断層よりは半導体層との接触抵抗の低い第二電流遮断層が形成される。その後、工程 (b 2) において、工程 (b 1) 及び (b 3) より薄膜の  $P_t$  を最上層に含む金属材料膜を成膜した後にコンタクトアニール処理を行って第一電流遮断層が形成され、工程 (c) 及び (d) を経て、この第一電流遮断層に対して前記基板の面に垂直な方向に関して対向する位置に電流供給部が形成される。

【0047】

従って、上記方法によつても、第一電極の鉛直下方に位置する領域に関して、電流供給部の近傍では接触抵抗の高い第一電流遮断層が半導体層と接触し、電流供給部から離れた位置では接触抵抗が第一電流遮断層よりも低い第二電流遮断層が半導体層と接触する。そして、第一電極が形成されていない領域の鉛直下方においては、接触抵抗が第一電流遮断層及び第二電流遮断層よりも低い第二電極が半導体層と接触する。これにより、電流供給部の近傍における電流集中を防止しつつ、半導体層に流れる電流を水平方向に更に拡げる効果を有した半導体発光素子が実現される。

【発明の効果】

【0048】

本発明の半導体発光素子によれば、電流供給部近傍における電流集中が緩和され、長寿命の高出力デバイスが実現される。また、本発明の半導体発光素子の製造方法によれば、前記高出力デバイスを製造することができます。

【図面の簡単な説明】

【0049】

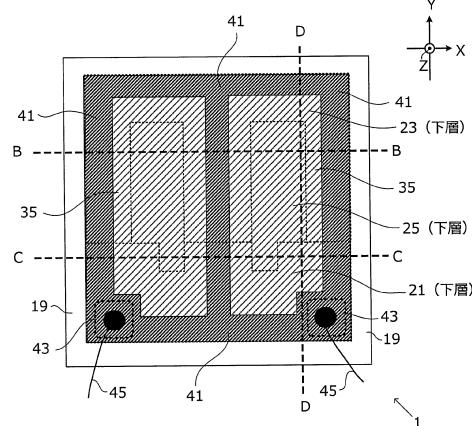

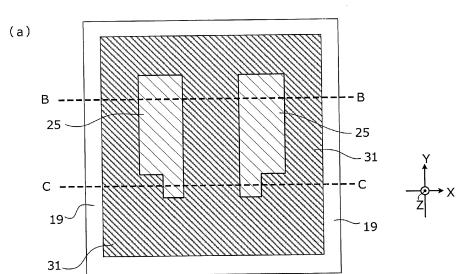

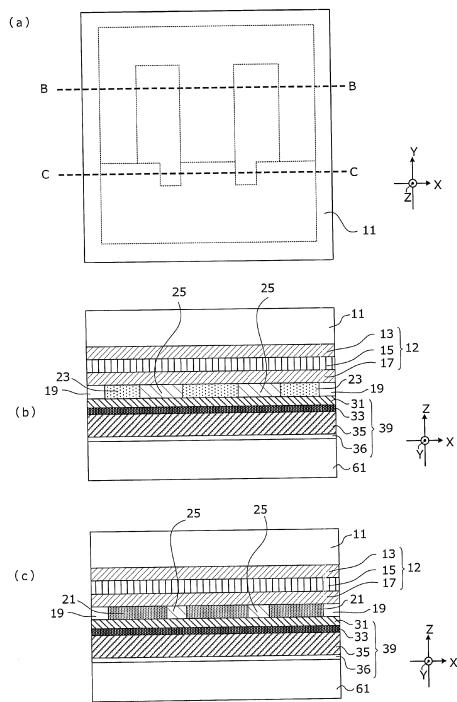

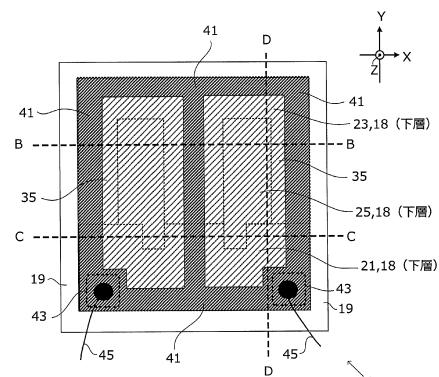

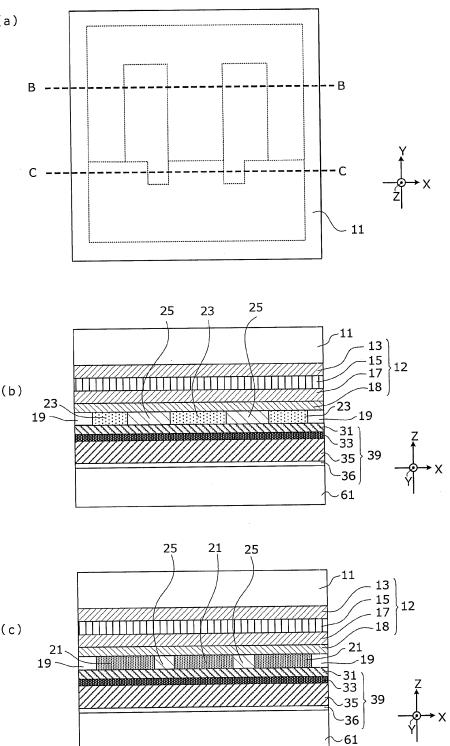

【図1A】本発明の第一実施形態の半導体発光素子を上から見たときの模式図である。

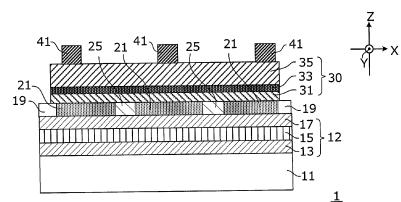

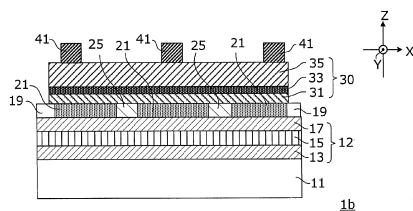

【図1B】図1Aにおける半導体発光素子をB-B線で切断したときの模式的な断面図である。

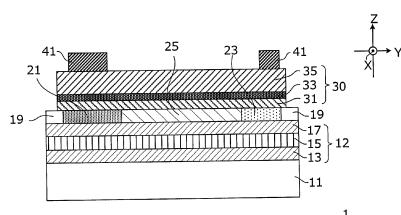

【図1C】図1Aにおける半導体発光素子をC-C線で切断したときの模式的な断面図である。

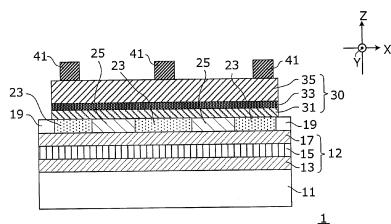

【図1D】図1Aにおける半導体発光素子をD-D線で切断したときの模式的な断面図である。

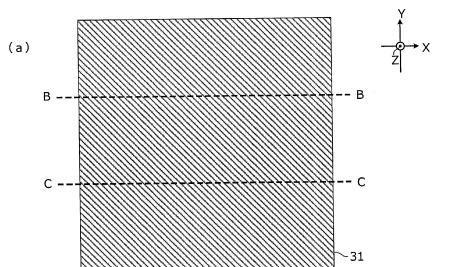

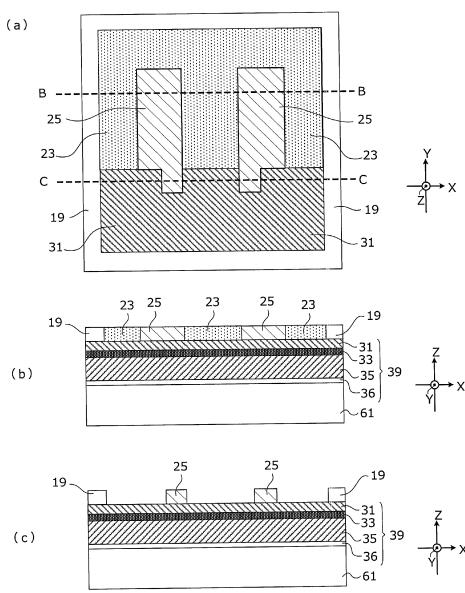

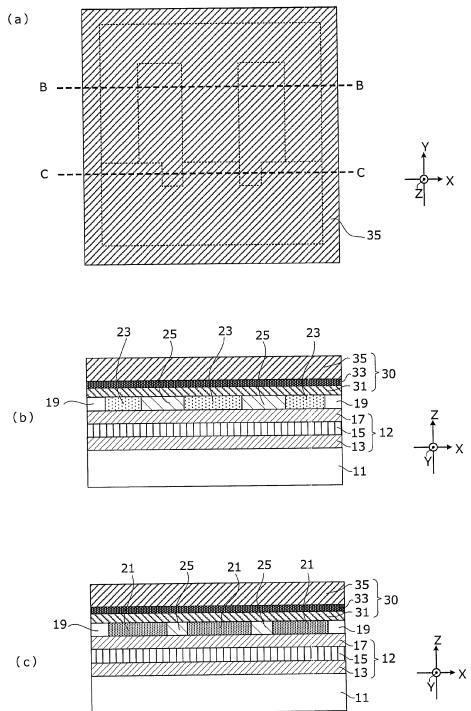

【図2A】半導体発光素子の第一実施形態の製造工程図の一部である。

【図2B】半導体発光素子の第一実施形態の製造工程図の一部である。

【図2C】半導体発光素子の第一実施形態の製造工程図の一部である。

【図2D】半導体発光素子の第一実施形態の製造工程図の一部である。

【図2E】半導体発光素子の第一実施形態の模式的な工程図の一部である。

【図2F】半導体発光素子の第一実施形態の模式的な工程図の一部である。

【図2G】半導体発光素子の第一実施形態の模式的な工程図の一部である。

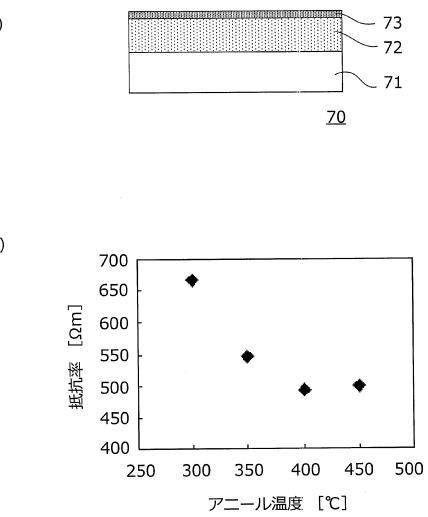

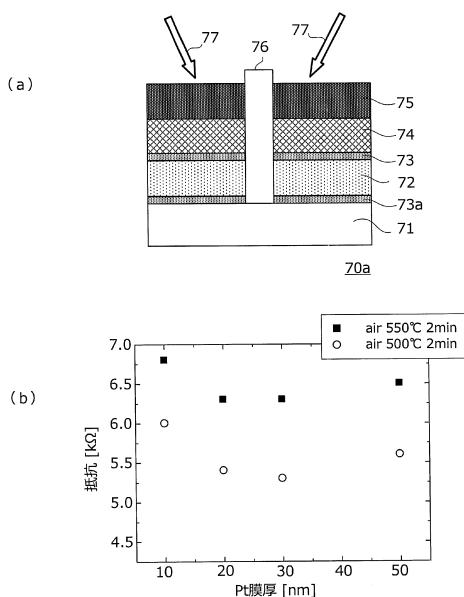

【図3】コンタクトアニール温度によって接触抵抗が制御できることを説明するための図である。

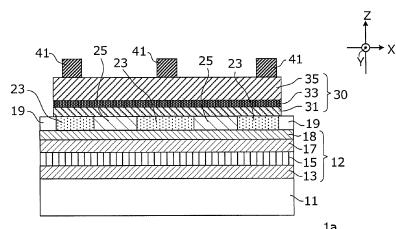

【図4】 $P_t$  の膜厚によって接触抵抗が制御できることを説明するための図である。

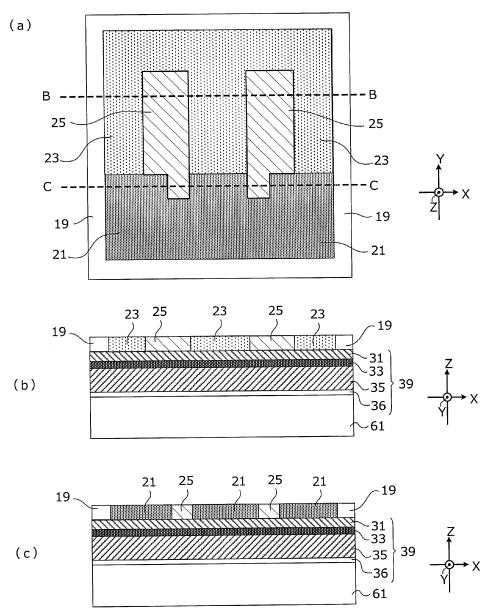

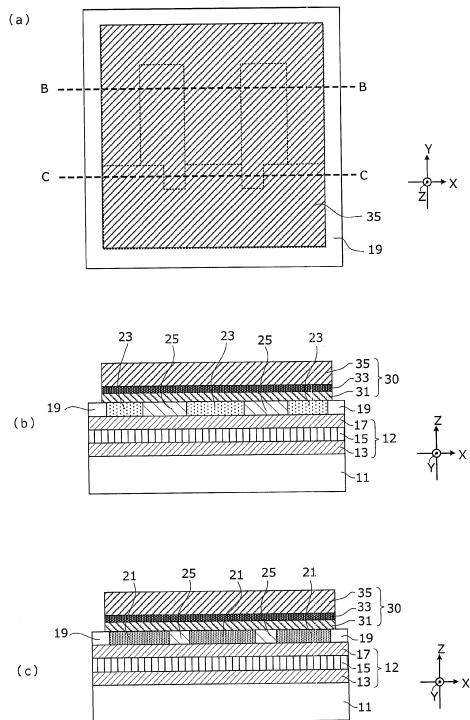

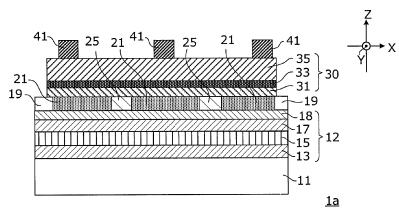

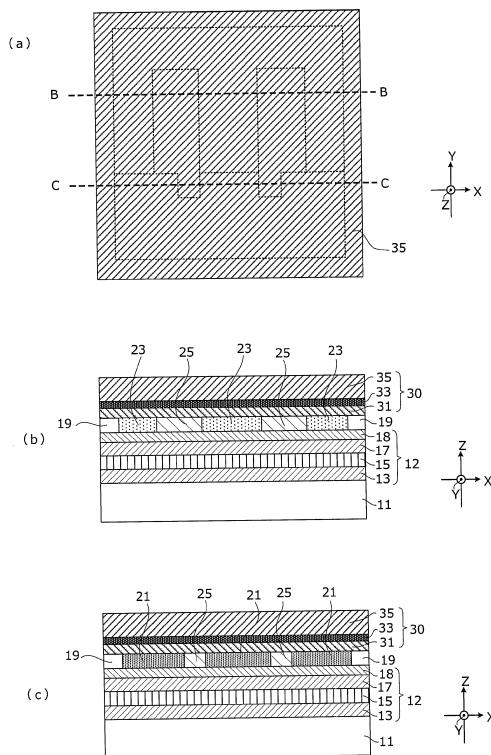

【図5A】本発明の第二実施形態の半導体発光素子を上から見たときの模式図である。

【図5B】図5Aにおける半導体発光素子をB-B線で切断したときの模式的な断面図である。

【図5C】図5Aにおける半導体発光素子をC-C線で切断したときの模式的な断面図である。

10

20

30

40

50

【図5D】図5Aにおける半導体発光素子をD-D線で切断したときの模式的な断面図である。

【図6】コンタクトアニール温度によって接触抵抗が制御できることを説明するための図である。

【図7A】半導体発光素子の第二実施形態の製造工程図の一部である。

【図7B】半導体発光素子の第二実施形態の製造工程図の一部である。

【図7C】半導体発光素子の第二実施形態の製造工程図の一部である。

【図7D】半導体発光素子の第二実施形態の製造工程図の一部である。

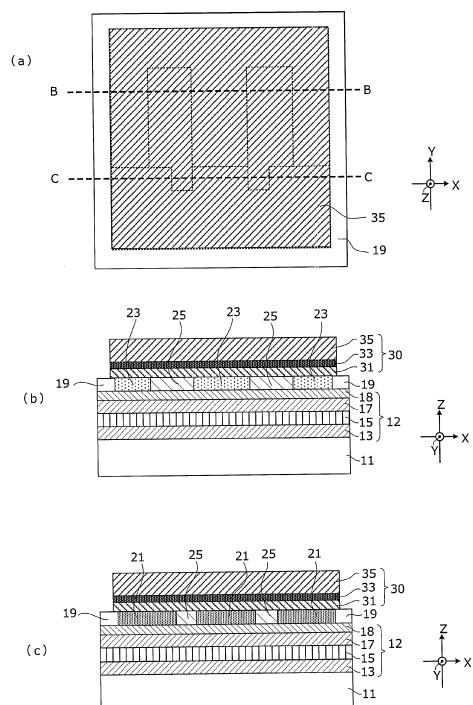

【図8A】本発明の別実施形態の半導体発光素子を上から見たときの模式図である。

【図8B】図8Aにおける半導体発光素子をB-B線で切断したときの模式的な断面図である。10

【図8C】図8Aにおける半導体発光素子をC-C線で切断したときの模式的な断面図である。

【図8D】図8Aにおける半導体発光素子をD-D線で切断したときの模式的な断面図である。

【図9】特許文献1に開示された半導体発光素子の断面図を模式的に示したものである。

【図10】特許文献1に開示された半導体発光素子の上面視の平面図を模式的に示したものである。

【図11】図10に示す構成を有する半導体発光素子の上面の写真である。

【図12】図10に示す構成を有する半導体発光素子の電流供給部に対して500mA、20

1000mAを供給したときの素子上面の温度分布を示す写真である。

【図13】図10に示す構成を有する半導体発光素子の電流供給部に対して500mA、

1000mAを供給したときの、素子上の位置における光出力の分布を示すグラフである。。

【図14】図10に示す構成を有する半導体発光素子の電流供給部に対して高い電流を一定時間供給した後の上面の写真である。

#### 【発明を実施するための形態】

##### 【0050】

本発明の半導体発光素子及びその製造方法につき、図面を参照して説明する。なお、各図において図面の寸法比と実際の寸法比は必ずしも一致しない。30

##### 【0051】

###### 【第一実施形態】

本発明の半導体発光素子の第一実施形態の構成及びその製造方法について説明する。

##### 【0052】

###### 構造

図1Aは、第一実施形態の半導体発光素子を上から見たときの模式的な平面図である。図1Aにおいて、半導体発光素子1は光取り出し方向が紙面上向き(Z方向)である。

##### 【0053】

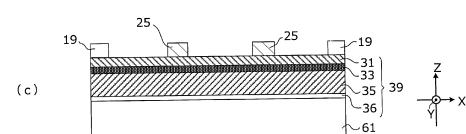

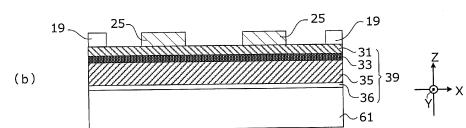

図1Bは、半導体発光素子1を図1AにおけるB-B線で切断したときの模式的な断面図である。図1Cは、半導体発光素子1を図1AにおけるC-C線で切断したときの模式的な断面図である。図1Dは、半導体発光素子1を図1AにおけるD-D線で切断したときの模式的な断面図である。40

##### 【0054】

本実施形態における半導体発光素子1は、基板11、導電層12、絶縁層19、半導体層30、第一電極41、第二電極25、第一電流遮断層21、及び第二電流遮断層23を有して構成される。半導体層30は、p型半導体層31、発光層33、及びn型半導体層35が下からこの順に積層されて形成されている。なお、図1Aを含む以下の各図面において、基板11の面に平行な方向をX-Y平面と規定し、この平面に垂直な方向をZ方向と規定する。

##### 【0055】

10

20

30

40

50

## (基板 11)

基板 11 は、例えば CuW、W、Mo 等の導電性基板、又は Si 等の半導体基板で構成される。

## 【0056】

## (導電層 12)

基板 11 の上層には、多層構造からなる導電層 12 が形成されている。本実施形態において、導電層 12 は、保護層 13、ハンダ層 15、及び保護層 17 を含む構成である。

## 【0057】

ハンダ層 15 は、例えば Au-Sn、Au-In、Au-Cu-Sn、Cu-Sn、Pd-Sn、Sn 等で構成される。このハンダ層 15 は、基板 11 と別の基板（後述する成長基板 61）とを貼り合わせる際、両者の密着性を確保するための層として機能している。

10

## 【0058】

保護層 17 は、例えば Pt 系の金属（Ti と Pt の合金）、W、Mo、Ni 等で構成される。後述するように、ハンダ層を介した貼り合わせの際、ハンダを構成する材料が第二電極 25 側に拡散して、第二電極 25 における反射率が落ちることによる発光効率の低下を防止する機能を果たしている。

## 【0059】

## (半導体層 30)

上述したように、半導体層 30 は、p 型半導体層 31、発光層 33、及び n 型半導体層 35 が基板 11 側からこの順に積層されて形成される。

20

## 【0060】

p 型半導体層 31 は、例えば GaN、AlGaN 等で構成され、Mg、Be、Zn、又は C 等の p 型不純物がドープされている。

## 【0061】

発光層 33 は、例えば InGaN からなる井戸層と AlGaN からなる障壁層が繰り返されてなる多重量子井戸構造を有する半導体層で形成される。これらの層はアンドープでも p 型又は n 型にドープされていても構わない。

## 【0062】

n 型半導体層 35 は、例えば AlGaN で構成される層（電子供給層）と GaN で構成される層（保護層）を含む多層構造で構成される。少なくとも保護層には、Si、Ge、S、Se、Sn、又は Te 等の n 型不純物がドープされている。

30

## 【0063】

なお、「AlGaN」という記述は、Al<sub>m</sub>Ga<sub>1-m</sub>N (0 < m < 1) という記述と同義であり、Al と Ga の組成比の記述を単に省略して記載したものであって、Al と Ga の組成比が 1 : 1 である場合に限定する趣旨ではない。「InGaN」という記述についても同様である。以下においても上記にならって記載される。

## 【0064】

## (第一電極 41)

第一電極 41 は、n 型半導体層 35 の一部領域の上面に形成されており、例えば Cr-Au で構成される。なお、図 1A に示すように、第一電極 41 は半導体発光素子 1 の中央から -Y 方向の位置において幅広部分を有しており、この領域に電流供給線 45 の一端が接続された電流供給部 43 が形成されている。電流供給線 45 の他端は、半導体発光素子 1 が配置されている基板 11 の給電パターン等に接続される（不図示）。なお、図 1A では、半導体発光素子 1 が電流供給部 43 を 2箇所備える場合を図示しているが、これは一例であって電流供給部 43 の数を限定する趣旨ではない。

40

## 【0065】

第一電極 41 は基板 11 の面 (X-Y 平面) に沿って縦横に延伸する構成であり、この延伸する第一電極 41 に囲まれた領域、すなわち n 型半導体層 35 の上面に第一電極 41 が形成されていない領域が光取り出し面に対応する。なお、第一電極 41 は、図 1A に示

50

すような形状に限られない。一例として、第一電極 4 1 に関して、Y 方向に延伸する本数を増やしてより細かい格子形状としても構わないし、更には X 方向に延伸する本数を増やして網目形状としても構わない。

【0066】

(第二電極 25)

第二電極 25 は、例えは Ag 系の金属 (Ni と Ag の合金)、Al、又は Rh 等を含む金属材料で構成することができる。本実施形態では、第二電極 25 が Ni / Ag の多層構造体で形成されているものとして説明する。

【0067】

第二電極 25 は、発光層 33 から射出される光を反射させることのできる導電性の材料で構成されており、且つ、p 型半導体層 31 との接触箇所においてオーム接触が形成されている。

【0068】

図 1B、図 1C、及び図 1D に示すように、第二電極 25 は、第一電極 41 が形成されていない領域の鉛直下方の一部領域に形成されている。すなわち、第二電極 25 は、鉛直方向 (Z 方向) に関して第一電極 41 とは対向しない位置に形成されている。

【0069】

また、第二電極 25 は、導電層 12 の上面及び半導体層 30 の底面に接触して形成されている。本実施形態の場合、第二電極 25 は、保護層 17 の上面と p 型半導体層 31 の底面に接触して形成されている。

【0070】

(第一電流遮断層 21、第二電流遮断層 23)

本実施形態において、第一電流遮断層 21 及び第二電流遮断層 23 は、第二電極 25 と同一の金属材料で形成されている。しかし、第一電流遮断層 21 及び第二電流遮断層 23 は、p 型半導体層 31 との接触箇所においてショットキー接触が形成されている。すなわち、第一電流遮断層 21 と p 型半導体層 31 との接触箇所における接触抵抗、及び第二電流遮断層 23 と p 型半導体層 31 との接触箇所における接触抵抗は、いずれも第二電極 25 と p 型半導体層 31 との接触箇所における接触抵抗よりも高くなっている。

【0071】

更に、第一電流遮断層 21 と第二電流遮断層 23 を比較した場合、第一電流遮断層 21 と p 型半導体層 31 との接触箇所における接触抵抗は、第二電流遮断層 23 と p 型半導体層 31 との接触箇所における接触抵抗よりも高くなっている。このように、p 型半導体層 31 との接触箇所における接触抵抗の大きさに差異を設ける方法については、製造方法を説明する際に後述される。

【0072】

第一電流遮断層 21 及び第二電流遮断層 23 は、いずれも導電層 12 の上面及び半導体層 30 の底面に接触して形成されている。本実施形態の場合、第一電流遮断層 21 及び第二電流遮断層 23 は、いずれも保護層 17 の上面と p 型半導体層 31 の底面に接触して形成されている。

【0073】

第一電流遮断層 21 は、第二電流遮断層 23 よりも電流供給部 43 に近い領域に形成されている。すなわち、第一電流遮断層 21 は、少なくとも電流供給部 43 の鉛直下方を含む領域に形成されている。これに対し、第二電流遮断層 23 は、第一電流遮断層 21 と比べて電流供給部 43 から Y 方向に離れた位置に形成されている。

【0074】

(絶縁層 19)

絶縁層 19 は、例えは SiO<sub>2</sub>、SiN、Zr<sub>2</sub>O<sub>3</sub>、AlN、Al<sub>2</sub>O<sub>3</sub> 等で構成される。この絶縁層 19 は、X-Y 平面に平行な方向に関して半導体層 30 の外側の位置に形成されており、隣接する半導体発光素子との間の絶縁性を確保するためのアイソレーション層として機能する他、後述するように素子分離時におけるエッチングストッパー層と

10

20

30

40

50

しても機能する。

【0075】

作用

図1Dに示すように、電流供給部43を構成する箇所における第一電極41(図1Dにおける-Y側に位置する第一電極41)の鉛直下方には、p型半導体層31との接触抵抗の高い第一電流遮断層21が形成されている。そして、電流供給部43からY方向に離れた位置において、第一電極41が形成されていない一部領域の鉛直下方にはp型半導体層31との接触抵抗が最も低い第二電極25が形成されている。また、電流供給部43からY方向に離れた位置において、第一電極41が形成されている領域の鉛直下方には、第一電流遮断層21よりはp型半導体層31との接触抵抗が低く第二電極25よりはp型半導体層31との接触抵抗が高い第二電流遮断層23が形成されている。10

【0076】

半導体発光素子1に対して、電流供給線45を介して電流供給部43に高い電流が供給された場合を想定する。上述したように、電流供給部43の鉛直下方には最も接触抵抗の高い第一電流遮断層21が形成されている。このため、電流供給部43に供給された電流は、電流供給部43からZ方向(鉛直方向)には極めて流れにくい構成となっている。

【0077】

また、図1Aを参照して上述したように、電流供給部43は第一電極41の一部を形成しており、第一電極41は基板11の面(X-Y平面)に沿って縦横に延伸する構成である。そして、第一電極41の鉛直下方の位置には第二電極25は形成されておらず、半導体層30との接触箇所がショットキー接觸となっている第一電流遮断層21又は第二電流遮断層23が形成されている。よって、第一電極41から鉛直下方には電流が流れにくく、電流供給部43に供給された電流は第一電極41を通じてX-Y平面に平行な方向に拡げられ、導電層12に向けて半導体層30内を流れる。20

【0078】

ただし、X-Y平面に関し、電流供給部43から離れた位置においては、第一電極41の鉛直下方の位置は、第一電流遮断層21よりは半導体層30との接触抵抗が低い第二電流遮断層23が形成されている。このため、電流供給部43から離れた位置においては、電流供給部43の直下の位置に比べると、幾つかの電流は鉛直下方に流れる構成となる。

【0079】

すなわち、半導体発光素子1は、第一電極41の直下には半導体層30との接触抵抗の高い層を設けておくことで、半導体層30内を鉛直方向に大部分の電流が流れることを防止しつつ、特に、電流が供給される電流供給部43の直下には、電流供給部43から離れた位置と比べて更に接触抵抗の高い層(第一電流遮断層21)を設けることで、電流供給部43の近傍に電流が集中することを防止している。これにより、半導体発光素子1が高出力デバイスとして利用される場合、すなわち高電流が供給される場合においても、電流供給部43の近傍に電流が集中して高温になることが防止されるので、従来に比べて長寿命の素子が実現される。30

【0080】

なお、本実施形態の構成によれば、第一電流遮断層21及び第二電流遮断層23の双方ともに、第二電極25と同一の金属材料で実現している。このため、発光層33から下向に射出された光は、第二電極25の面のみならず、第一電流遮断層21及び第二電流遮断層23の面においても反射させて、光取り出し面から取り出すことが可能であり、高い光取り出し効率が実現される。40

【0081】

ここで、図14に示す従来の半導体発光素子100において、電流供給部109の幅をdとし、電流供給部109のエッジからアイソレーション層106のエッジまでの間隔をbとする。これを、本実施形態の半導体発光素子1に当てはめると、電流供給部43の幅がdに対応し、電流供給部43のエッジから絶縁層19のエッジまでの間隔がbに対応する。このとき、電流供給部43の近傍に電流が集中するのを緩和するためには、第一電流50

遮断層 2 1 は、電流供給部 4 3 の鉛直下方の領域の全体を占有し、更にそこから X - Y 平面に平行な方向にある程度の広がりを有して形成されているのが好ましい。ここで、電流供給部 4 3 の鉛直下方の領域からの広がりについては、少なくとも電流供給部 1 0 9 のエッジと絶縁層 1 9 のエッジに挟まれた領域の鉛直下方の領域には、第一電流遮断層 2 1 が形成されているのが好ましい。つまり、第一電流遮断層 2 1 の X - Y 平面に平行な方向の幅を D とすると、 $D = d + b$  とするのが好ましい。

【 0 0 8 2 】

図 1 4 の写真において、 $d = 130 \mu m$ 、 $b = 10 \mu m$  であるため、この場合は  $D = 140 \mu m$  とするのが好ましいといえる。設計余裕を考慮すれば、 $D = 1.1d$  となるよう 10 に、第一電流遮断層 2 1 を形成するのが好ましい。

【 0 0 8 3 】

他方、第一電流遮断層 2 1 を極めて広く形成してしまうと、第一電流遮断層 2 1 から離れた箇所に向かって電流が流れにくくなってしまうため、第一電流遮断層 2 1 の近傍箇所に電流が集中するのを緩和する効果が減少してしまう。

【 0 0 8 4 】

ここで、図 1 2 ( b ) によれば、従来の半導体発光素子 1 0 0 においては、電流供給部 1 0 9 に高い電流を供給すると、電流供給部 1 0 9 の形成領域から当該領域を基準に Y 方向に  $3d$  離れた領域にわたって、高い温度が示されていることが分かる（上記と同様に電流供給部 1 0 9 の幅を  $d$  としている。）。なお、図 1 2 ( b ) に示す半導体発光素子 1 0 0 は、素子サイズ  $L = 1 mm$ 、電流供給部 1 0 9 の幅  $d = 130 \mu m$ 、n 側電極 1 0 8 の幅  $a = 18 \mu m$  で形成されたものである。 20

【 0 0 8 5 】

従って、本実施形態の半導体発光素子 1 において、電流供給部 4 3 の形成領域から  $3d$  より離れた箇所に第一電流遮断層 2 1 を形成しても、電流供給部 4 3 の近傍に電流が集中するのを緩和するという観点からあまり効果が得られないと考えられる。従って、第一電流遮断層 2 1 の X - Y 平面に平行な方向の幅を D とすると、 $D = 3d$  とするのが好ましい。つまり、 $1.1d = D = 3d$  となるように、第一電流遮断層 2 1 の大きさを設計するのが好ましい。

【 0 0 8 6 】

第一の製造方法

次に、半導体発光素子 1 の第一の製造方法の一例につき、図 2 A ~ 図 2 G に示す模式的な製造工程図、及び図 3 を参照して説明する。なお、以下で説明する製造条件や膜厚等の寸法はあくまで一例であって、これらの数値に限定されるものではない。 30

【 0 0 8 7 】

なお、図 2 A ~ 図 2 G において、いずれも、( a ) が上面から見たときの模式的平面図であり、( b ) が ( a ) の図面上の B - B 線の模式的な断面図であり、( c ) が ( a ) の図面上の C - C 線の模式的な断面図である。

【 0 0 8 8 】

( ステップ S 1 )

図 2 A に示すように、成長基板 6 1 上にエピタキシャル層 3 9 を形成する。このステップ S 1 は例えば以下の手順により行われる。 40

【 0 0 8 9 】

( 成長基板 6 1 の準備 )

成長基板 6 1 として c 面サファイア基板を準備して、これに対してクリーニングを行う。このクリーニングは、より具体的には、例えば M O C V D ( Metal Organic Chemical V apor Deposition : 有機金属化学気相蒸着 ) 装置の処理炉内に成長基板 6 1 ( c 面サファイア基板 ) を配置し、処理炉内に流量が  $10 \text{ s}^{-1} \text{ m}$  の水素ガスを流しながら、炉内温度を例えば  $1150^\circ\text{C}$  に昇温することにより行われる。

【 0 0 9 0 】

( アンドープ層 3 6 の形成 )

10

20

30

40

50

成長基板61の表面に、GaNよりなる低温バッファ層を形成し、更にその上層にGaNよりなる下地層を形成する。これらの低温バッファ層及び下地層がアンドープ層36に対応する。

#### 【0091】

具体的なアンドープ層36の形成方法は、例えば以下の通りである。まず、CVD装置の炉内圧力を100kPa、炉内温度を480<sup>o</sup>Cとする。そして、処理炉内にキャリアガスとして流量がそれぞれ5s1mの窒素ガス及び水素ガスを流しながら、原料ガスとして、流量が50μmol/minのトリメチルガリウム(TMГ)及び流量が250000μmol/minのアンモニアを処理炉内に68秒間供給する。これにより、成長基板61の表面に、厚みが20nmのGaNよりなる低温バッファ層を形成する。

10

#### 【0092】

次に、MOCVD装置の炉内温度を1150<sup>o</sup>Cに昇温する。そして、処理炉内にキャリアガスとして流量が20s1mの窒素ガス及び流量が15s1mの水素ガスを流しながら、原料ガスとして、流量が100μmol/minのTMГ及び流量が250000μmol/minのアンモニアを処理炉内に30分間供給する。これにより、低温バッファ層の表面に、厚みが1.7μmのGaNよりなる下地層を形成する。

#### 【0093】

##### (n型半導体層35の形成)

次に、アンドープ層36の上層にn型半導体層35を形成する。n型半導体層35の具体的な形成方法は、例えば以下の通りである。

20

#### 【0094】

まず、引き続き炉内温度を1150<sup>o</sup>Cとした状態で、MOCVD装置の炉内圧力を30kPaとする。そして、処理炉内にキャリアガスとして流量が20s1mの窒素ガス及び流量が15s1mの水素ガスを流しながら、原料ガスとして、流量が94μmol/minのTMГ、流量が6μmol/minのトリメチルアルミニウム(TMA)、流量が250000μmol/minのアンモニア及び流量が0.013μmol/minのテトラエチルシランを処理炉内に60分間供給する。これにより、例えばAl<sub>0.94</sub>Nの組成を有し、Si濃度が5×10<sup>19</sup>/cm<sup>3</sup>で、厚みが2μmのn型半導体層35がアンドープ層36の上層に形成される。

#### 【0095】

30

なお、この後、TMAの供給を停止すると共に、それ以外の原料ガスを6秒間供給することにより、n型AlGaN層の上層に、厚みが5nm程度のn型GaNよりなる保護層を有するn型半導体層35を実現してもよい。

#### 【0096】

上記の説明では、n型半導体層35に含まれるn型不純物をSiとする場合について説明したが、n型不純物としては、Si以外にGe、S、Se、Sn又はTe等を用いることができる。

#### 【0097】

##### (発光層33の形成)

次に、n型半導体層35の上層にInGaNで構成される井戸層及びn型AlGaNで構成される障壁層が周期的に繰り返される多重量子井戸構造を有する発光層33を形成する。

40

#### 【0098】

具体的には、まずMOCVD装置の炉内圧力を100kPa、炉内温度を830<sup>o</sup>Cとする。そして、処理炉内にキャリアガスとして流量が15s1mの窒素ガス及び流量が1s1mの水素ガスを流しながら、原料ガスとして、流量が10μmol/minのTMГ、流量が12μmol/minのトリメチルインジウム(TMI)及び流量が300000μmol/minのアンモニアを処理炉内に48秒間供給するステップを行う。その後、流量が10μmol/minのTMГ、流量が1.6μmol/minのTMA、0.02μmol/minのテトラエチルシラン及び流量が300000μmol/minの

50

アンモニアを処理炉内に120秒間供給するステップを行う。以下、これらの2つのステップを繰り返すことにより、厚みが2nmのInGANよりなる井戸層及び厚みが7nmのn型AlGANよりなる障壁層による15周期の多重量子井戸構造を有する発光層33が、n型半導体層35の上層に形成される。

【0099】

(p型半導体層31の形成)

次に、発光層33の上層に、AlGANで構成されるp型半導体層31を形成する。p型半導体層31の具体的な形成方法は、例えば以下の通りである。

【0100】

具体的には、MOCVD装置の炉内圧力を100kPaに維持し、処理炉内にキャリアガスとして流量が15s1mの窒素ガス及び流量が25s1mの水素ガスを流しながら、炉内温度を1025に昇温する。その後、原料ガスとして、流量が35μmol/minのTMG、流量が20μmol/minのTMA、流量が250000μmol/minのアンモニア及びp型不純物をドープするための流量が0.1μmol/minのビスシクロペンタジエニルマグネシウム(Cp<sub>2</sub>Mg)を処理炉内に60秒間供給する。これにより、発光層33の表面に、厚みが20nmのAl<sub>0.3</sub>Ga<sub>0.7</sub>Nの組成を有する正孔供給層を形成する。その後、TMAの流量を4μmol/minに変更して原料ガスを360秒間供給することにより、厚みが120nmのAl<sub>0.13</sub>Ga<sub>0.87</sub>Nの組成を有する正孔供給層を形成する。これらの正孔供給層によりp型半導体層31が形成される。このp型半導体層31のp型不純物濃度は、例えば3×10<sup>19</sup>/cm<sup>3</sup>程度である。

【0101】

なお、その後、TMAの供給を停止すると共に、Cp<sub>2</sub>Mgの流量を0.2μmol/minに変更して原料ガスを20秒間供給することにより、厚みが5nm程度で、p型不純物濃度が1×10<sup>20</sup>/cm<sup>3</sup>程度のp型コンタクト層を形成してもよい。この場合、p型半導体層31にはこのp型コンタクト層も含まれる。

【0102】

このようにして成長基板61上に、アンドープ層36、n型半導体層35、発光層33、及びp型半導体層31からなるエピタキシャル層39が形成される。このステップS1が工程(a)に対応する。

【0103】

(ステップS2)

ステップS1で得られたウェハに対して活性化処理を行う。より具体的には、RTA(Rapid Thermal Anneal:急速加熱)装置を用いて、窒素雰囲気下中650で15分間の活性化処理を行う。

【0104】

(ステップS3)

p型半導体層31の上面の所定箇所に絶縁層19を形成する(図2B参照)。

【0105】

より詳細には、隣接する素子との境界となる領域内におけるp型半導体層31の上面に、SiO<sub>2</sub>をスパッタリング法によって膜厚200nm程度成膜することで絶縁層19を形成する。なお成膜する材料は絶縁性材料であればよく、例えばSiN、Al<sub>2</sub>O<sub>3</sub>でも良い。このとき、絶縁層19を形成しない領域をマスクしておくものとしてよい。

【0106】

(ステップS4)

p型半導体層31の上面の所定領域に第二電極25を形成する(図2B参照)。第二電極25の具体的な形成方法は、例えば以下の通りである。

【0107】

p型半導体層31の上面の所定領域に所定の導電性材料で構成された材料膜を成膜する。例えばスパッタ装置にてp型半導体層31の上面の所定の領域に膜厚150nmのAg

10

20

30

40

50

及び膜厚30nmのNiを成膜する。なお、この材料膜として、p型半導体層31との密着性を高めるために、Ag層の下層に膜厚1.5nm程度のNiを成膜しても構わない。

【0108】

その後、RTA装置等を用いてドライエア又は不活性ガス雰囲気中で400～550、60秒～300秒間のコンタクトアニール処理を行い、前記材料膜とp型半導体層31とのオーミック接触を形成させ、第二電極25を形成する。不活性ガス雰囲気でアニールをした場合、マイグレーションによるp型半導体層31側へのAgの拡散を少なくすることができるため、ドライエア雰囲気の場合よりも更にショットキー効果を高めることができる。

【0109】

なお、図2Bに示すように、第二電極25は、C-C線上の領域においてB-B線上の領域よりも狭い幅で形成されている。これは、後に形成される電流供給部43と第二電極25の距離を一定程度離しながらも、第二電極25の大きさを十分に確保することを意図したものである。

【0110】

つまり、第二電極25を十分に大きくするためには、第二電極25の幅を、C-C線上においても、B-B線上の領域と同程度にすることが考えられるが、その場合、電流供給部43(図1A参照)と第二電極25が接近し過ぎる結果、電流供給部43から第二電極25に向かって鉛直方向に電流が流れやすくなってしまう。一方で、B-B線上の第二電極25の幅をC-C線上の領域と同程度にしてしまうと、第二電極25の占有領域が小さくなってしまい、半導体層30内を流れる電流量が少なくなってしまう。このような観点から、第二電極25を、C-C線上の領域すなわち電流供給部43の形成予定箇所の近傍領域において、B-B線上の領域すなわち電流供給部43の形成予定箇所から離れた領域よりも狭い幅で形成している。

【0111】

ただし、図2Bに示す第二電極25の形状はあくまで一例であって、このような形状に限定されるものではない。例えば、半導体層31内に十分な電流量が確保できる場合には、第二電極25を矩形形状で構成しても構わない。

【0112】

このステップS4が工程(b1)に対応する。なお、ステップS3とステップS4の順序を入れ替えて構わない。

【0113】

(ステップS5)

p型半導体層31の上面のうち、第二電極25が形成されていない領域の一部に、第二電流遮断層23を形成する(図2C参照)。より詳細には、p型半導体層31の上面のうち、第二電極25が形成されていない領域であって、電流供給部43の形成予定箇所からY方向に一定程度遠い領域に第二電流遮断層23を形成する。

【0114】

より具体的な一例としては、ステップS4と同様に、スパッタ装置にてp型半導体層31の上面の所定の領域に膜厚150nmのAg及び膜厚30nmのNiからなる材料膜を成膜する。その後、RTA装置等を用いてドライエア又は不活性ガス雰囲気中で、ステップS4よりも低温、例えば340～360程度、60秒～300秒間のコンタクトアニール処理を行う。

【0115】

上記の温度条件下で形成された第二電流遮断層23は、p型半導体層31との接触箇所にショットキー接触が形成され、第二電極25とp型半導体層31との間よりも高い接触抵抗となる。

【0116】

このステップS5は、工程(b3)に対応する。

【0117】

10

20

30

40

50

## (ステップS6)

p型半導体層31の上面のうち、第二電極25及び第二電流遮断層23が形成されていない領域に、第一電流遮断層21を形成する(図2D参照)。すなわち、第一電流遮断層21は、第二電流遮断層23よりも電流供給部43の形成予定箇所に近い領域に形成される。

## 【0118】

より具体的な一例としては、ステップS5と同様に、第二電極25及び第二電流遮断層23が形成されていないp型半導体層31の上面に、膜厚150nmのAg及び膜厚30nmのNiからなる材料膜を成膜する。その後、RTA装置等を用いてドライエア又は不活性ガス雰囲気中で、ステップS5よりも更に低温、例えば290～310程度、60秒～300秒間のコンタクトアニール処理を行う。10

## 【0119】

上記の温度条件下で形成された第一電流遮断層21は、p型半導体層31との接触箇所にショットキー接觸が形成され、第二電極25とp型半導体層31との間、更には第二電流遮断層23とp型半導体層31との間よりも高い接觸抵抗となる。

## 【0120】

このステップS6は、工程(b2)に対応する。

## 【0121】

以下、図3を参照して、コンタクトアニール温度によって接觸抵抗が制御できることを説明する。図3は、模擬的に形成した検証用素子と、その検証用素子におけるアニール温度と抵抗率の関係を示すグラフである。図3(a)に示す検証用素子70は、p型AlGaN層71上に、膜厚150nmのAg層72を形成し、その上層に膜厚30nmのNi層73を形成して構成されている。このAg層72とNi層73によって、ステップS5及びステップS6で成膜される材料膜が模擬されている。20

## 【0122】

図3(b)は、p型AlGaN層71上にAg層72及びNi層73を蒸着後、異なるアニール温度でコンタクトアニール処理を行った後、検証用素子70の抵抗率を測定してアニール温度との関係をグラフ化したものである。図3(b)において、アニール温度が400のときは、500m程度の値が示されているが、これは接觸していない箇所の抵抗が表示されているものであって、接觸部分における抵抗はほぼ0でオーミック接觸が実現されている。なお、450の場合も400と同等の抵抗率が実現されており、オーミック接觸が実現されていることが分かる。30

## 【0123】

これに対し、アニール温度が350の場合は、アニール温度が400の場合よりも接觸抵抗が高くなっている、アニール温度を300とすると更に接觸抵抗が高くなっている。このことから、アニール温度を低くすることで、p型AlGaN層71とAg層72をショットキー接觸とすることができます、且つその温度を低くすることで接觸抵抗を高くできることが分かる。

## 【0124】

なお、ステップS4、ステップS5、及びステップS6は、アニール温度がこの順に低くなるように設定されている。つまり、コンタクトアニール処理を実行する際のアニール温度が高い工程から順に実行する必要がある。これは、仮にステップS5とステップS6の順番を入れ替えた場合、ステップS6の実行後に、ステップS6よりもアニール温度の高いステップS5を実行すると、ステップS5の実行中にステップS6で形成された第一電流遮断層21とp型半導体層31との接觸箇所が高温下に置かれる結果、接觸抵抗が低下する可能性があるためである。40

## 【0125】

## (ステップS7)

第二電極25、第一電流遮断層21、及び第二電流遮断層23の上面に跨るように、全面に保護層17を形成する。その後、保護層17の上面にハンダ層15を形成する(図2)50

E 参照)。

【0126】

より詳細には、電子線蒸着装置(EB装置)にて、膜厚100nmのTiと膜厚200nmのPtを3周期成膜することで保護層17を形成する。更にその後、保護層17の上面(Pt表面)に、膜厚10nmのTiを蒸着させた後、Au80%Sn20%で構成されるAu-Snハンダを膜厚3μm蒸着させることでハンダ層15を形成する。

【0127】

(ステップS8)

次に、成長基板61とは別に準備された基板11に、上記保護層17と同様の方法で保護層13を形成する。基板11としては、上述したようにCuW、W、Mo等の導電性基板、又はSi等の半導体基板を利用することができる。

10

【0128】

そして、成長基板61と基板11とを貼り合わせる。一例としては、280℃の温度、0.2MPaの圧力下で、成長基板61上に形成されたハンダ層15と、基板11の上層に形成された保護層17とを貼り合わせる(図2E参照)。

【0129】

なお、基板11において、保護層17の上層にもハンダ層15を形成しておき、貼り合わせ時ににおいて、基板11上のハンダ層15と成長基板61上のハンダ層15を貼り合わせるものとしても構わない。

【0130】

20

(ステップS9)

次に、成長基板61を剥離する。より具体的には、成長基板61を上に、基板11を下に向かた状態で、成長基板61側からKrFエキシマレーザを照射して、成長基板61とエピタキシャル層39の界面を分解させることで成長基板61の剥離を行う。

【0131】

成長基板61としてサファイア基板を利用する場合、サファイアはレーザが通過する一方、その下層のGaN(アンドープ層36)はレーザを吸収するため、この界面が高温化してGaNが分解される。これによって成長基板61が剥離される。

【0132】

その後、ウェハ上に残存しているGaN(アンドープ層36)を、塩酸等を用いたウェットエッティング、又はICP装置を用いたドライエッティングによって除去し、n型半導体層35を露出させる。なお、本ステップS9においてアンドープ層36が除去されて、p型半導体層31、発光層33、及びn型半導体層35が下からこの順に積層されてなる半導体層30が残存する(図2F参照)。

30

【0133】

(ステップS10)

次に、図2Gに示すように、隣接する素子同士を分離する。具体的には、隣接素子との境界領域に対し、ICP装置を用いて絶縁層19の上面が露出するまで半導体層30をエッティングする。このとき、上述したように絶縁層19はエッティングストッパーとして機能する。

40

【0134】

(ステップS11)

次に、n型半導体層35の上面の所定の領域、より詳細には、第二電極25の形成領域の鉛直上方を除いた一部の領域、すなわち第一電流遮断層21の鉛直上方の領域の一部、及び第二電流遮断層23の鉛直上方の領域の一部に第一電極41を形成する。第一電極41の形成方法の一例としては、膜厚100nmのCrと膜厚3μmのAuを蒸着した後、窒素雰囲気中で250℃、1分間程度のアニール処理を行う。このステップS11が工程(c)に対応する。

【0135】

(ステップS12)

50

そして、各素子同士を例えばレーザダイシング装置によって分離し、基板 11 の裏面を例えば A g ペーストにてパッケージと接合する。更に、第一電流遮断層 21 の鉛直上方に形成されている第一電極 41 の一部領域を電流供給部 43 として、電流供給線 45 を接続するワイヤボンディングを行う。例えば、50 g の荷重で 100  $\mu\text{m}$  のボンディング領域に A u からなる電流供給線 45 を連結させることで、ワイヤボンディングを行う。このステップ S 12 が工程 (d) に対応する。

## 【0136】

以上、ステップ S 1 ~ S 12 を経て、図 1 A ~ 図 1 D に示す半導体発光素子 1 が形成される。

## 【0137】

なお、上述した製造方法では、ステップ S 4 において第二電極 25 を形成する際に成膜した材料膜と、ステップ S 5 において第二電流遮断層 23 を形成する際に成膜した材料膜、及びステップ S 6 において第一電流遮断層 21 を形成する際に成膜した材料膜を、全て共通の材料膜とした。しかし、発光層 33 からの射出光を反射させることのできる材料であって、アニール温度に応じて p 型半導体層 31 との接触箇所における接触抵抗を制御できる材料であれば、どのような材料を用いても構わない。

## 【0138】

また、少なくとも第二電極 25 を形成する際に成膜した材料膜については発光層 33 からの射出光を反射させることのできる材料とし、第一電流遮断層 21 及び第二電流遮断層 23 を形成する際に成膜した材料膜については、上記反射機能を有しない材料としても構わない。ただし、上述した製造方法によって製造される半導体発光素子 1 と比べて、反射機能が低下するため、光取り出し効率を更に高めるという観点からは、全ての材料膜について発光層 33 からの射出光を反射させることのできる材料とするのが好ましい。

## 【0139】

## 第二の製造方法

次に、半導体発光素子 1 の第二の製造方法の一例につき説明する。なお、第一の製造方法と共に通する箇所については、その旨を記載して適宜省略する。

## 【0140】

まず、第一の製造方法と同様に、ステップ S 1 ~ S 3 を実行する。

## 【0141】

(ステップ S 4 A)

p 型半導体層 31 の上面の所定領域に所定の導電性材料で構成された材料膜を成膜する。ここでは、当該材料膜として、A g / N i / T i / P t の多層膜を用いる。より具体的には、例えばスパッタ装置にて、p 型半導体層 31 の上面の所定の領域に、膜厚 130 nm の A g 、膜厚 30 nm の N i 、膜厚 20 nm の T i 、及び膜厚 30 nm の P t を成膜する。なお、この材料膜として、p 型半導体層 31 との密着性を高めるために、A g 層の下層に膜厚 1.5 nm 程度の N i を成膜しても構わない。

## 【0142】

その後、R T A 装置等を用いてドライエア又は不活性ガス雰囲気中で 400 ~ 550 、60 秒 ~ 300 秒間のコンタクトアニール処理を行い、前記材料膜と p 型半導体層 31 とのオーミック接触を形成させ、第二電極 25 を形成する(図 2 B 参照)。このステップ S 4 A が工程 (b 1) に対応する。

## 【0143】

(ステップ S 5 A)

次に、p 型半導体層 31 の上面のうち、第二電極 25 が形成されていない領域であって、電流供給部 43 の形成予定箇所から Y 方向に一定程度遠い領域に、所定の導電性材料で構成された材料膜を成膜する。ここでは、ステップ S 4 A と同様に、A g / N i / T i / P t の多層膜を用いる。より具体的には、例えばスパッタ装置にて、p 型半導体層 31 の上面の所定の領域に、膜厚 130 nm の A g 、膜厚 30 nm の N i 、膜厚 20 nm の T i 、及びステップ S 4 A よりも薄膜の膜厚 20 nm の P t を成膜する。なお、この材料膜と

10

20

30

40

50

して、p型半導体層31との密着性を高めるために、Ag層の下層に膜厚1.5nm程度のNiを成膜しても構わない。

【0144】

その後、RTA装置等を用いてドライエア又は不活性ガス雰囲気中で400～550、60秒～300秒間のコンタクトアニール処理を行う。ステップS4Aと比べて、最上層に形成されたPtの膜厚が薄膜であるため、ステップS4Aと同等のアニール温度でコンタクトアニールを行なっても、導電性材料とp型半導体層31との間にはショットキー接觸が形成される。これにより、第一の製造方法におけるステップS5と同様に第二電流遮断層23が形成される(図2C参照)。すなわち、第二電流遮断層23は、p型半導体層31との接觸箇所にショットキー接觸が形成され、第二電極25とp型半導体層31との間よりも高い接觸抵抗となる。

10

【0145】

このステップS5Aが工程(b3)に対応する。

【0146】

(ステップS6A)

次に、p型半導体層31の上面のうち、第二電極25及び第二電流遮断層23が形成されていない領域に、所定の導電性材料で構成された材料膜を成膜する。ここでは、ステップS4A及びステップS5Aと同様に、Ag/Ni/Ti/Ptの多層膜を用いる。より具体的には、例えばスパッタ装置にて、膜厚130nmのAg、膜厚30nmのNi、膜厚20nmのTi、及びステップS5Aよりも更に薄膜の膜厚10nmのPtを成膜する。

20

【0147】

その後、RTA装置等を用いてドライエア又は不活性ガス雰囲気中で400～550、60秒～300秒間のコンタクトアニール処理を行う。ステップS4Aと比べて、最上層に形成されたPtの膜厚が薄膜であるため、ステップS4Aと同等のアニール温度でコンタクトアニールを行なっても、導電性材料とp型半導体層31との間にはショットキー接觸が形成される。更に、ステップS5Aと比べても、最上層に形成されたPtの膜厚を薄膜としているため、ステップS5Aの場合よりもp型半導体層31との間の接觸抵抗を更に高めることができる。これにより、第一の製造方法におけるステップS6と同様に第一電流遮断層21が形成される(図2D参照)。すなわち、第一電流遮断層21は、p型半導体層31との接觸箇所にショットキー接觸が形成され、第二電極25とp型半導体層31との間、更には第二電流遮断層23とp型半導体層31との間よりも高い接觸抵抗となる。

30

【0148】

このステップS6Aが、工程(b2)に対応する。

【0149】

以下、図4を参照して、最上層のPtの膜厚によって接觸抵抗が制御できることを説明する。図4は、模擬的に形成した検証用素子と、その検証用素子におけるアニール温度と抵抗率の関係を示すグラフである。図4(a)に示す検証用素子70aは、p型AlGaN71上に、膜厚1.5nmのNi層73aが形成され、Ni層73aの上層には膜厚150nmのAg層72が形成され、Ag層72の上層には膜厚30nmのNi層73が形成され、Ni層73の上層には膜厚20nmのTi層74が形成され、Ti層74の上層にはPt層75が形成されている。なお、検証用素子70aは、素子分離絶縁層76によって隣接する2素子が電気的に分離されているが、素子分離絶縁層76を形成せずに単に2素子を空間的に分離した状態で形成しても構わない。

40

【0150】

図4(b)は、異なる膜厚でPt層75を成膜した後、所定のアニール条件でコンタクトアニール処理を行った後、隣接する2素子間の抵抗をプローブ77を用いて測定し、Pt層75の膜厚との関係をグラフ化したものである。なお、具体的には、550の雰囲気下で2分間、及び500の雰囲気下で2分間の各アニール条件の下で、それぞれPt

50

層 7 5 の膜厚と検証用素子 7 0 a の抵抗値の関係を図 4 ( b ) のグラフに示している。

【 0 1 5 1 】

図 4 ( b ) によれば、どのアニール条件の場合でも、P t 層 7 5 の膜厚を 3 0 n m としたときに抵抗値が最小値となっている。この時点において A g 層 7 2 と P 型 A 1 G a N 層 7 1 との接触箇所にはオーミック接触が形成されている。そして、P t 層 7 5 の膜厚を 2 0 n m 、 1 0 n m と薄膜とするに連れ、抵抗値が大きくなっている。これは、P t 層 7 5 の厚みが薄くすることで、大気中の酸素が T i 層 7 4 に取り込まれやすくなる結果、T i 酸化物が形成されることでショットキーバリアを形成しているものと考えられる。なお、P t 層 7 5 の膜厚を 5 0 n m とした場合には抵抗値が上昇しているが、これは膜厚の増加に伴う N i 層 7 3 への酸素供給濃度の低下に起因したものと考えられる。

10

【 0 1 5 2 】

つまり、第二の製造方法によれば、第一の製造方法と異なり、アニール温度を共通にしながらも、半導体層 3 0 ( p 型半導体層 3 1 ) との接触箇所における接触抵抗を制御することが可能となる。なお、上述した方法では、導電性材料を構成する最上層の P t 層の膜厚を制御することで接触抵抗を制御したが、アニール時ににおける雰囲気の酸素濃度を調整することでも接触抵抗を制御することが可能であると考えられる。

【 0 1 5 3 】

なお、図 4 では、P 型 A 1 G a N 層 7 1 の上層に N i 層 7 3 a を備えた検証用素子 7 0 a を用いて抵抗値の測定を行ったが、N i 層 7 3 a を備えない構成としても構わない。

【 0 1 5 4 】

ステップ S 6 A の実行後は、第一の製造方法と同様にステップ S 7 ~ S 1 2 を順次実行する。これにより、図 1 A ~ 図 1 D に示す半導体発光素子 1 が形成される。

20

【 0 1 5 5 】

なお、この第二の製造方法では、ステップ S 4 A 、ステップ S 5 A 、及びステップ S 6 A において、それぞれ最上層の P t の膜厚を変化させる一方、アニール温度は共通としたが、第一の製造方法と同様にアニール温度についても異ならせるものとしても構わない。

【 0 1 5 6 】

[ 第二実施形態 ]

本発明の半導体発光素子の第二実施形態の構成及びその製造方法について説明する。なお、第一実施形態と共に構成要素については、同一の符号を付している。

30

【 0 1 5 7 】

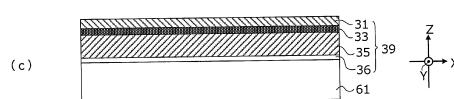

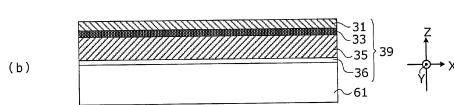

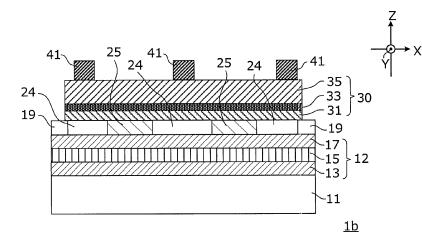

構造

図 5 A は、第二実施形態の半導体発光素子を上から見たときの模式的な平面図である。図 5 A において、半導体発光素子 1 a は光取り出し方向が紙面上向き ( Z 方向 ) である。

【 0 1 5 8 】

図 5 B は、半導体発光素子 1 a を図 5 A における B - B 線で切断したときの模式的な断面図である。図 5 C は、半導体発光素子 1 a を図 5 A における C - C 線で切断したときの模式的な断面図である。図 5 D は、半導体発光素子 1 a を図 5 A における D - D 線で切断したときの模式的な断面図である。

【 0 1 5 9 】

( 反射層 1 8 )

半導体発光素子 1 a は、第一実施形態の半導体発光素子 1 に加えて導電性の反射層 1 8 を更に備えている点が異なる。この反射層 1 8 は、発光層 3 3 から射出される光を反射する機能を有する導電性材料であり、導電層 1 2 の最上層を構成している。ここで、反射層 1 8 は、例えば第二電極 2 5 と同一の材料で構成することができる。

40

【 0 1 6 0 】

( 第一電流遮断層 2 1 、第二電流遮断層 2 3 )

本実施形態において、第一電流遮断層 2 1 及び第二電流遮断層 2 3 は、第二電極 2 5 とは異なり、発光層 3 3 から射出される光を透過する性質を有する導電性酸化膜 ( 例えば I T O ) で形成されている。なお、第一実施形態と同様、第一電流遮断層 2 1 及び第二電流

50

遮断層 2 3 は、 p 型半導体層 3 1 との接触箇所においてショットキー接觸が形成されている。

【 0 1 6 1 】

すなわち、第一電流遮断層 2 1 と p 型半導体層 3 1 との接触箇所における接觸抵抗、及び第二電流遮断層 2 3 と p 型半導体層 3 1 との接触箇所における接觸抵抗は、いずれも第二電極 2 5 と p 型半導体層 3 1 との接触箇所における接觸抵抗よりも高くなっている。更に、第一電流遮断層 2 1 と第二電流遮断層 2 3 を比較した場合、第一電流遮断層 2 1 と p 型半導体層 3 1 との接触箇所における接觸抵抗は、第二電流遮断層 2 3 と p 型半導体層 3 1 との接触箇所における接觸抵抗よりも高くなっている。

【 0 1 6 2 】

他の構成要素は第一実施形態の半導体発光素子 1 と共にであるため、説明を割愛する。

【 0 1 6 3 】

作用

本実施形態の半導体発光素子 1 a においても、第一電極 4 1 の直下には半導体層 3 0 との接觸抵抗の高い層（第一電流遮断層 2 1 、第二電流遮断層 2 3 ）が設けられるため、第一電極 4 1 から半導体層 3 0 内を鉛直方向に大部分の電流が流れることが防止される。そして、特に、電流が供給される電流供給部 4 3 の直下には、電流供給部 4 3 から離れた位置と比べて更に接觸抵抗の高い層（第一電流遮断層 2 1 ）を設けることで、電流供給部 4 3 の近傍に電流が集中することを防止している。これにより、半導体発光素子 1 a が高出力デバイスとして利用される場合、すなわち高電流が供給される場合においても、電流供給部 4 3 の近傍に電流が集中して高温になることが防止されるので、従来に比べて長寿命の素子が実現される。

【 0 1 6 4 】

製造方法

次に、半導体発光素子 1 a の製造方法の一例につき、図 2 A ~ 図 2 D 及び図 7 A ~ 図 7 D に示す模式的な製造工程図、並びに図 6 を参照して説明する。なお、第一実施形態の半導体発光素子 1 の製造方法と共に内容については、その旨を記載して適宜説明を割愛する。

【 0 1 6 5 】

まず、第一実施形態と同様の方法により、ステップ S 1 ~ S 4 を実行する（図 2 A ~ 図 2 B 参照）。この時点で、成長基板 6 1 上には、エピタキシャル層 3 9 、絶縁層 1 9 、及び第二電極 2 5 が形成される。

【 0 1 6 6 】

（ステップ S 5 B ）

ステップ S 5 と同様に、 p 型半導体層 3 1 の上面のうち、第二電極 2 5 が形成されていない領域の一部に、第二電流遮断層 2 3 を形成する（図 2 C 参照）。より詳細には、 p 型半導体層 3 1 の上面のうち、第二電極 2 5 が形成されていない領域であって、電流供給部 4 3 の形成予定箇所から Y 方向に一定程度遠い領域に第二電流遮断層 2 3 を形成する。

【 0 1 6 7 】

ここで、具体的には、スパッタ装置にて p 型半導体層 3 1 の上面の所定の領域に膜厚 1 0 0 ~ 2 0 0 nm 程度の I T O からなる材料膜を成膜する。その後、 R T A 装置等を用いてドライエア又は不活性ガス雰囲気中で、ステップ S 4 よりも低温、例えば 3 0 0 ~ 3 5 0 度、6 0 秒 ~ 3 0 0 秒間のコンタクトアニール処理を行う。不活性ガス雰囲気でコンタクトアニールを行った場合、ドライエア雰囲気の場合よりも I T O の透過率を高めることができるため、光取り出し効率を更に高める観点からは好適である。

【 0 1 6 8 】

上記の温度条件下で形成された第二電流遮断層 2 3 は、 p 型半導体層 3 1 との接触箇所にショットキー接觸が形成され、第二電極 2 5 と p 型半導体層 3 1 との間よりも高い接觸抵抗となる。

【 0 1 6 9 】

10

20

30

40

50

このステップ S 5 B は、工程 ( b 3 ) に対応する。

【 0 1 7 0 】

( ステップ S 6 B )

ステップ S 6 と同様に、 p 型半導体層 3 1 の上面のうち、第二電極 2 5 及び第二電流遮断層 2 3 が形成されていない領域に、第一電流遮断層 2 1 を形成する ( 図 2 D 参照 ) 。すなわち、第一実施形態と同様、第一電流遮断層 2 1 は、第二電流遮断層 2 3 よりも電流供給部 4 3 の形成予定箇所に近い領域に形成される。

【 0 1 7 1 】

具体的には、ステップ S 5 B と同様に、スパッタ装置にて p 型半導体層 3 1 の上面の所定の領域に膜厚 1 0 0 ~ 2 0 0 nm 程度の I T O からなる材料膜を成膜する。その後、 R T A 装置等を用いてドライエア又は不活性ガス雰囲気中で、ステップ S 5 B よりも低温、例えば 2 5 0 ~ 3 0 0 程度、 6 0 秒 ~ 3 0 0 秒間のコンタクトアニール処理を行う。

10

【 0 1 7 2 】

上記の温度条件下で形成された第一電流遮断層 2 1 は、 p 型半導体層 3 1 との接触箇所にショットキー接触が形成され、第二電極 2 5 と p 型半導体層 3 1 との間、更には第二電流遮断層 2 3 と p 型半導体層 3 1 との間よりも高い接触抵抗となる。

【 0 1 7 3 】

このステップ S 6 B は、工程 ( b 2 ) に対応する。

【 0 1 7 4 】

以下、図 6 を参照して、 I T O を形成する場合においてもコンタクトアニール温度によって接触抵抗が制御できることを説明する。図 6 は、模擬的に形成した検証用素子と、その検証用素子におけるアニール温度と抵抗率の関係を示すグラフである。図 3 ( a ) に示す検証用素子 7 0 b は、 p 型 A 1 G a N 層 7 1 上に、膜厚 1 5 0 nm の I T O 層 7 8 が形成されており、素子分離絶縁層 7 6 によって隣接する 2 素子が電気的に分離されている。なお、検証用素子 7 0 b は、素子分離絶縁層 7 6 によって隣接する 2 素子が電気的に分離されているが、素子分離絶縁層 7 6 を形成せずに単に 2 素子を空間的に分離した状態で形成しても構わない。

20

【 0 1 7 5 】

図 6 ( b ) は、 p 型 A 1 G a N 層 7 1 上に I T O 層 7 8 を蒸着し、異なるアニール温度でコンタクトアニール処理を行った後、隣接する 2 素子間の抵抗をプローブ 7 7 を用いて測定し、アニール温度との関係をグラフ化したものである。また、図 6 ( c ) は、アニール条件を異ならせて形成された各評価用素子 7 0 b に対する電流電圧特性をグラフにしたものである。

30

【 0 1 7 6 】

ここでは、 2 0 0 、 4 0 0 、 6 0 0 、 7 0 0 及び 8 0 0 の 5 種類の異なる温度条件でコンタクトアニールを行なっている。また、比較のために、 I T O 層 7 8 を蒸着した後にコンタクトアニールを行わなかった場合の結果も載せている。

【 0 1 7 7 】

図 6 ( b ) 及び ( c ) によれば、アニール温度が 4 0 0 以上の場合には、 p 型 A 1 G a N 層 7 1 と I T O 層 7 8 の間でオーミック接触が形成されていることが分かる。一方、アニール温度が 2 0 0 の場合、及びコンタクトアニール処理を行わなかった場合には、 p 型 A 1 G a N 層 7 1 と I T O 層 7 8 の間でショットキー接触が形成されていることが分かる。なお、図 6 ( b ) において、アニール温度が 4 0 0 の場合と 6 0 0 の場合を比較すると、アニール温度が 4 0 0 の方が少し接触抵抗が高くなっている。そしてアニール温度が 2 0 0 の場合と 4 0 0 の場合を比較すると、アニール温度が 2 0 0 の方が極めて接触抵抗が高くなっている。

40

【 0 1 7 8 】

従って、ステップ S 5 B において、 I T O で構成される材料膜を成膜した後、コンタクトアニール処理を 4 0 0 よりは低い温度条件で実行することで、 p 型半導体層 3 1 との接触箇所においてショットキー接触が形成される第二電流遮断層 2 3 が形成される。更に

50

、ステップS6Bにおいて、ITOで構成される材料膜を成膜した後、ステップS5Bよりも低い温度条件でコンタクトアニール処理を実行することで、p型半導体層31との接触箇所における接触抵抗が、第二電流遮断層23よりも更に高い第一電流遮断層21が形成される。

【0179】

(ステップS7A)

第二電極25、第一電流遮断層21、及び第二電流遮断層23の上面に跨るように、全面に反射層18を形成する(図7A参照)。この反射層18は、上述したように発光層33から射出される光を反射する機能を有する導電性材料であり、例えば、第二電極25と同一の材料で構成することができる。

10

【0180】

すなわち、具体的には、ステップS4と同様に、膜厚150nmのAg及び膜厚30nmのNiを成膜した後、ステップS6Bにおけるアニール温度と同等以下の温度でコンタクトアニールを処理を実行して、反射層18を形成する。この反射層18は、第二電極25、第一電流遮断層21、及び第二電流遮断層23との間で密着性が確保できればよいため、ステップS4のような高温でのコンタクトアニールを実行する必要はない。

【0181】

このステップS7Aは工程(b4)に対応する。

【0182】

(ステップS7B)

20

反射層18の上層に、第一実施形態のステップS7と同様の方法で保護層17を形成する。その後、保護層17の上面にハンダ層15を形成する(図7B参照)。

【0183】

(ステップS8～S12)

以下は、第一実施形態と同様にステップS8～S12を実行する。すなわち、ステップS8と同様、成長基板61とは別に準備された基板11に、上記保護層17と同様の方法で保護層13を形成した後、成長基板61と基板11とを貼り合わせる(図7B参照)。

【0184】

次に、ステップS9と同様に成長基板61を剥離した後、ウェハ上に残存しているGaN(アンドープ層36)を除去してn型半導体層35を露出させる(図7C参照)。その後、ステップS10と同様に、隣接する素子同士を分離する(図7D参照)。

30

【0185】

次に、ステップS11と同様に、n型半導体層35の上面の所定の領域、より詳細には、第二電極25の形成領域の鉛直上方を除いた一部の領域、すなわち第一電流遮断層21の鉛直上方の領域の一部、及び第二電流遮断層23の鉛直上方の領域の一部に第一電極41を形成する。その後、ステップS12と同様に、各素子同士を例えばレーザダイシング装置によって分離し、基板11の裏面を例えばAgペーストにてパッケージと接合する。更に、第一電流遮断層21の鉛直上方に形成されている第一電極41の一部領域を電流供給部43として、電流供給線45を接続するワイヤボンディングを行う。これにより、図5A～図5Dに示す半導体発光素子1aが形成される。

40

【0186】

[別実施形態]

以下、半導体発光素子及びその製造方法の別実施形態について説明する。

【0187】

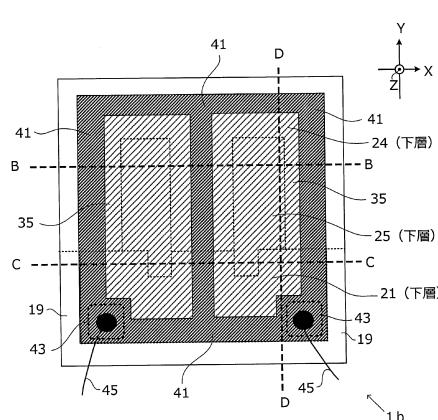

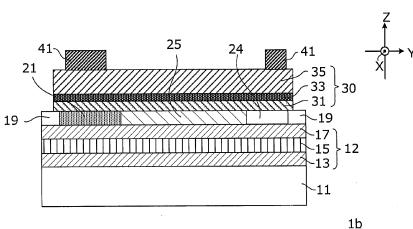

1 図8A～図8Dは、別実施形態の半導体発光素子1bの構成を模式的に示す図面である。図8Aは半導体発光素子1bを上から見たときの模式的な平面図、図8Bは、半導体発光素子1bを図8AにおけるB-B線で切断したときの模式的な断面図である。図8Cは、半導体発光素子1bを図8AにおけるC-C線で切断したときの模式的な断面図である。図8Dは、半導体発光素子1bを図8AにおけるD-D線で切断したときの模式的な断面図である。

50

## 【0188】

半導体発光素子1bは、上述した各実施形態と同様に、電流供給部43の鉛直下方を含む領域に第一電流遮断層21を備える一方、上述した各実施形態とは異なり、第二電流遮断層23を備えず、これに代えて絶縁層24を備える構成である。なお、この絶縁層24は絶縁層19と同一の材料で形成しても構わないし、異なる材料で形成しても構わない。

## 【0189】

このように構成された半導体発光素子1bにおいても、電流供給部43の鉛直下方には接触抵抗の高い第一電流遮断層21が形成されているため、電流供給部43に供給された電流は、電流供給部43からZ方向（鉛直方向）には極めて流れにくい構成となっている。よって、電流供給部43から供給された電流は、鉛直下方には流れず、第一電極41を介してX-Y平面に平行な方向に拡げられて、導電層12に向けて半導体層30内を流れ10する。これにより、電流供給部43の近傍に電流が集中することを緩和できる。

## 【0190】

ただし、半導体発光素子1bの構成の場合、電流供給部43からY方向に離れた位置においても、第一電極41の鉛直下方には抵抗の高い絶縁層24が形成されている。このため、上述した各実施形態の素子に比べて、電流供給部43からY方向に離れた位置に電流を拡げる効果は減少する。

## 【0191】

なお、図8A～図8Dに示す構成において、光取り出し効率を高める目的で、第二実施形態の半導体発光素子1aと同様に反射層18を備える構成としても構わない。この場合20、反射層18は、第二電極25、第一電流遮断層21、及び絶縁層24の下層に形成される。

## 【0192】

2 上述した第二実施形態の半導体発光素子1aは、第一電流遮断層21及び第二電流遮断層23をいずれもITO等の光透過性の材料で形成した上で、光取り出し効率を高める目的で反射層18をその下層に設ける構成とした。しかし、第一電流遮断層21及び第二電流遮断層23をいずれもITO等の光透過性の材料で形成しながらも、反射層18を備えない構成としても構わない。ただし、反射層18を備えた場合の方が、備えない場合に比べて光取り出し効率は向上する。

## 【0193】

3 第二電極25を形成する材料膜は、発光層33から射出される光の波長に応じて、適宜選択されるものとして構わない。例えば、発光層33からの光が波長350nm未満の深紫外光の領域である場合には、第二電極25を形成する材料をA1を含む材料とすることができる。また、発光層33からの光が波長350nm以上590nm以下の領域、すなわち紫外光～黄色光の領域である場合には、第二電極25を形成する材料をAgを含む材料とすることができる。また、発光層33からの光が590nmを超える領域、すなわち橙色光～赤外光領域である場合には、第二電極25を形成する材料をAg、Cu、又はAuを含む材料とすることができる。

## 【0194】

なお、第一電流遮断層21及び第二電流遮断層23が、第二電極25と同様に、発光層33から射出される光に対して反射機能を有する材料を用いて形成される場合には、これらの材料についても、前記した第二電極25と同様に発光層33から射出される光の波長に応じて適宜選択されるものとして構わない。

## 【0195】

4 上述の実施形態において、第二電極25は第一電極41の非形成領域の鉛直下方の一部領域に形成されるものとして説明した。しかし、第二電極25は、少なくとも電流供給部43の非形成領域の鉛直下方の一部領域に形成されればよく、例えば第二電極25の一部分が第一電極41の鉛直下方に位置しているものとしても構わない。ただし、半導体層30を流れる電流を基板11の面に平行な方向により拡げるという観点からは、上述した実施形態のように、第二電極25を第一電極41の形成領域の鉛直下方の位置50

には配置しないのが好ましい。

【符号の説明】

【0196】

|                     |   |             |    |

|---------------------|---|-------------|----|

| 1 , 1 a , 1 b       | ： | 本発明の半導体発光素子 |    |

| 1 1                 | ： | 基板          |    |

| 1 2                 | ： | 導電層         |    |

| 1 3                 | ： | 保護層         |    |

| 1 5                 | ： | ハンダ層        |    |

| 1 7                 | ： | 保護層         | 10 |

| 1 8                 | ： | 反射層         |    |

| 1 9                 | ： | 絶縁層         |    |

| 2 1                 | ： | 第一電流遮断層     |    |

| 2 3                 | ： | 第二電流遮断層     |    |

| 2 4                 | ： | 絶縁層         |    |

| 2 5                 | ： | 第二電極        |    |

| 3 0                 | ： | 半導体層        |    |

| 3 1                 | ： | p型半導体層      |    |

| 3 3                 | ： | 発光層         |    |

| 3 5                 | ： | n型半導体層      | 20 |

| 3 6                 | ： | アンドープ層      |    |

| 3 9                 | ： | エピタキシャル層    |    |

| 4 1                 | ： | 第一電極        |    |

| 4 3                 | ： | 電流供給部       |    |

| 4 5                 | ： | 電流供給線       |    |

| 6 1                 | ： | 成長基板        |    |

| 7 0 , 7 0 a , 7 0 b | ： | 検証用素子       |    |

| 7 1                 | ： | p型AlGaN層    |    |

| 7 2                 | ： | Ag層         |    |

| 7 3 , 7 3 a         | ： | Ni層         |    |

| 7 4                 | ： | Ti層         | 30 |

| 7 5                 | ： | Pt層         |    |

| 7 6                 | ： | 素子分離絶縁層     |    |

| 7 7                 | ： | プローブ        |    |

| 7 8                 | ： | ITO層        |    |

| 1 0 0               | ： | 従来の半導体発光素子  |    |

| 1 0 1               | ： | 支持基板        |    |

| 1 0 2               | ： | ボンディング層     |    |

| 1 0 3               | ： | 反射電極        |    |

| 1 0 4               | ： | オーム接觸層      | 40 |

| 1 0 5               | ： | 電流遮断層       |    |

| 1 0 6               | ： | アイソレーション層   |    |

| 1 0 7               | ： | 半導体層        |    |

| 1 0 8               | ： | n側電極        |    |

| 1 0 9               | ： | 電流供給部       |    |

| 1 1 1               | ： | p型半導体層      |    |

| 1 1 2               | ： | 発光層         |    |

| 1 1 3               | ： | n型半導体層      |    |

| 1 1 7               | ： | n型半導体層の割れ   |    |

| 1 1 8               | ： | n型半導体層の溶融   |    |

【図1A】

【図1C】

【図1D】

【図1B】

【図2A】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図6】

【図7A】

【図7B】

【図 7 C】

【図 7 D】

【図 8 A】

【図 8 C】

【図 8 B】

【図 8 D】

【図9】

【図10】

【図13】

【図11】

【図12】

【図14】

---

フロントページの続き

審査官 島田 英昭

(56)参考文献 特開2011-243956 (JP, A)

米国特許出願公開第2012/0061704 (US, A1)

特開2013-197197 (JP, A)

特開2012-169526 (JP, A)

特開2006-269912 (JP, A)

特開昭59-125680 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L33/00 - 33/64