(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5286034号

(P5286034)

(45) 発行日 平成25年9月11日(2013.9.11)

(24) 登録日 平成25年6月7日(2013.6.7)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 21/336 | (2006.01) | HO1L 29/78  | 616L |

| HO1L 29/786 | (2006.01) | HO1L 29/78  | 627F |

| HO1L 29/78  | (2006.01) | HO1L 29/78  | 301S |

| HO1L 21/265 | (2006.01) | HO1L 21/265 | 602C |

| HO1L 21/20  | (2006.01) | HO1L 21/265 | 602B |

請求項の数 7 (全 37 頁) 最終頁に続く

(21) 出願番号

特願2008-284435 (P2008-284435)

(22) 出願日

平成20年11月5日 (2008.11.5)

(65) 公開番号

特開2009-135483 (P2009-135483A)

(43) 公開日

平成21年6月18日 (2009.6.18)

審査請求日 平成23年10月28日 (2011.10.28)

(31) 優先権主張番号

特願2007-289750 (P2007-289750)

(32) 優先日

平成19年11月7日 (2007.11.7)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100103159

弁理士 加茂 裕邦

(72) 発明者 大沼 英人

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 鈴木 聰一郎

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

(57) 【特許請求の範囲】

## 【請求項 1】

第1の半導体層の表面を酸化あるいは窒化して、前記第1の半導体層の表面に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜をエッチングして、前記第1の絶縁膜上にソース領域及びドレイン領域の一部となる第2の半導体層を形成し、

前記第1の半導体層の表面を酸化あるいは窒化して、前記第1の半導体層の表面に第2の絶縁膜を形成し、

前記第2の絶縁膜上にゲート電極を形成し、

前記ゲート電極をマスクとして、前記第1の半導体層及び前記第2の半導体層に、一導電型を付与する不純物元素を添加し、

前記第1の半導体層及び前記第2の半導体層を加熱して、前記不純物元素を活性化させて前記ソース領域及び前記ドレイン領域を形成するとともに、前記第1の半導体層と前記第2の半導体層との間の前記第1の絶縁膜の少なくとも一部を消失させることを特徴とする半導体装置の作製方法。

## 【請求項 2】

第1の半導体層の表面を酸化あるいは窒化して、前記第1の半導体層の表面に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

10

20

前記半導体膜をエッティングして、前記第1の絶縁膜上にソース領域及びドレイン領域の一部となる第2の半導体層を形成し、

前記第1の半導体層の表面を酸化あるいは窒化して、前記第1の半導体層の表面に第2の絶縁膜を形成し、

前記第1の絶縁膜及び前記第2の絶縁膜上に、第3の絶縁膜を形成し、

前記第3の絶縁膜上に、ゲート電極を形成し、

前記ゲート電極をマスクとして、前記第1の半導体層及び前記第2の半導体層に、一導電型を付与する不純物元素を添加し、

前記第1の半導体層及び前記第2の半導体層を加熱して、前記不純物元素を活性化させて前記ソース領域及び前記ドレイン領域を形成するとともに、前記第1の半導体層と前記第2の半導体層との間の前記第1の絶縁膜の少なくとも一部を消失させることを特徴とする半導体装置の作製方法。 10

【請求項3】

第1の半導体層の表面を酸化あるいは窒化して、前記第1の半導体層の表面に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜をエッティングして、前記第1の絶縁膜上にソース領域及びドレイン領域の一部となる第2の半導体層を形成し、

前記第1の絶縁膜のうち、前記第1の半導体層と前記第2の半導体層との間の領域以外を除去して、前記第1の半導体層のうち、前記第2の半導体層が形成されていない領域を露出させ、 20

前記第1の半導体層の露出した表面を酸化あるいは窒化して、第2の絶縁膜を形成し、前記第2の絶縁膜上に、ゲート電極を形成し、

前記ゲート電極をマスクとして、前記第1の半導体層及び前記第2の半導体層に、一導電型を付与する不純物元素を添加し、

前記第1の半導体層及び前記第2の半導体層を加熱して、前記不純物元素を活性化させて前記ソース領域及び前記ドレイン領域を形成するとともに、前記第1の半導体層と前記第2の半導体層との間の前記第1の絶縁膜の少なくとも一部を消失させることを特徴とする半導体装置の作製方法。 30

【請求項4】

第1の半導体層の表面を酸化あるいは窒化して、前記第1の半導体層の表面に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜をエッティングして、前記第1の絶縁膜上にソース領域及びドレイン領域の一部となる第2の半導体層を形成し、

前記第1の絶縁膜のうち、前記第1の半導体層と前記第2の半導体層との間の領域以外を除去して、前記第1の半導体層のうち、前記第2の半導体層が形成されていない領域を露出させ、

前記第1の半導体層の露出した領域に、第2の絶縁膜を形成し、

前記第2の絶縁膜上に、ゲート電極を形成し、 40

前記ゲート電極をマスクとして、前記第1の半導体層及び前記第2の半導体層に、一導電型を付与する不純物元素を添加し、

前記第1の半導体層及び前記第2の半導体層を加熱して、前記不純物元素を活性化させて前記ソース領域及び前記ドレイン領域を形成するとともに、前記第1の半導体層と前記第2の半導体層との間の前記第1の絶縁膜の少なくとも一部を消失させることを特徴とする半導体装置の作製方法。 50

【請求項5】

第1の半導体層上に、ゲート絶縁膜を形成し、

前記ゲート絶縁膜上に、ゲート電極を形成し、

前記ゲート電極の側面に、サイドウォールを形成し、

前記ゲート絶縁膜のうち、前記ゲート電極及び前記サイドウォールが形成されていない領域をエッティングして、前記第1の半導体層のうち、前記ゲート電極及び前記サイドウォールが形成されていない領域を露出させ、

前記第1の半導体層の露出した表面を酸化あるいは窒化して、第1の絶縁膜を形成し、前記第1の絶縁膜、前記ゲート電極、及び前記サイドウォールを覆って、半導体膜を形成し、

前記半導体膜をエッティングして、前記第1の絶縁膜上にソース領域及びドレイン領域の一部となる第2の半導体層を形成し、

前記ゲート電極及び前記サイドウォールをマスクとして、前記第1の半導体層及び前記第2の半導体層に、一導電性を付与する不純物元素を添加し、

前記第1の半導体層及び前記第2の半導体層を加熱して、前記不純物元素を活性化させて前記ソース領域及び前記ドレイン領域を形成するとともに、前記第1の半導体層と前記第2の半導体層との間の前記第1の絶縁膜を消失させることを特徴とする半導体装置の作製方法。

#### 【請求項6】

請求項1乃至請求項3のいずれか一項において、

前記第1の絶縁膜及び前記第2の絶縁膜は、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかであることを特徴とする半導体装置の作製方法。

#### 【請求項7】

請求項4又は請求項5において、

前記第1の絶縁膜は、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかであることを特徴とする半導体装置の作製方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置の作製方法に関する。

##### 【背景技術】

##### 【0002】

L S I の分野で、ソース及びドレインのせり上げ構造 ( r a i s e d s o u r c e a n d d r a i n ) が開発されており、薄膜トランジスタ ( T h i n F i l m T r a n s i s t o r ) 等を作製する薄膜の分野での使用も検討されている。 L S I の分野では、高温プロセスである選択エピタキシャル法が用いられているが、薄膜分野ではガラス基板等を用いる場合、高温プロセスを用いることができないので、ソース及びドレインのせり上げ構造を実現するのが難しい。

##### 【0003】

薄膜の分野では結晶性半導体膜上に、n型の非晶質珪素膜 ( n<sup>+</sup> - S i ) を形成し、ドライエッティングにおける両者のエッティングレートの違いを利用して、n型の非晶質珪素膜のエッティングする一方、結晶性半導体膜をエッティングしないことが試みられている ( 非特許文献1参照 ) 。

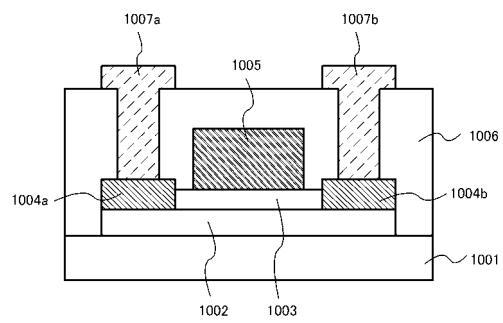

##### 【0004】

非特許文献1の薄膜トランジスタの構造を、図2に示す。図2では、膜厚200nmの酸化膜が形成された石英の基板あるいはシリコン基板1001上に、膜厚100nmの結晶性半導体膜1002、ゲート酸化膜1003、ゲート電極1005が設けられている。結晶性半導体膜1002上には、膜厚100nmのn型非晶質珪素膜1004a及び1004bが形成されている。

##### 【0005】

さらに、100nmの膜厚の酸化珪素膜1006が形成され、酸化珪素膜1006上に

10

20

30

40

50

は、n型非晶質珪素膜1004a及び1004bそれぞれに接続される、ソース電極及びドレイン電極1007a及び1007bが形成されている。

【非特許文献1】「Raised source and drain structure of poly-Si TFT」Shusheng He and Jersh en Maa, Electrochemical Society Proceeding, Volume 98-22, p. 204-220.

【発明の開示】

【発明が解決しようとする課題】

【0006】

結晶性半導体膜1002の厚さが厚い(非特許文献1では100nm)と、結晶性半導体膜1002とn型非晶質珪素膜( $n^+ - Si$ )1004a及び1004bのエッチャングレート比が大きくななくても、エッチャングを途中で止めることで、結晶性半導体膜1002をエッチャングすることなく、n型非晶質珪素膜( $n^+ - Si$ )1004a及び1004bのみをエッチャングできる。

【0007】

しかしながら、結晶性半導体膜1002の厚さが薄く(例えば40nm以下)なってしまうと、エッチャングレートの差があったとしても、n型非晶質珪素膜( $n^+ - Si$ )1004a及び1004bだけでなく、結晶性半導体膜1002もエッチャングしてしまう恐れがある。

【0008】

またCMOSトランジスタを形成する場合は、p型非晶質珪素膜( $p^+ - Si$ )を成膜及びエッチャングする必要が生じ、作製工程が複雑かつ不安定になってしまう恐れがある。

【課題を解決するための手段】

【0009】

第1の半導体膜上に、極薄い、半導体膜の、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、あるいは窒化膜を形成し、さらに第2の半導体膜を形成する。第2の半導体膜をエッチャングする際には、極薄い酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、あるいは窒化膜がエッチャングストッパーとなり、第1の半導体膜がエッチャングされるのを防ぐ。

【0010】

さらに第1と第2の半導体の間の、極薄い、半導体膜の、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、あるいは窒化膜は、一導電性を付与する不純物元素を導入し、活性化させる加熱処理により、酸素あるいは窒素が拡散し、極薄い、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、あるいは窒化膜は消滅する。これにより、ソース領域及びドレイン領域が形成される。

【0011】

さらに、一導電性を付与する不純物元素の導入の際に、酸素や窒素が不純物元素による衝突によってはじき出される。そのため酸化膜あるいは窒化膜中の、酸素濃度あるいは窒素濃度が低下する。

【0012】

本発明は、以下の半導体装置の作製方法に関するものである。

【0013】

本発明は、絶縁表面を有する基板上に、島状半導体膜を形成し、前記島状半導体膜の表面を酸化あるいは窒化して、前記島状半導体膜の表面に、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかである第1の絶縁膜を形成し、前記第1の絶縁膜の一部の領域上に、半導体膜を形成し、前記島状半導体膜の表面を酸化あるいは窒化して、前記島状半導体膜表面に、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜のいずれかである第2の絶縁膜を形成し、前記第1の絶縁膜及び、前記第2の絶縁膜をゲート絶縁膜とし、前記ゲート絶縁膜上に、ゲート電極を形成し、前記ゲート電極をマスクとして、前記島状半導体膜及び半導体膜に、一導電型を付与する不純物元素を添加し、前記島状半導体膜及び半導体膜を加

10

20

30

40

50

熱して、前記島状半導体膜及び半導体膜に添加された前記不純物元素を活性化させ、前記島状半導体膜及び半導体膜を加熱することにより、前記島状半導体膜及び半導体膜の間の前記第1の絶縁膜が消失することを特徴とする半導体装置の作製方法に関する。

【0014】

また本発明は、絶縁表面を有する基板上に、島状半導体膜を形成し、前記島状半導体膜の表面を酸化あるいは窒化して、前記島状半導体膜の表面に、前記島状半導体膜の、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかである第1の絶縁膜を形成し、前記第1の絶縁膜の一部の領域上に、半導体膜を形成し、前記島状半導体膜の表面を酸化あるいは窒化して、前記島状半導体膜表面に、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜のいずれかである第2の絶縁膜を形成し、前記第1の絶縁膜並びに前記第2の絶縁膜に、第3の絶縁膜を形成し、前記第3の絶縁膜上に、ゲート電極を形成し、前記ゲート電極をマスクとして、前記島状半導体膜及び半導体膜に、一導電型を付与する不純物元素を添加し、前記島状半導体膜及び半導体膜を加熱して、前記島状半導体膜及び半導体膜に添加された前記不純物元素を活性化させ、前記島状半導体膜及び半導体膜を加熱することにより、前記島状半導体膜及び半導体膜の間の前記第1の絶縁膜が消失することを特徴とする半導体装置の作製方法に関する。 10

【0015】

また本発明は、絶縁表面を有する基板上に、島状半導体膜を形成し、前記島状半導体膜の表面を酸化あるいは窒化して、前記島状半導体膜の表面に、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかである第1の絶縁膜を形成し、前記第1の絶縁膜の一部の領域上に、半導体膜を形成し、前記第1の絶縁膜の、前記島状半導体膜と前記半導体膜に挟まれている領域以外を除去して、前記島状半導体膜の中の前記半導体膜が形成されていない領域を露出させ、前記島状半導体膜の表面及び前記半導体膜を酸化あるいは窒化して、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかである第2の絶縁膜を形成し、前記島状半導体膜の露出した領域に形成された前記第2の絶縁膜上に、ゲート電極を形成し、前記ゲート電極をマスクとして、前記島状半導体膜及び半導体膜に、一導電型を付与する不純物元素を添加し、前記島状半導体膜及び半導体膜を加熱して、前記島状半導体膜及び半導体膜に添加された前記不純物元素を活性化させ、前記島状半導体膜及び半導体膜を加熱することにより、前記第1の絶縁膜が消失することを特徴とする半導体装置の作製方法に関する。 20

【0016】

また本発明は、絶縁表面を有する基板上に、島状半導体膜を形成し、前記島状半導体膜の表面を酸化あるいは窒化して、前記島状半導体膜の表面に、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかである第1の絶縁膜を形成し、前記第1の絶縁膜の一部の領域上に、半導体膜を形成し、前記第1の絶縁膜の、前記島状半導体膜と前記半導体膜に挟まれている領域以外を除去して、前記島状半導体膜の前記半導体膜が形成されていない領域を露出させ、前記島状半導体膜の露出した領域に、第2の絶縁膜を形成し、前記第2の絶縁膜上に、ゲート電極を形成し、前記ゲート電極をマスクとして、前記島状半導体膜及び半導体膜に、一導電型を付与する不純物元素を添加し、前記島状半導体膜及び半導体膜を加熱して、前記島状半導体膜及び半導体膜に添加された前記不純物元素を活性化させ、前記島状半導体膜及び半導体膜を加熱することにより、前記第1の絶縁膜が消失することを特徴とする半導体装置の作製方法に関する。 40

【0017】

また本発明は、絶縁表面を有する基板上に、島状半導体膜を形成し、前記島状半導体膜上に、絶縁膜を形成し、前記絶縁膜上に、ゲート電極を形成し、前記ゲート電極の側面に、サイドウォールを形成し、前記絶縁膜の、前記ゲート電極及びサイドウォールが形成されていない領域をエッチングし、前記島状半導体膜の前記ゲート電極及びサイドウォール 50

が形成されていない領域を露出させ、前記露出した島状半導体膜を酸化あるいは窒化して、酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜のいずれかである第1の絶縁膜を形成し、前記第1の絶縁膜、前記ゲート電極、前記サイドウォールを覆って、第1の半導体膜を形成し、前記第1の半導体膜をエッチングして、前記島状半導体膜及び前記第1の絶縁膜の一部の領域上に、第2の半導体膜を形成し、前記第2の半導体膜及び島状半導体膜に、一導電性を付与する不純物元素を添加し、前記島状半導体膜及び第2の半導体膜を加熱して、前記島状半導体膜及び第2の半導体膜に添加された前記不純物元素を活性化させ、前記島状半導体膜及び第2の半導体膜を加熱することにより、前記島状半導体膜及び第2の半導体膜の間の前記第1の絶縁膜が消失することを特徴とする半導体装置の作製方法に関する。 10

【0018】

本発明において、前記島状半導体膜は珪素を主成分とする結晶性半導体膜であり、前記半導体膜は、珪素を主成分とする半導体膜である。

【0019】

本発明において、前記島状半導体膜は珪素を主成分とする結晶性半導体膜であり、前記第1の半導体膜は、珪素を主成分とする半導体膜である。

【0020】

本発明において、前記島状半導体膜は珪素を主成分とする単結晶半導体層であり、前記半導体膜は、珪素を主成分とする半導体膜である。 20

【0021】

本発明において、前記島状半導体膜は珪素を主成分とする単結晶半導体層であり、前記第1の半導体膜は、珪素を主成分とする半導体膜である。

【0022】

本発明において、前記3の絶縁膜は、酸化珪素膜、窒素を含む酸化珪素膜、窒化珪素膜、酸素を含む窒化珪素膜のいずれか1つ、あるいは2つ以上の積層膜である。

【0023】

本発明において、前記2の絶縁膜は、酸化珪素膜、窒素を含む酸化珪素膜、窒化珪素膜、酸素を含む窒化珪素膜のいずれか1つ、あるいは2つ以上の積層膜である。

【0024】

本発明において、前記酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜の膜厚は、0.2 nm以上4 nm以下である。 30

【0025】

本発明において、前記酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、窒化膜、サブオキサイドを含む膜、あるいはサブナイトライドを含む膜の膜厚は、0.5 nm以上3 nm以下である。

【0026】

なお本明細書において、半導体装置とは、半導体を利用して機能する素子及び装置全般を指し、半導体を利用して機能する素子を搭載した電子機器もその範疇とする。 40

【発明の効果】

【0027】

基板を高温で加熱することなく、せり上げ構造のソース領域及びドレイン領域 (raised source and drain) を有する薄膜トランジスタを形成することができる。薄膜トランジスタにおいて、半導体膜上にせり上げ構造の低抵抗領域を形成することが可能となる。

【0028】

せり上げ構造の薄膜トランジスタの作製方法において、活性層である島状半導体膜をエッチングすることなく、せり上げ領域を形成することができる。

【発明を実施するための最良の形態】

10

20

30

40

50

## 【0029】

以下に本発明を図面を用いて説明する。ただし本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

## 【0030】

なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

## 【0031】

## [実施の形態1]

10

## 【0032】

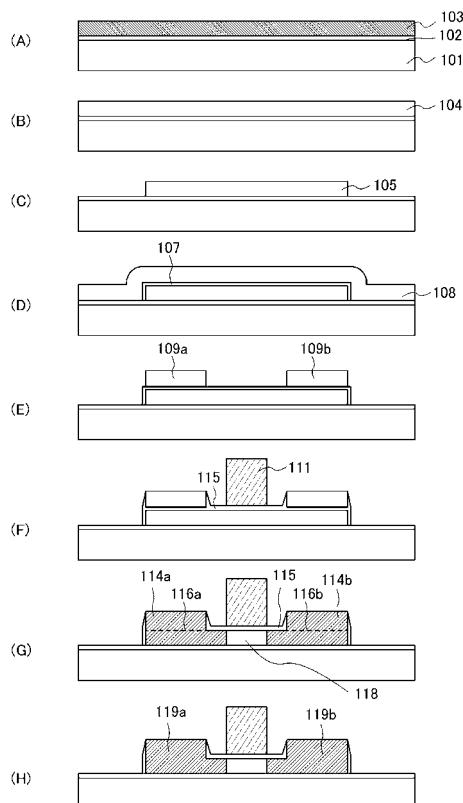

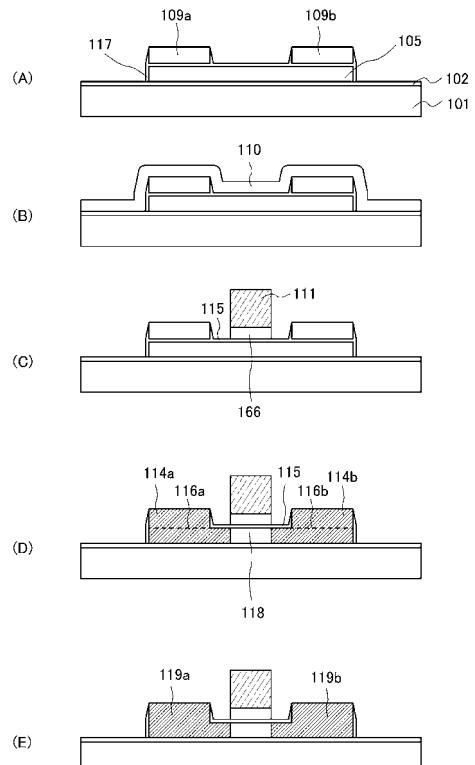

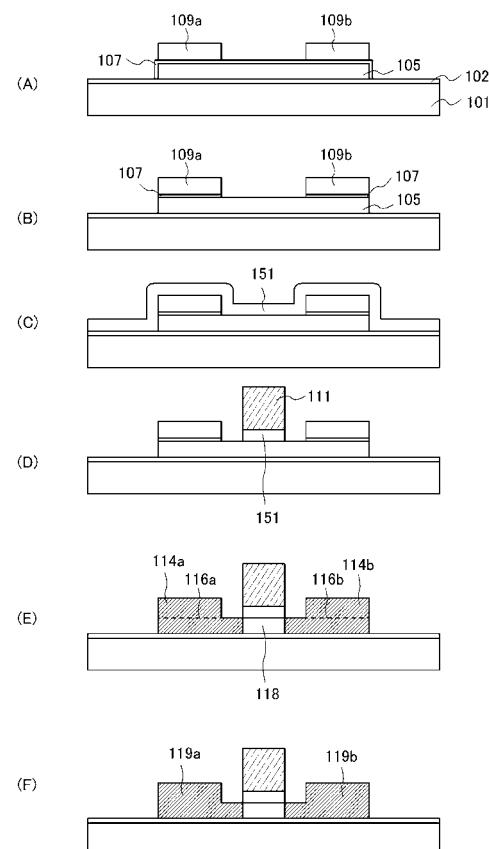

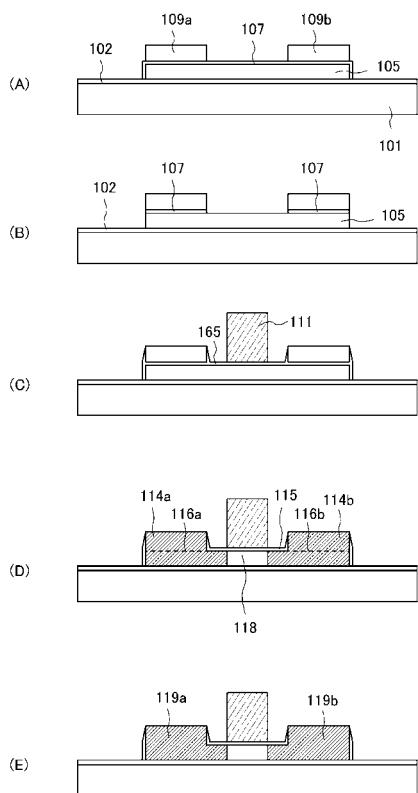

本実施の形態では、せり上げ構造の低抵抗領域を有する薄膜トランジスタの作製方法について、図1(A)～図1(H)、図10(A)～図10(E)、図11(A)～図11(F)、図23(A)～図23(E)を用いて説明する。

## 【0033】

基板101上に、下地絶縁膜102、さらに非晶質半導体膜103を形成する(図1(A)参照)。基板101は、ガラス基板、石英基板等を用いればよく、本実施の形態では、基板101としてガラス基板を用いる。

## 【0034】

下地絶縁膜102は、酸化珪素膜、窒素を含む酸化珪素膜、酸素を含む窒化珪素膜、窒化珪素膜のいずれか1つの単層膜、あるいはこれらを積層した積層膜を用いればよい。本実施の形態では、下地絶縁膜102として、窒素を含む酸化珪素膜と酸素を含む窒化珪素膜を積層した積層膜を用いる。また必要がなければ下地絶縁膜102を形成しなくてよい。

## 【0035】

基板101としてガラス基板、石英基板等を用いれば、基板101の表面は絶縁性を有している。また下地絶縁膜102を設けた基板101は、やはり絶縁表面を有する基板とみなせる。

## 【0036】

本実施の形態では、非晶質半導体膜103として、珪素を主成分とする半導体膜、例えば非晶質珪素膜(アモルファスシリコン膜)を、10～100nmの膜厚で成膜する。なお半導体膜としてゲルマニウムを主成分とする半導体膜を用いてもよい。珪素あるいはゲルマニウムを主成分とする半導体膜として、珪素膜、ゲルマニウム膜、シリコンゲルマニウム膜が含まれる。

## 【0037】

次いで非晶質半導体膜103を、レーザ照射による結晶化、加熱による結晶化等公知の方法で結晶化し、結晶性半導体膜104を形成する(図1(B)参照)。本実施の形態では、非晶質半導体膜103として非晶質珪素膜を成膜したので、結晶性半導体膜104として結晶性珪素膜が形成される。

## 【0038】

なお、基板101上に下地絶縁膜102及び結晶性半導体膜104を形成する代わりに、SOI(Silicon On Insulator)基板を用いてもよい。

## 【0039】

SOI基板を用いる場合について以下に説明する。

## 【0040】

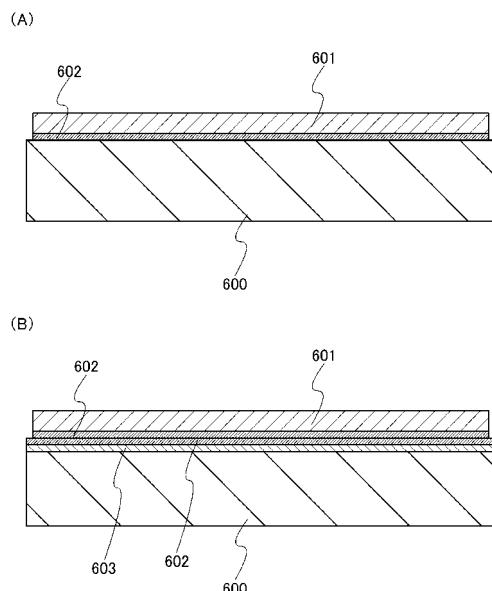

まずSOI構造を有する基板の構造について、図12(A)～図12(B)、図13(A)～図13(C)を用いて説明する。

## 【0041】

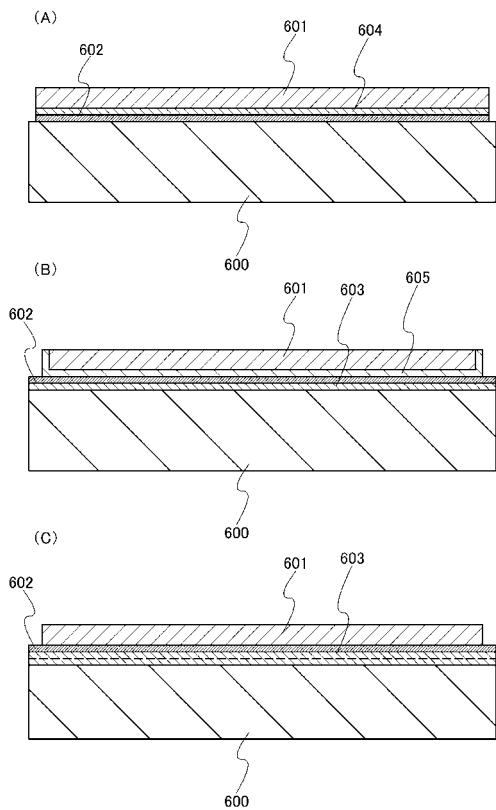

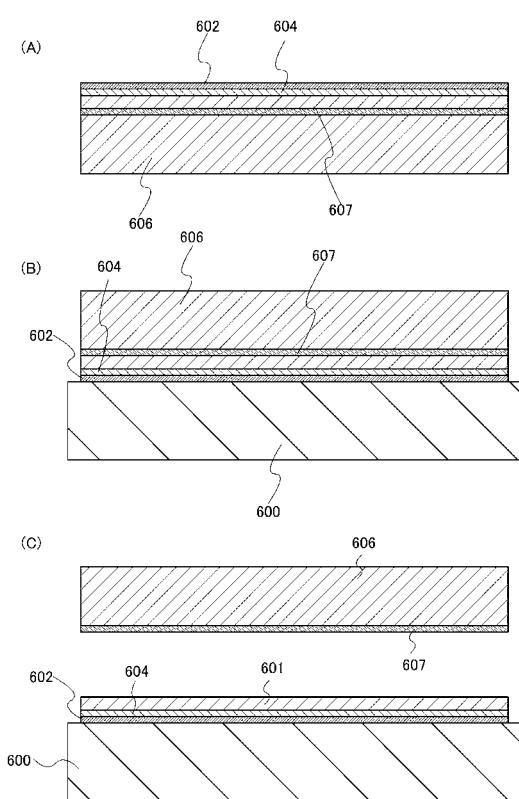

図12(A)において支持基板600は絶縁性を有するものまたは絶縁表面を有するものであり、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸

20

30

40

50

ガラスのような電子工業用に使われるガラス基板（「無アルカリガラス基板」とも呼ばれる）が適用される。

【0042】

すなわち、支持基板600として、熱膨張係数が $25 \times 10^{-7}/$ から $50 \times 10^{-7}/$ （好ましくは、 $30 \times 10^{-7}/$ から $40 \times 10^{-7}/$ ）であって歪み点が580から680（好ましくは、600から680）のガラス基板を適用することができる。その他に石英基板、セラミック基板、表面が絶縁膜で被覆された金属基板などのも適用可能である。

【0043】

LTSS (Low Temperature Single crystal Semiconductor) 層601は単結晶半導体層であり、珪素を主成分とする単結晶半導体層、あるいはゲルマニウムを主成分とする単結晶半導体層等、代表的には単結晶シリコン（単結晶珪素）が適用される。

【0044】

その他に、LTSS層601として、水素イオン注入剥離法のようにして単結晶半導体基板もしくは多結晶半導体基板から剥離可能であるガリウムヒ素、インジウムリンなどの化合物半導体による結晶性半導体層を適用することもできる。

【0045】

支持基板600とLTSS層601の間には、平滑面を有し親水性表面を形成する接合層602を設ける。この接合層602は平滑面を有し親水性表面を有する層とする。このような表面を形成可能なものとして、化学的な反応により形成される絶縁層が好ましい。例えば、熱的または化学的な反応により形成される酸化半導体膜が適している。主として化学的な反応により形成される膜であれば表面の平滑性を確保できるからである。

【0046】

また、平滑面を有し親水性表面を形成する接合層602は0.2nm乃至500nmの厚さで設けられる。この厚さであれば、被成膜表面の表面荒れを平滑化すると共に、当該膜の成長表面の平滑性を確保することが可能である。

【0047】

LTSS層601がシリコンによるものであれば、酸化性雰囲気下において熱処理により形成される酸化シリコン、酸素ラジカルの反応により成長する酸化シリコン、酸化性の薬液により形成されるケミカルオキサイドなどを接合層602とすることができる。

【0048】

接合層602としてケミカルオキサイドを用いる場合には0.2nmから3nmの厚さであれば良い。また、好適には化学気相成長法により堆積される酸化シリコンを接合層602とすることができます。この場合、有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。

【0049】

有機シランガスとしては、珪酸エチル (TEOS: 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、テトラメチルシラン (TMS: 化学式  $\text{Si}(\text{CH}_3)_4$ )、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン ( $\text{SiH}(\text{OC}_2\text{H}_5)_3$ )、トリスジメチルアミノシラン ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) 等のシリコン含有化合物を用いることができる。

【0050】

接合層602はLTSS層601側に設けられ、支持基板600の表面と密接することで、室温であっても接合をすることが可能である。より強固に接合を形成するには、支持基板600とLTSS層601を押圧すれば良い。異種材料である支持基板600と接合層602を接合するには表面を清浄化する。支持基板600と接合層602の互いに清浄化された表面を密接させると表面間引力により接合が形成される。

【0051】

10

20

30

40

50

さらに、支持基板 600 の表面に複数の親水基を付着させると、接合を形成するのにより好ましい態様となる。例えば、支持基板 600 の表面を酸素プラズマ処理もしくはオゾン処理、あるいはオゾン水への浸漬処理により親水性にすることが好ましい。

【0052】

このように支持基板 600 の表面を親水性にする処理を加えた場合には、表面の水酸基が作用して水素結合により接合が形成される。さらに清浄化された表面同士を密接させて接合を形成したものに対して、室温以上の温度で加熱すると接合強度高めることができる。

【0053】

異種材料である支持基板 600 と接合層 602 を接合するための処理として、接合を形成する表面にアルゴンなどの不活性ガスによるイオンビームを照射して清浄化しても良い。イオンビームの照射により、支持基板 600 もしくは接合層 602 の表面に未結合手が露呈して非常に活性な表面が形成される。

【0054】

このように活性化された表面同士を密接させると、支持基板 600 と接合層 602 の接合を低温でも形成することが可能である。表面を活性化して接合を形成する方法は、当該表面を高度に清浄化しておくことが要求されるので、真空中で行うことが好ましい。

【0055】

L T S S 層 601 は結晶半導体基板を薄片化して形成されるものである。例えば、単結晶半導体基板として単結晶シリコン基板を用いた場合、単結晶シリコン基板の所定の深さに水素クラスターイオン ( $H_2^+$ 、 $H_3^+$ ) を質量分離せずにドープするイオンドープ法でドープし、その後熱処理を行って表層の単結晶シリコン層を剥離して形成することができる。また、水素イオン ( $H^+$ ) や水素クラスターイオンをイオン注入法を用いて注入してもよい。

【0056】

また、ポーラスシリコン（多孔性シリコン）上に単結晶シリコンをエピタキシャル成長させた後、ポーラスシリコン層をウォータージェットで劈開して剥離する方法を適用しても良い。L T S S 層 601 の厚さは 5 nm 乃至 500 nm、好ましくは 10 nm 乃至 200 nm の厚さである。

【0057】

図 12 (B) は支持基板 600 にバリア層 603 と接合層 602 を設けた構成を示す。バリア層 603 を設けることで、支持基板 600 として用いられるガラス基板からアルカリ金属もしくはアルカリ土類金属のような可動イオン不純物が拡散して L T S S 層 601 が汚染されることを防ぐことができる。バリア層 603 上には接合層 602 を設けることが好ましい。

【0058】

支持基板 600 において、不純物の拡散を防止するバリア層 603 と接合強度を確保する接合層 602 による機能が異なる複数の層を設けることにより、支持基板の選択範囲を広げることができる。L T S S 層 601 側にも接合層 602 を設けておくことが好ましい。すなわち、支持基板 600 に L T S S 層 601 を接合するに際し、接合を形成する面の一方もしくは双方に接合層 602 を設けることが好ましく、それにより接合強度を高めることができる。

【0059】

図 13 (A) は L T S S 層 601 と接合層 602 の間に絶縁層 604 を設けた構成を示す。絶縁層 604 は窒素を含有する絶縁層であることが好ましい。例えば、窒化シリコン膜、酸素を含む窒化シリコン膜もしくは窒素を含む酸化シリコン膜から選ばれた 1 つまたは複数の膜を積層して形成することができる。

【0060】

例えば、絶縁層 604 として、L T S S 層 601 側から窒素を含む酸化シリコン膜、酸

10

20

30

40

50

素を含む窒化シリコン膜を積層した積層膜を用いることができる。接合層 602 が支持基板 600 と接合を形成する機能を有するのに対し、絶縁層 604 は不純物により LTSS 層 601 が汚染されることを防止する。

【0061】

なお、ここで窒素を含む酸化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が 55 原子% ~ 65 原子%、窒素が 0.5 原子% ~ 20 原子%、Si が 25 原子% ~ 35 原子%、水素が 0.1 原子% ~ 15 原子% の範囲で含まれるものという。また、酸素を含む窒化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が 5 原子% ~ 30 原子%、窒素が 20 原子% ~ 50 原子%、Si が 25 原子% ~ 35 原子%、水素が 15 原子% ~ 25 原子% の範囲で含まれるものという。10

【0062】

図 13 (B) は、支持基板 600 に接合層 602 を設けた構成である。支持基板 600 と接合層 602 との間にはバリア層 603 が設けられていることが好ましい。支持基板 600 として用いられるガラス基板からアルカリ金属もしくはアルカリ土類金属のような可動イオン不純物が拡散して LTSS 層 601 が汚染されることを防ぐためである。LTSS 層 601 には直接酸化で形成された酸化シリコン層 605 が形成されている。この酸化シリコン層 605 が接合層 602 と接合を形成し、支持基板 600 上に LTSS 層 601 を固定する。酸化シリコン層 605 は熱酸化により形成されたものが好ましい。20

【0063】

図 13 (C) は、支持基板 600 に接合層 602 を設けた別の構成である。支持基板 600 と接合層 602 との間にはバリア層 603 が設けられている。20

【0064】

図 13 (C) では、バリア層 603 は一層または複数の層をもって構成する。例えば、ナトリウムなどのイオンをブロッキングする効果の高い窒化シリコン膜または酸素を含む窒化シリコン膜を第 1 層目として用い、その上層に第 2 層目として酸化シリコン膜または窒素を含む酸化シリコン膜を設ける。

【0065】

バリア層 603 の第 1 層目は不純物の拡散を防止する目的を持った絶縁膜であり緻密な膜であるのに対し、第 2 層目は第 1 層目の膜の内部応力が上層に作用しないように、応力を緩和することを一つの目的としている。このように支持基板 600 にバリア層 603 を設けることで、LTSS 層を接合する際の基板の選択範囲を広げることができる。30

【0066】

バリア層 603 には接合層 602 が形成されており、支持基板 600 と LTSS 層 601 を固定する。

【0067】

図 12 (A) ~ 図 12 (B)、図 13 (A) ~ 図 13 (C) に示す SOI 構造を有する基板の作製方法について、図 14 (A) ~ 図 14 (C)、図 15 (A) ~ 図 15 (B)、図 16 (A) ~ 図 16 (C)、図 17 (A) ~ 図 17 (C)、図 18 (A) ~ 図 18 (B)、図 19 (A) ~ 図 19 (C) を用いて説明する。40

【0068】

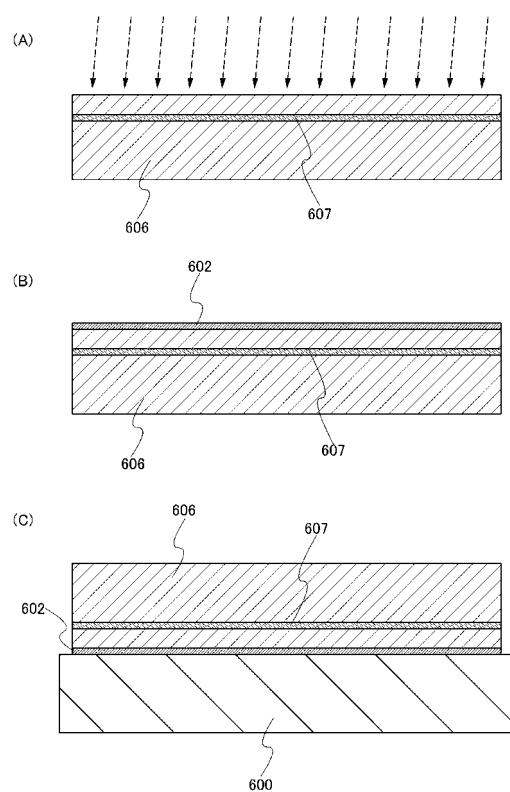

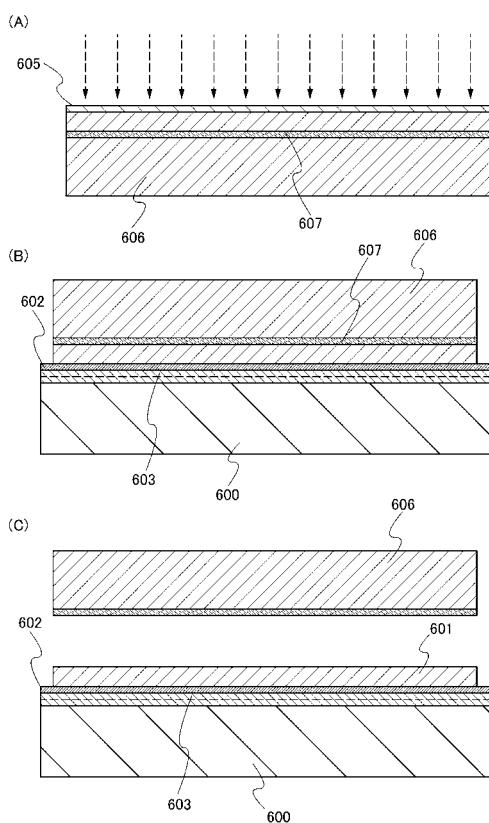

清浄化された半導体基板 606 の表面から電界で加速されたイオンを所定の深さに注入して分離層 607 を形成する (図 14 (A) 参照)。半導体基板 606 に形成される分離層 607 の深さは、イオンの加速電圧とイオンの入射角によって制御する。半導体基板 606 の表面からイオンの平均進入深さに近い深さ領域に分離層 607 が形成される。例えば、LTSS 層の厚さは 5 nm 乃至 500 nm、好ましくは 10 nm 乃至 200 nm の厚さであり、イオンを注入する際の加速電圧はこのような厚さを考慮して行われる。イオンの注入はイオンドーピング装置を用いて行うことが好ましい。すなわち、ソースガスをプラズマ化して生成された複数のイオン種を質量分離しないで注入するドーピング方式を用いる。50

## 【0069】

本実施の形態の場合、一または複数の同一の原子から成る質量の異なるイオンを注入することが好ましい。イオンドーピングは、加速電圧10kVから100kV、好ましくは30kVから80kV、ドーザ量は $1 \times 10^{16} / \text{cm}^2$ から $4 \times 10^{16} / \text{cm}^2$ 、ピーム電流密度が $2 \mu\text{A} / \text{cm}^2$ 以上、好ましくは $5 \mu\text{A} / \text{cm}^2$ 以上、より好ましくは $10 \mu\text{A} / \text{cm}^2$ 以上とすれば良い。

## 【0070】

水素イオンをドープあるいは注入する場合には、 $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$ イオンを含ませると共に、 $\text{H}_3^+$ イオンの割合を高めておくことが好ましい。水素イオンをドープあるいは注入する場合には、 $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$ イオンを含ませると共に、 $\text{H}_3^+$ イオンの割合を高めておくと注入効率を高めることができ、ドープ時間を短縮することができる。それにより、半導体基板606に形成される分離層607の領域には $1 \times 10^{20} / \text{cm}^3$ （好ましくは $5 \times 10^{20} / \text{cm}^3$ ）以上の水素を含ませることが可能である。10

## 【0071】

半導体基板606中において、局所的に高濃度の水素ドープ領域を形成すると、結晶構造が乱されて微小な空孔が形成される。分離層607を形成することができる。この場合、比較的低温の熱処理によって分離層607に含まれる水素ガスの圧力が上昇し、分離層607に沿って劈開することにより薄いLTSS層を形成することができる。

## 【0072】

イオンを質量分離して半導体基板606に注入しても、上記と同様に分離層607を形成することができる。この場合にも、質量の大きいイオン（例えば $\text{H}_3^+$ イオン）を選択的に注入することは上記と同様な効果を奏すこととなり好ましい。20

## 【0073】

イオンを生成するイオン種を生成するガスとしては水素の他に重水素、ヘリウムのような不活性ガスを選択することも可能である。原料ガスにヘリウムを用い、質量分離機能を有さないイオンドーピング装置を用いることにより、 $\text{He}^+$ イオンの割合が高いイオンビームが得ることができる。このようなイオンを半導体基板606に注入することで、微小な空孔を形成することができ上記と同様な分離層607を半導体基板606中に設けることができる。

## 【0074】

分離層607の形成に当たってはイオンを高ドーザ条件で注入する必要があり、半導体基板606の表面が粗くなってしまう場合がある。そのためイオンが注入される表面に緻密な膜を設けておいても良い。例えば、窒化シリコン膜もしくは酸素を含むは窒化シリコン膜などによりイオン注入に対する保護膜を50nm乃至200nmの厚さで設けておいても良い。30

## 【0075】

次に、支持基板600と接合を形成する面に接合層602として酸化シリコン膜を形成する（図14（B）参照）。酸化シリコン膜の厚さは10nm乃至200nm、好ましくは10nm乃至100nm、より好ましくは20nm乃至50nmとすれば良い。

## 【0076】

酸化シリコン膜としては上述のように有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板に形成した分離層607から脱ガスが起こらない温度として、例えば350℃以下の成膜温度が適用される。また、単結晶もしくは多結晶半導体基板からLTSS層を剥離する熱処理は、成膜温度よりも高い熱処理温度が適用される。40

## 【0077】

支持基板600と、半導体基板606の接合層602が形成された面を対向させ、密接させることで接合を形成する（図14（C）参照）。接合を形成する面は十分に清浄化しておく。そして、支持基板600と接合層602を密接させることにより接合が形成され50

る。接合は初期の段階においてファンデルワールス力が作用するものと考えられ、支持基板 600 と半導体基板 606 とを圧接することで水素結合により強固な接合を形成することが可能である。

【0078】

良好な接合を形成するために、表面を活性化しておいても良い。例えば、接合を形成する面に原子ビームもしくはイオンビームを照射する。原子ビームもしくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビームもしくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射もしくはラジカル処理を行う。このような表面処理により 200 乃至 400 の温度であっても異種材料間の接合強度を高めることが可能となる。

10

【0079】

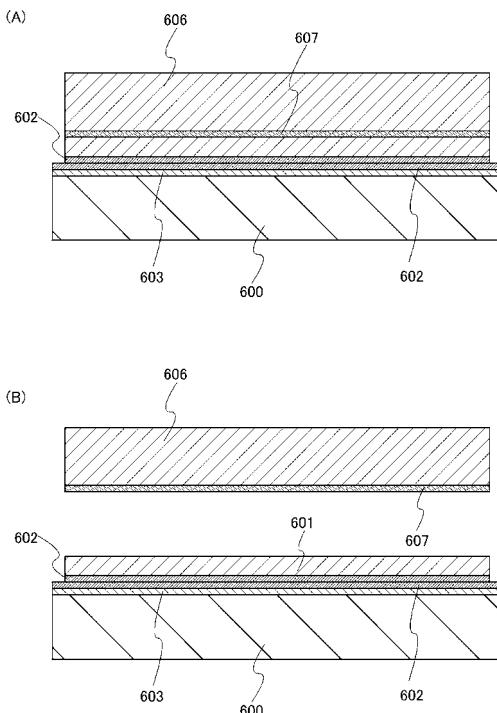

半導体基板 606 と支持基板 600 を重ね合わせた状態で第 1 の熱処理を行う。第 1 の熱処理により支持基板 600 上に薄い半導体層 (LTSS 層) を残して半導体基板 606 を分離を行う (図 15 (A) 参照)。第 1 の熱処理は接合層 602 の成膜温度以上で行うことが好ましく、400 以上 700 未満の温度で行うことが好ましい。この温度範囲で熱処理を行うことで分離層 607 に含まれる水素ガスの圧力が上昇し、分離層 607 に沿って半導体層を劈開することができる。接合層 602 は支持基板 600 と接合しているので、支持基板 600 上には半導体基板 606 と同じ結晶性の LTSS 層 601 が固定された形態となる。

【0080】

20

また第 1 の熱処理の前に、400 未満の熱活性を行い接合を強化してもよい。具体的には、200 で 1 分 ~ 120 分で加熱処理する。

【0081】

次に支持基板 600 に LTSS 層 601 が接合された状態で第 2 の熱処理を行う (図 15 (B) 参照)。第 2 の熱処理は、第 1 の熱処理温度よりも高い温度であって支持基板 600 の歪み点を超えない温度で行うことが好ましい。或いは、第 1 の熱処理と第 2 の熱処理は同じ温度であっても、第 2 の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱または輻射加熱などにより支持基板 600 及び / または LTSS 層 601 が加熱されるようにすれば良い。熱処理装置としては電熱炉、ランプアニール炉などを適用することができる。第 2 の熱処理は多段階に温度を変化させて行っても良い。また瞬間熱アニール (RTA) 装置を用いても良い。RTA 装置によって熱処理を行う場合には、基板の歪み点近傍またはそれよりも若干高い温度に加熱することもできる。

30

【0082】

第 2 の熱処理は、イオンをドープすることによって結晶性が損なわれた LTSS 層 601 の結晶性を回復させるために有効である。さらに、第 2 の熱処理は、半導体基板 606 を支持基板 600 と接合させ他後、第 1 の熱処理によって分割する際に生じる LTSS 層 601 のダメージを回復させることにも有効である。また、第 1 の熱処理と第 2 の熱処理を行うことで水素結合を、より強固な共有結合に変化させることができる。

【0083】

40

その後、さらにレーザ光を照射するのが望ましい。レーザ光の照射により、LTSS 層 601 の少なくとも一部が溶融し、再結晶化することになり、結晶欠陥が修復される。

【0084】

LTSS 層 601 の表面をより平坦化する目的で化学的機械研磨 (CMP) 処理を行っても良い。CMP 処理は第 1 の熱処理後もしくは第 2 の熱処理後に行うことができる。尤も、第 2 の熱処理前に行えば、LTSS 層 601 の表面を平坦化すると共に CMP 処理によって生じる表面の損傷層を第 2 の熱処理で修復することができる。

【0085】

いずれにしても、第 1 の熱処理と第 2 の熱処理を本形態のように組み合わせて行うことで、ガラス基板のような熱的に脆弱な支持基板の上に、結晶性に優れた結晶半導体層を設けることが可能となる。

50

## 【0086】

図14(A)～図14(C)及び図15(A)～図15(B)の工程を経て、図12(A)に示すSOI基板が形成される。

## 【0087】

図12(B)に示すSOI構造の基板を作成する方法について、図18(A)～図18(B)を用いて説明する。

## 【0088】

図14(A)～図14(B)に示す作製工程に基づいて、半導体基板606中に分離層607を形成し、さらに、半導体基板606の、支持基板600と接合を形成する面に、接合層602を形成する。

10

## 【0089】

次いで、バリア層603及び接合層602が形成された支持基板600と、半導体基板606の接合層602を密着させて接合を形成する(図18(A)参照)。

## 【0090】

この状態で第1の熱処理を行う。第1の熱処理は接合層602の成膜温度以上で行うことが好ましく、400以上700未満の温度で行うことが好ましい。それにより分離層607に含まれる水素ガスの圧力が上昇し、半導体基板606を劈開することができる。支持基板600上には半導体基板606と同じ結晶性を有するLTSS層601が形成される(図18(B)参照)。

## 【0091】

また第1の熱処理の前に、400未満の熱活性を行い接合を強化してもよい。具体的には、200で1分～120分で加熱処理する。

20

## 【0092】

次に支持基板600にLTSS層601が接合された状態で第2の熱処理を行う。第2の熱処理は、第1の熱処理温度よりも高い温度であって支持基板600の歪み点を超えない温度で行うことが好ましい。或いは、第1の熱処理と第2の熱処理は同じ温度であっても、第2の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱または輻射加熱などにより支持基板600及び/またはLTSS層601が加熱されるようすれば良い。第2の熱処理を行うことでLTSS層601に残留する応力を緩和することができ、第1の熱処理によって分割する際に生じるLTSS層601のダメージを回復させることにも有効である。

30

## 【0093】

その後、さらにレーザ光を照射するのが望ましい。レーザ光の照射により、LTSS層601の少なくとも一部が溶融し、再結晶化することになり、結晶欠陥が修復される。

## 【0094】

以上のようにして、図12(B)に示すSOI基板が形成される。

## 【0095】

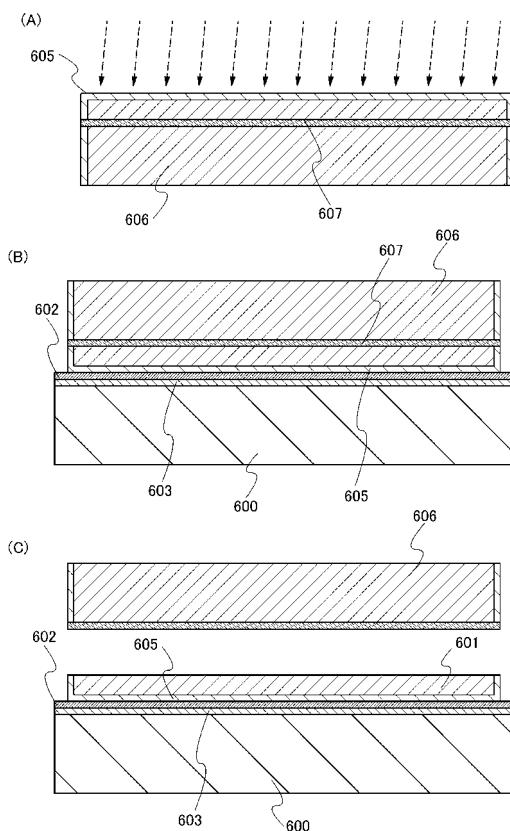

次いで図13(A)に示すSOI構造の基板の作製方法について、図19(A)～図19(C)を用いて説明する。

## 【0096】

まず図14(A)に示す作製工程に基づいて、半導体基板606中に分離層607を形成する。

40

## 【0097】

次に、半導体基板606の表面に絶縁層604を形成する。絶縁層604は窒素を含有する絶縁層であることが好ましい。例えば、窒化シリコン膜、酸素を含む窒化シリコン膜もしくは窒素を含む酸化シリコン膜から選ばれた1つまたは複数の膜を積層して形成することができる。

## 【0098】

さらに、絶縁層604上に接合層602として酸化シリコン膜を形成する(図19(A)参照)。

50

## 【0099】

支持基板 600 と、半導体基板 606 の接合層 602 が形成された面を対向させ、密接させることで接合を形成する（図 19（B）参照）。

## 【0100】

この状態で第 1 の熱処理を行う。第 1 の熱処理は接合層 602 の成膜温度以上で行うことが好ましく、400 以上 700 未満の温度で行うことが好ましい。それにより分離層 607 に含まれる水素ガスの圧力が上昇し、半導体基板 606 を劈開することができる。支持基板 600 上には半導体基板 606 と同じ結晶性を有する L T S S 層 601 が形成される（図 19（C）参照）。

## 【0101】

また第 1 の熱処理の前に、400 未満の熱活性を行い接合を強化してもよい。具体的には、200 で 1 分～120 分で加熱処理する。

## 【0102】

次に支持基板 600 に L T S S 層 601 が接合された状態で第 2 の熱処理を行う。第 2 の熱処理は、第 1 の熱処理温度よりも高い温度であって支持基板 600 の歪み点を超えない温度で行うことが好ましい。或いは、第 1 の熱処理と第 2 の熱処理は同じ温度であっても、第 2 の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱または輻射加熱などにより支持基板 600 及び / または L T S S 層 601 が加熱されるようすれば良い。第 2 の熱処理を行うことで L T S S 層 601 に残留する応力を緩和することができ、第 1 の熱処理によって分割する際に生じる L T S S 層 601 のダメージを回復させることにも有効である。

## 【0103】

その後、さらにレーザ光を照射するのが望ましい。レーザ光の照射により、L T S S 層 601 の少なくとも一部が溶融し、再結晶化することになり、結晶欠陥が修復される。

## 【0104】

図 19（A）～図 19（C）に示すように、絶縁層 604 を半導体基板 606 上に形成すると、絶縁層 604 によって不純物が L T S S 層 601 に混入するのを防ぐので、L T S S 層 601 が汚染されるのを防止することが可能となる。

## 【0105】

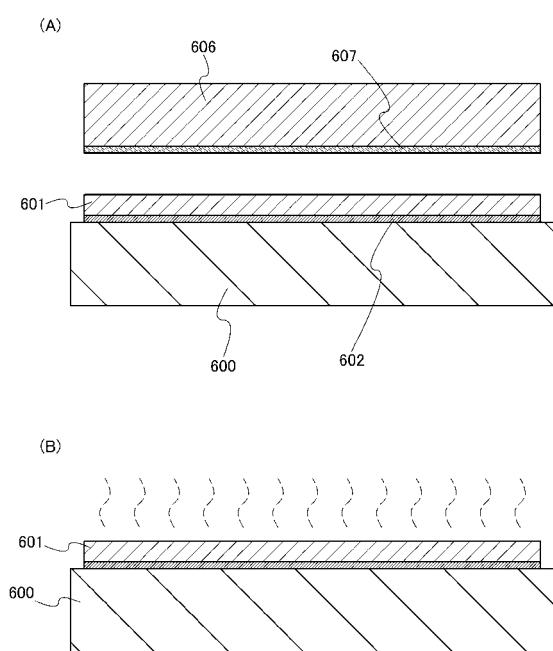

図 16（A）～図 16（C）は、支持基板側に接合層を設けて L T S S 層を有する S O I 構造の基板を製造する工程を示す。

## 【0106】

まず、酸化シリコン層 605 が形成された半導体基板 606 に電界で加速されたイオンを所定の深さに注入し、分離層 607 を形成する（図 16（A）参照）。酸化シリコン層 605 は、半導体基板 606 上に酸化シリコン層をスパッタ法や C V D 法で成膜してもよいし、半導体基板 606 が単結晶シリコン基板の場合、半導体基板 606 を熱酸化して形成してもよい。本実施の形態では、半導体基板 606 が単結晶シリコン基板として、酸化シリコン層 605 は単結晶シリコン基板を熱酸化して形成する。

## 【0107】

半導体基板 606 へのイオンの注入は図 14（A）の場合と同様である。半導体基板 606 の表面に酸化シリコン層 605 を形成しておくことでイオン注入によって表面がダメージを受け、平坦性が損なわれるのを防ぐことができる。

## 【0108】

バリア層 603 及び接合層 602 が形成された支持基板 600 と半導体基板 606 の酸化シリコン層 605 が形成された面を密着させて接合を形成する（図 16（B）参照）。

## 【0109】

この状態で第 1 の熱処理を行う。第 1 の熱処理は接合層 602 の成膜温度以上で行うことが好ましく、400 以上 700 未満の温度で行うことが好ましい。それにより分離層 607 に含まれる水素ガスの圧力が上昇し、半導体基板 606 を劈開することができる。支持基板 600 上には半導体基板 606 と同じ結晶性を有する L T S S 層 601 が形成

10

20

30

40

50

される（図16（C）参照）。

【0110】

また第1の熱処理の前に、400℃未満の熱活性を行い接合を強化してもよい。具体的には、200℃で1分～120分で加熱処理する。

【0111】

次に支持基板600にLTSS層601が接合された状態で第2の熱処理を行う。第2の熱処理は、第1の熱処理温度よりも高い温度であって支持基板600の歪み点を超えない温度で行なうことが好ましい。或いは、第1の熱処理と第2の熱処理は同じ温度であっても、第2の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱または輻射加熱などにより支持基板600及び／またはLTSS層601が加熱されるようにすれば良い。第2の熱処理を行うことでLTSS層601に残留する応力を緩和することができ、第1の熱処理によって分割する際に生じるLTSS層601のダメージを回復させることにも有効である。10

【0112】

その後、さらにレーザ光を照射するのが望ましい。レーザ光の照射により、LTSS層601の少なくとも一部が溶融し、再結晶化することになり、結晶欠陥が修復される。

【0113】

以上のようにして、図13（B）に示すSOI基板が形成される。

【0114】

図17（A）～図17（C）は支持基板側に接合層を設けてLTSS層を接合する場合における他の例を示す。20

【0115】

最初に半導体基板606に分離層607を形成する（図17（A）参照）。分離層607を形成するためのイオンの注入はイオンドーピング装置を用いて行う。この工程では電界で加速された質量の異なるイオンが高電界で加速されて半導体基板606に照射される。

【0116】

このとき、半導体基板606の表面はイオンの照射により平坦性が損なわれるおそれがあるので、保護膜として酸化シリコン層605を設けておくことが好ましい。酸化シリコン層605は熱酸化により形成しても良いし、ケミカルオキサイドを適用しても良い。ケミカルオキサイドは酸化性の薬液に半導体基板606を浸することで形成可能である。例えば、オゾン含有水溶液で半導体基板606を処理すれば表面にケミカルオキサイドが形成される。30

【0117】

また保護膜として、プラズマCVD法で形成した窒素を含む酸化シリコン膜、酸素を含む窒化シリコン膜、またはTEOSを用いて成膜した酸化シリコン膜を用いてもよい。

【0118】

支持基板600にはバリア層603を設けることが好ましい。バリア層603を設けることで、支持基板600として用いられるガラス基板からアルカリ金属もしくはアルカリ土類金属のような可動イオン不純物が拡散してLTSS層601が汚染されることを防ぐことができる。40

【0119】

バリア層603は一層または複数の層をもって構成する。例えば、ナトリウムなどのイオンをブロッキングする効果の高い窒化シリコン膜または酸素を含む窒化シリコン膜を第1層目として用い、その上層に第2層目として酸化シリコン膜または窒素を含む酸化シリコン膜を設ける。

【0120】

バリア層603の第1層目は不純物の拡散を防止する目的を持った絶縁膜であり緻密な膜であるのに対し、第2層目は第1層目の膜の内部応力が上層に作用しないように、応力を緩和することを一つの目的としている。このように支持基板600にバリア層603を

50

設けることで、LTSS層を接合する際の基板の選択範囲を広げることができる。

【0121】

バリア層603の上層に接合層602を設けた支持基板600と半導体基板606を接合させる(図17(B)参照)。半導体基板606の表面は保護膜として設けた酸化シリコン層605をフッ酸で除去しておき、半導体表面が露出する状態となっている。半導体基板606の最表面はフッ酸溶液の処理により水素で終端されている状態であれば良い。接合形成に際して表面終端水素により水素結合が形成され、良好な接合を形成することができる。

【0122】

また、不活性ガスのイオンを照射して半導体基板606の最表面に未結合手が露出する10ようにして、真空中で接合を形成しても良い。

【0123】

この状態で第1の熱処理を行う。第1の熱処理は接合層602の成膜温度以上で行うことが好ましく、400以上700未満の温度で行うことが好ましい。それにより分離層607に含まれる水素ガスの圧力が上昇し、半導体基板606を劈開することができる。支持基板600上には半導体基板606と同じ結晶性を有するLTSS層601が形成される(図17(C)参照)。

【0124】

また第1の熱処理の前に、400未満の熱活性を行い接合を強化してもよい。具体的には、200で1分～120分で加熱処理する。20

【0125】

次に支持基板600にLTSS層601が接合された状態で第2の熱処理を行う。第2の熱処理は、第1の熱処理温度よりも高い温度であって支持基板600の歪み点を超えない温度で行うことが好ましい。或いは、第1の熱処理と第2の熱処理は同じ温度であっても、第2の熱処理の処理時間を長くすることが好ましい。

【0126】

熱処理は、熱伝導加熱、対流加熱または輻射加熱などにより支持基板600及び/またはLTSS層601が加熱されるようにすれば良い。第2の熱処理を行うことでLTSS層601に残留する応力を緩和することができ、第1の熱処理によって分割する際に生じるLTSS層601のダメージを回復させることにも有効である。30

【0127】

その後、さらにレーザ光を照射するのが望ましい。レーザ光の照射により、LTSS層601の少なくとも一部が溶融し、再結晶化することになり、結晶欠陥が修復される。

【0128】

以上のようにして図13(C)に示すSOI基板を形成する。

【0129】

次いで結晶性半導体膜104あるいはLTSS層601をマスクを用いてエッチングし、島状半導体膜105を形成する(図1(C)参照)。

【0130】

島状半導体膜105をオゾン水または過酸化水素水で処理する、あるいは島状半導体膜105をUVオゾン法で酸化して、島状半導体膜105の表面に島状半導体膜の酸化膜107を形成する。この酸化膜107の膜厚はごく薄く、0.2nm～4nm、好ましくは、0.5nm～3nmである。40

【0131】

また島状半導体膜105を窒化することにより、酸化膜107の代わりに窒化膜を形成することも可能である。

【0132】

また酸化膜107あるいは窒化膜の形成前に、島状半導体膜105表面の自然酸化膜を希フッ酸で除去してもよい。

【0133】

島状半導体膜105の窒化工程として、例えばプラズマ窒化処理が挙げられる。プラズマ窒化処理とは、高真空状態の反応室にアンモニアガス、窒素ガス、または一酸化二窒素ガス( $N_2O$ )を導入し、高周波電力を印加することによってプラズマを発生させる処理である。島状半導体膜105にプラズマ窒化処理を行うと、島状半導体膜105の表面上に、ごく薄い窒化膜が形成される。さらにプラズマ窒化処理を行う反応室に酸素ガスを混合してもよい。

【0134】

あるいは、上記の工程により酸化膜107を形成した後に、窒化処理を行うことによって酸化膜の表面を窒化させ、酸化膜107の代わりに酸素を含む窒化膜を形成しても良い。サブオキサイドあるいはサブナイトライドは、10%～40%、好ましくは30%～40%含まれる。

10

【0135】

本明細書において、サブオキサイドとは、X線光電子分光(X-ray Photoelectron Spectroscopy: XPS)、あるいは、ESCA(El ectron Spectroscopy for Chemical Analysis)とも言われる)での測定結果により、便宜上、 $Si_2O$ 、 $SiO$ 、 $Si_2O_3$ で表されるものをいい、また便宜上、珪素の電荷はそれぞれ、 $Si^{1+}$ 、 $Si^{2+}$ 、 $Si^{3+}$ となる。なお $SiO_2$ 成分では $Si^{4+}$ となる。

【0136】

サブオキサイドが10%～40%というのは、便宜上 $Si_2O$ 、 $SiO$ 、 $Si_2O_3$ で表される珪素の酸化物及び $SiO_2$ で表される珪素の酸化物全体のうち、 $Si_2O$ 、 $SiO$ 、 $Si_2O_3$ で表される珪素の酸化物が、珪素の酸化物全体の10%～40%であるということである。

20

【0137】

なおサブナイトライドについては、サブオキサイドの酸素が窒素に置き換わっただけで、上記の考え方と同様である。

【0138】

酸化膜107の代わりに窒化膜、あるいは酸素を含む窒化膜を形成する場合でも、それぞれの膜厚は、0.2nm～4nm、好ましくは、0.5nm～3nmである。

【0139】

30

また、島状半導体膜105を酸化あるいは窒化せずに、半導体膜のごく薄い酸化膜、あるいは、半導体膜のごく薄い窒化膜を、CVD法等で、島状半導体膜105の表面上に形成してもよい。その場合にでも、それぞれの膜厚は、0.2nm～4nm、好ましくは、0.5nm～3nmがよい。サブオキサイドあるいはサブナイトライドは、10%～40%、好ましくは30%～40%含まれる。

【0140】

例えば、モノシラン( $SiH_4$ )と一酸化二窒素( $N_2O$ )の混合ガスを用いて、プラズマCVD法により、島状半導体膜105の表面上に酸素と含む窒化珪素膜または窒素を含む酸化珪素膜をごく薄い厚さで成膜することができる。

40

【0141】

島状半導体膜105をオゾン水または過酸化水素水で処理する、あるいは島状半導体膜105をUVオゾン法で酸化して、島状半導体膜105の表面上に形成された酸化膜107、及び、酸化膜107の代わりに形成可能である以下の膜、すなわち、島状半導体膜105にプラズマ窒化処理を行うことにより、島状半導体膜105の表面上に形成されるごく薄い窒化膜、酸化膜107を形成しさらに窒化処理を行うことで形成される酸素を含む窒化膜、島状半導体膜105の表面上にCVD法等で形成するごく薄い酸化膜、あるいは、ごく薄い窒化膜を、本明細書では、「第1の絶縁膜」と呼ぶことにする。サブオキサイドあるいはサブナイトライドは、10%～40%、好ましくは30%～40%含まれる。

【0142】

また第1の絶縁膜形成前に、希フッ酸で島状半導体膜105表面の自然酸化膜を除去し

50

てもよい。

【0143】

酸化膜107を形成後、島状半導体膜105及び酸化膜107上に、半導体膜108を膜厚10~50nmの厚さで成膜する(図1(D)参照)。

【0144】

半導体膜108は、非晶質半導体膜、結晶性半導体膜、微結晶性半導体膜(「セミアモルファス半導体膜」ともいう)のいずれかであればよい。

【0145】

なおセミアモルファス半導体(本明細書では「*Semi-amorphous Semiconductor (SAS)*」ともいう)膜とは、非晶質半導体と結晶構造を有する半導体(単結晶、多結晶を含む)膜の中間的な構造の半導体を含む膜である。このセミアモルファス半導体膜は、自由エネルギー的に安定な第3の状態を有する半導体膜であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5~20nmとして非単結晶半導体膜中に分散させて存在せしめることが可能である。なお微結晶半導体膜(マイクロクリスタル半導体膜)もセミアモルファス半導体膜に含まれる。

【0146】

セミアモルファス半導体膜の1つの例として、セミアモルファス珪素膜が挙げられる。セミアモルファス珪素膜は、そのラマンスペクトルが $520\text{ cm}^{-1}$ よりも低波数側にシフトしており、またX線回折ではSi結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。また、未結合手(ダンギングボンド)を終端化するために水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。本明細書では便宜上、このような珪素膜をセミアモルファス珪素膜と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体膜が得られる。

【0147】

またセミアモルファス珪素膜は珪素(シリコン)を含む気体をグロー放電分解することにより得ることができる。代表的な珪素(シリコン)を含む気体としては、 $\text{SiH}_4$ であり、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素(シリコン)を含む気体を希釈して用いることで、セミアモルファス珪素膜の形成を容易なものとすることができます。希釈率は2倍~1000倍の範囲で珪素(シリコン)を含む気体を希釈することが好ましい。またさらに、珪素(シリコン)を含む気体中に、 $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$ などの炭化物気体、 $\text{GeH}_4$ 、 $\text{GeF}_4$ などのゲルマニウム化気体、 $\text{F}_2$ などを混入させて、エネルギー bandwidth幅を1.5~2.4eV、若しくは0.9~1.1eVに調節しても良い。

【0148】

本実施の形態では、半導体膜108として珪素を主成分とする半導体膜、例えば非晶質珪素膜を用いる。またゲルマニウムを主成分とする半導体膜を用いてもよい。珪素あるいはゲルマニウムを主成分とする半導体膜には、珪素膜、ゲルマニウム膜、シリコンゲルマニウム膜が含まれる。

【0149】

また本実施の形態では、半導体膜108として、一導電性を付与する不純物元素を添加されていない非晶質珪素膜、いわゆる真性非晶質珪素膜、あるいは*i*型非晶質珪素膜を用いるが、これに限定されない。半導体膜108として、*n*型を付与する不純物元素、例えば、リン(P)やヒ素(As)を添加された半導体膜、いわゆる*n*型半導体膜を用いてもよいし、*p*型を付与する不純物元素、例えばホウ素(B)を添加された半導体膜、いわゆる*p*型半導体膜を用いてもよい。

【0150】

次いで、半導体膜108をエッティングして、島状半導体膜105の端部に近い領域上に半導体膜109(半導体膜109a及び半導体膜109b)を形成する(図1(E)参照)

10

20

30

40

50

)。半導体膜 108 をエッティングする際に、酸化膜 107 がエッティングストップとなり、島状半導体膜 105 がエッティングされてしまうのを防ぐ。もし酸化膜 107 が形成されないと、半導体膜 108 をエッティングする際に、島状半導体膜 105 までエッティングされてしまい、島状半導体膜 105 がえぐれてしまう恐れがある。なお半導体膜 108 のエッティングはドライエッティングでもよいし、ウェットエッティングでもよい。

#### 【0151】

本実施の形態では、アルカリ性溶液を用いウェットエッティングにて、半導体膜 108 をエッティングする。アルカリ性溶液として、テトラメチルアンモニウムハイドロオキサイド (TMAH) や水酸化カリウムを用い、50 ~ 70 に熱してウェットエッティングに用いる。

10

#### 【0152】

次いで島状半導体膜 105 を酸化して、新たに酸化膜を得る。本明細書では「第 2 の絶縁膜」と呼ぶ。第 2 の絶縁膜と酸化膜 107 (第 1 の絶縁膜) とを合わせて、ゲート絶縁膜 115 とする。なお島状半導体膜 105 を酸化する前に、酸化膜 107 (第 1 の絶縁膜) を除去しておいてもよい。その場合は、島状半導体膜 105 を新たに酸化して得られた酸化膜 (第 2 の絶縁膜) をゲート絶縁膜とする (後述及び図 23 (A) ~ 図 23 (E) 参照)。なお、実際には半導体膜 109 上にも酸化膜ができる可能性があるが、図 1 (F) ~ 図 1 (H) では省略している。

#### 【0153】

次いで、島状半導体膜 105 及び酸化膜 107 上で、半導体膜 109 が形成されていない領域に、ゲート電極 111 を形成する (図 1 (F) 参照)。

20

#### 【0154】

ゲート電極 111 は、クロム (Cr)、タンタル (Ta)、タンゲステン (W)、チタン (Ti)、アルミニウム (Al)、窒化タンタル等のいずれか 1 つ、あるいは 2 つ以上を積層した積層膜を用いて形成することができる。

#### 【0155】

次いでゲート電極 111 をマスクとして、半導体膜 109 に一導電性を付与する不純物元素を添加する。n 型を付与する不純物元素としては、例えばリン (P) やヒ素 (As) を用いてもよい。また p 型を付与する不純物元素としては、例えばホウ素 (B) を用いてもよい。

30

#### 【0156】

一導電性を付与する不純物元素は、イオンドーピング法やイオン注入法で添加され、加速電圧 (印加電圧ともいう) は、5 ~ 80 kV で行う。この添加工程の際に、半導体膜のごく薄い酸化膜 107、本実施の形態ではごく薄い酸化珪素膜中の構成元素である酸素や珪素等にイオンが衝突して、酸素や珪素が散乱あるいは跳躍するイオンミキシングが生じる。一導電性を付与する不純物元素は、 $1 \times 10^{14} \sim 1 \times 10^{16}$  atoms/cm<sup>2</sup> の範囲で添加すればよく、異なる加速電圧で 2 回以上添加してもよい。

#### 【0157】

不純物元素添加工程により、島状半導体膜 105 中のゲート電極 111 の下の領域に、チャネル形成領域 118 が形成される。島状半導体膜 105 中の不純物元素が添加された領域及び半導体膜 109 は、不純物領域 114 (不純物領域 114a 及び不純物領域 114b) となる。不純物領域 114 中のごく薄い酸化膜 107 はイオンミキシングされた酸化膜 116 (酸化膜 116a 及び酸化膜 116b) となる (図 1 (G) 参照)。

40

#### 【0158】

その後、レーザ活性化や、RTA (Rapid Thermal Anneal) や、炉を用いたファーネスアニール等を用いて、添加された不純物元素の活性化を行う。特に、レーザ活性化や RTA によって、島状半導体膜 105 と半導体膜 109 が 700 以上、特に 1000 以上になると、酸素の拡散が進み、イオンミキシングされた酸化膜 116 の少なくとも一部は消失する。またレーザ活性化時に酸化膜 116 及びその周辺の半導体膜が溶融すれば、酸化膜 116 は消失しやすくなる。同時に、島状半導体膜 105 の結

50

晶状態を反映した、半導体膜 109 の結晶成長、エピタキシャル成長が進行する。これにより半導体膜 109 が n 型あるいは p 型に低抵抗化され、n 型あるいは p 型の結晶性半導体膜となる。またレーザ活性化や R T A は、短時間の処理なのでガラス基板が溶融せず、また大きく変形させないという利点がある。

【0159】

以上により、チャネル形成領域 118 と、ソース領域またはドレイン領域の一方である領域 119a と、ソース領域またはドレイン領域の他方である領域 119b が形成される(図 1 (H) 参照)。

【0160】

なお上述のように、島状半導体膜 105 を酸化する前に、酸化膜 107 (第 1 の絶縁膜) を除去し、島状半導体膜 105 を新たに酸化して得られた酸化膜 (第 2 の絶縁膜) をゲート絶縁膜とする場合を、図 23 (A) ~ 図 23 (E) を用いて説明する。なお図 1 (A) ~ 図 1 (H) と同じものは同じ符号で表されている。

【0161】

まず図 1 (A) ~ 図 1 (E) の作製工程を経て、図 23 (A) に示す構造を得る。なお図 23 (A) は、図 1 (E) と同じ構造を示している。

【0162】

次いで、酸化膜 107 の島状半導体膜 105 と半導体膜 109 に挟まれている領域以外の領域、すなわち酸化膜 107 中の露出している領域を除去し、島状半導体膜 105 の半導体膜 109 (109a 及び 109b) が形成されていない領域を露出させる(図 23 (B) 参照)。

【0163】

次いで、島状半導体膜 105 を酸化あるいは窒化して、新たに酸化膜、窒素を含む酸化膜、酸素を含む窒化膜、あるいは、窒化膜を得る。本実施の形態では酸化膜 165 を得る。なお実際には半導体膜 109 上にも酸化膜ができると可能性があるが、図 23 (C) ~ 図 23 (E) では省略している。酸化膜 165 は、ゲート絶縁膜として機能する。ゲート絶縁膜たる酸化膜 165 上に、ゲート電極 111 を形成する(図 23 (C) 参照)。

【0164】

あとは図 1 (G) ~ 図 1 (H) の作製工程に基づいて、不純物添加工程、加熱工程等を行う(図 23 (D) ~ 図 23 (E) 参照)。

【0165】

また図 1 (H) のゲート絶縁膜 115 上に第 2 のゲート絶縁膜 166 を形成してもよい。図 10 (A) ~ 図 10 (D) に第 2 のゲート絶縁膜 166 した場合の作製工程を示す。

【0166】

まず図 1 (E) の半導体膜 109 (109a 及び 109b) を形成するまでの工程を行った後、島状半導体膜 105 を酸化して、新たに酸化膜(本明細書では「第 2 の絶縁膜」ともいう)を形成する。第 1 の絶縁膜である酸化膜 107 と第 2 の絶縁膜を合わせて、酸化膜 117 とする(図 10 (A) 参照)。なお、実際には半導体膜 109 上にも酸化膜ができると可能性があるが、図 10 (A) ~ 図 10 (E) では省略する。

【0167】

次いで、絶縁膜 110 (本明細書では「第 3 の絶縁膜」ともいう)を、島状半導体膜 105、半導体膜 109a 及び 109b、酸化膜 117 を覆って形成する(図 10 (B) 参照)。

【0168】

次いで絶縁膜 110 上にゲート電極 111 を形成して、ゲート電極 111 をマスクとして、絶縁膜 110 をエッティングして、第 1 のゲート絶縁膜 115 上の第 2 のゲート絶縁膜 166 とする(図 10 (C) 参照)。

【0169】

第 2 のゲート絶縁膜 166 は、酸化珪素膜、窒素を含む酸化珪素膜、窒化珪素膜、酸素を含む窒化珪素膜のいずれか 1 つ、あるいは 2 つ以上の積層膜を用いて形成すればよい。

10

20

30

40

50

## 【0170】

その後図1 (G) ~ 図1 (H) の作製工程に基づいて、薄膜トランジスタを作製する (図10 (D) ~ 図10 (E) 参照)。

## 【0171】

また半導体膜109 (109a及び109b) を形成後、酸化膜107の島状半導体膜105と半導体膜109に挟まれている領域以外の領域、すなわち酸化膜107中の露出している領域を除去し、島状半導体膜105の半導体膜109 (109a及び109b) が形成されていない領域を露出させる。そして島状半導体膜105の露出した領域上に、新たにゲート絶縁膜151を形成してもよい。酸化膜107の露出している領域を除去し、島状半導体膜105の半導体膜109 (109a及び109b) が形成されていない領域を露出させ、ゲート絶縁膜151を形成する工程について、図11 (A) ~ 図11 (F) を用いて説明する。

10

## 【0172】

ただし上述の通り、酸化膜107の代わりに窒化膜や酸素を含む窒化膜を用いてもよい。

。

## 【0173】

まず図1 (A) ~ 図1 (E) に示す作製工程に基づいて、半導体膜109 (109a及び109b) を形成するまでの工程を行う (図11 (A) 参照)。次いで半導体膜109 (109a及び109b) をマスクとして、露出している酸化膜107 (あるいは窒化膜や酸素を含む窒化膜) を除去する。これにより酸化膜107は、島状半導体膜105と半導体膜109に挟まれた領域のみが残存する (図11 (B) 参照)。

20

## 【0174】

次いで島状半導体膜105の、酸化膜107が除去された領域上に、ゲート絶縁膜151を形成する (図11 (C) 参照)。ゲート絶縁膜151は、酸化珪素膜、窒素を含む酸化珪素膜、窒化珪素膜、酸素を含む窒化珪素膜のいずれか1つ、あるいは2つ以上の積層膜を用いて形成すればよい。

## 【0175】

次いでゲート絶縁膜151上にゲート電極111を形成する (図11 (D) 参照)。その後図1 (G) ~ 図1 (H) の作製工程に基づいて、薄膜トランジスタを作製する (図11 (E) ~ 図11 (F) 参照)。

30

## 【0176】

## [実施の形態2]

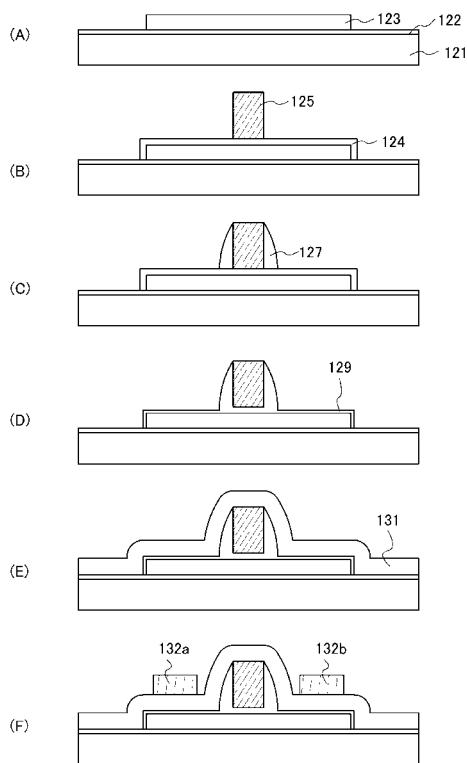

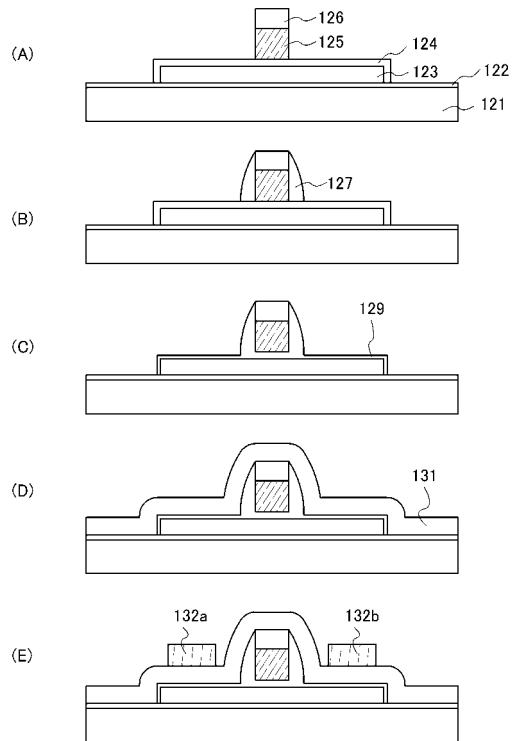

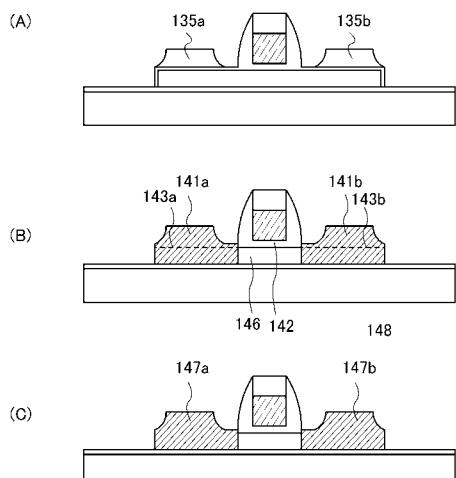

本実施の形態では、実施の形態1とは異なる構造を有する薄膜トランジスタの作製方法について、図3 (A) ~ 図3 (F)、図4 (A) ~ 図4 (C)、図8 (A) ~ 図8 (E)、図9 (A) ~ 図9 (C) を用いて説明する。

## 【0177】

実施の形態1に基づいて、図1 (C) に示す作製工程までを行う。図3 (A) は図1 (C) と同じであり、基板121、下地絶縁膜122、島状半導体膜123は、それぞれ基板101、下地絶縁膜102、島状半導体膜105に対応している。

## 【0178】

次いで、島状半導体膜123を覆って絶縁膜124を形成し、島状半導体膜123及び絶縁膜124上に、ゲート電極125を形成する。ゲート電極125はゲート電極111と同様にして形成すればよい (図3 (B) 参照)。

40

## 【0179】

なおゲート電極125を形成後、一導電型を付与する不純物元素を島状半導体膜123に導入してもよい。このときの不純物元素の濃度は、後述する不純物領域141 (不純物領域141a及び不純物領域141b) を形成するための不純物元素添加工程の際の、不純物濃度より低いものとする。

## 【0180】

次いで島状半導体膜123、絶縁膜124、ゲート電極125上に絶縁膜を形成し、異

50

方性エッティングを行って、ゲート電極 125 の側面にサイドウォール 127 を形成する（図 3（C）参照）。

【0181】

次いで、絶縁膜 124 の、ゲート電極 125 及びサイドウォール 127 が形成されていない領域をエッティングにより除去し、露出した島状半導体膜 123 をオゾン水または過酸化水素水で処理する、あるいは露出した島状半導体膜 123 をUVオゾン法で酸化して、島状半導体膜 123 の表面に島状半導体膜の酸化膜 129 を形成する（図 3（D）参照）。この酸化膜 129 の膜厚はごく薄く、0.5~3 nm である。

【0182】

酸化膜 129、サイドウォール 127、ゲート電極 125 を覆って、半導体膜 131 を成膜する（図 3（E）参照）。半導体膜 131 は、非晶質半導体膜、結晶性半導体膜、微結晶性半導体膜（「セミアモルファス半導体膜」ともいう）のいずれかであればよい。

【0183】

半導体膜 131 を成膜したら、半導体膜 131 上で、島状半導体膜 123 の端部に近い領域上に、レジストマスク 132（132a 及び 132b）を形成する（図 3（F）参照）。

【0184】

次いでレジストマスク 132 をマスクとして、半導体膜 131 をエッティングする。半導体膜 131 をエッティングする際に、酸化膜 129 がエッティングストップとなり、島状半導体膜 123 がエッティングされてしまうのを防ぐ。

【0185】

本実施の形態では、ウエットエッティングにより半導体膜 131 をエッティングする。

【0186】

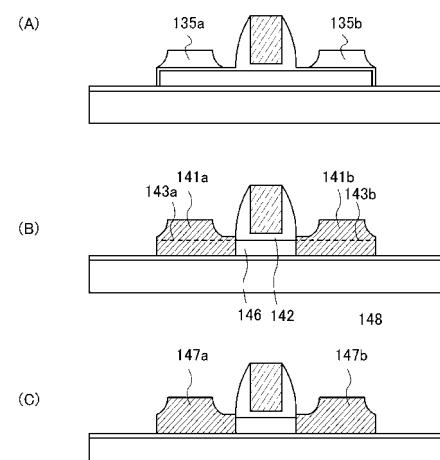

これにより島状半導体膜 123 の端部に近い領域上に半導体膜 135（135a 及び 135b）を形成する（図 4（A）参照）。

【0187】

また半導体膜 131 を成膜しエッティングして半導体膜 135 を形成する代わりに、ポリシランとシクロペンタシランを含む有機溶媒を塗布して、インクジェット法で、酸化膜 129 上に選択的に珪素膜を形成してもよい。

【0188】

あるいは半導体膜 131 を成膜する代わりにポリシランとシクロペンタシランを含む有機溶媒を塗布後に焼成してから、レジストマスク 132 を形成し、エッティングにより半導体膜 135 を形成してもよい。

【0189】

次いでゲート電極 125、サイドウォール 127 をマスクとして、半導体膜 135 に一導電性を付与する不純物元素を添加する。n型を付与する不純物元素としては、例えはリン（P）やヒ素（As）を用いてもよい。また p型を付与する不純物元素としては、例えはホウ素（B）を用いてもよい。

【0190】

一導電性を付与する不純物元素は、イオンドーピング法やイオン注入法で添加され、加速電圧（印加電圧ともいう）は、5~80 kV で行う。この添加工程の際に、ごく薄い酸化膜 129、本実施の形態ではごく薄い酸化珪素膜中の構成元素である酸素や珪素等にイオンが衝突して、酸素や珪素が散乱あるいは跳躍するイオンミキシングが生じる。一導電性を付与する不純物元素は、 $1 \times 10^{14} \sim 1 \times 10^{16}$  atoms/cm<sup>2</sup> の範囲で添加すればよく、異なる加速電圧で 2 回以上添加してもよい。

【0191】

不純物元素添加工程により、島状半導体膜 123 中のゲート電極 125、サイドウォール 127 の下の領域に、チャネル形成領域 146 が形成される。またチャネル形成領域 146 上にはゲート絶縁膜 142 が形成される。島状半導体膜 123 中の不純物元素が添加された領域と半導体膜 135 は、不純物領域 141（不純物領域 141a 及び不純物領域

10

20

20

30

40

50

141b)となる。不純物領域141中のごく薄い酸化膜129はイオンミキシングされた酸化膜143(半導体膜の酸化膜143a及び半導体膜の酸化膜143b)となる(図4(B)参照)。

【0192】

その後、レーザ活性化や、RTA(Rapid Thermal Anneal)や、炉を用いたファーネスアニール等を用いて、添加された不純物の活性化を行う。特に、レーザ活性化やRTAによって、島状半導体膜123と半導体膜135が700以上、特に1000以上になると、酸素の拡散が進み、イオンミキシングされた酸化膜143の少なくとも一部は消失する。またレーザ活性化時に酸化膜143及びその周辺の半導体膜が溶融すれば、酸化膜143は消失しやすくなる。同時に、島状半導体膜123の結晶状態を反映した、半導体膜135の結晶成長、エピタキシャル成長が進行する。これにより半導体膜135がn型あるいはp型に低抵抗化され、半導体膜135がn型あるいはp型の結晶性半導体膜となる。

10

【0193】

以上により、チャネル形成領域146と、ソース領域またはドレイン領域の一方である領域147aと、ソース領域またはドレイン領域の他方である領域147bが形成される(図4(C)参照)。

【0194】

また図3(B)に示すゲート電極125を形成後、ゲート電極125上に絶縁膜126を形成しても良い(図8(A)参照)。絶縁膜126は、酸化珪素膜、窒素を含む酸化珪素膜、窒化珪素膜、酸素を含む窒化珪素膜のいずれか1つ、あるいは2つ以上の積層膜を用いて形成すればよい。

20

【0195】

その後、図3(C)～図3(F)及び図4(A)～図4(C)に示す工程と同じ工程を経て薄膜トランジスタが作製される(図8(B)～図8(E)及び図9(A)～図9(C)参照)。

【0196】

[実施の形態3]

本実施の形態では、無線交信可能な半導体装置において、実施の形態1～実施の形態2のTFTを用いた場合について、図5、図6(A)～図6(B)を用いて説明する。

30

【0197】

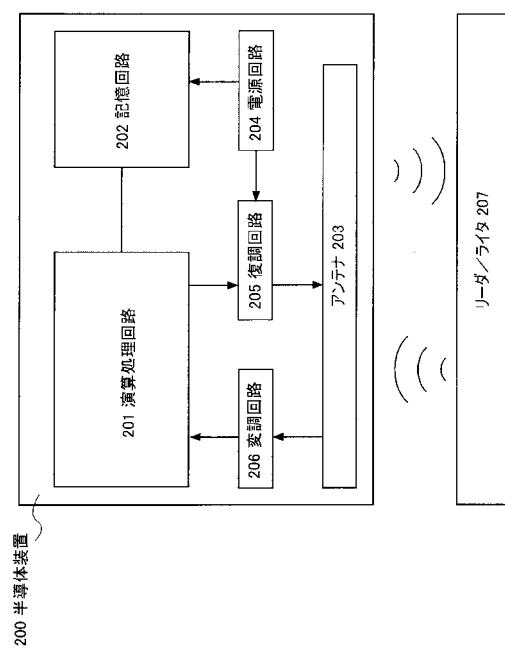

図5に示すように、本実施の形態の無線交信可能な半導体装置200は、演算処理回路201、記憶回路202、アンテナ203、電源回路204、復調回路205、変調回路206を有する。無線交信可能な半導体装置200は、アンテナ203と電源回路204を必須の構成要素としており、他の要素は、無線交信可能な半導体装置200の用途に従って、適宜設けられる。

【0198】

実施の形態1～実施の形態2に基づいて作製されたTFTは、演算処理回路201、記憶回路202、電源回路204、復調回路205、変調回路206に適用可能である。

【0199】

40

演算処理回路201は、復調回路205から入力される信号に基づき、命令の解析、記憶回路202の制御、外部に送信するデータの変調回路206への出力などを行う。

【0200】

記憶回路202は、記憶素子を含む回路と、データの書き込みやデータの読み出しを行う制御回路を有する。記憶回路202には、少なくとも、半導体装置自体の個体識別番号が記憶されている。個体識別番号は、他の半導体装置と区別するために用いられる。また、記憶回路202は、実施の形態1または実施の形態2で述べたTFTを用いて形成すればよい。

【0201】

アンテナ203は、リーダ/ライタ207から供給された搬送波を、交流の電気信号に

50

変換する。また、変調回路 206 により、負荷変調が加えられる。電源回路 204 は、アンテナ 203 が変換した交流の電気信号を用いて電源電圧を生成し、各回路に電源電圧を供給する。

【0202】

復調回路 205 は、アンテナ 203 が変換した交流の電気信号を復調し、復調した信号を、演算処理回路 201 に供給する。変調回路 206 は、演算処理回路 201 から供給される信号に基づき、アンテナ 203 に負荷変調を加える。

【0203】

リーダ／ライタ 207 は、アンテナ 203 に加えられた負荷変調を、搬送波として受信する。また、リーダ／ライタ 207 は、搬送波を無線交信可能な半導体装置 200 に送信する。なお、搬送波とは、リーダ／ライタ 207 が送受信する電磁波であり、リーダ／ライタ 207 は変調回路 206 により変調された搬送波を受信する。

【0204】

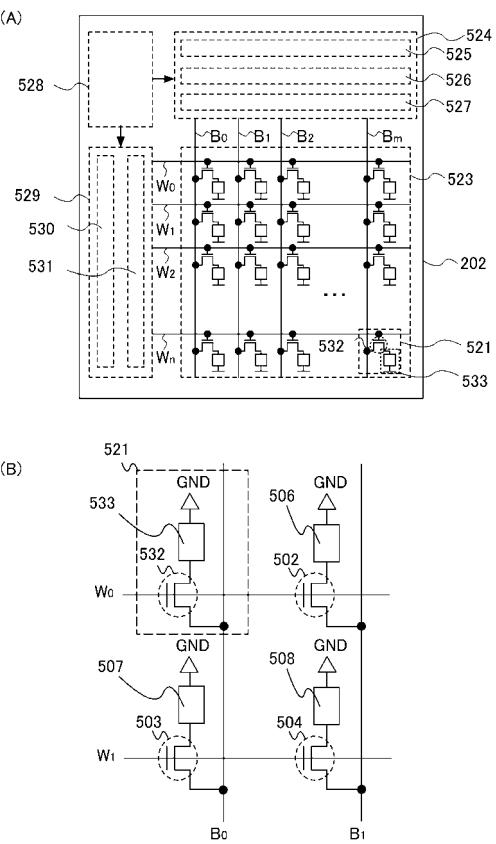

図 6 (A) に示すのは記憶素子をマトリクス状に配置した記憶回路 202 の構成の一例である。記憶回路 202 上にメモリセル 521 がマトリクス状に設けられたメモリセルアレイ 523、カラムデコーダ 525 と読み出し回路 526 とセレクタ 527 を有するビット線駆動回路 524、ロウデコーダ 530 とレベルシフタ 531 を有するワード線駆動回路 529、書き込み回路等を有し外部とのやりとりを行うインターフェース 528 を有している。なお、ここで示す記憶回路 202 の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の他の回路を有していてもよいし、書き込み回路をビット線駆動回路に設けてもよい。

【0205】

メモリセル 521 は、ワード線  $W_y$  ( $0 \leq y \leq n$ ) を構成する第 1 の配線と、ビット線  $B_x$  ( $0 \leq x \leq m$ ) を構成する第 2 の配線と、TFT 532 と、記憶素子 533 とを有する。

【0206】

次に、本発明のメモリセルへの書き込み及び読み込み動作について、図 6 (B) を参照しながら説明する。なお、ここではメモリセルに「0」が書き込まれた状態を第 2 の状態、「1」が書き込まれた状態を第 1 の状態とする。

【0207】

まず、メモリセル 521 に「0」を書き込むための回路動作の一例を述べる。書き込み処理は、メモリセル 521 のワード線  $W_0$  を選択し、ビット線  $B_0$  に電流を流すことで行われる。つまり、書き込みを行いたいメモリセルをワード線  $W_0$  により選択し、記憶素子 533 が第 1 の状態から第 2 の状態へ移行し、絶縁させることができ可能な電圧をかけねばよい。例えば、この電圧を 10V とする。このとき、他のメモリセル内の記憶素子 506、記憶素子 507 及び記憶素子 508 に書き込みが行われることを防止するために TFT 502、TFT 503 及び TFT 504 をオフにする。例えばワード線  $W_1$  及びビット線  $B_1$  は 0V としておくとよい。ワード線  $W_0$  のみが選択された状態で、ビット線  $B_0$  に、記憶素子 533 を第 1 の状態から第 2 の状態へと移行するのに十分な電圧をかけることで、記憶素子 533 に「0」が書き込まれた状態にすることができる。

【0208】

次に、メモリセル 521 の読み出し操作の例を示す。読み出し操作は、メモリセル 521 の記憶素子 533 に「1」が書き込まれた第 1 の状態であるか、「0」が書き込まれた第 2 の状態であるかを判別すればよい。例えば、メモリセル 521 に「0」が書き込まれている状態であるか、「1」が書き込まれている状態であるかを読み出す場合について説明する。記憶素子 533 は「0」が書き込まれた状態、つまり、絶縁状態である。ワード線  $W_0$  を選択して TFT 532 をオンにする。ここで、TFT 532 がオンの状態でビット線  $B_0$  に所定の電圧以上の電圧をかける。ここでは、所定の電圧を 5V とする。このとき、記憶素子 533 が第 1 の状態、つまり、絶縁されていない状態であれば、電流はメモリセル 521 内の接地している配線へと流れてしまい、ビット線  $B_0$  の電圧は 0V になる

10

20

30

40

50

。逆に、記憶素子 533 が第 2 の状態、つまり、絶縁状態であれば、電流はメモリセル 521 内の接地している配線に流れてしまうことなく、ビット線 B<sub>0</sub> の電圧は 5V で維持される。このように、ビット線の電圧により「0」が書き込まれているか、「1」が書き込まれているかを判別することができる。

【0209】

例えば、図 6 (B) に示される、TFT532、TFT503、TFT502、TFT504 を、それぞれ、実施の形態 1 の図 1 (H) に示す TFT、実施の形態 2 の図 4 (C) に示す TFT のいずれかを用いることが可能である。

【0210】

以上のようにして、本発明の TFT は無線交信可能な半導体装置に適用することが可能である。 10

【0211】

[実施の形態 4]

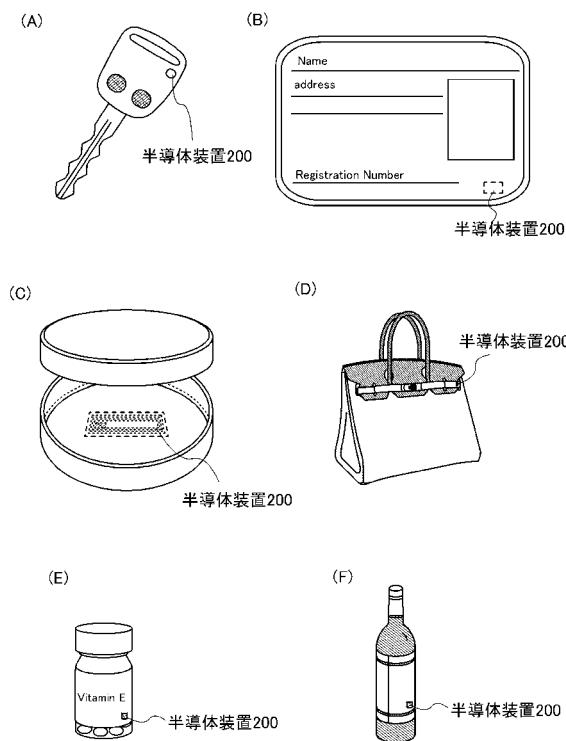

実施の形態 3 に基づいて作製された、無線交信可能な半導体装置 200 は、電磁波の送信と受信ができるという機能を活用して、様々な物品やシステムに用いることができる。物品とは、例えば、鍵 (図 7 (A) 参照)、紙幣、硬貨、有価証券類、無記名債券類、証書類 (運転免許証や住民票等、図 7 (B) 参照)、書籍類、容器類 (シャーレ等、図 7 (C) 参照)、包装用容器類 (包装紙やボトル等、図 7 (E) 及び図 7 (F) 参照)、記録媒体 (ディスクやビデオテープ等)、乗物類 (自転車等)、装身具 (鞄や眼鏡等、図 7 (D) 参照)、食品類、衣類、生活用品類、電子機器 (液晶表示装置、EL 表示装置、テレビジョン装置、携帯端末等) 等である。 20

【0212】

本発明を適用して作製された、無線交信可能な半導体装置 200 は、上記のような様々な形状の物品の表面に貼り付けたり、埋め込んだりして、固定される。また、システムとは、物品管理システム、認証機能システム、流通システム等であり、本発明の半導体装置を用いることにより、システムの高機能化、多機能化、高付加価値化を図ることができる。 30

【0213】

[実施の形態 5]

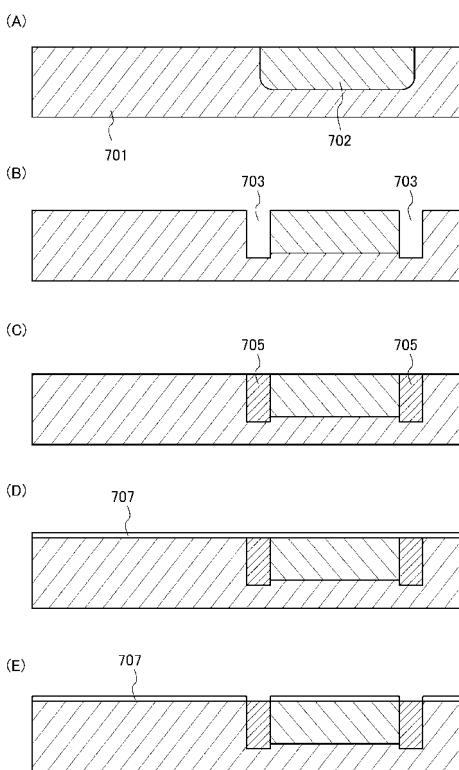

本実施の形態では、単結晶半導体基板を用いてトランジスタを作製する例を、図 20 (A) ~ 図 20 (E)、図 21 (A) ~ 図 21 (D)、図 22 (A) ~ 図 22 (C) を用いて説明する。 30

【0214】

まず p 型半導体基板 701 に n 型半導体領域 702 を形成する (図 20 (A) 参照)。なお、p 型半導体基板 701 の代わりに n 型半導体基板、及び、n 型半導体領域 702 の代わりに p 型半導体領域を用いてもよい。

【0215】

n 型半導体領域 702 の境界に溝 703 を形成する (図 20 (B) 参照)。次いで p 型半導体基板 701 を加熱して、溝 703 から熱酸化させ、酸化物 705 を形成する。酸化物 705 により、後の工程で完成される n チャネル型トランジスタと p チャネル型トランジスタが絶縁分離される。 40

【0216】

次いで実施の形態 1 に基づいて、p 型半導体基板 701 及び n 型半導体領域 702 上に、ごく薄い半導体の酸化膜、ごく薄い窒素を含む半導体の酸化膜、ごく薄い酸素を含む半導体の窒化膜、あるいは、ごく薄い半導体の窒化膜を形成する。図 20 (D) では、p 型半導体基板 701 及び n 型半導体領域 702 上に、ごく薄い半導体の酸化膜 707 を形成する例を示す。

【0217】

あるいは、やはり実施の形態 1 に基づいて、p 型半導体基板 701 及び n 型半導体領域 702 を酸化あるいは窒化して、ごく薄い、半導体の酸化膜、窒素を含む半導体の酸化膜 50

、酸素を含む半導体の窒化膜、半導体の窒化膜を形成する。図20(E)では、p型半導体基板701及びn型半導体領域702上に、ごく薄い半導体の酸化膜707を形成する例を示し、以下図20(E)の構成を用いて半導体装置を作製する工程について説明する。

【0218】

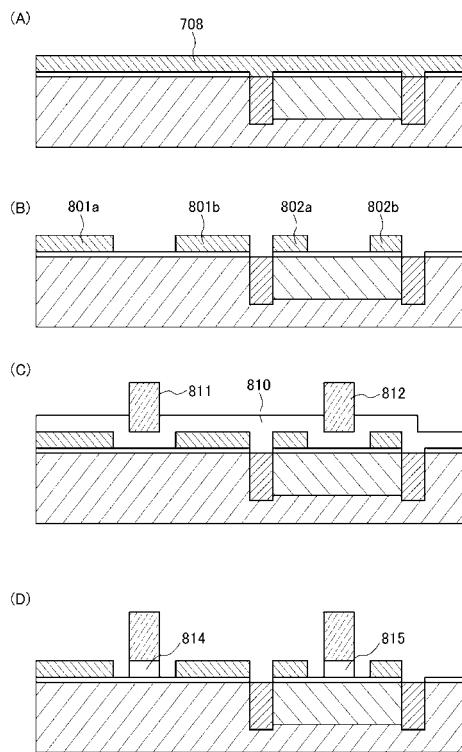

次いで、酸化膜707及び酸化物705上に半導体膜708を形成する(図21(A)参照)。半導体膜708は、半導体膜108と同様の材料及び同様の作製工程を用いて形成すればよい。

【0219】

半導体膜708をエッティングして、nチャネル型トランジスタが形成される領域の、端部に近い領域上に半導体膜801(半導体膜801a及び半導体膜801b)、並びに、pチャネル型トランジスタそれぞれが形成される領域の、端部に近い領域上に半導体膜802(半導体膜802a及び半導体膜802b)を形成する(図21(B)参照)。

【0220】

次いで、酸化膜707、酸化物705、半導体膜801、半導体膜802を覆って、絶縁膜810を形成する。半導体膜801及び半導体膜802に覆われていない酸化膜707を除去した後に、絶縁膜810を形成してもよい。絶縁膜810は、酸化珪素膜、窒素を含む酸化珪素膜、酸素を含む窒化珪素膜、窒化珪素膜のいずれか1つ、あるいは2つ以上の積層膜を用いればよい。

【0221】

絶縁膜810上に、ゲート電極811及びゲート電極812を形成する(図21(C)参照)。ゲート電極811及びゲート電極812は、ゲート電極111と同様の材料を用いて形成すればよい。

【0222】

ゲート電極811及びゲート電極812をマスクとして、絶縁膜810をエッティングし、ゲート電極811の下に絶縁膜814、ゲート電極812の下に絶縁膜815を形成する(図21(D)参照)。ゲート電極811の下の酸化膜707及び絶縁膜814を合わせて、nチャネル型トランジスタのゲート絶縁膜とする。またゲート電極812の下の酸化膜707及び絶縁膜815を合わせて、pチャネル型トランジスタのゲート絶縁膜とする。

【0223】

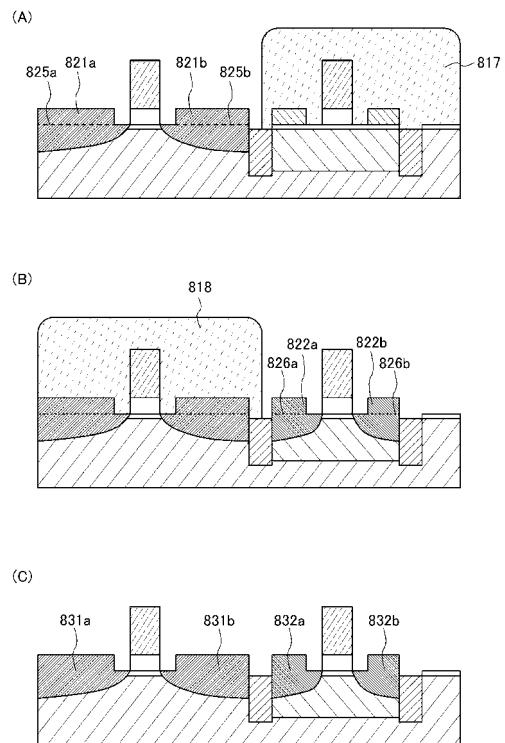

pチャネル型トランジスタとなる領域に、レジスト817を形成し、nチャネル型トランジスタとなる領域の半導体膜801及びp型半導体基板701にn型を付与する不純物元素を添加する。n型を付与する不純物元素としては、リン(P)やヒ素(As)を用いればよい。

【0224】

この添加工程の際に、酸化膜707中の構成元素である酸素や珪素等にイオンが衝突して、酸素や珪素が散乱あるいは跳躍するイオンミキシングが生じる。

【0225】

半導体膜801及びp型半導体基板701中のn型を付与する不純物が形成された領域は、不純物領域821(不純物領域821a及び不純物領域821b)となる。不純物領域821中の酸化膜707はイオンミキシングされた酸化膜825(酸化膜825a及び酸化膜825b)となる(図22(A)参照)。

【0226】

nチャネル型トランジスタとなる領域に、レジスト818を形成し、pチャネル型トランジスタとなる領域の半導体膜802及びn型半導体領域702にp型を付与する不純物元素を添加する。p型を付与する不純物元素としては、ホウ素(B)用いればよい。

【0227】

n型あるいはp型を付与する不純物元素は、 $1 \times 10^{14} \sim 1 \times 10^{16}$  atoms/cm<sup>2</sup>の範囲で添加すればよく、異なる加速電圧で2回以上添加してもよい。

10

20

30

40

50

## 【0228】

この添加工程の際に、酸化膜707中の構成元素である酸素や珪素等にイオンが衝突して、酸素や珪素が散乱あるいは跳躍するイオンミキシングが生じる。

## 【0229】

半導体膜802及びn型半導体領域702中のn型を付与する不純物が形成された領域は、不純物領域822（不純物領域822a及び不純物領域822b）となる。不純物領域822中の酸化膜707はイオンミキシングされた酸化膜826（酸化膜826a及び酸化膜826b）となる（図22（B）参照）。

## 【0230】

その後、レーザ活性化や、RTA（Rapid Thermal Anneal）や、10 炉を用いたファーネスアニール等を用いて、添加された不純物元素の活性化を行う。特に、レーザ活性化やRTAによって、p型半導体基板701、n型半導体領域702、不純物領域821、不純物領域822が700以上、特に1000以上になると、酸素の拡散が進み、イオンミキシングされた酸化膜825及び826の少なくとも一部は消失する。またレーザ活性化時に酸化膜825及び826、並びにそれらの周辺の半導体膜が溶融すれば、酸化膜825及び826は消失しやすくなる。

## 【0231】

以上により、nチャネル型トランジスタのソース領域またはドレイン領域の一方である領域831aと、ソース領域またはドレイン領域の他方である領域831b、領域831aと領域831bとの間にチャネル形成領域が形成される。またpチャネル型トランジスタのソース領域またはドレイン領域の一方である領域832aと、ソース領域またはドレイン領域の他方である領域832b、領域832aと領域832bとの間にチャネル形成領域が形成される（図22（C）参照）。

## 【図面の簡単な説明】

## 【0232】

【図1】本発明の半導体装置の作製工程を示す断面図。

【図2】従来の半導体装置の断面図。

【図3】本発明の半導体装置の作製工程を示す断面図。

【図4】本発明の半導体装置の作製工程を示す断面図。

【図5】本発明の半導体装置を利用した一形態を示す図。

【図6】本発明のTFTを搭載した半導体装置を示す回路図。

【図7】本発明の半導体装置の搭載例を示す図。

【図8】本発明の半導体装置の作製工程を示す断面図。

【図9】本発明の半導体装置の作製工程を示す断面図。

【図10】本発明の半導体装置の作製工程を示す断面図。

【図11】本発明の半導体装置の作製工程を示す断面図。

【図12】本発明のSOI基板の断面図。

【図13】本発明のSOI基板の断面図。

【図14】本発明のSOI基板の作製工程を示す断面図。

【図15】本発明のSOI基板の作製工程を示す断面図。

【図16】本発明のSOI基板の作製工程を示す断面図。

【図17】本発明のSOI基板の作製工程を示す断面図。

【図18】本発明のSOI基板の作製工程を示す断面図。

【図19】本発明のSOI基板の作製工程を示す断面図。

【図20】本発明の半導体装置の作製工程を示す断面図。

【図21】本発明の半導体装置の作製工程を示す断面図。

【図22】本発明の半導体装置の作製工程を示す断面図。

【図23】本発明の半導体装置の作製工程を示す断面図。

## 【符号の説明】

## 【0233】

10

20

30

40

50

|         |          |    |

|---------|----------|----|

| 1 0 1   | 基板       |    |

| 1 0 2   | 下地絶縁膜    |    |

| 1 0 3   | 非晶質半導体膜  |    |

| 1 0 4   | 結晶性半導体膜  |    |

| 1 0 5   | 島状半導体膜   |    |

| 1 0 7   | 酸化膜      |    |

| 1 0 8   | 半導体膜     |    |

| 1 0 9   | 半導体膜     |    |

| 1 0 9 a | 半導体膜     | 10 |

| 1 0 9 b | 半導体膜     |    |

| 1 1 0   | 絶縁膜      |    |

| 1 1 1   | ゲート電極    |    |

| 1 1 4   | 不純物領域    |    |

| 1 1 4 a | 不純物領域    |    |

| 1 1 4 b | 不純物領域    |    |

| 1 1 5   | ゲート絶縁膜   |    |

| 1 1 6   | 酸化膜      |    |

| 1 1 6 a | 酸化膜      |    |

| 1 1 6 b | 酸化膜      |    |

| 1 1 7   | 酸化膜      | 20 |

| 1 1 8   | チャネル形成領域 |    |

| 1 1 9 a | 領域       |    |

| 1 1 9 b | 領域       |    |

| 1 2 1   | 基板       |    |

| 1 2 2   | 下地絶縁膜    |    |

| 1 2 3   | 島状半導体膜   |    |

| 1 2 4   | 絶縁膜      |    |

| 1 2 5   | ゲート電極    |    |

| 1 2 6   | 絶縁膜      |    |

| 1 2 7   | サイドウォール  | 30 |

| 1 2 9   | 酸化膜      |    |

| 1 3 1   | 半導体膜     |    |

| 1 3 2   | レジストマスク  |    |

| 1 3 2 a | レジストマスク  |    |

| 1 3 2 b | レジストマスク  |    |

| 1 3 5   | 半導体膜     |    |

| 1 4 1   | 不純物領域    |    |

| 1 4 1 a | 不純物領域    |    |

| 1 4 1 b | 不純物領域    |    |

| 1 4 2   | ゲート絶縁膜   | 40 |

| 1 4 3   | 酸化膜      |    |

| 1 4 3 a | 酸化膜      |    |

| 1 4 3 b | 酸化膜      |    |

| 1 4 6   | チャネル形成領域 |    |

| 1 4 7 a | 領域       |    |

| 1 4 7 b | 領域       |    |

| 1 5 1   | ゲート絶縁膜   |    |

| 1 6 5   | 酸化膜      |    |

| 1 6 6   | ゲート絶縁膜   |    |

| 2 0 0   | 半導体装置    | 50 |

|         |           |    |

|---------|-----------|----|

| 2 0 1   | 演算処理回路    |    |

| 2 0 2   | 記憶回路      |    |

| 2 0 3   | アンテナ      |    |

| 2 0 4   | 電源回路      |    |

| 2 0 5   | 復調回路      |    |

| 2 0 6   | 変調回路      |    |

| 2 0 7   | リーダ／ライタ   |    |

| 5 0 2   | T F T     |    |

| 5 0 3   | T F T     |    |

| 5 0 4   | T F T     | 10 |

| 5 0 6   | 記憶素子      |    |

| 5 0 7   | 記憶素子      |    |

| 5 0 8   | 記憶素子      |    |

| 5 2 1   | メモリセル     |    |

| 5 2 3   | メモリセルアレイ  |    |

| 5 2 4   | ビット線駆動回路  |    |

| 5 2 5   | カラムデコーダ   |    |

| 5 2 6   | 読み出し回路    |    |

| 5 2 7   | セレクタ      |    |

| 5 2 8   | インターフェース  | 20 |

| 5 2 9   | ワード線駆動回路  |    |

| 5 3 0   | ロウデコーダ    |    |

| 5 3 1   | レベルシフタ    |    |

| 5 3 2   | T F T     |    |

| 5 3 3   | 記憶素子      |    |

| 6 0 0   | 支持基板      |    |

| 6 0 1   | L T S S 層 |    |

| 6 0 2   | 接合層       |    |

| 6 0 3   | バリア層      |    |

| 6 0 4   | 絶縁層       | 30 |

| 6 0 5   | 酸化シリコン層   |    |

| 6 0 6   | 半導体基板     |    |

| 6 0 7   | 分離層       |    |

| 7 0 1   | p型半導体基板   |    |

| 7 0 2   | n型半導体領域   |    |

| 7 0 3   | 溝         |    |

| 7 0 5   | 酸化物       |    |

| 7 0 7   | 酸化膜       |    |

| 7 0 8   | 半導体膜      |    |

| 8 0 1   | 半導体膜      | 40 |

| 8 0 1 a | 半導体膜      |    |

| 8 0 1 b | 半導体膜      |    |

| 8 0 2   | 半導体膜      |    |

| 8 0 2 a | 半導体膜      |    |

| 8 0 2 b | 半導体膜      |    |

| 8 1 0   | 絶縁膜       |    |

| 8 1 1   | ゲート電極     |    |

| 8 1 2   | ゲート電極     |    |

| 8 1 4   | 絶縁膜       |    |

| 8 1 5   | 絶縁膜       | 50 |

|           |               |    |

|-----------|---------------|----|

| 8 1 7     | レジスト          |    |

| 8 1 8     | レジスト          |    |

| 8 2 1     | 不純物領域         |    |

| 8 2 1 a   | 不純物領域         |    |

| 8 2 1 b   | 不純物領域         |    |

| 8 2 2     | 不純物領域         |    |

| 8 2 2 a   | 不純物領域         |    |

| 8 2 2 b   | 不純物領域         |    |

| 8 2 5     | 酸化膜           | 10 |

| 8 2 5 a   | 酸化膜           |    |

| 8 2 5 b   | 酸化膜           |    |

| 8 2 6     | 酸化膜           |    |

| 8 2 6 a   | 酸化膜           |    |

| 8 2 6 b   | 酸化膜           |    |

| 8 3 1 a   | 領域            |    |

| 8 3 1 b   | 領域            |    |

| 8 3 2 a   | 領域            |    |

| 8 3 2 b   | 領域            |    |

| 1 0 0 1   | シリコン基板        |    |

| 1 0 0 2   | 結晶性半導体膜       | 20 |

| 1 0 0 3   | ゲート酸化膜        |    |

| 1 0 0 4 a | n型非晶質珪素膜      |    |

| 1 0 0 4 b | n型非晶質珪素膜      |    |

| 1 0 0 5   | ゲート電極         |    |

| 1 0 0 6   | 酸化珪素膜         |    |

| 1 0 0 7 a | ソース電極及びドレイン電極 |    |

| 1 0 0 7 b | ソース電極及びドレイン電極 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

200 半導体装置

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 21/265

H 01 L 21/20

Q

(56)参考文献 特開平04-348040 (JP, A)

特表2007-500936 (JP, A)

特表2008-515188 (JP, A)

特開2005-167068 (JP, A)

特開平09-298170 (JP, A)

特開2007-027475 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/18 - 21/20

H 01 L 21/26 - 21/268

H 01 L 21/322 - 21/326

H 01 L 21/336

H 01 L 21/34 - 21/36

H 01 L 21/42 - 21/425

H 01 L 21/428

H 01 L 21/477 - 21/479

H 01 L 21/84

H 01 L 29/76

H 01 L 29/772

H 01 L 29/78 - 29/786