(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 102 96 959 T5 2004.08.05

(12)

## Veröffentlichung

der internationalen Anmeldung mit der

(87) Veröffentlichungs-Nr.: **WO 03/001388**

in deutscher Übersetzung (Art. III § 8 Abs. 2 IntPatÜG)

(21) Deutsches Aktenzeichen: **102 96 959.0**

(86) PCT-Aktenzeichen: **PCT/US02/18358**

(86) PCT-Anmeldetag: **15.05.2002**

(87) PCT-Veröffentlichungstag: **03.01.2003**

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: **05.08.2004**

(51) Int Cl.<sup>7</sup>: **G06F 13/364**

**G06F 13/30**

(30) Unionspriorität:

**09/888,278 23.06.2001 US**

(74) Vertreter:

**SCHUMACHER & WILLSAU,

Patentanwaltssozietät, 80335 München**

(71) Anmelder:

**Motorola, Inc., a Delaware Corp., Schaumburg, Ill.,

US**

(72) Erfinder:

**Moyer, William C., Dripping Springs, Tex., US**

### Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

(54) Bezeichnung: **System und Verfahren zum Steuern der Buszuteilung während Cache-Speicher-Burstzyklen**

(57) Hauptanspruch: System mit einer Vorrichtung zur Steuerung der Benutzung eines Kommunikationsbusses, umfassend:

eine Mehrzahl von Kommunikationsbus-Mastern, wobei wenigstens einer der Mehrzahl von Kommunikationsbus-Mastern mit dem Kommunikationsbus gekoppelt ist, um Information über den Kommunikationsbus in Burst-Zyklen zu kommunizieren, wenn er zu einem Bus-Master gemacht wurde; und

einen mit dem Kommunikationsbus gekoppelten Buszuteiler, der als Antwort darauf, dass zwei der Mehrzahl von Kommunikationsbus-Mastern Master-Kontrolle über den Kommunikationsbus wünschen, eine Zuteilungsstrategie implementiert, um selektiv alleinigen Zugriff durch einen der Mehrzahl von Kommunikationsbus-Mastern auf den Kommunikationsbus zu gestatten, wobei der Buszuteiler Benutzer-gesteuerte Schaltungseinrichtungen zum Empfangen von Steuerinformation aufweist, welche die Kontrolle über den Kommunikationsbus zu irgendeiner Zeit während eines Burst-Transfers von Information durch einen bestehenden der Mehrzahl von Kommunikationsbus-Mastern neu zuordnen kann, ohne zu warten, bis ein Ende einer aktuell bestehenden Burst-Kommunikation auf dem Kommunikationsbus erreicht ist.

**Beschreibung****Bezugnahme auf frühere Anmeldungen**

[0001] Diese Anmeldung wurde in den Vereinigten Staaten von Amerika als Patentanmeldung Nummer 09/888,278 am 23.06.2001 eingereicht.

**Gebiet der Erfindung**

[0002] Diese Erfindung bezieht sich allgemein auf Datenverarbeitungssysteme und insbesondere auf die Zuteilung der Kontrolle über Kommunikationsbusse in Datenverarbeitungssystemen.

**Hintergrund der Erfindung**

[0003] Bei Datenverarbeitungssystemen, die mehrere Kommunikationsbus-Master enthalten, wird eine Buszuteilungslogik verwendet, um einen von mehreren Mästern, die anfordern, die Bus-Inhaberschaft zu erhalten, auszuwählen. Die Auswahl eines Bus-Masters kann unter Verwendung einer Anzahl bekannter Verfahren durchgeführt werden. Beispiele für existierende Algorithmen, die zur Implementierung einer Auswahl verwendet werden, schließen das Implementieren der Auswahl mittels Round-Robin- bzw. Jeder-gegen-Jeden-Reihenfolge, die Auswahl nach Angemessenheit oder die Auswahl nach strikt zugeordneter Priorität ein. In vielen Datenverarbeitungssystemen ist es, um die Betriebseffizienz des Speichersystems zu verbessern, erwünscht, dass ein Bus-Master die Inhaberschaft über einen globalen Kommunikationsbus für die Dauer eines zu einer Zeilenfüll- oder Rückkopieroperation des Cache-Speichers gehörigen Burst-Transfers inne hat, ohne jegliche Unterbrechung der Bus-Inhaberschaft. Typischerweise wird der globale Kommunikationsbus während derartiger Operationen einem Bus-Master zugewiesen, indem irgendein Merkmal, wie etwa ein Burst-Attribut, einem anfänglichen Bereich des zu burstenden oder zu kommunizierenden Transfers zur Verfügung gestellt wird. Ein solches Attribut wird in dem System bestätigt, und eine Buszuteilungs-Steuerschaltung verhindert eine Neuzuweisung der Inhaberschaft über den Kommunikationsbus. Sobald er die Herrschaft über den Bus erlangt hat, behält der aktuelle Bus-Master die Bus-Inhaberschaft während der Dauer des Burst-Transfers bei.

[0004] Eine andere Technik, die verwendet wird, um die Bus-Inhaberschaft aufrechtzuerhalten, ist, dass die Vorrichtung, die die Kontrolle über den Bus inne hat, ein Bus-Verriegelungssignal setzt. Ein Nachteil dieser Technik ist, dass jeder weitere kritische Interrupt in dem System davon ausgeschlossen ist, den Bus zu verwenden, bis das Verriegelungssignal aufgehoben wird. Die Verwendung spezieller Verriegelungsbits ist eine bereits früher verwendete Implementation in Verbindung mit einem solchen Verriegelungssignal.

[0005] Andere bekannte Systeme spezifizieren, dass Burst-Transfers unterbrechbar sind, und erfordern, dass ein unterbrochener Burst-Transfer von dem unterbrochenen Bus-Master erneut gestartet wird, sobald dieser die Bus-Inhaberschaft zurückgewonnen hat. Ein Nachteil einer solchen Technik ist, dass der unterbrochene Bus-Master die Bus-Transfersequenz erneut aufbauen muss und so die Gesamtsystemeffizienz verringert und das Bus-Protokoll komplexer macht.

[0006] Unter einigen speziellen Umständen kann die Länge des Auffüllens einer Cache-Speicherzeile die erforderliche Maximallatenz eines zeitkritischen Alternativ-Bus-Masters übersteigen. Obgleich die Häufigkeit des Auftretens dieser Art von Unterbrechung im Allgemeinen gering ist, erfordern solche anderen Bus-Master den sofortigen Zugriff auf den Bus. Für solche Situationen ist es kritisch, dass die aktuelle Burst-Sequenz zeitweilig unterbrochen und dann erneut aufgenommen wird, obwohl eine solche Unterbrechung eines bestehenden Burst-Transfers die Effizienz des Speichersystems und des dem aktuellen Burst-Transfer zugeordneten Prozessors mit Sicherheit verringert wird.

**Kurze Beschreibung der Zeichnungen**

[0007] Die vorliegende Erfindung wird beispielhaft und nicht beschränkend durch die beigefügten Zeichnungen illustriert, in denen gleiche Bezugszeichen ähnliche Elemente bezeichnen.

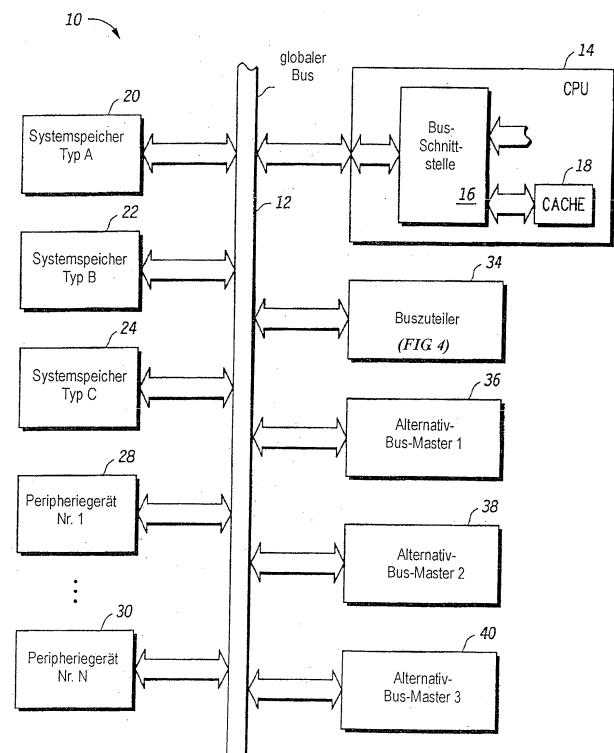

[0008] **Fig. 1** illustriert in Form eines Blockdiagramms ein beispielhaftes Verarbeitungssystem zur Verwendung mit der vorliegenden Erfindung;

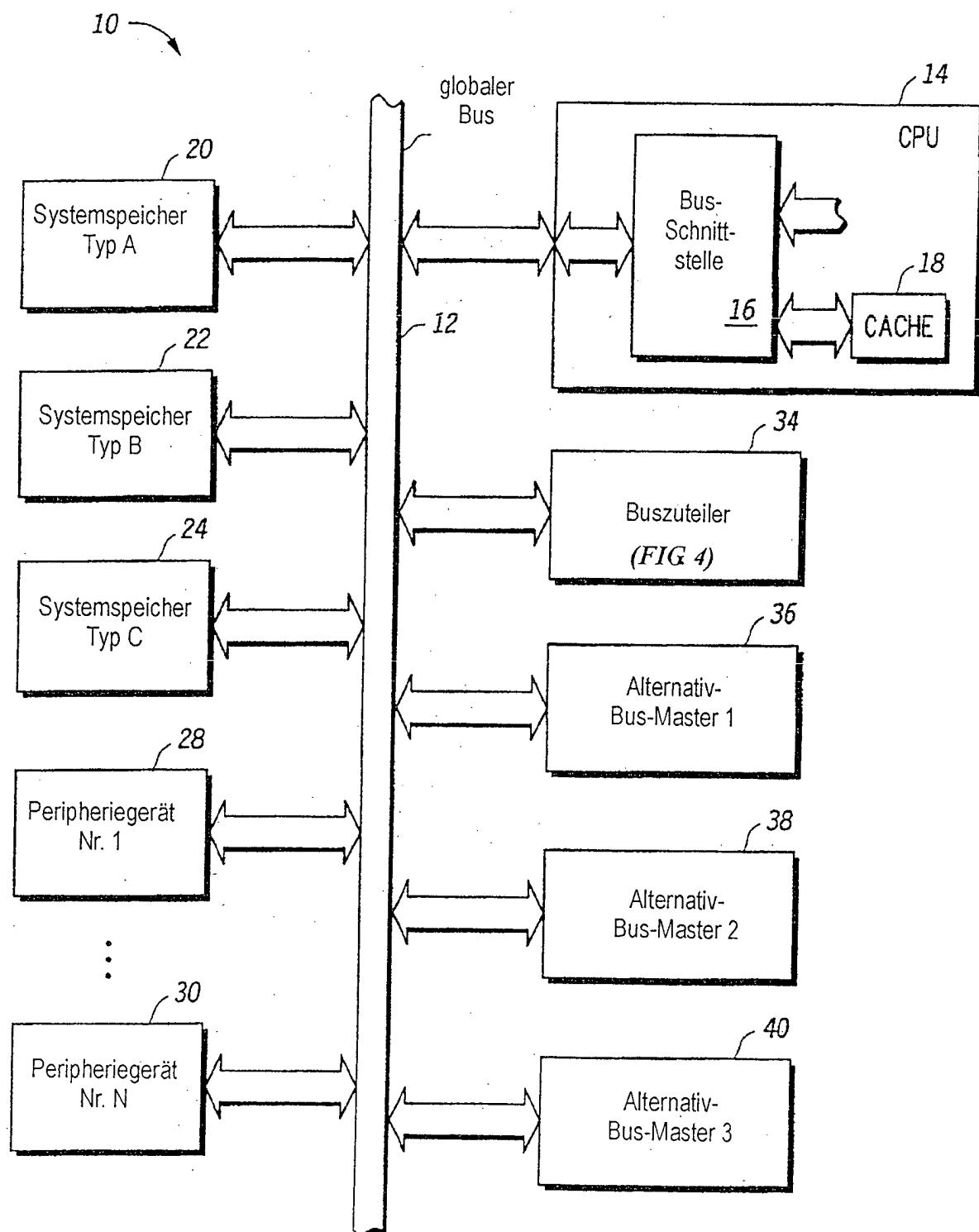

[0009] **Fig. 2** illustriert in Form eines Timing-Diagramms das kennzeichnende Format gebundener und ungebundener Burst-Transfers;

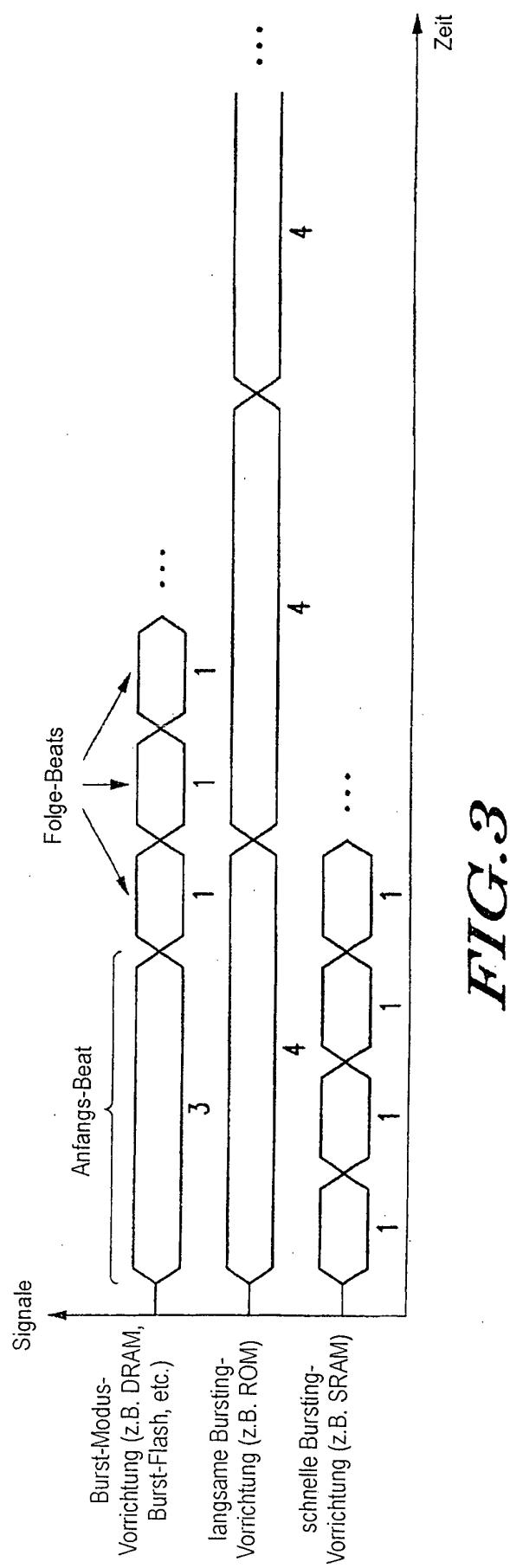

[0010] **Fig. 3** illustriert in Form eines Timing-Diagramms das kennzeichnende Format des Informations-Burstings, welches verschiedenen Typen von Speichervorrichtungen zugeordnet ist;

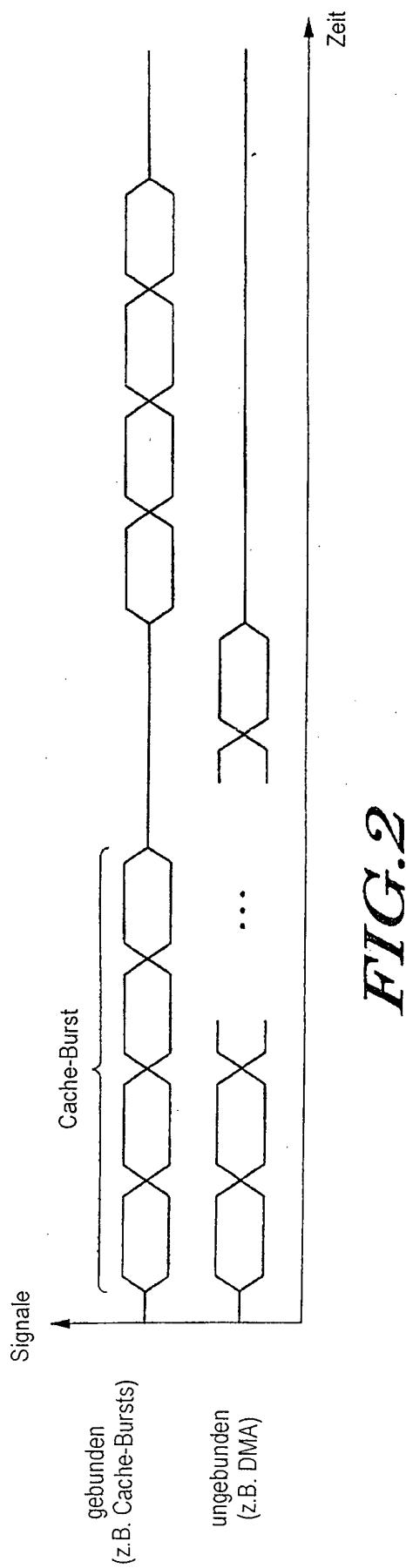

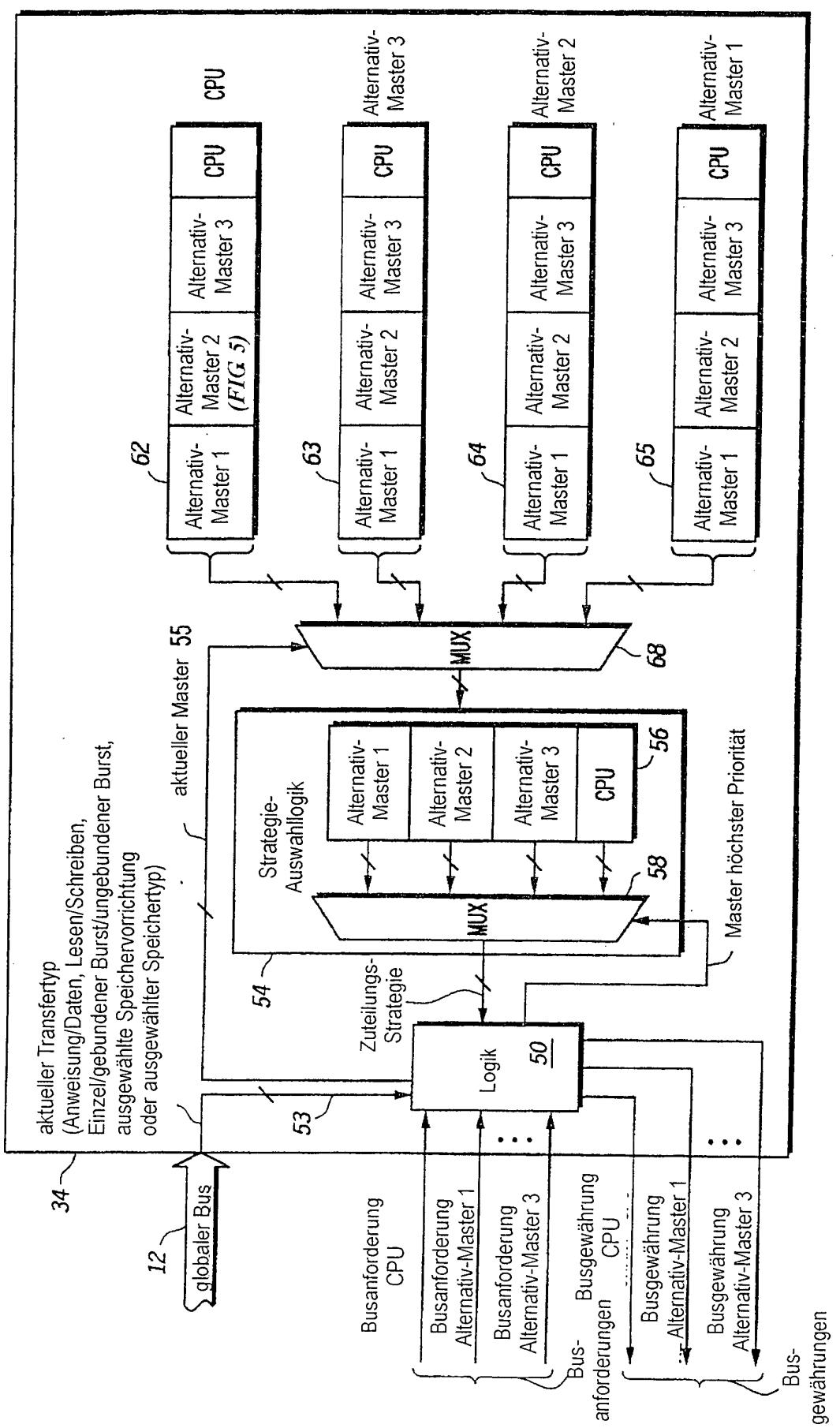

[0011] **Fig. 4** illustriert in Form eines Blockdiagramms eine beispielhafte Implementierung des Buszuteilers von **Fig. 1** gemäß der vorliegenden Erfindung;

[0012] **Fig. 5** illustriert in Tabellenform eine Codierung eines Steuerfeldes eines in **Fig. 4** illustrierten Steuerregisters; und

[0013] **Fig. 6** illustriert in Tabellenform eine weitere Codierung eines Steuerfeldes eines in **Fig. 4** illustrierten Steuerregisters.

[0014] Der Fachmann wird erkennen, dass Elemente in den Figuren zum Zwecke der Einfachheit und Klarheit nicht notwendigerweise maßstabsgetreu gezeichnet sind. Beispielsweise können die Dimensionen von einigen der Elementen in den Figuren relativ zu anderen Elementen übertrieben sein, um das Verständnis der Ausführungsform der vorliegenden Erfindung zu verbessern.

## Beschreibung einer bevorzugten Ausführungsform

[0015] Für Datenverarbeitungssysteme, die mehrere Kommunikationsbus-Master erfordern, wird ein verbessertes Bus-Inhaberschaft-Protokoll benötigt, insbesondere im Hinblick auf das Übertragen der Herrschaft über den Bus in Systemen, die Burst-Transfers von Information verwenden. In Datenverarbeitungssystemen, die mehrere Kommunikationsbus-Master enthalten, wird eine Buszuteilungslogik verwendet, um einen von mehreren Masters, die die Bus-Inhaberschaft anfordern, auszuwählen. Die Auswahl eines Bus-Masters kann unter Verwendung einer Anzahl bekannter Verfahren durchgeführt werden. Ein Priorisierungsschema ist eine Technik, die oft implementiert wird, um zu bestimmen, welcher Systemressource die Kontrolle über den Bus geben wird. Bei vielen Datenverarbeitungssystemen behält der aktuelle Master, sobald er die Herrschaft über den Bus erlangt hat, die Inhaberschaft für die Dauer des Burst-Transfers bei.

[0016] In **Fig. 1** ist ein beispielhaftes Datenverarbeitungssystem **10** illustriert, welches eine Buszuteilung erfordert. Ein globaler Bus **12** ist das Zentrum der Kommunikation in dem Datenverarbeitungssystem **10**. Der globale Bus **12** weist (nicht dargestellte) Leiter für Kommunikationsdaten, Adressen und Steuerinformationen auf. Eine zentrale Verarbeitungseinheit oder CPU **14** ("central processing unit") ist mit dem globalen Bus **12** verbunden. Die CPU **14** weist eine Bus-Schnittstelle **16** auf, die mit dem globalen Bus **12** und einem Cache **18** verbunden ist. Die Bus-Schnittstelle **16** ist auch mit allen weiteren (nicht dargestellten) Schaltungseinrichtungen der CPU **14** verbunden. Ein Systemspeicher **20**, ein Systemspeicher **22** und ein Systemspeicher **24** sind jeweils mit dem globalen Bus **12** verbunden. Jeder der Systemspeicher repräsentiert einen anderen Speichertyp. Der Systemspeicher **20** ist als einen Typ A implementierend bezeichnet, der Systemspeicher **22** ist als einen Typ B implementierend bezeichnet, und der Systemspeicher **24** ist als einen Typ C implementierend bezeichnet.

[0017] Beispiele von Speichertypen schließen DRAM (Dynamic Random Access Memory: dynamischer Direktzugriffspeicher) Flash, ROM (Read Only Memory: Nur-Lese-Speicher) und SRAM (Static Random Access Memory: statischer Direktzugriffspeicher) ein. Eine vorbestimmte Anzahl von Peripheriegeräten ist mit dem globalen Bus **12** verbunden. Ein erstes Peripheriegerät, das Peripheriegerät **28**, ist mit dem globalen Bus **12** verbunden und ein N-tes Peripheriegerät, das Peripheriegerät **30**, ist mit dem globalen Bus **12** verbunden. Die Peripheriegeräte **28-30** können verschiedene Typen von Peripheriegeräten sein, einschließlich Speicher-Controller, Grafik-Controller, ein Display, eine Tastatur etc. Bei der illustrierten Form ist N ein vorbestimmter ganzzahliger Wert. Ein Buszuteiler **34** ist mit dem globalen Bus **12** verbunden. Außerdem ist eine weitere vorbestimmte

Anzahl Alternativ-Bus-Master mit dem globalen Bus **12** verbunden. Bei der illustrierten Form sind jeweils ein Alternativ-Bus-Master **36**, ein Alternativ-Bus-Master **38** und ein Alternativ-Bus-Master **40** mit dem globalen Bus **12** verbunden.

[0018] Im Betrieb arbeitet die CPU **14**, um mit jedem der Peripheriegeräte, Speicher und Alternativ-Bus-Mastern zusammenzuarbeiten, um eine vorbestimmte Systemfunktion oder -operation durchzuführen. Ausgewählte Information, die von dem System **10** benötigt und von dem System **10** erzeugt wird, wird bereitgestellt und von den Systemspeichern **20**, **22** und **24** gespeichert. Da mehrere Operationen in dem System **10** simultan durchgeführt werden, muss der Buszuteiler **34** arbeiten, um den Zugriff auf den globalen Bus **12** zu steuern. Um die Notwendigkeit für die CPU **14**, auf die Systemspeicher zuzugreifen, zu minimieren, weist die CPU **14** einen internen Cache **18** auf, der hinsichtlich seiner Speicherkapazität typischerweise wesentlich kleiner ist als jeder der Systemspeicher. Der Cache **18** kann ein vereinheitlichter Cache sein, der sowohl Anweisungen als auch Daten enthält, oder er kann separate Cache-Module zum Speichern von Anweisungen und Daten in unterschiedlichen Modulen implementieren. Der Cache **18** speichert typischerweise Kopien von Informationen von dem Systemspeicher **20**, dem Systemspeicher **22** und dem Systemspeicher **24**. Der Cache **18** erhält Information von und schreibt Information zurück an den Systemspeicher **20**, den Systemspeicher **22** und den Systemspeicher **24**, wobei er Cache-Burst-Transfers verwendet. Cache-Bursts-Transfers übertragen typischerweise einen "Block" oder eine "Zeile" von Information, die aus einer Mehrzahl von Datenworten in einer Burst-Sequenz bestehen, über den globalen Bus **12**. Viele Speicher, die in einem Datenverarbeitungssystem implementiert sind, kommunizieren mittels Burst-Transfers aus Information, wobei die Information in schnellen kontinuierlichen Bursts kommuniziert wird.

[0019] Burst-Transfers können in zwei Typen kategorisiert werden:

ein gebundener Burst und ein ungebundener Burst. In **Fig. 2** ist in Form eines Timing-Diagramms ein Beispiel der zwei Typen von Burst-Transfers dargestellt, um den Unterschied zwischen einem gebundenen und einem ungebundenen Burst zu erläutern. Gebundene Bursts sind typischerweise Cache-Speichern zugeordnet, wobei ein Burst eine festgelegte Länge hat und typischerweise eine Anzahl von "Beats", die einer Potenz von zwei entspricht. Beispielsweise würde ein Cache, der eine Zeilenlänge von vier Worten benutzt, einen Cache-Burst ausführen, der aus vier Beats besteht, wobei jeder Beat einem der vier Worte entspricht. Der gebundene Burst von **Fig. 2** weist in jedem der illustrierten Cache-Bursts vier Beats auf. Ein Beispiel eines ungebundenen Burst könnte einen Alternativ-Bus-Master, wie etwa einen Direktzugriffspeicher (DMA)-Control-

ler (DMAC), der programmiert ist, eine beliebige Anzahl von Informations-Bytes oder -Worten zu übertragen, einbeziehen. Wie in **Fig. 2** illustriert, kann der ungebundene Burst eine variable Länge aufweisen, und ein Buszuteiler kann daher nicht zuverlässig voraussagen, wann die Freigabe der Herrschaft über den Bus durch den DMA-Controller auftreten wird.

[0020] **Fig. 3** illustriert in Form eines Timing-Diagramms eine Charakterisierung verschiedener Typen von Speichervorrichtungen, welche Burst-Transfers von Information verwenden und unterschiedliche Burst-Typen aufweisen. Eine Burst-Modus-Vorrichtung ist als einen anfänglichen Burst oder Beat aufweisend dargestellt, der in seiner Dauer länger ist als unmittelbar nachfolgende Beats. Der Anfangs-Beat kann beispielsweise drei Takte lang sein, und die nachfolgenden Beats können jeweils einen Takt Dauer aufweisen. Die Burst-Modus-Vorrichtung kann entweder ungebundene Bursts, wie dargestellt, oder gebundene Bursts unterstützen. Beispiele für übliche Burst-Modus-Vorrichtungen umfassen DRAMs und Flash-Speicher. Eine langsame Bursting-Vorrichtung ist als lange (d.h. langsame) kontinuierliche Beats derselben Taktzeit aufweisend dargestellt. Als ein Beispiel ist jeder Beat mit einer Länge von vier Taktzyklen dargestellt. Burst-Zugriffe auf eine langsame Bursting-Vorrichtung können entweder ungebunden oder gebunden sein. Ein Beispiel einer üblichen langsamen Bursting-Vorrichtung ist ein ROM. Im Gegensatz dazu zeigt eine schnelle Bursting-Vorrichtung einen kontinuierlichen Strom von kurzen Informations-Beats. In dem Beispiel von **Fig. 3** ist jeder Beat mit nur einem Taktzyklus Dauer dargestellt, wie bei Burst-Modus-Vorrichtungen und langsamen Bursting-Vorrichtungen können Zugriffe auf schnelle Bursting-Vorrichtung entweder ungebunden, wie dargestellt, oder gebunden sein.

[0021] In **Fig. 4** ist ein detailliertes Beispiel einer Implementation des Buszuteilers **34** von **Fig. 1** gemäß der vorliegenden Erfindung illustriert. Zur Bequemlichkeit des Verständnisses sind alle gemeinsamen Elemente zwischen **Fig. 1** und **Fig. 4** übereinstimmend nummeriert. Eine Logikschaltung **50** weist einen ersten, mit dem globalen Bus **12** verbundenen Eingang zum Empfang eines den Typ des aktuellen Transfers bezeichnenden Signals auf. Die den Typ des aktuellen Transfers bezeichnenden Signale **53** können verschiedene Informationen enthalten, die dem vorliegenden oder aktuellen Transfer, der über den globalen Bus **12** kommuniziert wird, zugeordnet sind. Beispiele für Informationstypen umfassen, sind jedoch nicht beschränkt auf Information, die identifiziert, ob Anweisungs- (d.h. Programm-) Information oder Dateninformation aktuell von dem globalen Bus **12** transferiert wird. Andere Information bezüglich des aktuellen Transfertyps kann umfassen, ob der aktuelle Transfer ein Lese- oder ein Schreibtransfer ist, ob der aktuelle Transfer ein Einzeltransfer oder ein Vielfach-Burst ist, ob der aktuelle Transfer ein gebundener Burst oder ein ungebundener Burst ist, wel-

che ausgewählte Speichervorrichtung dem aktuellen Transfer zugeordnet ist und welcher Typ von Speichervorrichtung dem aktuellen Transfer zugeordnet ist. Die Logikschaltung **50** weist auch eine Mehrzahl von Busanforderungseingängen zum jeweiligen Empfangen eines Busanforderungssignals von der CPU **14** und den Alternativ-Bus-Mastern **36, 38** und **40** auf. Die Busanforderungssignale können direkt (d.h. Punkt zu Punkt) von jedem der anfordernden Vorrichtungen kommuniziert werden oder sie können über den globalen Bus **12** kommuniziert werden. Die Logikschaltung **50** weist auch eine Mehrzahl von Busgenehmigungsausgängen auf, die jeweils mit der CPU **14** und den Alternativ-Bus-Mastern **36, 38** und **40** verbunden sind. Eine Strategieauswahllogikschaltung **54** erzeugt ein Zuteilungsstrategiessignal, welches mit einem zweiten Eingang der Logikschaltung **50** verbunden wird. Die Strategieauswahllogikschaltung **54** weist ein Steuerregister **56** auf, welches eine Mehrzahl von Feldern mit vorbestimmter Bitbreite hat. Bei der illustrierten Form weist das Steuerregister **56** dem ersten Alternativ-Bus-Master **36**, dem zweiten Alternativ-Bus-Master **38**, dem dritten Alternativ-Bus-Master **40** und der CPU **14** zugeordnete Felder auf. Jedes Feld des Steuerregisters **56** ist mit einem Eingang eines Multiplexers (Mux) **58** verbunden. Ein Ausgang des Multiplexers **58** ist mit dem zweiten Eingang der Logikschaltung **50** verbunden, um das Zuteilungsstrategiessignal zu liefern. Ein Ausgang der Logikschaltung **50** ist mit einem Steuereingang des Multiplexers **58** verbunden, um auszuwählen, welches Feld des Steuerregisters **56** verwendet werden soll. Zusätzliche Steuerregister können, falls erwünscht, vorgesehen sein. Wie aus der nachfolgenden Betriebsbeschreibung erkennbar wird, sind die Steuerregister **62–65** und der Multiplexer **68** optionale Schaltungseinrichtungen und bieten zusätzliche Benutzeroptionen zur Etablierung eines Burst-Zuteilungsprotokolls. Die Steuerregister **62–65** sind mit einer vorbestimmten Anzahl von Feldern illustriert, basierend auf der Anzahl von Alternativ-Bus-Mastern. Bei der illustrierten Form gibt es ein zusätzliches Steuerregister, jeweils für die CPU **14** und die Alternativ-Bus-Master **36, 38** und **40**. Außerdem weist jedes Steuerregister **62** bis **65** ein Feld auf, welches der CPU und den Alternativ-Bus-Mastern **36, 38** und **40** entspricht. Jedes der Steuerregister **62** bis **65** ist mit einem vorbestimmten Eingang eines Multiplexers (Mux) **68** verbunden. Ein Ausgang des Multiplexers **68** ist mit dem Steuerregister **56** der Strategieauswahllogikschaltung **54** verbunden.

[0022] Im Betrieb arbeitet der Buszuteiler **34**, um zu steuern, welche Vorrichtung in dem Datenverarbeitungssystem **10** der Master des globalen Busses **12** ist (d. h. die Rechte hat, diesen zu benutzen). Obgleich der Buszuteiler **34** als separat und getrennt in dem Datenverarbeitungssystem **10** dargestellt ist, sollte man erkennen, dass die Buszuteilungsfunktion in die CPU **14** oder andere Bereiche des Datenverarbeitungssystems **10** inkorporiert werden kann, so

dass es kein getrenntes Modul zum Durchführen der Buszuteilung gibt. Der Buszuteiler **34** verwendet Information über einen aktuellen Transfer, um beim Empfang eines oder mehrerer Busanforderungen zur Benutzung des globalen Busses **12** Steuerentscheidungen bezüglich des globalen Busses **12** zu treffen. Wenn die Logikschaltung **50** eine oder mehrere Busanforderungen von der CPU **14** oder den Alternativ-Bus-Mastern **36**, **38** oder **40** empfängt, wird in der Logikschaltung **50** eine Entscheidung getroffen, basierend auf einigen vorbestimmten Kriterien, wie etwa darauf, welche Busanforderung zuerst bedient werden sollte. Bei einer Form wird die Entscheidung basierend auf einer Prioritätsbasis getroffen, es sollte jedoch gut verstanden werden, dass andere Kriterien, die keine Prioritäten einbeziehen, wie etwa eine Round-Robin- bzw. eine zyklische Auswahl, auch verwendet werden können. Die Logikschaltung **50** liefert dem Multiplexer **58** ein Signal, welches einen Master höchster Priorität (d. h. entsprechend der Busanforderung, die zur Bedienung ausgewählt wurde) anzeigt, und der Multiplexer **58** verwendet dieses Signal, um das Steuerfeld des Steuerregisters **56** auszuwählen, welches diesem Master höchster Priorität zugeordnet ist. Das Steuerfeld des Steuerregisters **56** ist mittels einer benutzerprogrammierten oder benutzergesteuerten Codierung (d. h. einem Steuerwert) codiert, welche die Zuteilungsstrategie bestimmt, die von dem Buszuteiler **34** für diese spezielle, anfordernde Vorrichtung verwendet werden soll. Ein Benutzer kann einen Steuerwert erzeugen oder dessen Erzeugung veranlassen, indem ein Signal oder eine Spannung an einem integrierten Schaltkreispin eines integrierten Schaltkreises verwendet wird, der von dem Buszuteiler **34** oder durch die Ausführung einer vom Benutzer bereitgestellten Softwareanweisung innerhalb des Datenverarbeitungssystems **10** gesteuert wird. Die Logikschaltung **50** decodiert dann das ausgewählte Steuerfeld des Steuerregisters **56** und bestimmt, ob dem Bus-Master mit der höchsten Priorität in dem Datenverarbeitungssystem **10** die Inhaberschaft über den globalen Bus **12** während eines anstehenden Burst-Transfers gewährt wird oder ob er auf die Vollendung eines laufenden Burst-Transfers warten muss. Die Logik-Schaltung **50** setzt, je nach Fall, das Bus-Gewährungs-CPU-Signal oder ein Bus-Gewährungs-Signal für einen der anfragenden Alternativ-Bus-Master **36**, **38** und **40**, basierend auf den den Typ des aktuellen Transfers bezeichnenden Signalen **53** und der in dem Steuerregister **56** enthaltenen Information. Wenn die Bus-Inhaberschaft einem anderen Master als demjenigen zugeordnet wird, der den aktuellen Transfer durchführt (d.h. eine Übertragung des Master-Status von einem derzeitigen oder aktuellen Kommunikationsbus-Master), wird der aktuelle Transfer unterbrochen und ein zuvor gesetztes Busgewährungssignal wird negiert, um zu erzwingen, dass der globale Bus **12** freigegeben wird, und um so zu erlauben, dass der Master höchster Priorität die Bus-Inha-

berschaft während eines laufenden Burst-Transfers erhält. Es sollte verstanden werden, dass das Steuerregister **56** benutzerprogrammiert sein kann, um dem Datenverarbeitungssystem eine größere Flexibilität und die Fähigkeit zu geben, Bus-Interrupt-Latenzen anzupassen. Insbesondere kann das Steuerregister **56** mit speziellen Buszuteilungsstrategiekodierungen programmiert werden, um von der Logikschaltung **50** mittels Verwendung spezifischer Eingangssignale an vorbestimmte integrierte Schaltkreispins eines Ics, der das Datenverarbeitungssystem **10** verkörpert, oder mittels anderer in dem Datenverarbeitungssystem **10** enthaltener Signale interpretiert zu werden. Bei der Alternative kann das Steuerregister **56** unter Softwareanweisungssteuerung oder mittels anderer benutzerprogrammierter Techniken benutzerprogrammiert werden.

[0023] In Fig. 5 ist ein beispielhaftes Codierungsbeispiel illustriert, welches für jedes Steuerfeld in dem Steuerregister **56** verwendet werden kann. Es gibt viele verschiedene Codierungen, die verwendet werden können, und es sollte gut verstanden werden, dass die hier angegebenen Beispiele ohne weiteres modifiziert oder ausgedehnt werden können. Lediglich zum Zwecke der Illustration sei angenommen, dass ein 3-Bit-Codierungsfeld ausgewählt ist, wodurch eine Gesamtzahl von acht verschiedenen Codierungen bereitgestellt wird. Die Codierungen von Fig. 5 illustrieren eine Zuteilungsstrategie die darauf basiert, ob Änderungen der Bussteuerung während Burst-Zyklen erlaubt sind, ob Bussteuerungsänderungen, basierend auf dem zu kommunizierenden Typ von Information (z.B. Anweisungs- oder Programminformation gegenüber Dateninformation), erlaubt werden, ob Bussteuerungsänderungen, basierend darauf, ob eine Lese- oder Schreiboperation eines Systemspeichers auftritt, erlaubt werden und ob Bussteuerungsänderungen, basierend darauf, ob ein Cache-Burst (d.h. ein gebundener Burst) oder ein allgemeinerer ungebundener sequentieller Burst-Transfer auftritt, erlaubt werden. Die Zuteilungsstrategie kann auf anderen Faktoren oder auf einer Kombination der hier beschriebenen Charakteristiken basieren. Sobald identifiziert ist, welcher Typ aktuellen Transfers auf dem globalen Bus **12** vorliegt, kann die Logikschaltung **50** konstruiert sein, um optimal auf ein korrektes Busgewährungssignal zu antworten. Bei bestimmten Ausführungsformen des Datenverarbeitungssystems **10** sollte beispielsweise, falls ein Cache-Burst als aktuell auf dem globalen Bus **12** vorliegend identifiziert wird, erlaubt werden, dass der Cache-Burst vor Ausgabe eines Buserteilungssignals, welches die Herrschaft über den Bus verändert würde, vollendet wird. Wenn jedoch kein Cache-Burst vorliegt, kann aufgrund der ungewissen Länge, die zu einem ungebundenen sequentiellen Burst gehört, ein Buserteilungssignal ausgegeben werden. Cache-Bursts werden von ungebundenen sequentiellen Burst-Transfers unterschieden, da sie eine limitierte und bekannte Länge haben, wie etwa

typischerweise vier oder acht Beats. Die Cache-Bursts zugeordnete Transferzeit ist daher gebunden. Das Zurückhalten von Buserteilungen an Alternativ-Master während des limitierten Intervalls eines Cache-Zeilen-Bursts verbessert die Systemleistung, indem eine optimale Burst-Speicheroperation gestattet wird und indem die Anzahl von Verzögerungszyklen in CPUs mit blockierenden Caches minimiert wird.

[0024] Bei einigen Ausführungsformen des Datenverarbeitungssystems **10** wird außerdem, falls eine Lese-Operation auftritt, so dass Information von einem der Systemspeicher an die CPU **14** geliefert wird, diese Information als wichtig genug angenommen werden, um eine potentielle Verzögerung der CPU **14** zu vermeiden, um die Burst-Transaktion zu vollenden, bevor ein Wechsel der Bus-Inhaberschaft erlaubt wird. Wenn jedoch eine Schreiboperation auftritt, kann bei einer bestimmten Systemanwendung ein Wechsel der Herrschaft über den Bus auftreten, ohne die Systemleistung wesentlich zu verschlechtern. Die vorliegende Erfindung erlaubt es, dass ein Benutzer in der Lage ist, bestimmte Anwendungsregeln anzupassen, die damit verbunden sind, dass die Kommunikationsbus-Inhaberschaft geändert werden kann. Es kann sein, dass die gerade in diesem Absatz beschriebenen Regeln nicht immer für alle Systeme anwendbar sind, und die geeigneten Codierungen können in dem Steuerregister **56** so codiert werden, dass sie eine spezielle Systemanwendung optimieren.

[0025] Unter einigen speziellen Umständen kann die Länge der Cache-Zeilensättigung die erforderliche Maximal-Latenz eines zeitkritischen Alternativ-Master überschreiten. Diese Master erfordern unverzüglichen Zugriff auf den Bus, und die Häufigkeit dieser Art von Anforderung ist im Allgemeinen niedrig. Für diesen Typ von Master ist es kritisch, dass jegliche Burst-Sequenz unterbrochen und dann wieder aufgenommen wird und zwar trotz der verringerten Effizienz der den Burst anfordernden CPU und des Speichersystems, auf das zugegriffen wird. Es ist wünschenswert, das Auftreten von Burst-Unterbrechungen in einem System zu minimieren und Burst-Unterbrechungen auf einem begrenzten Satz von Mastern zu limitieren.

[0026] Bei einer Form zeigt eine Codierung von 000 an, dass keine Änderung der Bus-Inhaberschaft während eines Cache-Burst-Zyklus erlaubt ist. Dieses Merkmal ist vorteilhaft für ein Systemdesign, welches Burst-Transfers beinhaltet. Wenn es einem Bus-Master definitionsgemäß nicht erlaubt ist, die Zuteilung für einen Systembus zu gestatten, wenn der Bus-Master Information burstet, braucht dieser Bus-Master keine zusätzliche Logikschaltung, um teilweises Bursting implementieren zu können. Bei dem anderen Extrem zeigt eine Codierung von 111 an, dass ein Transfer der Bus-Inhaberschaft während eines Burst-Zyklus erlaubt ist. Eine Codierung von 001 zeigt an, dass ein Wechsel der Bus-Inhaber-

schaft nur während eines Anweisungs-Cache-(I-Cache) Burstzyklus oder eines ungebundenen Burst-Transfers erlaubt ist. Das bedeutet, dass die Bus-Inhaberschaft nur gestattet wird, wenn der Typ von Information auf dem Bus Programminformation ist und das Bursting nicht ungebunden ist, wie dies beim Cache-Bursting der Fall ist oder wenn irgendeine Art von ungebundenem Burst auftritt. Eine Codierung von 010 zeigt an, dass wenn ein Cache-Burst auftritt, ein Wechsel der Bus-Inhaberschaft nur während eines Daten-Cache-(D-Cache) Burst-Lesezyklus erlaubt wird. Daher werden drei Kriterien mit dieser Codierung angezeigt: (1) die Information besteht aus Daten; (2) der Burst ist ein Cache-Burst und (3) die Transaktion auf dem Bus ist eine Lesetransaktion. Eine Codierung von 011 zeigt an, dass ein Wechsel der Bus-Inhaberschaft nur während Cache-Burst-Lesezyklen erlaubt ist, oder wenn irgendeine Art ungebundener Burst auftritt. Eine Codierung von 100 zeigt an, dass ein Wechsel der Bus-Inhaberschaft nur während Cache-Burst-Schreibzyklen erlaubt ist oder wenn irgendeine Art ungebundener Burst auftritt.

[0027] Eine Codierung von 101 zeigt an, dass ein Wechsel der Bus-Inhaberschaft nur während eines Daten-Cache-Burst-Schreibzyklus oder eines Anweisungs-Cache-Burst-Zyklus erlaubt ist oder wenn irgendeine Art ungebundener Burst auftritt. Eine Codierung von 110 zeigt an, dass ein Wechsel der Bus-Inhaberschaft nur während eines Daten-Cache-Burstzyklus erlaubt ist oder wenn irgendeine Art ungebundener Burst auftritt. Die Logik der Logikschaltung **50** wird daher bereitgestellt, um diese genannten Beschränkungen als eine Zuteilungsstrategie zu erkennen, wenn die speziellen Werte von der Strategieauswahllogik **54** präsentiert werden. Der Buszuteiler **34** kann wenigstens zwei verschiedene Zuteilungsstrategien für Burst-Transfers von Information auf dem globalen Bus **12** als Antwort auf die codierte Steuerinformation implementieren. Die Variationen versetzen einen Benutzer in die Lage, eine angepasste Zuteilungsstrategie zu treffen, die den Burst-Transfers für jedes System-Schaltungsmodul zugeordnet sind, welches die Herrschaft über den Bus wünscht und welchem die Herrschaft über den Bus unter vorbestimmten Auswahlkriterien gewährt wird. Es sollte verstanden werden, dass das Zuteilungsverfahren, welches dem Bursting von Information auf einem globalen Datenbus zugeordnet ist, wie es hier gelehrt wird, getrennt ist von dem Algorithmus, der verwendet wird, um einen von mehreren anfordernden Mastern auszuwählen.

[0028] In **Fig. 6** ist eine Codierung für Felder in dem Steuerregister **56**, welches ein Feld mit zwei Bits verwendet, illustriert. Eine Codierung von 00 zeigt an, dass keine Änderung der Bus-Inhaberschaft während allen Burst-Zyklen gestattet wird, wohingegen eine Codierung von 11 anzeigt, dass ein Transfer der Bus-Inhaberschaft während Burst-Zyklen erlaubt ist. Eine Codierung von 01 zeigt an, dass keine Ände-

rung der Bus-Inhaberschaft während Zugriffen auf eine Burst-Modus-Vorrichtung erlaubt ist. Eine Codierung von 10 zeigt an, dass kein Wechsel der Bus-Inhaberschaft während Zugriffen auf eine schnelle Speichervorrichtung erlaubt ist. Durch dieses Beispiel ist daher klar, dass ein Benutzer eine Zuteilungsstrategie basierend darauf programmieren kann, ob eine anfordernde Vorrichtung eine Anforderung zu einer Zeit stellt, zu der die Kontrolle über den Bus bei einem Transfer liegt, der einen DRAM oder einen Flash einbezieht, gegenüber dem Fall, wenn der Transfer einen SRAM einbezieht.

[0029] Außerdem können die Steuerregister **62–65** und der Multiplexer **68** mit dem Steuerregister **56** kombiniert werden, um eine selektive Steuerung auf einer Bus-Master-Basis und auf einer Burst-Type-Basis bereitzustellen. Da die Typen von Bustransfers typischerweise an unterschiedliche Vorrichtungen gerichtet sind, können die Charakteristika der Vorrichtung die Protokollwahl ebenfalls beeinflussen. Jedes der Steuerregister **62–65** ist mit einem bestimmten Bus-Master korreliert und die Steuerfelde (d. h. die Burst-Zuteilungsstrategie) jedes Masters in dem System kann abhängig davon variiert werden, welcher Bus-Master derzeit die Buskontrolle inne hat und darauf, welcher Bus-Master die Buskontrolle beansprucht. Der Multiplexer **68** wählt eines der Steuerregister **62–65** aus, basierend auf Information, die von den den aktuellen Master bezeichnenden Signalen **55** geliefert werden. Für jeden potentiellen Bus-Master wird ein ausgewähltes der Steuerregister **62–65** an die Strategieauswahllogik **54** geliefert, basierend auf dem aktuelle aktiven Bus-Master. Die Strategieauswahllogik **54** kann dann die Steuerfelder in dem gelieferten Steuerregister **62–65** verwenden, um die Zuteilungsstrategie festzulegen, während der aktuelle Bus-Master im Besitz des Busses ist. Die Steuerregister **62–65** können mit Information programmiert werden, die für jeden aktuellen Bus-Master einzigartig ist, so dass die Buszuteilungsstrategien während des Busbesitzes eines bestimmten Bus-Masters unabhängig von dem Busbesitz aller übrigen Master programmiert werden können. Die Auswahlsteuerung auf einer Basis pro Master erlaubt es, dass die Buszuteilungsstrategie auf einer Master-für-Master Besitzbasis geändert und von einem Benutzer optimiert werden kann, um die Systemleistung weiter zu verbessern.

[0030] Es sollte nun offensichtlich sein, dass ein Verfahren und ein System zur Verfügung gestellt wurden, die einen Satz von Steuerbits in einem Register oder in einer anderen Speichervorrichtung oder einen Signalgebungsmechanismus verwenden, um zu Steuern, wie die Zuteilung während Burst-Transfers gehandhabt wird. Für jeden potentiellen Master in dem System wird ein Feld von Steuerinformation bereitgestellt, welches die Zuteilung des Busses während Burst-Transfers steuert. In dem Feld kann eine Steuerung für jeden Transfertyp, wie etwa ein I-Cache-Auffüllen, ein D-Cache-Auffüllen, ein I-Cache-Rückkopieren (Schreiben) etc. bereitgestellt werden. Bei einer alternativen Ausführungsform umfasst das Steuerfeld Steuerinformation, die einer ausgewählten Vorrichtung und dem Burst-Transfertyp entspricht, der von dieser Vorrichtung unterstützt wird. Während Burst-Transfers wird, falls ein Alternativ-Master eine Anforderung für den Bus stellt, die Anforderung nach dem laufenden Transfertyp und der entsprechenden Einstellung des zugeordneten Steuerfeldes qualifiziert.

[0031] Da die Vorrichtung, welche die vorliegende Erfindung implementiert, zum größten Teil aus elektronischen Komponenten und Schaltungen zusammengesetzt ist, die dem Fachmann bekannt sind, sollen Details nicht in einem größeren Ausmaß erläutert werden, als, wie oben illustriert, für das Verständnis und die Erkenntnis der zugrundeliegenden Konzepte der vorliegenden Erfindung notwendig erachtet wird und um nicht zu verwirren oder von der Lehre der vorliegenden Erfindung abzulenken.

[0032] In der vorangehenden Beschreibung wurde die Erfindung mit Bezug auf spezielle Ausführungsformen beschrieben, der Fachmann wird jedoch erkennen, dass verschiedene Modifikationen und Änderungen durchgeführt können, ohne sich von dem Umfang der vorliegenden Erfindung, wie in den Ansprüchen weiter unten aufgestellt, zu entfernen. Beispielsweise kann jede Art von Speicher und jede Art von Cache in Verbindung mit der vorliegenden Erfindung benutzt werden. Verschiedene Bursting-Strategien können codiert werden, abhängig von dem spezifischen System. Steuerstrategieinformation kann mittels Verfahren oder Strukturen geliefert werden, die von dem in der vorangehenden Beschreibung verwendeten Steuerregister verschieden sind. Außerdem kann die vorliegende Erfindung verwendet werden, obgleich nur ein Bus-Master in einem System in der Lage sein kann, Burst-Transaktionen zu verwenden. Entsprechend müssen die Beschreibung und die Figuren in einem illustrativen und nicht in einem restriktiven Sinn betrachtet werden und alle derartigen Modifikationen sollen in dem Umfang der vorliegenden Erfindung eingeschlossen sein.

[0033] Vorteile, weitere Vorteile und Lösungen von Problemen wurden oben unter Bezugnahme auf spezielle Ausführungsbeispiele beschrieben. Die Vorteile, Vorteile, Problemlösungen und jegliche Elemente, die verursachen können, dass irgendein Vorzug, ein Vorteil oder eine Lösung auftritt oder besser ausgeprägt werden, dürfen nicht als ein kritisches, erforderliches oder wesentliches Merkmal oder Element aller oder einiger Ansprüche betrachtet werden. Die Ausdrücke "umfassen", "umfassend" oder jegliche andere Variationen davon, wie sie hier benutzt werden, sollen einen nicht-exklusiven Einschluss abdecken, so dass ein Prozess, ein Verfahren, ein Artikel oder eine Vorrichtung, die eine Liste von Elementen umfassen, nicht nur diese Elemente umfassen, sondern dass sie auch andere Elemente, die nicht ausdrücklich aufgelistet oder einem solchen Prozess, ei-

nem Verfahren, Artikel oder Vorrichtung inhärent sind, einschließen.

## ZUSAMMENFASSUNG DER ERFINDUNG

[0034] Ein Buszuteiler (34) überwacht Charakteristiken, die dem Informationstyp, der über einen globalen Datenbus (12) während einer Bursttransaktion von Information übertragen wird, zugeordnet sind. Ein benutzergesteuertes Zuteilungsstrategieregister (56) kann mit Werten programmiert werden, die de-codiert werden, um zu steuern, ob eine Unterbrechung durch einen anfordernden Bus-Master erlaubt wird. Verschiedene Faktoren können verwendet werden, um Unterbrechungserlaubnisse zu bestimmen. Beispiele für solche Faktoren schließen den Typ der anfordernden Vorrichtung ein, ob eine Burst-Transaktion gebunden oder ungebunden ist, ob eine Transaktion ein Lesen oder ein Schreiben eines Systemspeichers ist und die Identität der speziellen Vorrichtung, die die Herrschaft über den Bus anfordert.

**Fig. 4** zur Zusammenfassung.

## Patentansprüche

1. System mit einer Vorrichtung zur Steuerung der Benutzung eines Kommunikationsbusses, umfassend:

eine Mehrzahl von Kommunikationsbus-Mastern, wobei wenigstens einer der Mehrzahl von Kommunikationsbus-Mastern mit dem Kommunikationsbus gekoppelt ist, um Information über den Kommunikationsbus in Burst-Zyklen zu kommunizieren, wenn er zu einem Bus-Master gemacht wurde; und einen mit dem Kommunikationsbus gekoppelten Buszuteiler, der als Antwort darauf, dass zwei der Mehrzahl von Kommunikationsbus-Mastern Master-Kontrolle über den Kommunikationsbus wünschen, eine Zuteilungsstrategie implementiert, um selektiv alleinigen Zugriff durch einen der Mehrzahl von Kommunikationsbus-Mastern auf den Kommunikationsbus zu gestatten, wobei der Buszuteiler Benutzer-gesteuerte Schaltungseinrichtungen zum Empfangen von Steuerinformation aufweist, welche die Kontrolle über den Kommunikationsbus zu irgendeiner Zeit während eines Burst-Transfers von Information durch einen bestehenden der Mehrzahl von Kommunikationsbus-Mastern neu zuordnen kann, ohne zu warten, bis ein Ende einer aktuell bestehenden Burst-Kommunikation auf dem Kommunikationsbus erreicht ist.

2. System nach Anspruch 1, wobei die Steuerinformation, die von dem Buszuteiler empfangen wird, die Zuteilungsstrategie bestimmt, basierend auf einem Typ von Burst-Transfer, der aktuell auf dem Kommunikationsbus vorliegt.

3. System nach Anspruch 2, wobei die Zuteilungsstrategie, basierend darauf bestimmt wird, ob

der Typ von Burst-Transfer, der aktuell auf dem Kommunikationsbus vorliegt, ein gebundener oder ungebundener Burst ist.

4. System nach Anspruch 2, weiter umfassend: einen mit dem Kommunikationsbus gekoppelten Speicher, wobei die Zuteilungsstrategie basierend darauf bestimmt wird, ob der Typ von Burst-Transfer, der aktuell auf dem Kommunikationsbus vorliegt, ein Lesen oder ein Schreiben des Speichers ist.

5. System nach Anspruch 1, wobei die Steuerinformation, die von dem Buszuteiler empfangen wird, die Zuteilungsstrategie basierend darauf bestimmt, welcher der Mehrzahl von Kommunikationsbus-Mastern aktuell die Kontrolle über den Kommunikationsbus hat.

6. System nach Anspruch 1, wobei die Steuerinformation, die von dem Buszuteiler empfangen wird, die Zuteilungsstrategie basierend darauf bestimmt, welcher oder welche der Mehrzahl von Kommunikationsbus-Mastern aktuell die Kontrolle über den Kommunikationsbus fordert/fordern.

7. System nach Anspruch 1, wobei die Steuerinformation, die von dem Buszuteiler empfangen wird, die Zuteilungsstrategie, basierend auf einem Burst-Typ einer Speichervorrichtung bestimmt, die auf einen Burst-Transfer antwortet, welcher aktuell auf dem Kommunikationsbus vorliegt.

8. System nach Anspruch 1, wobei die benutzer-gesteuerten Schaltungseinrichtungen weiter umfassen:

ein oder mehrere Register zum Speichern wenigstens eines vorbestimmten Steuersignals, welches von einem Benutzer bestimmt wird, wobei das vorbestimmte Steuersignal die Zuteilungsstrategie spezifiziert.

9. System nach Anspruch 8, wobei der Buszuteiler weiter umfasst:

Logikschaltungseinrichtung, die mit dem einen oder den mehreren Registern gekoppelt sind, wobei die Logikschaltungseinrichtung die Zuteilungsstrategie als Antwort auf sowohl das wenigstens eine vorbestimmte Steuersignal als auch ein vorbestimmtes Charakteristikum eines aktuellen Burst-Transfers, welcher gerade von dem Kommunikationsbus kommuniziert wird, implementieren.

10. Verfahren zum Steuern der Benutzung eines Kommunikationsbusses in einem System, umfassend:

Liefern eines Steuerwertes über benutzer-gesteuerte Mittel an einen Buszuteiler, wobei der Steuerwert eine aus einer vorbestimmten Mehrzahl von Zuteilungsstrategien während Burst-Transfers von Information auswählt, um unter einer Mehrzahl von

Bus-Mastern die Herrschaft über den Bus auszuwählen.

11. Verfahren nach Anspruch 10, weiter umfassend:

Liefern eines Statussignals an den Buszuteiler, wobei das Statussignal Information über den aktuellen Burst-Transfertyp enthält, die Typinformation über einen aktuellen Burst-Transfer liefert, der gerade über den Kommunikationsbus kommuniziert wird; und Verwenden sowohl des Steuerwertes als auch des Statussignals, um selektiv die Kontrolle über den Kommunikationsbus zu irgendeiner Zeit während eines aktuellen Burst-Transfers von Information durch einen aktuellen Bus-Masters neu zuzuordnen, ohne zu warten, bis ein Ende des aktuellen Burst-Transfers erreicht wurde.

Es folgen 4 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG.1

**FIG. 4**

| Steuerfeld-Codierung |                                                                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0                | Kein Wechsel der Bus-Inhaberschaft während Cache-Burst-Zyklen erlaubt                                                                         |

| 0 0 1                | Wechsel der Bus-Inhaberschaft nur während Anweisungs-Cache-Burst-Zyklen oder ungebundener Burst-Zyklen erlaubt                                |

| 0 1 0                | Wechsel der Bus-Inhaberschaft nur während Daten-Cache-Burst-Lesezyklen oder ungebundener Burst-Zyklen erlaubt                                 |

| 0 1 1                | Wechsel der Bus-Inhaberschaft nur während Cache-Burst-Lesezyklen oder ungebundener Burst-Zyklen erlaubt                                       |

| 1 0 0                | Wechsel der Bus-Inhaberschaft nur während Cache-Burst-Schreibzyklen oder ungebundener Burst-Zyklen erlaubt                                    |

| 1 0 1                | Wechsel der Bus-Inhaberschaft nur während Daten-Cache-Burst-Schreibzyklen oder Anweisungs-Cache-Bursts oder ungebundener Burst-Zyklen erlaubt |

| 1 1 0                | Wechsel der Bus-Inhaberschaft nur während Daten-Cache-Burst-Zyklen oder ungebundener Burst-Zyklen erlaubt                                     |

| 1 1 1                | Wechsel der Bus-Inhaberschaft während jeglicher Burst-Zyklen erlaubt                                                                          |

*FIG. 5*

| Steuerfeld-Codierung |                                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------|

| 0 0                  | Kein Wechsel der Bus-Inhaberschaft während Burst-Zyklen erlaubt                                     |

| 0 1                  | Kein Wechsel der Bus-Inhaberschaft während Zugriffen auf eine Burst-Modus-Vorrichtung erlaubt       |

| 1 0                  | Kein Wechsel der Bus-Inhaberschaft während Zugriffen auf eine schnelle Speicher-Vorrichtung erlaubt |

| 1 1                  | Wechsel der Bus-Inhaberschaft während jeglicher Burst-Zyklen erlaubt                                |

*FIG. 6*