(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7251951号**

**(P7251951)**

(45)発行日 令和5年4月4日(2023.4.4)

(24)登録日 令和5年3月27日(2023.3.27)

(51)国際特許分類

|        |                  |     |        |       |         |

|--------|------------------|-----|--------|-------|---------|

| H 01 L | 25/07 (2006.01)  | F I | H 01 L | 25/08 | Z       |

| H 01 L | 25/065 (2023.01) |     | H 01 L | 23/12 | 5 0 1 P |

| H 01 L | 25/18 (2023.01)  |     | H 01 L | 23/36 | Z       |

| H 01 L | 23/12 (2006.01)  |     | H 01 L | 21/60 | 3 1 1 Q |

| H 01 L | 23/36 (2006.01)  |     | H 01 L | 23/36 | D       |

請求項の数 7 (全18頁) 最終頁に続く

(21)出願番号 特願2018-212921(P2018-212921)

(22)出願日 平成30年11月13日(2018.11.13)

(65)公開番号 特開2020-80370(P2020-80370A)

(43)公開日 令和2年5月28日(2020.5.28)

審査請求日 令和3年10月18日(2021.10.18)

(73)特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74)代理人 100105957

弁理士 恩田 誠

100068755

弁理士 恩田 博宣

(72)発明者 五十嵐 陽平

長野県長野市小島田町80番地 新光電

気工業株式会社内

審査官 庄司 一隆

最終頁に続く

(54)【発明の名称】 半導体装置及び半導体装置の製造方法

**(57)【特許請求の範囲】****【請求項1】**

半導体装置であって、

放熱板と、

前記放熱板の下面に搭載された第1半導体素子と、

前記第1半導体素子の下面に形成された第1接続端子と、

前記放熱板の下面に形成されたスペーサと、

前記第1半導体素子と一部が上下に重なるように前記第1半導体素子の下面及び前記スペーサの下面に搭載された第2半導体素子と、

前記第2半導体素子の下面に形成された第2接続端子と、

前記第1接続端子と電気的に接続される第1接続パッドと、前記第2接続端子と電気的に接続される第2接続パッドとを有し、前記第1半導体素子及び前記第2半導体素子が実装された配線基板と、

前記第1接続パッド上に形成され、前記第1接続端子と電気的に接続される第3接続端子と、

前記配線基板と前記放熱板との間を充填するアンダーフィル樹脂と、を有し、

前記第1接続端子及び前記第3接続端子の一方が金属ポストであり、他方がはんだボールであり、

前記はんだボールは、球形状のコアボールと、前記コアボールの周囲を覆うはんだとを有するコア付きはんだボールであり、

10

20

前記半導体装置の側面において、前記放熱板の側面よりも前記半導体装置の内方側に前記スペーサの側面が設けられ、前記スペーサの側面よりも前記半導体装置の内方側に前記第2半導体素子の側面が設けられることにより、前記放熱板の側面と前記スペーサの側面と前記第2半導体素子の側面とが階段状に形成されており、

前記アンダーフィル樹脂は、前記スペーサの側面と前記第2半導体素子の側面とを被覆している半導体装置。

#### 【請求項2】

前記スペーサの下面是、前記第1半導体素子の下面と同一平面上に位置するように形成されており、

前記第2半導体素子は、前記スペーサの下面及び前記第1半導体素子の下面に接合されている請求項1に記載の半導体装置。 10

#### 【請求項3】

前記第1半導体素子はコイルを有しており、

前記第2半導体素子はコイルを有しており、

前記第1半導体素子のコイルと前記第2半導体素子のコイルとが磁界結合されている請求項1又は2に記載の半導体装置。 20

#### 【請求項4】

前記第1接続端子が前記金属ポストであり、前記第3接続端子が前記はんだボールである請求項1～3のいずれか一項に記載の半導体装置。

#### 【請求項5】

前記第1接続端子は、第1はんだ層を介して前記第3接続端子と電気的に接続されており、

前記第2接続端子は、第2はんだ層を介して前記第2接続パッドと電気的に接続されている請求項1～4のいずれか一項に記載の半導体装置。 20

#### 【請求項6】

下面に第1接続端子が形成された第1半導体素子を準備する工程と、

下面に第2接続端子が形成された第2半導体素子を準備する工程と、

前記第1接続端子と電気的に接続される第1接続パッドと、前記第2接続端子と電気的に接続される第2接続パッドとを有する配線基板を準備する工程と、

放熱板を準備する工程と、 30

スペーサを準備する工程と、

前記放熱板の下面に、前記第1半導体素子を接合する工程と、

前記放熱板の下面に、前記スペーサを接合する工程と、

前記第1半導体素子と一部が上下に重なるように前記第1半導体素子の下面及び前記スペーサの下面に前記第2半導体素子を接合することで、実装部を形成する工程と、

前記第1接続パッド上に第3接続端子を形成する工程と、

前記配線基板に前記実装部を実装する工程と、

前記配線基板と前記放熱板との間にアンダーフィル樹脂を充填する工程と、

を有し、

前記実装部を実装する工程では、前記第1接続端子が前記第3接続端子を介して前記第1接続パッドと電気的に接続されるとともに、前記第2接続端子が前記第2接続パッドと電気的に接続され、 40

前記第1接続端子及び前記第3接続端子の一方が金属ポストであり、他方がはんだボールであり、

前記はんだボールは、球形状のコアボールと、前記コアボールの周囲を覆うはんだとを有するコア付きはんだボールである半導体装置の製造方法。

#### 【請求項7】

前記半導体装置の側面において、前記放熱板の側面よりも前記半導体装置の内方側に前記スペーサの側面が設けられ、前記スペーサの側面よりも前記半導体装置の内方側に前記第2半導体素子の側面が設けられることにより、前記放熱板の側面と前記スペーサの側面

と前記第2半導体素子の側面とが階段状に形成され、

前記アンダーフィル樹脂は、前記スペーサの側面と前記第2半導体素子の側面とを被覆するように形成される請求項6に記載の半導体装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置及び半導体装置の製造方法に関するものである。

**【背景技術】**

**【0002】**

近年、電子機器の小型化及び高機能化の要求に伴い、それに用いられるICやLSI等の半導体素子が高集積化され大容量化されてきている。そして、半導体素子を実装する半導体装置（パッケージ）についても、小型化、薄型化、高密度化が要求されている。そこで、このような要求に応えるべく、複数の半導体素子を1つの配線基板上に実装させたシステム・イン・パッケージ（System in Package：SiP）が実用化されている。10

**【0003】**

この種の半導体装置では、例えば、1つの配線基板上に複数の半導体素子が積層されて搭載されている（例えば、特許文献1，2参照）。複数の半導体素子と配線基板とを接続する方法としては、フリップチップ接続やワイヤボンディング接続などの各種の方法が採用されている。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【文献】特開2010-34436号公報**

特開2014-38880号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

ところで、上記半導体装置においては、配線基板と複数の半導体素子との接続信頼性を確保することが求められている。

**【課題を解決するための手段】**

**【0006】**

本発明の一観点によれば、半導体装置であって、放熱板と、前記放熱板の下面に搭載された第1半導体素子と、前記第1半導体素子の下面に形成された第1接続端子と、前記放熱板の下面に形成されたスペーサと、前記第1半導体素子と一部が上下に重なるように前記第1半導体素子の下面及び前記スペーサの下面に搭載された第2半導体素子と、前記第2半導体素子の下面に形成された第2接続端子と、前記第1接続端子と電気的に接続される第1接続パッドと、前記第2接続端子と電気的に接続される第2接続パッドとを有し、前記第1半導体素子及び前記第2半導体素子が実装された配線基板と、前記第1接続パッド上に形成され、前記第1接続端子と電気的に接続される第3接続端子と、前記配線基板と前記放熱板との間を充填するアンダーフィル樹脂と、を有し、前記第1接続端子及び前記第3接続端子の一方が金属ポストであり、他方がはんだボールであり、前記はんだボールは、球形状のコアボールと、前記コアボールの周囲を覆うはんだとを有するコア付きはんだボールであり、前記半導体装置の側面において、前記放熱板の側面よりも前記半導体装置の内方側に前記スペーサの側面が設けられ、前記スペーサの側面よりも前記半導体装置の内方側に前記第2半導体素子の側面が設けられることにより、前記放熱板の側面と前記スペーサの側面と前記第2半導体素子の側面とが階段状に形成されており、前記アンダーフィル樹脂は、前記スペーサの側面と前記第2半導体素子の側面とを被覆している。40

**【発明の効果】**

**【0007】**

本発明の一観点によれば、配線基板と複数の半導体素子との接続信頼性を向上できると

10

20

30

40

50

いう効果を奏する。

**【図面の簡単な説明】**

**【0008】**

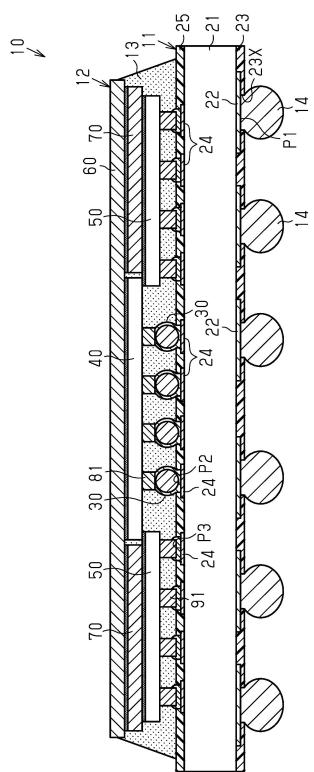

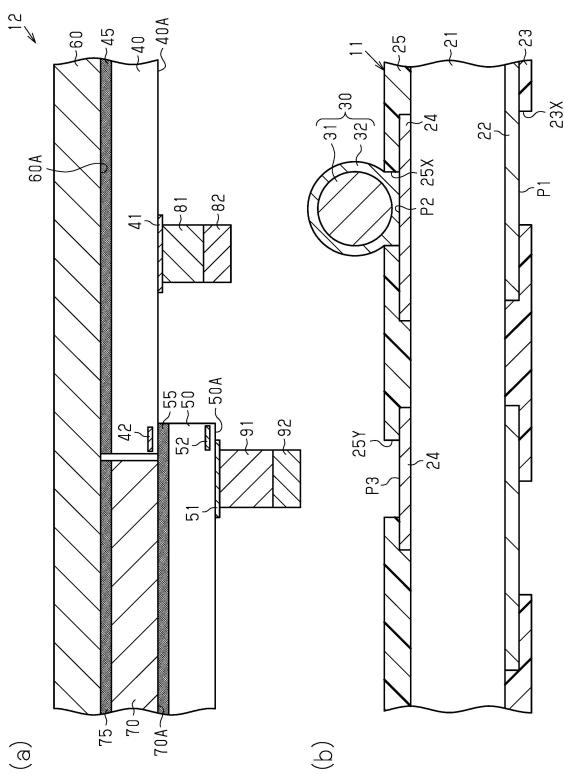

【図1】一実施形態の半導体装置を示す概略断面図（図3における1-1断面図）。

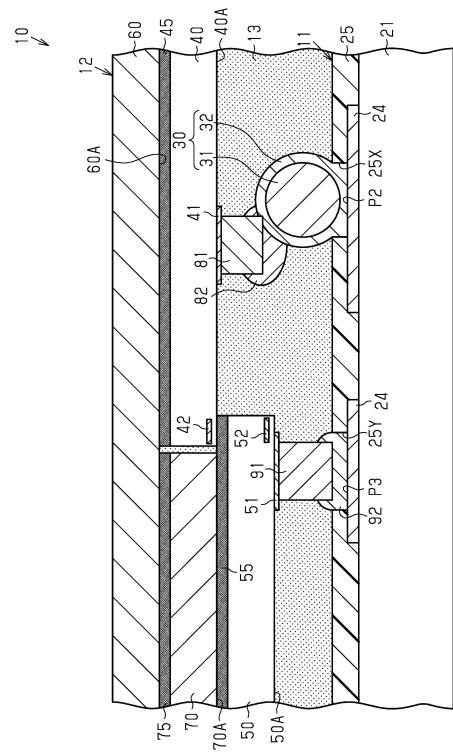

【図2】一実施形態の半導体装置を示す拡大断面図。

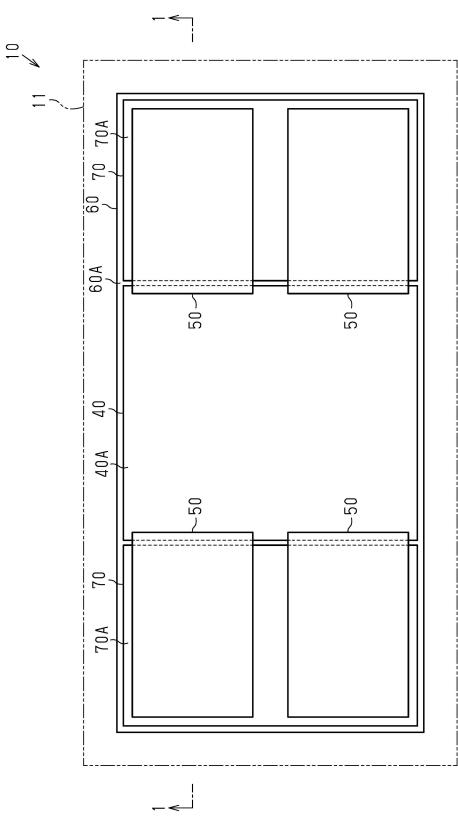

【図3】一実施形態の半導体装置を示す概略平面図。

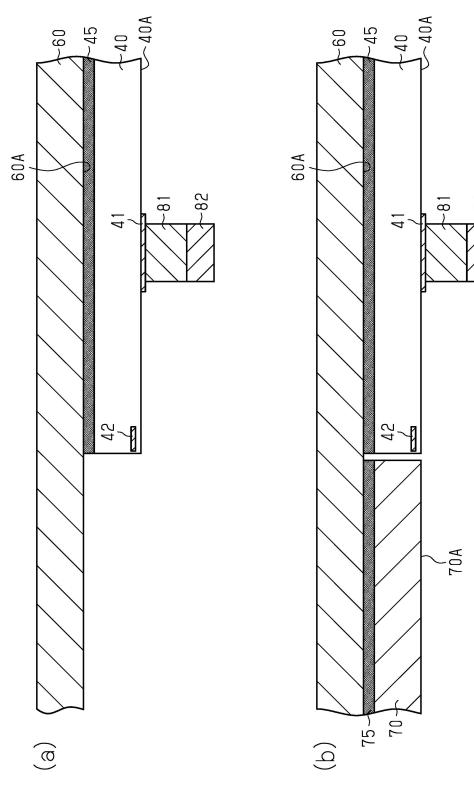

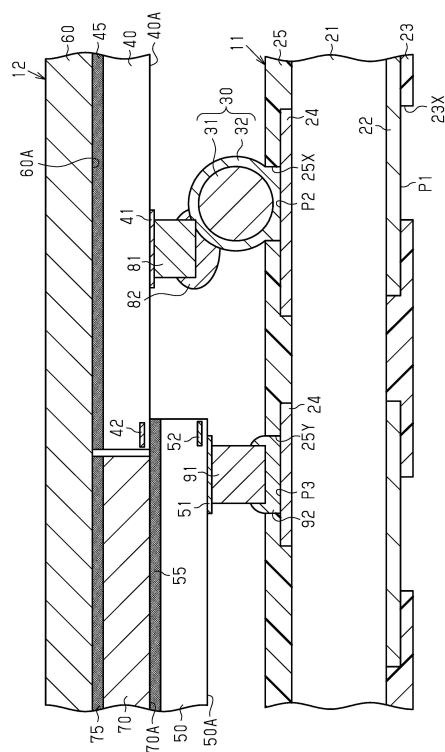

【図4】(a), (b)は、一実施形態の半導体装置の製造方法を示す拡大断面図。

【図5】(a), (b)は、一実施形態の半導体装置の製造方法を示す拡大断面図。

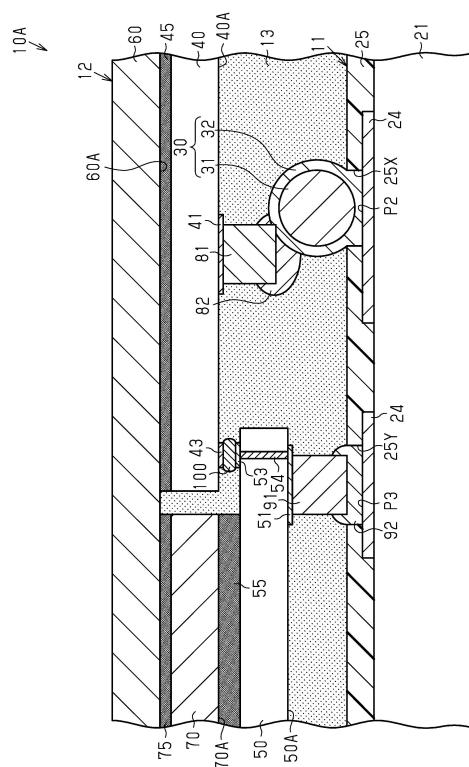

【図6】一実施形態の半導体装置の製造方法を示す拡大断面図。

【図7】変更例の半導体装置を示す拡大断面図。

10

**【発明を実施するための形態】**

**【0009】**

以下、一実施形態について添付図面を参照して説明する。

なお、添付図面は、便宜上、特徴を分かりやすくするために特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の部材のハッチングを梨地模様に代えて示し、一部の部材のハッチングを省略している。なお、本明細書において、「平面視」とは、対象物を図1等の鉛直方向（図中上下方向）から視ることを言い、「平面形状」とは、対象物を図1等の鉛直方向から視た形状のことを言う。

**【0010】**

20

まず、半導体装置10の構造について説明する。

図1に示すように、半導体装置10は、配線基板11と、配線基板11に実装された実装部12と、配線基板11と実装部12との間に形成されたアンダーフィル樹脂13とを有している。実装部12は、配線基板11に実装された半導体素子40と、配線基板11に実装された半導体素子50と、放熱板60とを有している。

**【0011】**

配線基板11は、基板本体21を有している。基板本体21の下面には、配線層22と、ソルダーレジスト層23とが順に積層されている。基板本体21の上面には、配線層24と、ソルダーレジスト層25とが順に積層されている。

**【0012】**

30

基板本体21としては、配線層22と配線層24とが基板内部を通じて相互に電気的に接続された構造を有していれば十分である。このため、基板本体21の内部には配線層が形成されていてもよく、配線層が形成されていなくてもよい。なお、基板本体21の内部に配線層が形成される場合には、例えば、複数の配線層が層間絶縁層を介して積層され、各配線層と各層間絶縁層に形成されたビアとによって配線層22と配線層24とが電気的に接続される。このような基板本体21としては、例えば、コア基板を有するコア付きビルドアップ基板やコア基板を有さないコアレス基板等を用いることができる。基板本体21としてコアレス基板を採用する場合には、例えば、最下層の配線層22の側面及び上面が基板本体21の最下層の絶縁層に埋め込まれ、その最下層の絶縁層から配線層22の下面が露出していてもよい。また、基板本体21の内部に配線層が形成されない場合には、例えば、基板本体21を厚さ方向に貫通する貫通電極によって配線層22と配線層24とが電気的に接続される。

40

**【0013】**

配線層22, 24の材料としては、例えば、銅(Cu)や銅合金を用いることができる。ソルダーレジスト層23, 25の材料としては、例えば、フェノール系樹脂やポリイミド系樹脂などを主成分とする感光性の絶縁性樹脂を用いることができる。ソルダーレジスト層23, 25は、例えば、シリカやアルミナ等のフィラーを含有していてもよい。

**【0014】**

配線層22は、基板本体21の下面に形成されている。配線層22は、例えば、基板本体21内の配線層や貫通電極を介して、配線層24と電気的に接続されている。配線層2

50

2は、例えば、配線基板11の最下層の配線層である。

**【0015】**

ソルダーレジスト層23は、配線層22の一部を被覆するように、基板本体21の下面に積層されている。ソルダーレジスト層23は、配線基板11の最外層（ここでは、最下層）の絶縁層である。ソルダーレジスト層23には、当該ソルダーレジスト層23を厚さ方向に貫通して配線層22の下面の一部を外部接続用パッドP1として露出させるための複数の開口部23Xが形成されている。外部接続用パッドP1には、外部接続端子14が形成されている。外部接続端子14は、例えば、図示しないマザーボード等の実装基板に設けられたパッドと電気的に接続される接続端子である。外部接続端子14としては、例えば、はんだボールやリードピンを用いることができる。本実施形態では、外部接続端子14として、はんだボールを用いている。10

**【0016】**

一方、配線層24は、基板本体21の上面に形成されている。配線層24は、例えば、配線基板11の最上層の配線層である。

ソルダーレジスト層25は、配線層24の一部を被覆するように、基板本体21の上面に積層されている。ソルダーレジスト層25は、配線基板11の最外層（ここでは、最上層）の絶縁層である。なお、配線層24の上面からソルダーレジスト層25の上面までの厚さは、例えば、5～25μm程度とすることができる。

**【0017】**

図2に示すように、ソルダーレジスト層25には、当該ソルダーレジスト層25を厚さ方向に貫通して配線層24の上面の一部を接続パッドP2として露出させるための複数の開口部25Xが形成されている。ソルダーレジスト層25には、当該ソルダーレジスト層25を厚さ方向に貫通して配線層24の上面の一部を接続パッドP3として露出させるための複数の開口部25Yが形成されている。接続パッドP2は、半導体素子40と電気的に接続される接続パッドである。接続パッドP2は、半導体素子40の電極パッド41に応じて配列されている。接続パッドP2は、例えば、半導体素子40の電極パッド41の各々に対向するように設けられている。接続パッドP3は、半導体素子50と電気的に接続される接続パッドである。接続パッドP3は、半導体素子50の電極パッド51に応じて配列されている。接続パッドP3は、例えば、半導体素子50の電極パッド51の各々に対向するように設けられている。20

**【0018】**

次に、図2及び図3に従って、実装部12の構造について説明する。なお、図3は、図1に示した半導体装置10を下方から見た平面図であり、配線基板11が透視的に描かれている。

**【0019】**

図3に示すように、放熱板60の下面60Aには、1つ又は複数（ここでは、1つ）の半導体素子40と、1つ又は複数（ここでは、2つ）のスペーサ70とが搭載（接合）されている。スペーサ70の下面70Aには、1つ又は複数（ここでは、4つ）の半導体素子50が搭載（接合）されている。半導体素子40は、例えば、放熱板60の下面60Aの平面視略中央部に設けられている。各スペーサ70は、放熱板60の下面60Aのうち半導体素子40よりも外側の外周領域に設けられている。2つのスペーサ70は、例えば、半導体素子40を両側（図3では左右両側）から挟むように設けられている。各半導体素子50は、例えば、その大部分がスペーサ70の下面70A上に設けられており、一部が半導体素子40の下面40A上に設けられている。40

**【0020】**

本実施形態では、放熱板60の平面形状が配線基板11の平面形状よりも小さい。半導体素子40の側面は、放熱板60の側面から半導体装置10の内方側に離間した（後退した）位置に設けられている。各スペーサ70の側面は、放熱板60の側面から半導体装置10の内方側に離間した位置に設けられている。各半導体素子50の側面は、放熱板60の側面から半導体装置10の内方側に離間した位置に設けられている。50

### 【0021】

放熱板60は、例えば、平面視矩形の板状に形成されている。放熱板60は、ヒートスペレッダとも呼ばれる。放熱板60は、例えば、半導体素子40が発する熱の密度を分散させる機能を有している。放熱板60は、半導体素子40, 50上に設けられているため、半導体素子40, 50を機械的に保護する機能も有している。放熱板60は、半導体素子40, 50を支持する支持基板としても機能している。放熱板60の材料としては、例えば、熱伝導率の良好な材料を用いることができる。例えば、放熱板60としては、銅(Cu)、銀(Ag)、アルミニウム(Al)又はそれらの合金で作製された基板を用いることができる。放熱板60としては、例えば、アルミナや窒化アルミニウム等のセラミックスやシリコン等の熱伝導率の高い絶縁材料や半導体材料で作製された基板を用いることもできる。放熱板60の材料としてシリコンを用いる場合には、例えば、絶縁性確保のために、シリコン表面に絶縁膜を形成してもよい。絶縁膜としては、例えば、シリコンの熱酸化処理によって形成されるシリコン酸化膜などを用いることができる。なお、放熱板60の厚さは、500~1000μm程度とすることができます。

10

### 【0022】

図2に示すように、半導体素子40は、例えば、接着層45を介して放熱板60の下面60Aに接着されている。接着層45は、放熱板60の下面60Aに接着するとともに、半導体素子40の上面に接着している。

20

### 【0023】

半導体素子40としては、例えば、CPU(Central Processing Unit)チップ、MPU(Micro Processing Unit)チップやGPU(Graphics Processing Unit)チップなどのロジックチップを用いることができる。また、半導体素子40としては、例えば、DRAM(Dynamic Random Access Memory)チップ、SRAM(Static Random Access Memory)チップやフラッシュメモリチップなどのメモリチップを用いることができる。本実施形態の半導体素子40はMPUチップである。

30

### 【0024】

半導体素子40の下面40Aには、電極パッド41が形成されている。例えば、半導体素子40は、シリコン(Si)等からなる薄板化された半導体基板上に、半導体集積回路(図示略)が形成された回路形成面(ここでは、下面40A)側が保護膜(図示略)で覆われ、その下面40Aに電極パッド41が配設された構造を有している。電極パッド41は、配線基板11に形成された接続パッドP2の各々に対向するように設けられている。電極パッド41の材料としては、例えば、銅、アルミニウム又はそれらの合金を用いることができる。

30

### 【0025】

本実施形態の半導体素子40は、コイル42を有している。例えば、半導体素子40の有する半導体集積回路内にコイル42が形成されている。すなわち、本実施形態の半導体素子40には、コイル42が内蔵されている。コイル42は、例えば、1回巻き以上の配線パターンによって構成することができる。

40

### 【0026】

なお、半導体素子40の平面形状は、任意の形状及び任意の大きさとすることができます。例えば、半導体素子40は、平面視矩形形状に形成されている。半導体素子40の大きさは、例えば、平面視で25mm×25mm程度とすることができます。半導体素子40の厚さは、例えば、500~1000μm程度とすることができます。

50

### 【0027】

接着層45としては、例えば、エポキシ系、ポリイミド系やシリコーン系等の熱硬化性の接着剤や、熱伝導部材(TIM: Thermal Interface Material)を用いることができる。熱伝導部材の材料としては、例えば、インジウム(In)、銀等の軟質金属、シリコーンゲル、又は金属フィラー、グラファイト等を含有した有機系の樹脂バインダー等を用いることができる。接着層45は、例えば、半導体素子40と放熱板60とを接着する機能と、半導体素子40と放熱板60とを熱的に接続する機能とを有している。なお、接着

層45の厚さは、例えば、20～50μm程度とすることができます。

#### 【0028】

各スペーサ70は、例えば、接着層75を介して放熱板60の下面60Aに接着されている。各接着層75は、放熱板60の下面60Aに接着するとともに、スペーサ70の上面に接着している。各スペーサ70の下面70Aは、半導体素子40の下面40Aと同一平面上に位置するように形成されている。すなわち、各スペーサ70の下面70Aと、半導体素子40の下面40Aとは略同一平面上に形成されている。各スペーサ70は、放熱板60の下面60Aと半導体素子50の上面との間の距離（離間距離）を規定値に保持する機能を有している。各スペーサ70は、例えば、半導体素子40及び接着層45と離間して設けられている。各接着層75は、例えば、半導体素子40及び接着層45と離間して設けられている。

10

#### 【0029】

各スペーサ70の材料としては、任意の材料を用いることができる。各スペーサ70の材料としては、例えば、良好な厚み精度が得られるように、高精度加工が可能な材料であることが好ましい。各スペーサ70の材料としては、例えば、アルミナや窒化アルミニウム等のセラミックスやシリコン等を用いることができる。また、各スペーサ70の材料としては、例えば、銅、銀、アルミニウム又はそれらの合金を用いることができる。なお、各スペーサ70の厚さは、例えば、500～1000μm程度とすることができます。

#### 【0030】

各接着層75としては、例えば、エポキシ系、ポリイミド系やシリコーン系等の熱硬化性の接着剤や、熱伝導部材を用いることができる。各接着層75の材料としては、接着層45と同じ材料であってもよいし、接着層45と異なる材料であってもよい。なお、各接着層75の厚さは、例えば、20～50μm程度とすることができます。

20

#### 【0031】

各半導体素子50は、例えば、接着層55を介してスペーサ70の下面70A及び半導体素子40の下面40Aに接着されている。各接着層55及び各半導体素子50は、スペーサ70と半導体素子40との間に架け渡されるように設けられている。例えば、各半導体素子50は、その大部分が接着層55を介してスペーサ70の下面70Aに接合されるとともに、その一部分が接着層55を介して半導体素子40の下面40Aに接合されている。図3に示すように、本実施形態では、各スペーサ70の下面70Aには、2つの半導体素子50が接合されており、半導体素子40の下面40Aには、4つの半導体素子50が接合されている。

30

#### 【0032】

各半導体素子50としては、例えば、DRAMチップ、SRAMチップやフラッシュメモリチップなどのメモリチップを用いることができる。また、各半導体素子50としては、例えば、CPUチップ、MPUチップやGPUチップなどのロジックチップを用いることができる。本実施形態の各半導体素子50はDRAMチップである。

#### 【0033】

図2に示すように、各半導体素子50の下面50Aには、電極パッド51が形成されている。例えば、各半導体素子50は、シリコン(Si)等からなる薄板化された半導体基板上に、半導体集積回路(図示略)が形成された回路形成面(ここでは、下面50A)側が保護膜(図示略)で覆われ、その下面50Aに電極パッド51が配設された構造を有している。電極パッド51は、配線基板11に形成された接続パッドP3の各々に対向するように設けられている。電極パッド51の材料としては、例えば、銅、アルミニウム又はそれらの合金を用いることができる。

40

#### 【0034】

本実施形態の半導体素子50は、コイル52を有している。例えば、半導体素子50の有する半導体集積回路内にコイル52が形成されている。すなわち、本実施形態の半導体素子50には、コイル52が内蔵されている。コイル52は、例えば、1回巻き以上の配線パターンによって構成することができる。半導体素子50は、内蔵されたコイル52が

50

半導体素子 4 0 に内蔵されたコイル 4 2 と平面視で重なるように配置されている。これら半導体素子 4 0 と半導体素子 5 0 は、例えば、データ送信側の半導体素子 4 0 のコイル 4 2 に電流を流して磁界を発生させ、その磁界を受信側の半導体素子 5 0 のコイル 5 2 で受信し、その磁界を電流に変換して情報を伝達する電磁誘導結合方式で接続されている。すなわち、半導体素子 4 0 と半導体素子 5 0 は、磁界結合されている。本実施形態の半導体素子 4 0 は、4 つの半導体素子 5 0 とそれぞれ磁界結合されている。

#### 【 0 0 3 5 】

なお、半導体素子 5 0 の平面形状は、任意の形状及び任意の大きさとすることができます。例えば、半導体素子 5 0 は、平面視矩形状に形成されている。半導体素子 5 0 の大きさは、例えば、平面視で  $20\text{ mm} \times 10\text{ mm}$  程度とすることができます。半導体素子 5 0 の厚さは、例えば、 $50 \sim 100\text{ }\mu\text{m}$  程度とすることができます。10

#### 【 0 0 3 6 】

接着層 5 5 としては、例えば、エポキシ系、ポリイミド系やシリコーン系等の熱硬化性の接着剤や、熱伝導部材を用いることができる。接着層 5 5 の材料としては、接着層 4 5 , 7 5 と同じ材料であってもよいし、接着層 4 5 , 7 5 と異なる材料であってもよい。なお、接着層 5 5 の厚さは、例えば、 $5 \sim 10\text{ }\mu\text{m}$  程度とすることができます。

#### 【 0 0 3 7 】

ここで、半導体装置 1 0 では、半導体素子 5 0 が半導体素子 4 0 の下面 4 0 A に搭載されているために、接続パッド P 2 と電極パッド 4 1 との離間距離が、接続パッド P 3 と電極パッド 5 1 との離間距離よりも長くなっている。このため、接続パッド P 2 と電極パッド 4 1 とを接続する接続部材の高さと、接続パッド P 3 と電極パッド 5 1 とを接続する接続部材の高さとが互いに異なる高さに設定される。なお、半導体素子 4 0 の下面 4 0 A からソルダーレジスト層 2 5 の上面までの離間距離は、例えば、 $100 \sim 300\text{ }\mu\text{m}$  程度とすることができます。半導体素子 5 0 の下面 5 0 A からソルダーレジスト層 2 5 の上面までの離間距離は、例えば、 $10 \sim 50\text{ }\mu\text{m}$  程度とすることができます。20

#### 【 0 0 3 8 】

次に、接続パッド P 2 と電極パッド 4 1 との接続構造、及び接続パッド P 3 と電極パッド 5 1 との接続構造について説明する。

電極パッド 4 1 の下面には、金属ポスト 8 1 が形成されている。金属ポスト 8 1 は、電極パッド 4 1 の下面から下方に延びる柱状の接続端子である。本例の金属ポスト 8 1 は、円柱状に形成されている。金属ポスト 8 1 の高さは、例えば、 $15 \sim 30\text{ }\mu\text{m}$  程度とすることができます。金属ポスト 8 1 の下面の直径は、例えば、 $60 \sim 150\text{ }\mu\text{m}$  程度とすることができます。金属ポスト 8 1 の材料としては、例えば、銅や銅合金を用いることができる。30

#### 【 0 0 3 9 】

接続パッド P 2 上には、コア付きはんだボール 3 0 が形成されている。すなわち、コア付きはんだボール 3 0 は、ソルダーレジスト層 2 5 から露出された配線層 2 4 の上面に搭載（接合）されている。本例のコア付きはんだボール 3 0 は、球形状の銅コアボール 3 1 と、その銅コアボール 3 1 の周囲を被覆するはんだ 3 2 を有している。コア付きはんだボール 3 0 （銅コアボール 3 1 及びはんだ 3 2 ）は、ソルダーレジスト層 2 5 の上面よりも上方に突出するように形成されている。本例のコア付きはんだボール 3 0 は、接続パッド P 2 よりも平面方向（つまり、配線基板 1 1 と実装部 1 2 とが積層される積層方向と直交する水平方向）に広がるように形成されている。銅コアボール 3 1 の高さ（直径）は例えば $50 \sim 150\text{ }\mu\text{m}$  程度とすることができます、はんだ 3 2 の厚さは例えば $5 \sim 20\text{ }\mu\text{m}$  程度とすることができます。また、コア付きはんだボール 3 0 の高さ（直径）は例えば $60 \sim 190\text{ }\mu\text{m}$  程度とすることができます。40

#### 【 0 0 4 0 】

半導体素子 4 0 の電極パッド 4 1 は、金属ポスト 8 1 及びコア付きはんだボール 3 0 を介して、配線基板 1 1 の接続パッド P 2 と電気的に接続されている。すなわち、半導体素子 4 0 と配線基板 1 1 とを電気的に接続する接続部材は、金属ポスト 8 1 とコア付きはんだボール 3 0 とが積層された構造を有している。本例の金属ポスト 8 1 は、はんだ層 8 2

10

20

30

40

50

を介してコア付きはんだボール30に接合されている。はんだ層82は、金属ポスト81に接合されるとともに、コア付きはんだボール30のはんだ32に接合されている。これにより、電極パッド41は、金属ポスト81、はんだ層82及びコア付きはんだボール30を介して、接続パッドP2と電気的に接続されている。

#### 【0041】

なお、はんだ層82としては、例えば、鉛フリーはんだのはんだめっきを用いることができる。はんだめっきの材料としては、例えば、錫(Sn) - Ag系、Sn - Cu系、Sn - Ag - Cu系、Sn - ビスマス(Bi)系の鉛フリーはんだを用いることができる。また、図2では、はんだ層82とコア付きはんだボール30のはんだ32とを分かり易くするために、両者を実線にて区別している。但し、実際には、はんだ層82とはんだ32との界面は消失していることがあり、境界が明確ではないことがある。

10

#### 【0042】

半導体素子50の電極パッド51の下面には、金属ポスト91が形成されている。金属ポスト91は、電極パッド51の下面から下方に延びる柱状の接続端子である。本例の金属ポスト91は、円柱状に形成されている。金属ポスト91の高さは、例えば、15~30μm程度とすることができる。金属ポスト91の高さは、例えば、金属ポスト81の高さと異なる高さであってもよいし、金属ポスト81の高さと同じ高さであってもよい。金属ポスト91の下面の直径は、例えば、60~150μm程度とすることができる。金属ポスト91の材料としては、例えば、銅や銅合金を用いることができる。

20

#### 【0043】

半導体素子50の電極パッド51は、金属ポスト91を介して、配線基板11の接続パッドP3と電気的に接続されている。本例の金属ポスト91は、はんだ層92を介して接続パッドP3に接合されている。はんだ層92は、接続パッドP3に接合されるとともに、金属ポスト91に接合されている。これにより、半導体素子50の電極パッド51は、金属ポスト91及びはんだ層92を介して配線基板11の接続パッドP3と電気的に接続されている。このように、本実施形態では、半導体素子50の電極パッド51と配線基板11の接続パッドP3とを電気的に接続する接続部材が、金属ポスト91とはんだ層92とによって構成されており、コア付きはんだボールを含まない構成となっている。

30

#### 【0044】

なお、はんだ層92としては、例えば、鉛フリーはんだのはんだめっきを用いることができる。はんだめっきの材料としては、例えば、Sn - Ag系、Sn - Cu系、Sn - Ag - Cu系、Sn - Bi系の鉛フリーはんだを用いることができる。

#### 【0045】

図1に示すように、配線基板11と実装部12との間には、アンダーフィル樹脂13が充填されている。アンダーフィル樹脂13は、半導体素子40と配線基板11との間の空間、各半導体素子50と配線基板11との間の空間、及び放熱板60と配線基板11との間の空間を充填するように形成されている。アンダーフィル樹脂13の材料としては、例えば、エポキシ系樹脂などの絶縁性樹脂を用いることができる。

#### 【0046】

以上説明した半導体装置10は、天地逆の状態で用いることができ、又は任意の角度で配置することができる。

40

本実施形態において、半導体素子40は第1半導体素子の一例、金属ポスト81は第1接続端子の一例、半導体素子50は第2半導体素子の一例、金属ポスト91は第2接続端子の一例である。また、接続パッドP2は第1接続パッドの一例、接続パッドP3は第2接続パッドの一例、コア付きはんだボール30は第3接続端子及びはんだボールの一例、銅コアボール31はコアボールの一例である。

#### 【0047】

次に、半導体装置10の製造方法について説明する。なお、説明の便宜上、最終的に半導体装置10の各構成要素となる部分には、最終的な構成要素の符号を付して説明する。

図4(a)に示すように、まず、放熱板60を準備するとともに、電極パッド41の下

50

面に金属ポスト 8 1 及びはんだ層 8 2 が形成された半導体素子 4 0 を準備する。半導体素子 4 0 は、公知の製造方法により製造することが可能であるため、図示を省略して詳細な説明を割愛するが、例えば以下のような方法で製造される。

#### 【0048】

まず、所要の大きさのシリコンウェハに対し、その一方の面側に所要のデバイスプロセスを施して複数のデバイス（例えば、CPU 等の能動素子）をアレイ状に作り込む。そのデバイスが形成されている側の面に窒化シリコン（SiN）やリンガラス（PSG）等からなる保護膜（図示略）を形成する。続いて、各デバイス上に所要のパターンで形成された電極パッド 4 1 に対応する部分の保護膜をレーザ等により除去し、その保護膜の下面及び電極パッド 4 1 の下面を被覆するようにシード層を形成する。次いで、金属ポスト 8 1 の形成領域に対応する部分のシード層を露出させたレジスト層を形成する。次に、レジスト層から露出されたシード層上に、そのシード層を給電層に利用する電解めっき法（例えば、電解銅めっき法）を施すことにより、電極パッド 4 1 の下面に柱状の金属ポスト 8 1 を形成する。続いて、金属ポスト 8 1 の下面に、はんだ層 8 2 を形成する。このはんだ層 8 2 は、例えば、シード層上に形成されたレジスト層をめっきマスクに利用し、シード層をめっき給電層に利用する電解はんだめっき法により、金属ポスト 8 1 の下面にはんだを披着することにより形成することができる。その後、不要なシード層及びレジスト層を除去する。次いで、シリコンウェハを所定の厚さ（例えば、500 ~ 1000 μm 程度）に研削した後、ダイサー等により各デバイス単位（例えば、25 mm × 25 mm のサイズ）に個片化する。以上の工程により、回路形成面である下面 4 0 A に電極パッド 4 1 が形成され、その電極パッド 4 1 の下面に金属ポスト 8 1 及びはんだ層 8 2 が形成された半導体素子 4 0 を得ることができる。10

#### 【0049】

次に、図 4 (a) に示す工程では、放熱板 6 0 の下面 6 0 A に半導体素子 4 0 を接合する。例えば、まず、放熱板 6 0 の下面 6 0 A に接着層 4 5 を形成する。接着層 4 5 は、例えば、接着層 4 5 となる液状樹脂やペースト状樹脂を放熱板 6 0 の下面 6 0 A に塗布することで形成することができる。例えば、本工程における接着層 4 5 は、A - ステージのものが使用される。なお、本工程における接着層 4 5 として、半硬化状態（B - ステージ）のものを用いるようにしてもよい。続いて、マウンタ等を用いて、接着層 4 5 上に半導体素子 4 0 を搭載する。このとき、半導体素子 4 0 は、回路形成面である下面 4 0 A とは反対側の上面（つまり、背面）が接着層 4 5 の下面に接するように搭載される。次いで、半導体素子 4 0 を放熱板 6 0 側に押圧し、熱圧着により半導体素子 4 0 を放熱板 6 0 の下面 6 0 A に接合する。20

#### 【0050】

続いて、図 4 (b) に示す工程では、放熱板 6 0 の下面 6 0 A にスペーサ 7 0 を接合する。例えば、まず、放熱板 6 0 の下面 6 0 A に接着層 7 5 を形成する。接着層 7 5 は、例えば、接着層 4 5 と同様の製造方法により形成することができる。続いて、接着層 7 5 上にスペーサ 7 0 を搭載する。次いで、スペーサ 7 0 を放熱板 6 0 側に押圧し、熱圧着によりスペーサ 7 0 を放熱板 6 0 に接合する。このとき、スペーサ 7 0 の下面 7 0 A が半導体素子 4 0 の下面 4 0 A と同一平面上に位置するように、スペーサ 7 0 が放熱板 6 0 の下面 6 0 A に接合される。30

#### 【0051】

次に、図 5 (a) に示す工程では、電極パッド 5 1 の下面に金属ポスト 9 1 及びはんだ層 9 2 が形成された半導体素子 5 0 を準備する。なお、半導体素子 5 0 は、半導体素子 4 0 と同様の製造方法により形成することができる。40

#### 【0052】

続いて、スペーサ 7 0 の下面 7 0 A 及び半導体素子 4 0 の下面 4 0 A に半導体素子 5 0 を接合する。例えば、まず、スペーサ 7 0 の下面 7 0 A 及び半導体素子 4 0 の下面 4 0 A に接着層 5 5 を形成する。接着層 5 5 は、例えば、接着層 4 5 と同様の製造方法により形成することができる。続いて、マウンタ等を用いて、接着層 5 5 上に半導体素子 5 0 を搭

10

20

30

40

50

載する。このとき、半導体素子 50 は、回路形成面である下面 50A とは反対側の上面（つまり、背面）が接着層 55 の下面に接するように搭載される。また、半導体素子 50 は、自身に内蔵されたコイル 52 が半導体素子 40 に内蔵されたコイル 42 と平面視で重なるように半導体素子 40 の下面 40A に搭載される。次いで、半導体素子 50 をスペーサ 70 及び半導体素子 40 側に押圧し、熱圧着により半導体素子 50 をスペーサ 70 及び半導体素子 40 に接合する。本工程により、半導体素子 50 の一部が半導体素子 40 と上下に重なるように、半導体素子 40 の下面 40A に半導体素子 50 が搭載される。

#### 【 0 0 5 3 】

以上の製造工程により、図 1 に示した実装部 12 を製造することができる。

次に、図 5 ( b ) に示す工程では、配線基板 11 を準備する。配線基板 11 は、公知の製造方法により製造することが可能であるため、図示を省略して詳細な説明を割愛するが、例えば以下のような方法で製造される。

#### 【 0 0 5 4 】

まず、基板本体 21 の下面に配線層 22 が形成され、基板本体 21 の上面に配線層 24 が形成された構造体を準備する。続いて、配線層 22 の所要の箇所に画定される外部接続用パッド P1 を露出させるための開口部 23X を有するソルダーレジスト層 23 を基板本体 21 の下面に積層する。また、配線層 24 の所要の箇所に画定される接続パッド P2, P3 をそれぞれ露出させるための開口部 25X, 25Y を有するソルダーレジスト層 25 を基板本体 21 の上面に積層する。これらソルダーレジスト層 23, 25 は、例えば、感光性のソルダーレジストフィルムをラミネートし、又は液状のソルダーレジストを塗布し、当該レジストを所要の形状にパターニングすることにより形成することができる。

#### 【 0 0 5 5 】

なお、必要に応じて、外部接続用パッド P1 上及び接続パッド P2, P3 上に表面処理層を形成するようにしてもよい。表面処理層の例としては、金 (Au) 層、ニッケル (Ni) 層 / Au 層 (Ni 層と Au 層をこの順番で積層した金属層)、Ni 层 / パラジウム (Pd) 层 / Au 層 (Ni 层と Pd 层と Au 層をこの順番で積層した金属層) などを挙げることができる。このような表面処理層は、例えば、無電解めっき法により形成することができる。また、外部接続用パッド P1 上及び接続パッド P2, P3 上に、OSP (Organic Solderability Preservative) 処理などの酸化防止処理を施して表面処理層を形成するようにしてもよい。以上の製造工程により、図 1 に示した配線基板 11 を製造することができる。

#### 【 0 0 5 6 】

続いて、接続パッド P2 上に、コア付きはんだボール 30 を搭載（接合）する。例えば、接続パッド P2 上に適宜フラックスを塗布した後、コア付きはんだボール 30 を搭載し、230 ~ 260 度の温度でリフローして接続パッド P2 上にコア付きはんだボール 30 を固定する。その後、表面を洗浄してフラックスを除去する。

#### 【 0 0 5 7 】

次いで、図 6 に示す工程では、配線基板 11 に実装部 12 を実装する。まず、配線基板 11 の上方に、半導体素子 40, 50 及び放熱板 60 を有する実装部 12 を配置する。具体的には、金属ポスト 81 (電極パッド 41) と接続パッド P2 とが対向するように、且つ、金属ポスト 91 (電極パッド 51) と接続パッド P3 とが対向するように、実装部 12 を位置決めする。続いて、はんだ層 82 を介して金属ポスト 81 をコア付きはんだボール 30 に接合するとともに、はんだ層 92 を介して金属ポスト 91 を接続パッド P3 に接合する。例えば、実装部 12 を、金属ポスト 81, 91 及びコア付きはんだボール 30 等を間に挟んだ状態で配線基板 11 の上に配置し、それら重ね合わされた配線基板 11 及び実装部 12 をリフロー炉で 230 ~ 260 度の温度で加熱する。このリフロー処理は、例えば、実装部 12 を配線基板 11 に対して押圧しながら行われる。このようなリフロー処理により、はんだ層 82 及びコア付きはんだボール 30 のはんだ 32 が溶融して合金となり、それらはんだ層 82 及びコア付きはんだボール 30 が金属ポスト 81 及び接続パッド P2 に接合される。これにより、金属ポスト 81 と接続パッド P2 とがはんだ層 82

10

20

30

40

50

及びコア付きはんだボール30を介して電気的に接続される。また、リフロー処理により、はんだ層92が溶融し、はんだ層92が金属ポスト91及び接続パッドP3に接合される。これにより、金属ポスト91と接続パッドP3とがはんだ層92を介して電気的に接続される。

#### 【0058】

ここで、本工程では、製造誤差や搭載精度等に起因して、図6に示すように、金属ポスト81と接続パッドP2との平面位置（水平方向の位置）がずれる場合がある。このとき、接続パッドP2上にコア付きはんだボール30が形成されており、そのコア付きはんだボール30の外周には球状にはんだ32が形成されている。このように、接続パッドP2上に形成されたはんだ32が、平面方向に広がるように、且つ立体的（3次元的）に形成されている。このため、金属ポスト81と接続パッドP2との平面位置がずれた場合であっても、そのずれ量をコア付きはんだボール30で吸収することができる。これにより、金属ポスト81と接続パッドP2との平面位置がずれた場合であっても、コア付きはんだボール30を介して金属ポスト81と接続パッドP2との電気的接続を良好に行うことができる。

#### 【0059】

その後、実装部12と配線基板11との間に、図1に示したアンダーフィル樹脂13を充填し、そのアンダーフィル樹脂13を硬化する。また、外部接続用パッドP1上に、図1に示した外部接続端子14を形成する。

#### 【0060】

以上の製造工程により、図1に示した半導体装置10を製造することができる。

次に、本実施形態の作用効果を説明する。

(1) 半導体素子40とその半導体素子40の下面40Aに搭載された半導体素子50とを配線基板11に実装し、その配線基板11と半導体素子40とを電気的に接続する接続部材を、金属ポスト81とコア付きはんだボール30とを積層した構造とした。この構成によれば、コア付きはんだボール30の外周に球状にはんだ32が形成されており、はんだ32が平面方向に広がるように、且つ立体的（3次元的）に形成されている。このため、金属ポスト81と接続パッドP2との平面位置がずれた場合であっても、そのずれ量をコア付きはんだボール30で吸収することができる。これにより、金属ポスト81と接続パッドP2との平面位置がずれた場合であっても、コア付きはんだボール30を介して金属ポスト81と接続パッドP2とを電気的に接続することができる。この結果、金属ポスト81と接続パッドP2が互いに離間して電気的に接続されない、所謂オープン不良が発生することを好適に抑制でき、配線基板11と半導体素子40との接続信頼性を向上させることができる。

#### 【0061】

(2) また、金属ポスト81とコア付きはんだボール30とを組み合わせたことにより、金属ポスト81のみで配線基板11と半導体素子40とを接続する場合に比べて、金属ポスト81の高さを抑えることができる。これにより、金属ポスト81を形成するための製造時間（例えば、めっき時間）を短縮することができ、半導体装置10の生産性を向上させることができる。

#### 【0062】

(3) 半導体素子40と一部が上下に重なるように半導体素子40の下面40Aに半導体素子50を搭載するようにした。これにより、半導体装置10が平面方向に大型化することを抑制することができる。

#### 【0063】

(4) 半導体素子40の上面に放熱板60を搭載するようにした。これにより、半導体素子40が放熱板60に熱結合されるため、半導体素子40から発生した熱が放熱板60に放熱される。このため、半導体素子40から発生した熱を効率良く放熱させることができ、半導体素子40の温度上昇を抑制することができる。

#### 【0064】

10

20

30

40

50

(5) 放熱板60の下面60Aにスペーサ70を搭載し、そのスペーサ70の下面70Aに半導体素子50を搭載するようにした。このスペーサ70を設けたことにより、積層方向(図1等の上下方向)における半導体素子50の位置精度を向上させることができる。

#### 【0065】

(6) スペーサ70の下面70Aを、半導体素子40の下面40Aと同一平面上に位置するように形成し、スペーサ70の下面70A及び半導体素子40の下面40Aに半導体素子50を搭載するようにした。これにより、スペーサ70の下面70Aと半導体素子40の下面40Aとが同一平面上に形成されているため、それら下面70A, 40A上に搭載された半導体素子50が積層方向(図1等の上下方向)に傾くことを好適に抑制できる。

#### 【0066】

(7) 半導体素子40にコイル42を形成し、半導体素子50にコイル52を形成し、半導体素子40のコイル42と半導体素子50のコイル52とを磁界結合するようにした。この構成によれば、コイル42とコイル52とが上下に重なるように半導体素子40, 50を上下に重なることで、半導体素子40と半導体素子50とを接続することができる。

#### 【0067】

(8) 半導体装置10の側面において、放熱板60の側面から半導体装置10の内方側に離間した位置にスペーサ70の側面を設け、スペーサ70の側面から半導体装置10の内方側に離間した位置に半導体素子50の側面を設けた。これにより、放熱板60の側面とスペーサ70の側面と半導体素子50の側面とが階段状に形成される。したがって、半導体装置10の側面において、放熱板60とスペーサ70と半導体素子50との各側面が面一に形成される場合と比べて、放熱板60とスペーサ70と半導体素子50とに対するアンダーフィル樹脂13の接触面積を増大させることができる。このため、放熱板60とスペーサ70と半導体素子50とに対するアンダーフィル樹脂13の密着性を向上させることができる。この結果、アンダーフィル樹脂13による半導体素子40, 50と配線基板11との接続部分の保護を確実に行うことができ、半導体装置10の信頼性を向上させることができる。

#### 【0068】

##### (他の実施形態)

上記実施形態は、以下のように変更して実施することができる。上記実施形態及び以下の変更例は、技術的に矛盾しない範囲で互いに組み合わせて実施することができる。

#### 【0069】

- 上記実施形態では、半導体素子40, 50を磁界結合するようにしたが、半導体素子40, 50の接続方法はこれに限定されない。

例えば図7に示すように、半導体素子40と半導体素子50とを電気的に接続するようにしてもよい。図7に示した半導体装置10Aでは、半導体素子40の下面40Aに配線パターン43が形成されており、半導体素子50の上面に配線パターン53が形成されている。配線パターン53は、例えば、半導体素子50を厚さ方向に貫通する貫通電極54を介して電極パッド51と電気的に接続されている。半導体素子50は、一部が半導体素子40と上下に重なるように半導体素子40の下面40Aに搭載されている。具体的には、半導体素子50の配線パターン53がバンプ100を介して半導体素子40の配線パターン43と電気的に接続されている。これにより、半導体素子40の配線パターン43は、バンプ100、配線パターン53及び貫通電極54を介して電極パッド51と電気的に接続されている。なお、バンプ100は、例えば、はんだバンプである。

#### 【0070】

図7に示した例では、接着層55を厚く形成することにより、配線パターン43、バンプ100及び配線パターン53が配設される空間を確保している。これに限らず、例えばスペーサ70や接着層75の厚さを調整することにより、配線パターン43、バンプ100及び配線パターン53が配設される空間を確保するようにしてもよい。

#### 【0071】

- 上記実施形態における半導体素子40, 50は配線基板11と電気的に接続されてい

10

20

30

40

50

れば、半導体素子 4 0 と半導体素子 5 0 とは接続されていなくてもよい。

・上記実施形態のコア付きはんだボール 3 0 の導電性コアボールとして銅コアボール 3 1 を用いるようにした。これに限らず、銅コアボール 3 1 の代わりに、例えば金やニッケル等の銅以外の金属により形成した導電性コアボールを用いるようにしてもよいし、樹脂により形成した樹脂コアボールを用いるようにしてもよい。あるいは、コア付きはんだボール 3 0 の代わりに、導電性コアボールや樹脂コアボールなどのコアボールを省略したはんだボールを用いるようにしてもよい。

#### 【 0 0 7 2 】

・上記実施形態では、半導体素子 4 0 の電極パッド 4 1 上に形成された第 1 接続端子を金属ポスト 8 1 に具体化し、配線基板 1 1 の接続パッド P 2 上に形成された第 3 接続端子をコア付きはんだボール 3 0 に具体化したが、これに限定されない。例えば、半導体素子 4 0 の電極パッド 4 1 上に形成された第 1 接続端子をコア付きはんだボール 3 0 に具体化し、配線基板 1 1 の接続パッド P 2 上に形成された第 3 接続端子を金属ポスト 8 1 に具体化してもよい。

10

#### 【 0 0 7 3 】

・上記実施形態におけるはんだ層 8 2 , 9 2 を省略してもよい。

・上記実施形態では、接着層 4 5 , 5 5 , 7 5 として、液状樹脂やペースト状樹脂を用いるようにした。これに限らず、例えば、接着層 4 5 , 5 5 , 7 5 として、半硬化状態 (B - ステージ) のフィルム状の接着剤 (接着フィルム) を用いるようにしてもよい。接着フィルムとしては、例えば、エポキシ系、ポリイミド系、シリコーン系等の熱硬化性の接着剤を用いることができる。接着層 4 5 , 5 5 , 7 5 として接着フィルムを用いた場合の製造方法について以下に説明する。

20

#### 【 0 0 7 4 】

はじめに、半導体素子 4 0 を放熱板 6 0 の下面 6 0 A に接合する方法の一例を説明する。まず、半導体素子 4 0 となるシリコンウェハに金属ポスト 8 1 及びはんだ層 8 2 を形成し、シリコンウェハを所定の厚さに研削した後、シリコンウェハの背面に半硬化状態の接着フィルムを貼付して接着層 4 5 を形成する。続いて、シリコンウェハをダイシングすることにより、背面に接着層 4 5 を有する個々の半導体素子 4 0 に分割する。次いで、放熱板 6 0 の下面 6 0 A に対して半導体素子 4 0 の背面側を加熱しながら押圧することで接着層 4 5 を硬化させ、半導体素子 4 0 を放熱板 6 0 の下面 6 0 A に接合する。

30

#### 【 0 0 7 5 】

次に、スペーサ 7 0 を放熱板 6 0 の下面 6 0 A に接合する方法の一例を説明する。

まず、スペーサ 7 0 となる大判の基板の背面に半硬化状態の接着フィルムを貼付して接着層 7 5 を形成する。続いて、大判の基板を切断し、背面 (図 4 ( b ) では、上面) に接着層 7 5 を有する個々のスペーサ 7 0 に分割する。次いで、放熱板 6 0 の下面 6 0 A に対してスペーサ 7 0 の背面側を加熱しながら押圧することで接着層 7 5 を硬化させ、スペーサ 7 0 を放熱板 6 0 の下面 6 0 A に接合する。

#### 【 0 0 7 6 】

次に、半導体素子 5 0 をスペーサ 7 0 及び半導体素子 4 0 に接合する方法の一例を説明する。

40

まず、半導体素子 5 0 となるシリコンウェハに金属ポスト 9 1 及びはんだ層 9 2 を形成し、シリコンウェハを所定の厚さに研削した後、シリコンウェハの背面に半硬化状態の接着フィルムを貼付して接着層 5 5 を形成する。続いて、シリコンウェハをダイシングすることにより、背面に接着層 5 5 を有する個々の半導体素子 5 0 に分割する。次いで、スペーサ 7 0 の下面 7 0 A と半導体素子 4 0 の下面 4 0 A とに対して半導体素子 5 0 の背面側を加熱しながら押圧することで接着層 5 5 を硬化させ、半導体素子 5 0 をスペーサ 7 0 の下面 7 0 A 及び半導体素子 4 0 の下面 4 0 A に接合する。

#### 【 0 0 7 7 】

・上記実施形態における接着層 4 5 と接着層 7 5 とを一体に形成するようにしてもよい。

・上記実施形態では、放熱板 6 0 の下面 6 0 A に接着層 4 5 により半導体素子 4 0 を接

50

合した後に、放熱板 6 0 の下面 6 0 A に接着層 7 5 によりスペーサ 7 0 を接合するようにした。これに限らず、例えば、放熱板 6 0 の下面 6 0 A に、半導体素子 4 0 とスペーサ 7 0 とを同時に接合するようにしてもよい。この場合には、例えば、接着層 4 5 と接着層 7 5 とが同時に熱硬化される。

#### 【 0 0 7 8 】

・上記実施形態におけるスペーサ 7 0 を省略してもよい。この場合には、例えば、半導体素子 5 0 の上面と放熱板 6 0 との間の空間がアンダーフィル樹脂 1 3 によって充填される。

#### 【 0 0 7 9 】

・上記実施形態における放熱板 6 0 を省略してもよい。

・上記実施形態におけるアンダーフィル樹脂 1 3 を省略してもよい。

・上記実施形態では、半導体素子 4 0 をロジックチップに具体化し、半導体素子 5 0 をメモリチップに具体化した。これに限らず、例えば、半導体素子 4 0 をメモリチップに具体化し、半導体素子 5 0 をロジックチップに具体化してもよい。

#### 【 0 0 8 0 】

・上記実施形態では、1つの配線基板 1 1 に、M P U チップである半導体素子 4 0 と、D R A M チップである半導体素子 5 0 とを実装するようにした。すなわち、1つの配線基板 1 1 に、ロジックチップとメモリチップとを組み合わせて搭載するようにした。これに限らず、半導体素子 4 0 , 5 0 の双方をロジックチップに具体化してもよいし、半導体素子 4 0 , 5 0 の双方をメモリチップに具体化してもよい。

#### 【 0 0 8 1 】

・上記実施形態では、半導体素子 4 0 の下面 4 0 A に搭載された複数の半導体素子 5 0 を全て D R A M チップに具体化した。これに限らず、複数の半導体素子 5 0 として、複数種類のチップ、例えば D R A M チップ、S R A M チップや C P U チップなどを組み合わせて採用するようにしてもよい。

#### 【 符号の説明 】

#### 【 0 0 8 2 】

1 0 , 1 0 A 半導体装置

1 1 配線基板

1 2 実装部

1 3 アンダーフィル樹脂

3 0 コア付きはんだボール

3 1 銅コアボール

3 2 はんだ

4 0 半導体素子

4 1 電極パッド

4 2 コイル

5 0 半導体素子

5 1 電極パッド

5 2 コイル

6 0 放熱板

7 0 スペーサ

8 1 金属ポスト

8 2 はんだ層

9 1 金属ポスト

9 2 はんだ層

P 2 接続パッド

P 3 接続パッド

10

20

30

40

50

## 【図面】 【図 1】

【図2】

【 四 3 】

【図4】

10

20

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

50

---

フロントページの続き

(51)国際特許分類 F I

H 01 L 21/60 (2006.01)

- (56)参考文献 特表2014-512691 (JP, A)

特開2014-049477 (JP, A)

特開2014-038880 (JP, A)

米国特許出願公開第2015/0236002 (US, A1)

特表2013-520835 (JP, A)

特開2006-108130 (JP, A)

特開2015-122445 (JP, A)

特開2014-049476 (JP, A)

特開2007-096025 (JP, A)

特開2012-169586 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

H 01 L 25/07

H 01 L 23/12

H 01 L 23/36

H 01 L 21/60