(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4743983号

(P4743983)

(45) 発行日 平成23年8月10日(2011.8.10)

(24) 登録日 平成23年5月20日(2011.5.20)

(51) Int.Cl.

H01L 27/148 (2006.01)

F 1

H01L 27/14

B

請求項の数 3 (全 9 頁)

(21) 出願番号 特願2001-81327 (P2001-81327)

(22) 出願日 平成13年3月21日 (2001.3.21)

(65) 公開番号 特開2001-326344 (P2001-326344A)

(43) 公開日 平成13年11月22日 (2001.11.22)

審査請求日 平成20年3月10日 (2008.3.10)

(31) 優先権主張番号 09/533051

(32) 優先日 平成12年3月22日 (2000.3.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000846

イーストマン コダック カンパニー

アメリカ合衆国 ニューヨーク州 ロ彻

スター ステート ストリート 343

(74) 代理人 100075258

弁理士 吉田 研二

(74) 代理人 100096976

弁理士 石田 純

(72) 発明者 エリック ゴードン スティーブンス

アメリカ合衆国 ニューヨーク州 ロ彻

スター シナバー ロード 168

(72) 発明者 ウィリアム エフ デジタルダン

アメリカ合衆国 ニューヨーク州 ホリー

ホリー バイロン ロード 5074

最終頁に続く

(54) 【発明の名称】電荷結合イメージセンサ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

行と列とのアレイ状に配列された複数のピクセルと、

前記列を形成するのに用いられ、前記ピクセルを定義する複数の垂直電荷結合素子シフ

トレジスタと、

前記各ピクセルに対して少なくとも一つが配置され、上方に形成された複数の相電極(

$1, 2$ )と、

を備え、

少なくとも一個の前記相電極( $1, 2$ )は、ホールを有し、前記各ホール内には、

前記ホールを有する相電極( $1, 2$ )のすぐ次の層の電極材料より形成された掃き出

し電極が配置され、

前記掃き出し電極は、それぞれのピクセルから、前記掃き出し電極に隣接して配置され

たドレインに電荷を完全に転送する、

ことを特徴とする電荷結合イメージセンサ装置。

## 【請求項 2】

請求項1に記載の電荷結合イメージセンサ装置であって、前記各ドレインが基板内に埋

設されたラテラル・オーバーフロードレイン構造であることを特徴とする電荷結合イメ

ジセンサ装置。

## 【請求項 3】

請求項1に記載の電荷結合イメージセンサ装置であって、前記各ホールがバリア・イン

プラント領域の上方に形成されることを特徴とする電荷結合イメージセンサ装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明の分野は一般に、デバイスのメインアレイから電荷を選択的に掃き出しするのに用いることができる固体イメージセンサ用高速掃き出し構造に関する。特に本発明は、フレームトランスファー型またはフル・フレーム型のイメージセンサに関するが、このイメージセンサはラテラル・オーバーフロードレイン（L O D）を用いてブルーミングを抑圧する。

【0002】

10

【従来の技術】

従来、高速掃き出し構造は、通常垂直C C Dと水平C C Dとの間の遷移領域に用いられている。高速掃き出し構造を用いると、水平レジスタに電荷転送を行う前にデバイスのメインアレイから電荷を選択的に掃き出しができるのでイメージの有効かつ高速のサブサンプリングを行うことができる。これらの構造は、垂直部のすべての列に、あるいは特定の位置に（すなわち、特定の行および／または列に）配置することができ、米国特許第5,440,343号に記載のように設計時に予め定めておくことができる。しかし、そのような従来技術のデバイスでは普通、各構造各々のドレイン領域に直結される接点が必要なので、与えられた設計ルールに対して実現することができるセルサイズに明白な制約が生じる。

20

【0003】

他の従来技術の構造では、個別のドレインごとに接点を設ける必要性を回避するのに、水平C C Dの下に隣接して長い高速掃き出しゲートとドレインとを設置している。しかし、これらのタイプの構造では、電荷は水平C C D中を転送され、その後でこの水平C C Dの下に配置された高速掃き出し構造へ転送される必要があるので、この高速掃き出し操作を行うのにかかる時間が延びてしまうという欠点がある。

【0004】

30

【発明が解決しようとする課題】

従って、従来技術に求められることは、小さなサイズのピクセルを備えるデバイスに用いることが可能で、同時に水平シフトレジスタ（複数を含む）中の電荷転送を回避してアレイのメイン部から電荷を急速に掃き出すことができる高速掃き出し構造を提供することである。

【0005】

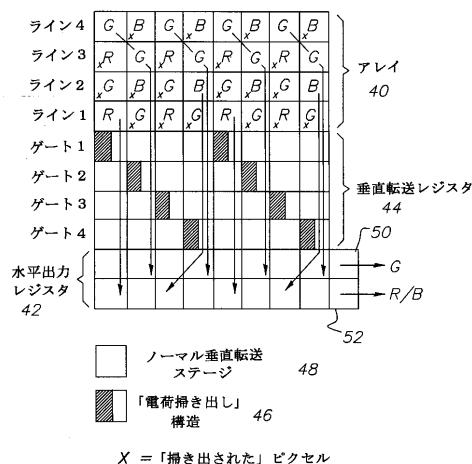

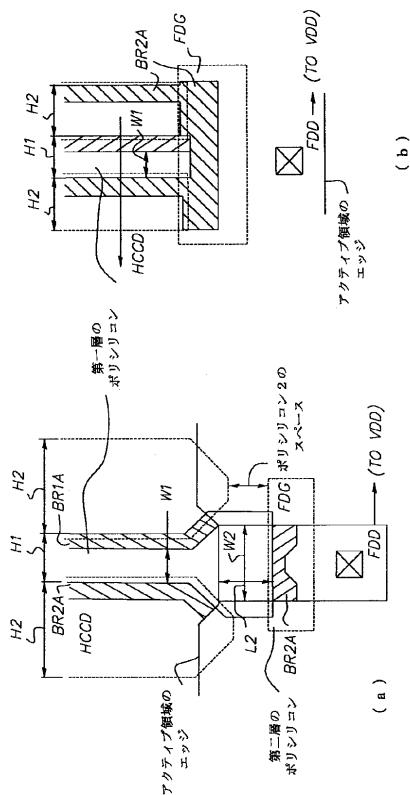

高速掃き出し構造は普通、従来技術のデバイスでは図1に示されるように垂直C C Dと水平C C Dとの間の遷移領域に用いられる。高速掃き出し構造を用いると、水平レジスタに電荷転送を行う前にデバイスのメインアレイから電荷を選択的に掃き出すことができるのでイメージの有効かつ高速のサブサンプリングを行うことができる。これらの構造は垂直部のすべての列に、あるいは特定の位置に（すなわち、特定の行および／または列に）配置することができ、米国特許第5,440,343号に記載のように設計時に予め定めておくことができる。しかし、そのような従来技術のデバイスでは普通、そのような構造各々のドレイン領域に直結される接点が必要なので、所定の設計ルールに対して実現することができるセルサイズに明白な制約が生じる。図2（a）に示されるように、列ごとに個別の接点を設ける必要性をなくする他のタイプの高速掃き出し構造も存在するが、これらのタイプの構造では、電荷は水平シフトレジスタ中を転送されなければならないので、処理速度が遅くなってしまうという欠点がある。

40

【0006】

【課題を解決するための手段】

この新規構造の主要な利点は、フル・フレームC C Dイメージセンサに普通に用いられるラテラル・オーバーフロードレイン（L O D）ブルーミング抑圧構造（例えば、米国特許第5,130,774号を参照のこと）の既存ドレインを用いることによって、ドレイン

50

領域に個別の接点を設ける必要がなくなることである。L O Dをドレインとして用いることによって、ドレイン接点に要するゲート電極用の個別の開口を設けないで済むので、よりコンパクトな構造になる。ゲート制御は、L O D構造の特定のオーバーフローチャネル領域の上方にC C Dゲート電極用のホールをエッチングし、これを次のゲート電極層の一つで埋め込むことによって行われる。この次のゲート電極を用いて高速掃き出し操作を制御する。タイミングは蓄積モードのクロック信号で操作されている二相C C Dについて示しているが、他のタイプのC C Dやクロックスキームも用いることができるこことも理解されねばならない。

#### 【0007】

この構造のもう一つの利点は、通常のL O D構造を採用する二重（あるいは多重）電極C C Dプロセスを用いて作るときマスキングやプロセス工程などを付加して行う必要がないことである。

10

#### 【0008】

本発明のイメージセンサ装置は、行と列とのアレイ状に配列された複数のピクセルと、前記列を形成するのに用いられ、前記ピクセルが各々多相を備える場所を定義する複数の垂直電荷結合素子シフトレジスタと、前記各ピクセルに対して少なくとも一つが配置され、上方に形成された複数の電極と、少なくとも一個の前記ピクセルの前記電極の範囲内に形成され、前記電極のすぐ次の層の電極材料より形成された掃き出し電極を内部に備えるホールと、前記ピクセルに隣接し前記掃き出し電極が作動時には接続されているドレインと、を備えていることを特徴とする。

20

#### 【0009】

本発明のイメージセンサ装置において、前記ドレインが基板内に埋設されたラテラル・オーバーフロードレイン構造であるものとすることもできる。

#### 【0010】

本発明のイメージセンサ装置において、前記ホールがバリア・インプラント領域の上方に形成されるものとすることもできる。

#### 【0011】

【発明の実施の形態】

高速掃き出し構造は普通、従来技術のデバイスでは図1に示されるように垂直C C Dと水平C C Dとの間の遷移領域に用いられる。高速掃き出し構造を用いると、水平レジスタに電荷転送を行う前にデバイスのメインアレイから電荷を選択的に掃き出すことができる。これでイメージの有効かつ高速のサブサンプリングを行うことができる。これらの構造は垂直部のすべての列に、あるいは特定の位置に（すなわち、特定の行および／または列に）配置することができ、米国特許第5,440,343号に記載のように設計時に予め定めておくことができる。しかし、そのような従来技術のデバイスでは普通、そのような構造各々のドレイン領域に直結される接点が必要なので、所定の設計ルールに対して実現することができるセルサイズに明白な制約が生じる。他のタイプの高速掃き出しゲート（F D G）構造では、高速掃き出しドレイン（F D D）に電荷を取り除くのに各列に個別の接点を設ける必要性をなくする構造が存在する。そのようなデバイスを説明する例は、図2（b）に示され、従来技術のデバイスは図2（a）に示される。これらの構造では、電荷は水平シフトレジスタ（H1, H2）を経由して転送されなければならないので、処理速度が低下してしまうという欠点がある。尚、多重相とは、2を超える個数の相を備えるデバイスは勿論のこと、2相のデバイスも仮想の相のデバイスも含む。仮想相デバイスは、一つのクロック制御された相B R 1 Aと仮想（ノンクロック）相B R 2 Aとを備える。これらの相はバリア・インプラントと称される。

30

#### 【0012】

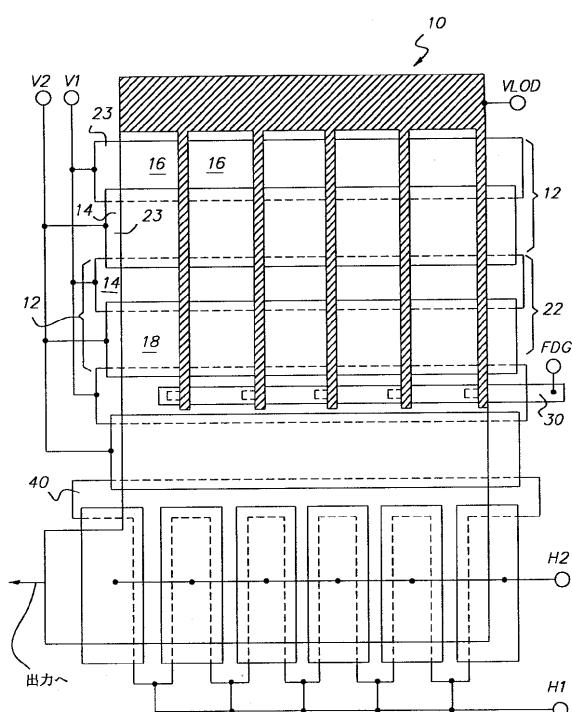

イメージセンサ装置は、従来技術の設計に対する改良である高速掃き出し構造を備える。図3を参照すると、イメージセンサ装置10は、行14と列16とのアレイに配列された複数のピクセル12を備える。好ましい実施の形態では、イメージセンサ装置10は、垂直C C Dシフトレジスタ18として形成される列16を有する2相のフル・フレーム装置

40

50

である。各垂直シフトレジスタ 18 は、各ピクセル 12 に対して多重相 23 を有する多重のピクセル 12 を備える。好ましい実施の形態では、イメージセンサ装置 10 としてフル・フレーム装置を採用する。最良のモードがフル・フレーム装置であるという本質的な利点があるからである。しかし、本発明はインターライン型の装置にも採用することも可能である。

【0013】

図 3 は、本発明の好ましい実施の形態で採用される二相装置であって、各 CCD ピクセル 12 には個別の相電極 1, 2 がある。相電極 1, 2 は、電圧源 V1, V2 にそれぞれ電気的に接続され、ピクセル 12 内の 2 相に交互にパルスが送られ、各垂直シフトレジスタ 18 二相 CCD 装置内での電荷転送に影響を与える。多重相 23 に対する相電極 1, 2 10

各々は個別の電極材料から形成されるので 2 層の電極材料となる。相電極 1, 2 はここでは隣接の電極がオーバーラップするように示される。しかし、多重相の電荷転送装置を形成するのに非オーバーラップタイプの電極を採用することも関連技術内に既知であり、本発明の内容の中で実行可能な別法となることもある。普通、相電極 1, 2 はポリシリコンから形成されるが、当業界には無数の教示があり、相電極 1, 2 の少なくとも片方は異なる材料、例えば、インジウム錫酸化物 (ITO) から形成される。

【0014】

高速掃き出しゲート 30 は、選択された CCD ピクセル 12 内の戦略的な箇所に形成されるが、選択された CCD ピクセル 12 内の相電極 1, 2 のうちの一つの間にホールを形成することによって最初形成される。ドレインは、このホールに隣接して形成され、垂直シフトレジスタ 18 の選択されたセル 22 からピクセル電荷がここに掃き出される。この掃き出し方で解像度を変えることができる。解像度を変える能力は、高速適用のような多くの適用やウィンドウ適用に望ましいものである。ウィンドウ適用とは撮像装置 10 のピクセルアレイ全体の内のサブセットだけが必要な適用である。低解像度モードでは、ピクセル電荷すべてを水平シフトレジスタ 40 から出力する必要はかならずしもない。従って、高速掃き出しゲート電極 30 は、ドレインに隣接したホール内に電極を形成することによって望ましくないピクセルデータを出来るだけ迅速に掃き出すように形成される。この電極は、上記ホールが形成される電極とは異なる電極層から形成されるので、垂直 CCD シフトレジスタ 18 内の電荷転送に影響せずにピクセル電荷ドレインを制御できる。高速掃き出しゲート電極 30 に適用された所定の閾値を超える電圧レベルを印加することによって一旦高速掃き出しゲート電極 30 が起動されると、高速掃き出しゲート電極 30 を備える CCD セル 22 内の電荷はすべて掃き出される。電荷のドレインは、イメージセンサ装置 10 内の選択されたどんな一行、または選択されたどんな複数の行に対する選択された垂直 CCD からも行われる。好ましい実施の形態では、CCD は二相デバイスであり、2 層の電極材料（ポリシリコン、ITO または他の電極材料）を備えるデバイスである。好ましい実施の形態ではホールは、第一電極層と同じ高さに形成され、次いでこのホールの上に高速掃き出しゲート電極 30 が第二層の電極材料の一部分から形成される。こうすると、高速掃き出しゲート電極 30 を第一電極層から分離することが可能で、高速掃き出しゲート電極 30 は垂直 CCD シフトレジスタ 18 内の作動に影響することなく高速掃き出しゲート電極 30 の作動を独立的に働かせるように形成される。好ましい実施の形態の内の高速掃き出しゲート電極 30 は、CCD の列 16 各々内にある対応するセル 22 に形成され、CCD からのドレインがすべての行のピクセルについて行われるようになる。好ましい実施の形態の内では、高速掃き出しゲートを形成するのに用いられるドレインは、ラテラル・オーバーフロードレイン構造であり、CCD はフル・フレーム装置であることが好ましい。

【0015】

図 4 はイメージセンサ装置 10 の一部分の上面図で、新規の高速掃き出しゲート 30 の機能と構造を示すのに選択されたものである。図 4 に示されるように、相 1 の電極 1 が電圧源 V1 に電気的に接続され、相 2 の電極 2 が電圧源 V2 に電気的に接続され、好ましい実施の形態の 2 相式のイメージセンサ装置 10 が新たに生成される。高速掃き出しゲー 50

ト 3 0 の電極は、相 1 の電極 <sub>1</sub> 領域内（電極 <sub>1</sub> と同じ高さの領域）に形成するのが好ましい。これがセルの最後の相であり、こうすることにより、セル内に含まれた電荷すべてを効率的に掃き出すのが容易になるからである。高速掃き出しゲート 3 0 はどこの相に形成してもよいことは当業者には理解されることであろうが、これはセルの最後の相内に形成することが好ましい。このことは好ましい実施の形態のフレームトランスファー型イメージセンサ装置 1 0 に示されている。このイメージセンサ装置 1 0 では、相 1 の電極 <sub>1</sub> からの電荷は、電荷が高速掃き出しゲート 3 0 により掃き出される領域である相 1 の電極

1 領域内へシフトされる相 2 の電極 <sub>2</sub> からの電荷より前に高速掃き出しゲート 3 0 により掃き出される。最後の相が高速掃き出しゲート 3 0 を含むようにさせるという構成は、電荷をセルから転送するということに照らし合わせて整合しており、高速掃き出しゲート 3 0 構造によりセルから電荷すべてを掃き出すことが望ましい。従って、セル内の最後の相は、高速掃き出しゲート 3 0 構造を配置するのに好ましい相である。

#### 【 0 0 1 6 】

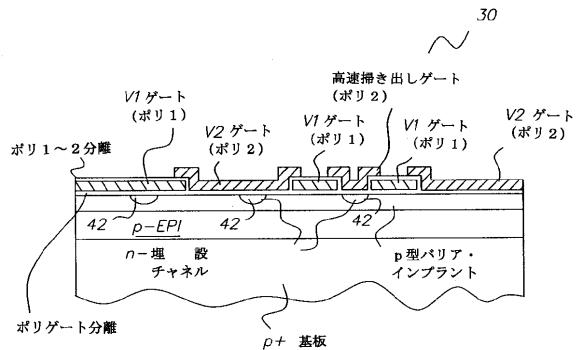

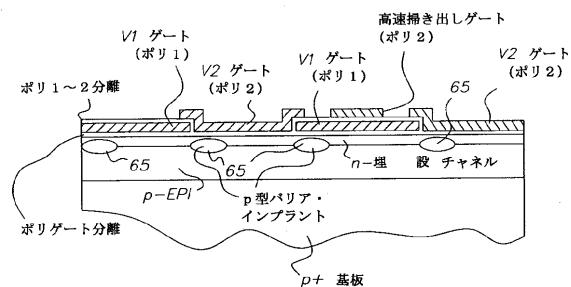

更に図 4 を参照すると、フレームトランスファー型イメージセンサ撮像装置 1 0 は、前に議論したように 2 相から成るセル 3 2 に形成された高速掃き出しゲート 3 0 構造を備える。センサ内の列 1 6 各々は列 1 6 の片側にラテラル・オーバーフロードレイン（L O D）を備える。L O D 5 2 は、好ましい実施の形態では  $n^+$  材料から形成される。列 1 6 各々の L O D 5 2 の反対側にはチャネルストップ 5 4 が  $p^+$  材から形成される。列 1 6 は、L O D 5 2 と、 $p$  型基板上に形成された  $p$  型エピタキシャル層内に形成されたチャネルストップ 5 4 とを備える。 $n$  型埋設チャネル 4 2 が列 1 6 の部分内に形成されるが、これは多くの相を介して電荷を運ぶためである。 $n$  型埋設チャネル 4 2 は、L O D 5 2 と相電極 <sub>1</sub>、<sub>2</sub> の接合端との近辺領域を除いてイメージセンサ装置 1 0 の至る所に存在する。従って、 $n$  型埋設チャネル 4 2 の指状突起が、図 4 に見られるように相電極 <sub>1</sub>、<sub>2</sub> のセンター領域で  $n^+$  型 L O D に達する。高速掃き出しゲート 3 0 が形成されるセルでは、図 4 に見られるように L O D 5 2 に向かって延びる  $n$  型埋設チャネル 4 2 の指状突起を超えて相電極のセンターにトレンチが形成される。

#### 【 0 0 1 7 】

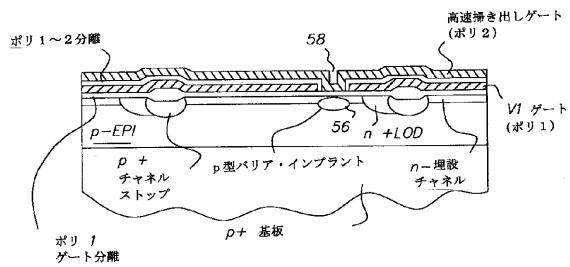

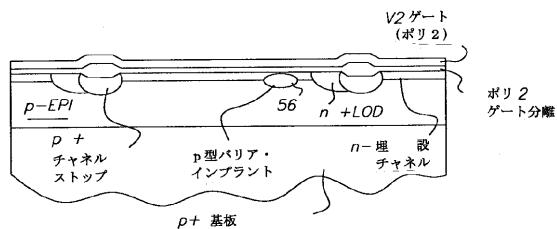

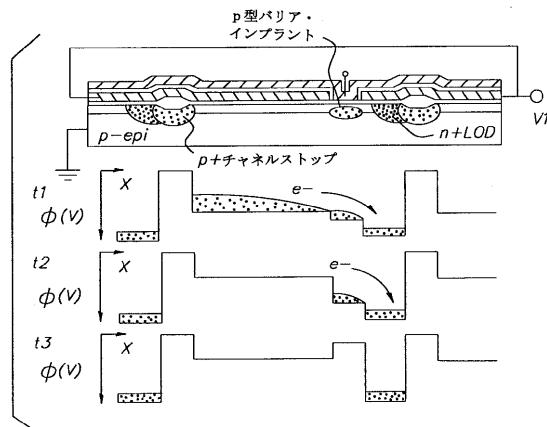

図 5 は図 4 のライン 5 A - 5 A で切断した断面図で、 $p$  型バリア・インプラント 5 6 がノッチ 5 8 の下に示されている。この  $p$  型バリア・インプラント 5 6 は L O D 5 2 近くの列 1 6 のエッジに沿っている。前に議論されたような長軸に沿って走る電極に形成されるトレンチに加えて、図 5 に見られるように  $p$  型バリア・インプラント 5 6 上に形成されたノッチ 5 8 もある。

#### 【 0 0 1 8 】

図 6 は図 4 のライン 5 B - 5 B で切断した断面図で、高速掃き出しゲート 3 0 を有しない相の全幅を示す。図 5 と図 6 とを比較すると、これらの図の相違は、図 5 に示されるノッチ 5 8 が高速掃き出しゲート 3 0 を有する相に含まれていることだけである。これら両図は、L O D 5 2 への電荷の閾値を決める  $p$  型バリア・インプラント 5 6 を含んでいる。図 6 に示されるような高速掃き出しゲート 3 0 を有していない相も  $p$  型バリア・インプラント 5 6 を備える。

#### 【 0 0 1 9 】

図 7 は図 4 のライン 5 C - 5 C で切断した断面図で、高速掃き出しゲート 3 0 を有する相を含む列の一つに対する典型的な電荷転送パスを示す。図 7 はノッチ 5 8 を直接貫通する図で、前に議論された図 5 と合わせて本発明の高速掃き出しゲート 3 0 構造がどのように形成されるかを示す。 $n$  型埋設チャネル 4 2 の多くの指状突起のような露出部を、 $p$  型バリア・インプラント 5 6 内に埋設された各電極のセンターの下の各相内に見ることができる。また、列全体に沿って走る  $p$  型バリア・インプラント 5 6 も図 7 内に明らかに示される。好ましい実施の形態の高速掃き出しゲート 3 0 は、この高速掃き出しゲート 3 0 を含むように選択された相に対して  $n$  型埋設チャネル 4 2 露出部の頂部の直上に配置される。

#### 【 0 0 2 0 】

図 4 のライン 5 D - 5 D で切断した断面図である図 8 では、この断面は、図 7 に対して上

10

20

30

40

50

で議論したラインに平行なラインに沿って、ただし電荷転送セル各個のセンターに寄った所での好ましい実施の形態の構造を示す。p型バリア・インプラント65は各電極のエッジに配置され、各相の間のポテンシャル閾値を定める。

【0021】

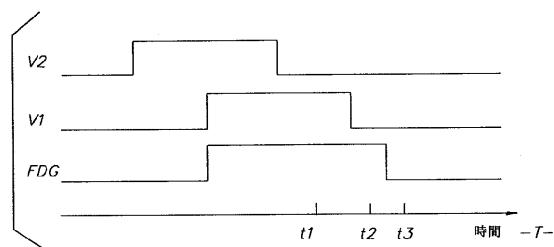

図9は、図4の高速掃き出し構造のサンプルタイミング図である。図10は、図4の高速掃き出し構造に対するチャネルポテンシャル図で、その相に含まれていた電荷がラテラル・オーバーフロードレイン52に掃き出される高速掃き出しゲート30の作動を示す。

【0022】

この新規構造の高速掃き出しゲート30の主要な利点は、ドレイン領域に個別の接点を必要とせず、その代わり普通ブルーミング抑圧目的に用いられるラテラル・オーバーフロードレイン(LOD)という既存のドレインを用いる構造を提供することである。LOD構造は普通、フル・フレームCCDイメージセンサに用いられている。LODを高速掃き出しゲート30として用いることによって、ドレイン接点用にゲート電極に設けられる個別の開口が回避されるので、よりコンパクトな構造になる。ゲート制御は、LOD構造のオーバーフローチャネル領域の上方のCCDゲート電極(と同じ高さの領域)にホールをエッチングし、これを次のゲート電極層の一つで埋め込むことによって行われる。この次のゲート電極を用いて高速掃き出し動作を制御する。このような構造に対する上面図、断面図、タイミング図は、図4～図10に示される。タイミングは蓄積モードのクロック信号で操作されている二相CCDについて示しているが、他のタイプのCCDやクロックスキームも用いることができることも理解されねばならない。

【0023】

この構造のもう一つの利点は、通常のLOD構造を採用する二重(あるいは多重)電極CCDプロセスを用いて作るときマスキングあるいはプロセス工程を付加して行う必要がないことである。

【図面の簡単な説明】

【図1】 米国特許第5,440,343号に開示の従来の高速掃き出し構造の上面図である。

【図2】 従来の高速掃き出し構造の上面図である。

【図3】 本発明の新規の高速掃き出し構造を用いるフル・フレーム型イメージセンサの上面図である。

【図4】 新規の高速掃き出し構造の上面図である。

【図5】 図4のライン5A-5Aで切断した断面図である。

【図6】 図4のライン5B-5Bで切断した断面図である。

【図7】 図4のライン5C-5Cで切断した断面図である。

【図8】 図4のライン5D-5Dで切断した断面図である。

【図9】 図4の高速掃き出し構造のサンプルタイミング図である。

【図10】 図9のタイミングのチャネルポテンシャル図である。

【符号の説明】

10 イメージセンサ装置、12 ピクセル、14 行、16 列、18 垂直シフトレジスタ、22 セル、23 相、30 高速掃き出しゲート、32 セル、40 水平シフトレジスタ、42 n型埋設チャネル、52 ラテラルオーバーフロードレイン(LOD)、54 p+チャネルストップ、56 p型バリア・インプラント、58 ノッチ、65 p型バリア・インプラント、V1 電圧源、V2 電圧源、<sub>1</sub>, <sub>2</sub> 相電極。

10

20

30

40

【図1】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

審査官 穴 哲次

(56)参考文献 特開平10-107252 (JP, A)

特開平09-232558 (JP, A)

特開昭58-017788 (JP, A)

特開2000-134540 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/148