(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5891100号

(P5891100)

(45) 発行日 平成28年3月22日(2016.3.22)

(24) 登録日 平成28年2月26日(2016.2.26)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO4L 25/02   | (2006.01) |

| HO3K 19/0175 | (2006.01) |

| HO1L 21/822  | (2006.01) |

| HO1L 27/04   | (2006.01) |

|      |       |      |

|------|-------|------|

| HO4L | 25/02 | 303B |

| HO3K | 19/00 | 101P |

| HO1L | 27/04 | E    |

請求項の数 13 (全 30 頁)

(21) 出願番号

特願2012-101655 (P2012-101655)

(22) 出願日

平成24年4月26日(2012.4.26)

(65) 公開番号

特開2013-229815 (P2013-229815A)

(43) 公開日

平成25年11月7日(2013.11.7)

審査請求日

平成27年2月2日(2015.2.2)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 100103894

弁理士 家入 健

(72) 発明者 堀山 隼一

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

審査官 阿部 弘

最終頁に続く

(54) 【発明の名称】半導体装置及びデータ送信方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電源系において動作し、入力されたデータ信号及び第1の再送要求信号に基づいて、パルス信号を出力する送信回路と、

前記第1の電源系と異なる第2の電源系において動作し、前記パルス信号に基づいて、前記データ信号を復元する受信回路と、

前記送信回路と前記受信回路とを磁界または電界により結合する絶縁結合素子と、を備え、

前記送信回路は、

前記データ信号及び前記第1の再送要求信号をそれぞれ遅延させた遅延データ信号及び第1の遅延再送要求信号を生成し、

前記遅延データ信号及び前記第1の遅延再送要求信号のエッジにおいて前記パルス信号を出力するとともに、前記遅延データ信号のエッジを跨ぐ所定の期間、前記第1の遅延再送要求信号のエッジにおける前記パルス信号の出力を禁止する、

半導体装置。

## 【請求項 2】

前記送信回路は、

前記遅延データ信号のエッジを跨ぐ所定の期間、前記パルス信号の出力を禁止するための期間信号を生成する第1の論理回路を備えている、

請求項1に記載の半導体装置。

10

20

**【請求項 3】**

前記第1の論理回路に、前記データ信号と、前記遅延データ信号をさらに遅延させた信号とが入力される。

請求項 2 に記載の半導体装置。

**【請求項 4】**

前記送信回路に、さらに第2の再送要求信号が入力され、

前記送信回路は、

前記第2の再送要求信号を遅延させた第2の遅延再送要求信号のエッジにおいて、さらに前記パルス信号を出力すると共に、

前記遅延データ信号のエッジを跨ぐ所定の期間及び前記第1の遅延再送要求信号のエッジを跨ぐ所定の期間、前記第2の遅延再送要求信号のエッジにおける前記パルス信号の出力を禁止する。

10

請求項 1 に記載の半導体装置。

**【請求項 5】**

前記送信回路は、

前記第1の遅延再送要求信号のエッジを跨ぐ所定の期間、前記パルス信号の出力を禁止するための期間信号を生成する第2の論理回路を備えている。

請求項 4 に記載の半導体装置。

**【請求項 6】**

前記第2の論理回路に、前記第1の再送要求信号と、前記第1の遅延再送要求信号をさらに遅延させた信号とが入力される。

請求項 5 に記載の半導体装置。

**【請求項 7】**

前記第1の電源系の電圧が所定の値より低い場合、前記第1又は第2の再送要求信号を出力する低電圧ロックアウト回路を、さらに備える。

請求項 4 に記載の半導体装置。

**【請求項 8】**

定期的に前記第1又は第2の再送要求信号を出力する信号生成回路を、さらに備える。

請求項 4 に記載の半導体装置。

**【請求項 9】**

前記受信回路が、所定の期間、前記パルス信号を検出しない場合、エラー信号を出力するタイマをさらに備える。

請求項 8 に記載の半導体装置。

**【請求項 10】**

前記送信回路に前記データ信号を出力するマイコンと、

前記受信回路が復元した前記データ信号が入力される駆動回路と、をさらに備える。

請求項 1 に記載の半導体装置。

**【請求項 11】**

前記駆動回路により駆動されるパワートランジスタと、

前記パワートランジスタのオンオフにより電流が制御されるモータと、をさらに備える

40

請求項 10 に記載の半導体装置。

**【請求項 12】**

前記絶縁結合素子がコイルを含む。

請求項 1 に記載の半導体装置。

**【請求項 13】**

データ信号及び第1の再送要求信号を遅延させ、遅延データ信号及び第1の遅延再送要求信号を生成し、

前記遅延データ信号及び前記第1の遅延再送要求信号のエッジにおいてパルス信号を出力するとともに、前記遅延データ信号のエッジを跨ぐ所定の期間、前記第1の遅延再送要

50

求信号のエッジにおける前記パルス信号の出力を禁止する、

データ送信方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びデータ送信方法に関し、例えば絶縁結合素子を備えた半導体装置及びデータ送信方法に関する。 10

【背景技術】

【0002】

電源電圧の異なる複数の半導体チップ間で信号を送受信する場合、半導体チップ間を絶縁結合素子によって電気的に絶縁しつつ信号を送受信する必要がある。絶縁結合素子としては、コンデンサやコイルなどを用いた交流結合素子あるいは光結合素子（フォトカプラ）などが知られている。特許文献1～3及び非特許文献1には、絶縁結合素子としてコイルを用いて、信号を送受信する半導体装置が開示されている。 10

【0003】

一の半導体チップ上の送信回路から絶縁結合素子を用いて他の半導体チップ上の受信回路へデータ信号を送信する場合、特許文献1には、データ信号がH（High）レベルの間、パルス信号を送信し続け、データ信号がL（Low）レベルの間、パルス信号を送信しない手法が開示されている。 20

【0004】

他方、非特許文献1、特許文献2には、データ信号のエッジをトリガとする1回あるいは2回のパルス信号を送信回路から送信する手法が開示されている。ここで、送信回路からは、データ信号の立ち上がりエッジ（ライズエッジ）と立ち下がりエッジ（フォールエッジ）との区別が可能なパルス信号が送信される。そのため、受信回路においてデータ信号を復元することができる。 30

【0005】

非特許文献1や特許文献2に開示された手法は、データ信号のエッジのみでパルス信号を送信するため、データ信号がHレベルの間パルス信号を出力し続ける特許文献1に開示された手法に比べ、消費電力が小さく、放射ノイズも小さいという長所を有している。なお、特許文献3には両方の手法が開示されている。 30

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許第6262600号明細書

【特許文献2】米国特許第7075329号明細書

【特許文献3】米国特許第7302247号明細書

【非特許文献】

【0007】

【非特許文献1】S. Kaeriyama, S. Uchida, M. Furumiya, M. Okada, M. Mizuno, "A 2.5kV isolation 35kV/us CMR 250Mbps 0.13mA/Mbps digital isolator in standard CMOS with an on-chip small transformer", 2010 Symposium on VLSI Circuits, Technical Digest of Technical Papers, 2010, pp197-198 40

【発明の概要】

【発明が解決しようとする課題】

【0008】

発明者は以下の課題を見出した。

データ信号のエッジのみでパルス信号を送信する手法は、上述した長所を有する一方で、例えばノイズによりデータ信号の値が反転しまう恐れがある。このような誤りを訂正するため、再送要求信号に応じて、何らかのタイミングで（例えば定期的に）、送信回路からデータ信号の値を再送し、データ信号の値を正しい値に維持又は更新することが好まし 50

い。

しかしながら、データ信号のエッジと再送要求信号のエッジとが接近し過ぎると、受信回路においてデータ信号が誤って復元される恐れがあった。

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

一実施の形態によれば、送信回路が、データ信号及び第1の再送要求信号をそれぞれ遅延させた遅延データ信号及び第1の遅延再送要求信号を生成し、前記遅延データ信号及び前記第1の遅延再送要求信号のエッジにおいてパルス信号を出力するとともに、遅延データ信号のエッジを跨ぐ所定の期間、前記第1の遅延再送要求信号のエッジにおける前記パルス信号の出力を禁止する。 10

【発明の効果】

【0010】

前記一実施の形態によれば、受信回路においてデータ信号が誤って復元されることを抑制することができる。

【図面の簡単な説明】

【0011】

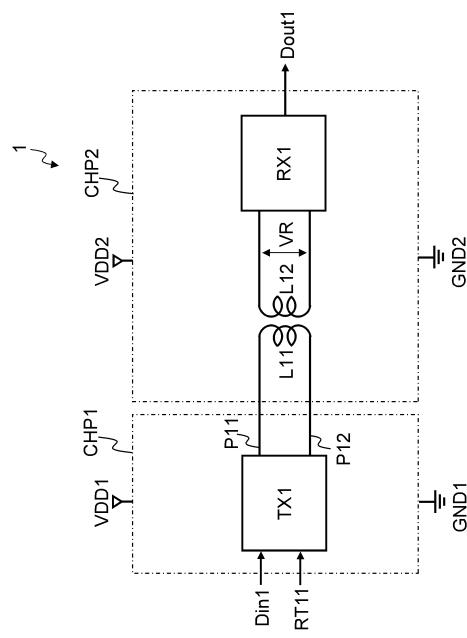

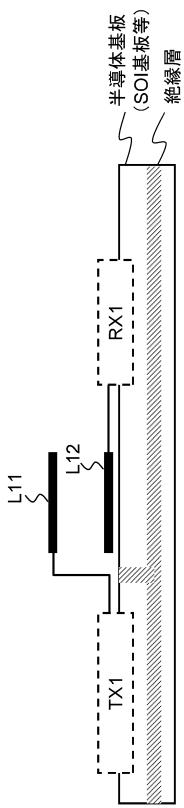

【図1】実施の形態1に係る半導体装置を示すブロック図である。

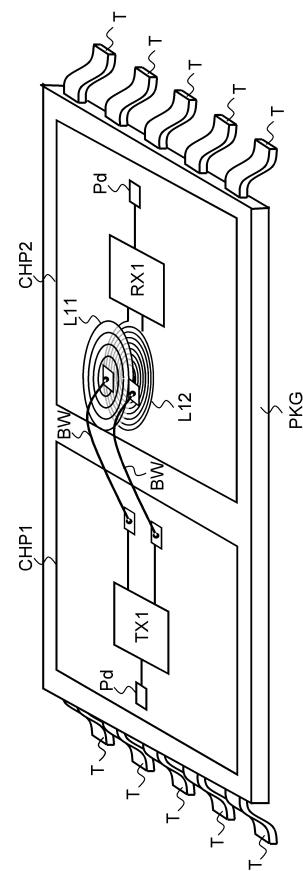

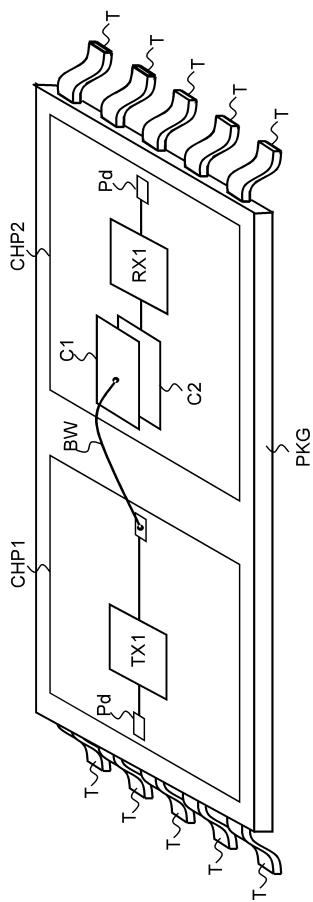

【図2】実施の形態1に係る半導体装置の実装例を示す模式図である。 20

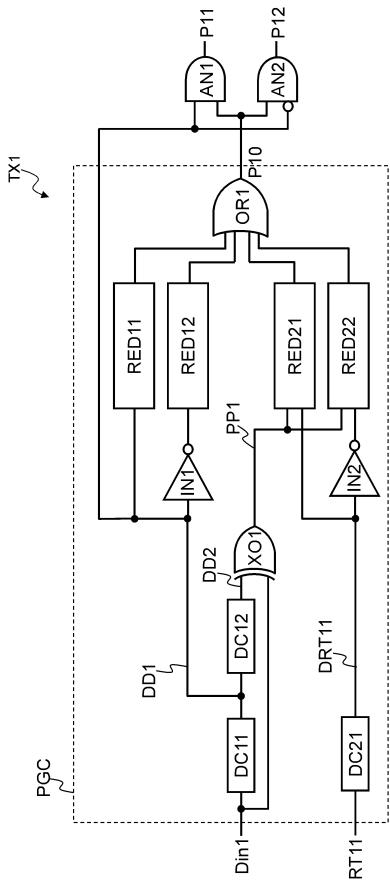

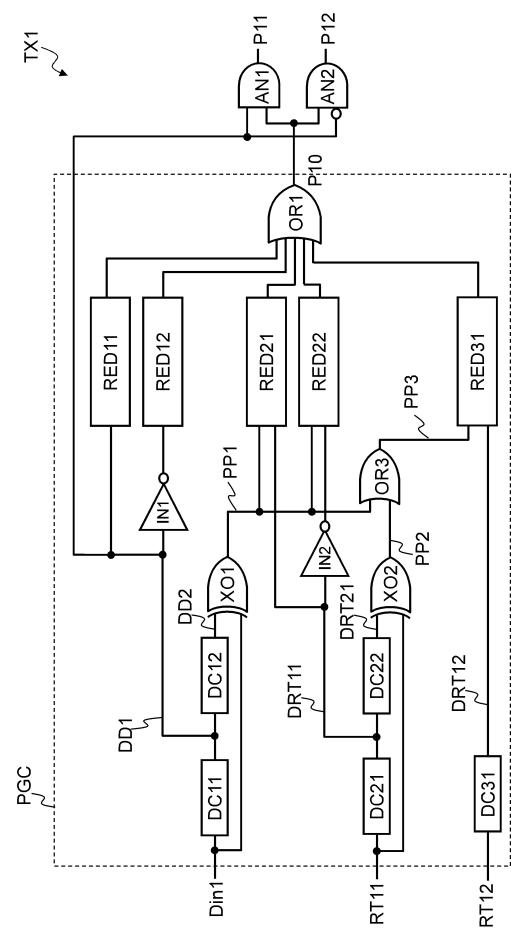

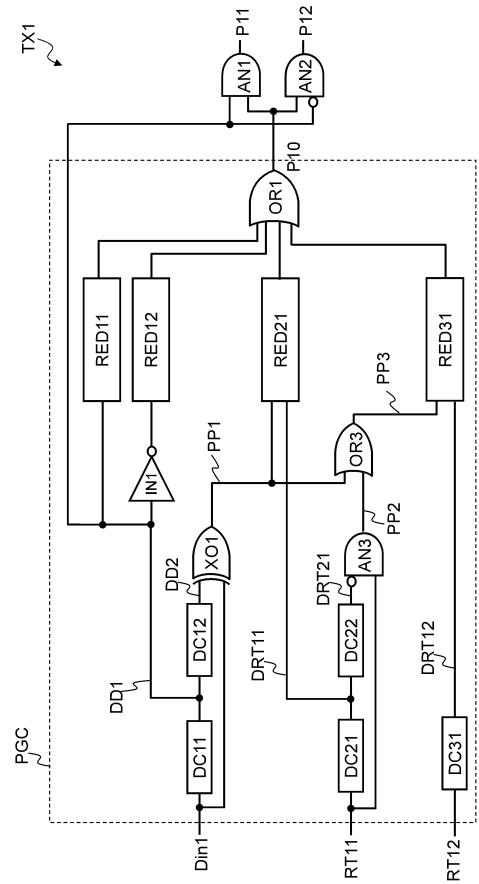

【図3】実施の形態1に係る送信回路TX1の具体的な回路構成の一例を示す回路図である。

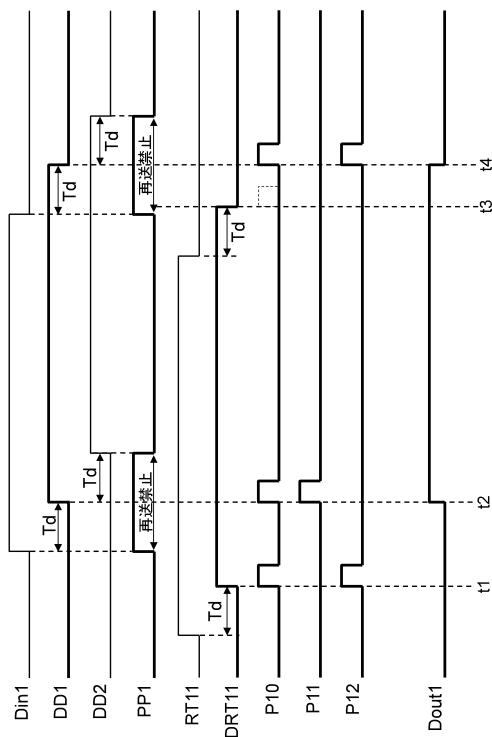

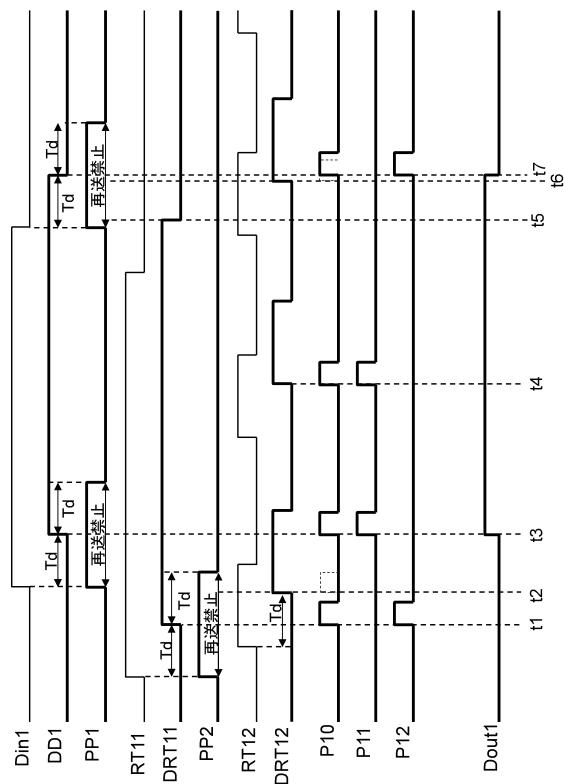

【図4】実施の形態1に係る送信回路TX1の動作の一例を示すタイミングチャートである。

【図5】実施の形態1に係る受信回路RX1の具体的な回路構成の一例を示す回路図である。

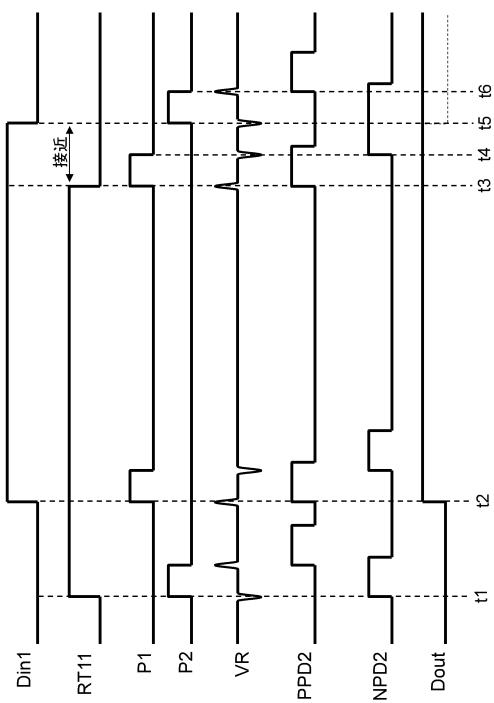

【図6】実施の形態1に係る受信回路RX1の動作の一例を示すタイミングチャートである。 30

【図7】実施の形態1の比較例に係る送信回路TX10の具体的な回路構成の一例を示す回路図である。

【図8】受信回路においてデータ信号が誤って復元される例について説明するためのタイミングチャートである。

【図9】受信回路においてデータ信号が誤って復元される例について説明するためのタイミングチャートである。

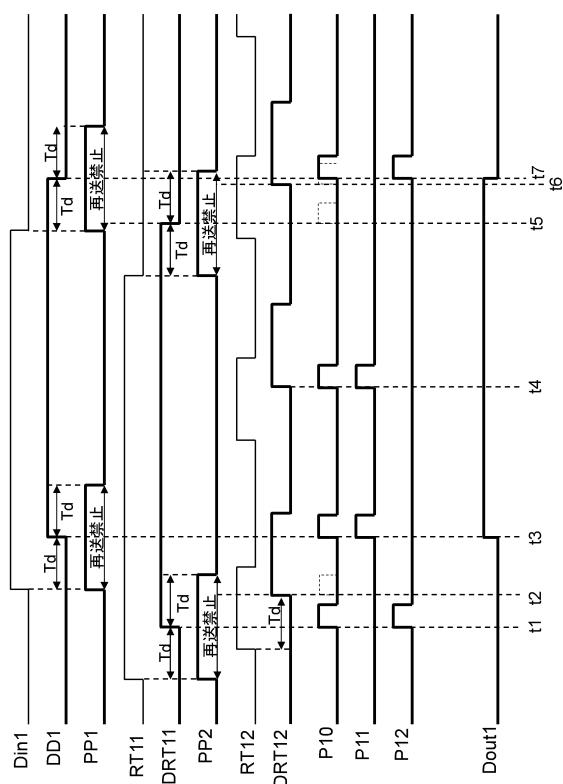

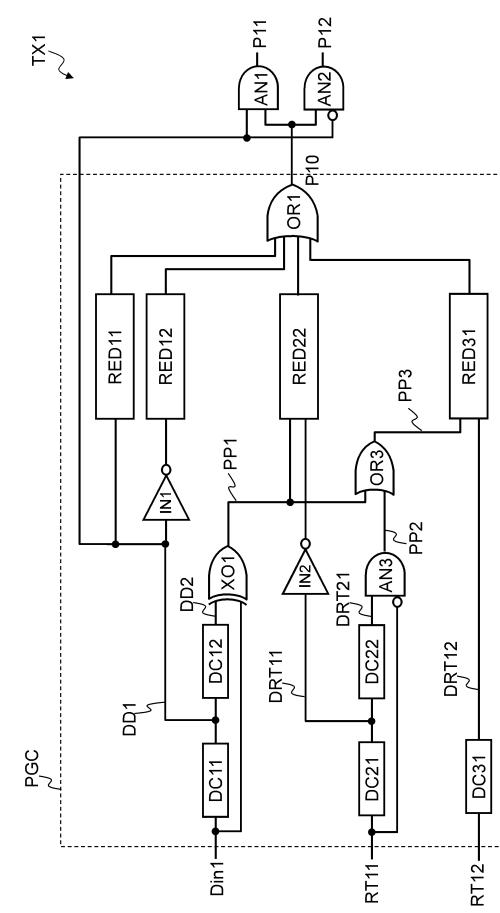

【図10】実施の形態2に係る送信回路TX1の具体的な回路構成の一例を示す回路図である。

【図11】実施の形態2に係る送信回路TX1の動作の一例を示すタイミングチャートである。

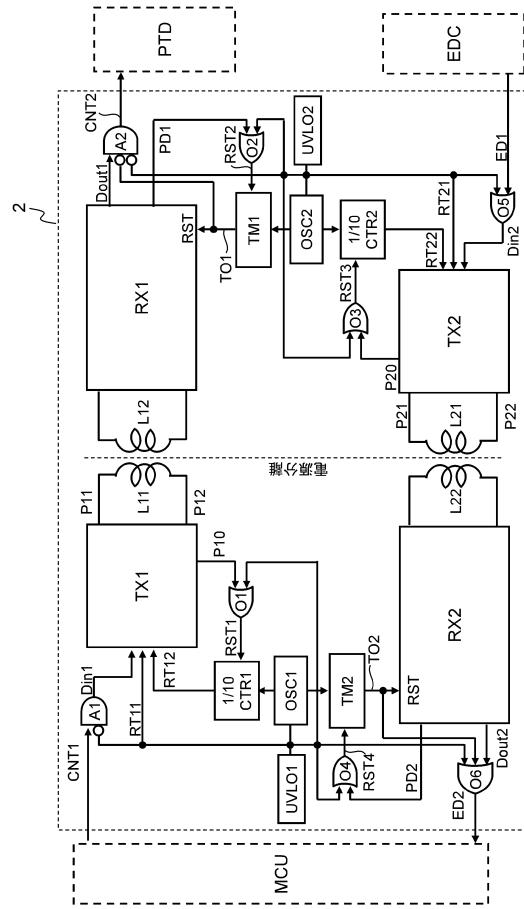

【図12】実施の形態3に係る半導体装置2の構成を示すブロック図である。

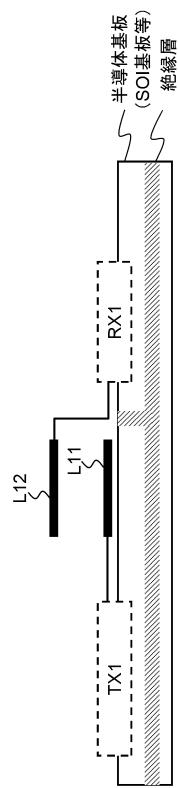

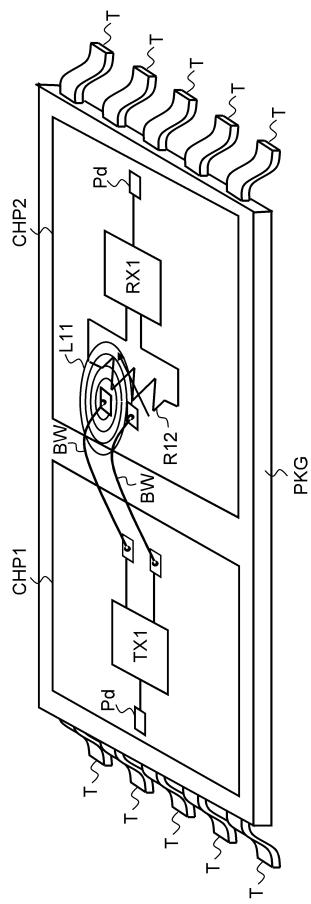

【図13】半導体装置の実装例を示す模式図である。 40

【図14】半導体装置の実装例を示す模式図である。

【図15】半導体装置の実装例を示す模式図である。

【図16】半導体装置の実装例を示す模式図である。

【図17】半導体装置の実装例を示す模式図である。

【図18】半導体装置の実装例を示す模式図である。

【図19】半導体装置の実装例を示す模式図である。

【図20】半導体装置の実装例を示す模式図である。

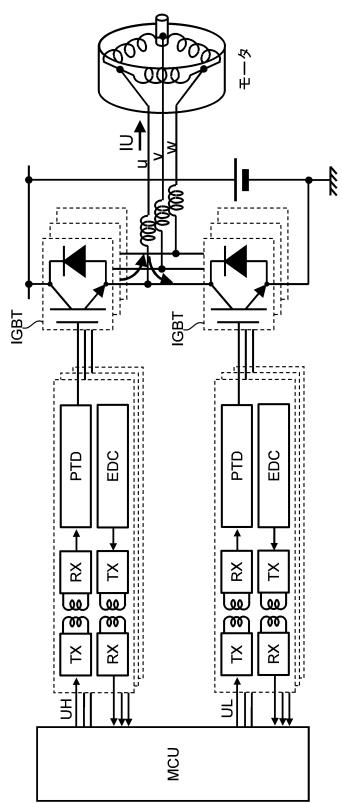

【図21】半導体装置が適用されるインバータ装置を示す図である。

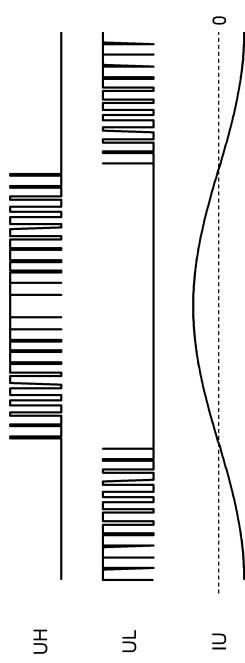

【図22】半導体装置が適用されるインバータ装置の動作を示すタイミングチャートである。 50

【図23】実施の形態2の変形例に係る送信回路TX1の具体的な回路構成の一例を示す回路図である。

【図24】実施の形態2の変形例に係る送信回路TX1の具体的な回路構成の一例を示す回路図である。

【図25】実施の形態2の変形例に係る送信回路TX1の動作の一例を示すタイミングチャートである。

【図26】実施の形態2の変形例に係る送信回路TX1の動作の一例を示すタイミングチャートである。

**【発明を実施するための形態】**

**【0012】**

10

以下、具体的な実施の形態について、図面を参照しながら詳細に説明する。ただし、以下の実施の形態に限定される訳ではない。また、説明を明確にするため、以下の記載及び図面は、適宜、簡略化されている。

**【0013】**

**(実施の形態1)**

まず、図1を参照して、実施の形態1に係る半導体装置について説明する。図1は、実施の形態1に係る半導体装置1の構成を示すブロック図である。実施の形態1に係る半導体装置1は、送信回路TX1、一次コイルL11、二次コイルL12、受信回路RX1を備え、アイソレータを構成している。

**【0014】**

20

送信回路TX1は、半導体チップCHP1に形成される。なお、半導体チップCHP1は、第1の電源系に属する第1の電源（電源電圧VDD1、接地電圧GND1）によって駆動される。

**【0015】**

一次コイルL11、二次コイルL12、受信回路RX1は、半導体チップCHP2に形成される。なお、半導体チップCHP2は、第1の電源系と異なる第2の電源系に属する第2の電源（電源電圧VDD2、接地電圧GND2）によって駆動される。

**【0016】**

一次コイルL11、二次コイルL12は、電源電圧の異なる2つの半導体チップCHP1、CHP2を電気的に絶縁しつつ磁界または電界により結合する絶縁結合素子を構成している。この絶縁結合素子により、半導体チップCHP1上の送信回路TX1から電源電圧の異なる半導体チップCHP2上の受信回路RX1へデータ信号を送信することができる。

**【0017】**

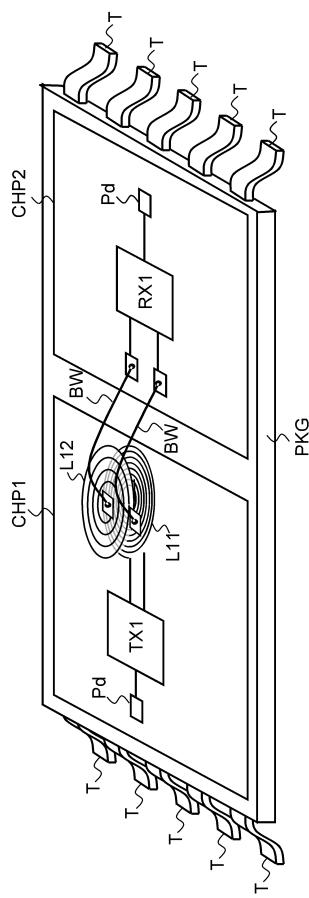

ここで、図2を参照して、半導体装置1の実装例について説明する。図2は、半導体装置1の実装例を示す図である。なお、図2は、主として送信回路TX1、受信回路RX1及びこれらの間に設けられた一次コイルL11、二次コイルL12の実装例を説明するものである。

**【0018】**

30

図2に示す実装例は、半導体パッケージPKGに2つの半導体チップCHP1、CHP2が搭載される。半導体チップCHP1、CHP2は、それぞれパッドPadを有する。そして、半導体チップCHP1、CHP2のそれぞれのパッドPadは、図示しないボンディングワイヤを介して半導体パッケージPKGに設けられた複数のリード端子（外部端子）Tに接続される。

**【0019】**

図2に示すように、半導体チップCHP1には送信回路TX1が形成される。半導体チップCHP2には、受信回路RX1、一次コイルL11、及び二次コイルL12が形成される。また、半導体チップCHP1には、送信回路TX1の出力に接続されるパッドが形成され、半導体チップCHP2には、一次コイルL11の両端にそれぞれ接続されるパッドが形成される。そして、送信回路TX1は、これらパッドとボンディングワイヤBWと

40

50

を介して、半導体チップCHP2に形成された一次コイルL11と接続される。

**【0020】**

なお、図2に示す例では、一次コイルL11及び二次コイルL12が、それぞれ1つの半導体チップ内において上下方向に積層される第1の配線層及び第2の配線層に形成されている。

**【0021】**

図1に戻り、半導体装置1の構成例の詳細について説明する。送信回路TX1は、第1の電源系に属する第1の電源に基づき動作する。一方、受信回路RX1は、第2の電源系に属する第2の電源に基づき動作する。

**【0022】**

送信回路TX1は、入力データ信号Din1と再送要求信号RT11のエッジに応じて、送信パルス信号P11、P12を出力する。本実施の形態では、送信パルス信号P11は、Hレベル（例えば第1のレベル）を伝達するためのパルス信号であって、一次コイルL11の一端に出力される。他方、送信パルス信号P12は、Lレベル（例えば第2のレベル）を伝達するためのパルス信号であって、一次コイルL11の他端に出力される。

**【0023】**

一次コイルL11及び二次コイルL12は、送信回路TX1から出力された送信パルス信号P11、P12を、受信信号VRへ変換し、受信回路RX1に伝達する。具体的には、送信パルス信号P11、P12の遷移により一次コイルL11に流れる電流が変化し、これに応じて二次コイルL12の両端間の電圧である受信信号VRが変化する。

**【0024】**

受信回路RX1は、二次コイルL12の受信信号VRに基づいて入力データ信号Din1を復元し、出力データ信号Dout1として出力する。

**【0025】**

本実施の形態に係る半導体装置1では、送信回路TX1が、入力データ信号Din1及び再送要求信号RT11を遅延させた遅延データ信号DD1及び遅延再送要求信号DRT11（図3、4を参照して後述）を生成し、遅延データ信号DD1のエッジを跨ぐ所定の期間、遅延再送要求信号DRT11のエッジにおける送信パルス信号P11、P12の発生を禁止する。これにより、受信回路RX1においてデータ信号が誤って復元されることを抑制することができる。

**【0026】**

次に、図3を参照して、送信回路TX1の具体的な回路構成について説明する。以下に示す回路構成はあくまでも一例である。図3は、実施の形態1に係る送信回路TX1の具体的な回路構成の一例を示す回路図である。図3に示すように、送信回路TX1は、パルス生成回路PGCと2つのANDゲートAN1、AN2とから構成されている。ここで、パルス生成回路PGCは、3つの遅延回路DC11、DC12、DC21、1つのXORゲートXO1、2つのインバータIN1、IN2、4つのライズエッジ検出回路RED11、RED12、RED21、RED22、1つのORゲートOR1を備えている。

**【0027】**

以下に接続関係について説明する。

入力データ信号Din1は、遅延回路DC11に入力される。遅延回路DC11は、入力データ信号Din1を遅延時間Tdだけ遅延させた遅延データ信号DD1（第1の遅延信号）を出力する。ここで、入力データ信号Din1ではなく、遅延データ信号DD1が、受信回路に送信され、データ信号として復元される。

**【0028】**

そのため、遅延データ信号DD1が、ライズエッジ検出回路RED11に入力される。ライズエッジ検出回路RED11は、遅延データ信号DD1のライズエッジにおいてエッジ検出信号を出力する。

また、インバータIN1を介した遅延データ信号DD1の反転信号が、ライズエッジ検出回路RED12に入力される。ライズエッジ検出回路RED11は、遅延データ信号D

10

20

30

40

50

D 1 の反転信号のライズエッジすなわち遅延データ信号 D D 1 のフォールエッジにおいてエッジ検出信号を出力する。

#### 【 0 0 2 9 】

さらに、遅延データ信号 D D 1 は、遅延回路 D C 1 2 に入力される。遅延回路 D C 1 2 は、遅延データ信号 D D 1 を遅延時間 T d だけさらに遅延させた遅延データ信号 D D 2 を出力する。

入力データ信号 D i n 1 と遅延データ信号 D D 2 とが、X O R ゲート X O 1 に入力される。X O R ゲート X O 1 は、入力データ信号 D i n 1 のエッジから遅延データ信号 D D 2 のエッジまでの 2 T d の期間を示す禁止期間信号 P P 1 を出力する。禁止期間信号 P P 1 は、遅延データ信号 D D 1 のエッジの前後 T d (合計 2 T d ) の期間、後述する遅延再送要求信号 D R T 1 1 (第 2 の遅延信号) のエッジ検出を禁止するための信号である。10

#### 【 0 0 3 0 】

再送要求信号 R T 1 1 は、遅延回路 D C 2 1 に入力される。遅延回路 D C 2 1 は、再送要求信号 R T 1 1 を遅延時間 T d だけ遅延させた遅延再送要求信号 D R T 1 1 を出力する。ここで、再送要求信号 R T 1 1 ではなく、遅延再送要求信号 D R T 1 1 のエッジにおいて、遅延データ信号 D D 1 の値を再送する。

#### 【 0 0 3 1 】

そのため、遅延再送要求信号 D R T 1 1 は、ライズエッジ検出回路 R E D 2 1 に入力される。ライズエッジ検出回路 R E D 2 1 は、遅延再送要求信号 D R T 1 1 のライズエッジにおいてエッジ検出信号を出力する。ここで、ライズエッジ検出回路 R E D 2 1 には、禁止期間信号 P P 1 も入力されている。そのため、ライズエッジ検出回路 R E D 2 1 は、遅延再送要求信号 D R T 1 1 のライズエッジが再送禁止期間 (遅延データ信号 D D 1 のエッジの前後 T d の期間) にある場合には、エッジ検出信号を出力しない。20

#### 【 0 0 3 2 】

また、インバータ I N 2 を介した遅延再送要求信号 D R T 1 1 の反転信号は、ライズエッジ検出回路 R E D 2 2 に入力される。ライズエッジ検出回路 R E D 2 2 は、遅延再送要求信号 D R T 1 1 の反転信号のライズエッジすなわち遅延再送要求信号 D R T 1 1 のフォールエッジにおいてエッジ検出信号を出力する。ここで、ライズエッジ検出回路 R E D 2 2 にも、禁止期間信号 P P 1 が入力されている。そのため、ライズエッジ検出回路 R E D 2 2 も、遅延再送要求信号 D R T 1 1 のフォールエッジが再送禁止期間 (遅延データ信号 D D 1 のエッジの前後 T d の期間) にある場合には、エッジ検出信号を出力しない。30

#### 【 0 0 3 3 】

4 つのライズエッジ検出回路 R E D 1 1 、 R E D 1 2 、 R E D 2 1 、 R E D 2 2 から出力されたエッジ検出信号は、O R ゲート O R 1 に入力される。O R ゲート O R 1 からは、総合パルス信号 P 1 0 が出力される。

総合パルス信号 P 1 0 は、2 つのA N D ゲート A N 1 、 A N 2 に入力される。また、A N D ゲート A N 1 には、遅延データ信号 D D 1 が入力される。一方、A N D ゲート A N 2 には、遅延データ信号 D D 1 の反転信号が入力される。

この結果、A N D ゲート A N 1 は、総合パルス信号 P 1 0 がアクティブ (H レベル) になったタイミングにおいて、H レベルを伝達する送信パルス信号 P 1 1 を出力する。また、A N D ゲート A N 2 は、総合パルス信号 P 1 0 がアクティブになったタイミングにおいて、L レベルを伝達する送信パルス信号 P 1 2 を出力する。40

#### 【 0 0 3 4 】

次に、図 4 を参照して、送信回路 T X 1 の動作について説明する。図 4 は、実施の形態 1 に係る送信回路 T X 1 の動作の一例を示すタイミングチャートである。なお、図 4 に示す動作は、絶縁結合素子としてコイルが用いられる場合に限られず、コンデンサ、G M R 素子等が用いられた場合にも同様にも実現可能である。

#### 【 0 0 3 5 】

図 4 の上から順に、入力データ信号 D i n 1 、遅延データ信号 D D 1 、遅延データ信号 D D 2 、禁止期間信号 P P 1 、再送要求信号 R T 1 1 、遅延再送要求信号 D R T 1 1 、総

合パルス信号 P 1 0、送信パルス信号 P 1 1、送信パルス信号 P 1 2、出力データ信号 D o u t 1 が、示されている。

#### 【 0 0 3 6 】

2 段目に示された遅延データ信号 D D 1 は、最上段に示された入力データ信号 D i n 1 が遅延時間 T d だけ遅延された信号である。上述のように、この遅延データ信号 D D 1 が、最下段に示された出力データ信号 D o u t 1 として復元される。

遅延データ信号 D D 2 は、遅延データ信号 D D 1 がさらに遅延時間 T d だけ遅延された信号である。

禁止期間信号 P P 1 は、遅延データ信号 D D 1 のエッジ前後 T d の期間、6 段目に示された遅延再送要求信号 D R T 1 1 のエッジ検出を禁止するための期間信号である。上述の通り、入力データ信号 D i n 1 と遅延データ信号 D D 2 から容易に生成することができる。

10

#### 【 0 0 3 7 】

6 段目に示された遅延再送要求信号 D R T 1 1 は、5 段目に示された再送要求信号 R T 1 1 が遅延時間 T d だけ遅延された信号である。上述のように、遅延再送要求信号 D R T 1 1 のエッジにおいて、遅延データ信号 D D 1 の値が再送される。

#### 【 0 0 3 8 】

次に、時系列に説明する。

時刻 t 1 では、遅延再送要求信号 D R T 1 1 が L レベルから H レベルへ切り換わる（つまりライズエッジである）ため、総合パルス信号 P 1 0 が出力される（つまり、総合パルス信号 P 1 0 が L レベルから H レベルへ一時的に切り換わる）。また、時刻 t 1 では、遅延データ信号 D D 1 が L レベルであるため、L レベルを伝達する送信パルス信号 P 1 2 が出力される。この結果、出力データ信号 D o u t 1 として、L レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルは維持される。

20

#### 【 0 0 3 9 】

時刻 t 2 では、遅延データ信号 D D 1 が L レベルから H レベルへ切り換わる（つまりライズエッジである）ため、総合パルス信号 P 1 0 が出力される。そして、H レベルを伝達する送信パルス信号 P 1 1 が出力される。この結果、出力データ信号 D o u t 1 として、H レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルが、L レベルから H レベルへ切り換わる。なお、遅延データ信号 D D 1 のライズエッジである時刻 t 2 の前後 T d の期間は、再送禁止期間である。

30

#### 【 0 0 4 0 】

時刻 t 3 では、遅延再送要求信号 D R T 1 1 が H レベルから L レベルへ切り換わる（つまりフォールエッジである）が、再送禁止期間であるため、総合パルス信号 P 1 0 は出力されない（つまり、総合パルス信号 P 1 0 は L レベルのままである）。

#### 【 0 0 4 1 】

時刻 t 4 では、遅延データ信号 D D 1 が H レベルから L レベルへ切り換わる（つまりフォールエッジである）ため、総合パルス信号 P 1 0 が出力される。そして、L レベルを伝達する送信パルス信号 P 1 2 が出力される。この結果、出力データ信号 D o u t 1 として、L レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルが、H レベルから L レベルへ切り換わる。

40

#### 【 0 0 4 2 】

時刻 t 3 において説明してように、遅延再送要求信号 D R T 1 1 のエッジが遅延データ信号 D D 1 のエッジに接近し、再送禁止期間に位置する場合、総合パルス信号 P 1 0 は出力されない。これにより、受信回路 R X 1 においてデータ信号が誤って復元されることを抑制することができる。

#### 【 0 0 4 3 】

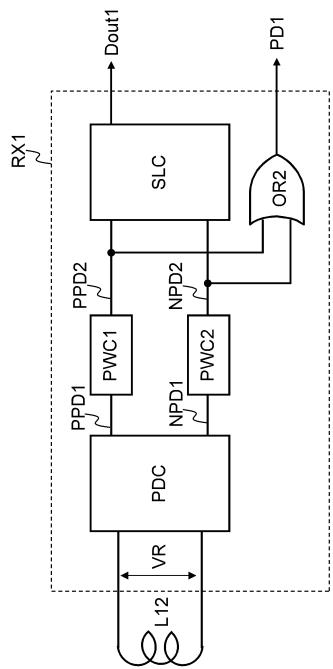

次に、図 5 を参照して、受信回路 R X 1 の具体的な回路構成について説明する。以下に示す回路構成はあくまでも一例である。図 5 は、実施の形態 1 に係る受信回路 R X 1 の具体的な回路構成の一例を示す回路図である。図 5 に示すように、受信回路 R X 1 は、パル

50

ス検出回路 PDC と 2 つのパルス拡幅回路 PWC1、PWC2、順序回路 SLC、OR ゲート OR2 を備えている。

#### 【0044】

以下に接続関係について説明する。

送信回路 TX1 から出力された送信パルス信号 P11、P12 に応じて二次コイル L12 の両端間に発生する受信信号 VR は、パルス検出回路 PDC に入力される。パルス検出回路 PDC は、正パルスを検出した場合は正パルス検出信号 PPD1 を、負パルスを検出した場合は負パルス検出信号 NPD1 を出力する。具体的には、送信回路 TX1 から送信パルス信号 P11、P12 が出力されると、いずれの場合も 1 対の正パルス検出信号 PPD1、負パルス検出信号 NPD1 が出力される。しかし、送信パルス信号 P11 と送信パルス信号 P12 とでは、正パルス検出信号 PPD1 と負パルス検出信号 NPD1 との出力順序が逆転する。本実施の形態では、送信パルス信号 P11 が出力されると正パルス検出信号 PPD1 が先に出力され、送信パルス信号 P12 が出力されると負パルス検出信号 NPD1 が先に出力される。10

#### 【0045】

正パルス検出信号 PPD1 がパルス拡幅回路 PWC1 に、負パルス検出信号 NPD1 がパルス拡幅回路 PWC2 に、入力される。パルス拡幅回路 PWC1、PWC2 は、それぞれ入力された正パルス検出信号 PPD1、負パルス検出信号 NPD1 を拡幅し、正パルス検出信号 PPD2、負パルス検出信号 NPD2 を出力する。ここで、パルス拡幅回路 PWC1、PWC2 は、正パルス検出信号 PPD1、負パルス検出信号 NPD1 のライズエッジは変更せずに、フォールエッジのみを遅延させる。これにより、正パルス検出信号 PPD2 の H レベルの期間と、負パルス検出信号 NPD2 の H レベルの期間とを、一部重複させる。20

#### 【0046】

正パルス検出信号 PPD2 及び負パルス検出信号 NPD2 は、順序回路 SLC に入力される。順序回路 SLC は、入力された正パルス検出信号 PPD2 及び負パルス検出信号 NPD2 の順序を判定し、出力データ信号 Dout1 を出力する。具体的には、順序回路 SLC は、正パルス検出信号 PPD2 が先に入力された場合、出力データ信号 Dout として H レベルを出力する。他方、順序回路 SLC は、負パルス検出信号 NPD2 が先に入力された場合、出力データ信号 Dout1 として L レベルを出力する。30

#### 【0047】

さらに、正パルス検出信号 PPD2 及び負パルス検出信号 NPD2 は、OR ゲート OR2 に入力される。OR ゲート OR2 はパルス検出信号 PD1 を出力する。このパルス検出信号 PD1 は、実施の形態 3 で後述するように、例えばパルス検出信号 PD1 が出力されてからの時間を計測するタイマのリセット信号として用いることができる。なお、図 5 からも明らかなように、OR ゲート OR2 は、出力データ信号 Dout1 を生成する上では必須ではない。

#### 【0048】

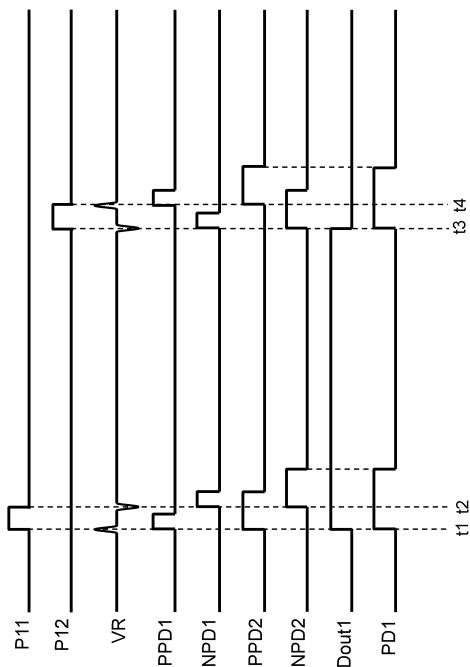

次に、図 6 を参照して、受信回路 RX1 の動作について説明する。図 6 は、実施の形態 1 に係る受信回路 RX1 の動作の一例を示すタイミングチャートである。図 6 の上から順に、送信回路 TX1 から出力された送信パルス信号 P11 及び送信パルス信号 P12、二次コイル L12 の受信信号 VR、正パルス検出信号 PPD1、負パルス検出信号 NPD1、正パルス検出信号 PPD2、負パルス検出信号 NPD2、出力データ信号 Dout1、パルス検出信号 PD1 が、示されている。40

#### 【0049】

3 段目に示された二次コイル L12 の受信信号 VR では、最上段に示された送信パルス信号 P11 及び 2 段目に示された送信パルス信号 P12 に応じて、グラフ上側に突出した正パルスもしくはグラフ下側に突出した負パルスが発生する。具体的には、送信パルス信号 P11 のライズエッジ及び送信パルス信号 P12 のフォールエッジでは、正パルスが発生する。一方、送信パルス信号 P11 のフォールエッジ及び送信パルス信号 P12 のライ50

ズエッジでは、負パルスが発生する。

#### 【0050】

4段目に示された正パルス検出信号P P D 1は、受信信号V Rの正パルス発生タイミングにおいて出力される。

5段目に示された負パルス検出信号N P D 1は、受信信号V Rの負パルス発生タイミングにおいて出力される。

#### 【0051】

6段目に示された正パルス検出信号P P D 2は、パルス拡幅回路P W C 1において正パルス検出信号P P D 1のフォールエッジを遅延させることにより拡幅された信号である。

7段目に示された負パルス検出信号N P D 2は、パルス拡幅回路P W C 2において負パルス検出信号N P D 1のフォールエッジを遅延させることにより拡幅された信号である。 10

9段目に示されたパルス検出信号P D 1は、送信パルス信号P 1 1及び送信パルス信号P 1 2が出力される毎に出力される信号である。上述の通り、正パルス検出信号P P D 2及び負パルス検出信号N P D 2から生成される。

#### 【0052】

次に、時系列に説明する。

時刻t 1では、送信パルス信号P 1 1がLレベルからHレベルへ切り換わるため、受信信号V Rに正パルスが発生する。そのため、時刻t 1では、正パルス検出信号P P D 1、P P D 2がLレベルからHレベルへ切り換わる。正パルス検出信号P P D 2がLレベルからHレベルへ切り換わった結果、出力データ信号D o u t 1として、Hレベルが出力される。 20

#### 【0053】

時刻t 2では、送信パルス信号P 1 1がHレベルからLレベルへ切り換わるため、受信信号V Rに負パルスが発生する。そのため、時刻t 2では、負パルス検出信号N P D 1、N P D 2がLレベルからHレベルへ切り換わる。すなわち、時刻t 2では、負パルス検出信号N P D 2がLレベルからHレベルへ切り換わるが、正パルス検出信号P P D 2がHレベルのままである。そのため、出力データ信号D o u t 1として、Lレベルが出力されず、Hレベルが維持される。つまり、正パルス検出信号P P D 2がHレベルの状態で、負パルス検出信号N P D 2がLレベルからHレベルへ遷移しても、出力データ信号D o u t 1は変化しない。 30

#### 【0054】

時刻t 3では、送信パルス信号P 1 2がLレベルからHレベルへ切り換わるため、受信信号V Rに負パルスが発生する。そのため、時刻t 3では、負パルス検出信号N P D 1、N P D 2がLレベルからHレベルへ切り換わる。負パルス検出信号N P D 2がLレベルからHレベルへ切り換わった結果、出力データ信号D o u t 1として、Lレベルが出力される。

#### 【0055】

時刻t 4では、送信パルス信号P 1 2がHレベルからLレベルへ切り換わるため、受信信号V Rに正パルスが発生する。そのため、時刻t 4では、正パルス検出信号P P D 1、P P D 2がLレベルからHレベルへ切り換わる。すなわち、時刻t 4では、正パルス検出信号P P D 2がLレベルからHレベルへ切り換わるが、負パルス検出信号N P D 2がHレベルのままである。そのため、出力データ信号D o u t 1として、Hレベルが出力されず、Lレベルが維持される。つまり、負パルス検出信号N P D 2がHレベルの状態で、正パルス検出信号P P D 2がLレベルからHレベルへ遷移しても、出力データ信号D o u t 1は変化しない。 40

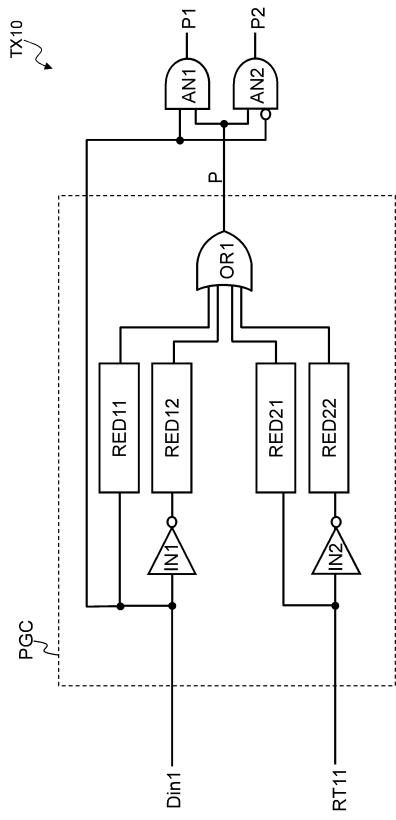

#### 【0056】

次に、図7を参照して、実施の形態1の比較例に係る送信回路T X 1 0について説明する。図7は、実施の形態1の比較例に係る送信回路T X 1 0の具体的な回路構成の一例を示す回路図である。図7に示すように、送信回路T X 1 0も、パルス生成回路P G Cと2つのANDゲートA N 1、A N 2とから構成されている。ここで、パルス生成回路P G C 50

は、2つのインバータIN1、IN2、4つのライズエッジ検出回路RED11、RED12、RED21、RED22、1つのORゲートOR1を備えている。つまり、図3に示した本実施の形態1に係る送信回路TX1と比べると、3つの遅延回路DC11、DC12、DC21、1つのXORゲートXO1を備えていない。

#### 【0057】

以下に接続関係について説明する。

比較例に係る送信回路TX10では、入力データ信号Din1が、そのまま受信回路に送信され、データ信号として復元される。

そのため、入力データ信号Din1が、直接ライズエッジ検出回路RED11に入力される。ライズエッジ検出回路RED11は、入力データ信号Din1のライズエッジにおいてエッジ検出信号を出力する。10

また、インバータIN1を介した入力データ信号Din1の反転信号が、ライズエッジ検出回路RED12に入力される。ライズエッジ検出回路RED12は、入力データ信号Din1の反転信号のライズエッジすなわち入力データ信号Din1のフォールエッジにおいてエッジ検出信号を出力する。

#### 【0058】

再送要求信号RT11は、ライズエッジ検出回路RED21に入力される。ライズエッジ検出回路RED21は、再送要求信号RT11のライズエッジにおいてエッジ検出信号を出力する。

また、インバータIN2を介した再送要求信号RT11の反転信号は、ライズエッジ検出回路RED22に入力される。ライズエッジ検出回路RED22は、再送要求信号RT11の反転信号のライズエッジすなわち再送要求信号RT11のフォールエッジにおいてエッジ検出信号を出力する。20

#### 【0059】

4つのライズエッジ検出回路RED11、RED12、RED21、RED22から出力されたエッジ検出信号は、ORゲートOR1に入力される。ORゲートOR1からは、総合パルス信号Pが出力される。

総合パルス信号Pは、2つのANDゲートAN1、AN2に入力される。また、ANDゲートAN1には、入力データ信号Din1が入力される。一方、ANDゲートAN2には、入力データ信号Din1の反転信号が入力される。30

この結果、ANDゲートAN1は、総合パルス信号Pがアクティブ(Hレベル)になったタイミングにおいて、Hレベルを伝達する送信パルス信号P1を出力する。また、ANDゲートAN2は、総合パルス信号Pがアクティブになったタイミングにおいて、Lレベルを伝達する送信パルス信号P2を出力する。

#### 【0060】

以上説明したように、比較例に係る送信回路TX10は、本実施の形態に係る送信回路TX1が備える遅延回路DC11、DC12、DC21、及びXORゲートXO1を備えていない。そのため、入力データ信号Din1のエッジと再送要求信号RT11のエッジとが接近し過ぎた場合、再送要求信号RT11に応じた送信パルス信号P1、P2の発生を禁止することができない。そのため、受信回路においてデータ信号が誤って復元される恐れがあった。40

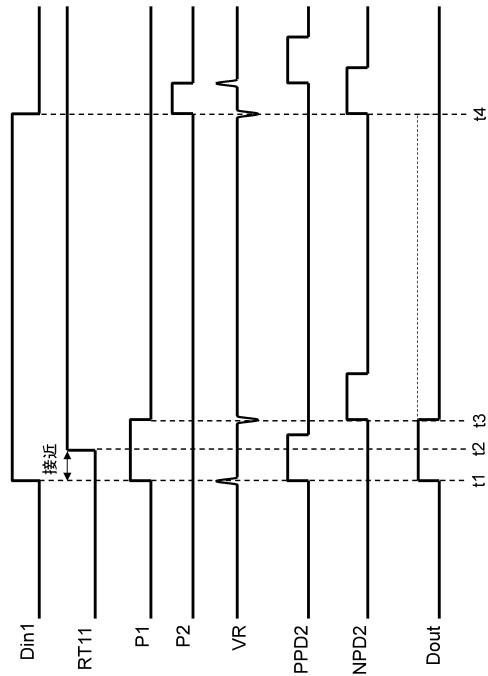

#### 【0061】

次に、図8、9を参照し、比較例に係る送信回路TX10を用いた場合、受信回路においてデータ信号が誤って復元される例について説明する。受信回路の構成は、図5と同じである。図8、9はいずれも、受信回路においてデータ信号が誤って復元される例について説明するためのタイミングチャートである。なお、あくまでも例であり、その他のメカニズムによりデータ信号が誤って復元されることもある。

#### 【0062】

図8、9の上から順に、入力データ信号Din1、再送要求信号RT11、送信パルス信号P1、送信パルス信号P2、二次コイルL12の受信信号VR、正パルス検出信号P50

P D 2、負パルス検出信号 N P D 2、出力データ信号 D o u t 1 が、示されている。

**【 0 0 6 3 】**

まず、図 8 について説明する。

時刻 t 1 では、入力データ信号 D i n 1 が L レベルから H レベルへ切り換わる。そのため、送信パルス信号 P 1 も L レベルから H レベルへ切り換わり、受信信号 V R に正パルスが発生する。従って、時刻 t 1 では、正パルス検出信号 P P D 2 が L レベルから H レベルへ切り換わる。その結果、出力データ信号 D o u t 1 として、H レベルが出力される。

**【 0 0 6 4 】**

時刻 t 2 では、再送要求信号 R T 1 1 が L レベルから H レベルへ切り換わる。ここで、

10 入力データ信号 D i n 1 が H レベルであるため、送信パルス信号 P 1 が出力される。ここで、時刻 t 1 における入力データ信号 D i n 1 のライズエッジと、時刻 t 2 における再送要求信号 R T 1 1 のライズエッジが接近している。そのため、時刻 t 1 で出力された送信パルス信号 P 1 と、時刻 t 2 で出力された送信パルス信号 P 1 とが結合して 1 つのパルス信号となってしまっている。そのため、受信信号 V R に正パルスは発生せず、入力データ信号 D i n 1 の値は伝達されない。

**【 0 0 6 5 】**

時刻 t 3 では、送信パルス信号 P 1 が H レベルから L レベルへ切り換わるため、受信信号 V R に負パルスが発生する。そのため、時刻 t 3 では、負パルス検出信号 N P D 2 が L レベルから H レベルへ切り換わる。ここで、時刻 t 1 に立ち上がった正パルス検出信号 P P D 2 は、時刻 t 3 において既に L レベルへ遷移している。そのため、出力データ信号 D o u t 1 として、誤って L レベルが出力されてしまう。このように、2 つの送信パルス信号 P 1 (あるいは P 2 ) が結合してしまうことにより、データ信号が誤って復元され得る。

20

**【 0 0 6 6 】**

なお、時刻 t 4 では、入力データ信号 D i n 1 が H レベルから L レベルへ切り換わり、出力データ信号 D o u t 1 として、L レベルが正しく出力されているため、詳細な説明は省略する。

**【 0 0 6 7 】**

次に、図 9 について説明する。

まず、時刻 t 1 では、再送要求信号 R T 1 1 が L レベルから H レベルへ切り換わり、入力データ信号 D i n 1 の値 ( L レベル ) が、出力データ信号 D o u t 1 として、正しく伝達されている。また、時刻 t 2 では、入力データ信号 D i n 1 が L レベルから H レベルへ切り換わり、出力データ信号 D o u t 1 として、H レベルが正しく出力されている。そのため、詳細な説明は省略する。

30

**【 0 0 6 8 】**

時刻 t 3 では、再送要求信号 R T 1 1 が H レベルから L レベルへ切り換わる。ここで、入力データ信号 D i n 1 が H レベルであるため、送信パルス信号 P 1 が出力される。そのため、送信パルス信号 P 1 も L レベルから H レベルへ切り換わり、受信信号 V R に正パルスが発生する。従って、時刻 t 3 では、正パルス検出信号 P P D 2 が L レベルから H レベルへ切り換わる。その結果、出力データ信号 D o u t 1 として、H レベルが伝達される。

40

**【 0 0 6 9 】**

時刻 t 4 では、送信パルス信号 P 1 が H レベルから L レベルへ切り換わるため、受信信号 V R に負パルスが発生する。そのため、時刻 t 4 では、負パルス検出信号 N P D 2 が L レベルから H レベルへ切り換わる。しかし、上述の通り、正パルス検出信号 P P D 2 が H レベルのままであるため、出力データ信号 D o u t 1 として、L レベルが出力されない。

**【 0 0 7 0 】**

時刻 t 5 では、入力データ信号 D i n 1 が H レベルから L レベルへ切り換わる。そのため、送信パルス信号 P 2 も L レベルから H レベルへ切り換わり、受信信号 V R に負パルスが発生する。従って、負パルス検出信号 N P D 2 が出力される。ここで、時刻 t 4 で出力された負パルス検出信号 N P D 2 と、時刻 t 5 で出力された負パルス検出信号 N P D 2 と

50

が結合して1つのパルス信号となってしまっている。そのため、時刻 $t_5$ では、負パルス検出信号N P D 2がLレベルからHレベルへ遷移せず、出力データ信号D o u t 1として、Lレベルが出力されず、誤ってHレベルに維持される。このように、2つの負パルス検出信号N P D 2（あるいは正パルス検出信号P P D 2）が結合してしまうことにより、データ信号が誤って復元され得る。

#### 【0071】

なお、時刻 $t_6$ では、送信パルス信号P 2がHレベルからLレベルへ切り換わるため、受信信号V Rに正パルスが発生する。そのため、時刻 $t_6$ では、正パルス検出信号P P D 2がLレベルからHレベルへ切り換わる。しかし、上述の通り、負パルス検出信号N P D 2がHレベルのままであるため、出力データ信号D o u t 1として、Lレベルが出力されない。10

#### 【0072】

以上説明したように、本実施の形態に係る半導体装置1では、送信回路T X 1が、入力データ信号D i n 1及び再送要求信号R T 1 1を遅延させた遅延データ信号D D 1及び遅延再送要求信号D R T 1 1を生成し、遅延データ信号D D 1のエッジを跨ぐ所定の期間、遅延再送要求信号D R T 1 1のエッジにおける送信パルス信号P 1 1、P 1 2の発生を禁止する。これにより、受信回路R X 1においてデータ信号が誤って復元されることを抑制することができる。

#### 【0073】

##### (実施の形態2)

20

次に、図10を参照して、実施の形態2に係る送信回路T X 1について説明する。図10は、実施の形態2に係る送信回路T X 1の具体的な回路構成の一例を示す回路図である。図10に示すように、送信回路T X 1は、パルス生成回路P G Cと2つのA N DゲートA N 1、A N 2とから構成されている。ここで、パルス生成回路P G Cは、5つの遅延回路D C 1 1、D C 1 2、D C 2 1、D C 2 2、D C 3 1、2つのX O RゲートX O 1、X O 2、2つのインバータI N 1、I N 2、5つのライズエッジ検出回路R E D 1 1、R E D 1 2、R E D 2 1、R E D 2 2、R E D 3 1、2つのO RゲートO R 1、O R 3を備えている。

#### 【0074】

図10に示すように、送信回路T X 1には、入力データ信号D i n 1、再送要求信号R T 1 1に加え、再送要求信号R T 1 2が入力される。例えば、再送要求信号R T 1 1は特定のイベントに応じて不定期に出力され、再送要求信号R T 2は定期的に出力される場合などが考えられる。30

送信回路T X 1は、実施の形態1に係る送信回路T X 1の回路構成に加え、さらに、遅延回路D C 2 2、D C 3 1、X O RゲートX O 2、O RゲートO R 3、ライズエッジ検出回路R E D 3 1を備えている。

#### 【0075】

以下に接続関係について説明する。

入力データ信号D i n 1は、遅延回路D C 1 1に入力される。遅延回路D C 1 1は、入力データ信号D i n 1を遅延時間T dだけ遅延させた遅延データ信号D D 1（第1の遅延信号）を出力する。ここで、入力データ信号D i n 1ではなく、遅延データ信号D D 1が、受信回路に送信され、データ信号として復元される。40

#### 【0076】

そのため、遅延データ信号D D 1が、ライズエッジ検出回路R E D 1 1に入力される。ライズエッジ検出回路R E D 1 1は、遅延データ信号D D 1のライズエッジにおいてエッジ検出信号を出力する。

また、インバータI N 1を介した遅延データ信号D D 1の反転信号が、ライズエッジ検出回路R E D 1 2に入力される。ライズエッジ検出回路R E D 1 2は、遅延データ信号D D 1の反転信号のライズエッジすなわち遅延データ信号D D 1のフォールエッジにおいてエッジ検出信号を出力する。50

## 【0077】

さらに、遅延データ信号 D D 1 は、遅延回路 D C 1 2 に入力される。遅延回路 D C 1 2 は、遅延データ信号 D D 1 を遅延時間 T d だけさらに遅延させた遅延データ信号 D D 2 を出力する。

入力データ信号 D i n 1 と遅延データ信号 D D 2 とが、X O R ゲート X O 1 に入力される。X O R ゲート X O 1 は、入力データ信号 D i n 1 のエッジから遅延データ信号 D D 2 のエッジまでの 2 T d の期間を示す禁止期間信号 P P 1 を出力する。詳細については後述するが、禁止期間信号 P P 1 は、遅延データ信号 D D 1 のエッジの前後 T d (合計 2 T d ) の期間、後述する再送要求信号 R T 1 1 、R T 1 2 を遅延時間 T d だけ遅延させた遅延再送要求信号 D R T 1 1 、D R T 1 2 のエッジ検出を禁止するための信号である。

10

## 【0078】

再送要求信号 R T 1 1 は、遅延回路 D C 2 1 に入力される。遅延回路 D C 2 1 は、再送要求信号 R T 1 1 を遅延時間 T d だけ遅延させた遅延再送要求信号 D R T 1 1 を出力する。ここで、再送要求信号 R T 1 1 ではなく、遅延再送要求信号 D R T 1 1 のエッジにおいて、遅延データ信号 D D 1 の値を再送する。

## 【0079】

そのため、遅延再送要求信号 D R T 1 1 は、ライズエッジ検出回路 R E D 2 1 に入力される。ライズエッジ検出回路 R E D 2 1 は、遅延再送要求信号 D R T 1 1 のライズエッジにおいてエッジ検出信号を出力する。ここで、ライズエッジ検出回路 R E D 2 1 には、禁止期間信号 P P 1 も入力されている。そのため、ライズエッジ検出回路 R E D 2 1 は、遅延再送要求信号 D R T 1 1 のライズエッジが再送禁止期間 (遅延データ信号 D D 1 のエッジの前後 T d の期間) にある場合には、エッジ検出信号を出力しない。

20

## 【0080】

また、インバータ I N 2 を介した遅延再送要求信号 D R T 1 1 の反転信号は、ライズエッジ検出回路 R E D 2 2 に入力される。ライズエッジ検出回路 R E D 2 2 は、遅延再送要求信号 D R T 1 1 の反転信号のライズエッジすなわち遅延再送要求信号 D R T 1 1 のフォールエッジにおいてエッジ検出信号を出力する。ここで、ライズエッジ検出回路 R E D 2 2 にも、禁止期間信号 P P 1 が入力されている。そのため、ライズエッジ検出回路 R E D 2 2 も、遅延再送要求信号 D R T 1 1 のフォールエッジが再送禁止期間 (遅延データ信号 D D 1 のエッジの前後 T d の期間) にある場合には、エッジ検出信号を出力しない。

30

## 【0081】

さらに、遅延再送要求信号 D R T 1 1 は、遅延回路 D C 2 2 に入力される。遅延回路 D C 2 2 は、遅延再送要求信号 D R T 1 1 を遅延時間 T d だけさらに遅延させた遅延再送要求信号 D R T 2 1 を出力する。

再送要求信号 R T 1 1 と遅延再送要求信号 D R T 2 1 とが、X O R ゲート X O 2 に入力される。X O R ゲート X O 2 は、再送要求信号 R T 1 1 のエッジから遅延再送要求信号 D R T 2 1 のエッジまでの 2 T d の期間を示す禁止期間信号 P P 2 を出力する。詳細については後述するが、禁止期間信号 P P 2 は、再送要求信号 R T 1 1 のエッジの前後 T d (合計 2 T d ) の期間、後述する再送要求信号 R T 1 2 を遅延時間 T d だけ遅延させた遅延再送要求信号 D R T 1 2 のエッジ検出を禁止するための信号である。

40

禁止期間信号 P P 1 、P P 2 は、O R ゲート O R 3 に入力される。O R ゲート O R 3 からは、禁止期間信号 P P 3 が出力される。

## 【0082】

再送要求信号 R T 1 2 は、遅延回路 D C 3 1 に入力される。遅延回路 D C 3 1 は、再送要求信号 R T 1 2 を遅延時間 T d だけ遅延させた遅延再送要求信号 D R T 1 2 を出力する。ここで、再送要求信号 R T 1 2 ではなく、遅延再送要求信号 D R T 1 2 のライズエッジにおいて、遅延データ信号 D D 1 の値を再送する。

## 【0083】

そのため、遅延再送要求信号 D R T 1 2 は、ライズエッジ検出回路 R E D 3 1 に入力される。ライズエッジ検出回路 R E D 3 1 は、遅延再送要求信号 D R T 1 2 のライズエッジ

50

においてエッジ検出信号を出力する。ここで、ライズエッジ検出回路 R E D 3 1 には、禁止期間信号 P P 3 も入力されている。そのため、ライズエッジ検出回路 R E D 3 1 は、遅延再送要求信号 D R T 1 2 のライズエッジが再送禁止期間（遅延データ信号 D D 1 及び遅延再送要求信号 D R T 1 1 のエッジの前後 T d の期間）にある場合には、エッジ検出信号を出力しない。

#### 【 0 0 8 4 】

5つのライズエッジ検出回路 R E D 1 1、R E D 1 2、R E D 2 1、R E D 2 2、R E D 3 1 から出力されたエッジ検出信号は、ORゲート O R 1 に入力される。ORゲート O R 1 からは、総合パルス信号 P 1 0 が出力される。

総合パルス信号 P 1 0 は、2つのANDゲート A N 1、A N 2 に入力される。また、ANDゲート A N 1 には、遅延データ信号 D D 1 が入力される。一方、ANDゲート A N 2 には、遅延データ信号 D D 1 の反転信号が入力される。

この結果、ANDゲート A N 1 は、総合パルス信号 P 1 0 がアクティブ（Hレベル）になったタイミングにおいて、Hレベルを伝達する送信パルス信号 P 1 1 を出力する。また、ANDゲート A N 2 は、総合パルス信号 P 1 0 がアクティブになったタイミングにおいて、Lレベルを伝達する送信パルス信号 P 1 2 を出力する。

#### 【 0 0 8 5 】

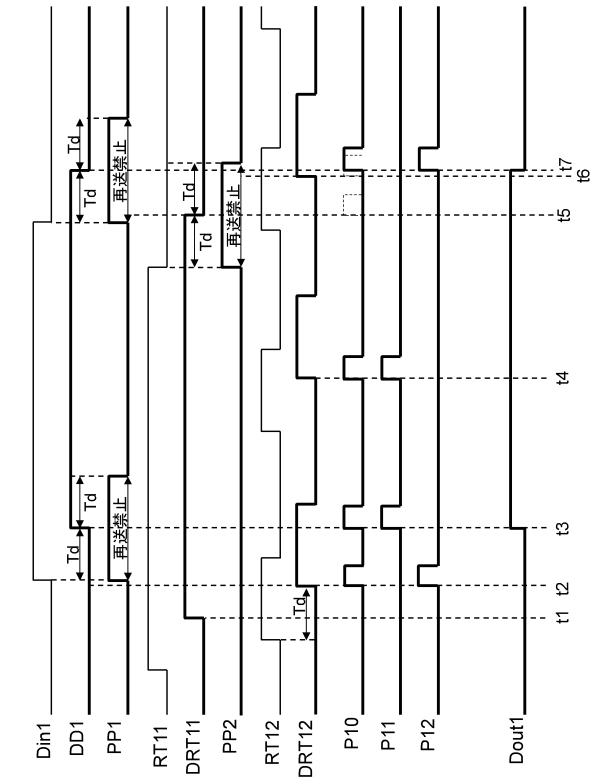

次に、図 1 1 を参照して、送信回路 T X 1 の動作について説明する。図 1 1 は、実施の形態 2 に係る送信回路 T X 1 の動作の一例を示すタイミングチャートである。

図 1 1 の上から順に、入力データ信号 D i n 1、遅延データ信号 D D 1、禁止期間信号 P P 1、再送要求信号 R T 1 1、遅延再送要求信号 D R T 1 1、禁止期間信号 P P 2、再送要求信号 R T 1 2、遅延再送要求信号 D R T 1 2、総合パルス信号 P 1 0、送信パルス信号 P 1 1、送信パルス信号 P 1 2、出力データ信号 D o u t 1 が、示されている。

#### 【 0 0 8 6 】

2段目に示された遅延データ信号 D D 1 は、最上段に示された入力データ信号 D i n 1 が遅延時間 T d だけ遅延された信号である。上述のように、この遅延データ信号 D D 1 が、最下段に示された出力データ信号 D o u t 1 として復元される。

3段目に示された禁止期間信号 P P 1 は、遅延データ信号 D D 1 のエッジ前後 T d の期間、5段目に示された遅延再送要求信号 D R T 1 1 及び8段目に示された遅延再送要求信号 D R T 1 2 のエッジ検出を禁止するための期間信号である。

#### 【 0 0 8 7 】

5段目に示された遅延再送要求信号 D R T 1 1 は、4段目に示された再送要求信号 R T 1 1 が遅延時間 T d だけ遅延された信号である。上述のように、遅延再送要求信号 D R T 1 1 のエッジにおいて、遅延データ信号 D D 1 の値が再送される。

6段目に示された禁止期間信号 P P 2 は、遅延再送要求信号 D R T 1 1 のエッジ前後 T d の期間、8段目に示された遅延再送要求信号 D R T 1 2 のエッジ検出を禁止するための期間信号である。

#### 【 0 0 8 8 】

次に、時系列に説明する。

時刻 t 1 では、遅延再送要求信号 D R T 1 1 が L レベルから H レベルへ切り換わるため、総合パルス信号 P 1 0 が出力される。また、時刻 t 1 では、遅延データ信号 D D 1 が L レベルであるため、L レベルを伝達する送信パルス信号 P 1 2 が出力される。この結果、出力データ信号 D o u t 1 として、L レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルは維持される。なお、遅延再送要求信号 D R T 1 1 のライズエッジである時刻 t 1 の前後 T d の期間は、遅延再送要求信号 D R T 1 2 による再送禁止期間である。

#### 【 0 0 8 9 】

時刻 t 2 では、遅延再送要求信号 D R T 1 2 が L レベルから H レベルへ切り換わるが、遅延再送要求信号 D R T 1 1 のエッジ近傍の再送禁止期間である。そのため、総合パルス信号 P 1 0 は出力されない。

10

20

30

40

50

**【0090】**

時刻  $t_3$  では、遅延データ信号 D D 1 が L レベルから H レベルへ切り換わるため、総合パルス信号 P 1 0 が出力される。そして、H レベルを伝達する送信パルス信号 P 1 1 が出力される。この結果、出力データ信号 D o u t 1 として、H レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルが、L レベルから H レベルへ切り換わる。なお、遅延データ信号 D D 1 のライズエッジである時刻  $t_3$  の前後  $T_d$  の期間は、遅延再送要求信号 D R T 1 1、D R T 1 2 による再送禁止期間である。

**【0091】**

時刻  $t_4$  では、遅延再送要求信号 D R T 1 2 が L レベルから H レベルへ切り換わるため、総合パルス信号 P 1 0 が出力される。また、時刻  $t_4$  では、遅延データ信号 D D 1 が H レベルであるため、H レベルを伝達する送信パルス信号 P 1 1 が出力される。この結果、出力データ信号 D o u t 1 として、H レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルは維持される。10

**【0092】**

時刻  $t_5$  では、遅延再送要求信号 D R T 1 1 が H レベルから L レベルへ切り換わるが、遅延データ信号 D D 1 のエッジ近傍の再送禁止期間であるため、総合パルス信号 P 1 0 は出力されない。

**【0093】**

時刻  $t_6$  では、遅延再送要求信号 D R T 1 2 が L レベルから H レベルへ切り換わるが、遅延データ信号 D D 1 のエッジ近傍の再送禁止期間であるため、総合パルス信号 P 1 0 は出力されない。なお、時刻  $t_6$  は、遅延再送要求信号 D R T 1 1 のエッジ近傍の再送禁止期間でもある。20

**【0094】**

時刻  $t_7$  では、遅延データ信号 D D 1 が H レベルから L レベルへ切り換わるため、総合パルス信号 P 1 0 が出力される。そして、L レベルを伝達する送信パルス信号 P 1 2 が出力される。この結果、出力データ信号 D o u t 1 として、L レベルが伝達される。つまり、出力データ信号 D o u t 1 の信号レベルが、H レベルから L レベルへ切り換わる。

**【0095】**

このように、優先度の高い信号のエッジ近傍では、より優先度の低い信号のエッジに応じた送信パルス信号の出力を禁止する。これにより、受信回路 R X 1 においてデータ信号が誤って復元されることを抑制することができる。なお、再送要求信号は、データ信号を送信する信号であるため、データ信号の優先度が最も高いが、再送要求信号同士の優先度は適宜決定すればよい。30

**【0096】****(実施の形態 3 )**

次に、図 1 2 を参照して、実施の形態 3 に係る半導体装置 2 について説明する。図 1 2 は、実施の形態 3 に係る半導体装置 2 の構成を示すブロック図である。実施の形態 3 に係る半導体装置 2 は、2 つの送信回路 T X 1、T X 2、一次コイル L 1 1、L 2 1、二次コイル L 1 2、L 2 2、2 つの受信回路 R X 1、R X 2、2 つの発振回路 O S C 1、O S C 2、2 つの 1 / 1 0 カウンタ C T R 1、C T R 2、2 つのタイマ T M 1、T M 2、2 つの低電ロックアウト ( U V L O : Under Voltage Lock Out ) 回路 U V L O 1、U V L O 2、2 つ A N D ゲート A 1、A 2、6 つ O R ゲート O 1 ~ O 6 を備えている。40

**【0097】**

ここで、送信回路 T X 1、T X 2 は、実施の形態 2 において図 1 0 を参照して説明した送信回路 T X 1 と同様の構成を有している。また、受信回路 R X 1、R X 2 は、実施の形態 1 において図 5 を参照して説明した受信回路 R X 1 と同様の構成を有している。実施の形態 3 に係る半導体装置 2 は、パワートランジスタの制御システムに適用されたアイソレータの例である。

**【0098】**

まず、主要な構成及び信号の流れについて説明する。

マイコンMCUから出力された制御信号CNT1が、入力データ信号Din1として、送信回路TX1に入力される。また、送信回路TX1には、再送要求信号RT11、RT12も入力される。

送信回路TX1は、実施の形態2において説明したように、入力データ信号Din1、再送要求信号RT11、RT12をそれぞれ同じだけ遅延させた信号のエッジに応じた送信パルス信号P11、P12を出力する。具体的には、優先度の高い信号のエッジに、優先度の低い信号のエッジが接近した場合、優先度の高い信号のエッジに応じた送信パルス信号のみを発生させ、優先度の低い信号に応じた送信パルス信号は発生させない。

#### 【0099】

送信回路TX1から出力された送信パルス信号P11、P12は、一次コイルL11、二次コイルL12を介して受信回路RX1に送信される。受信回路RX1は、受信した信号からデータ信号を復元し、出力データ信号Dout1を出力する。この出力データ信号Dout1が制御信号CNT2として、パワートランジスタドライバPTDに入力される。

つまり、マイコンMCUから出力された制御信号CNT1が、送信回路TX1及び受信回路RX1を介して、制御信号CNT2としてパワートランジスタドライバPTDに入力される。

#### 【0100】

他方、エラー検出回路EDCから出力されたエラー検出信号ED1が、入力データ信号Din2として、送信回路TX2に入力される。また、送信回路TX2には、再送要求信号RT21、RT22も入力される。

送信回路TX2も、実施の形態2において説明したように、入力データ信号Din2、再送要求信号RT21、RT22をそれぞれ同じだけ遅延させた信号のエッジに応じた送信パルス信号P21、P22を出力する。具体的には、優先度の高い信号のエッジに、優先度の低い信号のエッジが接近した場合、優先度の高い信号のエッジに応じた送信パルス信号のみを発生させ、優先度の低い信号に応じた送信パルス信号は発生させない。

#### 【0101】

送信回路TX2から出力された送信パルス信号P21、P22は、一次コイルL21、二次コイルL22を介して受信回路RX2に送信される。受信回路RX2は、受信した信号からデータ信号を復元し、出力データ信号Dout2を出力する。この出力データ信号Dout2がエラー検出信号ED2として、マイコンMCUに入力される。

つまり、エラー検出回路EDCから出力されたエラー検出信号ED1が、送信回路TX2及び受信回路RX2を介して、エラー検出信号ED2としてマイコンMCUに入力される。

#### 【0102】

以下に詳細な構成及び信号の流れについて説明する。

マイコンMCUから出力された制御信号CNT1が、ANDゲートA1を介して、入力データ信号Din1として送信回路TX1に入力される。ここで、ANDゲートA1には、UVLO回路UVLO1から出力される再送要求信号RT11の反転信号も入力される。再送要求信号RT11は、送信回路TX1にも入力される。

#### 【0103】

再送要求信号RT11は、正常時にはLレベルであり、電源電圧が低下した異常時には、Hレベルとなる。つまり、再送要求信号RT11がLレベルである正常時は、マイコンMCUから出力された制御信号CNT1が、入力データ信号Din1として、送信回路TX1に入力される。一方、再送要求信号RT11がHレベルの異常時には、ANDゲートA1により、マイコンMCUから出力された制御信号CNT1の送信回路TX1への入力が遮断されるようになっている。

#### 【0104】

また、実施の形態1、2において説明したように、再送要求信号RT11がLレベルからHレベルあるいはHレベルからLレベルへ遷移するタイミングで、入力データ信号Di

10

20

30

40

50

n1（制御信号C N T 1）の値が送信回路T X 1から受信回路R X 1へ再送される。つまり、電源電圧が低下した場合だけでなく、パワーオン後に電源電圧が上昇し正常値へ移行するタイミングでも、送信側のデータ信号の値と受信側のデータ信号の値を同期させる。

#### 【0105】

さらに、1/10カウントCTR1から出力された再送要求信号R T 1 2が、送信回路T X 1に入力される。再送要求信号R T 1 2は、発振回路O S C 1から出力されたクロック信号の10回に1回の割合でHレベルとなる信号である。例えば、発振回路O S C 1から10MHzのクロック信号が出力された場合、1/10カウントCTR1において、1μs周期(1MHz)の再送要求信号R T 1 2が生成される。再送要求信号R T 1 2により、データ値に変化がなくても10カウントに1回の割合でデータ値が再送される。そのため、ノイズなどにより受信回路R X 1において復元したデータ値が反転した場合でも、速やかに正しい値に復帰させることができる。10

#### 【0106】

また、1/10カウントCTR1は、総合パルス信号P 1 0又はU V L O回路U V L O 1から出力される再送要求信号R T 1 1によりリセットされる。つまり、総合パルス信号P 1 0と再送要求信号R T 1 1とを入力とするORゲートO 1から出力されるリセット信号R S T 1によりリセットされる。

#### 【0107】

送信回路T X 1は、入力データ信号D i n 1、再送要求信号R T 1 1、R T 1 2に基いて、送信パルス信号P 1 1、P 1 2を出力する。送信パルス信号P 1 1、P 1 2は、一次コイルL 1 1、L 1 2を介して受信回路R X 1に入力される。受信回路R X 1はデータ信号を復元して、出力データ信号D o u t 1として出力する。なお、詳細は実施の形態1、2において説明した通りである。20

#### 【0108】

出力データ信号D o u t 1は、ANDゲートA 2を介してパワートランジスタドライバP T Dに入力される。ここで、ANDゲートA 2には、U V L O回路U V L O 2から出力される再送要求信号R T 2 1の反転信号が入力される。また、タイマT M 1から出力されるタイムアウト信号T O 1の反転信号が入力される。

#### 【0109】

再送要求信号R T 2 1は、正常時にはLレベルであり、電源電圧が低下した場合、Hレベルとなる。また、タイムアウト信号T O 1も正常時にはLレベルであり、所定のカウント（例えば40カウント）まで、パルス検出信号P D 1が検出されないと、Hレベルとなる。つまり、再送要求信号R T 2 1及びタイムアウト信号T O 1がLレベルである正常時は、出力データ信号D o u t 1がパワートランジスタドライバP T Dに入力される。他方、再送要求信号R T 2 1又はタイムアウト信号T O 1がHレベルへ切り換わると、ANDゲートA 2により、出力データ信号D o u t 1のパワートランジスタドライバP T Dへの入力が遮断される。また、タイムアウト信号T O 1は、受信回路R X 1をリセットする。なお、正常に動作していれば、再送要求信号R T 1 2により、10カウントに1回は送信回路T X 1からデータ値が再送され、受信回路R X 1からパルス検出信号P D 1が出力される。そのため、タイマT M 1が40カウントに達することはない。一方、送信回路T X 1が停止した場合などには、タイムアウト信号T O 1が出力される。再送要求信号R T 1 2により、送信回路T X 1の動作異常を検出することができる。3040

#### 【0110】

ここで、タイマT M 1は、発振回路O S C 2が出力するクロック信号をカウントする。また、タイマT M 1は、受信回路R X 1から出力されるパルス検出信号P D 1又はU V L O回路U V L O 2から出力される再送要求信号R T 2 1によりリセットされる。つまり、パルス検出信号P D 1と再送要求信号R T 2 1とを入力とするORゲートO 2から出力されるリセット信号R S T 2によりリセットされる。

#### 【0111】

他方、エラー検出回路E D Cから出力されたエラー検出信号E D 1が、ORゲートO 550

を介して、入力データ信号 D<sub>in</sub>2 として送信回路 TX2 に入力される。エラー検出信号 E<sub>D</sub>1 は、正常時には L レベルであり、何らかのエラーが検出された異常時には H レベルとなる。ここで、OR ゲート O5 には、UVLO 回路 UVLO2 から出力される再送要求信号 RT21 も入力される。再送要求信号 RT21 は、正常時には L レベルであり、電源電圧が低下した異常時、H レベルとなる。つまり、再送要求信号 RT21 は、エラー信号としても、エラー検出信号 E<sub>D</sub>1 と共に送信回路 TX2 に入力される。

#### 【0112】

また、実施の形態 1、2 において説明したように、再送要求信号 RT21 が L レベルから H レベルあるいは H レベルから L レベルへ遷移するタイミングで、入力データ信号 D<sub>in</sub>2 の値が送信回路 TX2 から受信回路 RX2 へ再送される。つまり、電源電圧が低下した場合だけでなく、パワーオン後に電源電圧が上昇し正常値へ移行するタイミングでも、送信側のデータ信号の値と受信側のデータ信号の値を同期させる。

10

#### 【0113】

さらに、1/10 カウンタ CTR2 から出力された再送要求信号 RT22 が、送信回路 TX1 に入力される。再送要求信号 RT22 は、発振回路 OSC2 から出力されたクロック信号の 10 回に 1 回の割合で H レベルとなる信号である。再送要求信号 RT22 により、データ値に変化がなくても 10 カウントに 1 回の割合でデータ値が再送される。そのため、ノイズなどにより受信回路 RX2 において復元したデータ値が反転した場合でも、速やかに正しい値に復帰させることができる。

20

#### 【0114】

また、1/10 カウンタ CTR2 は、総合パルス信号 P20 又は UVLO 回路 UVLO2 から出力される再送要求信号 RT21 によりリセットされる。つまり、総合パルス信号 P20 と再送要求信号 RT21 とを入力とする OR ゲート O3 から出力されるリセット信号 RST3 によりリセットされる。

#### 【0115】

送信回路 TX2 は、入力データ信号 D<sub>in</sub>2、再送要求信号 RT21、RT22 に基いて、送信パルス信号 P21、P22 を出力する。送信パルス信号 P21、P22 は、一次コイル L21、L22 を介して受信回路 RX2 に入力される。受信回路 RX2 はデータ信号を復元して、出力データ信号 D<sub>out</sub>2 として出力する。

#### 【0116】

30

出力データ信号 D<sub>out</sub>2 は、OR ゲート O6 を介してマイコン MCU に入力される。ここで、OR ゲート O6 には、UVLO 回路 UVLO1 から出力される再送要求信号 RT11 が入力される。また、タイマ TM2 から出力されるタイムアウト信号 TO2 が入力される。つまり、再送要求信号 RT11 及びタイムアウト信号 TO2 は、出力データ信号 D<sub>out</sub>2 と共に、エラー検出信号 E<sub>D</sub>2 として、マイコン MCU に入力される。

#### 【0117】

ここで、タイムアウト信号 TO2 は、正常時には L レベルであり、所定のカウント（例えば 40 カウント）まで、パルス検出信号 PD2 が検出されないと、H レベルとなる。また、タイムアウト信号 TO2 は、受信回路 RX2 をリセットする。なお、正常に動作していれば、再送要求信号 RT22 により、10 カウントに 1 回は送信回路 TX2 からデータ値が再送され、受信回路 RX2 からパルス検出信号 PD2 が出力される。そのため、タイマ TM2 が 40 カウントに達することはない。一方、送信回路 TX2 が停止した場合には、タイムアウト信号 TO2 が outputされる。再送要求信号 RT22 により、送信回路 TX2 の動作異常を検出することができる。

40

#### 【0118】

ここで、タイマ TM2 は、発振回路 OSC1 が outputするクロック信号をカウントする。また、タイマ TM2 は、受信回路 RX2 から出力されるパルス検出信号 PD2 又は UVLO 回路 UVLO1 から出力される再送要求信号 RT11 によりリセットされる。つまり、パルス検出信号 PD2 と再送要求信号 RT11 とを入力とする OR ゲート O4 から出力されるリセット信号 RST4 によりリセットされる。

50

**【0119】**

(その他の実施の形態)

半導体装置の実装例は、図2に示した実装例に限られるものではない。以下、代表して、半導体装置の他の実装例について、図13～図20を用いて説明する。なお、図13～図18は、絶縁結合素子としてコイルが用いられた場合の実装例である。図19は、絶縁結合素子としてコンデンサが用いられた場合の実装例である。図20は、絶縁結合素子としてGMR素子が用いられた場合の実装例である。

**【0120】**

図13に示す実装例では、半導体チップCHP1に、送信回路TX1と、絶縁結合素子を構成する一次コイルL11及び二次コイルL12と、が形成され、半導体チップCHP2に、受信回路RX1が形成される。さらに、半導体チップCHP1には、二次コイルL12の両端にそれぞれ接続されるパッドが形成される。また、半導体チップCHP2には、受信回路RX1の入力と接続されるパッドが形成される。そして、受信回路RX1は、これらパッドとボンディングワイヤBWとを介して、半導体チップCHP1に形成された二次コイルL12と接続される。なお、図13に示す実装例では、一次コイルL11と二次コイルL12とが、それぞれ一つの半導体チップにおいて上下方向に積層される第1の配線層及び第2の配線層に形成される。

10

**【0121】**

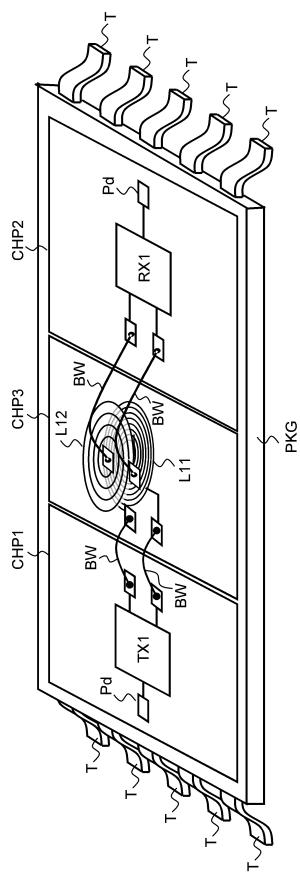

図14に示す実装例では、半導体チップCHP1に送信回路TX1が形成され、半導体チップCHP2に受信回路RX1が形成され、半導体チップCHP1、CHP2とは異なる半導体チップCHP3に一次コイルL11及び二次コイルL12が形成される。さらに、半導体チップCHP1には、送信回路TX1の出力に接続されるパッドが形成される。半導体チップCHP2には、受信回路RX1の入力に接続されるパッドが形成される。また、半導体チップCHP3には、一次コイルL11の両端にそれぞれ接続されるパッド及び二次コイルL12の両端にそれぞれ接続されるパッドが形成される。そして、送信回路TX1は、これらパッドとボンディングワイヤBWを介して、半導体チップCHP3に形成された一次コイルL11と接続される。また、受信回路RX1は、これらパッドとボンディングワイヤBWを介して、半導体チップCHP3に形成された二次コイルL12と接続される。なお、図14に示す実装例では、一次コイルL11と二次コイルL12とが、それぞれ一つの半導体チップにおいて上下方向に積層される第1の配線層及び第2の配線層に形成される。

20

**【0122】**

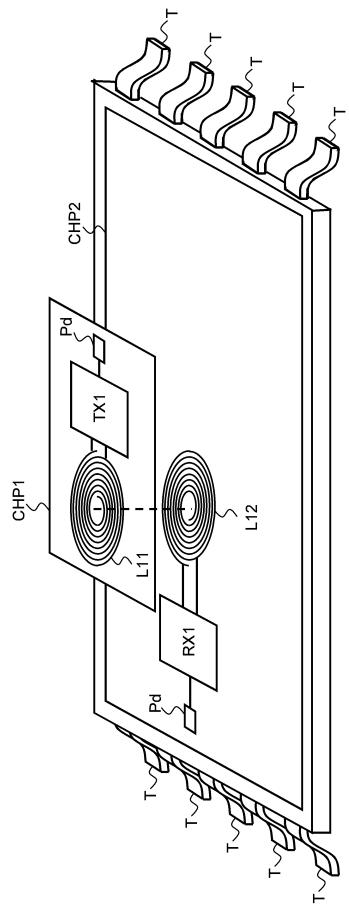

図15に示す実装例では、半導体チップCHP1に送信回路TX1及び一次コイルL11が形成され、半導体チップCHP2に受信回路RX1及び二次コイルL12が形成され、半導体チップCHP1と半導体チップCHP2とが積層される。また、半導体チップCHP1と半導体チップCHP2とは、積層された状態において、一次コイルL11の中心位置と二次コイルL12の中心位置とが同一直線状になるように配置される。

30

**【0123】**

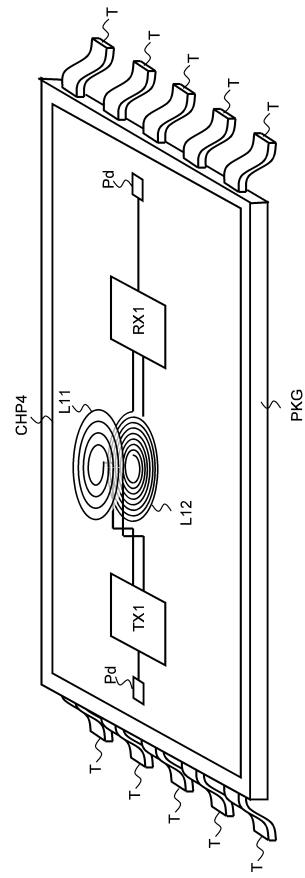

図16に示す実装例では、共通の半導体チップCHP4上に送信回路TX1、受信回路RX1、絶縁結合素子を構成する一次コイルL11及び二次コイルL12が形成される。図16の例では、一次コイルL11と二次コイルL12とが、それぞれ半導体チップCHP4上において上下方向に積層される第1の配線層と第2の配線層に形成される。そして、送信回路TX1が配置される領域と受信回路RX1が配置される領域とは、半導体チップCHP4の基板中に形成される絶縁層により互いに絶縁される。

40

**【0124】**

図17及び図18は、図16に示す半導体チップCHP4の基板の断面図である。図17に示す例では、送信回路TX1が形成される領域と受信回路RX1が形成される領域とが絶縁層により電気的に分断される。そして、一次コイルL11及び二次コイルL12は、受信回路RX1が形成される領域に設けられる。一方、図18に示す例では、送信回路TX1が形成される領域と受信回路RX1が形成される領域とが絶縁層により電気的に分

50

断される。そして、一次コイル L 1 1 及び二次コイル L 1 2 は、送信回路 TX 1 が形成される領域に設けられる。

【 0 1 2 5 】

図 19 は、図 2 に示す実装例において絶縁結合素子として用いられるコイルを、コンデンサに置き換えたものである。より具体的には、一次コイル L 1 1 をコンデンサの一方の電極 C 1 1 に置き換え、二次コイル L 1 2 をコンデンサの他方の電極 C 1 2 に置き換えたものである。

【 0 1 2 6 】

図 20 は、図 2 に示す実装例において絶縁結合素子として用いられるコイルを、GMR 素子に置き換えたものである。より具体的には、一次コイル L 1 1 をそのままにして、二次コイル L 1 2 を GMR 素子 R 1 2 に置き換えたものである。

10

【 0 1 2 7 】

上記したように、絶縁結合素子の種類、絶縁結合素子の配置に関しては特に制限はない。なお、上記説明では、絶縁結合素子を半導体チップ上に形成するとしたが、絶縁結合素子は、外付け部品として設けることも可能である。

【 0 1 2 8 】

上記実施の形態 1 ~ 3 に係る半導体装置の制御対象は、例えば、絶縁ゲートバイポーラトランジスタ ( IGBT : Insulated Gate Bipolar Transistor ) に代表されるパワートランジスタである。この場合、上記実施の形態 1 ~ 3 に係る半導体装置は、受信回路によって再生されたデータ Dout 1 に応じてパワートランジスタのオンオフを制御することにより、電源と負荷との間の導通状態を制御する。

20

【 0 1 2 9 】

さらに、上記実施の形態 1 ~ 3 に係る半導体装置は、例えば、図 21 に示すような、3 相モータ ( 負荷 ) を駆動するインバータ装置に適用される。図 21 に示すインバータ装置は、ハイサイド及びローサイドにそれぞれ u 相、v 相、w 相に対応する 3 つずつ ( 合計 6 つ ) のパワートランジスタドライバ PTD 及びエラー検出回路 EDC を有している。マイコン MCU から出力された制御信号 ( 例えば UH, UL ) が、送信回路 TX 、コイル、受信回路 RX を介して、パワートランジスタドライバ PTD に伝達され、制御対象である IGBT のオンオフが制御される。一方、エラー検出回路 EDC が検出したエラー信号が、送信回路 TX 、コイル、受信回路 RX を介して、マイコン MCU に伝達される。

30

【 0 1 3 0 】

図 22 のグラフに示すように、マイコン MCU から出力された制御信号 ( 例えば UH, UL ) は、PWM 制御信号であり、モータに流れる電流 ( 例えば IU ) がアナログ的に制御される。ここで、制御信号 ( 例えば UH, UL ) が、実施の形態 1, 2 における入力データ信号 DIn 1 に相当する。

【 0 1 3 1 】

さらに、図 23 - 26 を参照して、実施の形態 2 の変形例について説明する。図 23, 24 は、実施の形態 2 の変形例に係る送信回路 TX 1 の具体的な回路構成の一例を示す回路図である。

40

【 0 1 3 2 】

図 23 では、図 10 と比較して、ライズエッジ検出回路 RED22 を備えていない。そのため、遅延再送要求信号 DRT11 のライズエッジのみでデータ信号を再送し、フォールエッジでは、データ信号を再送しない。これに伴い、禁止期間信号 PP2 を生成する論理回路として、XOR ゲート X02 に代えて、再送要求信号 DRT11 の入力にインバータ ( 図面では で表示 ) を備えた AND ゲート AN3 が用いられている。

【 0 1 3 3 】

図 24 では、図 10 と比較して、ライズエッジ検出回路 RED21 を備えていない。そのため、遅延再送要求信号 DRT11 のフォールエッジのみでデータ信号を再送し、ライズエッジでは、データ信号を再送しない。これに伴い、禁止期間信号 PP2 を生成する論理回路として、XOR ゲート X02 に代えて、遅延再送要求信号 DRT21 の入力にイン

50

バーダ（図面では IN で表示）を備えた AND ゲート AN 3 が用いられている。

【 0 1 3 4 】

図 25、26 は、実施の形態 2 の変形例に係る送信回路 TX 1 の動作の一例を示すタイミングチャートである。図 25 は図 23 の送信回路 TX 1 に、図 26 は図 24 の送信回路 TX 1 に、対応したものである。

【 0 1 3 5 】

図 25 では、図 11 のタイミングチャートと比較して、遅延再送要求信号 DRT 11 のフォールエッジである時刻 t5 では、そもそも総合パルス信号 P10 が出力されない。また、時刻 t5 近傍において、禁止期間信号 PP2 が出力されず、L レベルのままとなっている。その他の点は、図 11 と同様であるため、説明を省略する。

10

【 0 1 3 6 】

図 26 では、図 11 のタイミングチャートと比較して、遅延再送要求信号 DRT 11 のライズエッジである時刻 t1 において、総合パルス信号 P10 及び送信パルス信号 P12 が出力されず、L レベルのままとなっている。また、時刻 t1 近傍において、禁止期間信号 PP2 が出力されず、L レベルのままとなっている。そのため、遅延再送要求信号 DRT 12 のライズエッジである時刻 t2 において、図 11 では出力されていなかった総合パルス信号 P10 及び送信パルス信号 P12 が出力されている。その他の点は、図 11 と同様であるため、説明を省略する。

【 0 1 3 7 】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は既に述べた実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能であることはいうまでもない。

20

【 符号の説明 】

【 0 1 3 8 】

1、2 半導体装置

A1、A2、AN1、AN2 AND ゲート

BW ボンディングワイヤ

C11、C12 電極

CHP1 - CHP4 半導体チップ

CTR1、CTR2 カウンタ

30

DC11、DC12、DC21、DC22、DC31 遅延回路

EDC エラー検出回路

IN1、IN2 インバータ

L11、L21 一次コイル

L12、L22 二次コイル

MCU マイコン

O1 - O6 OR ゲート

OR1 - OR3 OR ゲート

OSC1、OSC2 発振回路

Pd パッド

40

PDC パルス検出回路

PGC パルス生成回路

PKG 半導体パッケージ

PTD パワートランジスタドライバ

PWC1、PWC2 パルス拡幅回路

R12 GMR 素子

RED11、RED12、RED21、RED22、RED31 ライズエッジ検出回路

RX、RX1、RX2 受信回路

SLC 順序回路

T リード端子

50

TM1、TM2 タイマ

TX、TX1、TX2 送信回路

UVLO1、UVLO2 UVLO回路

XO1、XO2 XOゲート

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

(56)参考文献 特表2001-513276(JP,A)

特開2011-146934(JP,A)

国際公開第2011/092864(WO,A1)

(58)調査した分野(Int.Cl., DB名)

|         |     |

|---------|-----|

| H 0 4 L | 2 5 |

| H 0 1 L | 2 1 |

| H 0 1 L | 2 7 |

| H 0 3 K | 1 9 |