(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4267655号

(P4267655)

(45) 発行日 平成21年5月27日(2009.5.27)

(24) 登録日 平成21年2月27日(2009.2.27)

(51) Int.Cl.

F 1

H04L 25/02 (2006.01)

H03K 19/0175 (2006.01)H04L 25/02

H03K 19/00 101F

請求項の数 19 (全 15 頁)

(21) 出願番号 特願2006-284417 (P2006-284417)

(22) 出願日 平成18年10月18日 (2006.10.18)

(65) 公開番号 特開2007-124644 (P2007-124644A)

(43) 公開日 平成19年5月17日 (2007.5.17)

審査請求日 平成20年10月24日 (2008.10.24)

(31) 優先権主張番号 11/263138

(32) 優先日 平成17年10月27日 (2005.10.27)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】電子回路、該電子回路として構成された差分送信機、及び、自己直列終端送信機を形成する方法

(振幅制御、プリ・エンファシス制御及びスルー・レート制御のためのセグメント化と振幅精度

## (57) 【特許請求の範囲】

## 【請求項1】

データ入力ノード、選択入力ノード及び出力ノードと、

前記データ入力ノード及び前記出力ノードに対して並列に配置されている複数のセグメントであって、各セグメントが一対のトランジスタ及び関連の抵抗器を有する複数のセグメントと、

各々がオン/オフ・ゲート信号を前記セグメントの1つのうちの前記一対のトランジスタに供給し、各々が、データ入力及び前記データ入力の相補と、前記セグメントに対して前記データ入力及び前記データ入力の前記相補の1つを前記オン/オフ・ゲート信号として個別に選択できるようにする選択信号入力とを受信する複数のプリ・バッファと、

第1セグメントのゲート入力ノードと第2セグメントのゲート入力ノードとの間に結合されている抵抗器と、

各セグメント内の前記一対のトランジスタの特定のトランジスタをターン・オンまたはオフするのに前記選択信号入力を用いて前記複数のセグメントに所望の出力電圧振幅を生成できるようにする手段と、

前記ゲート入力ノードに信号を供給し続いて前記セグメントをスイッチ・オンする際の遅延が、前記複数のセグメントの全出力にわたって表れるように、前記第2セグメントのプリ・バッファからのオン/オフ・ゲート信号を選択的にターン・オフすることにより、および、前記ゲート入力ノードに信号を前記第1セグメントから前記抵抗器を介して供給することにより、電子回路の出力電流のスルー・レートを制御する手段と、

10

20

を含む電子回路。

【請求項 2】

前記複数のセグメントが、前記出力ノードにわたって所定の出力／チャネル・ターミネーション・インピーダンスを集合的に供給する、請求項 1 に記載の電子回路。

【請求項 3】

各セグメント内の前記一対のトランジスタが、前記出力ノードで直列に接続されているプル・アップ・トランジスタ及びプル・ダウン・トランジスタを含む、請求項 1 に記載の電子回路。

【請求項 4】

前記プル・アップ・トランジスタがドレインでプル・アップ抵抗器に結合され、

前記プル・ダウン・トランジスタがドレインでプル・ダウン抵抗器に結合され、

前記プル・アップ抵抗器及びプル・ダウン抵抗器が前記出力ノードを介して互いに相手側の端部に結合されている、

請求項 3 に記載の電子回路。

【請求項 5】

前記プル・アップ・トランジスタが P 型トランジスタであり、前記プル・ダウン・トランジスタが N 型トランジスタである、請求項 3 に記載の電子回路。

【請求項 6】

各セグメントの前記プル・アップ・トランジスタがソースにおいてその他のセグメント内のその他のプル・アップ・トランジスタのソースとソース電圧ノードとに結合され、

各セグメントの前記プル・ダウン・トランジスタがソースにおいてその他のセグメント内のその他のプル・ダウン・トランジスタのソースとソース電圧ノードとに結合されている、

請求項 3 に記載の電子回路。

【請求項 7】

各セグメントが前記出力電圧振幅の分数部分を供給し、

スイッチ・オンされた各プル・アップ・セグメントが、正の電圧追加分を前記出力電圧振幅に与え、

スイッチ・オンされた各プル・ダウン・セグメントが、負の電圧追加分を前記出力電圧振幅に与え、

前記セグメントのすべてが同一方向に切り換えられると、最大出力電圧が供給され、

前記セグメントの 1 つが、前記セグメントの大部分と反対する方向に切り換えられると、最大出力電圧が前記分数部分の 2 倍だけ減少される、

請求項 3 に記載の電子回路。

【請求項 8】

前記プリ・バッファが前記トランジスタのゲートで零(0)のゲート信号を供給すると、

プル・アップ・セグメントがスイッチ・オンされ、

前記プリ・バッファが前記トランジスタの前記ゲートで 1 のゲート信号を供給すると、

プル・ダウン・セグメントがスイッチ・オンされる、

請求項 7 に記載の電子回路。

【請求項 9】

前記電子回路の測定された電圧特性の較正及び精度を可能にするため、前記電子回路の電圧入力の少なくとも 1 つに適用される調節可能な電圧調整器を更に含む、請求項 1 に記載の電子回路。

【請求項 10】

前記データ入力ノードと前記プリ・バッファとの間に結合されている遅延インバータを更に含み、

前記プリ・バッファが、前記データ入力と、前記データ入力の遅延された相補とを受信する、

請求項 1 に記載の電子回路。

10

20

30

40

50

## 【請求項 11】

前記遅延インバータの遅延構成要素が 1 またはそれ以上のビット・タイムだけ前記データ入力を遅延し、前記電子回路が、

前記複数のセグメントの少なくとも 1 つのセグメントに対して、遅延された反転入力を選択することによりプリ・エンファシス制御を行う手段であって、前記選択は、

( a ) 前記遅延された反転入力を常に選択するため、前記セグメントのプリ・バッファをバイアスすること、及び、

( b ) 必要に応じて、前記遅延された反転入力を確定的に選択することの中からなされる、手段と、

請求項 10 に記載の電子回路。

10

## 【請求項 12】

各選択信号入力が、それぞれのプリ・バッファをターン・オンまたはターン・オフするオン／オフ入力であり、

ターン・オンされると、各プリ・バッファが前記データ入力のみを移動し、ターン・オフされれば、いかなる入力も移動されない、

請求項 1 に記載の電子回路。

## 【請求項 13】

請求項 1 に記載の電子回路として構成された差分送信機であって、各セグメントの個々の出力特性の絶対値の合計である全出力特性を生成するため、前記複数のセグメントの 2 つの分岐がタンデムに動作する差分送信機。

20

## 【請求項 14】

自己直列終端送信機を形成する方法であって、

データ入力ノード、選択入力ノード及び出力ノードを割り当てるステップと、

前記データ入力ノード及び前記出力ノードに対して、トランジスタの並列に接続された複数のセグメントの 2 つの分岐を設けるステップであって、各セグメントが一対のトランジスタ及び関連の抵抗器を有し、

( a ) 前記一対のトランジスタが、前記出力ノードで直列に接続されているプル・アップ・トランジスタ及びプル・ダウン・トランジスタを含み、

( b ) 前記プル・アップ・トランジスタがそのドレインにおいてプル・アップ抵抗器に結合され、

( c ) 前記プル・ダウン・トランジスタがそのドレインにおいてプル・ダウン抵抗器に結合され、

30

( d ) 前記プル・アップ抵抗器及び前記プル・ダウン抵抗器が前記出力ノードを介して互いに相手側の端部に結合され、

( e ) 各セグメントの前記プル・アップ・トランジスタがソースでその他のセグメント内のその他のプル・アップ・トランジスタの前記ソースとソース電圧ノードとに結合され、

( f ) 各セグメントの前記プル・ダウン・トランジスタがそのソースにおいて、その他のセグメント内のその他のプル・ダウン・トランジスタのソースとソース電圧ノードとに結合される、ステップと、

40

各セグメントに対してプリ・バッファを設け、前記プリ・バッファの出力ノードからのオン／オフ・ゲート信号を前記セグメント内の前記一対のトランジスタのゲートに接続するステップと、

前記プリ・バッファの第 1 入力ノードをデータ入力に結合し、第 2 入力ノードを前記データ入力の相補に結合するステップと、

前記セグメントに対して前記データ入力ノード及び前記データ入力ノードの前記相補の 1 つを前記オン／オフ・ゲート信号として個別に選択できるようにする選択信号入力信号を前記プリ・バッファに供給するステップと、

第 1 セグメントのゲート入力ノードと第 2 セグメントのゲート入力ノードとの間に抵抗器を結合するステップと、

50

これにより、前記ゲート入力ノードに信号を供給し続いて前記セグメントをスイッチ・オンする際の遅延が、前記複数のセグメントの全出力にわたって表れるように、前記第2セグメントのプリ・バッファからのオン／オフ・ゲート信号を選択的にターン・オフすることにより、および、前記ゲート入力ノードに信号を前記第1セグメントから前記抵抗器を介して供給することにより、送信機出力電流のスルー・レートがその動作中に制御され、前記選択信号が前記プリ・バッファをターン・オンまたはオフし、前記プリ・バッファがターン・オンされると、前記データ入力のみが移送され、前記プリ・バッファがターン・オフされると、いかなる入力も移送されない、ステップと、

を含み、

前記送信機の構成が、各セグメント内の前記一対のトランジスタの特定のトランジスタをターン・オンまたはオフするのに前記選択信号入力を用いて前記複数のセグメントに所望の出力電圧振幅を生成できるようにし、

10

前記複数のセグメントの前記2つの分岐が、各セグメントの個々の出力特性の絶対値の合計である全出力特性を生成するためタンデムに動作する、

方法。

【請求項15】

(a) セグメントを加えるか差し引くこと、及び、(b) セグメント内の抵抗器の値を変更することの1つまたはそれ以上によりターミネーション・インピーダンスを前記出力ノードで較正して、前記複数のセグメントが、前記出力ノードにわたって所定の出力ノチュネル・ターミネーション・インピーダンスを集合的に供給するステップを更に含む、

20 請求項14に記載の方法。

【請求項16】

各セグメントが前記出力電圧振幅の分数部分を供給し、

スイッチ・オンされた各ブル・アップ・セグメントが、正の電圧追加分を前記出力電圧振幅に与え、

スイッチ・オンされた各ブル・ダウン・セグメントが、負の電圧追加分を前記出力電圧振幅に与え、

前記セグメントのすべてが同一方向に切り換えられると、最大出力電圧が供給され、

前記セグメントの1つが、前記セグメントの大部分と反対する方向に切り換えられると、

30 最大出力電圧が前記分数部分の約2倍だけ減少される、

請求項14に記載の方法。

【請求項17】

前記ブル・アップ・トランジスタがP型トランジスタであり、前記ブル・ダウン・トランジスタがN型トランジスタであり、

前記プリ・バッファが前記トランジスタの前記ゲートで零(0)のゲート信号を供給すると、ブル・アップ・セグメントがスイッチ・オンされ、

前記プリ・バッファが前記トランジスタの前記ゲートで1のゲート信号を供給すると、

ブル・ダウン・セグメントがスイッチ・オンされる、

40 請求項14に記載の方法。

【請求項18】

回路の測定された電圧特性の較正及び精度を可能にするため、前記回路の電圧入力の少なくとも1つにオン・チップの調節可能な電圧調整器を接続するステップを更に含む、

請求項14に記載の方法。

【請求項19】

前記データ入力ノードと前記プリ・バッファとの間に結合されている遅延インバータを設けるステップを更に含み、

前記プリ・バッファが、前記データ入力と、前記データ入力の遅延された相補とを受信し、

前記複数のセグメントの少なくとも1つのセグメントに対して、遅延された反転入力を選択することにより前記送信機の動作中のプリ・エンファシス制御を可能にするため、

50 前

記述延インバータの遅延構成要素が 1 またはそれ以上のビット・タイムだけ前記データ入力を遅延し、

前記選択は、

( a ) 前記遅延された反転入力を常に選択するため、前記セグメントのプリ・バッファをバイアスすること、及び、

( b ) 必要に応じて、前記遅延された反転入力を確定的に選択することの中からなされる、

請求項 1 4 に記載の方法。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、概して、電子回路に関し、特に、送信機回路に関する。更に詳しくは、本発明は、シリアル・リンク送信機回路及びその設計に関する。

【背景技術】

【0002】

デジタル・データの高速伝送を実行及び達成する能力は、今日のコンピュータ環境において期待されるようになった。ほとんどの場合、長距離にわたるデジタル・データの伝送は、コンピュータ通信を処理するように設計された通信リンク上でデータを高速シリアル形式で（すなわち、シングルビットを次々に）送信することにより遂行される。このようにして、コンピュータ・システムが地理的に遠くても、データをあるコンピュータ・システムから別のコンピュータ・システムへ転送することができる。

20

【0003】

高速シリアル伝送が生じるためには、シリアル通信リンク上でデータを伝送する前に、コンピュータ内部からのデジタル・データ信号をパラレル形式からシリアル形式へ変換しなければならない。この変換は、シリアル・リンク送信機または「シリアルライザ」として既知である電子回路を介してコンピュータの内部データ信号を処理することにより一般に達成される。シリアルライザの機能は、入力としての並列データ・ストリームを受信し、並列データ・ストリームを操作することにより、適切な通信リンク上で高速伝送できるシリアル形態のデータを出力することにある。シリアル化データが所望の送り先に到着した後、「デシリアルライザ」として既知であるコンピュータ機器の一部が、送り先のコンピュータ・システム内で受信データを用いるため、シリアル形式からパラレル形式へ変換するのに用いられる。

30

【0004】

従来の高速シリアル・リンク送信機は電流モード回路技術を用いて典型的に実装されているので、ソース端で並列ターミネーションを必要とする。しかし、ソース端並列ターミネーションが用いられる場合、送信機の 2 つの並列な出力側の一方だけを介して送信機が受信機に電流を導くため、送信機の出力電流の半分だけが受信機に移動される。従って、所望の出力振幅（例えば、電圧）を発生させるために、並列ターミネーションを有する電流モード送信機は、電流の約 50 % の損失に合わせる調節のために比較的大きい電力消費を必要とする。

40

【0005】

所望の出力振幅を発生する際のこの大きい電力消費要件を削減するため、1 つには、自己直列終端送信機が導入されはじめてきた。自己直列終端送信機の場合、送信機の出力電流のほとんどすべてが受信機に移動する。従って、自己直列終端送信機の出力電流すべてが受信機に移動するので、受信機における所定の信号振幅に対して、自己直列終端送信機は、並列ターミネーションを有する電流モード送信機よりも著しく少ない電力を消費する。

【発明の開示】

【発明が解決しようとする課題】

【0006】

50

従来技術において何種類かの自己直列終端送信機が記述されている。自己直列終端送信機は効率の良く電力を使用するが、特に出力振幅制御、プリ・エンファシス制御及びスルーレート制御に関する設計を含む従来の設計では、幾つかの他の制限が指摘されている。従って、データ伝送速度が増大し続けるので、送信機がますます向上する必要がある。

【課題を解決するための手段】

【0007】

電圧調整、振幅精度及び高電圧保護を達成しながら、振幅、プリ・エンファシス及びスルーレートの優れた制御を行うセグメント化自己直列終端（S S S T）送信機を開示する。送信機は、並列に配置されている複数のセグメントを有し、所望の出力インピーダンスに等しく組み合わされた並列インピーダンスを有するように設計されている。一実施形態では、供給電圧を調整することによりかなり正確な出力電圧を可能にする電圧調整器が供給入力端に設けられている。通常の入力信号及び反転入力信号の両方は一連のバッファを介して供給され、各バッファはセグメントの1つの入力ノードに接続されている。通常の入力信号または反転入力信号のどちらかを選択する選択入力信号が各バッファに供給される。すべてのセグメントが同一の（通常または反転）入力を受信すれば、（通常または反転された）全出力信号は出力受信機で供給される。セグメントの1つ以上が反転入力を受信するが、他のセグメントが通常の入力を受信すれば、出力信号は、選択信号の総数の合計に対する反転選択信号の割合に基づいて全信号の分数部分に減少する。

10

【0008】

S S S T送信機によるスルーレート制御及びプリ・エンファシス制御を可能にするため、S S S T送信機の設計への更なる機能強化も行われる。前者の送信機では、抵抗器がバッファ入力端間に配置され、1つのバッファがターン・オフされて單一バッファに2つ以上のセグメントを駆動させ、従ってスルーレートを制御する。後者の送信機では、遅延された反転信号が少なくとも1つのセグメントに供給されて、出力信号のエンファシス制御を改善するように生成されたハイ信号及びロー信号を強調する。

20

【発明を実施するための最良の形態】

【0009】

上述した目的、特徴及び利点の他に本発明の追加の目的、特徴及び利点も、下記の詳細な説明において明らかになるであろう。

【0010】

30

添付図面と併せて読む図示の実施形態の詳細な説明を参考することにより本発明自体を最も良く理解するであろう。

【0011】

本発明は、抵抗器と関連付けられたデュアル・プル・アップ及びプル・ダウン・トランジスタの複数の個々に制御できるセグメントのパラレル構成を有するセグメント化自己直列終端（S S S T）送信機の設計を用いて振幅、プリ・エンファシス及びスルーレートの柔軟な制御を可能にする回路設計方法及び送信機を提供する。振幅制御、スルーレート制御及びプリ・エンファシス制御は、様々なセグメントに対する通常入力または反転入力の選択により可能になる。本発明は、供給電圧を調整することにより、（ソース直列終端送信機とも称する）自己直列終端（S S T）送信機の全体にわたって正確な出力振幅を供給／維持する機構をも提供する。供給電圧の調整は従来のシリアル・リンク受信機タミネーション電圧との互換性を可能にし、これら電圧が装置への通常の供給よりも大きければ送信機出力装置を保護する。

40

【0012】

本発明の各機能は、下記のセクションの先頭に記述している特定機能を可能にする送信機入力の異なる構成を含む。特に、4つの主な構成、すなわち、（a）電圧調整及び（b）セグメント化の両方を含む（1）出力振幅調整／制御、（2）プリ・エンファシス制御及び（3）スルーレート制御を提供し、各々を本明細書内で別々のセクションに記述する。

【0013】

50

本発明に従って設計された送信機を標準の自己直列（またはソース直列）終端（SST）送信機から区別するため、本発明の送信機をセグメント化自己直列終端（SSTS）送信機と称し、本発明の送信機が、図面及び以下の説明により示すように本発明の実施形態に従ってセグメントに構成されていることを表す。特に断りのない限り、以後に記述する送信機への言及はSSTS送信機を対象とする。

【0014】

ここから図面を参照する。図面は、まず、電圧調整を用いるSST送信機（図1）を示し、次に、本発明に従って構成されたSSTS送信機の3つの実施形態（図2～4）を示す。異なる図面において、図中、同一の符号は同様の要素に付されているが、新たな特徴が図に初めて示されれば、新たな特徴には別の符号が付されている。

10

【0015】

A. 振幅制御

1. 電圧調整

【0016】

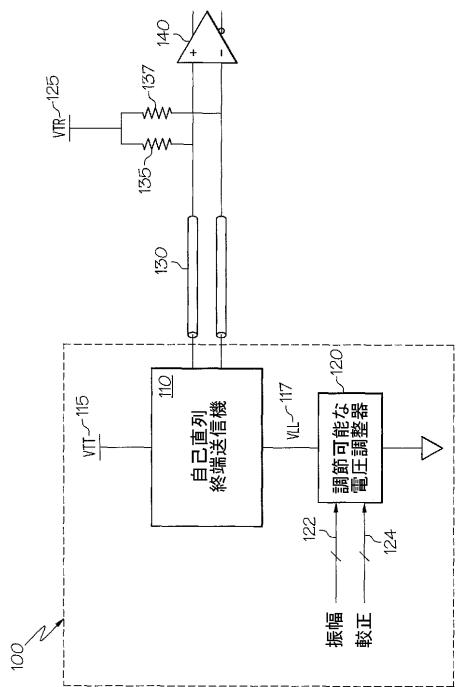

先に述べたように、図1は、（新たに設計されたSSTS送信機を含まない）第1実施形態に従い、入力において電圧較正及び振幅調整を可能にする調節可能な電圧調整器の追加により改良された設計及び動作を有するSST送信機を表すロー・レベルのブロック図である。

【0017】

従来のSST送信機は、出力電圧の振幅及び精度を制御できるようにする何らかの機構を有するように設計されていない。しかし、一般的なシリアル・リンク規格に準拠するため、送信機は、正確な（信頼できる）出力振幅を生成できるよう要求されている。従って、シリアル・リンク設計において、異なる出力振幅を供給するため、供給電圧に調節が要求されることもある。しかも、送信機パッケージまたはコネクタ内の信号損失は、信号損失を無効にするため、例えば10%、20%または30%だけ電源を増大させるような何らかの形態の較正により出力振幅を固定するよう要求する場合がある。

20

【0018】

出力電圧が変動することが多い正規の電源に直接接続する自己直列終端送信機の従来の設計及び使用を用いると、一般的に出力振幅を調整及び制御することができない。通常、供給電圧は変動しすぎて充分な振幅精度にすることはできない。また、一般には、供給電圧を容易に調節することができない。

30

【0019】

従って、図1は、自己直列終端送信機が精度及びサイズの両方に関して所望の振幅要件を満足できる一方法を提供する。図示のように、SST送信機110は、高電圧ノード（入力端）で高電圧レール115に接続され、低電圧ノード（入力端）で調節可能な電圧調整器120に接続されている。調節可能な電圧調整器120は2つの入力信号すなわち振幅信号122及び較正入力信号124を受信する。実装される実施形態によれば、調節可能な電圧（例えば、VLL117）は、SST送信機の電源電圧の一方または両方に供給される。VLL117は、（変動することが多い）電源よりも正確な電力を供給するので、SST送信機110により供給される出力振幅を優れた精度にすることができます。更に、外部電源へ何らかの変更を必要とせず、送信機供給電圧を所望の値に動的に設定（調節）することができる。従って、送信機パッケージまたはコネクタ内の信号損失のいずれをも考慮するため、調節可能な電圧調整器120により更にSST送信機110を容易に較正することができる。

40

【0020】

自己直列終端送信機110は、チャネル130を介して差動出力信号を受信機140に転送する。両方の差動出力信号線は、高電圧端で互いに且つターミネーション電圧レールすなわちVTR125に接続されているそれぞれのプル・アップ抵抗器135/137（受信機ターミネーション・インピーダンス）に接続されている。受信機140及びプル・アップ抵抗器135/137が代表的なシリアル・リンク受信機構成を表すことに留意す

50

べきである。別の構成も可能である。

【0021】

前述の構成要素を有する改良された送信機回路100を用いることにより、SST送信機110は受信機端で振幅精度要件を達成することができる。更に、調節可能な電圧調整器120は、可変且つ正確な振幅を達成できるようにする。代替の実施形態では、調節可能な電圧調整器120は、振幅損失の補償を可能にする調節可能なスケーリング係数を含むこともできる。最も現実的なシステムが、出力振幅に影響を与えるおそれのある可変損失を有するので、この代替の実施形態が実装される。

【0022】

特に、図1は、SST送信機110の低電圧入力端に結合されている单一の調節可能な電圧調整器120を示している。従って、調節可能な電圧調整器120はSST送信機110に低供給電圧を生成する。この特定の構成は、受信機の上側供給レールに接続されているDCターミネーション・インピーダンスを有する最も一般的なシリアル・リンク受信機構造との互換性を可能にする。しかし、この実施形態が図示されているが、本発明の(図示していない)別の実施形態も幾つかの代替の電圧調整器構成を提供する。例えば、1つの実行可能な実施形態では、調節可能な電圧調整器は高供給電圧入力端に結合されているが、別の実行可能な実施形態では、2つの調節可能な電圧調整器が設けられ、一方は低電圧電源に結合され、他方は高電圧電源に結合されている。

【0023】

2. セグメント化による振幅制御

【0024】

上記の改良されたSST構成が出力振幅及び較正の測定可能な制御を行うが、送信機が可変供給電圧を受けると、回路性能の変動を生じさせることがあり、その結果として、幾つかの実施形態で、特に、送信機の出力振幅を調節するのに電圧調整器120が用いられる場合、上記のシステム設計を困難なものにする。幾つかの実施形態では、正確な出力振幅を達成するため、特定の出力振幅要件が、低すぎて正確に回路を動作することができない(すなわち、トランジスタが、ターン・オン/動作するのに充分大きい電流を受信することができないか、または、正確に動作するのに必要とされる電圧よりも低い電圧を受信するおそれがある)入力電源電圧を要求する場合がある状況が生じるおそれがある。

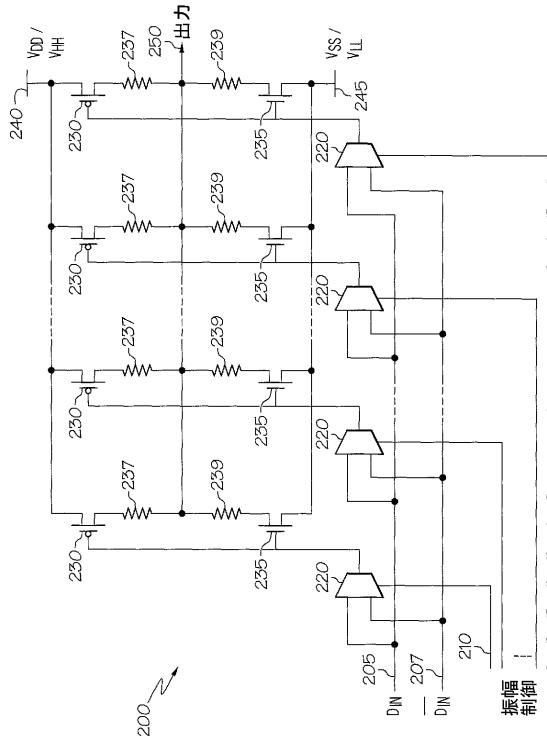

【0025】

従って、1つ以上の電圧調整器を追加することにより改良されたSST送信機を特に用いる上記の実施形態に加えて、本発明の他の実施形態は、セグメント化SST送信機(または、上記に提示したSSST送信機)を提供する。図2には、SSST送信機の構成を示す。図2に示すように、(設計が既知である)SST送信機と異なって、SSST送信機は、(垂直に見て)対になって接続されているトランジスタ及び抵抗器の並列セグメントを用いて設計されている。各セグメントは、出力波形を生成するため、入力データにより切り換えられるブル・アップ及びブル・ダウン素子から成っている。ブル・アップ素子は、高入力レール( $V_{HH}$ )240にソースで接続され、ブル・アップ抵抗器237にドレインで接続されたP型トランジスタ230を含む。ブル・ダウン素子は、低入力レール( $V_{LL}$ )245にソースで接続され、ブル・ダウン抵抗器239にドレインで接続されたN型トランジスタ235を含む。ブル・アップ抵抗器237及びブル・ダウン抵抗器239は共通ノードで(直列に)接続されている。共通ノードは各セグメントを介して接続され、出力信号250を生成する。この実施形態によれば、SSST送信機200は、多数の独立して制御できるセグメントに分割されている。図示では、4つのセグメントだけが設けられている。しかし、破線により示唆されるように、実際に用いられるセグメントの数は、SSST送信機200に望まれる制御の精度に関連する設計パラメータである。従って、例えば、SSST送信機200は、16、20、32、64またはその他のあらゆる数のセグメントを含むことができる。

【0026】

セグメントの各々は、並列組み合わせが所望のチャネル・ターミネーション・インピー

10

20

30

40

50

ダンスに等しいように特定の出力インピーダンスを有する。各セグメントのインピーダンスを抵抗器インピーダンス及びトランジスタ・インピーダンスの組み合わせとすることができる。しかし、プル・アップ抵抗素子またはプル・ダウン抵抗素子あるいはその両方を必要とせずに所望のインピーダンスを生成するのに充分小さいトランジスタが用いられると考えられる。同様に、トランジスタが、無視できるインピーダンスを生成するように充分トランジスタを大きくすることができ、これにより、一度に1つのトランジスタ（スイッチ）だけがオン状態であるので、各セグメントのインピーダンス値がそれぞれプル・アップ抵抗器またはプル・ダウン抵抗器のどちらかに等しくなる。

## 【0027】

図示の実施形態では、用いられているトランジスタはMOSトランジスタ（すなわち、P MOS及びN MOSトランジスタ）である。MOSトランジスタとして記述するが、当然のことながら、異なる種類のトランジスタを用いて本発明を実装することができ、従って、本発明は、本明細書に開示したものだけに限定されない。例えば、トランジスタを他の種類のFETやバイポーラ・トランジスタなどとすることができる。最後に、当業者は、提示した図が、完全な差動送信機の半分（上半分または下半分）だけを示すものであって、両半分は全く同一であることを理解するであろう。従って、実際の送信機出力は両半分における出力の組み合わせである。両半分がタンデムに動作すれば、それらは、等しい振幅を有するが、互いに反転された出力を生成する。その結果、片半分の反転の後、組み合わされた出力は、図示した回路の出力信号250の2倍（2X）である。

## 【0028】

SSST送信機設計の実装は、（図1の）調節可能な電圧調整器を必要とせず、送信機出力振幅の柔軟な制御を可能にさせる。更に、この構成は、トランジスタを正常に動作できるほど大きくない入力電源に関するいかなる問題をも削減する。各セグメントへの入力は、P型トランジスタ230及びN型トランジスタ235に加えられるゲート入力である。図示のように、各セグメントの入力は、入力源（図示せず）からのデータ入力205とデータ入力の相補すなわち反転データ入力207との両方を実際に受信するそれぞれのバッファ220（または反転バッファ）から受信されたバッファ入力である。個別化された振幅制御入力210はバッファ220に供給され、バッファが通常のデータ入力205または反転データ入力207を特定のセグメントに移せる選択入力として作用する。例えば、振幅制御入力210が1であれば、反転データがセグメントに送信されるが、振幅制御が0であれば、通常のデータ入力がセグメントに送信される。図示の実施形態では、振幅制御入力210が0であれば、バッファ220は通常のデータ入力205をセグメントに移動する。あるいはまた、振幅制御入力210が1であれば、バッファ220は反転データ入力207をセグメントに移動する。移動されたデータ入力は1または0であり、それぞれP型トランジスタ230またはN型トランジスタ235をターン・オンする。すなわち、バッファを通過するよう選択されたデータが0である場合、0の入力データは、P型トランジスタをターン・オンする（その一方で、N型トランジスタをターン・オフする）ことによりセグメントの上部分岐がプル・アップとなるようにする。これと反対に、バッファを通過するよう選択されたデータが1である場合、1の入力データは、N型トランジスタをターン・オンする（その一方で、P型トランジスタをターン・オフする）ことによりセグメントの下部分岐がプル・ダウンとなるようにする。プル・アップ及びプル・ダウン動作が生じる間、セグメントにわたる抵抗は同じ状態のままである。

## 【0029】

最大振幅を達成するため、すべてのセグメントは未修正の（通常の）入力データ信号で駆動される。低い振幅を生成するため、セグメントのサブセット（すなわち、1つまたはそれ以上）が反転データにより駆動される。反転されたセグメントの各々は、それ自体と、通常のデータ入力を受信する別のセグメントとにより生成された出力振幅の一部を相殺する。特に、セグメントにわたる並列抵抗の組み合わせが所望の出力抵抗に加算されるように抵抗器の値が選択される。従って、SSST送信機は、ターミネーション・インピーダンスを減少することなく、またはこれに影響を与えることなく、出力振幅を選択可能に

10

20

30

40

50

減少できるようにする。この方法は、許容可能な回路性能に対して供給電圧が充分に大きいまま維持できるようにしながら、最大振幅の定義された分数である振幅を生成する。この実施形態では、セグメントの総数と、反転入力信号で駆動されているセグメントの数とを用いて出力電圧の減少率を計算することができる。完全な送信機の（図示のような）片半分のみに用いるこのような計算の式は、「 $actual = max \times fraction$ 」であり、特に、

実際の出力振幅 = 最大出力振幅 × [ (セグメント数 - 2 × 反転セグメント数) / セグメント数 ]

#### 【0030】

特に、反転されたセグメントが、等しい数の反転されていないセグメントの電圧利得を相殺するので、この計算は、2倍の反転セグメントを差し引くことを含む。同じ解析により、より多くのセグメントが反転データ入力を受信すれば、出力信号は、出力信号の極性の反転を示す負の値となる。実際の回路動作では、理想的なピーク・ツー・ピーク差動出力振幅は  $V_{H\text{--}} - V_{L\text{--}}$  に等しい。

10

#### 【0031】

SSST送信機を用いる別の実施形態では、振幅制御は、一連（1つ以上）のセグメントを、残りのセグメントから受信される反転入力に対して静的に設定することにより行われる。従って、ある割合のセグメントを反転データで駆動するよりはむしろセグメントが静的に設定される。その結果、セグメント対が反対に設定されると、一定のデータ値、類似の振幅減少及び一定のインピーダンスが、（図2の振幅制御入力により示した）上記に述べたようにセグメントを設定する動的な方法と同様に生成される。この実施形態は、入力電圧に対して設定された出力電圧を供給する。

20

#### 【0032】

特に、一実施形態では、振幅制御のセグメント化方法は、極めて柔軟且つ正確な送信機振幅制御を行うために（上記の関連セクションに記述した）電圧調整器方法と組み合わされている。セグメント化により所望の出力インピーダンスを維持しながら振幅を調節できると同時に、一定の調整器が、良好な回路性能を可能にする振幅精度及び供給レベルを達成する。

#### 【0033】

B. プリ・エンファシス制御

30

#### 【0034】

上述した送信機内で要求され、次に提供する制御の1つはエンファシス（特に、プリ・エンファシス）制御である。本明細書で用いられるプリ・エンファシスは、伝送チャネルにわたる伝送中の全体的な信号対雑音（S/N）比を改善するため低周波成分に対して高周波成分を強調する処理を意味する。高周波成分を送信機端で強調／誇張することにより、プリ・エンファシスは、チャネルの帯域幅制限と、結果として生じる符号間干渉（ISI）とを緩和し（または、その悪影響を最小限に抑え）ようとする。従来のシリアル・リンク送信機は、出力信号の遅延バージョンが主信号から差し引かれて、チャネルの低域特性を特に相殺する高域特性を生成する有限インパルス応答（FIR）デジタル・フィルタに類似する構造により調節可能な出力信号プリ・エンファシス機能を典型的に行う。

40

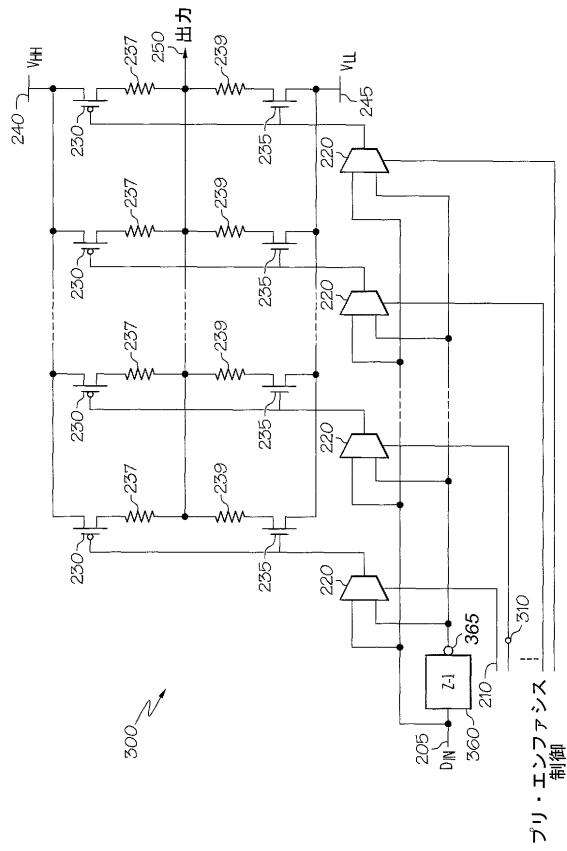

#### 【0035】

次に、図3を参照する。図3は、図2のSSST送信機200が、一実施形態に従ってプリ・エンファシス制御を行うように更に適合され／改良されたことを示している。上述したセグメント及びバッファ220に加えて、SSST送信機200は、プリ・エンファシス制御を可能にするのに異なる入力を含む。図2の実施形態における電力振幅の通常の信号入力及び反転信号入力よりも、図3のSSST送信機は、バッファ220まで第2入力経路に沿って送信される入力信号のコピーを遅延し、その後、入力の遅延されたコピーを反転するため、インバータ365が後に続く遅延素子360を含む。遅延素子360は、受信した入力信号を1ビット・タイム（すなわち、入力信号の1ビットが入力端を通過する時間）だけ遅延する。バッファ220の観点から、時間T1で受信した入力は通常の

50

データ入力 205 と時間 T0 からの反転データ入力とである。すなわち、バッファ 220 までの第1入力経路でのデータ入力（通常のデータ入力）が 10101100 であると仮定すると、第2入力経路で考えられる入力は -0101001 である。

#### 【0036】

代替の実施形態では、複数の遅延バージョンのデータ・ストリームをイネーブルにするのに複数の遅延素子（または、複数の遅延を行う単一の素子）を設けることができる。例えば、1、2、3 またはそれ以上のビット・タイムによる遅延を行うことができる。適切に遅延されたデータを一群のセグメントに供給するだけで、この一般的なプリ・エンファシス・アプローチと互換性があるように SSSST 送信機が設計される。

#### 【0037】

図示の実施形態によれば、多数の独立して制御できるセグメントとして送信機を表すことにより、調節可能なプリ・エンファシス制御を自己直列終端送信機すなわち SSSST 送信機 300 の特定の実施形態内に実装することができる。上述のように、セグメントの並列組み合わせが所望のチャネル・ターミネーション・インピーダンスに等しいようにセグメントが出力インピーダンスを有する。更に、各セグメントは、出力波形を生成するために入力データにより選択的に切り換えられるプル・アップ及びプル・ダウン素子より成る。

#### 【0038】

図示の実施形態では、特定レベルのプリ・エンファシスが、選択されたサブセットのセグメントを、（バッファからの）遅延された反転データで駆動することにより生じる。遅延された反転入力データを受信するのに単一のセグメントがバイアスされる（すなわち、バッファへの選択入力が、常にターン・オンされる「1」）と仮定すれば、遷移後の第1データ・ビットに対して、すべてのセグメントは同一方向にプルし、送信機は全振幅出力を生成する。これにより、各遷移中、送信機が瞬時に全振幅を生成することができる。1ビットよりも大きい切り換えラン長（連続した 0 または 1）に対して、遅延したセグメントは逆方向にプルし、結果として生じたインピーダンスの分割は出力を、全振幅の定義された分数まで減少させる。従って、事実上、この発生は低周波を「強調解除」する。入力を遅延し、反転し、SSSST 送信機 300 により生成された全出力から差し引くことが、SSSST 送信機 300 まで拡張された入力の全体的な効果である。

#### 【0039】

振幅及びプリ・エンファシス制御用のセグメント化方式が充分な互換性を有し、従って、同一の SSSST 送信機内に組み入れられてもよいことに留意すべきである。この 2 重機能 SSSST 送信機の場合、セグメントの幾つかはプリ・エンファシス制御のために設けられるが、その他のすべては振幅制御のために設けられる。

#### 【0040】

C. スルー・レート制御

#### 【0041】

しばしば、シリアル・リンク送信機は、出力信号スルー・レートを調節する機能を有するように設計されている。スルー・レートは、送信機の出力電圧の最大変化率を意味する。すなわち、スルー・レートは、どのくらい速く出力が移動するかという 1 秒当たりの電圧で測定される測度を供給する。誤ったスルー・レートは、他のチャネルとのクロス・トーク干渉の原因となるおそれがある。

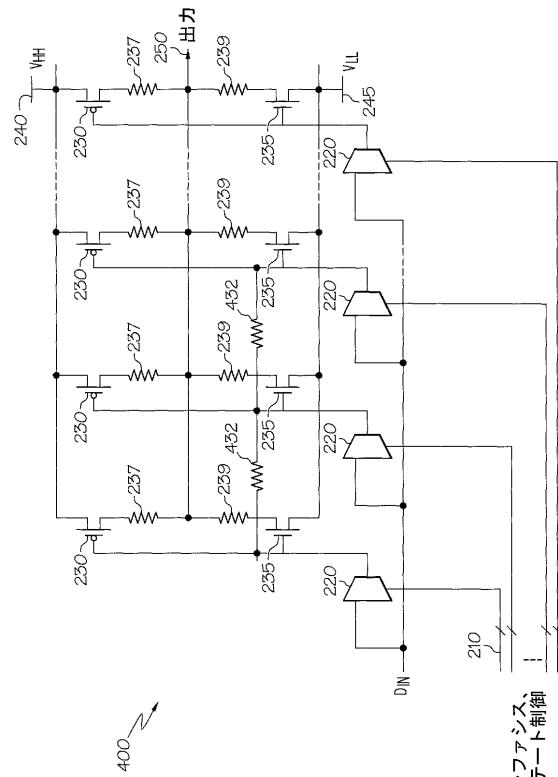

#### 【0042】

図 4 は、出力スルー・レートを制御する手段をどのようにして自己直列終端送信機回路のセグメント化が用いるかを表している SSSST 送信機 400 への機能強化を示す。各出力セグメントは、高出力インピーダンス状態を呈するよう構成できる（プリ・バッファとも称する）別々のバッファ 220 により起動される。選択された一連のセグメント（すなわち、1 つ以上の連続的なセグメント）に対して、各バッファ 220 の出力端は、スルー制御抵抗器 432 を介して前のセグメントのプリ・バッファの出力端に永久的に接続されている。スルー制御抵抗器へのこの接続は、セグメントの P 型及び N 型トランジスタのゲ

10

20

30

40

50

ートに追加される。すなわち、図示のように、スルー制御抵抗器 432 の一端は最初のプリ・バッファの出力端に接続され、しかも、図示のように、スルー制御抵抗器 432 の他端は、（連続する）次のプリ・バッファの出力端に接続されている。

【0043】

動作中、いかなる入力データ信号もバッファ 220 を通過しないように、出力に接続されたスルー制御抵抗器 432 を有するそれぞれの後のバッファ 220 はターン・オフされる（オフ状態に置かれる）。どのシーケンスのプリ・バッファ出力がスルー制御抵抗器 432 と相互接続し、その後、どのバッファ 220 がターン・オフされるかの決定は設計により決定される。しかし、同一の出力（すなわち、通常の入力データまたは反転入力データ）を有するプリ・バッファのみがこのように直列に接続される。2つの異なる一連の直列接続されたプリ・バッファ出力を S S S T 送信機 400 内に設けることができる。

10

【0044】

直列に接続されているプリ・バッファの最初のプリ・バッファは、接続されたセグメントの各々のドライバとして動作する。直列の後続するプリ・バッファがターン・オフされると、これらプリ・バッファに関連するセグメントは（複数の）スルー制御抵抗器 432 を介して最初のプリ・バッファから入力を受信する。最初のプリ・バッファは、増大した負荷（スルー制御抵抗器 432 及び後続のセグメントのトランジスタ）を供給し、従って、出力遷移の速度が減速される。更に、スルー制御抵抗器 432 はそれら自体、遅延を生成し、異なる時間で（次々と）セグメントに切り換えを行わせる。一連のセグメントを介する入力データの減速動作による遅延切り換えのため、出力も、先に切り換えられたセグメントに比べて遅い速度で受信される。従って、出力信号は遅延され、後に切り換えられるセグメントが、先に切り換えられたセグメントと同じ状態になるまで待機しなければならない。

20

【0045】

上述の構成では、全グループ内のバッファ 220 の一部を高インピーダンス状態に置き、残りのバッファ 220 にグループ内のすべての出力セグメントを駆動できるようにさせることにより S S S T 送信機の出力のスルー・レートを減少させることができる。スルー制御抵抗器 432 を介して駆動される出力セグメントは、入力端で信号を受信する際、わずかに遅延するようになる。これら遅延は、最終送信機出力端でセグメントの出力を合計すると出力スルー・レートを減少させる。

30

【0046】

特に、この実施形態では、図 2 の場合のようにデュアル（差動）入力を必要とする図示した他の S S S T 送信機と異なり、単一の制御入力が用いられる。一実施形態では、バッファ 220 から受信した制御信号を用いて、どのプリ・バッファをオフ状態に置くべきかを決定することができる。上述の設計では、スルー制御抵抗器 432 の両端が同じ電圧にあり、従って、接続されたセグメント間に電流の流れを生じさせないので、すべてのバッファがオン状態にあれば、送信機の通常動作への影響はない。ターン・オフされると、バッファ 220 は、逆流する電流を遮断する高インピーダンス装置になる。

【0047】

特に、送信機における最初の 2 つのセグメントのプリ・バッファがスルー制御抵抗器 432 をサポートするように示されているが、当業者は、複数の利用可能なセグメントのうちの（最初のセグメント以外の）いかなるセグメントも、スルー制御抵抗器 432 を介して入力信号を受信するために配線でき、本明細書で与えた特定の記述が、本発明を示すためだけのものであることを理解するであろう。

40

【0048】

好適な実施形態に関して本発明を特に図示し、説明したが、当然のことながら、当業者は、本発明の精神及び範囲から逸脱することなく、様々な形態及び詳細の変更を行うことができる。

【図面の簡単な説明】

【0049】

50

【図1】本発明の一実施形態に従って自己直列送信機への入力電圧を調整する調節可能な電圧調整器の使用を示すハイ・レベル図である。

【図2】本発明の一実施形態によるセグメント化自己直列終端送信機( S S S T T )の回路図である。

【図3】本発明の一実施形態に従ってプリ・エンファシス制御用に遅延及びインバータ・ユニットを有する S S S T T の回路図である。

【図4】本発明の一実施形態に従ってスルー・レート制御用に追加の抵抗器を有する S S S T T の回路図である。

【符号の説明】

【0050】

- |             |                            |

|-------------|----------------------------|

| 100         | 改良された送信機回路                 |

| 110         | 自己直列終端( S S T )送信機         |

| 115         | 高電圧レール                     |

| 120         | 電圧調整器                      |

| 125         | ターミネーション電圧レール( V T R )     |

| 130         | チャネル                       |

| 140         | 受信機                        |

| 135、137     | プル・アップ抵抗器                  |

| 200、300、400 | S S S T 送信機                |

| 220         | バッファ                       |

| 230         | P型トランジスタ                   |

| 235         | N型トランジスタ                   |

| 237         | プル・アップ抵抗器                  |

| 239         | プル・ダウン抵抗器                  |

| 240         | 高入力レール( V <sub>H H</sub> ) |

| 245         | 低入力レール( V <sub>L L</sub> ) |

| 360         | 遅延素子                       |

| 365         | インバータ                      |

| 432         | スルー制御抵抗器                   |

10

20

【 四 1 】

【 図 2 】

【図3】

### 【図4】

ブリ・エンファシス、

トライステート制御

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 ハイデン・シー・クランフォードジュニア

アメリカ合衆国 27519 ノースキャロライナ州 キャリー ブラントン・ドライブ 690

0

(72)発明者 キャリー・イー・コックス

アメリカ合衆国 27519 ノースキャロライナ州 キャリー カトリーン・ロード 403

(72)発明者 スティーブン・エム・クレメンツ

アメリカ合衆国 27615 ノースキャロライナ州 ラレイ ホワイトストン・ロード 102

08

(72)発明者 トッド・エム・ラスムス

アメリカ合衆国 27513 ノースキャロライナ州 キャリー ベネディッティ・コート 10

4

(72)発明者 ウィリアム・ピー・コーンウェル

アメリカ合衆国 27713 ノースキャロライナ州 ダーラム チェセルデン・ドライブ 70

4

審査官 白井 亮

(56)参考文献 特開2004-327602 (JP, A)

特開2001-222474 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 25/00 - 25/66

(54)【発明の名称】電子回路、該電子回路として構成された差分送信機、及び、自己直列終端送信機を形成する方法

(振幅制御、プリ・エンファシス制御及びスルー・レート制御のためのセグメント化と振幅精度

及び高電圧保護のための電圧調整とを有する自己直列終端シリアル・リンク送信機)