(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-100877

(P2011-100877A)

(43) 公開日 平成23年5月19日(2011.5.19)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 29/78</b> (2006.01)  | H01L 29/78 | 652N        |

| <b>H01L 21/336</b> (2006.01) | H01L 29/78 | 652D        |

|                              | H01L 29/78 | 653A        |

|                              | H01L 29/78 | 652S        |

|                              | H01L 29/78 | 658A        |

審査請求 未請求 請求項の数 5 O L (全 13 頁)

|           |                              |          |                                       |

|-----------|------------------------------|----------|---------------------------------------|

| (21) 出願番号 | 特願2009-255078 (P2009-255078) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (22) 出願日  | 平成21年11月6日 (2009.11.6)       | (74) 代理人 | 100108062<br>弁理士 日向寺 雅彦               |

|           |                              | (72) 発明者 | 松岡 長<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内    |

|           |                              |          |                                       |

|           |                              |          |                                       |

(54) 【発明の名称】半導体装置及びその製造方法

(57) 【要約】 (修正有)

【課題】電界集中の生じ易い終端部においてアバランシエ耐量の高い半導体装置、およびその製造方法を提供する。

【解決手段】N型ドレイン層11上のN型ドリフト層12と、N型ドリフト層12上のP型ベース層13と、P型ベース層13の表面に設けられたN型ソース領域14と、ドレイン電極15と、ソース電極16と、ドレイン電極15とソース電極16との間の縦方向に主電流が流れるセル領域8に設けられ、複数のユニットセル3を画すトレンチゲート2と、複数のユニットセル3のそれぞれの中央部に形成された第1コンタクトホール4の底部のP型の不純物を含む第1コンタクト領域21と、周辺の終端領域に形成された複数の第2コンタクトホール5の底部のP型の不純物を含む第2コンタクト領域22と、を備え、第2コンタクトホール5の開口面積は、第1コンタクトホール4の開口面積と等しいか、または小さくする。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1半導体層と、

前記第1半導体層の第1の主面上に設けられた第1導電型の第2半導体層と、

前記第2半導体層上に設けられた第2導電型の第3半導体層と、

前記第3半導体層の表面に設けられた第1導電型のソース領域と、

前記第1半導体層の第2の主面に電気的に接続された第1の主電極と、

前記ソース領域に電気的に接続された第2の主電極と、

前記第1の主電極と前記第2の主電極との間で前記ソース領域を介して縦方向に主電流が流れるセル領域に設けられた複数のユニットセルを画し、前記第3半導体層の表面から前記第2の半導体層に達して設けられたトレンチゲートと、

前記複数のユニットセルのそれぞれの中央部において前記第3の半導体層に形成された第1のコンタクトホールの底部にイオン注入された第2導電型の不純物を含み、前記第2の主電極と前記第3半導体層とを電気的に接続する第1コンタクト領域と、

前記セル領域の周囲に設けられた終端領域において前記第3の半導体層に形成された複数の第2コンタクトホールの底部にイオン注入された第2導電型の不純物を含み、前記第2の主電極と前記第3半導体層とを電気的に接続する第2コンタクト領域と、

を備え、

前記第2コンタクトホールの開口面積は、前記第1コンタクトホールの開口面積と等しいか、または前記第1コンタクトホールの開口面積よりも小さいことを特徴とする半導体装置。

## 【請求項 2】

前記第2半導体層と前記第1コンタクト領域との間隔よりも、前記第2半導体層と前記第2コンタクト領域との間隔の方が狭いことを特徴とする請求項1記載の半導体装置。

## 【請求項 3】

前記セル領域が外側へ突出する前記セル領域のコーナー部に隣接した前記終端領域の幅は、前記セル領域のコーナー部以外に隣接した前記終端領域の幅よりも広く、前記第2コンタクトホールは、前記セル領域のコーナー部に隣接した部分と前記セル領域のコーナー部以外に隣接した部分とにおいて同一のピッチで設けられていることを特徴とする請求項1または2のいずれか1つに記載の半導体装置。

30

## 【請求項 4】

前記セル領域において前記第3半導体層に形成され前記第1コンタクトホールよりも開口面積の大きい複数の第3コンタクトホールの底部にイオン注入された第2導電型の不純物を含み、前記第2の主電極と前記第3半導体層とを電気的に接続する第3コンタクト領域をさらに備えたことを特徴とする請求項1～3のいずれか1つに記載の半導体装置。

## 【請求項 5】

第1導電型の第1半導体層と、

前記第1半導体層の第1の主面上に設けられた第1導電型の第2半導体層と、

前記第2半導体層上に設けられた第2導電型の第3半導体層と、

前記第3半導体層の表面に設けられた第1導電型のソース領域と、

前記第1半導体層の第2の主面に電気的に接続された第1の主電極と、

前記ソース領域に電気的に接続された第2の主電極と、

前記第1の主電極と前記第2の主電極との間で前記ソース領域を介して縦方向に主電流が流れるセル領域に設けられた複数のユニットセルを画し、前記第3半導体層の表面から前記第2の半導体層に達して設けられたトレンチゲートと、

40

を有する半導体装置の製造方法であって、

前記複数のユニットセルのそれぞれの中央部において前記第3の半導体層に形成された第1コンタクトホールの底部と、前記セル領域の周囲に設けられた終端領域において前記第3の半導体層に形成された第2コンタクトホールの底部と、に、第2導電型の不純物を同時にイオン注入することを特徴とする半導体装置の製造方法。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及びその製造方法に関する。

**【背景技術】****【0002】**

電力制御用に用いられるパワー半導体装置では、スイッチング動作時の電力損失を抑えるため、オン抵抗の低減が図られてきた。例えば、ゲート構造にトレンチゲートを採用することで、ブレーナ構造のゲートに比べてチャネル密度を増加させることができる。さらに、素子構造の微細化を進めることにより、大幅にオン抵抗を低減させることができることが可能となっている。

10

**【0003】**

一方、パワーMOS-FETなど低耐圧のパワー半導体装置では、スイッチング電源やDC-DCコンバータなどの用途のために、高速動作への要求が高まりつつある。この場合、高速スイッチング時に生ずるパルス幅の狭いサージ電圧に対して、素子が破壊しないことが望まれている。

**【0004】**

これに対応するためには、アバランシェ破壊に対する耐量の高い半導体装置を実現する必要がある。特許文献1には、トレンチゲートを有するMOS-FETであって、終端コーナー部における電界集中を緩和するために、トレンチゲート間の幅の広いセルのみを用いて終端部を構成する技術が開示されている。すなわち、電界分布が非対称となり電界集中が生じ易い終端部、特に、コーナー部において高耐圧化を実現することが望ましい。

20

**【先行技術文献】****【特許文献】****【0005】****【特許文献1】特開2004-281524号公報****【発明の概要】****【発明が解決しようとする課題】****【0006】**

本発明の目的は、電界集中の生じ易い終端部において高いアバランシェ耐量を有する半導体装置、およびその製造方法を提供することである。

30

**【課題を解決するための手段】****【0007】**

本発明の一態様によれば、第1導電型の第1半導体層と、前記第1半導体層の第1の主面上に設けられた第1導電型の第2半導体層と、前記第2半導体層上に設けられた第2導電型の第3半導体層と、前記第3半導体層の表面に設けられた第1導電型のソース領域と、前記第1半導体層の第2の主面に電気的に接続された第1の主電極と、前記ソース領域に電気的に接続された第2の主電極と、前記第1の主電極と前記第2の主電極との間で前記ソース領域を介して縦方向に主電流が流れるセル領域に設けられた複数のユニットセルを画し、前記第3半導体層の表面から前記第2の半導体層に達して設けられたトレンチゲートと、前記複数のユニットセルのそれぞれの中央部において前記第3の半導体層に形成された第1コンタクトホールの底部にイオン注入された第2導電型の不純物を含み、前記第2の主電極と前記第3半導体層とを電気的に接続する第1コンタクト領域と、前記セル領域の周辺に設けられた終端領域において前記第3の半導体層に形成された複数の第2コンタクトホールの底部にイオン注入された第2導電型の不純物を含み、前記第2の主電極と前記第3半導体層とを電気的に接続する第2コンタクト領域と、を備え、前記第2コンタクトホールの開口面積は、前記第1コンタクトホールの開口面積と等しいか、または前記第1コンタクトホールの開口面積よりも小さいことを特徴とする半導体装置が提供される。

40

また、本発明の別の一態様によれば、第1導電型の第1半導体層と、前記第1半導体層

50

の第1の主面上に設けられた第1導電型の第2半導体層と、前記第2半導体層上に設けられた第2導電型の第3半導体層と、前記第3半導体層の表面に設けられた第1導電型のソース領域と、前記第1半導体層の第2の主面に電気的に接続された第1の主電極と、前記ソース領域に電気的に接続された第2の主電極と、前記第1の主電極と前記第2の主電極との間で前記ソース領域を介して縦方向に主電流が流れるセル領域に設けられた複数のユニットセルを画し、前記第3半導体層の表面から前記第2の半導体層に達して設けられたトレンチゲートと、を有する半導体装置の製造方法であって、前記複数のユニットセルのそれぞれの中央部において前記第3の半導体層に形成された第1コンタクトホールの底部と、前記セル領域の周囲に設けられた終端領域において前記第3の半導体層に形成された第2コンタクトホールの底部と、に、第2導電型の不純物を同時にイオン注入することを特徴とする半導体装置の製造方法が提供される。

10

## 【発明の効果】

## 【0008】

本発明によれば、電界集中の生じ易い終端部においてアバランシェ耐量の高い半導体装置、およびその製造方法を実現することができる。

## 【図面の簡単な説明】

## 【0009】

【図1】本発明の第1の実施形態に係る半導体装置を示す模式図である。

【図2】第1の実施形態に係る半導体装置の断面を示す模式図である。

20

【図3】第1の実施形態に係る半導体装置の製造工程を模式的に示す断面図である。

【図4】第1の実施形態に係る半導体装置の製造工程を模式的に示す断面図である。

【図5】第1の実施形態に係る半導体装置の製造工程を模式的に示す断面図である。

【図6】第1の実施形態に係る半導体装置の製造工程を模式的に示す断面図である。

【図7】第2の実施形態に係る半導体装置を示す模式図である。

【図8】第3の実施形態に係る半導体装置を示す模式図である。

【図9】比較例に係る半導体装置の断面を示す模式図である。

## 【発明を実施するための形態】

## 【0010】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、以下の説明では、半導体装置として電力制御用のシリコンパワーMOS-FETを例に挙げる。また、図面中の同一部分には同一番号を付してその詳しい説明は適宜省略し、異なる部分について適宜説明する。

30

## 【0011】

## (第1の実施形態)

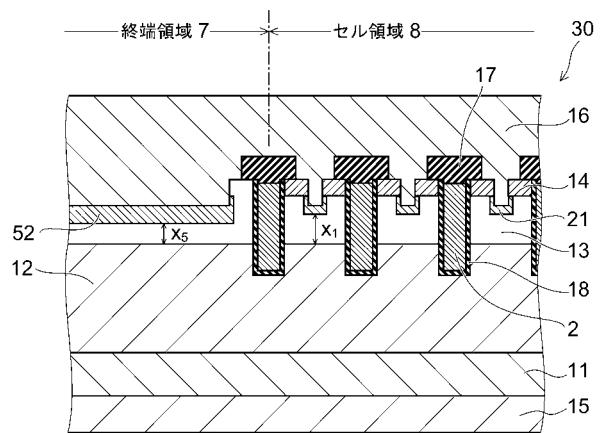

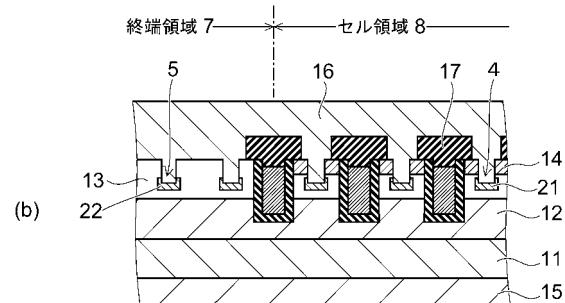

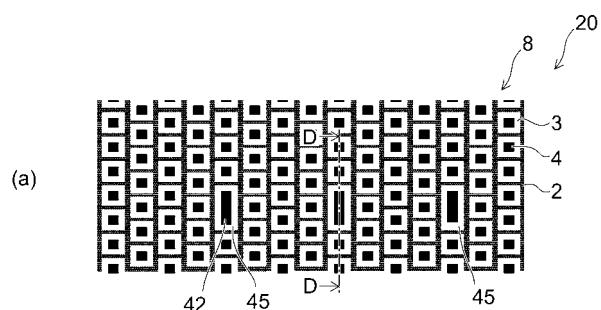

図1は、第1の実施形態に係るパワーMOS-FET1を示す模式図である。ただし、同図中には、ソース電極のない表面が模式的に示されている。また、以下の説明において、図7(a)および図8(a)についても同様である。

## 【0012】

図1(a)は、パワーMOS-FET1の主面(チップ面)を模式的に示す平面図である。チップ面の中央には、MOS-FETのユニットセルが複数配置されたセル領域8が設けられている。また、同図中の右下隅には、ゲートパッド9が配置されている。

40

## 【0013】

図1(b)は、図1(a)中に破線で示すA領域のセル配置を拡大して示す模式図である。セル領域8に配置されたユニットセル3は、トレンチゲート2によって個々に画されている。また、各ユニットセル3の中央には、第1コンタクトホール4が設けられている。

## 【0014】

一方、セル領域8を囲む終端領域7(トレンチゲート2が設けられていない領域)には、第2コンタクトホール5が、例えば、セル領域と同じ間隔で設けられている。さらに、セル領域8が外側へ突出するセル領域8のコーナー部Eに隣接した終端領域7の幅は広く

50

設けられている。これにより、図1(b)中に示すように、セル領域8のコーナー部Eに隣接した終端領域7における第2コンタクトホール5の数は、セル領域8のコーナー部E以外の部分に隣接した終端領域7に設けられた第2コンタクトホール5の数よりも多くなっている。

#### 【0015】

ここで、第1コンタクトホール4と第2コンタクトホール5とを区別するのは、それが設けられた場所が、異なるからである。すなわち、第1コンタクトホール4はセル領域に設けられ、第2コンタクトホール5は終端領域に設けられている。また、以下の説明においても、「第1コンタクト領域」は、セル領域に設けられ、「第2コンタクト領域」は終端領域7に設けられたものとする。

10

#### 【0016】

MOS-FETのアバランシェ耐量を高くする場合、ターンオフ時のブレイクダウンが素子の特定箇所に集中しないように設計することが望ましい。なぜなら、ブレイクダウン局的に発生すると、その場所にアバランシェ電流が集中し素子が破壊に至る可能性が高いからである。したがって、電界が集中してブレイクダウンが起こり易い場所を、チップ面内の複数の場所に分散させるロバストな構造設計を探ることが望ましい。

#### 【0017】

例えば、電界分布の対称性が崩れ、電界集中が生じ易い終端領域7の耐圧を高くすることが望ましい。中でも、セル領域8が外側へ突出するコーナー部Eにおいて、電界集中が生じる傾向が強く、高耐量化を図ることが望まれる。また、図1(a)中に示すF領域およびG領域においても、図1(b)に示すA領域と同じように高耐圧化を図ることが望まれる。

20

#### 【0018】

本実施形態に係るMOS-FET1では、図1(b)に示すように、セル領域8に設けられた第1コンタクトホール4と同じサイズの第2コンタクトホール5を終端領域7に設けることにより、終端部のアバランシェ耐量を向上させることができる。さらに、セル領域8のコーナー部Eに隣接した部分において、他の部分よりも終端領域7の幅を広くすることにより、数多く第2コンタクトホール5を設けることができる。これにより、コーナー部Eに隣接した部分のコンタクト抵抗を低下させて、アバランシェ耐量を向上させることができる。

30

#### 【0019】

後述するように、終端領域7のコンタクト構造をホールコンタクトとすることにより、イオン注入の深さをセル領域8と同じか、または浅くすることが可能となり、終端領域7のアバランシェ耐量の低下を防ぐことができる。また、コーナー部Eに隣接した部分において、第2コンタクトホールを数多く設けることにより、コンタクト抵抗を低くすることができる。これにより、MOS-FET内部の高電界領域で発生する正孔の排出をスムーズにして、さらにアバランシェ耐量を向上させることができる。

#### 【0020】

例えば、終端領域7の第2コンタクトホール5間のピッチを、フォトリソグラフィでレジストパターンの形状が維持できる限界まで狭く設けることができる。これにより、終端領域7のコンタクト抵抗を最小とすることが可能であり、アバランシェ耐量をより向上させることができる。これは、光学的シミュレーション、およびプロセスシミュレーション、デバイスシミュレーションを用いてマスク寸法を最適化することにより実施することができる。

40

#### 【0021】

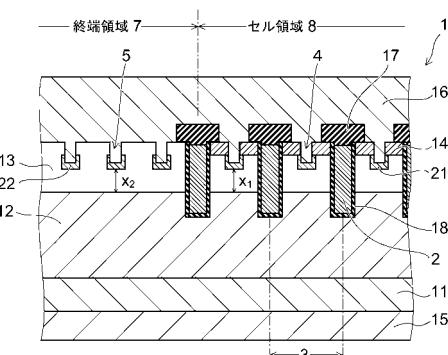

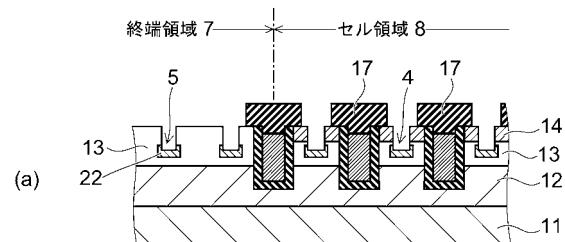

図2は、第1実施形態に係るMOS-FET1の断面を示す模式図である。同図中に示す断面は、図1(b)中に示したB-B線に沿った断面である。以下の説明において、N型は第1導電型に対応し、P型は第2導電型に対応する。また、後述する実施形態においても同様である。

#### 【0022】

50

本実施形態に係るMOS-FETは、N型の第1半導体層であるドレイン層11と、ドレイン層11の第1の主面上に設けられたN型の第2半導体層であるドリフト層12と、を備えている。ドリフト層12の上部には、P型の第3の半導体層であるベース層13が設けられている。また、P型ベース層13の表面には、N型ソース領域14が設けられている。

#### 【0023】

さらに、N型ドレイン層11の第2の主面との間で電気的に接続された第1の主電極であるドレイン電極15と、N型ソース領域14に電気的に接続された第2の主電極であるソース電極16が設けられている。

#### 【0024】

図2中に示すように、N型ソース領域14は、ドレイン電極15とソース電極16との間で、縦方向に主電流が流れるセル領域8に設けられている。セル領域8には、N型ソース領域14の表面からN型ドリフト層12に達するトレンチゲート2と、トレンチゲート2により画された複数のユニットセル3と、が設けられている（図1（b）参照）。

#### 【0025】

さらに、複数のユニットセル3のそれぞれの中央部のベース層13には、第1コンタクトホール4が設けられている。また、第1コンタクトホール4の底部には、P型の不純物がイオン注入された第1コンタクト領域21が設けられている。第1コンタクト領域21は、ソース電極16とP型ベース層13とを電気的に接続する。

#### 【0026】

一方、セル領域の周辺に設けられた終端領域のベース層13には、複数の第2コンタクトホール5が形成されている。第2コンタクトホールの底部には、セル領域8に設けられた第1コンタクトホール4と同様に、P型の不純物がイオン注入された第2コンタクト領域22が設けられている。第2コンタクト領域22も、ソース電極16とP型ベース層13とを電気的に接続している。

#### 【0027】

本実施形態に係るMOS-FET1では、第2コンタクトホール5は、第1コンタクトホール4と開口面積が等しくなるように設けられている。これにより、N型ドリフト層12と第1コンタクト領域21との間隔X<sub>1</sub>と、N型ドリフト層12と第2コンタクト領域22との間隔X<sub>2</sub>と、が等しくなる。つまり、P型ベース層13とN型ドリフト層12との界面であるPN接合と、第1コンタクト領域21との間の間隔X<sub>1</sub>が、第2コンタクト領域22とPN接合との間隔X<sub>2</sub>と等しくなる。

#### 【0028】

本発明者の知見によれば、P型の不純物をイオン注入して形成される第1コンタクト領域21および第2コンタクト領域22のN型ドレイン層11方向の深さは、それぞれのコンタクトホールの開口面積に依存して変化する。例えば、第1コンタクトホール4の開口面積を、第2コンタクトホール5の開口面積よりも大きくすれば、第1コンタクト領域21とPN接合との間の間隔X<sub>1</sub>は、第2コンタクト領域22とPN接合との間隔X<sub>2</sub>よりも狭くなる。

#### 【0029】

一方、第1コンタクト領域21または第2コンタクト領域22からN型ドレイン層11に向かう方向の電界分布の最大値は、PN接合とコンタクト領域との間の間隔X<sub>1</sub>およびX<sub>2</sub>が狭いほど高くなる。したがって、PN接合とコンタクト領域との間隔が狭くなるとアバランシェ降伏が生じやすくなりアバランシェ耐量が低下する傾向にある。

#### 【0030】

図9は、比較例に係るMOS-FET30の断面を示す模式図である。本比較例のMOS-FET30では、同図中に示すように、終端領域7の広い面積をエッチングしてコンタクト領域52を形成している。したがって、コンタクト領域52のP型不純物は深くイオン注入され、PN接合との間隔X<sub>5</sub>は、セル領域に設けられた第1コンタクト領域21とPN接合との間隔X<sub>1</sub>より狭くなる傾向がある。

10

20

30

40

50

## 【0031】

これにより、終端領域7のアバランシェ耐量が、セル領域8のアバランシェ耐量よりも低くなる傾向にあった。特に、電界集中が生じやすいコーナー部Eにおいて、アバランシェ耐量の低下が生じ易い傾向にあった。

## 【0032】

これに対して、本実施形態に係るMOS-FET1では、終端領域に第2コンタクトホール5を設けて、第2コンタクト領域22とPN接合との間隔X<sub>2</sub>が、第1コンタクト領域21とPN接合との間隔X<sub>1</sub>より狭くならないようにしている。

## 【0033】

また、本実施形態に係るMOS-FET1では、X<sub>1</sub>とX<sub>2</sub>とが等しくなるように、第1コンタクトホール4と第2コンタクトホール5との開口面積と同じに設けているが、第1コンタクトホール4の開口面積を第2コンタクトホール5の開口面積よりも大きくして、X<sub>1</sub>がX<sub>2</sub>より狭くなるようにしてもよい。これにより、終端領域7のアバランシェ耐量をセル領域8よりも高くすることが可能となる。

10

## 【0034】

図3～図6は、第1実施形態に係るMOS-FET1の製造工程を模式的に示す断面図である。各図中に示す断面は、図1(b)中に示したB-B線に沿った断面である。本具体例のMOS-FET1は、シリコンを材料とするシリコンMOS-FETである。

## 【0035】

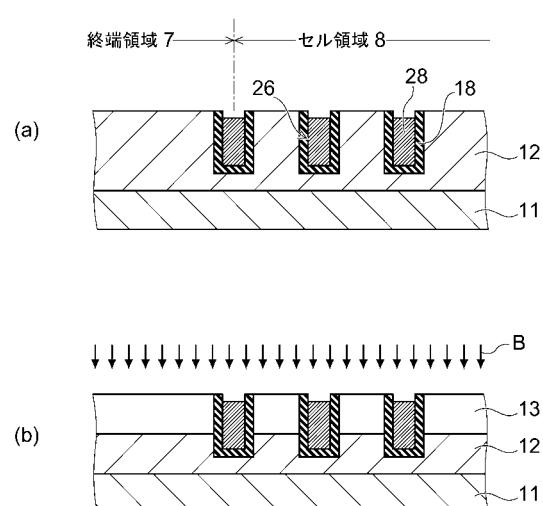

図3(a)に示すように、N型ドレイン層11の第1の主面上にエピタキシャル成長したN型ドリフト層12に、トレンチ26を形成し、ゲート電極となる導電性のポリシリコン28を埋め込む。ポリシリコン28は、トレンチ26を形成したN型ドリフト層の全面にCVD法を用いて形成する。その後、トレンチ26内に残される部分を除いて、エッチングにより除去する。

20

## 【0036】

N型ドレイン層11としては、シリコン基板上にエピタキシャル成長した高濃度のシリコン層、または高濃度にドープされたシリコン基板を用いることができる。また、トレンチ26の内面には、ゲート絶縁膜18となるシリコン酸化膜SiO<sub>2</sub>を形成する。

## 【0037】

次に、図3(b)に示すように、N型ドリフト層12の表面にP型不純物をイオン注入してP型ベース層13を形成する。P型不純物として、例えば、ボロン(B)を用いることができる。また、イオン注入後にシリコン基板を熱処理することにより、P型不純物を、N型ドリフト層12の表面から所定の深さまで拡散させる。これにより、同図中に示すP型ベース層13が形成される。

30

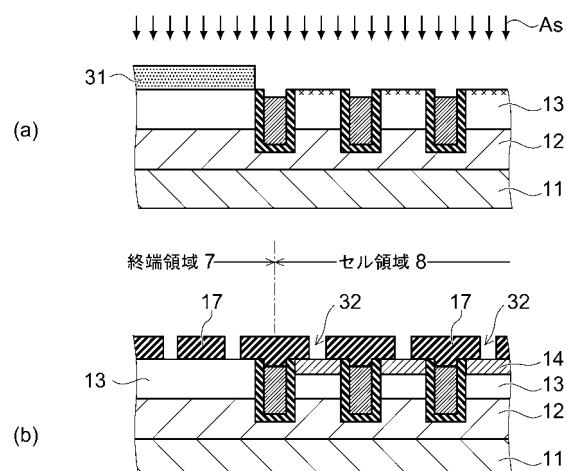

## 【0038】

続いて、図4(a)に示すように、N型不純物、例えば、ヒ素(As)を、P型ベース層13の表面にイオン注入し、N型ソース領域を形成する。この際、選択注入を行うための注入マスク31として、フォトレジストを用いることができる。

## 【0039】

さらに、図4(b)に示すように、P型ベース層13およびN型ソース領域14、ポリシリコン28の表面に、層間絶縁膜17を形成する。なお、N型ソース領域14に注入されたN型不純物は、層間絶縁膜17を形成する過程で実施される熱処理により活性化することができる。また、層間絶縁膜17には、第1コンタクトホール4および第2コンタクトホール5を形成するための開口32を形成する。

40

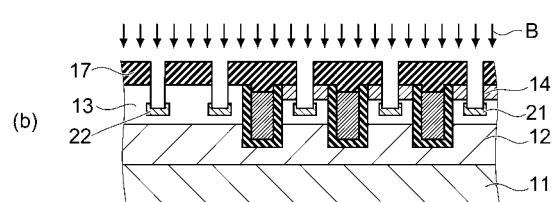

## 【0040】

次に、図5(a)に示すように、開口32が形成された層間絶縁膜17をマスクとして、N型ソース領域14およびP型ベース層13の表面をドライエッティングして、第1コンタクトホール4および第2コンタクトホール5を形成する。ドライエッティングの方法としては、例えばリアクティブ・イオン・エッティング(RIE)法を用いることができる。また、ドライエッティングは、セル領域8に形成される第1コンタクトホール4が、N型ソ-

50

ス領域 1 4 を貫通して P 型ベース層 1 3 に連通するまで実施する。

【 0 0 4 1 】

次に、層間絶縁膜 1 7 を注入マスクとして、P 型不純物、例えば、ボロン ( B ) をイオン注入する。P 型不純物は、第 1 コンタクトホールの底部と、第 2 コンタクトホールの底部と、の両方に同時にイオン注入され、第 1 コンタクト領域 2 1 および第 2 コンタクト領域 2 2 が形成される。

【 0 0 4 2 】

この際、セル領域 8 と終端領域 7 において、層間絶縁膜 1 7 に設けられた開口 3 2 の開口面積を変えることにより、イオン注入により形成される第 1 コンタクト領域 2 1 と第 2 コンタクト領域 2 2 を、異なる深さに形成することができる。すなわち、層間絶縁膜 1 7 の開口 3 2 を形成する際に用いるフォトマスクの設計を変更するだけで、製造工程を変更することなく、第 1 コンタクト領域 2 1 の深さと第 2 コンタクト領域 2 2 の深さとを変えることができる。これにより、前述したように、終端領域 7 におけるアバランシェ耐量を、セル領域 8 と同じか、または高くすることが可能となる。

10

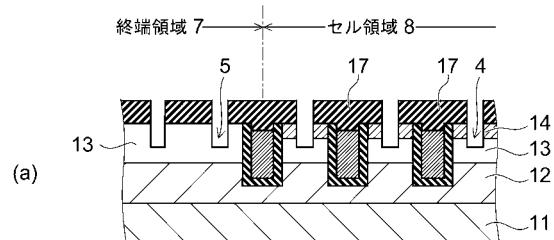

【 0 0 4 3 】

次に、図 6 ( a ) に示すように、層間絶縁膜 1 7 の表面を所定量エッチングし、N 型ソース領域 1 4 の表面の一部を露出させる。また、終端領域 7 に形成された層間絶縁膜 1 7 をエッチングして除去する。

【 0 0 4 4 】

さらに、図 6 ( b ) に示すように、セル領域 8 の N 型ソース領域 1 4 、第 1 コンタクトホール 4 、層間絶縁膜 1 7 、および、終端領域の P 型ベース層 1 3 、第 2 コンタクトホール 5 を覆って、ソース電極 1 6 を形成する。これにより、セル領域 8 において、ソース電極 1 6 と P 型ベース層 1 3 とが第 1 コンタクト領域 2 1 を介して電気的に接続され、P 型ベース層 1 3 の電位が固定されるので、M O S - F E T 1 の動作を安定させることができる。また、終端領域 7 において、第 2 コンタクト領域 2 2 を介してソース電極 1 6 と P 型ベース層 1 3 との間が低抵抗に接続されるので、ホールの排出抵抗が小さくなり、アバランシェ耐量を向上させることができる。

20

【 0 0 4 5 】

一方、図 6 ( b ) 中に示すように、N 型ドレイン層 1 1 の第 2 の主面には、ドレイン電極 1 5 が形成される。具体的には、M O S - F E T 1 が形成されたシリコン基板の裏面を研削して薄板化し、メタライズすることにより、ドレイン電極 1 5 を形成する。

30

【 0 0 4 6 】

( 第 2 の実施形態 )

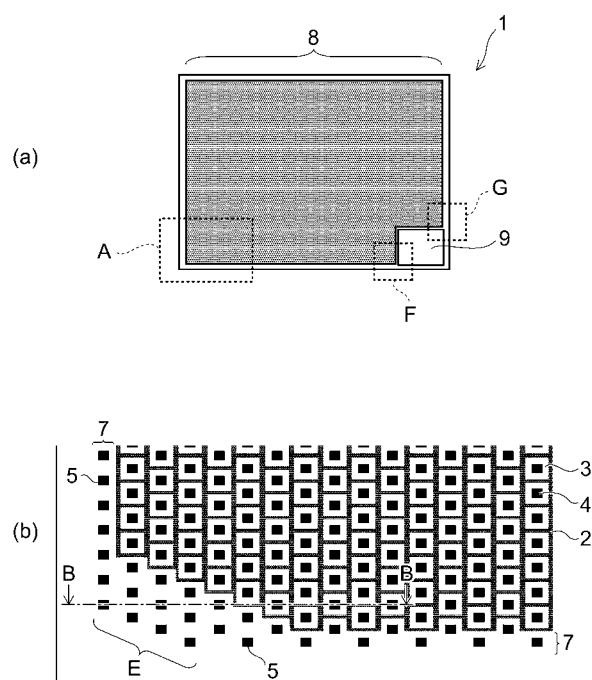

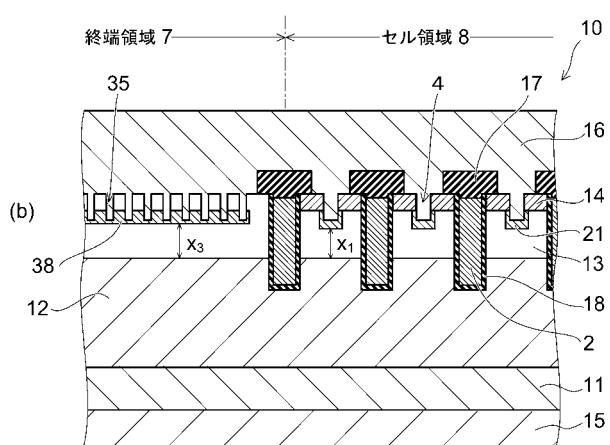

図 7 は、第 2 の実施形態に係る M O S - F E T 1 0 を示す模式図である。図 7 ( a ) は、M O S - F E T チップのコーナー部 E の周辺を模式的に示す平面図である。また、図 7 ( b ) は、図 7 ( a ) 中に示した C - C 線に沿った断面を示す模式図である。

40

【 0 0 4 7 】

図 7 ( a ) および ( b ) に示すように、セル領域 8 では、トレンチゲート 2 で画されたユニットセル 3 が設けられ、ユニットセル 3 の中央に第 1 コンタクトホール 4 が設けられている点で、第 1 の実施形態に示した M O S - F E T 1 と同じである。

【 0 0 4 8 】

一方、セル領域 8 の周辺の終端部には、第 1 コンタクトホール 4 よりも開口面積が小さい第 2 コンタクトホール 3 5 が設けられている。また、第 2 コンタクトホール 3 5 は、M O S - F E T 1 に比べて狭いピッチで、数多く設けられている。これにより、終端部 7 において、ソース電極 1 6 と P 型ベース層 1 3 との間のコンタクト抵抗が低く維持されている。

【 0 0 4 9 】

また、セル領域 8 が外側に突出するコーナー部 E に隣接した部分においては、セル領域 8 のそれ以外の部分に隣接した部分よりも終端領域 7 の幅が広い。そして、第 2 コンタクトホール 3 5 は、コーナー部 E に隣接した部分と、それ以外の部分と、において同一のピ

50

ツチで形成されている。つまり、本実施形態に係るMOS-FET10においても、第2コンタクトホール35の数は、セル領域8のコーナー部E以外の部分に隣接した終端領域7に設けられた第2コンタクトホール35の数よりも、セル領域8のコーナー部Eに隣接した終端領域7においてさらに多く設けられている。したがって、ソース電極16とP型ベース層13との間の抵抗がさらに低くなり、正孔の排出抵抗がより小さくなる。これにより、コーナー部Eでの電界集中によるアバランシェ耐量の低下を防ぐことができる。

#### 【0050】

また、図7(b)に示すように、第2コンタクトホール35の開口面積が、第1コンタクトホール4の開口面積よりも小さいことから、第1コンタクト領域21の深さよりも、第2コンタクト領域38の深さの方が浅くなっている。すなわち、第1コンタクト領域21とPN接合との間隔X<sub>1</sub>よりも、第2コンタクト領域38とPN接合との間隔X<sub>3</sub>の方が広くなっている。終端領域7のアバランシェ耐量が高くなっている。

10

#### 【0051】

本実施形態に係るMOS-FET10では、開口面積の小さい第2コンタクトホール35を多数設けることにより、ソース電極16とP型ベース層13との間のコンタクト抵抗を小さくし、さらに、第2コンタクト領域38を浅く形成してアバランシェ耐量を高めることによって、終端領域7で発生するアバランシェ降伏を抑えることができる。

#### 【0052】

また、前述したように、第2コンタクトホール35のピッチを狭く形成することにより、図7(b)中に示すように、隣接する第2コンタクト領域38が一体となり、1つのコンタクト領域となるように形成することもできる。これにより、さらにソース電極とP型ベース層のコンタクト抵抗を下げることが可能となり、アバランシェ耐量の向上を図ることができる。第2コンタクトホール35のピッチは、フォトリソグラフィにおいて開口パターンの形状を維持できる限界まで狭く形成することが可能である。

20

#### 【0053】

##### (第3の実施形態)

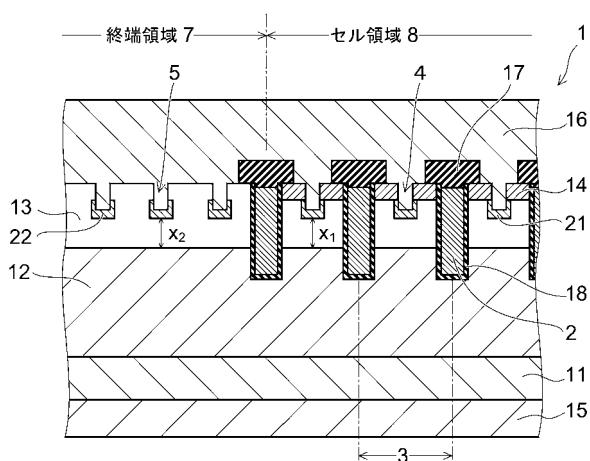

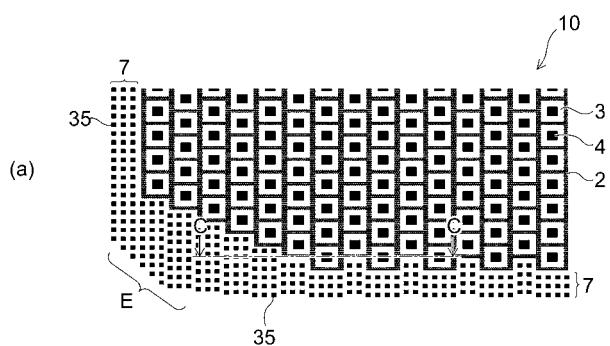

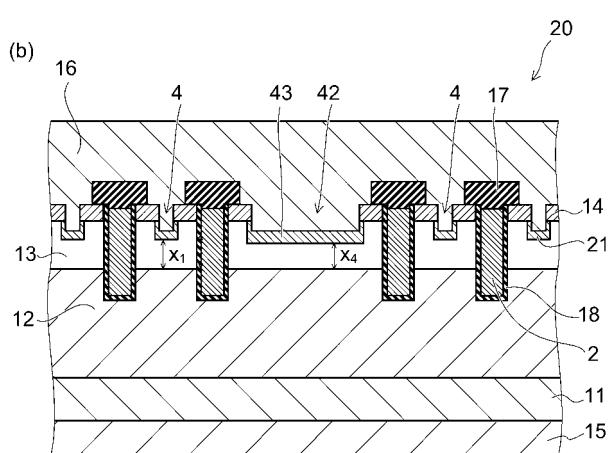

図8は、第3の実施形態に係るMOS-FET20を示す模式図である。図8(a)は、MOS-FETチップのセル領域8を模式的に示す平面図である。また、図8(b)は、図8(a)中に示したD-D線に沿った断面を示す模式図である。

30

#### 【0054】

図8(a)に示すように、本実施形態に係るMOS-FET20では、セル領域8内に、第1コンタクトホール4よりも開口面積の大きい複数の第3コンタクトホール42が設けられた複数のユニットセル45を有している。一方、図示しない終端領域には、第1の実施形態または第2の実施形態に関して前述したように、第1コンタクトホール4と開口面積が同じか、または小さい第2コンタクトホールが設けられている。

#### 【0055】

また、図8(b)の断面図に示すように、第3コンタクトホール42の底部に設けられた第3コンタクト領域43のN型ドレイン層11方向の深さは、第1コンタクトホール4の底部に設けられた第1コンタクト領域21の深さよりも深くなっている。すなわち、第3コンタクト領域43と、P型ベース層13とN型ドリフト層12との境界のPN接合との間隔X<sub>4</sub>は、第1コンタクト領域21とPN接合との間隔X<sub>1</sub>よりも狭くなっている。

40

#### 【0056】

したがって、第3コンタクトホール42が設けられたユニットセル45のアバランシェ耐量は、第1コンタクトホール4が設けられたユニットセル3よりも低くなる。一方、終端領域のアバランシェ耐量は、第1の実施形態または第2の実施形態に関して前述したように、ユニットセル3よりも高くなっている。つまり、第3コンタクトホール42が設けられたユニットセル45において、アバランシェ耐量が最も低くなり、アバランシェ降伏が生じ易くなっている。

#### 【0057】

50

すなわち、本実施形態に係るMOS-FET20では、ターンオフ時に過剰な電圧が加わった場合に、セル領域8に複数配置されたユニットセル45において、積極的にアバランシェ降伏を起こさせることができる。これにより、アバランシェ電流を分散させて電流集中を防ぎ、素子破壊を回避することができる。

#### 【0058】

ここで、個々のユニットセル45に流れるアバランシェ電流が、素子破壊に至る限界値を超えないように、セル領域8に設けられるユニットセル45の数と配置位置とを、デバイスシミュレーション技術を用いて最適化するとよい。

#### 【0059】

このように本実施形態に係るMOS-FET20では、ソース電極16とP型ベース層13との間のコンタクト構造を最適化することにより、アバランシェ電流を均一に拡散させることができあり、素子破壊を有効に回避することができる。また、これを実施するために製造工程が増えることはなく、歩留りの改善も可能であるから、製造コストを低減することが可能である。

#### 【0060】

以上、本発明に係る一実施形態を参照して本発明を説明したが、本発明はこれらの実施形態に限定されるものではない。例えば、出願時の技術水準に基づいて、当業者がなし得る設計変更や、材料の変更等、本発明と技術的・思想を同じとする実施態様も本発明の技術的範囲に含有される。

#### 【0061】

例えば、上記の実施態様に示したNチャネルのMOS-FETのみならず、PチャネルのMOS-FETにも適用できる。また、シリコンを材料とするMOS-FETに限られる訳ではなく、SiCやGaN等を材料とする半導体装置にも適用可能である。

#### 【符号の説明】

#### 【0062】

1、10、20 MOS-FET

2 トレンチゲート

3、45 ユニットセル

4 第1コンタクトホール

5、35 第2コンタクトホール

30

7 終端領域

8 セル領域

9 ゲートパッド

11 N型ドレイン層

12 N型ドリフト層

13 P型ベース層

14 N型ソース領域

15 ドレイン電極

16 ソース電極

17 層間絶縁膜

40

18 ゲート絶縁膜

21 第1コンタクト領域

22、38 第2コンタクト領域

26 トレンチ

28 ポリシリコン

42 第3コンタクトホール

43 第3コンタクト領域

E コーナー部

【 図 1 】

【 図 2 】

【図3】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図9】