(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4154598号

(P4154598)

(45) 発行日 平成20年9月24日(2008.9.24)

(24) 登録日 平成20年7月18日(2008.7.18)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G09G 3/20 (2006.01)**

GO9G 3/36

GO2F 1/133 525

GO2F 1/133 550

GO9G 3/20 611J

GO9G 3/20 612B

請求項の数 20 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2003-301589 (P2003-301589)

(22) 出願日

平成15年8月26日 (2003.8.26)

(65) 公開番号

特開2005-70539 (P2005-70539A)

(43) 公開日

平成17年3月17日 (2005.3.17)

審査請求日

平成18年3月29日 (2006.3.29)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100125689

弁理士 大林 章

(74) 代理人 100125335

弁理士 矢代 仁

(74) 代理人 100121108

弁理士 高橋 太朗

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤綱 英吉

(74) 代理人 100107261

弁理士 須澤 修

最終頁に続く

(54) 【発明の名称】 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

一対の基板間に液晶層を封入してなり、前記一対の基板の一方の基板には複数の走査線と複数のデータ線と前記各走査線および前記各データ線に接続された画素スイッチング素子と前記画素スイッチング素子に接続された画素電極とを有し、更に前記画素電極に対して液晶を介して対向配置されたコモン電極を有し、

前記複数の走査線に接続された前記画素スイッチング素子をローインピーダンス状態にする一つ又は複数の選択電位と、該走査線に接続された前記画素スイッチング素子をハイインピーダンス状態にする一つ又は複数の非選択電位とを走査線毎に異なったタイミングで順次出力する走査線駆動回路が、前記複数の走査線に接続されてなり、前記走査線駆動回路は異なる電位を有した複数の電源配線と接続されてなる液晶表示装置の駆動方法において、

前記コモン電極を相対的に高い電位のコモン・ハイ状態と相対的に低い電位のコモン・ロー状態の交互に反転駆動するコモン反転駆動であり、かつ前記コモン電極の電位が前記コモン・ハイ状態から前記コモン・ロー状態に、ならびに前記コモン・ロー状態から前記コモン・ハイ状態に切り換えるコモン反転動作は、前記複数の走査線の少なくとも一部が前記複数の電源配線から電気的に分離されているフローティング状態であり、

前記複数の走査線は、

前記選択電位の電源と比較的低い電気抵抗で接続された状態の選択状態である期間と、

前記非選択電位の電源と比較的低い電気抵抗で接続された状態の非選択状態である期間

10

20

と、

前記フロー ティング状態である期間とをそれぞれ有する、

ことを特徴とした液晶表示装置の駆動方法。

【請求項 2】

前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記走査線が前記フロー ティング状態となるタイミングでは該走査線の電位は前記非選択電位と概略等しく、かつ前記コモン電極が前記コモン・ハイ状態である

ことを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項 3】

前記画素スイッチング素子はPチャネル型電界効果トランジスターであり、

前記走査線が前記フロー ティング状態となるタイミングでは該走査線の電位は前記非選択電位と概略等しく、かつ前記コモン電極が前記コモン・ロー状態である

ことを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項 4】

前記画素スイッチング素子はNチャネル型電界効果トランジスターよりなる第一スイッチングトランジスターとPチャネル型電界効果トランジスターよりなる第二スイッチングトランジスターより構成される相補型伝送ゲートであり、

前記走査線は前記第一スイッチングトランジスターに接続される第一走査線と前記第二スイッチングトランジスターに接続される第二走査線よりなり、

前記第一走査線が前記フロー ティング状態となるタイミングでは前記第一走査線の電位は前記非選択電位と概略等しくかつ前記コモン電極が前記コモン・ハイ状態であり、

さらに前記第二走査線が前記フロー ティング状態となるタイミングでは前記第二走査線の電位は前記非選択電位と概略等しくかつ前記コモン電極が前記コモン・ロー状態であることを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項 5】

前記非選択状態である期間の長さは一定でないことを特徴とする

請求項1から4のいずれか一項に記載の液晶表示装置の駆動方法。

【請求項 6】

前記複数の走査線は前記選択状態から次に前記選択状態になるまでの間に複数の前記非選択状態を有し、さらに前記複数の非選択状態の間に前記フロー ティング状態を有する、

請求項1から5のいずれか一項に記載の液晶表示装置の駆動方法。

【請求項 7】

前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記選択状態の間にある複数の非選択状態のうち前記選択状態直後のものを除いた2回目以降の非選択状態は常に前記コモン電極が前記コモン・ハイ状態である時に実施され、かつ前記2回目以降の非選択状態中に前記コモン反転動作を生じない

ことを特徴とした請求項6に記載の液晶表示装置の駆動方法。

【請求項 8】

前記画素スイッチング素子はPチャネル型電界効果トランジスターであり、

前記選択状態の間にある複数の非選択状態のうち前記選択状態直後のものを除いた2回目以降の非選択状態は常に前記コモン電極が前記コモン・ロー状態である時に実施され、かつ前記2回目以降の非選択状態中に前記コモン反転動作を生じない

ことを特徴とした請求項6に記載の液晶表示装置の駆動方法。

【請求項 9】

前記コモン電極がコモン・ハイ状態である期間長と、コモン・ロー状態である期間長は等しくないことを特徴とする請求項1から8のいずれか一項に記載の液晶表示装置の駆動方法。

【請求項 10】

前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記コモン電極がコモン・ハイ状態である期間長はコモン・ロー状態である期間長より大

10

20

30

40

50

きい

ことを特徴とする請求項 9 に記載の液晶表示装置の駆動方法。

**【請求項 11】**

前記画素スイッチング素子は P チャネル型電界効果トランジスターであり、前記コモン電極がコモン・ハイ状態である期間長はコモン・ロー状態である期間長より小さい

ことを特徴とする請求項 9 に記載の液晶表示装置の駆動方法。

**【請求項 12】**

前記非選択電位は前記コモン電極の電位によらず概略一定の値である

請求項 1 から 11 のいずれか一項に記載の液晶表示装置の駆動方法。 10

**【請求項 13】**

前記画素スイッチング素子は N チャネル型電界効果トランジスターであり、前記非選択電位の値が、前記データ線に印加される映像信号電位の最低値に前記画素スイッチング素子のしきい値を足した値より低く、前記映像信号電位の最低値から前記コモン・ハイ状態での前記コモン電極の電位を引き前記コモン・ロー状態での前記コモン電極の電位を足した値より高い

ことを特徴とする請求項 12 に記載の液晶表示装置の駆動方法。

**【請求項 14】**

前記画素スイッチング素子は P チャネル型電界効果トランジスターであり、前記非選択電位の値が、前記データ線に印加される映像信号電位の最高電位に画素スイッチング素子のしきい値を足した値より高く、前記コモン・ハイ状態での前記コモン電極への印加電位から前記コモン・ロー状態での前記コモン電極の印加電位を引いた値に前記映像信号電位の最高値を足した値より低い 20

ことを特徴とする請求項 12 に記載の液晶表示装置の駆動方法。

**【請求項 15】**

前記コモン・ハイ状態のときの前記非選択電位と前記コモン・ロー状態のときの前記非選択電位が相互に異なり、

前記コモン・ハイ状態のときの前記非選択電位が前記コモン・ロー状態のときの前記非選択電位より大きい

ことを特徴とする請求項 1 から 11 のいずれか一項に記載の液晶表示装置の駆動方法。 30

**【請求項 16】**

前記コモン反転動作では少なくとも前記複数のデータ線の一部、より望ましくは全ての前記複数のデータ線がフローティング状態であることを特徴とする請求項 1 から 15 のいずれか一項に記載の液晶表示装置の駆動方法。

**【請求項 17】**

請求項 1 から 16 のいずれか一項に記載の駆動方法を用いて画像を表示する液晶表示装置。

**【請求項 18】**

前記走査線の数の二乗を画像表示部の対角方向の長さに乗じた係数が 30000 以上であることを特徴とする請求項 17 に記載の液晶表示装置。 40

**【請求項 19】**

前記走査線駆動回路の少なくとも一部は前記アクティブマトリクス基板上に形成された薄膜トランジスターによって構成されている駆動回路内蔵型液晶表示装置である請求項 17 および 18 に記載の液晶表示装置。

**【請求項 20】**

請求項 17 から 19 のいずれか一項に記載の液晶表示装置を用いて画像を表示する機能を有したバッテリーで駆動される携帯電子機器。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は液晶表示装置の駆動法、液晶表示装置、及び携帯型電子機器に関するものであり、特にアクティブマトリクス基板を使用した液晶表示装置のコモン反転駆動に関するものである。

## 【背景技術】

## 【0002】

近年、ノートPCやモニター用を筆頭に薄膜トランジスターなどのアクティブ素子を用いた液晶表示装置は急速に普及している。通常のネマティック相液晶材料を用いた液晶表示装置においては、信頼性を確保するために液晶に印加する電圧を一定時間で極性反転させる交流駆動が必要である。一般的に白表示時と黒表示時で液晶にかける電圧差は3~5Vである。従って、交流駆動を行うためには液晶を挟み込んだのアクティブマトリクス基板と対向する基板の電極（コモン電極）を固定電位とした場合、アクティブマトリクス基板上の画素電極には6~10Vの電圧振幅の信号を入力しなくてはならない。しかし、一般的にICで5V以上の電圧振幅を持つ信号を出力するためには高耐圧性に優れた特殊なプロセスで製造される必要があるためコストが高くなる。これを回避するためにコモン電極の電位を交流駆動することで入力信号を低減にするコモン反転駆動法が考案されている（特許文献1参照）。

10

## 【0003】

以下、図12を用いてコモン反転ならびに液晶印加電圧極性反転を走査線選択周期（1H周期）毎に行う1Hコモン反転駆動について、ノーマリー・ホワイトモード、画素スイッチング素子はNチャネル型薄膜トランジスターである液晶表示装置を例にとり説明する。

20

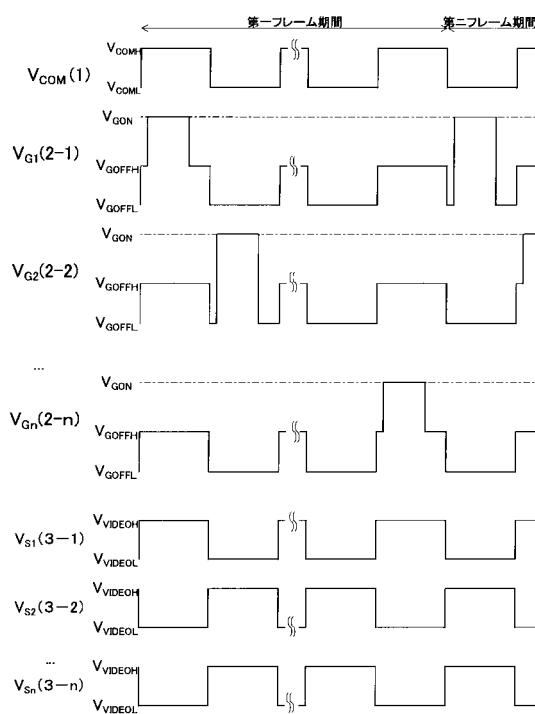

## 【0004】

$V_{com}(1)$ は前記のコモン電極電位であり、補助容量（Cs）を形成する場合は補助容量共通電極の電位も同じとなる。 $V_{com}(1)$ はコモン反転駆動では一定周期で $V_{comH}$ と $V_{comL}$ 間を反転駆動される。 $V_{G1-n}$ （2-1~2-n）はn番目の走査線に走査線駆動回路から与えられる電位であり、 $V_{com}(1)$ が反転する毎に順次、一つの走査線に画素スイッチング素子をONする選択電位（ $V_{GON}$ ）が印加され、それ以外の時間では接続された画素スイッチング素子をOFFする非選択電位として $V_{GOFFH}$ 又は $V_{GOFFL}$ のどちらかが $V_{com}(1)$ の電位に応じて選択されて印加される。なお、ここで $V_{com}(1)$ の電位に応じて非選択電位を $V_{GOFFH}$ と $V_{GOFFL}$ の二値にするのは画素スイッチング素子の信頼性確保などの理由によるもので、例えば特許文献2などに詳細が記載されている。 $V_{S1-m}$ （3-1~3-m）はデータ線にデータ線駆動回路から与えられる映像信号電位であり、 $V_{VIDEOH}$ から $V_{VIDEOL}$ までの間の振幅を有する。ここで使用する液晶素子を± $V_{WHITE}$ の電位差を持つ電極で挟み込んだとき白（透過）表示をし、± $V_{BLACK}$ の電位差を持つ電極で挟み込んだとき黒（非透過）表示をするように液晶材料やギャップを選択すると、 $V_{comH} - V_{VIDEOH} > V_{VIDEOL} - V_{comL}$ 、 $V_{comH} - V_{VIDEOH} = V_{VIDEOL} - V_{comL} = V_{WHITE}$ 、 $V_{comH} - V_{VIDEOL} = V_{VIDEOH} - V_{comL} = V_{BLACK}$ となるように設定する。

30

## 【0005】

$V_{S1-m}$ （3-1~3-m）の電位は選択電位（ $V_{GON}$ ）にある走査線に接続されている画素スイッチング素子を通じ、画素電極へと印加される。ここで $V_{PIX4-1-1} \sim V_{PIX4-n-m}$ はm番目のデータ線とn番目の走査線に接続された画素電極の電位とすると、 $V_{PIX4-1-1}$ 、 $V_{PIX4-1-2}$ は走査線1が選択電位（ $V_{GON}$ ）にある時にデータ線1、2の電位（ $V_{s1}$ 、 $V_{s2}$ ）に充電され、それぞれ $V_{VIDEOH}$ 、 $V_{VIDEOL}$ の電位となる。この際、コモン電位は $V_{comH}$ であり、 $V_{PIX4-1-1}$ に対応する画素電極上の液晶には $V_{VIDEOH} - V_{comH} = -V_{WHITE}$ の電位が、 $V_{PIX4-1-2}$ に対応する画素電極上の液晶には $V_{VIDEOL} - V_{comH} = -V_{BLACK}$ の電位が印加されていることになる。すなわち、 $V_{PIX4-1-1}$ に対応する画素は透過（ホワイ

40

50

ト) 表示、 $V_{PIX4-1-2}$ に対応する画素は非透過(ブラック)表示となる。

#### 【0006】

次に走査線2が選択された時にはコモン電位は $V_{comL}$ に反転しているが、 $V_{PIX4-1-1}$ 、 $V_{PIX4-1-2}$ に対応する画素電極は接続されるスイッチング画素が高抵抗のためフローティング状態にあり、コモン電極と容量線との容量以外の容量が無視できるくらい小さいとすれば、容量結合により $V_{PIX4-1-1}$ 、 $V_{PIX4-1-2}$ の電位はコモン電極電位の変動幅分( $V_{comL} - V_{comH}$ )同時に下がり、 $V_{PIX4-1-1}$ に対応する画素は透過(ホワイト)表示、 $V_{PIX4-1-2}$ に対応する画素は非透過(ブラック)表示のままとなる。このように、コモン電位が反転を繰り返しても、非選択電位の走査線につながっている画素電極との電位差は変わらず、次の走査線が選択電位になるまでの間、同じ階調表示を維持できる。

10

#### 【0007】

一方、 $V_{PIX4-2-1}$ 、 $V_{PIX4-2-2}$ は走査線2が選択電位( $V_{GON}$ )にある時にデータ線1、2の電位( $V_{s1}$ 、 $V_{s2}$ )に充電され、それぞれ $V_{VIDEO1}$ 、 $V_{VIDEOH}$ の電位となる。この際は $V_{PIX4-2-1}$ に対応する画素電極上の液晶には $V_{VIDEO1} - V_{comL} = V_{WHITE}$ の電位が、 $V_{PIX4-2-2}$ に対応する画素電極上の液晶には $V_{VIDEOH} - V_{comL} = V_{BLACK}$ の電位が印加されていることになり、それぞれ透過(ホワイト)、非透過(ブラック)表示となるが、 $V_{PIX4-1-1}$ 、 $V_{PIX4-1-2}$ に対応する画素とは液晶にかかる電圧の極性が反転している。先ほどの説明と同様に走査線2が非選択電位となった後にコモン電位が反転しても、コモン電位と画素電位の電位差は変化せずに表示は保持される。リフレッシュ・レートに応じた書き換え時間の後、次フレームで再度走査線が選択電位になる際には、走査線1が選択電位( $V_{GON}$ )になるときにはコモン電位は $V_{comL}$ 、走査線2が選択電位( $V_{GON}$ )になるときにはコモン電位は $V_{comH}$ であり、液晶素子にかかる電位は前フレームとは極性が反転するため液晶の交流駆動が実現できる。以上が従来の1Hコモン反転駆動法である。

20

#### 【0008】

この方法によれば外部ICからの入力映像信号振幅は3~5Vで一般的なCMOSプロセスにより製造された安価なICが使用できるためにコストを低減できる。これはアクティブマトリクス基板の駆動回路を全て外付けする場合はもちろんあるし、駆動回路をアクティブマトリクス基板上に内蔵した駆動回路内蔵LCDの場合でも映像アナログ信号を入力するアナログ駆動においては映像信号を出力するICが必要であるし、DACやデコーダーを内蔵したデジタル駆動においてもDACやデコーダーにDC電源を供給する電源ICが必要なので同様である。また、電源生成回路をアクティブマトリクス基板上に内蔵した電源・駆動回路内蔵LCDの場合でも生成する電源の電圧範囲が広くなるほど、回路面積、消費電流が増大し、かつ薄膜トランジスターの信頼性に悪影響を与えるため、コモン反転駆動は有効な手法である。

30

#### 【0009】

【特許文献1】特開昭62-49399号公報

【特許文献2】特開2001-306041号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0010】

しかしながら、コモン反転駆動はあまり大きなサイズあるいは高い精細度のパネルには適用できないという問題を有している。すなわち、大型化、高精細化が進むとコモン電極の電気容量(C)が大きくなり、コモン電極の抵抗(R)も高くなるため、コモン電位を反転するのに容量遅延(RC遅延)が大きくなつてコモン電位の反転に時間がかかり、またコモン反転時に流れる電流も大きくなるため消費電流が増大するのである。

40

#### 【課題を解決するための手段】

#### 【0011】

本発明は上記の問題点を解決するため、コモン電位を反転する際(コモン反転タイミング)には走査線の少なくとも一部を各電位電源から高抵抗によって電気的に切り離した、いわゆるフローティング状態にすることでコモンの容量を低減するものである。発明者の

50

計算によると、コモン反転タイミングでデータ線がフロー・ティングされている場合、従来のコモン反転駆動方法においてはコモン電極の電気容量のうち 80% 以上は走査線との間の容量である。従って、なるべく多くの走査線をフロー・ティングにすることが好ましい。全ての走査線をフロー・ティングすれば最も望ましく、この場合はコモン電位の反転時間は従来例に比し 2 割にまで低減される。しかしながら、後述するように駆動上の都合により特定の走査線一本のみがフロー・ティングになっていなくても、例えば総走査線数 480 本とすると、残りの 479 本がフロー・ティングになっていれば全ての走査線をフロー・ティングした場合との容量の差異は 1% 以下であり差し支えは無い。このように、走査線をフロー・ティングすることで走査線数が増えて大型化が進んでも 1H コモン反転駆動あるいは他のコモン反転を実施でき、消費電力も低減されるというメリットを有する。

10

#### 【0012】

さらに本発明は走査線をフロー・ティング状態にするタイミングとして、画素トランジスターが N チャネル型の時にはコモン電位が高いときを選ぶ事を提案する。これにより、従来例のようにコモン電位によって走査線の非選択電位を切り替えたりすることなく、また非選択電位を信頼性に問題ができるほど低くすることなく、選択期間中以外の走査線電位がソースの映像信号の最低電位を上回らず確実に画素 TFT を OFF し、かつ走査線駆動回路に供給する電位の種類を少なくすることが可能となり、パネルの表示品位を落とさずにコストを低減し、信頼性を向上することができる。画素トランジスターが P チャネル型の場合はコモン電位が低い、すなわち次回コモン電位反転後は電位が高くなるタイミングを選んで走査線をフロー・ティング状態にすれば同様の効果が得られ、画素スイッチ素子に相補型伝送ゲートを使う時には伝送ゲートの N チャネル型トランジスターに繋がった走査線はコモン電位が高い時にフロー・ティング状態にし、P チャネル型トランジスターに繋がった走査線はコモン電位が低い時にフロー・ティング状態にすれば同様の効果が得られる。

20

#### 【0013】

さらに本発明は画素書き込み完了後、走査線に非選択電位を印加し始めてから走査線をフロー・ティングするまでの時間長を一定でなく複数とする駆動方法を提案する。これにより走査線選択期間を固定としたまま、前術のようにコモン電位の高低によって走査線をフロー・ティングにするタイミングを選ぶ事を可能とするため表示品位を低下させることが無い。

#### 【0014】

30

さらに本発明は走査線に選択電位を印加して接続された画素書き込み完了し、次に走査線に非選択電位を印加して画素スイッチング素子を OFF した後、適切なタイミングで走査線をフロー・ティング状態にしてから次に走査線に選択電位を印加するまでの間に、1 回あるいはそれ以上、非選択電位を印加する駆動方法を提案する。これにより、画像保持期間中のリーク電流等により走査線の電位が上昇して接続された画素スイッチング素子が予期せぬタイミングで ON 状態になることを防止できる。また、2 回目以降の非選択電位印加期間は画素スイッチング素子が N チャネル型トランジスターである場合はコモン電位が高い期間内に限り、また画素スイッチング素子が P チャネル型トランジスターである場合はコモン電位が低い期間内に限ることもあわせて提案する。これにより、非選択期間によって印加電位を変える必要が無く、走査線駆動回路に接続する電源電位の数を低減できるためコスト・信頼性の面で有利である。

40

#### 【0015】

さらに本発明はコモン反転時、コモン電位が高い期間とコモン電位が低い期間を互いに異なるようにし、画素スイッチング素子が N チャネル型薄膜トランジスターの場合はコモン電位が高い期間をコモン電位が低い期間より長く、また画素スイッチング素子が P チャネル型薄膜トランジスターの場合はコモン電位が低い期間をコモン電位が高い期間より長くする駆動方法を提案する。これにより、走査線選択・非選択期間を固定あるいはあまり差が大きくなない範囲の変動でコモン電位の高低によって走査線をフロー・ティングにするタイミングを選ぶ事を可能とし、表示品位を低下させること無く、駆動回路の構成を簡略化できる。

50

## 【0016】

さらに本発明は走査線の非選択電位はコモン電位によらず、常に一定値 ( $V_{GOFF}$ ) である駆動方法を提案する。これにより、走査線駆動回路に接続する電源数を低減し、駆動回路の構成を簡略化できるとともに、走査線をフローティングにするタイミングを選ぶ事で走査線の電位が画素スイッチを確実に OFF できるように駆動できる。

## 【0017】

また画素スイッチング素子が N チャネル型電界効果トランジスターの場合、データ線駆動回路により印加される映像信号電位の最低電位を  $V_{VIDEOOL}$ 、画素スイッチング素子のしきい値を  $V_{th}$ 、コモン電極の電位が高い時の電位を  $V_{COMH}$ 、コモンの電位が低い時の電位を  $V_{COML}$  としたとき、 $V_{GOFF} < V_{VIDEOOL} + V_{th} < V_{GOFF} < V_{VIDEOOL} - (V_{COMH} - V_{COML})$  を満たすように設定する事を提案する。 $V_{VIDEOOL} + V_{th} > V_{GOFF}$  であることで、映像信号が最低電位をとっても画素スイッチング素子は OFF し続ける。また、 $V_{GOFF} > V_{VIDEOOL} - (V_{COMH} - V_{COML})$  とすることでその分画素スイッチング素子にかかる逆バイアスを低減でき信頼性やリーク電流低減に役立つ一方で走査線をフローティングするタイミングを選択しているためにコモン反転時に走査線の電位が  $V_{VIDEOOL}$  を超えることがなく表示品位の低下がない。さらに望ましくは画素スイッチング素子のしきい値ばらつき、サブスレッシュホールド領域や逆バイアスでのリーク電流を考慮して、 $V_{VIDEOOL} - V_{GOFF} = V_{VIDEOH} - 6$  (ボルト) とすることが好ましい。

10

## 【0018】

同様に画素スイッチング素子が P チャネル型電界効果トランジスターの場合、 $V_{VIDEOH} + V_{th} < V_{GOFF} < V_{VIDEOOL} - (V_{COMH} - V_{COML})$  の範囲であること、さらに望ましくは  $V_{VIDEOH} - V_{GOFF} = V_{VIDEOOL} + 6$  (ボルト) であることを提案する。

20

## 【0019】

さらに本発明は走査線に非選択電位を与える期間の長さが常に一定であり、非選択電位は前記コモン・ハイ状態での値 (=  $V_{GOFFH}$ ) と前記コモン・ロー状態での値 (=  $V_{GOFFL}$ ) で相互に異なり、かつ  $V_{GOFFH} > V_{GOFFL}$  であることを特徴とする駆動方法も提案する。これは非選択電位を常に一定に保つ前記の提案に比べ、電源電位数が多くなるというデメリットの一方で、非選択電位を与える期間長を一定とできることから、駆動回路が簡略になるという長所を有している。

## 【0020】

30

さらに本発明はコモン電位反転時に走査線と同時にデータ線をも一部、より望ましくは全数フローティングとする駆動を提案する。これによりコモン電極の容量はより劇的に低減し、本発明の効果はさらに顕著となる。

## 【0021】

さらに本発明はこれらの駆動方法を用いた液晶表示装置を提案する。これらの駆動方法を用いる事で、大型高精細パネルにおいても低耐圧の I C を使用できるため、安価に装置が提供できる。また、消費電流も従来の駆動方式に比べ低減される。

## 【0022】

さらに本発明は走査線駆動回路の少なくとも一部は前記アクティブラマトリクス基板上に形成された薄膜トランジスターによって構成されている駆動回路内蔵型液晶表示装置であることを提案する。これにより、画素部から走査線駆動回路までの走査線引き回し配線部が短くなり、この部分の容量による容量分割によりコモン電位の変動より走査線の電位変動が小さくなる現象が最小限におさえられるという効果を有すると同時に、外部 I C の変更無しに提案してきたように駆動方法を変更できる。

40

## 【0023】

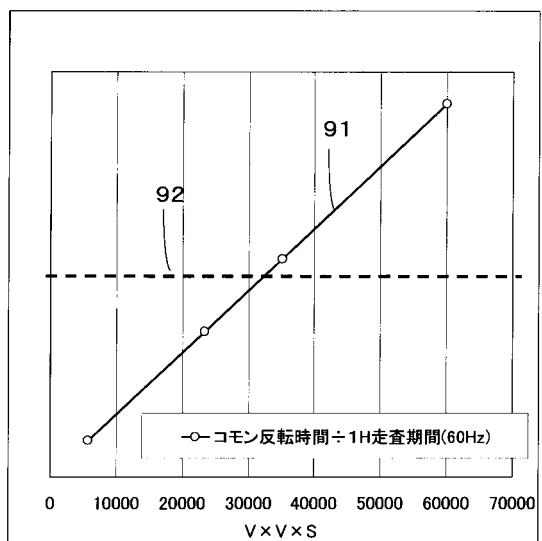

これらの発明は前述の通り、走査線の本数が多く、パネルが大型化するにつれて有効になる。具体的には、前記走査線の数 (=  $V$ ) の二乗に画像表示エリアの対角方向のサイズ (=  $S (m)$ ) で乗じた係数 (=  $V \times V \times S$ ) が 30000 以上になるような条件を満たすパネルについて本発明を適用する事をあわせて提案する。

## 【0024】

50

さらに本発明はこれらの駆動方法を用いた液晶表示装置を搭載したバッテリーで駆動される携帯電子機器を提案する。これらの駆動方法を用いた液晶表示装置を搭載することで従来より大型高精細の表示装置を備えていながら比較的安価な製品が提供でき、消費電流も従来の駆動方式に比べ低減されているためバッテリーの駆動時間が長くなる。ここでいう携帯電子機器とは、例えばノートパソコン、PDA、デジタルカメラ、ビデオカメラ、携帯テレビ、携帯電話、携帯フォトビューワー、携帯ビデオプレイヤー、携帯DVDプレイヤー、携帯オーディオプレイヤーなど液晶表示装置とバッテリーを搭載した電子機器のことである。

**【発明を実施するための最良の形態】**

**【0025】**

以下、本発明の実施形態を図面に基づいて説明する。

**【実施例1】**

**【0026】**

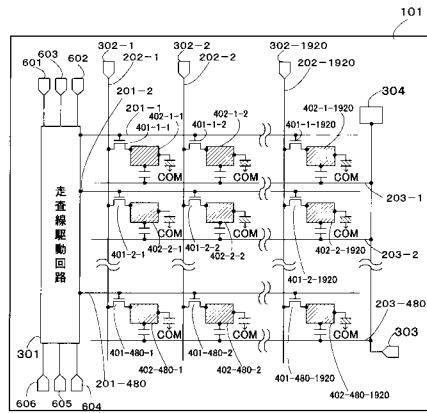

図1は本発明の請求項1、2、5、6、7、9、10、13および16に記載の駆動方法を実現する第一の実施例での走査線駆動回路内蔵型のアクティブマトリクス基板の構成図である。アクティブマトリクス基板(101)上には480本の走査線(201-1～480)と1920本のデータ線(202-1～1920)が直交して形成されており、480本の容量線(203-1～480)は走査線(201-1～480)と並行かつ交互に配置されている。データ線(202-1～1920)はデータ線入力端子(302-1～1920)に接続されている。容量線(203-1～480)は相互に短絡されてコモン電位入力端子(303)に接続される。対向導通部(304)もまた、コモン電位入力端子(303)に接続される。

**【0027】**

走査線(201-n)とデータ線(202-m)の各交点にはNチャネル型電界効果薄膜トランジスターよりなる画素スイッチング素子(401-n-m)が形成されており、そのゲート電極は走査線(201-n)に、ソース・ドレイン電極はそれぞれデータ線(202-m)と画素電極(402-n-m)に接続されている。画素電極(402-n-m)は容量線(203-n)と補助容量コンデンサーを形成し、また液晶表示装置として組み立てられた際には液晶素子をはさんで対抗基板電極(COM)とやはりコンデンサーを形成する。

**【0028】**

走査線(201-1～480)はアクティブマトリクス基板上にポリシリコン薄膜トランジスターを集積することで形成された走査線駆動回路(301)に接続されて駆動信号を与えられる。走査線駆動回路(301)にはCLK信号端子(601)、CLKX信号端子(602)、XST信号端子(603)、HENB端子(604)、LENB端子(605)、LCHG端子(606)が接続されている。また図示しないが、複数の電源電位も走査線駆動回路に接続されている。

**【0029】**

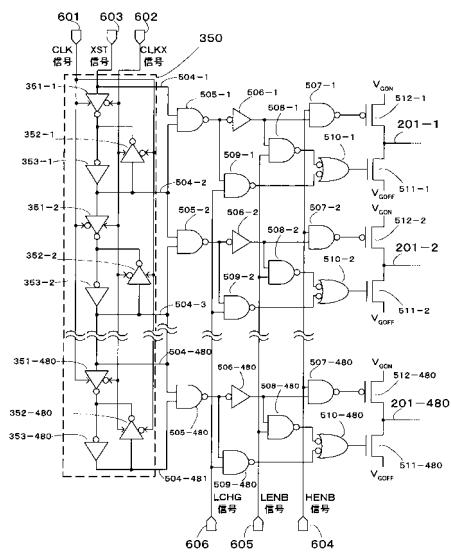

図2は走査線駆動回路(301)の詳細なる回路構成図である。走査線駆動回路(301)内にはシフトレジスタ回路(350)が内蔵されており、CLK信号端子(601)、CLKX信号端子(602)、XST信号端子(603)が接続されている。シフトレジスタは第一のクロックドインバーター(351-n)、第二のクロックドインバーター(352-n)、第一のインバーター(353-n)で一つの段が形成され、全部で480段となっており、初端・終端を含めて計481本の出力端子(504-1～481)を有している。

**【0030】**

シフトレジスタ回路(350)からのn(=1～480)番目の出力端子(504-n)とn+1番目の出力端子(504-n+1)が第一NAND回路(505-n)の入力端子にそれぞれ接続されており、第一NAND回路(505-n)の出力端子は第二インバーター(506-n)の入力端子と第四NAND回路(509-n)の入力端子の一方

10

20

30

40

50

に接続されており、第二インバーター（506-n）の出力端子は第二NAND回路（507-n）の入力端子の一方と第三NAND回路（508-n）の入力端子の一方に接続されている。さらに、第二NAND回路（507-n）の入力端子のもう一方にはHENB信号端子（604）が接続され、第三NAND回路（508-n）の入力端子のもう一方にはLENB信号（605）が接続され、第四NAND回路（509-n）の入力端子のもう一方にはLCHG信号端子（606）が接続されている。さらに、第三NAND回路（508-n）の出力端子と第四NAND回路（509-n）の出力端子はそれぞれ第五NAND回路（510-n）の入力端子に接続されている。第二NAND回路（507-n）の出力端子はPチャネル型薄膜トランジスターである第二トランジスター（512-n）のゲート端子に接続され、第五NAND回路（510-n）の出力端子はNチャネル型薄膜トランジスターである第一トランジスター（511-n）のゲート端子に接続されている。10

#### 【0031】

第一トランジスター（511-n）のソース端子は $V_{GOFF}$ の電位を有する電源に接続され、第二トランジスター（512-n）のソース端子は $V_{GON}$ の電位を有する電源に接続されている。また、第一トランジスター（511-n）のドレイン端子と第二トランジスター（512-n）のドレイン端子は走査線（201-n）に接続されている。図示しないが、第一のクロックドインバーター（351-n）、第二のクロックドインバーター（352-n）、第一のインバーター（353-n）、第一NAND回路（505-n）、第二インバーター（506-n）、第二NAND回路（507-n）、第三NAND回路（508-n）、第四NAND回路（509-n）および第五NAND回路（510-n）は電源として、VH電位端子ならびにVL電位端子と接続される。20

#### 【0032】

以下、図3、4ならびに5を用いて第一の実施例における具体的な駆動方法を説明する。図3、4ならびに5は奇数フレームの場合の図であり、偶数フレームの場合、コモン・ロー状態からフレームが始まり、同じくコモン・ロー状態で終了するため、各走査線が選択電位を与えられる時のコモン電極の電位が逆転することになる。

#### 【0033】

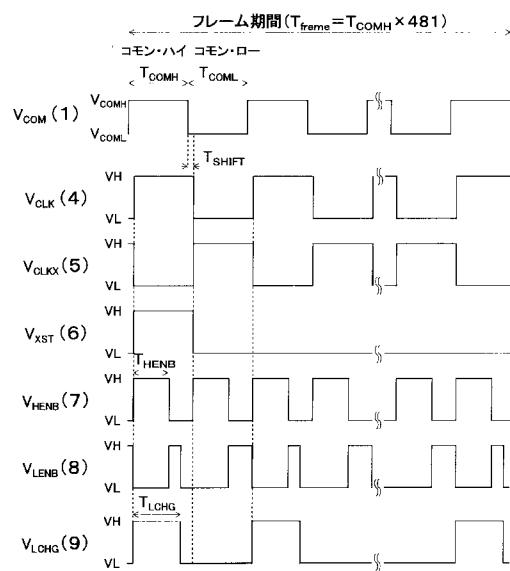

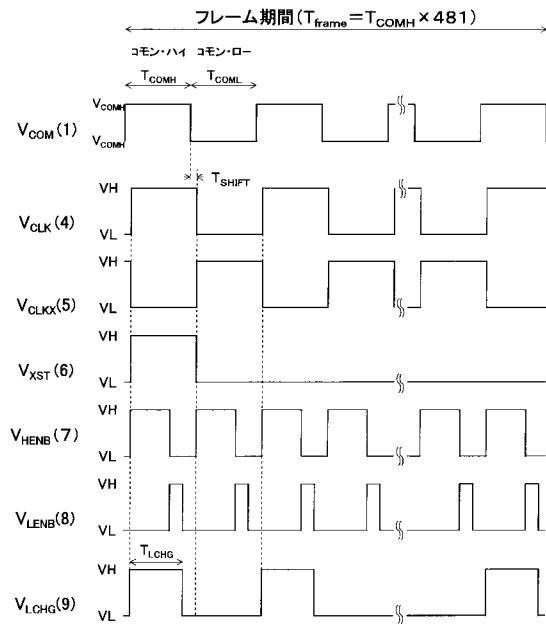

図3は第一の実施例における奇数フレームでの外部信号系より与えられる各信号のタイミングチャート図である。 $V_{COM}$ (1)はコモン電位入力端子(303)に与えられる電位であり、一定周期で $V_{COMH}$ と $V_{COML}$ 間を反転駆動される。 $V_{COMH}$ の保持期間 $T_{COMH}$ (この期間中をコモン・ハイ状態と称する)と $V_{COML}$ の保持期間 $T_{COML}$ (この期間中をコモン・ロー状態と称する)は等しく、 $T_{COMH}$ の481倍周期が1フレーム期間 $T_{frame}$ となる。 $V_{CLK}$ (4)はCLK信号端子(601)に与えられるシフトレジスタ駆動用正相クロック信号電位であり、 $V_{COM}$ (1)の反転周期と同一周期で $T_{SHIFT}$ だけずれた位相でVHとVLの間を反転駆動された信号が入力され、 $V_{CLKX}$ (5)はCLKX信号端子(602)に入力されるシフトレジスタ駆動用逆相クロック信号電位であり、VCLKとは逆極性の信号が入力される。 $V_{XST}$ (6)はXST信号端子(603)に入力されるシフトレジスタ初段ビットへの入力電位であり、パルス長 $T_{COMH}$ 、周期 $T_{frame}$ のパルス波である。30

#### 【0034】

$V_{HENB}$ (7)はHENB信号端子(604)に入力されるシフトレジスタにより選択された走査線に選択電位を与えるタイミングを意味する電位であり、 $V_{CLK}$ (4)が反転すると同時にVHとなり、一定期間( $T_{HENB} < T_{COMH}$ )後にVLとなる。40

#### 【0035】

$V_{LENB}$ (8)はLENB信号端子(605)に入力されるシフトレジスタにより選択された走査線に非選択電位を与えるタイミングを意味する電位であり、 $V_{HENB}$ (7)がVLに変化するとほぼ同時にVHとなり、コモン・ハイ状態期間では $V_{com}$ (1)が反転する前にVLに戻るが、コモン・ロー状態中には $V_{com}$ (1)が反転した後、VCLKが反転するのとほぼ同時にVLに戻る信号である。

#### 【0036】

10

20

30

40

50

$V_{LCHG}$ (9)はLCHG信号端子(606)に入力されるシフトレジスタにより選択された走査線以外に非選択電位を与える、すなわち走査線への $V_{GOFF}$ 再充電のタイミングを意味する電位であり、コモン・ハイ状態中に一定期間( $T_{LCHG} < T_{COMH}$ ) $VH$ となり、その他の期間は $VL$ となるパルス波である。

#### 【0037】

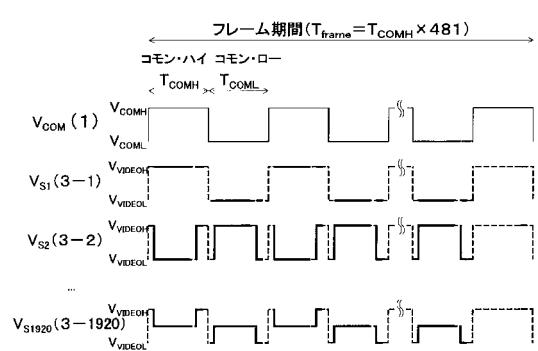

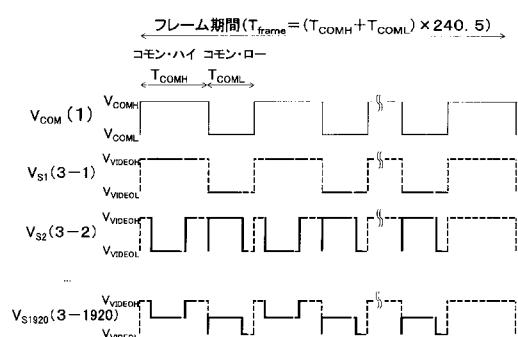

図4は第一の実施例における奇数フレームでの外部駆動回路から与えられる映像信号タイミングチャート図である。実線は電位が外部電源より与えられている状態を示し、破線は各外部電源との間が高抵抗で遮断されているフローティング状態を示す。以下、ノーマリー・ホワイトモードである事を前提として説明する。

$V_{S1-1920}$ (3-1~1920)はデータ線入力端子(302-1~1920)に入力される映像信号電位であり、最高電位 $V_{VIDEOH}$ ~最低電位 $V_{VIDEOL}$ の範囲内であって、その詳細波形は表示する画像により異なる。本実施例ではデータ線1(202-1)に接続された画素では白(透過)表示、データ線2(202-2)に接続された画素では黒(非透過)表示、データ線1920(202-1920)に接続された画素ではグレー(半透過)表示をそれぞれ行うように、また画素電極への充電完了・画素スチーリング素子OFF後、プレチャージ信号として白レベル信号を入力した後、コモン反転タイミングではフローティングするようにして $V_{S1}$ 、 $V_{S2}$ および $V_{S1920}$ の波形を描いている。 $V_{S1-1920}$ (3-1~1920)の映像信号の出力開始・停止タイミングやプレチャージタイミングは点順次駆動、線順次駆動、ブロック順次駆動などの駆動方式によりそれぞれ異なるが、いずれの場合でもコモン反転タイミングではデータ線をフローティング状態にしておくべきである。本実施例では線順次駆動を前提としている。

#### 【0038】

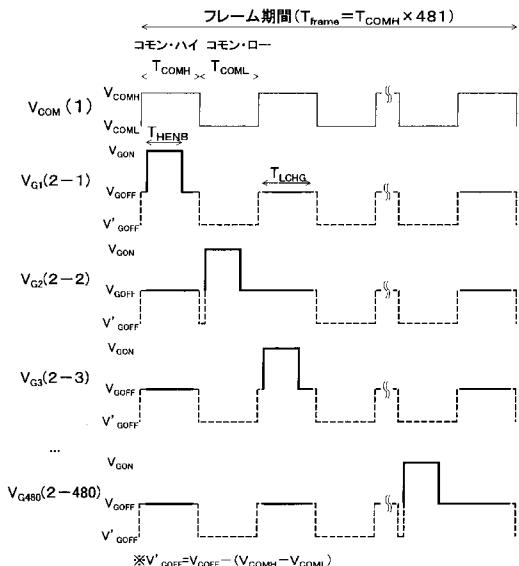

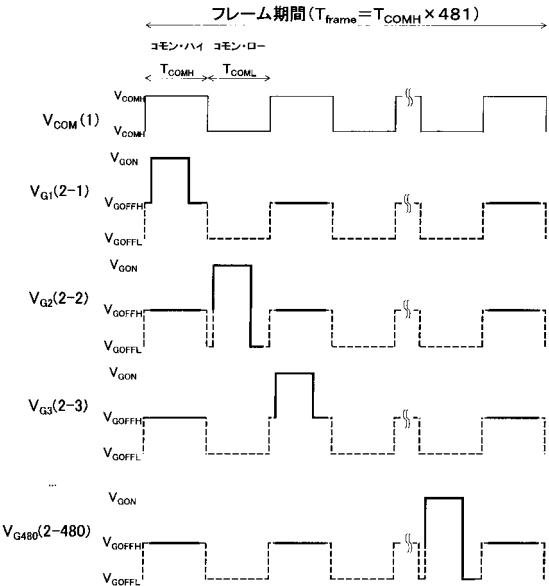

図5は第一の実施例における奇数フレームでの走査線駆動回路(301)から走査線(201-1~480)に与えられる出力信号を示すタイミングチャートである。実線は電位が外部電源より与えられている状態を示し、破線は各外部電源との間が高抵抗で遮断されているフローティング状態を示す。シフトレジスタ(350)は順次、特定の出力端子(504-n)とその隣の出力端子(504-n+1)にのみ $VH$ を出力し、CLK信号： $V_{CLK}$ (4)とCLKX信号： $V_{CLKX}$ (5)が反転する都度、 $VH$ を出力する端子が一つずつシフトしていく。これにより、最終的に走査線には $V_{G1-n}$ (2-1~2-480)のような電位が印加されることとなる。すなわち、奇数フレームでの走査線1、3、5... (2-1、2-3、2-5、...) のようにコモン・ハイ状態中に選択電位 $V_{GON}$ が与えられた走査線はコモン・ハイ状態期間内にフローティング状態となり、奇数フレームでの走査線2、4、6... (2-2、2-4、2-6、...) のようにコモン・ロー状態中に選択電位 $V_{GON}$ が与えられた走査線は $V_{COM}$ (1)が反転してから $T_{SHIFT}$ 後に $V_{CLK}$ (4)が反転するまでフローティング状態とならない。すなわち、非選択電位を書き込む時間を可変とする事で、フローティング状態になるタイミングを切り替えている。また、選択された走査線以外はコモン・ハイ期間中には非選択電位を $T_{LCHG}$ 期間書き込むが、コモン・ロー状態ならびにコモン・ハイ状態とコモン・ロー状態の反転タイミング前後ではフローティング状態をとる。なお図示しないが、偶数フレームでは奇数フレームとでは同じ走査線に選択電位 $V_{GON}$ が与えられる時のコモン電位の極性が反転し、液晶の交流駆動が行われるために液晶の信頼性も確保される。

#### 【0039】

本実施例での各電源電位は $VH > V_{GON} > V_{VIDEOH} > V_{VIDEOL} > V_{GOFF} > VL$ かつ $V_{comH} > V_{VIDEOH} > V_{VIDEOL} > V_{comL}$ となるように設定することが望ましい。また、 $V_{COMH} - V_{VIDEOH} = V_{WHITE}$ が使用する液晶素子、セルギャップに応じたノーマリー・ホワイト表示での白(透過)表示電圧、 $V_{VIDEOH} - V_{COML} = V_{BLACK}$ が同じくノーマリー・ホワイト表示での黒(非透過)表示電圧になるように設定する。

#### 【0040】

本実施例のように、画素スイッチング素子がポリシリコン薄膜トランジスターの場合しきい値ばらつきが大きく、サブスレッシュホールド領域や逆バイアスでのリーク電流が無視

10

20

30

40

50

できない。画面のリフレッシュ・レートが 60 Hz 以下の場合、リーク電流が 1 pA を超えると大きな保持容量を必要とし、表示品位を落とすほどに開口率が低下する。

#### 【0041】

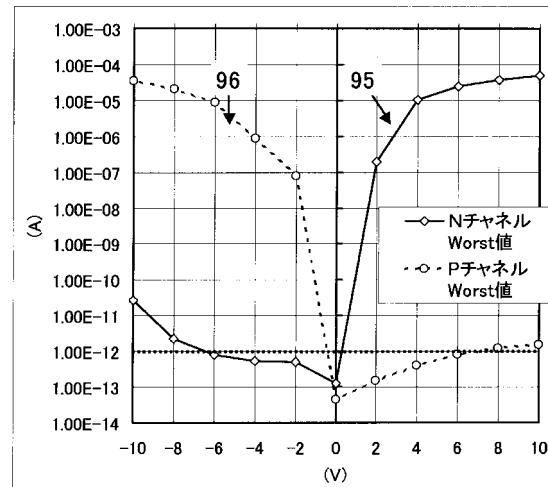

図 13 は発明者の測定したポリシリコン薄膜トランジスターを用いた画素スイッチング素子のリーク電流グラフである。横軸はゲート・ソース間電位 (V) であり、縦軸はソース・ドレイン間リーク電流 (A) であり、多点測定して最もリーク電流が大きかったデータを記載している。グラフ 1 (95) は N チャネル型トランジスターのデータであり、グラフ 2 (95) は P チャネル型トランジスターのデータである。本実施例のように N チャネル型トランジスターを使用している場合、グラフ 1 (95) より、画素スイッチング素子のリーク電流の最大値が 1 pA を下回るのはゲート・ソース間電位が 0 ~ -6 (V) の範囲であることがわかる。本発明における駆動ではゲート電位が  $V_{GOFF}$  の時、ゲート・ソース間電位は  $V_{GOFF} - V_{VIDEOL} \sim V_{GOFF} - V_{VIDEOH}$  の間になるので、 $V_{VIDEOL} - V_{GOFF} = V_{VIDEOH} - 6$  (V) とすることでゲート・ソース間電位は 0 ~ -6 (V) となってさらに好ましい。また、画素スイッチング素子に P チャネル型ポリシリコン薄膜トランジスターを利用した場合はグラフ 2 (96) よりリーク電流が 1 pA を下回るゲート・ソース間電位は 0 ~ +6 (V) の範囲であるため、 $V_{VIDEOH} - V_{GOFF} = V_{VIDEOL} + 6$  (V) の範囲がより好ましい。

10

#### 【0042】

また、一般的に一つの回路や素子に印加される電位の中心値（すなわち高電位と低電位の平均）はコモン電極電位の平均値と等しい事が液晶素子への影響という点から好ましい。

20

以上の条件を勘案した本実施例での各電位の設定値として、例えば  $V_{WHITE} = 0.5$  (V)、 $V_{BLACK} = 4.0$  (V) となるような液晶材料並びに貼り合わせギャップを選択したとするなら、 $V_H = 8.5$  (V)、 $V_{GON} = 7.5$  (V)、 $V_{COMH} = 6.5$  (V)、 $V_{VIDEOH} = 6$  (V)、 $V_{VIDEOL} = 2.5$  (V)、 $V_{COML} = 2$  (V)、 $V_{GOFF} = 1$  (V)、 $V_L = 0$  (V) とすれば良い。

#### 【0043】

このような駆動方法により、コモン・ハイからコモン・ローへの反転タイミングでは全ての走査線 (480 本) が、コモン・ローからコモン・ハイへの反転タイミングでは選択された走査線以外の走査線 (479 本) がフローティング状態であり、全ての走査線に非選択電位を書き込みづける従来の駆動方法に比べ、コモン反転時にコモン電位入力端子 (303) に流れる電流は非常に少なくなり、コモン電位の変化も早くなる。すなわち、同時に大型・高精細でも表示品位を落とさずコモン反転駆動が使用でき、映像信号を出力する I C として安価な低耐圧 I C が使用できる上に消費電力も少なくなる。

30

#### 【0044】

しかも、走査線をフローティングにするタイミングをコモン・ハイ状態とコモン・ロー状態で変えているため、走査線への非選択電位は一つであるにも関わらず、図 5 の  $V_{G1-480}$  (2 - 1 ~ 480) の通り、非選択状態での走査線はコモン電位と結合して電位が変動するが、 $V_{GOFF}$  以上には電位が上がらない。また、 $T_{COMH} + T_{COML}$  期間ごとに非選択電位の再書き込みを行うから、図 2 の第一トランジスター (511 - n) や第二トランジスター (512 - n) のリーク電流が大きくても走査線が保持期間中に非選択電位からずれる心配がない。

40

#### 【0045】

また、 $V_{GOFF}$  はコモン・ハイ状態でもコモン・ロー状態でも一定の電位で良く、電源電位を反転させる、あるいは二つの電位から一つを選択するといった必要性が無いため回路構成が簡易となり、コスト低減・歩留まり向上に効果的である。さらに  $V_{GOFF}$  を適切な値に設定しているので、コモン反転時にもソース電位によって画素スイッチング素子 (401 - n - m) が非選択 (保持) 期間中に ON してしまうことがなく、かつ画素スイッチング素子 (401 - n - m) にかかる逆バイアスを最小におさえ、信頼性の低下・画素スイッチング素子のリーク電流増大をまねく心配がない。

50

## 【0046】

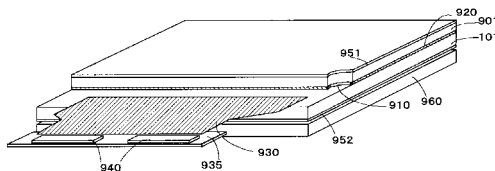

図6は請求項17から19に記載の液晶表示装置を実現する第一の実施例を示した透過型液晶表示装置の斜視構成図(一部断面図)である。アクティブマトリクス基板(101)と、カラーフィルター基板上にITOを成膜することでコモン電極を形成した対抗基板(901)をシール材(920)により貼り合わせ、その中にネマティック相液晶材料(910)を封入している。図示しないが、アクティブマトリクス基板(101)、対抗基板(901)ともに液晶材料(910)と接触する面にはポリイミドなどからなる配向材料が塗布され、互いに直交する方向にラビング処理されている。また、アクティブマトリクス基板(101)上の対向導通部(304)には導通材が配置され、対抗基板(901)のコモン電極と短絡されている。

10

## 【0047】

データ線入力端子(302-1~1920)、コモン電位入力端子(303)、CLK信号端子(601)、CLKX信号端子(602)、スタートパルス信号端子(603)、HENB信号端子(604)、LENB信号(605)、LCHG信号端子(606)や各種電源端子にはアクティブマトリクス基板(101)上に実装されたFPC(930)を通じて回路基板(935)上の1ないし複数の外部IC(940)に接続され、必要な電気信号・電位を供給される。

## 【0048】

さらに対抗基板の外側には上偏向板(951)を、アクティブマトリクス基板の外側には下偏向板(952)を配置し、互いの偏光方向が直交するよう(クロスニコル状)に配置する。さらに下偏向板(952)下にバックライトユニット(960)を取り付けて完成する。バックライトユニット(960)は冷陰極管に導光板や散乱板をとりつけたものでも良いし、EL素子によって発光するユニットでもよい。図示しないが、さらに必要に応じ、周囲を外殻で覆うあるいは上偏向板のさらに上に保護用のガラスやアクリル版を取り付けても良いし、視野角改善のため、光学補償フィルムを貼っても良い。

20

## 【0049】

このような液晶表示装置でコモン反転駆動を行った時のコモン電位遅延時間定数( $= C_{COM}$ )はコモン電極の平均抵抗( $= R_{COM}$ )と固定電位とつながった他の導体に対する総容量( $= C_{COM}$ )の積に概略比例( $C_{COM} \propto R_{COM} \times C_{COM}$ )する。一般的に $R_{COM}$ は対向電極のシート抵抗値や対向導通部・実装端子部の抵抗値などプロセス上の制約で決まり、あまりパネルサイズや精細度による変動は大きくない。一方、従来のコモン反転駆動方法では前記のとおり走査線との容量が $C_{COM}$ の80%以上であるため、総走査線数( $= V$ (本))に概略比例して $C_{COM}$ は増加する。また、走査線の長さが長いほど走査線1本当たりの容量は増大するから、画像表示エリアの対角方向のサイズ( $= S(m)$ )にも概略比例して $C_{COM}$ は増加する。一方、リフレッシュ・レートが一定であれば総走査線数( $= V$ (本))に反比例して1走査線への書き込み時間( $= T_{1H}$ )は低下する。すなわち、従来のコモン反転駆動方法では1走査線への書き込み時間に占めるコモン反転時間の割合( $C_{COM} \div T_{1H}$ )は、 $C_{COM} \div T_{1H} = V \times V \times S$ に概略準じ、この係数があまり大きくなると十分な画素書き込み時間が得られなくなり、表示品位や信頼性の低下につながる。

30

## 【0050】

図14は一般的なガラス基板を用いたアクティブマトリクス製造プロセスを使用する場合の前記走査線の数( $= V$ )の二乗に画像表示エリアの対角方向のサイズ( $= S(m)$ )で乗じた係数( $= V \times V \times S$ )と1H時間の中に占めるコモン反転時間の割合( $C_{COM} \div T_{1H}$ )を計算した結果を示すグラフである。なお、リフレッシュ・レートは60Hzとしている。グラフ1(91)が $C_{COM} \div T_{1H}$ を示すグラフであり、ほぼ $V \times V \times S$ に比例していることがわかる。限界線1(92)は画素書き込み時間を十分に確保するために必要な最低時間から割り出した限界ラインであり、これによると概略 $V \times V \times S = 30000$ 以上では従来の駆動方法では1Hコモン反転を行う事は困難になることがわかる。そこで、 $V \times V \times S = 30000$ を満たすパネルについて本実施例を適用する事で従来方法のコモン反転駆動が不可能であった大型・高精細パネルでも安価な低耐圧ICが使用できるため

40

50

、モジュール価格を安く製造でき、消費電力も少なくなる。本実施例では画素数 1920 × 480 のいわゆる VGA で対角 152.4 mm(6 型)であれば、 $V \times V \times S = 35113$  を得るので、このような条件を満たすことになる。

#### 【0051】

なお、本実施例においては第二のトランジスター(512-1~489)のリーク電流が少なければ、 $V_{LCHG}$  信号(9)が VH になる周期をより長くとって差し支えなく、さらには LCHG 信号端子(606)とそれに接続される配線、ならびに図 2 の第四 NAND 回路(509-n)を略し、第五 NAND 回路(510-1)をインバーター回路に置き換える構わない。これにより入力信号や回路構成が簡略化されるので、より安価な液晶表示装置が製造可能となる。

10

#### 【0052】

また、コモン電極の電位は二値( $V_{COMH}$ ,  $V_{COML}$ )の場合を例にとり説明したが、駆動方法によってはさらに細かな振幅を加え、三値以上としても構わない。この場合はコモン・ハイ状態でのコモン電極の平均電位、最大電位、最小電位のいずれかを  $V_{COMH}$ 、コモン・ロー状態でのコモン電極の平均電位、最大電位、最小電位のいずれかを  $V_{COML}$  と置き換えるべき。また、ゲートの選択電位や非選択電位をより細かな多値とするような駆動法にしても差し支えない。

また、図 2 の 350 に示したようなクロックドインバーターによるシフトレジスタ構成でなく、フリップフロップ回路や伝送ゲートによるシフトレジスタ構成に置き換えても良いし、シフトレジスタでなく様々な順次選択回路を用い、それにあわせて図 2 の論理回路部を変更してももちろん構わない。

20

#### 【0053】

また、本実施例では走査線駆動回路(301)を VH( $V_{GON}$ ) と VL( $V_{GOFF}$ ) の電位で駆動したが、そのうち一部をより低い電位差で駆動しても構わない。例えばシフトレジスタ(350)部の電源として VH M(< $V_{GON}$ ) と VL M(> $V_{GOFF}$ ) を用い、VCLK(4)、VCLKX(5)、VXST(6) の各信号の振幅も同様とする。そして出力端子(504-n)から第一トランジスター(511-n)・第二トランジスター(512-n)の間のいずれかの位置にレベルシフタ回路を設け、VH ~ VL レベルにまで昇圧すればよい。あるいは、シフトレジスタ(350)や第一 NAND 回路から第五 NAND 回路自体にレベルシフト機能をえた回路構成としても良い。このような構成にすることによって、消費電流を低減できる。

30

#### 【実施例 2】

#### 【0054】

図 7、8 および 9 は本発明の請求項 1、2、6、7、9、10、12、13 および 16 に記載の駆動方法を実現する第二の実施例における奇数フレームでの信号タイミングチャート図である。図中、実線は電位が外部電源より与えられている状態を示し、破線は各外部電源との間が高抵抗で遮断されているフローティング状態を示す。

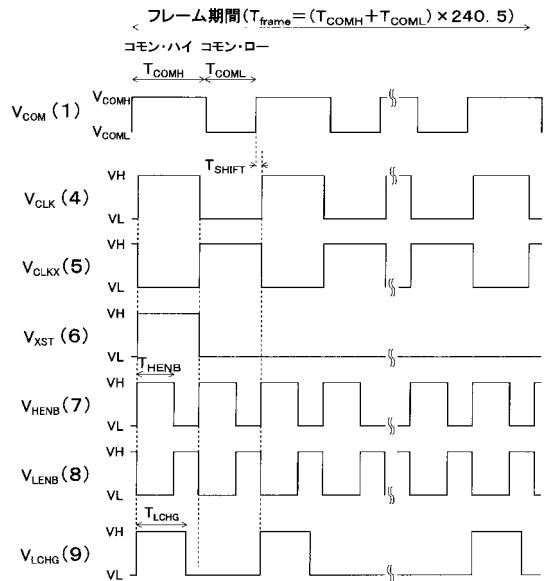

#### 【0055】

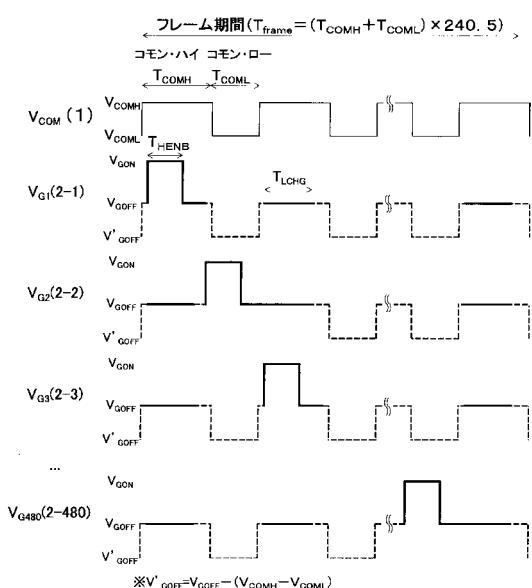

図 7 は第二の実施例における奇数フレームでの外部信号系より与えられる各信号タイミングチャート図である。 $V_{COM}(1)$  の  $V_{COMH}$  の保持期間  $T_{COMH}$  と  $V_{COML}$  の保持期間  $T_{COML}$  は  $T_{COMH} > T_{COML}$  であり、 $(T_{COMH} + T_{COML}) \times 240.5$  がフレーム期間  $T_{frame}$  となる。すなわち、偶数フレームではコモン・ハイの途中の状態から始まる事になる。

40

#### 【0056】

$V_{CLK}(4)$ 、 $V_{CLKX}(5)$ 、 $V_{XST}(6)$ 、 $V_{HENB}(7)$ 、 $V_{LCHG}(9)$  は実施例 1 と同じ波形であるが、 $V_{LENB}(8)$  はコモン・ハイ期間とコモン・ロー期間で VH となる長さは同一であり、 $V_{HENB}(7)$  と  $V_{LENB}(8)$  は逆極性波形になっている。

#### 【0057】

図 8 は第一の実施例における奇数フレームでの外部駆動回路から与えられる映像信号タイミングチャート図である。コモン反転タイミングでソースラインをフローティングにするため、映像信号の画素電極への印加時間が短くなっている他は特に第一の実施例の図 4

50

との差異は無い。

#### 【0058】

図9は第二の実施例における奇数フレームでの走査線駆動回路(301)から走査線(201-1~480)に与えられる出力信号を示すタイミングチャートである。VG1(2-1)、VG3(2-3)、...はコモン反転タイミングでコモン・ハイ状態となってからT<sub>SHIFT</sub>後に選択電位(V<sub>GON</sub>)を印加され、コモン・ハイ期間内にフローティングになるが、VG2(2-2)、VG4(2-4)、...はコモン反転タイミング直前にコモン・ハイ状態で選択電位(V<sub>GON</sub>)を印加されてからコモン反転タイミングとなり、非選択電位出力中に再度コモン反転タイミングとなる。本実施例では、コモン・ハイからコモン・ローへの反転タイミングでは選択電位を与えている走査線以外(479本)が、コモン・ローからコモン・ハイへの反転タイミングでは非選択電位を与えている走査線以外の走査線(479本)がフローティング状態であり、第一の実施例と同様に大型・高精細でも表示品位を落とさずコモン反転駆動が使用でき、映像信号を出力するICとして安価な低耐圧ICが使用できる上に消費電力も少なくなる。10

#### 【0059】

さらに、本実施例の場合、V<sub>HENB</sub>(7)信号とV<sub>LENB</sub>(8)信号が互いに極性反転した信号となっているため、どちらか一方のみを外部ICから供給し、他方はアクティブマトリクス基板上のインバーター回路により生成することで入力信号数、配線を簡単に削減できるという利点を有する。

#### 【0060】

なお、アクティブマトリクス基板の構成図、走査線駆動回路図、液晶表示装置のモジュール構成図は第一の実施例と同じであり、それぞれ図1、図2、図6を参照のこと。また、各種電源電位の設定とその効果も実施例1と同じである。20

#### 【実施例3】

#### 【0061】

図10および図11は請求項1、2、15および16に記載の駆動方法を実現する第三の実施例における奇数フレームでの信号タイミングチャート図である。実線は電位が外部電源より与えられている状態を示し、破線は各外部電源との間が高抵抗で遮断されているフローティング状態を示す。

#### 【0062】

図10は第三の実施例における奇数フレームでの外部信号系より与えられる各信号タイミングチャート図である。この実施例ではV<sub>comH</sub>の保持期間T<sub>comH</sub>(この期間中をコモン・ハイ状態と称する)とV<sub>comL</sub>の保持期間T<sub>comL</sub>(この期間中をコモン・ロー状態と称する)は等しく、T<sub>comH</sub>の481倍周期が1フレーム期間T<sub>frame</sub>となる。また、V<sub>HENB</sub>(7)信号とV<sub>LENB</sub>(8)信号はコモン・ハイ期間とコモン・ロー期間で変化は無く、T<sub>comH</sub>周期での繰り返し信号となっている。供給される映像信号のタイミングチャートは第一の実施例と相違ないため、図4参照のこと。30

#### 【0063】

図11は第三の実施例における奇数フレームでの走査線駆動回路(301)から走査線(201-1~480)に与えられる出力信号を示すタイミングチャートである。非選択電位は一定の値でなく、コモン・ハイ期間ではV<sub>GOFFH</sub>、コモン・ロー期間ではV<sub>GOFFL</sub>がそれぞれ走査線に印加される。なお、本実施例ではV<sub>GOFFH</sub>-V<sub>GOFFL</sub>=V<sub>COMH</sub>-V<sub>COML</sub>に概略一致するように設定する。40

#### 【0064】

本実施例の駆動方法によると、コモン・ハイからコモン・ロー、あるいはコモン・ローからコモン・ハイへのコモン電位反転タイミングでは全ての走査線(480本)がフローティング状態であり、第一の実施例や第二の実施例と同様あるいはそれ以上にコモン反転時の容量が少なく、大型・高精細液晶表示装置でも表示品位を落とさずコモン反転駆動法が使用でき、映像信号を出力するICとして安価な低耐圧ICが使用できる上に消費電力も少なくなる。また、第一や第二の実施例と比較するとV<sub>GOFF</sub>を反転させながら交流駆動50

させるための駆動回路数の増大や消費電流の増大、電源電位数の増大というデメリットはあるが、駆動信号の波形が単純なものになるため、外部信号回路の構成が簡素にできるという利点を有する。

#### 【0065】

また、画素スイッチング素子の逆バイアス時のリーク電流や信頼性が性能上十分であれば、本第三の実施例において $V_{GOFF}$ を常に（コモン・ハイ状態でも） $V_{GOFFL}$ に固定しても良い。この場合、装置内の回路構成は極めて単純なものになる。

#### 【0066】

なお、アクティブマトリクス基板の構成図、走査線駆動回路図、液晶表示装置のモジュール構成図は第一の実施例、第二の実施例と同じであり、それぞれ図1、図2、図6を参考のこと。10

#### 【産業上の利用可能性】

#### 【0067】

本発明は前述の実施の形態に限定されるものではなく、データ線駆動回路も内蔵した完全ドライバ内蔵アクティブマトリクス基板を使用した液晶表示装置でも構わないし、逆に走査線駆動信号を外部I C回路で供給する駆動回路非内蔵アクティブマトリクス基板を使用した液晶表示装置でも構わない。また、駆動回路の構成も相補型（CMOS）回路でなく、NチャネルまたはPチャネル型のみからなる片チャネル駆動回路でも実現可能である。画素スイッチング素子もP型トランジスタや相補型伝送ゲートを用いても構わないし、ポリシリコンでなくアモルファスシリコン薄膜トランジスターを用いてもよい。また、絶縁基板上に薄膜トランジスターを形成するのではなく、結晶シリコンウェハー上に画素スイッチング素子や駆動回路を作りこんだアクティブマトリクス基板でも良い。20

#### 【0068】

また、液晶表示装置として実施例のような透過型で無く反射型や半透過型としてもよいし、直視型で無く投影用のライトバルブとしてもよい。さらに実施例のようにノーマリー・ホワイトモードのみならず、ノーマリー・ブラックモードを使用してもよい。特にこの場合は液晶の配向モードとして垂直配向モードにしてもよい。

#### 【図面の簡単な説明】

#### 【0069】

【図1】本発明の実施例を説明するためのアクティブマトリクス基板構成図。30

【図2】本発明の実施例を説明するための走査線駆動回路図。

【図3】第一の実施例における奇数フレームでの外部信号系より与えられる各駆動信号タイミングチャート図。

【図4】第一の実施例・第三の実施例における奇数フレームでの外部信号系より与えられる映像信号タイミングチャート図。

【図5】第一の実施例における奇数フレームでの走査線信号出力タイミングチャート図。

【図6】本発明の実施例における液晶表示装置の斜視図（一部断面図）。

【図7】第二の実施例における奇数フレームでの外部信号系より与えられる各駆動信号タイミングチャート図。

【図8】第二の実施例における奇数フレームでの外部信号系より与えられる映像信号タイミングチャート図。40

【図9】第二の実施例における奇数フレームでの走査線信号出力タイミングチャート図。

【図10】第三の実施例における奇数フレームでの外部信号系より与えられる各駆動信号タイミングチャート図。

【図11】第三の実施例における奇数フレームでの走査線信号出力タイミングチャート図。45

【図12】従来のコモン反転駆動法を説明するための信号タイミングチャート図。

【図13】Nチャネル型薄膜トランジスターならびにPチャネル型薄膜トランジスターの画素スイッチング素子のリーク電流測定結果グラフ。

【図14】従来方法でのコモン反転駆動ができる液晶パネルのサイズ・精細度の限界を説50

明するためのグラフ。

【符号の説明】

【0070】

|                          |                             |    |

|--------------------------|-----------------------------|----|

| 101                      | アクティブマトリクス基板                |    |

| 201 - 1 ~ 480            | 走査線 1 ~ 480                 |    |

| 202 - 1 ~ 1920           | データ線 1 ~ 1920               |    |

| 301                      | 走査線駆動回路                     |    |

| 303                      | コモン電極電位入力端子                 |    |

| 304                      | 対向導通部                       |    |

| 350                      | シフトレジスタ                     | 10 |

| 351 - 1 ~ 480            | 第一のクロックドインバーター              |    |

| 352 - 1 ~ 480            | 第二のクロックドインバーター              |    |

| 353 - 1 ~ 480            | 第一のインバーター                   |    |

| 402 - 1 ~ 480 - 1 ~ 1920 | 画素電極 ( 1 ~ 480 , 1 ~ 1920 ) |    |

| 505 - 1 ~ 480            | 第一NAND回路                    |    |

| 506 - 1 ~ 480            | 第二インバーター                    |    |

| 507 - 1 ~ 480            | 第二NAND回路                    |    |

| 508 - 1 ~ 480            | 第三NAND回路                    |    |

| 509 - 1 ~ 480            | 第四NAND回路                    |    |

| 510 - 1 ~ 480            | 第五NAND回路                    | 20 |

| 511 - 1 ~ 480            | 第一トランジスター                   |    |

| 512 - 1 ~ 480            | 第二トランジスター                   |    |

| 601                      | C L K信号端子                   |    |

| 602                      | C L K X信号端子                 |    |

| 603                      | X S T信号端子                   |    |

| 604                      | H E N B端子                   |    |

| 605                      | L E N B端子                   |    |

| 606                      | L C H G端子                   |    |

| 901                      | 対向基板                        |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図 1 4】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 2 C |

| G 0 9 G | 3/20 | 6 2 2 Q |

| G 0 9 G | 3/20 | 6 2 3 Y |

| G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 G | 3/20 | 6 2 4 C |

| G 0 9 G | 3/20 | 6 8 0 S |

| G 0 9 G | 3/20 | 6 8 0 T |

(72)発明者 小橋 裕

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 一宮 誠

(56)参考文献 特開2001-306041(JP,A)

実開平07-033075(JP,U)

特開平09-274470(JP,A)

特開2003-233351(JP,A)

実開平7-33075(JP,U)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3