(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5152741号

(P5152741)

(45) 発行日 平成25年2月27日(2013.2.27)

(24) 登録日 平成24年12月14日(2012.12.14)

(51) Int.Cl.

HO3K 7/08 (2006.01)

F 1

HO3K 7/08

C

請求項の数 2 (全 10 頁)

(21) 出願番号 特願2007-97406 (P2007-97406)

(22) 出願日 平成19年4月3日 (2007.4.3)

(65) 公開番号 特開2008-258819 (P2008-258819A)

(43) 公開日 平成20年10月23日 (2008.10.23)

審査請求日 平成22年4月2日 (2010.4.2)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 江川 貢治

東京都目黒区下目黒1丁目8番1号 アル

コタワー15階 フリースケール・セミコ

ンダクタ・ジャパン株式会社内

最終頁に続く

(54) 【発明の名称】パルス幅変調波出力回路

## (57) 【特許請求の範囲】

## 【請求項 1】

パルス幅変調波出力回路であって、

第1のランプ電圧を負入力端子において受信する第1の電圧比較手段と、

前記第1のランプ電圧の位相をずらした第2のランプ電圧を負入力端子において受信する第2の電圧比較手段とを備え、

前記第1、第2の電圧比較手段はそれらの正入力端子において基準電圧を受信し、この基準電圧との比較に基づいて第1および第2パルス幅変調信号の生成に使用される第1および第2の比較信号を出力し、前記パルス幅変調波出力回路は更に、

前記第1及び第2の電圧比較手段から出力される比較信号を入力する第1及び第2の信号選択手段を備え、

前記第1の信号選択手段は、第1のクロック信号を取得し、この第1のクロック信号のオンオフに対応して前記第1及び第2の電圧比較手段から出力される比較信号を相互に選択して第1パルス幅変調信号を生成し、

前記第2の信号選択手段は、前記第1のクロック信号に対してオン期間の重複がある第2のクロック信号を取得し、この第2のクロック信号のオンオフに対応して前記第1、第2の電圧比較手段から出力される比較信号を相互に選択して第2パルス幅変調信号を生成することを特徴とするパルス幅変調波出力回路。

## 【請求項 2】

前記第1、第2のランプ電圧はのこぎり波形であることを特徴とする請求項1に記載の

10

20

パルス幅変調波出力回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ランプ電圧を用いて PWM 信号を出力するパルス幅変調波出力回路に関するものである。

【背景技術】

【0002】

一般に、交流から安定した直流電圧を供給するための電源装置には、リニアレギュレータやスイッチングレギュレータがある（例えば、特許文献 1、2 を参照。）。スイッチングレギュレータは、リニアレギュレータに比べ軽くて小さく、効率が高い。このスイッチングレギュレータは、スイッチング方式で制御する直流安定化電源の一つであり、パワー MOSFET などの半導体スイッチをオンオフすることで入力電力をスイッチングして、出力電圧を制御する。半導体スイッチのオンオフの時間の比率（デューティ比）を変えることで、出力電圧を制御する。

【0003】

例えば、特許文献 1 に記載のスイッチングレギュレータでは、入力電圧の変化に応じて生ずる出力電圧の変動を小さくするため、スイッチングレギュレータの制御回路に、入力電圧の微分回路とレベルシフト回路とを付加し、入力電圧の変化に応じて制御回路におけるのこぎり波レベルを変化させている。

【0004】

また、特許文献 2 に記載のスイッチングレギュレータでは、効率のよいスイッチング動作を実現するために、出力電位を平滑化するためのインダクタの後段の電位に基づいて、三角波発生回路からの出力を切り替える。

【0005】

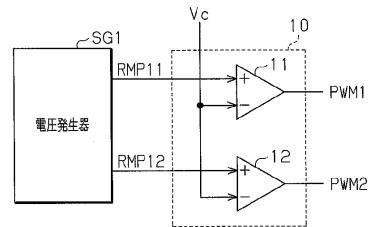

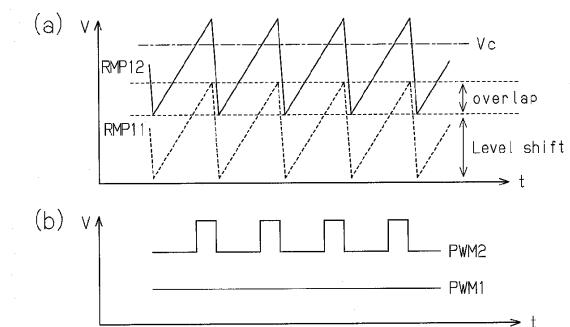

更に、2つの同じ波高のランプ電圧を用いて、二つのパルス幅変調（PWM）波を出力するデュアル PWM 波出力回路 10 に関する技術も検討されている。このデュアル PWM 波出力回路 10 を、図 7～図 9 を用いて説明する。このデュアル PWM 波出力回路 10 では、図 7 に示すように、2つのコンパレータ（11、12）を用いる。そして、このコンパレータ 11 には、電圧発生器 SG1 のランプ電圧 RMP11 と基準電圧 Vc とが入力されて変調波 PWM1 が出力される。一方、電圧発生器 SG1 のコンパレータ 12 には、ランプ電圧 RMP12 と基準電圧 Vc とが入力されて変調波 PWM2 が出力される。

【0006】

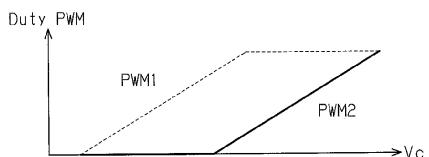

ここで、図 8 (a) に示すように、電圧発生器 SG1 のランプ電圧 (RMP11、RMP12) は、のこぎり波形の電圧であり、ランプ電圧 RMP12 は、ランプ電圧 RMP11 の最低電圧をレベルシフトさせて生成する。この結果、図 8 (b) に示すように、デュアル PWM 波出力回路 10 から変調波 (PWM1、PWM2) が出力される。ここで、ランプ電圧 (RMP11、RMP12) の重ね合わせの領域を制御することにより、基準電圧 Vc に対する変調波 (PWM11、PWM12) のパルス幅を制御することができる。そして、図 9 に示すように、基準電圧 Vc に対して、変調波 (PWM1、PWM2) のオノオフ比 (デューティ) を制御することができる。

【特許文献 1】特開平 5 - 68372 号公報（第 1 頁）

【特許文献 2】特開 2006 - 17462 号公報（第 1 頁）

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、特許文献 1、2 においては、昇降圧型 (Buck Boost) 用の 2 重のランプ電圧波形を用いる構成は考慮されていない。そして、一方の最低電圧を単純にレベルシフトして他方のランプ電圧を生成する方式では、電源電圧が低いアプリケーションでは十分な振幅を確保することが困難である。そして、ランプ電圧波高のばらつきと電圧シフト量のばら

10

20

30

40

50

つきとが独立であるため、ランプ電圧の最大値のばらつきが大きくなる。これは低電圧化を行なう場合にダイナミックレンジを制限する要因となる。また、この電圧のバラツキにより、重ねあわせ量のばらつきも大きくなる。このため、的確なパルス幅変調波を出力することができない。

#### 【0008】

本発明は、上記課題を解決するために、的確なデュアルPWM波を効率的に出力することができるパルス幅変調波出力回路を提供することにある。

#### 【課題を解決するための手段】

#### 【0009】

本発明のパルス幅変調波出力回路では、第1のランプ電圧を入力する第1の電圧比較手段と、前記第1のランプ電圧の位相をずらした第2のランプ電圧を入力する第2の電圧比較手段とを備え、前記第1、第2の電圧比較手段は基準電圧を取得し、この基準電圧との比較に基づいて出力される比較信号を利用してオンオフ比が異なるパルス幅変調信号を生成することを要旨とする。通常、ランプ電圧をレベルシフトする場合には、高い電圧精度が必要であり、また電源電圧に律則されることになる。本発明では、位相をずらしたランプ電圧を利用することにより、電源電圧に律則されることなく的確なデュアルPWM波を効率的に出力することができる。10

#### 【0010】

本発明のパルス幅変調波出力回路では、前記第1、第2のランプ電圧はのこぎり波形であることを要旨とする。これにより、デュアルPWM波を効率的に出力することができる。20

#### 【0011】

本発明のパルス幅変調波出力回路では、前記第1、第2の電圧比較手段から出力される比較信号を入力する論理和手段と論理積手段とを更に備え、前記論理和手段及び論理積手段から、オンオフ比が異なるパルス幅変調信号を生成することを要旨とする。従って、論理和手段及び論理積手段からの出力を用いてデュアルPWM波を出力することができる。

#### 【0012】

本発明のパルス幅変調波出力回路では、前記第1、第2の電圧比較手段から出力される比較信号を入力する第1、第2の信号選択手段を更に備え、前記第1の信号選択手段は、第1のクロック信号を取得し、この第1のクロック信号のオンオフに対応して前記第1、第2の電圧比較手段から出力される比較信号を相互に選択してパルス幅変調信号を生成し、前記第2の信号選択手段は、前記第1のクロック信号に対してオン期間の重複がある第2のクロック信号を取得し、この第2のクロック信号のオンオフに対応して前記第1、第2の電圧比較手段から出力される比較信号を相互に選択してパルス幅変調信号を生成することを要旨とする。これにより、位相のずれた第1、第2のクロック信号（マルチクロック）を利用して、周期が安定したデュアルPWM波を出力することができる。この結果、低電圧化を行なう場合にもより広いダイナミックレンジを確保することができる。更に、クロック信号の2倍の周波数のデュアルPWM波を生成するとともに、オン期間の重複量に応じてオンオフ比（デューティ）を制御することができる。30

#### 【0013】

本発明のパルス幅変調波出力回路では、位相をずらした第3、第4のランプ電圧を入力する第1、第2のアナログ信号選択手段を更に備え、前記第1のアナログ信号選択手段は、第1のクロック信号を取得し、この第1のクロック信号のオンオフに対応して前記第3、第4のランプ電圧を相互に選択して前記第1のランプ電圧を生成し、前記第2のアナログ信号選択手段は、前記第1のクロック信号に対してオン期間の重複がある第2のクロック信号を取得し、この第2のクロック信号のオンオフに対応して前記第3、第4のランプ電圧を相互に選択して前記第2のランプ電圧を生成することを要旨とする。第1、第2のアナログ信号選択手段を用いて、位相とレベルとが異なる第1、第2のランプ電圧を生成し、周期が安定したデュアルPWM波を出力することができる。この結果、低電圧化を行なう場合にもより広いダイナミックレンジを確保することができる。更に、クロック信号4050

の2倍の周波数のデュアルPWM波を生成するとともに、オン期間の重複量に応じてオンオフ比(デューティ)を制御することができる。

**【発明の効果】**

**【0014】**

本発明によれば、簡易な回路構成により、的確なデュアルPWM波を効率的に出力することができる。

**【発明を実施するための最良の形態】**

**【0015】**

(第1の実施形態)

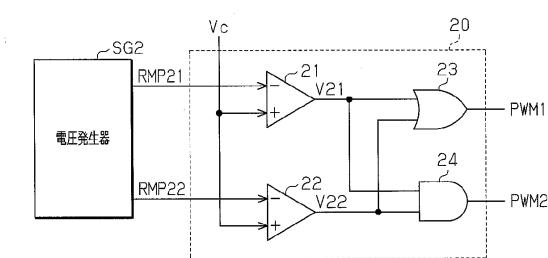

以下、本発明を具体化したパルス幅変調波出力回路の一実施形態を図1、2に従って説明する。本実施形態のパルス幅変調波出力回路としてのデュアルPWM波出力回路20は、図1に示すように、2つのコンパレータ(21、22)、論理和手段としての論理和演算回路23、論理積手段としての論理積演算回路24を備えている。ここで、コンパレータ21は第1の電圧比較手段、コンパレータ22は第2の電圧比較手段として機能する。

**【0016】**

そして、このコンパレータ21の負入力端子には電圧発生器SG2のランプ電圧RMP21(第1のランプ電圧)が入力され、正入力端子には基準電圧Vcが入力されて電圧V21が出力される。一方、コンパレータ22の負入力端子には電圧発生器SG2のランプ電圧RMP22(第2のランプ電圧)が入力され、正入力端子には基準電圧Vcが入力されて電圧V22が出力される。

**【0017】**

そして、電圧V21及び電圧V22は、論理和演算回路23及び論理積演算回路24に入力される。そして、論理和演算回路23からは変調波PWM1が出力され、論理積演算回路24からは変調波PWM2が出力される。

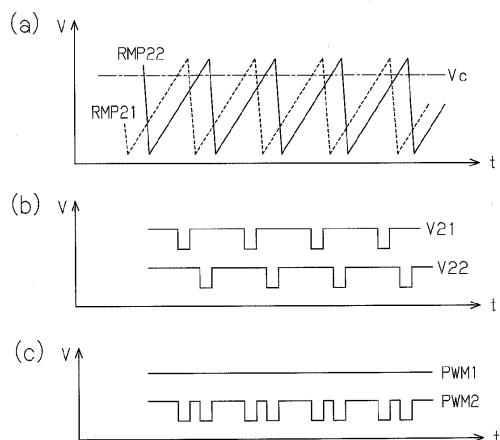

**【0018】**

ここで、電圧発生器SG2において生成され、コンパレータ(21、22)に入力されるランプ電圧(RMP21、RMP22)の波形を図2(a)に示す。図2(a)に示すように、電圧発生器SG2のランプ電圧(RMP21、RMP22)は、のこぎり波形の電圧であり、ランプ電圧RMP22は、ランプ電圧RMP21と同じ波高が維持しながら、時間軸上でシフト(位相をシフト)させて生成する。この場合、ランプ電圧(RMP21、RMP22)に、電圧(V21、V22)にオーバーラップ領域が生じるようにシフト量を制御しておく。

**【0019】**

この場合、コンパレータ(21、22)から出力される電圧(V21、V22)は、図2(b)に示すように、位相がシフトした矩形波となる。そして、このような電圧(V21、V22)の論理積、論理和を算出する。これにより、図2(c)に示すように、デュアルPWM波出力回路20から、デューティ(オンオフ比)が異なる変調波(PWM1、PWM2)が出力される。

**【0020】**

上記実施形態のパルス幅変調波出力回路によれば、以下のよう効果を得ることができる。

(1) 上記実施形態では、デュアルPWM波出力回路20には、同じ波高で時間軸上において位相をシフトさせたランプ電圧(RMP21、RMP22)を入力する。これらのランプ電圧を用いてデューティが異なる変調波(PWM1、PWM2)を出力する。これにより、ランプ電圧の波高や電圧シフトによるばらつきを抑えることにより、低電圧化を行なう場合にもより広いダイナミックレンジを確保し、的確なパルス幅変調波を出力することができる。従って、電源電圧が低いアプリケーションでも十分なスイングを確保することができる。

**【0021】**

(2) 上記実施形態では、ランプ電圧(RMP21、RMP22)に、電圧(V21

10

20

30

40

50

、V<sub>22</sub>)にオーバーラップ領域が生じるようにシフト量を制御しておく。そして、このシフト量により、デューティが異なる変調波(PWM1、PWM2)を出力する。電圧方向にシフトさせる場合は、ランプ電圧の傾きをコンパレータで比較して時間信号に変換することになるが、上記実施形態のように時間軸でシフトさせた場合には直接時間信号として扱うため、誤差要因がすくなくなり、精度を上げることが可能となる。

#### 【0022】

##### (第2の実施形態)

次に、本発明を具体化したパルス幅変調波出力回路の第2の実施形態を図3、4に従つて説明する。なお、第2の実施形態は、第1の実施形態の論理和演算回路23及び論理積演算回路24に対して、マルチプレクサ(33、34)を用いた構成になっている。本実施形態においても、第1の実施形態と同様に、時間軸上で位相をシフトさせた二つのランプ電圧を用いる。10

#### 【0023】

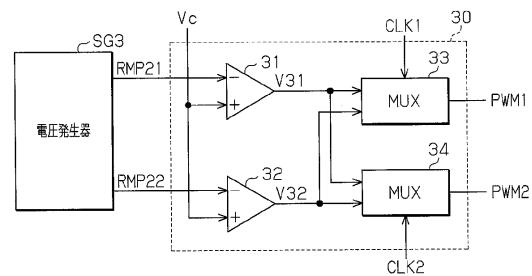

本実施形態のパルス幅変調波出力回路としてのデュアルPWM波出力回路30は、図3に示すように、2つのコンパレータ(31、32)、マルチプレクサ(33、34)を備えている。ここで、コンパレータ31は第1の電圧比較手段、コンパレータ32は第2の電圧比較手段として機能する。コンパレータ31の負入力端子には電圧発生器SG3のランプ電圧RMP31が入力され、正入力端子には基準電圧Vcが入力される。また、コンパレータ32の負入力端子には電圧発生器SG3のランプ電圧RMP32が入力され、正入力端子には基準電圧Vcが入力される。そして、コンパレータ31からは電圧V31が出力され、コンパレータ32からは電圧V32が出力される。20

#### 【0024】

また、マルチプレクサ(33、34)は第1、第2の信号選択手段として機能し、入力された複数の信号の中から、クロック信号に応じて、所定の入力信号を選択する。

そして、電圧V31及び電圧V32は、マルチプレクサ(33、34)に入力される。このマルチプレクサ33にはクロック信号CLK1(第1のクロック信号)、マルチプレクサ34にはクロック信号CLK2(第2のクロック信号)が入力される。そして、マルチプレクサ33からは変調波PWM1が出力され、マルチプレクサ34からは変調波PWM2が出力される。30

#### 【0025】

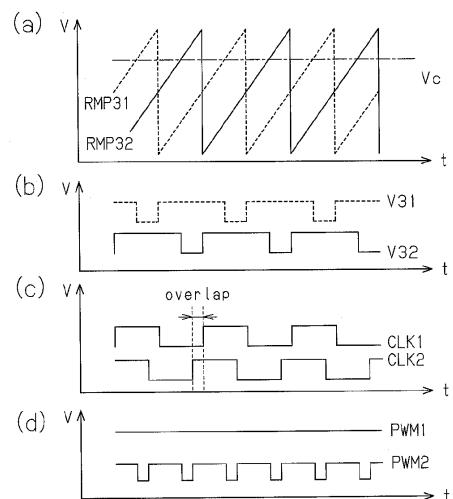

ここで、電圧発生器SG3において生成され、コンパレータ(31、32)に入力されるランプ電圧(RMP31、RMP32)の波形を図4(a)に示す。図4(a)に示すように、電圧発生器SG3のランプ電圧(RMP31、RMP32)は、のこぎり波形の電圧である。そして、ランプ電圧RMP32は、ランプ電圧RMP31と同じ波高が維持しながら、位相を180度、シフトさせて生成する。この場合、コンパレータ(31、32)から出力される電圧(V31、V32)は、図4(b)に示すように、位相がシフトした矩形波が出力される。

#### 【0026】

更に、マルチプレクサ(33、34)には、図4(c)に示すように、同じクロック周波数であって、時間軸上でシフト(位相をシフト)させたクロック信号(CLK1、CLK2)を入力する。このクロック信号(CLK1、CLK2)には、オンレベルを重ね合わせたオーバーラップ領域(オン期間の重複)を設けておく。40

#### 【0027】

ここで、マルチプレクサ33は、クロック信号CLK1がオンレベルの場合は電圧V32を選択し、クロック信号CLK1がオフレベルの場合は電圧V31を選択する。マルチプレクサ34は、クロック信号CLK2がオンレベルの場合は電圧V31を選択し、クロック信号CLK2がオフレベルの場合は電圧V32を選択する。この結果、マルチプレクサ(33、34)からは、図4(d)に示すように、デューティが異なる変調波(PWM1、PWM2)が出力される。ここで、変調波PWM2は、クロック信号のタイミングによって2倍の周波数とすることができます。50

## 【0028】

上記実施形態のパルス幅変調波出力回路によれば、第1の実施形態の(1)に記載の効果に加えて以下のような効果を得ることができる。

(3) 上記実施形態では、デュアルPWM波出力回路30は、2つのコンパレータ(31、32)、複数の信号を合成するマルチプレクサ(33、34)を備えている。マルチプレクサ(33、34)には、同じクロック周波数であって、位相をシフトさせたクロック信号(CLK1、CLK2)を入力する。このクロック信号(CLK1、CLK2)は同じクロック周期であり、更にオンレベルを重ね合わせたオーバーラップ領域を設けておく。第1の実施形態のデュアルPWM波出力回路20では、時間軸上でシフトさせた2つのランプ電圧(RMP21、RMP22)と比較した上でパルス幅変調波を重ね合わせるため、生成されたPWMのデューティはランプ電圧の基点によって、1周期おきに変調波は異なるものとなる。また、2つの異なるコンパレータ(21、22)を用いて1つのパルス幅変調波を生成するため、コンパレータのオフセットの差による影響も受けることがある。上記実施形態では、重ね合わせをクロック信号(CLK1、CLK2)より時間的に作るので、重ね合わせ量のばらつきを低減させることができる。10

## 【0029】

## (第3の実施形態)

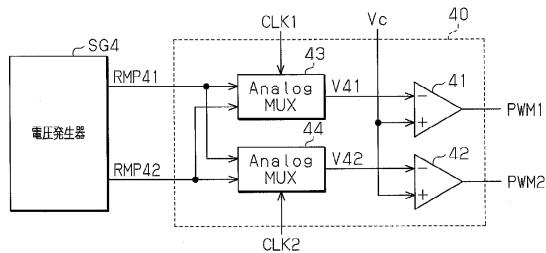

次に、本発明を具体化したパルス幅変調波出力回路の第3の実施形態を図5、6に従って説明する。なお、第2の実施形態は、第1の実施形態の論理和演算回路23及び論理積演算回路24に対して、アナログマルチプレクサ(43、44)を用いた構成になっている。本実施形態においても、第1、第2の実施形態と同様に、時間軸上で位相をシフトさせた二つのランプ電圧を用いる。20

## 【0030】

本実施形態のパルス幅変調波出力回路としてのデュアルPWM波出力回路40は、図5に示すように、2つのコンパレータ(41、42)、アナログマルチプレクサ(43、44)を備えている。ここで、コンパレータ41は第1の電圧比較手段、コンパレータ42は第2の電圧比較手段として機能する。

## 【0031】

アナログマルチプレクサ(43、44)は、第1、第2のアナログ信号選択手段、入力された複数のアナログ信号(第3、第4のランプ電圧)の中から、クロック信号に応じて、所定の信号を選択する。このアナログマルチプレクサ(43、44)には、電圧発生器SG4のランプ電圧(RMP41、RMP42)が入力される。そして、アナログマルチプレクサ43にはクロック信号CLK1、アナログマルチプレクサ44にはクロック信号CLK2が入力される。そして、アナログマルチプレクサ43からは電圧V41が出力され、アナログマルチプレクサ44からは電圧V42が出力される。30

## 【0032】

そして、各コンパレータ(41、42)の正入力端子には基準電圧Vcが入力されるとともに、電圧V41はコンパレータ41の負入力端子、電圧V42はコンパレータ42の負入力端子に、それぞれ入力される。そして、コンパレータ41からは変調波PWM1が出力され、コンパレータ42からは変調波PWM2が出力される。40

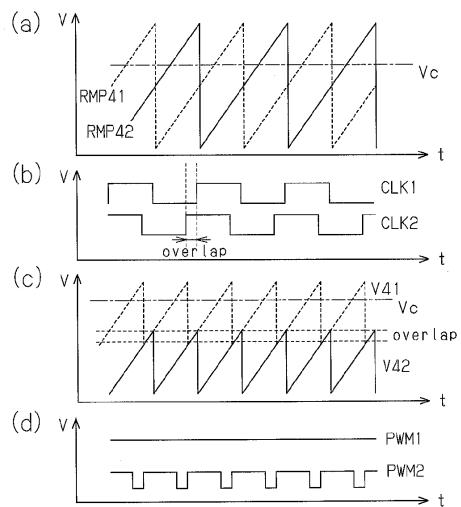

## 【0033】

ここで、電圧発生器SG4において生成され、アナログマルチプレクサ(43、44)に入力されるランプ電圧(RMP41、RMP42)の波形を図6(a)に示す。図6(a)に示すように、電圧発生器SG4のランプ電圧(RMP41、RMP42)は、のこぎり波形の電圧であり、ランプ電圧RMP42は、ランプ電圧RMP41と同じ波高が維持しながら、位相を180度、シフトさせて生成する。

## 【0034】

更に、アナログマルチプレクサ(43、44)には、図6(b)に示すように、同じクロック周波数であって、位相をシフトさせたクロック信号(CLK1、CLK2)を入力する。このクロック信号(CLK1、CLK2)には、オンレベルを重ね合わせたオーバ

一ラップ領域を設けておく。

**【0035】**

ここで、アナログマルチブレクサ43は、クロック信号CLK1がオンレベルの場合はランプ電圧RMP42を選択し、クロック信号CLK1がオフレベルの場合はランプ電圧RMP41を選択する。アナログマルチブレクサ44は、クロック信号CLK2がオンレベルの場合はランプ電圧RMP41を選択し、クロック信号CLK2がオフレベルの場合はランプ電圧RMP42を選択する。この結果、アナログマルチブレクサ(43、44)からは、図6(c)に示すように、電圧レベルとともに位相がシフトした電圧(V41、V42)が出力される。

**【0036】**

そして、電圧V41が入力されたコンパレータ41は、電圧V41と基準電圧Vcとを比較して、変調波PWM1を出力する。また、電圧V42が入力されたコンパレータ42は、電圧V42と基準電圧Vcとを比較して、変調波PWM2を出力する。この結果、デュアルPWM波出力回路30から、図6(d)に示すように、デューティが異なる変調波(PWM1、PWM2)が出力される。

**【0037】**

上記実施形態のパルス幅変調波出力回路によれば、第1の実施形態の(1)、第2の実施形態の(3)に記載の効果に加えて以下のような効果を得ることができる。

(4) 上記実施形態では、デュアルPWM波出力回路40は、2つのコンパレータ(41、42)、クロック信号に応じて複数の信号から任意の信号を選択するアナログマルチブレクサ(43、44)を備えている。従来の2つのコンパレータによる構成の前段に、アナログマルチブレクサ(43、44)を設けることにより、的確なデュアルPWM波を効率的に出力することができる。

**【0038】**

なお、上記実施形態は以下のように変更してもよい。

上記第1の実施形態のデュアルPWM波出力回路20では、時間軸上でシフトさせた2つのランプ電圧(RMP21、RMP22)と比較した上でパルス幅変調波を重ね合わせるため、生成されたPWMのデューティはランプ電圧の基点によって、1周期おきに変調波は異なるものとなる。この場合、ランプ電圧(RMP21、RMP22)の位相のずれを180度にすることにより、均一な周期の変調波(PWM1、PWM2)を出力させることができる。

**【0039】**

上記第2、第3の実施形態では、デュアルPWM波出力回路に入力する2つのランプ電圧RMPにおいて、位相を180度シフトさせたが、ランプ電圧の位相のずれは180度に限定されるものではない。

**【0040】**

上記実施形態では、デュアルPWM波出力回路(20、30、40)のコンパレータ22の正入力端子に基準電圧Vcを入力するように構成したが、負入力端子に入力するように構成することも可能である。

**【図面の簡単な説明】**

**【0041】**

【図1】本実施形態のパルス幅変調波出力回路の説明図。

【図2】動作時のタイミングチャートであり、(a)は入力するランプ電圧、(b)はコンパレータからの出力電圧、(c)は出力されるPWM波の説明図。

【図3】他の実施形態のパルス幅変調波出力回路の説明図。

【図4】動作時のタイミングチャートであり、(a)は入力するランプ電圧、(b)はコンパレータからの出力電圧、(c)はマルチブレクサに入力されるクロック信号、(d)は出力されるPWM波の説明図。

【図5】他の実施形態のパルス幅変調波出力回路の説明図。

【図6】動作時のタイミングチャートであり、(a)は入力するランプ電圧、(b)はア

10

20

30

40

50

ナログマルチプレクサに入力されるクロック信号、(c)はコンパレータからの出力電圧、(d)は出力されるPWM波の説明図。

【図7】従来のパルス幅変調波出力回路の説明図。

【図8】動作時のタイミングチャートであり、(a)は入力するランプ電圧、(b)は出力されるPWM波の説明図。

【図9】デュアルPWM波における基準電圧とデューティの関係の説明図。

【符号の説明】

【0042】

SG1, SG2, SG3, SG4...出電圧発生器、10, 20, 30, 40...デュアル

PWM波出力回路、21, 22, 31, 32, 41, 42...コンパレータ、23...論理和

演算回路、24...論理積演算回路、33, 34...マルチプレクサ、43, 44...アナログ

マルチプレクサ、RMP11, RMP12, RMP21, RMP22, RMP31, RMP32, RMP41, RMP42...ランプ電圧、

PWM1, PWM2...変調波、Vc...基準電圧。 10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 村上 晋太郎

東京都目黒区下目黒1丁目8番1号 アルコタワー15階 フリースケール・セミコンダクタ・ジャパン株式会社内

審査官 吉田 隆之

(56)参考文献 特開昭62-6524(JP,A)

特開昭62-130016(JP,A)

特開昭62-194728(JP,A)

特開2006-6016(JP,A)

特開2000-92851(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K