## (12) 发明专利

(10) 授权公告号 CN 107094370 B

(45) 授权公告日 2021.01.05

(21) 申请号 201380023414.X

(72) 发明人 厄尔·T·柯亨

(22) 申请日 2013.05.01

(74) 专利代理机构 北京律盟知识产权代理有限公司 11287

(65) 同一申请的已公布的文献号

申请公布号 CN 107094370 A

代理人 章蕾

(43) 申请公布日 2017.08.25

(51) Int.CI.

G11C 29/00 (2006.01)

(30) 优先权数据

G11C 16/06 (2006.01)

13/464,433 2012.05.04 US

G11C 16/34 (2006.01)

(85) PCT国际申请进入国家阶段日

2014.11.03

(56) 对比文件

US 2010070799 A1, 2010.03.18

(86) PCT国际申请的申请数据

US 2010020604 A1, 2010.01.28

PCT/US2013/039138 2013.05.01

CN 101611549 A, 2009.12.23

(87) PCT国际申请的公布数据

审查员 黄晓亮

W02013/166200 EN 2013.11.07

(73) 专利权人 希捷科技有限公司

权利要求书3页 说明书30页 附图5页

(74) 地址 美国加利福尼亚州

(54) 发明名称

固态硬盘控制器的0-1平衡管理

(57) 摘要

SSD控制器保持0计数和1计数,和/或在一些实施方案中0/1的差异计数,用于每个读取单元从SLC NVM(或MLC下页)读取。在读取单元是不可校正的事件,部分是由于阈值电压分布远离其标称分布的漂移,保持的计数能判断方向和/或幅度来调整进行跟踪阈值电压漂移和恢复读取数据的0/1平衡的读取阈值。在各种实施例中,调整后的读取阈值由所描述的各种方法(计数、百分比),其基于多个描述因子(确定阈值电压分布、已知存储值,过去NVM操作事件)确定。对MLC存储器上述技术的扩展也描述了。

1. 一种用于管理0-1平衡的方法,所述方法包括:

加扰被写入到非易失性存储器的部分中的数据,以产生具有0位的已知统计平均数和1位的已知统计平均数的加扰数据;

写入所述加扰数据到所述非易失性存储器的部分;

在所述写入之后,读取所述非易失性存储器的部分;

计算从所述非易失性存储器的部分读取数据中0位数和1位数的差异;

至少部分基于所述差异为所述非易失性存储器的后续读取确定阈值电压;

使用所述阈值电压重新读取所述非易失性存储器的部分;

在重新读取之前,使用ECC解码器解码从所述非易失性存储器的部分读取的所述数据,以确定从所述非易失性存储器的部分读取的所述数据是不可校正的;

其中所述写入包括使用ECC编码器编码所述加扰数据并将所编码的所述加扰数据写入至所述非易失性存储器的所述部分,且其中所述ECC编码器添加一个或多个字节到所述加扰数据,并且其中由所述ECC编码器添加的所述一个或多个字节具有所述0位的已知统计平均数和所述1位的已知统计平均数。

2. 根据权利要求1所述的方法,其中所述计算包括:评估预期的0位数和从所述非易失性存储器的部分读取的0位数之间的差。

3. 根据权利要求1所述的方法,其中所述确定进一步基于0位的已知统计平均数或1位的已知统计平均数。

4. 根据权利要求1所述的方法,其中所述差异是第一差异,所述阈值电压为第一阈值电压,并且还包括:

使用第一阈值电压以ECC解码器解码从非易失性存储器的部分重新读取的所述数据,以确定使用所述第一阈值电压从所述非易失性存储器的部分重新读取的所述数据是不可校正的;

计算使用所述第一阈值电压从所述非易失性存储器的部分重新读取数据中0位数和1位数之间的第二差异;

以及至少部分基于所述第二差异,为所述非易失性存储器的第二重新读取确定第二阈值电压。

5. 根据权利要求4所述的方法,还包括:

使用所述第二阈值电压重新读取所述非易失性存储器的部分。

6. 根据权利要求4所述的方法,其中基于所述第二差异相对于所述0位的已知统计平均数和所述1位的已知统计平均数指示过量的1位,所述第二阈值电压低于所述第一阈值电压。

7. 根据权利要求4所述的方法,其中基于所述第二差异相对于所述0位的已知统计平均数和所述1位的已知统计平均数指示过量的0位,所述第二阈值电压高于所述第一阈值电压。

8. 根据权利要求1所述的方法,其中所述非易失性存储器包括多级单元非易失性存储器,并且所述差异是针对下页读取。

9. 一种用于耦合至外部非易失性存储器的设备,所述设备包括:

用于加扰被写入到所述外部非易失性存储器的部分中的数据,以产生具有0位的已知

统计平均数和1位的已知统计平均数的加扰数据的装置；

用于写入所述加扰数据到所述外部非易失性存储器的部分的装置；

用于在所述写入之后,读取所述外部非易失性存储器的部分的装置；

用于计算从所述外部非易失性存储器的部分读取数据中0位数和1位数的差异的装置；

用于至少部分基于所述差异确定所述外部非易失性存储器的后续读取的阈值电压的装置；

用于使用所述阈值电压重新读取所述外部非易失性存储器的部分的装置；

用于在重新读取之前,使用ECC解码器解码从所述外部非易失性存储器的部分读取的数据,以确定从所述非易失性存储器的部分读取的数据是不可校正的装置；其中所述写入包括使用ECC编码器编码所述加扰数据并将所编码的加扰数据写入至所述外部非易失性存储器的所述部分,其中所述ECC编码器添加一个或多个字节到所述加扰数据,并且其中由所述ECC编码器添加的所述一个或多个字节具有所述0位的已知统计平均数和所述1位的已知统计平均数。

10. 根据权利要求9所述的设备,其中所述确定进一步基于所述0位的已知统计平均数或所述1位的已知统计平均数。

11. 根据权利要求9所述的设备,其中所述差异是第一差异,所述阈值电压为第一阈值电压,并且还包括:

用于使用第一阈值电压以ECC解码器解码从所述外部非易失性存储器的所述部分重新读取的所述数据,以确定使用所述第一阈值电压从所述外部非易失性存储器的部分重新读取的所述数据是不可校正的装置；

用于计算使用所述第一阈值电压从所述外部非易失性存储器的部分重新读取数据中0位数和1位数之间的第二差异的装置；以及

用与至少部分地基于所述第二差异来确定用于所述外部非易失性存储器的第二次重新读取的第二阈值电压的装置。

12. 根据权利要求11所述的设备,进一步包括:

用于使用所述第二差异,重新读取所述外部非易失性存储器的所述部分的装置。

13. 根据权利要求11所述的设备,其中基于所述第二差异相对于所述0位的已知统计平均数和所述1位的已知统计平均数指示过量的1位,所述第二阈值电压低于所述第一阈值电压。

14. 根据权利要求11所述的设备,其中基于所述第二差异相对于所述0位的已知统计平均数和所述1位的已知统计平均数指示过量的0位,所述第二阈值电压高于所述第一阈值电压。

15. 根据权利要求9所述的设备,其中所述外部非易失性存储器包括多级单元非易失性存储器,并且所述差异是针对下页读取。

16. 一种非暂时性计算机可读介质,其上存储一组指令,当由处理元件执行时引起处理元件执行和/或控制操作,包括:

加扰被写入到非易失性存储器的部分中的数据,以产生具有0位的已知统计平均数和1位的已知统计平均数的加扰数据；

写入所述加扰数据到所述非易失性存储器的部分；

在所述写入之后,读取所述非易失性存储器的部分;

计算从所述非易失性存储器的部分读取数据中0位数和1位数的差异;

至少部分基于所述差异为所述非易失性存储器的后续读取的确定阈值电压;

使用所述阈值电压重新读取所述非易失性存储器的部分;

在重新读取之前,使用ECC解码器解码从所述非易失性存储器的部分读取的数据,以确定从所述非易失性存储器的部分读取的所述数据是不可校正的;

其中所述写入包括使用ECC编码器编码所述加扰数据并将所编码的加扰数据写入至所述非易失性存储器的所述部分,且其中所述ECC编码器添加一个或多个字节到所述加扰数据,并且其中由所述ECC编码器添加的所述一个或多个字节具有所述0位的已知统计平均数和所述1位的已知统计平均数。

17.根据权利要求16所述的非暂时性计算机可读介质,其中所述确定进一步基于0位的已知统计平均数或1位的已知统计平均数。

18.根据权利要求16所述的非暂时性计算机可读介质,其中所述差异是第一差异,所述阈值电压为第一阈值电压,并且所述操作还包括:

使用第一阈值电压以ECC解码器解码从所述非易失性存储器的所述部分重新读取的所述数据,以确定使用所述第一阈值电压从所述非易失性存储器的部分重新读取的所述数据是不可校正的;

计算使用所述第一阈值电压从所述非易失性存储器的部分重新读取数据中0位数和1位数之间的第二差异;以及

至少部分基于所述第二差异,为所述非易失性存储器的第二重新读取确定第二阈值电压。

19.根据权利要求18所述的非暂时性计算机可读介质,所述操作进一步包括:

使用所述第二阈值电压重新读取所述非易失性存储器的部分。

20.根据权利要求18所述的非暂时性计算机可读介质,其中基于所述第二差异相对于所述0位的已知统计平均数和所述1位的已知统计平均数指示过量的1位,所述第二阈值电压低于所述第一阈值电压。

21.根据权利要求18所述的非暂时性计算机可读介质,其中基于所述第二差异相对于所述0位的已知统计平均数和所述1位的已知统计平均数指示过量的0位,所述第二阈值电压高于所述第一阈值电压。

22.根据权利要求16所述的非暂时性计算机可读介质,其中所述非易失性存储器包括多级单元非易失性存储器,并且所述差异是针对下页读取。

## 固态硬盘控制器的0-1平衡管理

### 技术领域

[0001] 非易失性存储技术的进步被需要用来提供性能、效率以使用效用的改进。

### 背景技术

[0002] 除非明确标识为公开或众所周知,此处提及的技术和概念,包括用于上下文、定义或比较的目的,不应当被解释为承认这样的技术和概念是之前公开已知的或是现有技术的一部分。本文引用的所有参考文献(如果有),包括专利、专利申请和出版物,在此通过引用并入其整体,无论是专门并入与否,用于所有目的。

[0003] 固态硬盘(SSD)控制器所使用的闪存的各个方面现在将被描述成部分地建立背景技术和部分地建立本说明书的平衡中所使用先行术语。通过SSD控制器从非易失性存储器(Non-Volatile Memory, NVM)读出的数据最小尺寸是“读取单元”,它由包括的误差校正保护,如低密度奇偶校验(Low-Density Parity-Check, LDPC)码。在一些实施方案中,每个读取单元包含大约4K到大约32K位的用户数据,加上纠错开销。在SSD控制器的命令下,这些位从非易失性存储器的存储器单元被读出,其中根据下面讨论的技术,可以保持每个单元一个或多个位。在一些实施方案中,出于安全原因,在写入到NVM数据之前SSD控制器加密数据。在一些实施方案中,相对于相同可编程单元的长字符串,考虑到电路设计的限制,在写入NVM数据之前SSD控制器加扰数据。

[0004] 单独地考虑,每个单元都有特定的存储(可编程)电荷对应于该单元设备阈值电压,并进一步对应于存储在该单元中的逻辑位值。理想状态是对于存储的逻辑位值来说所有NVM中的单元会具有相同的设备阈值电压,而实践中由于各种原因设备阈值电压在整个单元中沿阈值电压轴概率分布(即,“阈值电压分布”)类似于高斯形状。

[0005] 考虑到在大量单元集合体中,如读取单元,存在多种设备阈值电压分布(例如高斯概率曲线)如同每个单元的状态(每单元每存储位的两种状态)。即,对于每个存储单元的N位,有 $2^{**N}$ 个状态和相同数量的阈值电压分布。一般情况下, $(2^{**N}) - 1$ 不同读取阈值(读取基准电压 $V_{READ1}$ 至 $V_{READ(N-1)}$ )被NVM中的读取电路所需以便在 $2^{**N}$ 个状态之间进行区分。

[0006] 从上述继续,单层单元(Single Level Cell, SLC)闪存, $N=1$ 。从而SLC存储器每个存储单元保存一位,有两个设备阈值电压分布(一个0和另一个1),并且需要单独读取阈值,读取基准电压 $V_{READ1}$ 。从低到高阈值电压,这两个阈值电压分布被称为E(擦除)状态和D1(第一数据)状态。任意地,常规映射(编码)用来分配逻辑1给E状态和逻辑0给D1状态。因此,0和1的引用都是D1状态和E状态各自解码的代理引用。

[0007] 从上述进一步继续,多层单元(Multi-Level Cell, MLC)闪存, $N>1$ 。因而MLC存储器每单元存储多于一位,具有两个以上的设备阈值电压分布,并且需要多个不同的读取阈值来区分分布。例如,4LC存储器每单元存储两位,有四个设备阈值电压分布,并且通常需要三个读取阈值(读取基准电压 $V_{READ1}$ 、 $V_{READ2}$ 和 $V_{READ3}$ )。从低到高阈值电压,该四个设备阈值电压分布被称为E(清除)、D1(数据1)、D2(数据2)和D3(数据3)状态。任意地,按照特定的二进制序列四个阈值电压分布的每个也被映射(编址),诸如格雷码序列。因此,对一个或多个的

11、10、00和01状态的引用是用于E、D1、D2和D3状态的各自解码的代理引用。

[0008] 相对于处理MLC状态的地址映射,每个可被表示为具有最高有效位 (Most Significant Bit,MSB) 和最低有效位 (Least Significant Bit,LSB) (并且每个单元多于2位,在之间有意义的位)。虽然MLC的NVM编程这些单元有各种方式,下面的方法是常见的。初始编程轮(电荷分布操作)设置LSB,例如,写入“下页”。以相同方式写入SLC可以松散地完成,例如,建立E状态阈值电压分布和第二状态阈值电压分布的充电操作。根据所使用的二进制序列,该第二状态阈值电压分布与D1状态阈值电压分布类似,也类似于D2状态阈值电压分布,或在D1和D2状态阈值电压分布之间。对于MLC而言,一个或多个附加编程轮进一步操纵设备阈值电压分布(在数量上,沿电压阈轴的位置,并在形状上),正如每个MLC层数所需要的。更具体地,一个或多个后续的编程操作写“中间页”(如果有的话,为每个单元多于2位),和最后的编程操作建立MSB,例如,写入“上页”。例如在4LC(每单元MLC2位)中,E分布和第一程序轮的第二分布通过第二程序轮分别分岔入E和D1分布及D2和D3分布。

[0009] 由于一个或多个因素阈值电压分布被修改偏离其初始/标称分布,诸如读取干扰、写入干扰和保留损失。更具体地,随着时间的推移,温度以及使用相关的其他因素,每个阈值电压分布的位置相对于阈值电压轴移动。由于读取阈值是先前基于标称阈值电压分布建立的,这种变化增加了使用读取基准电压值产生的读取错误的可能性。在一些SLC实施方案中,当硬判决不可校正错误在从NVM读出的读取单元中被遇到时,一系列的重试操作被进行以恢复读取单元。重试操作包括在读取阈值 $V_{READ1}$ 的不同电压值时NVM重新读取(采样)该读取单元,如通过来自SSD控制器的I/O命令写入的寄存器设置来决定。通过读取在所读取阈值 $V_{READ1}$ 不同设置,读出单元对阈值电压轴不同点进行采样以试图找出(硬判决)可校正的读取单元样本。

[0010] 一种NVM供应商建议的算法是慢慢向上(从它的标称数值增加读取基准电压 $V_{READ1}$ )扫描SLC读取阈值以试图找到可校正的读取单元样本。如果这个过程失败,则所读取的阈值被扫描在另一个方向上(从它的标称数值降低读取基准电压 $V_{READ1}$ )。如果这两个扫描失败,则读取单元是不可校正(通过硬判决解码)。线性扫描读取阈值,在不同的各自读取基准电压的设定值下可能具有16至64的步骤,需要读取单元的许多费时的样本(每个有伴随恢复时间延迟)。甚至当这样的搜索很少需要,因此在平均延迟上不产生重大的影响,对于具有严格的最大延迟需求的应用,包括一些数据库应用,这种费时的搜索是不能接受的。

## 发明内容

[0011] 本发明可以以多种方式实现,包括作为方法、制造品、设备、系统、物质组成以及计算机可读介质如计算机可读存储介质(例如,在大容量存储设备如磁盘,或者具有非易失性存储器的集成电路如闪存的光介质和/或磁介质)或程序指令通过光学或电子通信链路被发送的计算机网络。在本说明书中,这些实现方式或本发明可以采取的任何其他形式可以被称为技术。具体实施方式提供了在上述确定的领域能改善性能、效率以及使用效能的本发明的一个或多个实施方案的阐述。本具体实施方式包括简介以便于对详细说明其余部分更快速的理解。根据描述的概念引言包括系统、方法、制品以及计算机可读介质的一个或多个示例实施方案。如同在结论中更详细地讨论,本发明包括授权的权利要求书范围内的所有可能的修改和变化。

[0012] 本发明人认为首先要注意到对于读取阈值管理和随之而来的低延迟性能和延长寿命的好处,加扰数据写入到NVM以及跟踪和管理加扰数据状态的统计分布的重要意义。更具体地,本发明人认为首先要注意在读取与写入数据状态的统计分布的差距表明用于读取NVM的最佳读取阈值中的偏移。在一些实施方案中,SSD控制器加扰数据,例如将数据写入NVM之前加密。加扰数据具有已知的0/1平衡(存储为0和1的位的统计分布),如具有接近0位和1位的50-50平衡。随着高效加扰,数据是随机的。在NVM读取单元的大小的随机抽样中,0和1的分布往往是非常严格的(平均值的狭义分散)。例如,16K(16384)的随机位,0计数或1计数的概率远离平均值(8K)超过大约300在任一方向是<1% (和超过大约500的概率在任一方向是<百万分之一)。

[0013] 相对于阈值电压轴远离标称分布(由于任意数量的因素)的各种阈值电压分布的变换,采取行动来改变阈值电压分布峰值之间的中心点的位置。没有相应的跟踪调整到相应的读取阈值地改变实际“阈值电压中点”是读取错误的原因。本发明人认为首先要注意中心点变化的意义,对于读取阈值电压管理和随之而来的低延迟性能和延长寿命的好处。

[0014] 根据上述观察,在一些实施方案中SSD控制器至少暂时保持从SLC的NVM(或MLC的下页)读取的每个读取单元的0计数和1计数。该情况下读取单元是不可校正的部分原因是阈值电压分布偏离(初始)标称分布的偏移,0计数和/或1计数能确定方向和/或幅值以移动读取阈值(读取基准电压 $V_{READ1}$ )用以跟踪偏移阈值电压分布和恢复0/1平衡。呈现在具体实施方式中,根据实施方案,读取阈值的新电压设定是根据一些因素(例如,观察到的/推断的阈值电压分布、已知的存储值和过去的NVM操作活动)以各种方式(计数、百分比)来确定的。

[0015] 上述技术对于MLC存储器是可扩展的,包括用于维持上页计数和多个读取阈值的变动。上述技术也可以用于具有已知0/1平衡而不是50-50平衡的多种加密/加扰方式。

## 附图说明

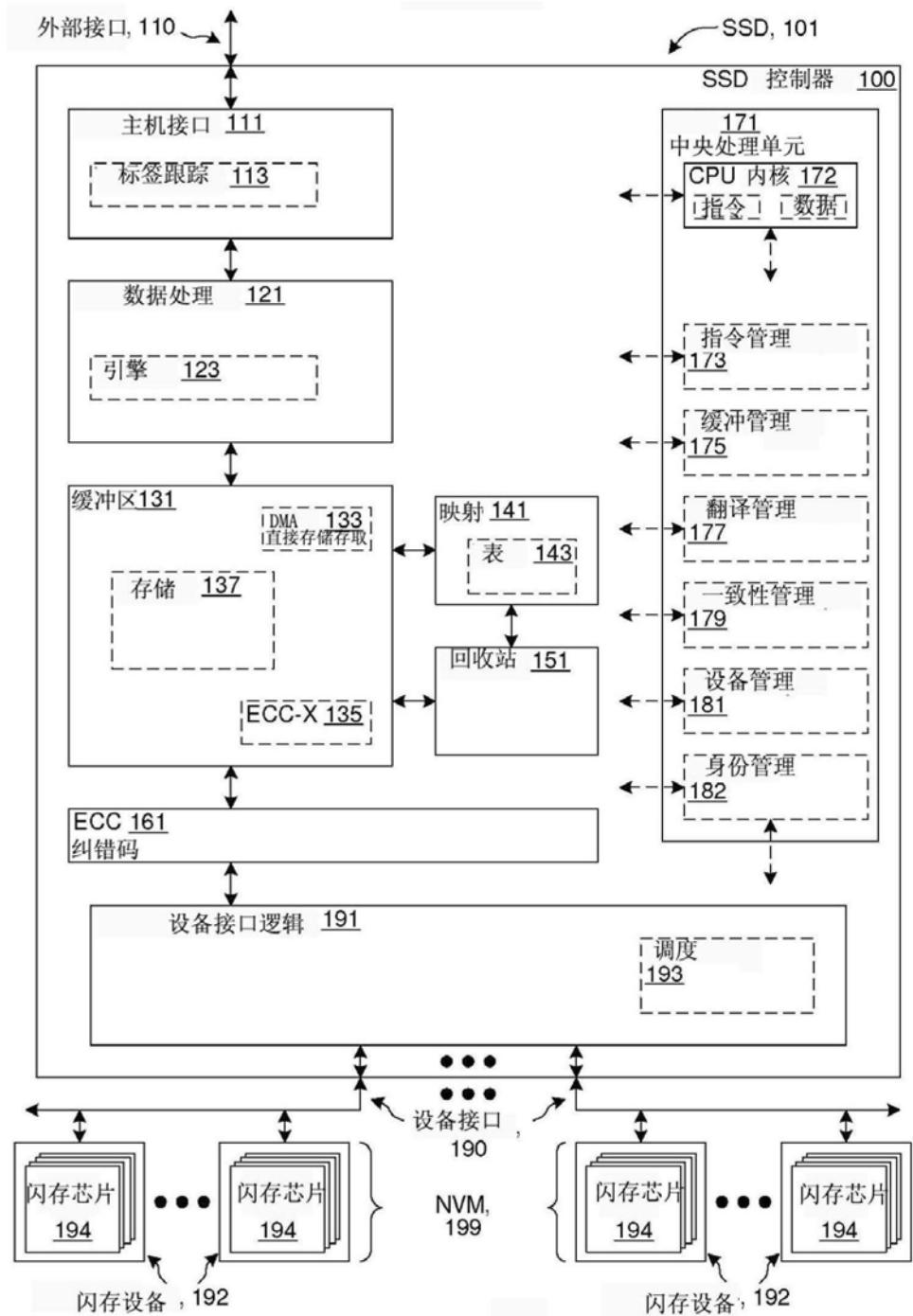

[0016] 图1A示出了固态磁盘(SSD)实施方案经选择的细节包括在非易失性存储器中提供平台以实现0/1平衡管理技术的SSD控制器,如通过非易失性存储器(NVM)元件(例如,闪存)来实现。

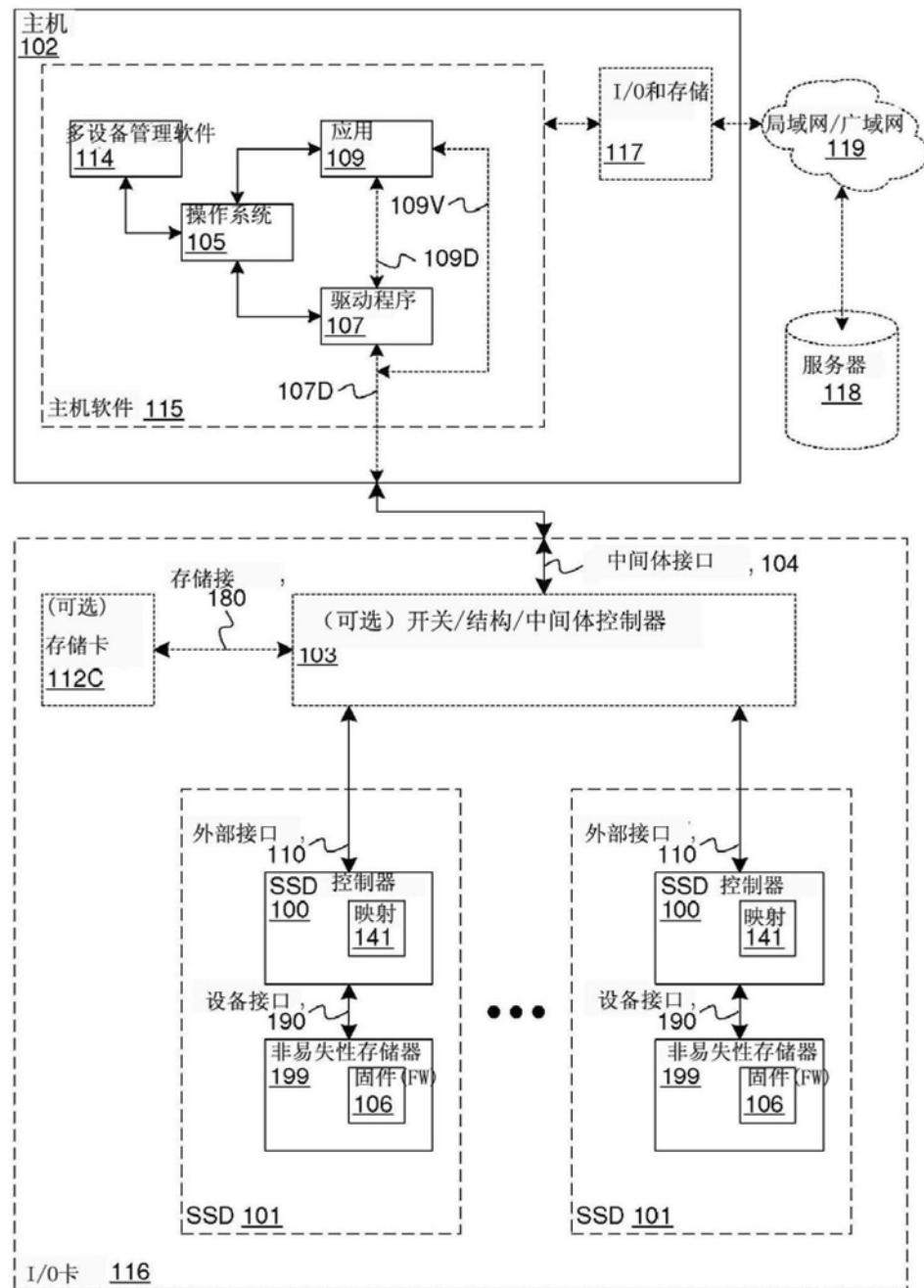

[0017] 图1B示出了各种系统实施方案经选择的细节包括图1A的一个或多个SSD实例。

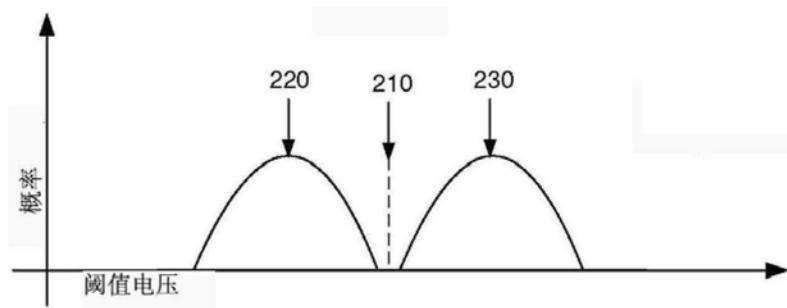

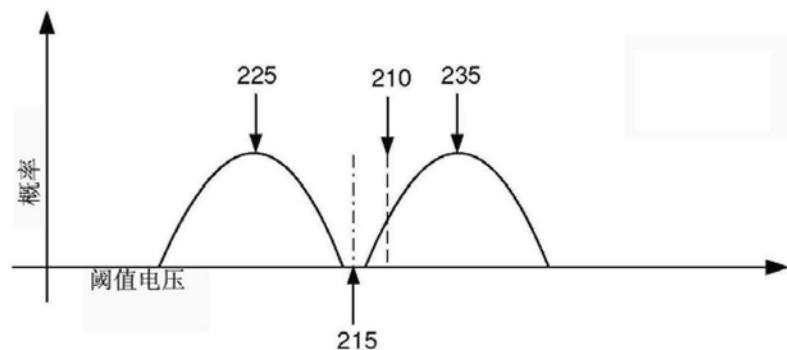

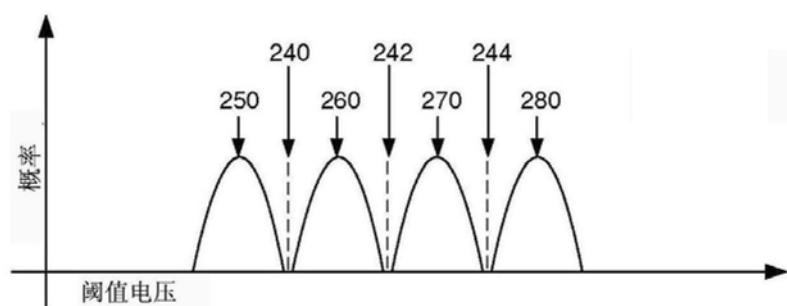

[0018] 图2A到图2D示出了有关0/1平衡恢复的示例阈值电压分布。图2A和2B是SLC特例,分别示出了在第一和稍后第二时间的阈值电压分布。图2C和2D是MLC特例,分别示出了在第一和稍后第二时间的阈值电压分布。

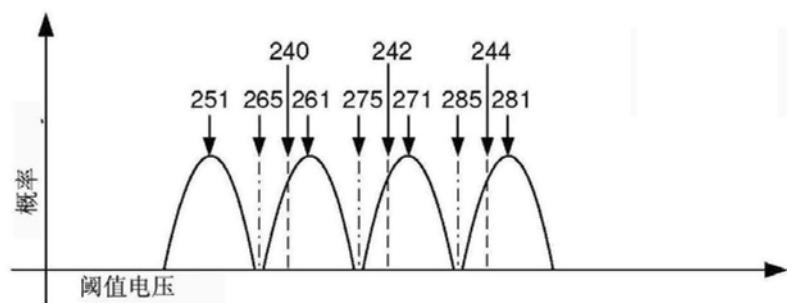

[0019] 图3A示出了图1A的SSD实例的系统实施方案的经选择的细节,提供有关0/1平衡管理的具体细节。

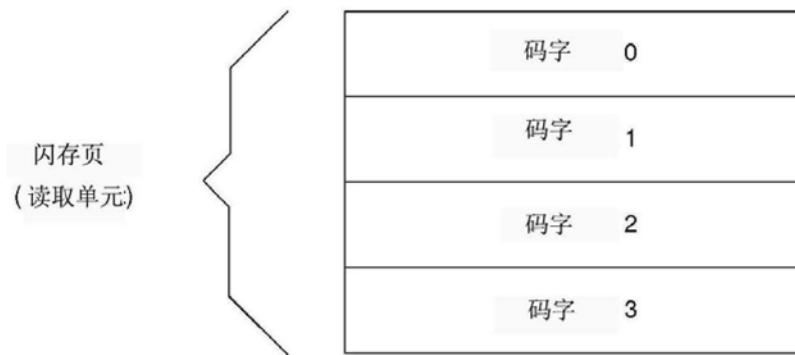

[0020] 图3B示出了用于图3A实施方案的读取单元组织的经选择的细节。

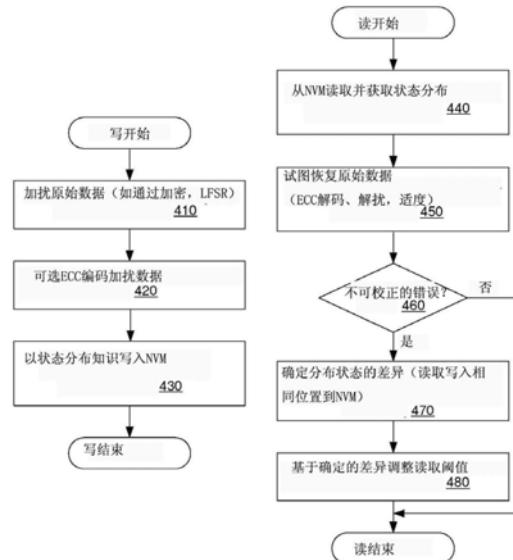

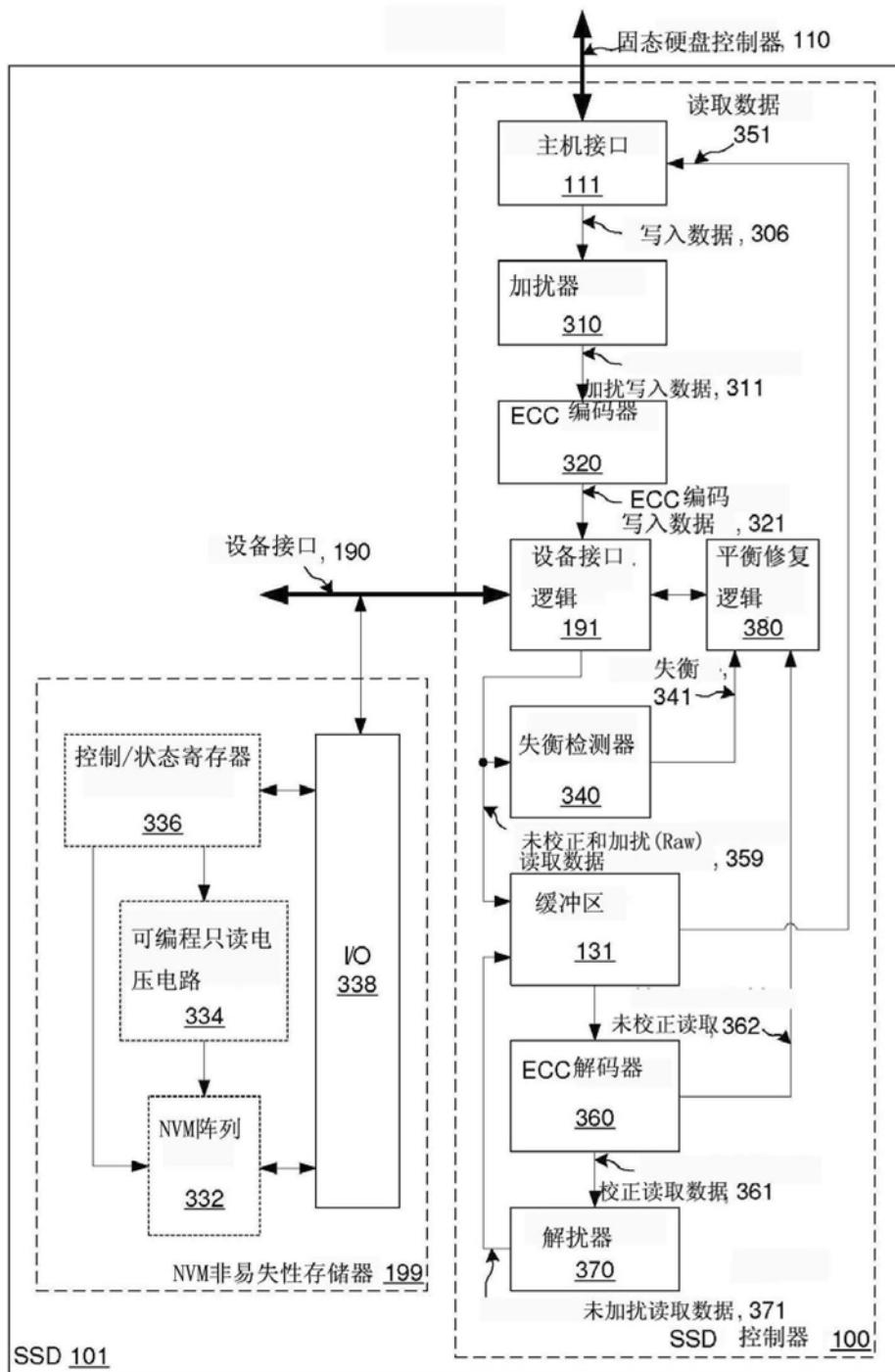

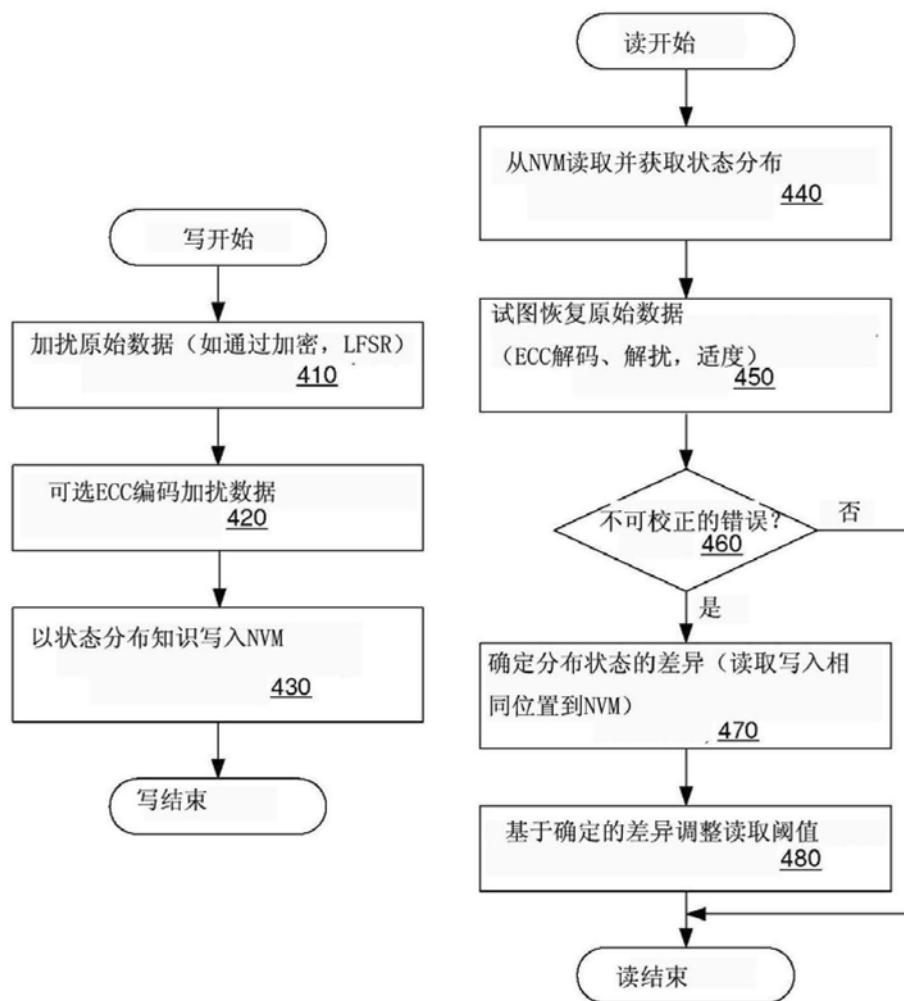

[0021] 图4示出了图1A、图1B和图3中的SSD实施方案经选择的控制流程细节,提供关于写入相关操作(操作410至430)和读取相关操作(操作440至480)特定的细节。

[0022] 附图中元件标号列表

| [0023] | 元件标号 | 元件名称    |

|--------|------|---------|

|        | 100  | 固态硬盘控制器 |

| [0024] | 元件标号 | 元件名称    |

|        |                          |

|--------|--------------------------|

| 101    | 固态硬盘                     |

| 102    | 主机                       |

| 103    | (可选) 开关/结构/中间体控制器        |

| 104    | 中间体接口                    |

| 105    | 操作系统                     |

| 106    | 固件(FW)                   |

| 107    | 驱动                       |

| 107D   | 虚线箭头(主机软件<→I/O设备通信)      |

| 109    | 应用                       |

| 109D   | 虚线箭头(应用<→通过驱动程序的I/O设备通信) |

| 109V   | 虚线箭头(应用<→通过VF的I/O设备通信)   |

| 110    | 外部接口                     |

| 111    | 主机接口                     |

| 112C   | (可选) 存储卡                 |

| 113    | 标签跟踪                     |

| 114    | 多设备管理软件                  |

| 115    | 主机软件                     |

| 116    | I/O卡                     |

| 117    | I/O和存储设备/资源              |

| 118    | 服务器                      |

| 119    | 局域网/广域网                  |

| 121    | 数据处理                     |

| 123    | 引擎                       |

| 131    | 缓冲区                      |

| 133    | DMA                      |

| 135    | ECC-X                    |

| 137    | 存储                       |

| 141    | 映射                       |

| [0025] |                          |

| 元件标号   | 元件名称                     |

| 143    | 表                        |

| 151    | 回收站                      |

| 161    | ECC                      |

| 171    | CPU                      |

| 172    | CPU内核                    |

| 173    | 指令管理                     |

| 175    | 缓冲管理                     |

| 177    | 翻译管理                     |

| 179    | 一致性管理                    |

| 180    | 存储接口                     |

|        |             |              |

|--------|-------------|--------------|

| 181    | 设备管理        |              |

| 182    | 身份管理        |              |

| 190    | 设备接口        |              |

| 191    | 设备接口逻辑      |              |

| 192    | 闪存设备        |              |

| 193    | 调度          |              |

| 194    | 闪存芯片        |              |

| 199    | NVM         |              |

| 210    | SLC标称读取阈值   |              |

| 215    | SLC调整读取阈值   |              |

| 220    | SLC标称最负阈值状态 |              |

| 225    | SLC偏移最负阈值状态 |              |

| 230    | SLC标称最正阈值状态 |              |

| 235    | SLC偏移最正阈值状态 |              |

| 240    | MLC标称第一读取阈值 |              |

| 242    | MLC标称第二读取阈值 |              |

| 244    | MLC标称第三读取阈值 |              |

| 250    | MLC标称最负阈值状态 |              |

| [0026] | 元件标号        | 元件名称         |

|        | 251         | MLC调整最负阈值状态  |

|        | 260         | MLC标称次最负阈值状态 |

|        | 261         | MLC调整次最负阈值状态 |

|        | 265         | MLC调整第一读取阈值  |

|        | 270         | MLC标称次最正阈值状态 |

|        | 271         | MLC调整次最正阈值状态 |

|        | 275         | MLC调整第二读取阈值  |

|        | 280         | MLC标称最正阈值状态  |

|        | 281         | MLC调整最正阈值状态  |

|        | 285         | MLC调整第三读取阈值  |

|        | 306         | 写入数据         |

|        | 310         | 加扰器          |

|        | 311         | 加扰写入数据       |

|        | 320         | ECC编码器       |

|        | 321         | ECC编码写入数据    |

|        | 332         | NVM阵列        |

|        | 334         | 可编程只读电压电路    |

|        | 336         | 控制/状态寄存器     |

|        | 338         | I/O          |

|        | 340         | 失衡检测器        |

|        |                   |

|--------|-------------------|

| 341    | 失衡                |

| 351    | 读取数据              |

| 359    | 未校正和加扰 (Raw) 读取数据 |

| 360    | ECC解码器            |

| 361    | 校正读取数据            |

| 362    | 未校正读取             |

| 370    | 解扰器               |

| 371    | 未加扰读取数据           |

| [0027] |                   |

| 元件标号   | 元件名称              |

| 380    | 平衡修复逻辑            |

| 410    | 加扰数据              |

| 420    | ECC编码             |

| 430    | 写入NVM             |

| 440    | 读取NVM             |

| 450    | 数据恢复              |

| 460    | 不可校正错误评估          |

| 470    | 差异测定              |

| 480    | 读取阈值调整            |

## 具体实施方式

[0028] 在下文中,现在将详细参照本发明的各个实施方式,在附图中示出了这些实施方式的实例并在下文进行了描述。尽管本发明的内容结合示例性实施方式进行描述,但是应该理解的是,本说明书并非旨在将本发明限制为那些示例性实施方式。相反,本发明旨在不但覆盖这些示例性实施方式,而且覆盖可以包括在由所附权利要求所限定的本发明的精神和范围之内的各种替换、修改、等效形式以及其他实施方式。

[0029] 如下提供了本发明的一个或多个实施方案的详细描述连同附图说明本发明的选择的细节。本发明是结合实施方案描述的。本文的实施方案被理解为仅仅是示例性的,本发明明确地不限于或受限于通过本文提及实施方案的部分或全部,并且本发明包括许多替代、修改和等同物。为避免单调的论述,各种单词的标签(包括但不限于:第一、最后、某种、多种、进一步、其他、特定、选择、某些以及显著的)也可以应用于实施方案的单独集合;如本文中所使用的标签明确地不意味着传达品质、或任何形式的偏爱或偏见,而只是为了方便独立集合之间的区分。公开的方法的某些操作顺序在本发明的范围内是可变的。只要多个实施方案用于描述过程、方法、和/或程序指令特征的变化,其他实施方案可以预期的是根据预定的或动态确定的准则进行静态和/或动态地选择多个操作模式分别对应于多个复杂实施方案。在以下的说明中大量具体细节被阐述以提供对本发明透彻的理解。提供用于示例目的的细节并且本发明可以在无一些或全部细节的情况下根据权利要求进行实践。为了清晰表达,已知的与本发明相关的技术领域内的技术材料未被详细描述以使本发明不会不必要地模糊不清。

[0030] 引言

[0031] 此引言仅包含便利于更加快速地对具体实施方式的理解；本发明并不限于在引言中提出的概念（包括明确的实施方案中，如果有的话），因为任何引言的段落必然是整个主题的简略视图并且不意味着是详尽的或限制性的描述。例如，下面的引言提供了由于空间所限的概述信息和仅为某些实施方案的组织。还有许多其他的实施方案，包括那些权利要求将最终被描述的将在平衡整个说明书中进行讨论。

[0032] 缩略语

[0033] 至少一些参考本文中所用的某些元素不同的简短缩写（例如，首字母缩写词）在这里定义。

| <u>缩写</u> | <u>说明</u>                                 |

|-----------|-------------------------------------------|

| AES       | 高级加密标准                                    |

| AHCI      | 高级主机控制器接口                                 |

| API       | 应用程序接口                                    |

| ASCII     | 美国信息交换标准码                                 |

| ATA       | 高级技术附件（AT 附件）                             |

| BCH       | 博斯－乔赫里－霍克文黑姆码（Bose Chaudhuri Hocquenghem） |

| CD        | 光盘                                        |

| CF        | 闪存                                        |

| CMOS      | 互补金属氧化物半导体                                |

| CPU       | 中央处理单元                                    |

| CRC       | 循环冗余校验                                    |

| DAS       | 直接连接存储                                    |

| DDR       | 双倍数据速率                                    |

[0035]

| <u>缩写</u> | <u>说明</u> |

|-----------|-----------|

| DES       | 数据加密标准    |

| DMA       | 直接存储存取    |

| DNA       | 直接NAND存取  |

| DRAM      | 动态随机存取存储器 |

| DVD       | 数字多功能/视频盘 |

| DVR       | 数字视频录像机   |

| ECC       | 纠错码       |

|       |                |

|-------|----------------|

| eMMC  | 嵌入式多媒体卡        |

| eSATA | 外部串行高级技术附件     |

| GPS   | 全球定位系统         |

| HDD   | 硬盘驱动器          |

| I/O   | 输入/输出          |

| IC    | 集成电路           |

| IDE   | 电子集成驱动器        |

| JPEG  | 联合图像专家组        |

| LAN   | 局域网            |

| LB    | 逻辑块            |

| LBA   | 逻辑块地址          |

| LDPC  | 低密度奇偶校验        |

| LFSR  | 线性反馈移位寄存器      |

| LPN   | 逻辑页码           |

| LSB   | 最低有效位          |

| LZ    | Lempel-Ziv压缩算法 |

| MLC   | 多层单元           |

| MMC   | 多媒体卡           |

| MPEG  | 运动图像专家组        |

| MSB   | 最高有效位          |

| NAS   | 网络附加存储         |

[0036]

| 缩写    | 说明                    |

|-------|-----------------------|

| NCQ   | 本机命令队列                |

| NVM   | 非易失性存储器               |

| ONA   | 优化的NAND存取             |

| ONFI  | 开放式NAND闪存接口           |

| OS    | 操作系统                  |

| PC    | 个人电脑                  |

| PCIe  | 外围组件互连特快(PCI特快)       |

| PDA   | 个人数字助理                |

| PHY   | 物理接口                  |

| POS   | 销售点                   |

| RAID  | 廉价/独立磁盘冗余阵列           |

| RASIE | 硅元素独立冗余阵列             |

| ReRAM | 电阻式随机存取存储器            |

| RS    | 里德-索罗门                |

| RSA   | 维斯特、沙米尔和艾德曼           |

| SAN   | 附网存储                  |

| SAS   | 串行连接小型计算机系统接口(串行SCSI) |

|        |                 |

|--------|-----------------|

| SATA   | 串行高级技术附件(串行ATA) |

| SCSI   | 小型计算机系统接口       |

| SD     | 安全数字            |

| SDR    | 单倍数据速率          |

| SLC    | 单层单元            |

| SMART  | 自我监测分析和报告技术     |

| SSD    | 固态硬盘/驱动器        |

| TCG    | 可信计算组           |

| UFS    | 统一闪存存储          |

| USB    | 通用串行总线          |

| VF     | 虚拟功能            |

| [0037] | 缩写              |

|        | 说明              |

| [0038] | WAN             |

|        | 广域网             |

[0038] 跟踪和恢复0/1平衡

[0039] 下面的初始讨论中,跟踪和管理0和1计数以及用来区分0和1的状态读取阈值的偏移,可以直接适用于SLC存储器和(轻微变化,已注明)MLC存储器的下页。更一般地对于MLC存储器来说,延伸跟踪和管理上页的计数和多个读取阈值的偏移(如读取基准电压 $V_{READ1}$ 、 $V_{READ2}$ 和 $V_{READ3}$ )在下面单独段落详述。

[0040] 在一些实施方案中,0的计数和1的计数为每个读取单元(或从NVM芯片读取单元每组的一次偏移)从SLC的NVM读取获得。在事件中读取单元是不可校正的部分原因是阈值电压分布偏离(初始)标称分布的偏移,0计数和/或1计数能确定方向和/或幅值以移动读取阈值(读取基准电压 $V_{READ1}$ )用以跟踪偏移阈值电压分布和恢复0/1平衡。对于SLC存储器读取阈值被调整为读取基准电压 $V_{READ1}$ 并且对于MLC存储器的下页为读取基准电压 $V_{READ2}$ 。举例来说,在SLC中将逻辑1分配给擦除状态,并写入使用已知统计相等的0和1分布(50-50%,又名50/50%,或仅50/50),如果0/1计数电流说明1占优势, $V_{READ1}$ 偏移至低;如果0/1计数电流说明0占优势, $V_{READ1}$ 偏移至高。(在上述例子中替换 $V_{READ2}$ 为 $V_{READ1}$ ,对于MLC存储器的下页。)改变(偏移)读取阈值的幅度的多少是任选由0(或1)数量的百分比来确定的。幅值是基于以下一个或多个:一个或多个样品中观察到的0和/或1的数量;一个或多个样品的读取阈值电压增量;对应于两个分布的顶点之间的中点预测阈值电压分布的知识;编程/擦除计数(磨损);读取干扰计数;保留时间;和其它类似的因素。

[0041] 发现读取平衡点

[0042] 在进一步的实施方案中,二进制搜索近似的操作(以适当的读取基准电压相应的值重复采样相同的读取单元)是用来寻找读取阈值“读取平衡点”。这是在所读取的原始数据(预纠错)统计状态分布的相邻阈值电压分布之间的阈值电压轴的点,匹配写入统计分布状态内的误差统计差额,或者相同的理想化模型。

[0043] 对于SLC存储器和随机加扰,如从加密得到,读取平衡点是读取阈值(读取基准电压 $V_{READ1}$ )其中0/1平衡(从NVM读取的原始数据)是最均匀(几乎相同)。在这种情况下,两个状态分布呈现50-50平衡。也就是说,读取状态的50%是0并且读取状态的50%是1。(在上述例子中替换 $V_{READ2}$ 为 $V_{READ1}$ ,对于MLC存储器的下页。)

[0044] 在一些实施方案中,读取平衡点对应一个或多个:两个电压分布之间的中心点,两个电压分布之间的极小值,在读取的数据的0/1平衡的点最接近50-50,并且根据在其它两个点发现0/1平衡的插值来确定的点。读取平衡点对应于在具有对称相邻阈值电压分布的实施方案中的相邻阈值电压分布之间的中心点。

[0045] 对于所需的读取平衡点寻找和设置读取阈值减少了读取数量需要找到尝试硬判决解码的最佳点。在又一实施方案中,硬判决解码尝试在每个读取阈值采样点(对于SLC存储器的V<sub>READ1</sub>的每个值,或者对于MLC存储器下页的V<sub>READ2</sub>的每个值)在二进制搜索中读取阈值读取平衡点被发现之前“足够好”读取阈值被发现的事件中。当发现了足够好的读取阈值搜索一般被终止,除了如下面所讨论的为达到软判决解码目的围绕所确定的读取平衡点可能采取的附加采样。在各种实施方案中,“足够好”的读取阈值是读取数据成功硬判决解码的结果。在一些实施方案中,在二进制搜索中搜索步骤(读取阈值电压的增量)的幅值是被确定(基于的),关于读取阈值电压变化的幅值至少部分地基于上述所详述的各种因素。

#### [0046] MLC的注意事项

[0047] 在MLC存储器中,多个读取阈值被管理。在一些实施方案中,这是通过假设多个设备阈值电压分布的均匀位移和为基于下页的读取数据0/1平衡的第一读取阈值(V<sub>READ1</sub>)作出决定的基础上改变所有其他读取阈值来执行的。

[0048] 对于4LC的NVM,理论上有25-25-25-25(相对于50-50的0/1平衡)的11/10/00/01平衡。然而,不存在单一的操作来直接提供这种平衡,因为4LCs通常使用三个读取基准电压通过两个单独读取操作来读取:V<sub>READ2</sub>对应下页而V<sub>READ1</sub>和V<sub>READ3</sub>对应上页。因此可以评估两个各自的0/1平衡:D1和D2状态之间对应下页,而E和D1的状态之间结合D2和D3状态之间对应上页。另外,可以进行三个单独的下页近似读取设置单个下页读取阈值以接近V<sub>READ1</sub>、V<sub>READ2</sub>和V<sub>READ3</sub>的每个值。

[0049] 通过示例的方式,在一些4LC的NVM实施方案中,读取基准电压V<sub>READ1</sub>、V<sub>READ2</sub>和V<sub>READ3</sub>可能需要偏移,至少对于存储单元中的两位中的一位。与SLC情况下的工作类似,存储在单元中的两位中的一位需要在第一读取阈值(V<sub>READ2</sub>,在这种MLC情况下)单独读取。确定其他位需要两个额外的读取阈值(V<sub>READ1</sub>和V<sub>READ3</sub>,以及有效地由NVM内部执行的两个相关各自附加读取)。

[0050] 根据不同的实施方案,二者之一:其他位的两个读取阈值(V<sub>READ1</sub>和V<sub>READ3</sub>)是根据相同和/或不同量(根据两状态漂移类似的推定)被统一移动;或者其他位的两个读取阈值被独立移动(额外读取操作成本)。后面的选择需要知道在单元中SLC类似位的状态(LSB),因为SLC类似位的状态确定两个读取阈值(V<sub>READ1</sub>和V<sub>READ3</sub>)之一被用于确定相应的其他位(MSB)。

[0051] 在一些4LC实施方案中,结合“上页”读取数据0/1平衡是针对同时融合了E和D1分布及D2和D3分布进行评估的。基于结合0/1平衡在读取与写入的差距,并考虑到位感的反转(E移动到D1那么1到0,D2移动到D3那么0到1),对应的两个读取阈值(V<sub>READ1</sub>和V<sub>READ3</sub>)一致地在相反方向上移动。这样使得混合组件的0/1平衡“在相同的方向”移动(例如,移动不冲突)。

[0052] 在一些4LC实施方案中,两个上页读取阈值(V<sub>READ1</sub>和V<sub>READ3</sub>)的移动分别通过对上页0/1平衡各自的评价来确定而为读取单元的每位使用相应的LSB。当LSB=1时,移动方向与

LSB=0的情况是相反的。例如,不是计算在上页读取数据中0的计数和1的计数之间的差异,而是上页的差异在对应下页读取数据位的基础上通过选择性地修改上页读取数据的每位进行计算的,变换上页读取数据的位感从数量值到定向值,例如,0表示较高阈值电压而1表示较低阈值电压。在一些实施方案中,上页读取数据位的同或(XNOR)与对应的下页读取数据位进行转换。

[0053] 从软判决样品中排除偏差

[0054] 在一些实施方案中,从NVM获得的软判决信息用以执行基于解码的软判决。通过在多种读取阈值采样点读取的读取单元(或从NVM芯片读取单元每组的一次偏移)中获得的软判决信息(SLC,V<sub>READ1</sub>的值)靠近标称(未调整)读取阈值以获得读取单元数据的多个样本,从而建立了读取单元每位的值的软判决的可能性。样品的间距取决于至少部分地基于所使用的NVM的特别性质,如标称电荷分离状态。

[0055] 然而,软判决信息是偏置,除非样品被采取的那些标称读取阈值是读取阈值的读取平衡点(如上所述)。如果当前读取阈值不是阈值读取平衡点,那么所有的软判决信息被偏置在一个方向或另一个方向。有两种方法来调整从而获得不偏置的(或至少是不太偏)软判决信息:

[0056] 1.由于在每个读取阈值的采样点采样的读取单元的0/1平衡容易被识别,读取阈值的读取平衡点容易被确定(根据实施方案,例如通过使用线性插值)。对应于确定的读取阈值的读取平衡点和(旧的,未调整的)标称读取阈值之间的差,偏移被计算出来。先前确定的软判决信息被启用以得到适当的“重定中心”并且仍然通过先前采样的软判决信息的相关电压偏移被使用(值大于1.0或小于0.0的被截断)。这种方法不需要额外的读取,但是会产生精确/准确度不同量的一些数据。

[0057] 2.由于在每个读取阈值的采样点采样的读取单元的0/1平衡容易被识别,收集所有必需的样本之后,读取阈值采样点最接近读取阈值的读取平衡点容易被确定。最接近的是0/1平衡最接近写入0/1平衡的读取阈值采样点。对SLC加密(或加扰)的情况下,读取阈值采样点最接近具有50-50平衡。由于所有样品的名义上彼此具有同样间距,最接近的样品被选作新的标称读取阈值,并且附加的软判决信息样品可选性聚集(假设新的标称读取阈值不同于旧的)。另外,首先完成二进制搜索找到阈值读取平衡点,按照软判决信息所需精度要求,用精密的二进制搜索限制采样的最佳粒度。软判决信息所需的精度具有围绕新的标称读取阈值的相关联采样窗口。多重读取的部分内容进行二进制搜索需要获得软判决信息而不需要额外的读取,除非旧的标称读取阈值降到所需精度样本窗口之外。

[0058] 在到目前为止所描述的SLC加密实施方案中,上述技术都集中在发现产生最接近于50-50的读取数据0/1平衡的首选读取阈值。在阈值电压分布是大致相同的对称形状并且没有实质性的重叠的情况下,这个首选读取阈值电压也将对应于组合阈值电压分布的最小值。

[0059] 来自己知点阈值电压分布的读取阈值插值

[0060] 在一些实施方案中,找出首选读取阈值的另一种方法是代替地找到两个点,每个相邻阈值电压分布上取一个,并且通过插值确定这两个点之间的中点。例如,在每个阈值电压分布的峰值采样应该产生读取数据0/1的75:25平衡(或1/0,这取决于哪个峰值)。一旦这两个峰值被确定,在两对的阈值电压轴之间所计算的中间点用来设置新的读取阈值。

[0061] 如果已知早先的阈值电压分布是不均匀的(例如,向一侧或另一侧非对称地偏置,如具有长尾巴),则在一些实施方案中的信息被用来解读峰值的位置并通过略为复杂的插值(例如,不只是中点)来定位中心。如保留时间和/或磨损等因素会影响阈值电压分布的对称性并且在一些实施方案中会被认定。多个采样点也用在一些实施方案中用以展示阈值电压分布的形状。

[0062] 在一些实施方案中阈值电压调整的范围是有限的,可能无法找到真正的峰值。尤其是低于0V阈值电压不能被移动,一些闪存设备通过E状态的电压分布延伸至负阈值电压。阈值电压分布的知识仍允许通过插值确定中点。例如,如果在0V读取数据0/1平衡是60/40,则大约10%过量的0都被观察到并且到0V的右侧的E分布的面积大约为10%。在一些实施方案的第一种方法中,D1分布的峰值被找到,并且中点是基于E分布的近似形状的知识被插入的。在一些实施方案的第二种方法中,在读取数据0/1平衡是40/60的D1分布的点(从0V测量的相对点)被发现。60/40和40/60观测之间所计算的中点而后用于设置新的首选读取阈值。所计算的中间点可以与两个阈值电压分布的额外知识和/或更高精度的测量来确定。

[0063] 在一些实施方案中被插入的点都是在读取平衡点的同一侧。例如,已知第一读取阈值采样点X产生75/25读取数据的0/1平衡并且第二读取阈值采样点Y则产生62.5/37.5,读取平衡点接近为 $Y+/- (X-Y)$ 其中“+”与“-”取决于Y是否小于X。读取平衡点的方向是对应于移动接近50/50的读取数据0/1平衡的方向。在给出的例子中,即由X和向Y的方向。阈值电压分布的知识将产生更精确的插值,而不是所示的简单的线性插值。

#### 具体实施方式

[0064] 在总结引言的详细描述中,接下来是示例性实施方案的集合,至少包括一些明确列举为“ECs”(Example Combinations,示例组合),根据本文所描述的概念提供了各种实施方案类型的额外描述;这些实施方案并不意味着是相互排斥的、详尽的或是限制性的;并且本发明并不限于这些示例性实施方案而是涵盖了授权权利要求及其等同的范围内的所有可能的修改和变化。

[0065] EC1) 一种方法,包括:

[0066] 对于NVM的至少一个或多个读取确定0的数量和1的数量之间的差异;和

[0067] 对应于NVM中不可校正的读取,通过至少部分地基于所确定的差异而有选择地偏移阈值电压从而减少随后的差异。

[0068] EC2) EC1的方法,还包括:

[0069] 其中NVM是具有多个状态的MLC存储器,依据规定的格雷码映射每个状态具有相关联的MSB和LSB的值,NVM的一个或多个读取是MSB读取;和

[0070] 其中确定差异包括对应于一个或多个MSB读取使用LSB读取以便选择性反转MSB读取的数据。

[0071] EC3) EC1的方法,其中至少一个或多个读取的每个都是NVM中相应页中至少一部分的独立读取。

[0072] EC4) EC1的方法,其中确定差异包括确定0的数量和1的数量之间的差。

[0073] EC5) EC1的方法,其中0的数量和1的数量分别经相应的计数来确定的。

[0074] EC6) EC4的方法,其中如果差值的绝对值低于预定量则不进行偏移。

[0075] EC7) EC1的方法,其中如果差值的绝对值低于预定量则通过预定电压进行偏移。

[0076] EC8) EC1的方法,其中阈值电压的偏移方向至少部分基于逻辑状态到NVM充电状态的映射。

[0077] EC9) EC1的方法,其中NVM是具有逻辑1到擦除状态映射的SLC存储器,并且阈值电压向下偏移至少部分地基于0的数量少于1的数量这一确定情况。

[0078] EC10) EC9的方法,其中阈值电压进一步向下偏移至少部分基于差异超过预定量这一确定情况。

[0079] EC11) EC1的方法,其中NVM是具有逻辑1到擦除状态映射的SLC存储器,并且阈值电压向下偏移基于差异表示1占优势这一确定情况。

[0080] EC12) EC1的方法,其中NVM是具有逻辑1到擦除状态映射的SLC存储器,并且阈值电压向上偏移至少部分地基于0的数量多于1的数量这一确定情况。

[0081] EC13) EC12的方法,其中差异是超过预定量的。

[0082] EC14) EC1的方法,其中NVM是具有逻辑1到擦除状态映射的SLC存储器,并且阈值电压向上偏移基于差异表示0占优势这一确定情况。

[0083] EC15) EC4的方法,其中在差异中所使用的0的数量和1的数量是基于多个读取的。

[0084] EC16) EC1的方法,其中确定在多个阈值电压中的每个执行,并且偏移至少部分地基于确定的差异。

[0085] EC17) 一种设备,包括:

[0086] 对于NVM的至少一个或多个读取用于确定0的数量和1的数量之间的差异的装置;和

[0087] 用于响应于从NVM中不可校正的读取,至少部分地基于确定的差异通过有选择地偏移阈值电压从而减少后续差异的装置。

[0088] EC18) EC17的设备,还包括:

[0089] 其中NVM是具有多个状态的MLC存储器,依据规定的格雷码映射每个状态具有相关联的MSB和LSB的值,NVM的一个或多个读取是MSB读取;和

[0090] 其中用于确定差异的装置包括对应于一个或多个MSB读取使用LSB读取的装置以便选择性反转MSB读取的数据。

[0091] EC19) EC17的设备,其中至少一个或多个读取的每个都是NVM中相应页中至少一部分的独立读取。

[0092] EC20) EC17的设备,其中确定差异包括确定0的数量和1的数量之间的差。

[0093] EC21) EC17的设备,其中0的数量和1的数量分别经相应的计数来确定的。

[0094] EC22) EC20的设备,其中如果差值的绝对值低于预定量则不进行偏移。

[0095] EC23) EC20的设备,其中在差异中所使用的0的数量和1的数量是基于多个读取的。

[0096] EC24) EC17的方法,其中确定是在多个阈值电压中的每个执行的,并且偏移至少部分地基于确定的差异。

[0097] EC25) 一种方法,包括:

[0098] 确定差异,每个差异都具有各自的幅值和被存储在NVM的各自己知分布与从NVM读出的相应值的差异;和

[0099] 周期性地响应于来自NVM的不可校正的读取,在偏移之前至少部分地基于至少一个确定的差异有选择地偏移至少一个读取阈值电压。

[0100] EC26) EC25的方法,其中至少一个读取阈值电压的每个周期性偏移值是根据偏移之后的保持低于预定量的至少一个确定差异的各自幅值为目标来确定。

[0101] EC27) EC26的方法,其中,至少直到下一个不可校正的读取,偏移之后的至少一个确定差异的各自幅值通过单个更新的至少一个读取阈值被减少到预定量之下。

[0102] EC28) EC25的方法,其中NVM是SLC。

[0103] EC29) EC25的方法,其中NVM是MLC。

[0104] EC30) EC29的方法,其中MLC是4LC的MLC,且差异以E状态和许多D状态的至少两个状态被评估。

[0105] EC31) EC29的方法,其中MLC是4LC的MLC,且已知分布在四个状态25-25-25-25%之中。

[0106] EC32) EC25的方法,其中NVM是具有多个状态的MLC,依据规定的格雷码映射每个状态都具有相关的MSB和LSB的值,至少一个阈值电压偏移鉴于正执行的关于下页读取的确定差异,并且对应于0的差异的优势电压偏移在第一方向而对应于1的差异的优势电压偏移在第二方向。

[0107] EC33) EC25的方法,其中NVM是具有多个状态的MLC,依据规定的格雷码映射每个状态都具有相关的MSB和LSB的值,并且至少一个阈值电压偏移鉴于正执行的关于上页读取的确定差异。

[0108] EC34) EC33的方法,其中用于确定的差异进行的上页读取是对于读取单元的每位使用特定的LSB执行的,并且用于第一LSB值电压偏移是在第一方向上对应于0的差异的优势而在第二方向上对应于1的差异的优势,而对于第二个LSB值电压偏移的方向感觉是相反的。

[0109] EC35) EC33的方法,其中用于确定的差异进行的上页读取是对于读取单元的每位使用特定的LSB执行的,并且电压偏移的方向是至少部分地基于上页读取的特定LSB值和至少部分地基于差异的性质来确定的。

[0110] EC36) EC25的方法,其中NVM是具有E状态和多个D状态的MLC,并且至少有一个阈值电压是在E状态和多个D状态中选定的一个之间。

[0111] EC37) EC25的方法,其中NVM是具有E状态和多个D状态的MLC,并且至少有一个阈值电压是在多个D状态的选定两个相邻的D状态之间。

[0112] EC38) EC25的方法,还包括:

[0113] 其中NVM是具有多个状态的MLC存储器,依据规定的格雷码映射每个状态具有相关联的MSB和LSB的值,并且对于从NVM读取的值,该读取是MSB读取;和

[0114] 其中确定差异包括对应于一个或多个MSB读取使用LSB读取以便选择性反转MSB读取的数据。

[0115] EC39) 一种设备,包括:

[0116] 确定差异,每个差异都具有各自的幅值和被存储在NVM的各自已知分布与从NVM读出的相应值的差异;和

[0117] 用于周期性地响应于来自NVM的不可校正的读取,在偏移之前至少部分地基于至少一个确定的差异有选择地偏移至少一个读取阈值电压的装置。

[0118] EC40) EC39的方法,其中至少一个读取阈值电压的每个周期性偏移值是根据偏移

之后的保持低于预定量的至少一个确定差异的各自幅值为目标来确定。

[0119] EC41) EC40的设备,其中,至少直到下一个不可校正的读取,偏移之后的至少一个确定差异的各自幅值通过单个更新的至少一个读取阈值被减少到预定量之下。

[0120] EC42) EC39的设备,其中NVM是SLC。

[0121] EC43) EC39的设备,其中NVM是MLC。

[0122] EC44) 一种方法,包括:

[0123] 确定来自NVM的数据读取的一个或多个部分的每个中0的计数和1的计数的差异;

[0124] 其中在多个读取阈值的读取基准电压设置的每个确定被执行并且差值被计算;

[0125] 利用计算出的插值的差值来计算阈值中心点;和

[0126] 至少部分地根据计算出的阈值中心点偏移读取阈值以便更新读取基准电压设定。

[0127] EC45) EC44的方法,其中插值是线性插值。

[0128] EC46) EC44的方法,其中确定差值包括对于之前计算的NVM的至少一个或多个读取确定0的计数和1的计数以便计算0的计数1的计数的差值。

[0129] EC47) 一种设备,包括:

[0130] 用于确定来自NVM的数据读取的一个或多个部分的每个中0的计数和1的计数的差异的装置,其中在多个读取阈值的读取基准电压设置的每个确定被执行并且差值被计算;

[0131] 用于利用计算出的插值的差值来计算阈值中心点的装置;和

[0132] 用于至少部分地根据计算出的阈值中心点偏移读取阈值以便更新读取基准电压设定的装置。

[0133] EC48) EC47的设备,其中插值是线性插值。

[0134] EC49) EC47的设备,确定差值包括对于之前计算的NVM的至少一个或多个读取确定0的计数和1的计数的装置以便计算0的计数1的计数的差值的装置。

[0135] EC50) 一种方法,包括:

[0136] 在多个阈值电压的每个中读取相同读取单元的数据;

[0137] 对于相同读取单元的每个读取确定0的读取计数和1的读取计数;

[0138] 至少部分地基于读取计数计算阈值中心点;和

[0139] 至少部分地基于数据读取和计算出的阈值中心点产生软判决信息。

[0140] EC51) EC50的方法,其中阈值中心点的计算至少部分地使用0的读取计数与1的读取计数的差值计算出的插值来执行。

[0141] EC52) EC51的方法,其中插值是线性插值。

[0142] EC53) EC50的方法,其中多个软判决信息的值是基于读出在相对于计算出的阈值中心点的各自阈值电压偏移数据而生成的。

[0143] EC54) EC53的方法,其中偶数编号的数值产生对应于计算出的阈值中心点上下的各自电压偏移的相等数量。

[0144] EC55) EC53的方法,其中作为用于生成软判决信息的基准计算出的阈值中心点的使用改进了当前通过减少偏差生成的软判决信息的有效性。

[0145] EC56) 一种设备,包括:

[0146] 在多个阈值电压的每个中读取相同读取单元的数据的装置;

- [0147] 对于相同读取单元的每个读取确定0的读取计数和1的读取计数的装置；

- [0148] 至少部分地基于读取计数计算阈值中心点的；和

- [0149] 至少部分地基于数据读取和计算出的阈值中心点产生软判决信息的装置。

- [0150] EC57) EC56的设备，其中阈值中心点的计算至少部分地使用0的读取计数与1的读取计数的差值计算出的插值来执行。

- [0151] EC58) EC57的设备，其中插值是线性插值。

- [0152] EC59) EC56的设备，其中多个软判决信息的值是基于读出在相对于计算出的阈值中心点的各自阈值电压偏移数据而生成的。

- [0153] EC60) EC59的设备，其中偶数编号的数值产生对应于计算出的阈值中心点上下的各自电压偏移的相等数量。

- [0154] EC61) EC59的设备，其中作为用于生成软判决信息的基准计算出的阈值中心点的使用改进了当前通过减少偏差生成的软判决信息的有效性。

- [0155] EC62) 一种方法，包括：

- [0156] 在多个阈值电压的每个中读取相同读取单元的数据；

- [0157] 对于相同读取单元的每个读取，确定0的计数和1的计数；

- [0158] 至少部分地基于读取计数，确定最接近于多个阈值电压的中心点阈值电压，最靠近中心点的阈值电压对应于概念上的阈值中心点；和

- [0159] 至少部分地基于数据的读取和所识别的最接近中心点阈值电压产生软判决信息。

- [0160] EC63) EC62的方法，其中阈值中心点的计算至少部分地使用0的读取计数与1的读取计数的差值计算出的插值来执行。

- [0161] EC64) EC63的方法，其中插值是线性插值。

- [0162] EC65) EC62的方法，其中多个软判决信息的值是基于读出在相对于计算出的阈值中心点的各自阈值电压偏移数据而生成的。

- [0163] EC66) EC65的方法，其中对应于各自电压偏移确定的时间间隔产生了一些数值。

- [0164] EC67) EC62的方法，其中作为用于生成软判决信息的基准计算出的阈值中心点的使用改进了当前通过减少偏差生成的软判决信息的有效性。

- [0165] EC68) 一种设备，包括：

- [0166] 在多个阈值电压的每个中读取相同读取单元的数据的装置；

- [0167] 对于相同读取单元的每个读取确定0的计数和1的计数的装置；

- [0168] 至少部分地基于读取计数，确定最接近于多个阈值电压的中心点阈值电压，最靠近中心点的阈值电压对应于概念上的阈值中心点的装置；和

- [0169] 至少部分地基于数据的读取和所识别的最接近中心点阈值电压产生软判决信息的装置。

- [0170] EC69) EC68的设备，其中阈值中心点的计算至少部分地使用0的读取计数与1的读取计数的差值计算出的插值来执行。

- [0171] EC70) EC69的设备，其中插值是线性插值。

- [0172] EC71) EC68的设备，其中多个软判决信息的值是基于读出在相对于计算出的阈值中心点的各自阈值电压偏移数据而生成的。

- [0173] EC72) EC71的设备，其中对应于各自电压偏移确定的时间间隔产生了一些数值。

[0174] EC73) EC68的设备,其中作为用于生成软判决信息的基准计算出的阈值中心点的使用改进了当前通过减少偏差生成的软判决信息的有效性。

[0175] EC74) 一种方法,包括:

[0176] 在NVM中存储数据,其中存储的数据具有特定的0-1平衡;

[0177] 维持0的计数和1的计数,其中0的计数和1的计数是读取计数;

[0178] 评估NVM的0-1平衡作为0的计数、1的计数和特定0-1平衡的函数;

[0179] 从来自NVM不可校正的读取和确定0-1平衡是在规定范围之外后,至少部分地基于评估和在尽可能少的阈值电压偏移的情况下根据恢复0-1平衡到规定范围内的目标来偏移阈值电压至确定的值;和

[0180] 其中来自NVM的数据恢复是被优化的。

[0181] EC75) EC74的方法,还包括:

[0182] 其中阈值电压的偏移是向低电压的偏移基于相对于特定0-1平衡包括过量的1的0-1平衡的确定;和

[0183] 其中阈值电压的偏移是向高电压的偏移基于相对于特定0-1平衡包括过量的0的0-1平衡的确定。

[0184] EC76) EC74的方法,其中使用加密方法数据被存储并且特定0-1平衡是50%的0和50%的1。

[0185] EC77) EC74的方法,其中特定0-1平衡对应于低于55%的0和高于45%的1。

[0186] EC78) EC74的方法,其中特定0-1平衡对应于超过52.5%的零的概率小于万分之一。

[0187] EC79) EC74的方法,其中特定0-1平衡对应于低于45%的0和大于55%的1。

[0188] EC80) 一种设备,包括:

[0189] 在NVM中存储数据,其中存储的数据具有特定的0-1平衡的装置;

[0190] 维持0的计数和1的计数,其中0的计数和1的计数是读取计数的装置;

[0191] 评估NVM的0-1平衡作为0的计数、1的计数和特定0-1平衡的函数的装置;

[0192] 从来自NVM不可校正的读取和确定0-1平衡是在规定范围之外后,至少部分地基于评估和在尽可能少的阈值电压偏移的情况下根据恢复0-1平衡到规定范围内的目标来偏移阈值电压至确定的值的装置;和

[0193] 其中来自NVM的数据恢复是被优化的。

[0194] EC81) EC80的设备,还包括:

[0195] 其中阈值电压的偏移是向低电压的偏移基于相对于特定0-1平衡包括过量的1的0-1平衡的确定;和

[0196] 其中阈值电压的偏移是向高电压的偏移基于相对于特定0-1平衡包括过量的0的0-1平衡的确定。

[0197] EC82) EC80的设备,其中使用加密方法数据被存储并且特定0-1平衡是50%的0和50%的1。

[0198] EC83) EC80的设备,其中特定0-1平衡对应于低于55%的0和高于45%的1。

[0199] EC84) EC80的设备,其中特定0-1平衡对应于超过52.5%的零的概率小于万分之一。

- [0200] EC85) EC80的设备,其中特定0-1平衡对应于低于45%的0和大于55%的1。

- [0201] EC86) 一种方法,包括:

- [0202] 加扰被写入到非易失性存储器的部分中的数据,以产生具有0位的已知统计平均数和1位的已知统计平均数的加扰数据;

- [0203] 写入加扰数据到非易失性存储器的部分;

- [0204] 写入之后,读取非易失性存储器的部分;

- [0205] 计算从非易失性存储器的部分读取的数据中0位数和1位数之间的差异;和

- [0206] 至少部分地基于差异非易失性存储器的后续读取确定阈值电压。

- [0207] EC87) EC86的方法,其中确定进一步基于0位的已知统计平均数或1位的已知统计平均数。

- [0208] EC88) EC86的方法,还包括:

- [0209] 使用阈值电压重新读出非易失性存储器的部分。

- [0210] EC89) EC88的方法,其中写入包括使用ECC编码器编码加扰数据和写入编码的加扰数据到非易失性存储器的部分,并且还包括:

- [0211] 重新读取之前,使用ECC解码器解码从非易失性存储器的部分中读取的数据以确定从非易失性存储器的部分读取的数据是不可校正的。

- [0212] EC90) EC89的方法,其中差异是第一差异,阈值电压是第一阈值电压,并且还包括:

- [0213] 使用第一阈值电压以ECC解码器解码从非易失性存储器的部分重新读取的数据,以确定使用第一阈值电压从非易失性存储器的部分重新读取的数据是不可校正的;

- [0214] 计算使用第一阈值电压从非易失性存储器的部分重新读取的数据中0位数和1位数之间的第二差异;和

- [0215] 至少部分地基于第一差异和第二差异为非易失性存储器的第二重新读取确定第二阈值电压。

- [0216] EC91) EC90的方法,还包括:

- [0217] 使用第二阈值电压重新读取非易失性存储器的部分。

- [0218] EC92) EC89的方法,其中ECC编码器添加一个或多个字节到加扰数据,并且其中由ECC编码器添加的一个或多个字节具有0位的已知统计平均数和1位的已知统计平均数。

- [0219] EC93) 一种设备,包括:

- [0220] 加扰被写入到非易失性存储器的部分中的数据,以产生具有0位的已知统计平均数和1位的已知统计平均数的加扰数据的装置;

- [0221] 写入加扰数据到非易失性存储器的部分的装置;

- [0222] 写入之后,读取非易失性存储器的部分的装置;

- [0223] 计算从非易失性存储器的部分读取的数据中0位数和1位数之间的差异的装置;和

- [0224] 至少部分地基于差异为非易失性存储器的后续读取确定阈值电压的装置。

- [0225] EC94) EC93的设备,其中确定进一步基于0位的已知统计平均数或1位的已知统计平均数。

- [0226] EC95) EC93的设备,还包括:

- [0227] 使用阈值电压重新读出非易失性存储器的部分的装置。

- [0228] EC96) EC95的设备,其中写入包括使用ECC编码器编码加扰数据和写入编码的加扰

数据到非易失性存储器的部分,并且还包括:

[0229] 重新读取之前,使用ECC解码器解码从非易失性存储器的部分中读取的数据以确定从非易失性存储器的部分读取的数据是不可校正的装置。

[0230] EC97) EC96的设备,其中差异是第一差异,阈值电压是第一阈值电压,并且还包括:

[0231] 用于使用第一阈值电压以ECC解码器解码从非易失性存储器的部分重新读取的数据以确定该数据使用第一阈值电压从非易失性存储器的部分重新读取的数据是不可校正的装置;

[0232] 用于计算使用第一阈值电压从非易失性存储器的部分重新读取的数据中0位数和1位数之间的第二差异的装置;和

[0233] 用于至少部分地基于第一差异和第二差异为非易失性存储器的第二重新读取确定第二阈值电压装置。

[0234] EC98) EC97的设备,还包括:

[0235] 使用第二阈值电压重新读取非易失性存储器的部分的装置。

[0236] EC99) EC96的设备,其中ECC编码器添加一个或多个字节到加扰数据,并且其中由ECC编码器添加的一个或多个字节具有0位的已知统计平均数和1位的已知统计平均数。

[0237] EC100) 一种有形计算机可读介质,其上存储一组指令,当由处理元件执行时引起处理元件执行和/或控制操作包括:

[0238] 加扰被写入到非易失性存储器的部分中的数据,以产生具有0位的已知统计平均数和1位的已知统计平均数的加扰数据;

[0239] 写入加扰数据到非易失性存储器的部分;

[0240] 写入之后,读取非易失性存储器的部分;

[0241] 计算从非易失性存储器的部分读取的数据中0位数和1位数之间的差异;和

[0242] 至少部分地基于差异为非易失性存储器的后续读取确定的阈值电压。

[0243] EC101) EC100的有形计算机可读介质,其中确定进一步基于0位的已知统计平均数或1位的已知统计平均数。

[0244] EC102) EC100的有形计算机可读介质,操作还包括:

[0245] 使用阈值电压重新读出非易失性存储器的部分。

[0246] EC103) EC102的有形计算机可读介质,其中写入包括使用ECC编码器编码加扰数据和写入所编码的加扰数据到非易失性存储器的部分,并且操作还包括:

[0247] 在重新读取之前,使用ECC解码器解码从非易失性存储器的部分中读取的数据以确定从非易失性存储器的部分读取的数据是不可校正的。

[0248] EC104) EC103的有形计算机可读介质,其中差异是第一差异,阈值电压是第一阈值电压,并且操作还包括:

[0249] 使用第一阈值电压以ECC解码器解码从非易失性存储器的部分重新读取的数据以确定使用第一阈值电压从非易失性存储器的部分重新读取的数据是不可校正的;

[0250] 计算使用第一阈值电压从非易失性存储器的部分重新读取的数据中0位数和1位数之间的第二差异;和

[0251] 至少部分地基于第一差异和第二差异为非易失性存储器的第二重新读取确定的第二阈值电压。

[0252] EC105) EC104的有形计算机可读介质,操作还包括:

[0253] 使用第二阈值电压重新读取非易失性存储器的部分。

[0254] EC106) EC103的有形计算机可读介质,其中ECC编码器添加一个或多个字节到扰数据,并且其中由ECC编码器添加的一个或多个字节具有0位的已知统计平均数和1位的已知统计平均数。

[0255] 系统

[0256] 图1A示出了SSD101实施方案经选择的细节,包括使用0/1平衡恢复管理非易失性存储器的SSD控制器,如通过NVM元件来实现(例如,闪存)。SSD控制器100经由一个或多个外部接口110与主机(如图1B所示的主机102)通信地耦合。根据各种实施方案,外部接口110为一个或多个:SATA接口;SAS接口;PCIe接口;光纤通道接口;以太网接口(如10千兆位以太网);前述接口中的任一非标准版本;自定义接口;或用于连接存储和/或通信和/或计算设备的任何其它类型的接口。例如,在一些实施方案中,SSD控制器100包括SATA接口和PCIe接口。

[0257] SSD控制器100还经由一个或多个设备接口190通信地耦合到包括一个或多个存储设备的NVM199,如一个或多个闪存设备192。根据各种实施方案,设备接口190为一个或多个:异步接口;同步接口;单数据速率(SDR)接口;双数据速率(DDR)接口;DRAM兼容的DDR或DDR2同步接口;ONFI兼容的接口,如ONFI2.2或ONFI3.0兼容接口;切换模式兼容闪存接口;前述接口中的任一非标准版本;自定义接口;或任何用于连接到存储设备的其它类型接口。

[0258] 每个闪存设备192具有,在一些实施方案中,一个或多个单独的闪存芯片194。根据闪存设备192中的特定类别,特定闪存设备192中的多个闪存芯片194被任选和/或有选择地并行访问。闪存设备192仅仅是代表能通信地耦合到SSD控制器100的一种存储设备类型。在各种实施方案中,任何类型的存储设备是可使用的,如SLC NAND闪存、MLC NAND闪存、NOR闪存、使用多晶硅或硅的氮化物技术为基础的电荷存储单元的闪存、二维或三维的技术为基础的闪存、只读存储器、静态随机存取存储器、动态随机存取存储器、磁性存储器、相变存储器、赛道存储器、ReRAM或任何其它类型的存储器设备或存储介质。

[0259] 根据各种实施方案,设备接口190被组织为:一个或多个总线对应每条总线的一个或多个闪存设备192;一组或多组的总线对应每条总线的一个或多个闪存设备192,其中一组总线通常是并行访问的;或一个或多个闪存设备192的任何其他组织到设备接口190。

[0260] 继续在图1A中,SSD控制器100具有一个或多个模块,例如主机接口111、数据处理121、缓冲区131、映射141、回收站151、ECC161、设备接口逻辑191和CPU171。显示在图1A中的专用模块和互连中仅仅代表一个实施方案,一些或所有模块的许多布局和互连,以及没有被示出的额外模块,可被设想。在第一示例中,在一些实施方案中,有两个或更多的主机接口111以提供双端口。在第二示例中,在一些实施方案中,数据处理121和/或ECC161与缓冲区131是结合的。在第三示例中,在一些实施方案中,主机接口111被直接耦合到缓冲区131,并且数据处理121任选和/或选择性地操作存储在缓冲区131中的数据。在第四示例中,在一些实施方案中,设备接口逻辑191被直接耦合到缓冲区131,并且ECC161任选和/或选择性地操作存储在缓冲区131中的数据。

[0261] 经由外部接口110主机接口111发送并接收的指令和/或数据,并且在一些实施方案中,通过标签跟踪113跟踪各个指令的进度。例如,该指令包括读取指令指定的地址(例如

LBA) 和要读取的数据量 (如一些LBA量子, 例如, 扇区); 针对SSD提供读取状态和/或读取数据。对于另一示例, 该指令包括: 写入指令指定的地址 (例如LBA) 和要写入的数据量 (如一些LBA量子, 例如, 扇区); 针对SSD提供了写如状态和/或请求写入的数据和随后可选地提供了写入状态。对于又一示例, 该指令包括重新分配指令 (例如, 修剪指令) 指定的一个或多个地址 (例如一个或多个LBA) 不再需要被分配; 针对SSD相应和任选地修改映射提供重新分配状态。在某些情况下ATA兼容的修剪指令是示例性的重新分配指令。对于又一示例, 该指令包括超级电容器测试指令或数据强化成功查询; 相应地, SSD提供适当的状态。在一些实施方案中, 主机接口111使用SATA协议兼容并且, 使用NCQ指令, 使能具有多达32个等待指令, 每个指令使用从0到31的唯一标签来表示。在一些实施方案中, 标签跟踪113将经由外部接口110接收命令的外部标签与用来由SSD控制器100处理过程中跟踪指令的内部标签相关联。

[0262] 根据各种实施方案, 一个或多个: 数据处理121任选和/或有选择地处理一些或所有缓冲区131和外部接口110之间发送的数据; 并且数据处理121任选和/或有选择地处理存储在缓冲区131中的数据。在一些实施方案中, 数据处理121使用一个或多个引擎123来执行一个或多个: 格式化; 重新格式化; 转码; 和任何其它数据处理和/或操纵任务。

[0263] 缓冲区131存储数据发送/来自到外部接口110从/到设备接口190。在一些实施方案中, 缓冲区131附加地存储系统数据, 如部分或全部映射表, 通过SSD控制器100用于管理一个或多个闪存设备192。在各种实施方案中, 缓冲区131具有一个或多个: 存储器137用于临时存储数据; DMA133用来控制数据去和/或从缓冲器131的移动; 和ECC-X135用来提供更高级别的错误校正和/或冗余的功能; 和其它数据的移动和/或操作功能。更高级别的冗余功能的示例是类似RAID的功能, 其中的冗余是闪存设备 (例如, 多个闪存设备192) 级别和/或闪存芯片 (例如, 闪存芯片194) 级别而不是在磁盘级别。

[0264] 根据各种实施方案中, 一个或多个: ECC161任选和/或有选择地处理一些或所有在缓冲区131和设备接口190之间发送的数据; 和ECC161任选和/或有选择地处理存储在缓冲区131中的数据。在一些实施方案中, ECC161被用来提供低级别的错误校正和/或冗余的功能, 如根据一个或多个ECC技术。在一些实施方案中, ECC161实现了一个或多个: CRC码; 海明码; RS码; BCH码; LDPC码; 维特比编码; 格式码; 硬判决码; 软判决码; 基于擦除的编码; 任何错误检测和/或校正编码; 和任意前述的组合。在一些实施方案中, ECC161包括一个或多个解码器 (如LDPC解码器)。

[0265] 通过设备接口190设备接口逻辑191控制闪存设备192的实例。根据闪存设备192的协议设备接口逻辑191能够发送数据到达/来自闪存设备192的实例。设备接口逻辑191包括通过设备接口190调度193到闪存设备192的实例的选择性序列控制。例如, 在一些实施方案中, 调度193被启用排队操作闪存设备192的实例, 和选择性地发送该操作到闪存设备192的个别实例 (或闪存芯片194) 由于闪存设备192的个别实例 (或闪存芯片194) 是可用的。

[0266] 映射141在用于外部接口110的数据寻址和用于设备接口190的数据寻址之间进行转换, 使用表143来映射外部数据地址到NVM199中的位置。例如, 在一些实施方案中, 映射141用于使用在外部接口110上LBAs到指向一个或多个的闪存芯片194的块和/或页地址的转换, 通过表143提供的映射。对于自驱动器生产或取消分配从未被写入过的LBAs, 如果LBAs被阅读该映射指向返回默认值。例如, 当处理重新分配指令时, 该映射被修改使得相应重新分配的LBAs条目指向默认值中的一个。在各种实施方案中, 有各种各样的默认值, 每一

个都具有相应的指针。多个默认值能够读取一些重新分配的LBAs (例如在第一范围内) 为一个默认值, 而读取其他的重新分配的LBAs (例如在第二范围内) 为另一个默认值。默认值, 在各种实施方案中, 由闪存、硬件、固件、指令和/或原始的实参和/或参数、可编程寄存器或它们的各种组合来定义。

[0267] 在一些实施方案中, 映射141使用表143来执行和/或查找在外部接口110使用的地址和设备接口190使用的数据地址之间的翻译。根据各种实施方案, 表143是一个或多个: 单级别的映射; 两个级别的摄影; 多级别的映射; 映射缓存; 压缩映射; 从一个地址空间到另一个的任意类型映射; 和上述的任何组合。根据各种实施方案, 表143包括一个或多个: 静态随机存取存储器; 动态随机存取存储器; NVM (例如闪存); 高速缓存; 单片存储器; 片外存储器; 和上述的任何组合。

[0268] 在一些实施方案中, 回收站151执行无用单元收集。例如, 在一些实施方案中, 包含闪存设备192的实例的块在被重新写入之前必须被擦除。回收站151被启动以确定闪存设备192的实例哪些部分积极地使用中 (例如, 分配而不是重新分配), 如通过扫描由映射141维持的映射, 并且通过擦除它们使闪存设备192的实例未使用的 (例如, 重新分配) 部分能够被写入。在进一步的实施方案中, 回收站151能移动闪存设备192的实例中所存储的数据使得闪存设备192的实例的最大连续部分可用于写入。

[0269] 在一些实施方案中, 闪存设备192的实例有选择地和/或动态配置、管理和/或使用具有一个或多个频带用于存储不同类型和/或性能的数据。数字、布局、大小和频带的类型都是动态变化的。例如, 来自计算主机的数据被写入到一个热的 (活跃) 频带, 而来自回收站151的数据被写入到冷的 (不活跃) 频带。在一些使用场景中, 如果计算主机写入长期的、连续的数据流, 则热频带的大小增加, 而如果计算主机随机写入或很少写入, 则冷频带的大小增加。

[0270] CPU171控制SSD控制器100的各个部分。CPU171包括CPU内核172。CPU内核172是, 根据各种实施方案, 一个或多个单核或多核处理器。在CPU内核172中各处理器核心是, 在一些实施方案中, 多线程。CPU内核172包括指令和/或数据高速缓存和/或存储器。例如, 指令存储器中包含的指令能使CPU内核172执行程序 (例如, 软件有时被称为固件) 来控制SSD控制器100。在一些实施方案中, 一些由CPU内核172执行的部分或全部固件被存储在闪存设备192的实例中 (如图所示, 例如, 图1B中的NVM199的固件106)。

[0271] 在各种实施方案中, CPU171还包括: 指令管理173当指令正在执行时跟踪并控制经由外部接口110接收的指令; 缓冲管理175控制缓冲区131的分配和使用; 翻译管理177控制映射141; 一致性管理179来控制数据寻址的一致性以避免如外部数据访问和回收数据访问之间的冲突; 设备管理181控制设备接口逻辑191; 身份管理182控制身份信息的修改与通信, 以及任选的其他管理单元。没有, 任何或所有由CPU171执行的管理功能, 根据不同的实施方案, 由硬件、软件或它们的任何组合控制和/或管理 (如执行在CPU内核172上或经由外部接口110连接的主机上的固件)。

[0272] 在一些实施方案中, CPU171能够执行其他管理任务, 例如一个或多个: 收集和/或报告性能统计; 实现智能; 控制电源时序, 控制和/或监控和/或调节功耗; 应对停电; 控制和/或监控和/或调节时钟频率; 和其他管理任务。

[0273] 各种实施方案包括计算主机的闪存控制器, 它类似于SSD控制器100和与各种计算

主机操作兼容,例如通过主机接口111和/或外部接口110相匹配。各种计算主机包括一个或任意组合计算机、工作站计算机、服务器计算机、存储服务器、SAN、NAS设备、DAS设备、存储设备、PC、笔记本电脑、上网本电脑、平板设备或计算机、超极本电脑、电子阅读设备(如电子阅读器)、PDA、导航系统、(手持式)GPS设备、汽车控制系统、汽车多媒体控制系统或电脑、打印机、复印机或传真机或一体设备、POS设备、现金寄存器、媒体播放器、电视、媒体录像机、DVR、数码相机、蜂窝手机,无绳电话和电子游戏。

[0274] 在各种实施方案中,SSD控制器的所有或任何部分(或计算主机的闪存控制器)是在单一集成电路、多模集成电路的单芯片、多芯片集成电路的多个芯片或多个集成电路中实现的。例如,缓冲区131是与SSD控制器100的其它元件在同一芯片上实现的。又例如,缓冲区131在SSD控制器100的其它元件之外的不同芯片来实现的。

[0275] 图1B示出了各种系统实施方案经选择的细节包括图1A的一个或多个SSD实例。SSD101包括SSD控制器100耦合到NVM199通过设备接口190。附图示出了各类实施方案:单一SSD直接耦合到主机,多个SSD的每个分别通过各自的外部接口直接耦合到主机,一个或多个SSD通过各种互连元件间接耦合到主机。

[0276] 作为单一SSD直接耦合到主机的示例实施方案,SSD101的实例经由外部接口110直接耦合到主机102(例如,开关/结构/中间体控制器103被省略、旁路或直通)。作为经由各自外部接口多个SSD的每个直接耦合到主机的示例实施方案,经由外部接口110的各自实例多个SSD101的实例的每个分别直接耦合到主机102(例如,开关/结构/中间体控制器103被省略、旁路或直通)。作为经由各种互连元件一个或多个SSD间接地耦合到主机的示例实施方案,一个或多个SSD101实例中每个分别间接地耦合到主机102。每个间接耦合是经由外部接口110的各自实例耦合到开关/结构/中间体控制器103,并且中间体接口104耦合到主机102。

[0277] 包括开关/结构/中间体控制器103的一些实施方案还包括存储卡112C通过存储器接口180耦合并且通过SSDs可访问。在各种实施方案中,一个或多个SSDs、开关/结构/中间体控制器和/或存储卡被包括在物理识别模块、存储卡或可插拔的元素上(例如I/O卡116)。在一些实施方案中,对应于SAS驱动器或SATA驱动器的SSD101(或其变体)耦合到引发操作主机102。

[0278] 主机102能够执行主机软件115的各种元素,如OS105的各种组合、驱动器107、应用109和多设备管理软件114。虚线箭头107D代表主机软件<→I/O设备通信,如发送/接收的数据向/从一个或多个SSD101的实例和从/到任何一个或多个OS105经由驱动器107、驱动器107以及应用109,可以通过驱动器107或者直接作为虚拟功能。

[0279] OS105包括和/或能操作驱动器用于与SSD的接口(由驱动器107概念性示出)。各种版本的Windows(如:95、98、ME、NT、XP、2000、服务器、Vista和7)、各种版本的Linux(如红帽、Debian、和Ubuntu)以及各种版本的MacOS(如8、9和X)是OS105的示例。在各种实施方案中,驱动程序是标准和/或通用驱动程序(有时被称为“收缩包装”或“预安装”)用于标准的接口和/或协议如SATA、AHCI或NVM Express或任选定制和/或供应商特制以便能够使特定指令到SSD101。一些驱动器和/或驱动程序有直通模式以便应用级的程序,比如通过优化的应用109NAND访问(有时称为ONA)或直接NAND访问(有时称为DNA)技术,直接与SSD101通信指令,使用通用的驱动程序实现了定制化的应用使用特定指令到SSD101。ONA技术包括一个或多

个:使用非标准的调节器(提示);使用供应商特定指令;非标准的统计数据通信,如根据压缩实际NVM的使用;和其他技术。DNA技术包括一个或多个:使用非标准指令或供应商特定提供的未映射的读取、写入和/或擦除访问NVM;使用非标准或供应商特定的指令提供更直接地访问NVM,比如旁路I/O设备反而要做的格式化数据;和其他技术。驱动程序的示例是没有ONA或DNA支持、启用ONA的驱动程序、启用DNA驱动程序以及启用ONA/DNA驱动程序的驱动程序。驱动程序的进一步示例是供应商提供的、供应商开发的和/或供应商增强的驱动程序以及客户提供的、客户开发的和/或客户增强的驱动程序。

[0280] 应用级程序的示例是没有ONA或DNA支持、启用ONA应用、启用DNA应用以及启用ONA/DNA应用。虚线箭头109D为代表应用 $\longleftrightarrow$ I/O设备通信(例如对于应用,通过驱动程序旁路或通过虚拟功能旁路),例如对于SSD启用ONA的应用和启用ONA驱动程序通信,如不使用OS为中介的应用。虚线箭头109V代表应用 $\longleftrightarrow$ I/O设备通信(例如对于应用,通过虚拟功能旁路),例如对于SSD启用DNA应用和启用DNA驱动程序通信,如不使用OS或驱动程序作为中介的应用。

[0281] 在一些实施方案中,NVM199中的一个或多个部分被用于固件存储,例如固件106。固件存储包括一个或多个固件图像(或其部分)。固件图像,例如,固件的一个或多个图像,如由SSD控制器100的CPU内核172执行。对于另一示例,固件图像具有一个或多个图像的常量、参数值和NVM设备的信息、引用,如通过CPU内核固件执行过程中。固件的图像对应于,例如,当前的固件图像和先前的0个或多个(相对于固件更新)固件图像。在各种实施方案中,固件提供了通用的、标准的、ONA和/或DNA的操作模式。在一些实施方案中,一个或多个固件操作模式通过键或各种软件技术的被启用(例如一个或多个API被“解锁”),由驱动程序任选通信和/或提供。

[0282] 在一些缺乏开关/结构/中间体控制器的实施方案中,SSD经由外部接口110直接耦合到主机。在各种实施方案中,通过一个或多个中间级的其它控制器如RAID控制器,SSD控制器100耦合到主机。在一些实施方案中,SSD101(或其变体)对应于SAS驱动器或SATA驱动器且开关/结构/中间体控制器103对应于扩展器又耦合到调节器,或者开关/结构/中间体控制器103对应于通过扩展器间接耦合到调节器的桥接器。在一些实施方案中,开关/结构/中间体控制器103包括一个或多个PCIe开关和/或结构。

[0283] 在各种实施方案中,如一些实施方案其中主机102是计算主机(如计算机、工作站计算机、服务器计算机、存储服务器、SAN、NAS设备、DAS设备、存储设备、个人电脑、笔记本电脑和/或上网本电脑),计算主机可选启用(例如,通过可选的I/O和存储设备/资源117和可选的LAN/WAN119)与一个或多个本地和/或远程服务器(例如,可选的服务器118)通信。通信启用,例如,本地和/或远程访问、管理和/或SSD101元件的任一或更多使用。在一些实施方案中,通信是完全或部分地经由以太网。在一些实施方案中,通信是完全或部分地经由光纤通道。在各种实施方案中,LAN/WAN119是代表一个或多个本地和/或广域网,如在服务器群中的任一或多个、网络耦合的服务器群、城域网和互联网。

[0284] 在各种实施方案中,SSD控制器和/或计算主机的闪存控制器与一个或多个NVM相组合以实现为非易失性存储元件,如USB存储元件、CF存储元件、MMC存储元件、eMMC存储元件,霹雳存储元件、UFS存储元件、SD存储元件、记忆棒存储元件以及xD图像卡存储元件。

[0285] 在各种实施方案中,SSD控制器的所有或任何部分(或计算主机的闪存控制器),或

其功能,在与该控制器耦合的主机中被实现(例如,图1B中的主机102)。在各种实施方案中,SSD控制器的所有或任何部分(或计算主机的闪存控制器),或其功能,是通过硬件(例如,逻辑电路)、软件和/或固件(例如,驱动器软件或SSD控制固件),或者它们的任意组合来实现的。例如,ECC单元相关功能性(例如,类似于ECC161和/或ECC-X135图1A)是部分地通过主机上的软件和部分地通过SSD控制器中的固件和硬件的组合来实现的。再比如,回收单元相关功能性(比如类似于图1A的回收站151)是部分地通过主机上的软件和部分地通过计算主机的闪存控制器中的硬件来实现的。

[0286] 0/1平衡恢复

[0287] 图2A到图2D示出了有关0/1平衡恢复的阈值电压分布。为了讨论的目的,每个小山般的凹凸是代表了NVM的部分读取单元大小的相应状态的阈值电压概率分布的独立的高斯型曲线的抽象。阈值电压轴被绘制为向右侧增加正电压。有意地没有提供绝对尺度,并没有确定参考点,使得该曲线更普遍适用于NVMS的较大多数。图2A和2B是SLC特例,而图2C和2D是MLC特例。

[0288] 在图2A中,代表初始时间(例如,当相应数据被写入时),最左侧的分布220代表逻辑1而最右侧的分布230代表逻辑0。根据不同的技术,最左侧的分布可以驻留(至少主要地)在负电压。读取阈值210坐落在两个分布之间。

[0289] 除非与本文中的实施方案相关联,这些阈值电压分布的独立,在一些实施方案中,NVM被写入存储的0和1的统计分布的具体知识。更具体地,在一些实施方案中的各种加密和/或加扰技术被用来使得0和1的统计分布是50-50%的(50%的0和50%的1)。当使用标称读取阈值读取SLC时,如图2A所示的理想的坐落情况,被观察的读取数据0和1的统计分布同样是50-50%左右。50-50%的统计分布不意味着任何样品数据将具有0位和1位的准确平衡,而是对于因样本数量的增加而增加紧的概率边界来说表示平均多个采样产生的0位和1位的比率汇集在50-50%上。打个比方是当硬币翻转多次的正面和背面分布,产生近似 $N/4$ 方差的高斯分布其中n是硬币翻转的次数。例如,如果0位和1位的50-50%的统计分布的读取单元中有18432位,0位(或1位)数量的方差大约是4608,标准偏差约为68。对于68的标准偏差,小于1的读取单位百万样品预计将有一批多于340的0位(5个标准差)偏离9216的平均水平。

[0290] 在图2B中,代表稍后的时间,标称读取阈值210是如图2A所示,并且两个阈值电压分布225和235相对于在图2A中的它们较早的分布220和230偏移。为示例的目的,两个分布被示出为都均匀地向左侧偏移(朝向更负电压)。但是应当理解一般地两个分布在正方向或负方向上彼此独立地移动。

[0291] 如图2B所示,当使用标称读取阈值210再次读取SLC时,所观察到的直接从NVM读取0和1统计分布(例如,之前的任何纠错)不会是50-50%左右是可预测的。更具体地,对于给定的概念性示例,1的错误过量是可以预料的,因为读取阈值是一些0将被错误地读取为1。

[0292] 在实践中,推断的方向是相反的。也就是说,在实际应用中,通常阈值电压分布的偏移不是已知或直接可知。在一些实施方案中,代替在观察中从NVM读取(相对于已知0和1的存储分布)的0和1的差异被用来推断在阈值电压分布的偏移的存在。此外,在这些实施方案中读取阈值是至少部分地基于观察到的差异被调整(详见本文其他地方)到读取阈值215,根据需要直到恢复0/1平衡。

[0293] 类似地,图2C代表初始时间(例如,当相应数据被写入时)与初始阈值电压分布,而图2D表示稍后的时间与相应的稍后的阈值电压分布。更具体地,对于可选择的格雷码映射,分别表示11、10、00和10状态,阈值电压分布(图2D的)251、261、271和281相对于它们较早各自的阈值电压分布250、260、270和280(图2C的)偏移。三个标称(初始值)读取阈值显示: $V_{READ1}240$ 、 $V_{READ2}242$ 和 $V_{READ3}244$ 。再次为示例的目的,在图2D中四个分布被示为都均匀地向左边偏移(朝向更负电压)。但是应当理解一般地四个分布在正方向或负方向上彼此独立地移动。

[0294] 在一些实施方案中,各种加扰技术的使用使得四个状态的统计分布是25-25-25-25%(每个状态25%)。当使用标称读取阈值读取MLC时,如图2C所示的理想的坐落情况,在一些实施方案中的四种状态的统计分布能确认到同样是25-25-25-25%左右。(如别处所讨论的,0和1是直接由控制器观察到的,但所有四种状态是根据需要推理的)。在一些实施方案中,从NVM(相对于已知存储的状态分布)读取的观察到的差异(预期25-25-25-25%的偏差)被用来推断阈值电压分布偏移的存在。读取阈值如图2D所示被调整(详见本文其他地方)成为 $V_{READ1}265$ 、 $V_{READ2}275$ 和 $V_{READ3}285$ 。在一些实施方案中,读取阈值的调整是分别执行用于下页读取(调整 $V_{READ2}275$ )和上页读取(调整 $V_{READ1}265$ 和/或 $V_{READ3}285$ )。

[0295] 0/1平衡恢复的功能

[0296] 图3A提供了图1A和图1B的SSD101、SSD控制器100和NVM199的交替视图。选择地重绘了逻辑块的边界以强调特定功能。SSD101在顶层设有外部接口110、SSD控制器100、NVM199和设备接口190。

[0297] 外部接口110耦合连接到主机,如图1B所示的主机102,并支持高级存储协议如SATA,包括主机来源存储相关的指令和写入数据和控制器来源的读取数据并在图1A的上述讨论中所详述。设备接口190支持低级的NVM的I/O事务,如在图1A的详细讨论中。NVM199拥有NVM阵列332、可编程只读电压电路334、控制/状态寄存器336和I/O338。SSD控制器100拥有主机接口111、加扰器310、ECC编码器320、设备接口逻辑191、失衡检测器340、缓冲区131、ECC解码器360、解扰器370和平衡恢复逻辑380。如先前所讨论的主机接口111经由外部接口110耦合连接主机,提供了写入数据306到加扰器310并接收从缓冲区131读取数据351。

[0298] 写入路径和功能如下。加扰器310操作写入数据306以产生加扰写入数据311到ECC编码器320。加扰器310以可逆的方式加扰写入数据306使得加扰写入数据311具有已知存储状态的统计分布。在一些实施方案中,加扰器310执行加密,如通过AES编码器,该随机化的数据作为加密的副产品。在一些实施方案中,加扰器310使用线性反馈偏移寄存器(LFSR)来随机化数据(但没有任何数据安全意图)。ECC编码器320处理加扰写入数据311添加额外的ECC位,从而产生ECC编码的写入数据321,其被提供到设备接口191经由设备接口190用于存储到NVM199。

[0299] 基本的读取路径和功能如下。NVM页,包括未校正和加扰(RAW)读取数据359,通过设备接口190从NVM199被接收。在一些实施方案和如图3B所示的详细介绍中,每个NVM页读取的包括四个码字(即读取单元):码字0到码字3。继续如图3A所示,每个码字名义上包含来自加扰器301的加扰数据以及由ECC编码器320产生的额外ECC位,但一般作为无意改变NVM存储和检索操作的结果。通过缓冲区131码字被提供给ECC解码器360。ECC解码器360处理该码字,利用所包含的附加ECC位以校正来自最初ECC编码数据的一般可能出现在任何点和时

间的任何差错,产生校正读取数据361,它被提供给解扰器370。解扰器370操作校正读取数据361,与加扰器310执行的加扰相反,从而产生解扰读取数据371,其作为读取数据351经由缓冲区131被提供到主机接口111。

[0300] 读取路径和功能还包括失衡检测器340和平衡恢复逻辑380。失衡检测器340监视从NVM接收到的原始读取数据359,并至少暂时保持统计状态分布的数据。平衡恢复逻辑380与NVM控制/状态寄存器336交互,通过设备接口逻辑191和NVM I/0338,以通过可编程的NVM读取电压电路334选择性地调整NVM读取阈值(用来读取NVM阵列332)。读取阈值是基于1)通过ECC解码器360检测的不可校正读取362,和2)不平衡检测器340检测的失衡341进行调整的。读取单元是在SLC和MLC的实施方案中的二进制数据。0和1的差异在SLC的情况下是直接测量(或当MLC是可操作的尽管是SLC)。在一些实施方案中,多于两个MLC状态的差异是基于如何在NVM中保存数据的知识被推断的。

[0301] 图3A示出了在作为从NVM199写入和读取数据的来源和汇聚地的主机中0/1平衡恢复的功能。在各种实施方案中(如图1A和图1B所示),一个或多个其他代理操作作为从NVM199写入和读取数据的来源和汇聚地。其他代理的示例是图1A所示的回收站151,在NVM199中将数据从一个位置移动到另一个位置将在本文其他地方描述。

[0302] 在各种实施方案中,与加扰器310、ECC编码器320、ECC解码器360和解扰器370的任何一个或多个相关联的功能性的任何或所有部分使用一个或多个数据处理121和ECC161至少部分地被实现(两者如图1A所示)。

[0303] 0/1平衡恢复的控制流

[0304] 图4示出用于图1A、图1B和图3A的SSD实施方案所选择的流程控制细节,提供关于写入相关的操作与读取相关操作的特定信息。写入操作开始动作410,并且通过430继续。然而返回路径没有明确画出,后续的写入操作重新开始动作410。同样地,动作440开始的读取操作,持续到460,并有条件地继续通过480。虽然返回路径未明确画出,随后的读取操作重新开始于动作440。假定在读取相同区域之前至少初始写入。否则,除人为的情况下,如在测试中,当应用需要时,读取操作和写入操作通常独立地调用,对于相同的或一般的不同位置。然而,在一个启发式的例子,第一读取操作440概念上在相同位置的最后写入操作430之后立即继续。

[0305] 考虑到更详细的写入相关的操作,原始数据将被写入到NVM,通常首先在动作410加扰,如通过加密或使用LFSR。除非更特殊性的情况下,术语“加扰”是指对原始数据的处理,可以通过任何在存储在NVM里的各种状态间的导致统计分布的操作或选择。加扰方法包括加密和线性反馈偏移寄存器技术。(也参看图3A的加扰器310)。在一些加密的实施方案中,加扰按照AES加密规范中的至少一个版本。在一些LFSR实施方案中,加扰是按照至少一个LFSR的选择。在一些实施方案中,加扰是更直接地通过一个或多个测试模式的选择来确定,当写入到NVM(而不必使用加密或LFSR的处理)提供状态的被选择的统计分布。

[0306] LFSR是具有产生从移位寄存器的选定抽头的线性函数或者上面的软件模型的输入位的组合逻辑反馈网络的硬件移位寄存器。该线性反馈移位寄存器产生确定性的伪随机序列。至少在概念上,该线性反馈移位寄存器生成的伪随机序列是模2加到原始数据,以提供经加扰的数据。

[0307] 接着,加扰数据是下一个通常(但可选的)ECC编码,如动作420所示(也参看图3A的

ECC编码器的320)。在面对当使用NVM时由于各种原因出现的错误,ECC编码提供了方便的数据恢复(通过误差校正)的冗余信息。这种错误是更加普遍,因此ECC编码较为普遍的,并且因此ECC编码更加可取,与一个或多个更小的几何形状、更广泛地使用、更大的年限、更大的温度偏差并使用MLC存储器。

[0308] 加扰的与可选的ECC编码的数据将被写入到NVM,如动作430所示,最后的写入相关的操作。被写入的状态分布被称为加扰的结果。在使用SLC存储器和AES加密的情况下,0-1分布是50-50(即,50%的0和50%的1)。在使用4LC(4级MLC)存储器和AES加密的情况下,写入下页与上页后的分布是25-25-25-25(即,在每四种状态的25%)。

[0309] 在一些实施方案中,至少一个参考区域专用于一种或多种如上所述的测试模式。在一些实施方案中,参考区域的位置被选择以最小化(或相反,以最大化)在各种NVM的写入/读取工件的测试模式上的冲击。在一些实施方案中,参考区域是参考页,并且它的位置被选择为写入块中的最后一页,以便尽量减少对写入数据的写入干扰的冲击。由于一些影响的电压分布的现象是时间与/或温度变化,参考区用作0/1差异效应的一个已知的措施。

[0310] 考虑到更详细的读取相关的操作,在动作440中开始,一个或多个从NVM读取和状态的分布读取的读取单元被捕获。在一些实施方案中,每一个0计数和1计数被直接确定。接着,在动作450,做出尝试以恢复原始数据。执行写入之前的任何被执行的数据操作的反操作。通常,在写入之前ECC编码被加入,并将由此通常读取单元下一步进行ECC解码。(也参看图3A的ECC解码器360。)在每个读取单元的基础上,如果ECC解码成功,则解码接下来执行,如合适的。例如,AES加密在写入之前被使用,AES解密被执行。或者,其中线性反馈移位寄存器生成的伪随机序列被使用,相同的序列是模2加到ECC从读取单元解码后的数据。

[0311] 当原始数据可恢复时,读取相关的操作早结束,要么没有错误或者是通过ECC解码可纠正的错误。参看从460判定“否”路径。然而,在读取单元的任一无法纠正的错误,动作470和480也被执行。参看460的判定“是”路径。在动作470中,状态分布的差异被评估。(也参看图3A失衡检测器340)。在一些实施方案中所确定的差异是在0计数和1计数间所确定的差值。在各种实施方案中,所确定的差异通过所有的读取单元,甚至少于具有不可校正错误的读取单元来计算。

[0312] 接着,在动作480中,用于至少一个读取阈值的调整值(即阈值偏移)至少部分基于所确定的差异的大小予以确定。在一些实施方案中,如果所确定的差异的幅度低于预定容差,读取阈值不被调整。在一些实施方案中的多因子“校正算法”被使用以确定调整后的读取阈值,因为确定差异的大小是一个因素。

[0313] 在一些实施方案中,校正算法采用用于选择要读取的阈值的替代值的查找表的形式。所确定的差异的大小是至少查找表的部分索引的基础。在一些实施方案中,查找表是基于正在使用的NVM的特定供应商的预先特征(加权)。在一些实施方案中,索引具有额外的部分,包括一个或多个的:P/E循环、年龄、停留时间(从上次写入时间)、温度、以及可能涉及到漂移的任何其他因素、或扰动、NVM阈值电压的分布。(也参看图3A的平衡恢复逻辑380)。

[0314] 此处和在整个具体实施方式中,应该记住的是,在通常使用的闪存的微架构,通常被访问的数据的读取与写入粒度是不同。读取访问(读取单元)的最小单位是页。页被组织成一个或多个码字,在一些实施方案中,如本文其他地方所讨论的。与此相反,写入存取的最小单位是多页的块。

[0315] 在一些实施方案中,差异是基于整个页进行评估。在一些实施方案中,差异基于码字进行评估。与在读取操作的不可校正错误的差异评估在与最近块写入操作写入位置相同(页或者码字)的位置,包括相同的位置。

[0316] 示例实现技术

[0317] 在一些实施方案中,所有或部分操作的组合通过0-1平衡SSD执行,例如使用闪存、计算主机的闪存控制器、和/或SSD控制器(例如图1A的SSD控制器100)、与处理器、微处理器、片上系统、特定应用集成电路、硬件加速器、或其他提供所有上述操作的全部或部分的电路,由与计算机系统处理兼容的规范所规定。本说明书与各种描述一致,如硬件描述语言、电路描述、网表描述、掩模描述,或布局描述。描述实例包括:Verilog、VHDL、SPICE、SPICE变体如PSpice、IBIS、LEF、DEF、GDS-II、OASIS、或其他描述。在各种实施方式中,处理包括:任何解释、编译、仿真、以及合成的组合以产生,验证,或指定适用于包含在一个或多个集成电路的逻辑与/或电路。每个集成电路,根据各种实施方案,根据各种技术是可设计和/或制造的。该技术包括可编程技术(如集成电路中现场或掩盖可编程门阵列)、半定制技术(如全部或部分基于单元的集成电路)与完全定制技术(如基本上专用集成电路),它们的任何组合,或任何其它与集成电路的设计与/或制造兼容的技术。

[0318] 在一些实施方案中,由具有一组存储其中的指令的计算机可读介质描述的所有或部分操作的各种组合通过一个或多个程序指令的执行与/或解释,通过一个或多个源与/或脚本语言语句,或者通过由编译、翻译产生的二进制指令的执行予以执行,与/或编程或脚本语言语句所表达的解释信息。语句与任何标准编程或脚本语言兼容(例如C、C++、Fortan、Pascal、Ada、Java、VBscript与Shell)。一个或一个以上的程序指令、语言的语句,或二进制指令被可选地存储在一个或多个计算机可读存储介质的元件中。在各种实施方案中,程序指令的一些、全部或各种部分被实现为一个或多个函数、例程、子例程、内联例程、过程、宏或它们的部分。

[0319] 结论

[0320] 描述中的已经做出的某些选择仅仅是为准备文本与附图的方便,以及除非有相反指示,选择不应该被解释本身作为传达关于所述实施方案的结构和操作的附加信息。选择的例子包括:用于计算数字与元件标识符(例如标注或数字指示符)的特定组织或分配的型号的特定组织或分配,用于标识与引用实施方案的特征与元件。

[0321] “包括”或“包括”一语是专门旨在被理解为抽象描述的开放式范围的逻辑集合,并且不意味着传达物理包含除非明确后跟单词“之内”。

[0322] 虽然为了描述和理解的清楚的目的,前述实施方案已经在一些细节予以描述,但本发明并不限于所提供的细节。存在本发明的许多实施方案。所公开的实施方案是示例性的而不是限制性的。

[0323] 应当理解的是,在构造、布局与使用方面的许多变型可能与说明书相一致,并且在授权专利的权利要求书的范围内。例如,根据每个组件块的各种实施方案,互连和功能单元位宽度、时钟速度,以及所使用的技术类型是可变的。互连和逻辑的名称仅仅是示范性的,而且不应该被解释为限制所描述的概念。根据各种实施方案,流程图和流程图的过程、操作和功能元件的次序与排列是可变的。此外,除非明确有相反的说明,规定的数值范围、所使用的最大值和最小值、或其他特定的规格(如闪存技术的类型,以及寄存器和缓冲器条数或

段数),仅仅是那些所描述的实施方案中,预计将跟踪实现技术的改进和变化,并且不应当被解释为限制。

[0324] 功能上,在本领域中已知的等效技术是可以采用的,而不是所描述的那些来实现的各种组件、子系统、操作、函数、例程、子例程、内联例程、程序、宏或它们的部分。这也就可以理解,实施方案的许多功能方面有选择地使用硬件(例如,一般的专用电路)或软件(例如,通过可编程控制器或处理器的一些方式)具有可实现性,根据实施方案的设计约束和更快处理的技术趋势(先前硬件中的功能向软件的便利的迁移)和更高的集成度(先前软件中的功能向硬件便利的迁移)。在各种实施方案中具体的变化包括,但不限于:在分区的差异;不同的形状系数和配置;使用不同的操作系统和其他系统软件;使用不同的接口标准、网络协议或通信链路;在根据特定应用的独特的工程技术及商业限制,实现这里描述的概念时,可以预料的其它变化。

[0325] 已经使用细节和环境上下文所描述的实施方案远远超出了所描述的实施方案的许多方面的最小实现所需要的。那些本领域的普通技术人员将认识到在没有改变剩余元件间的基本协作情况下,某些实施方案省略所公开的元件或特征。由此可以理解,许多所公开的细节不是实现所描述的实施方案的各个方面的需要。为了达到剩余的元件区别于被省略的现有技术、组件和功能的程度不限制于本文中所描述的概念。

[0326] 所描述的实施方案所传达的教导的所有这些设计变化是非实质性的。还应当理解,在其他计算与网络应用领域,本文中所描述的实施方案具有广泛的适用性,并且不限于所描述的实施方案的特定的应用领域或行业。因此,本发明应当被解释为包括在授权专利的权利要求书的范围内所包含的所有可能的修改和变化。

图1A

图1B

图2A

图2B

图2C

图2D

图3A

图3B

图4