(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4097891号

(P4097891)

(45) 発行日 平成20年6月11日(2008.6.11)

(24) 登録日 平成20年3月21日(2008.3.21)

(51) Int.Cl.

F 1

H04L 12/28 (2006.01)

H04L 7/00 (2006.01)H04L 12/28 200Z

H04L 7/00 Z

請求項の数 20 (全 30 頁)

(21) 出願番号 特願2000-360279 (P2000-360279)

(22) 出願日 平成12年11月27日 (2000.11.27)

(65) 公開番号 特開2002-164903 (P2002-164903A)

(43) 公開日 平成14年6月7日 (2002.6.7)

審査請求日 平成17年10月21日 (2005.10.21)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 仲井 勘

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72) 発明者 鈴木 健司

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72) 発明者 茅野 真一郎

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】 IEEE1394を用いた同期システム

## (57) 【特許請求の範囲】

## 【請求項1】

IEEE1394を用いて接続されたネットワーク内の各ノード間の同期をとるIEEE1394を用いた同期システムにおいて、

前記各ノードが有する各サイクルタイム同士の遅延ずれ量を計測するサイクルタイム遅延計測手段と、

前記サイクルタイム遅延計測手段が計測した遅延ずれ量をもとに前記各サイクルタイム同士の遅延ずれを補正するサイクルタイム遅延補正手段と、

を備え、

前記サイクルタイム遅延計測手段は、要求ノードから応答ノードに対してReadパケットを送信し、該応答ノードのサイクルタイム値を読み取り、この読み取ったサイクルタイム値を含むReadResponseパケットを前記要求ノードが受信し、この受信したサイクルタイム値と要求ノードのサイクルタイム値との差をもとに前記遅延ずれ量を算出する、

ことを特徴とするIEEE1394を用いた同期システム。

## 【請求項2】

前記要求ノードは、

前記Readパケットを送信し、前記ReadResponseパケットが返送される一連のシーケンスが、同一のアシンクロナス転送が行われている時間帯である同一のAsynchronous転送時間帯で完了するか否かを判定する判定手段を備え、

前記判定手段が、同一のAsynchronous転送時間帯で完了すると判定した場合に、Readパ

ケットを前記応答ノードに送出することを特徴とする請求項1に記載のI E E E 1 3 9 4を用いた同期システム。

【請求項3】

前記応答ノードの上位層は、

アシンクロナス転送が行われている時間帯であるAsynchronous転送時間帯であるか否かを判定する判定手段を備え、

前記判定手段がAsynchronous転送時間帯であると判定した場合に、前記上位層が前記ReadResponseパケットを送信バッファに蓄えることを特徴とする請求項1に記載のI E E E 1 3 9 4を用いた同期システム。

【請求項4】

10

前記応答ノードのリンク層は、

パケットの送出直前に該パケットにデータを書き込む書き込手段を備え、

前記ReadResponseパケットがリンク層バッファから送出される直前に前記書き込手段によって該ReadResponseパケットに当該応答ノードのサイクルタイム値を書き込むことを特徴とする請求項1に記載のI E E E 1 3 9 4を用いた同期システム。

【請求項5】

各ノードは、前記遅延ずれ量を記憶するサイクルタイム遅延記憶手段を備えたことを特徴とする請求項1～4のいずれか一つに記載のI E E E 1 3 9 4を用いた同期システム。

【請求項6】

20

前記サイクルタイム遅延記憶手段は、全てのノード間の遅延ずれ量をデータテーブル形式で記憶することを特徴とする請求項5に記載のI E E E 1 3 9 4を用いた同期システム。

【請求項7】

前記サイクルタイム遅延記憶手段は、サイクルマスタとしてのノードに設けられたことを特徴とする請求項6に記載のI E E E 1 3 9 4を用いた同期システム。

【請求項8】

前記ネットワークの構成の変化を判別するネットワーク構成変化判別手段をさらに備え、

前記ネットワーク構成変化判別手段がネットワークの構成に変化があったと判別した場合、該ネットワークの再構成後、前記サイクルタイム遅延計測手段がサイクルタイム同士の遅延ずれ量を計測し、前記サイクルタイム遅延補正手段が該遅延ずれ量をもとにサイクルタイム同士の遅延ずれを補正する処理を一回行うことを特徴とする請求項1～7のいずれか一つに記載のI E E E 1 3 9 4を用いた同期システム。

30

【請求項9】

前記ネットワーク構成変化判別手段は、サイクルマスタとしてのノードに設けられたことを特徴とする請求項8に記載のI E E E 1 3 9 4を用いた同期システム。

【請求項10】

前記サイクルタイム遅延計測手段および前記サイクルタイム遅延補正手段は、ノード間の同期を用いる所定のノードに設けられたことを特徴とする請求項1～9のいずれか一つに記載のI E E E 1 3 9 4を用いた同期システム。

40

【請求項11】

前記遅延ずれ量を伝送するサイクルタイム遅延伝送手段をさらに備え、

同期の基準となるサイクルタイムを有するサイクルマスタのノードは、前記サイクルタイム遅延計測手段および前記サイクルタイム遅延伝送手段を有し、

前記サイクルマスタのノード以外の所定のノードは、前記サイクルタイム遅延補正手段を有し、

前記サイクルマスタのノードが、該ノードが計測した遅延ずれ量を前記所定のノードに伝送し、あるいは該ノードが計測した遅延ずれ量をデータテーブルに記憶し、前記所定のノードが前記サイクルマスタのノードから該遅延ずれ量を取得し、その後所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに該ノードのサイクルタイムの

50

遅延ずれを補正することを特徴とする請求項 1 ~ 9 のいずれか一つに記載の I E E E 1 3 9 4 を用いた同期システム。

【請求項 1 2】

前記サイクルタイマ遅延補正手段は、サイクルスタートパケットを受信した際に、遅延ずれ量をもとにサイクルタイマ値を設定することを特徴とする請求項 1 0 または 1 1 に記載の I E E E 1 3 9 4 を用いた同期システム。

【請求項 1 3】

前記サイクルタイマ遅延補正手段は、上位層がサイクルタイマ値の使用時に、前記遅延ずれ量を用いて遅延ずれを補正することを特徴とする請求項 1 0 または 1 1 に記載の I E E E 1 3 9 4 を用いた同期システム。

10

【請求項 1 4】

前記所定のノードは、第 2 のサイクルタイマをさらに備え、

前記サイクルタイマ遅延補正手段は、任意のタイミングで遅延ずれ量を用いて前記遅延ずれを補正したサイクルタイマ値を前記第 2 のサイクルタイマに設定することを特徴とする請求項 1 0 または 1 1 に記載の I E E E 1 3 9 4 を用いた同期システム。

【請求項 1 5】

前記サイクルマスタのノードは、タイムスタンプを生成するタイムスタンプ生成手段を備え、

前記所定のノードは、タイムスタンプが示す時刻を監視するタイムスタンプ時刻監視手段を備え、

20

前記サイクルタイマ遅延補正手段は、前記遅延ずれ量をもとに、前記サイクルマスタのノードから送られた前記タイムスタンプのタイムスタンプ値を更新し、

前記タイムスタンプ時刻監視手段は、前記更新されたタイムスタンプ値が示す時刻を監視することを特徴とする請求項 1 0 または 1 1 に記載の I E E E 1 3 9 4 を用いた同期システム。

【請求項 1 6】

前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延補正手段は、サイクルマスタとしてのノードに設けられたことを特徴とする請求項 1 ~ 9 のいずれか一つに記載の I E E E 1 3 9 4 を用いた同期システム。

【請求項 1 7】

前記遅延ずれ量を伝送するサイクルタイマ遅延伝送手段をさらに備え、

サイクルマスタのノードは、前記サイクルタイマ遅延補正手段を有し、

前記サイクルマスタのノード以外の所定のノードは、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延伝送手段を有し、

前記所定のノードが、該所定のノードで計測した遅延ずれ量を前記サイクルマスタのノードに伝送し、あるいは前記所定のノードから遅延ずれ量を取得し、その後該所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに前記サイクルマスタのノードのサイクルマスタの遅延ずれを補正することを特徴とする請求項 1 ~ 9 のいずれか一つに記載の I E E E 1 3 9 4 を用いた同期システム。

30

【請求項 1 8】

前記サイクルマスタのノードは、タイムスタンプを生成するタイムスタンプ生成手段を備え、

前記所定のノードは、タイムスタンプが示す時刻を監視するタイムスタンプ時刻監視手段を備え、

前記サイクルタイマ遅延補正手段は、前記遅延ずれ量をもとに、前記タイムスタンプ生成手段が生成したタイムスタンプのタイムスタンプ値を更新することを特徴とする請求項 1 6 または 1 7 に記載の I E E E 1 3 9 4 を用いた同期システム。

40

【請求項 1 9】

請求項 1 ~ 1 8 のいずれか一つに記載した I E E E 1 3 9 4 を用いた同期システムは、サーボドライブ装置とこれを制御するコントローラとからなる制御システムであることを

50

特徴とする I E E E 1 3 9 4 を用いた同期システム。

【請求項 20】

前記コントローラは、サイクルマスタであることを特徴とする請求項 19 に記載の I E E E 1 3 9 4 を用いた同期システム。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、I E E E 1 3 9 4 をネットワークのデータ伝送手段として使用しているシステムにおける各ノード間のサイクルタイム遅延を測定し補償することができる I E E E 1 3 9 4 を用いた同期システムに関し、特に、1 つ以上のコントローラと、センサやサーボドライブなどの1 つ以上の被制御対象機器とによって構成される制御システムにおいて、I E E E 1 3 9 4 をネットワークのデータ伝送手段として使用している場合におけるコントローラと被制御対象機器との間のサイクルタイム遅延を測定し補償することができる I E E E 1 3 9 4 を用いた同期システムに関するものである。 10

【0002】

【従来の技術】

従来から、コントローラとサーボドライバとの間の通信方式は、各メーカー独自が方式で行われていた。一方、近年、このような F A 用コントローラの分野においても、オープン化に対応した製品への要求が高まっている。オープン化コントローラの普及によって、ユーザ独自仕様の組み込み、汎用パソコン資産の利用が可能になり、メーカーの異なる製品間の接続も容易になるなど、ユーザの使いやすさの向上が実現される。 20

【0003】

このようなコントローラとサーボドライバとの間のオープンなインターフェースとして、I E E E 1 3 9 4 や U S B を利用することが検討され始めている。特に、ホームオートメーション用のネットワーク規格 I E E E 1 3 9 4 を F A 用途に利用しようとする動きが本格化してきている。I E E E 1 3 9 4 は、

- (1) 100Mバイト/秒以上の高速のデータ転送が可能

- (2) アイソクロナス転送方式が可能で速い通信周期の同期通信が可能

- (3) 電源を切ることなく接続や切り離しが可能（活線挿抜）

- (4) 63台までの機器が接続できる

といった特徴を持つ。さらに量産効果によってインターフェース部分を低コストに製造できる可能性がある。また、インターフェース基板は、イーサネット (Ethernet) に比較して小型なので、各種の機器に組み込みやすい。 30

【0004】

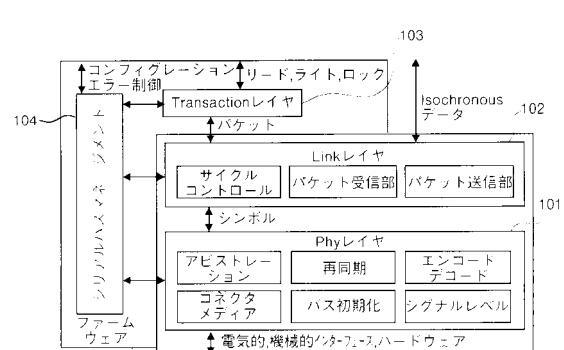

図 23 は、I E E E 1 3 9 4 の通信レイヤの構成を示す図である。図 23において、I E E E 1 3 9 4 の通信レイヤは、物理層 (Phyレイヤ) 1 0 1、リンク層 (Linkレイヤ) 1 0 2、トランザクション層 (Transactionレイヤ) 1 0 3 の3層と、シリアルバスマネジメント 1 0 4 とから構成される。

【0005】

Phyレイヤ 1 0 1 は、送受信する電気信号とLinkレイヤとの間で信号処理を行うレイヤである。Phyレイヤ 1 0 1 は、コネクタ、ケーブルなどの機械的インターフェースの規定、Linkレイヤ 1 0 2 が使用する論理信号のアナログディジタル変換を行うエンコードおよびデコード、通信信号の電気レベルを決めるシグナルレベルなどの電気的インターフェースの規定、通信ノード決定のためのアービトレーション、通信ロックの再同期、バスの初期化検出などを行っている。 40

【0006】

Linkレイヤ 1 0 2 は、Phyレイヤ 1 0 1 と Transactionレイヤ 1 0 3 との間で信号処理を行うレイヤである。Linkレイヤ 1 0 2 は、アドレス割当、データのチェック、データのフレーム分けを行うパケット送受信、サイクルのコントロールを行っている。なお、Isochronousデータは、Transactionレイヤを経由せずに、データが処理される。

## 【0007】

Transactionレイヤ103は、上位アプリケーションとLinkレイヤ102との間で信号処理を行うレイヤである。Transactionレイヤ103は、データの読み出し、書き込みなどの処理を行う。すなわち、Transactionレイヤ103は、Linkレイヤ102の処理を利用して、リクエストパケットの送信とレスポンスパケットの受信を行うことによって、指定されたノードとアドレスに対する1つの通信処理を行っている。また、逆に、リクエストパケットの受信とレスポンスパケットの送信という、他のノードから自ノードへの通信処理を行っている。

## 【0008】

シリアルバスマネージメント104は、3つのレイヤ全体の制御を行っている。なお、典型的な通信レイヤの実装としては、Phyレイヤ101とLinkレイヤ102とをハードウェアで構成し、Transactionレイヤ103とシリアルバスマネージメント104をファームウェアで構成する。

## 【0009】

I E E E 1 3 9 4 のAsynchronous通信は、非同期に、データの通信を行う際に用いられる。Asynchronous通信では、相手ノードに確実にパケットを送信することを保証し、送信の遅延時間は保証しない。送信ノードは、ヘッダ情報と実データとを指定先のノードに送信し、受信ノードは、Acknowledgeパケットを返信することで、パケットを受け取ったことを知らせる。

## 【0010】

I E E E 1 3 9 4 のIsochronous通信は、一種の同期通信であり、動画や音声などの伝送に適している。Isochronous通信では、125 μsec毎にデータ転送が完了することを保証する。Isochronousパケットの送信ノードは、特定のノードに送信するのではなく、0～63までのチャネル番号を使用してバス全体に送信し、受信ノードは、Acknowledgeパケットを返信しない。Isochronousパケットのヘッダは、6ビットのチャネル番号を使用することで、パケットを識別できるため、Asynchronousパケットのヘッダのように、64ビットのアドレス空間を使うのに比べて単純化されており、ヘッダ情報を少なくすることができる。受信ノードは、自ノードが受信したいチャネル番号のIsochronousパケットを選択して取り込む。送信ノードと受信ノードとが同じチャネル番号を使ってデータの送受信を行うことで、Isochronous通信が確立できる。

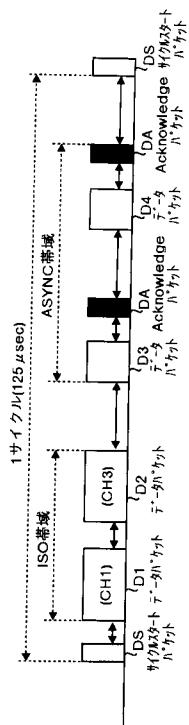

## 【0011】

図24に示すように、Isochronous通信とAsynchronous通信とは混在できる。1サイクル125 μsecのうち、最大で100 μsecをIsochronous通信に使用し、残りをAsynchronous通信に使用する。なお、パケット転送速度によって、Asynchronousパケットのデータペイロードの最大値が決定されているのは、Asynchronousデータの伝送時間が長すぎて、Isochronous通信を保証できなくなるのを回避するためである。

## 【0012】

Isochronous転送時間帯は、Isochronous通信を行う帯域であり、Asynchronous転送時間帯は、Asynchronous通信を行う帯域である。図24に示すように、Isochronous通信が常にAsynchronous通信よりも先に開始され、Isochronous通信を保証することができる。1サイクルでは、サイクルスタートパケットDSが送信された後に、図24では、Isochronous転送時間帯において、チャネルCH1のデータパケットD1およびチャネルCH3のデータパケットD2が伝送される。その後、Asynchronous転送時間帯において、データパケットD3, D4が伝送されるが、各データパケットD3, D4には、AcknowledgeパケットDAが返送される。

## 【0013】

I E E E 1 3 9 4 の各ノードのうち、アイソクロナス(Isochronous)能力のあるノードが搭載するLinkレイヤは、バスとクロック同期するためのCYCLE\_TIMEレジスタを実装し、このCYCLE\_TIMEレジスタの内容を最新にするためのタイマを有している。このタイマをサイクルタイマと呼ぶ。このサイクルタイマの時刻は、サイクルスタート(Cycle Star

10

20

30

40

50

t) パケットによって設定される。また、I E E E 1 3 9 4 では、このサイクルスタートパケットを発信するノードのことを、サイクルマスタと呼び、このサイクルマスタ以外のノードは、サイクルスレーブと呼ばれる。

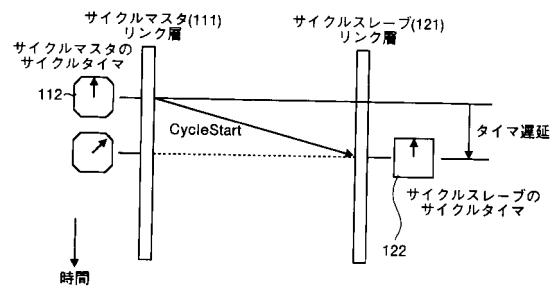

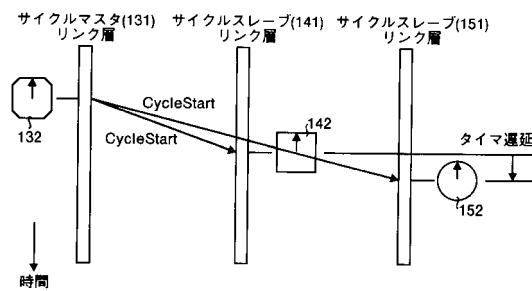

#### 【 0 0 1 4 】

すなわち、図 2 5 および図 2 6 に示すように、サイクルマスタ 1 1 1 , 1 3 1 が有するサイクルタイマ 1 1 2 , 1 3 2 の時刻をサイクルスタートパケット「CycleStart」に乗せて各ノード（サイクルスレーブ）1 2 1 , 1 4 1 , 1 5 1 に伝えることによって、各ノード 1 2 1 , 1 4 1 , 1 5 1 が有するサイクルタイマ 1 2 2 , 1 4 2 , 1 5 2 の時刻がサイクルマスタ 1 1 1 , 1 3 1 が有するサイクルタイマ 1 1 2 , 1 3 2 と同じ時刻に設定される。

10

#### 【 0 0 1 5 】

I E E E 1 3 9 4 を利用したリアルタイムデータ転送は、Isochronousパケットによって伝送されるが、サイクルタイマを基準にして、送信側と受信側でデータの同期を取っている。同期の方法としてIsochronousパケットにタイムスタンプを入れたりする。

#### 【 0 0 1 6 】

##### 【発明が解決しようとする課題】

しかしながら、実際には伝送遅延があるため、送信側のノードと受信側のノードのサイクルタイマは厳密に同じ時刻にはならない。すなわち、応答ノードがサイクルスタートパケットを受信してサイクルタイマの時刻を設定した瞬間には、要求ノードのサイクルタイマの時刻はその分だけ既に進んでおり、伝送遅延によって、送信側のノードと受信側のノードとの間の同期が精度良くとれないとになる。

20

#### 【 0 0 1 7 】

特に、I E E E 1 3 9 4 によって接続されたネットワークを用いた制御システムを考えた場合、コントローラとサーボドライブとは、これらサイクルタイマを基準として同期制御を実現することになる。しかしながら、この制御システムに対しては、高速高精度、特に同期制御の高速高精度が要求されており、そのようなコントローラとサーボドライブとの間のタイマ遅延が、制御の高速高精度、特に同期制御の高速高精度に大きな影響を与えてしまうという問題点があった。

#### 【 0 0 1 8 】

この発明は上記に鑑みてなされたもので、送信側のノードと受信側のノードとが有するサイクルタイマのタイマ遅延を補償し、特にI E E E 1 3 9 4 をコントローラとサーボドライブとの間のオープンなインターフェースとして使用した場合でも、高速高精度な制御、特に同期制御の高速高精度を実現することができるI E E E 1 3 9 4 を用いた同期システムを得ることを目的とする。

30

#### 【 0 0 1 9 】

##### 【課題を解決するための手段】

上記目的を達成するため、この発明にかかるI E E E 1 3 9 4 を用いた同期システムは、I E E E 1 3 9 4 を用いて接続されたネットワーク内の各ノード間の同期をとるI E E E 1 3 9 4 を用いた同期システムにおいて、前記各ノードが有する各サイクルタイマ同士の遅延ずれ量を計測するサイクルタイマ遅延計測手段と、前記サイクルタイマ遅延計測手段が計測した遅延ずれ量をもとに前記各サイクルタイマ同士の遅延ずれを補正するサイクルタイマ遅延補正手段とを備え、前記サイクルタイマ遅延計測手段は、要求ノードから応答ノードに対してReadパケットを送信し、該応答ノードのサイクルタイマ値を読み取り、この読み取ったサイクルタイマ値を含むReadResponseパケットを前記要求ノードが受信し、この受信したサイクルタイマ値と要求ノードのサイクルタイマ値との差をもとに前記遅延ずれ量を算出することを特徴とする。

40

#### 【 0 0 2 0 】

この発明によれば、I E E E 1 3 9 4 を用いて接続されたネットワーク内の各ノード間の同期をとる際、サイクルタイマ遅延計測手段が、前記各ノードが有する各サイクルタイマ同士の遅延ずれ量を計測し、要求ノードから応答ノードに対してReadパケットを送信し

50

、該応答ノードのサイクルタイム値を読み取り、この読み取ったサイクルタイム値を含むReadResponseパケットを前記要求ノードが受信し、この受信したサイクルタイム値と要求ノードのサイクルタイム値との差をもとに前記遅延ずれ量を算出するようにしていると共に、サイクルタイム遅延補正手段が、前記サイクルタイム遅延計測手段が計測した遅延ずれ量をもとに前記各サイクルタイム同士の遅延ずれを補正するようにしている。

#### 【0031】

つぎの発明にかかるI E E E 1 3 9 4を用いた同期システムは、上記の発明において、前記要求ノードは、前記Readパケットを送信し、前記ReadResponseパケットが返送される一連のシーケンスが、同一のアシンクロナス転送が行われている時間帯である同一のAsynchronous転送時間帯で完了するか否かを判定する判定手段を備え、前記判定手段が、一連のシーケンスが同一のAsynchronous転送時間帯で完了すると判定した場合に、Readパケットを前記応答ノードに送出することを特徴とする。

10

#### 【0032】

この発明によれば、前記要求ノードの判定手段が、前記Readパケットを送信し、前記ReadResponseパケットが返送される一連のシーケンスが、同一のアシンクロナス転送が行われている時間帯である同一のAsynchronous転送時間帯で完了するか否かを判定し、前記要求ノードが、前記判定手段が同一のAsynchronous転送時間帯で完了すると判定した場合に、Readパケットを前記応答ノードに送出するようにし、ReadResponseパケットが同一のAsynchronous転送時間帯内で返送されるようにしている。

20

#### 【0033】

つぎの発明にかかるI E E E 1 3 9 4を用いた同期システムは、上記の発明において、前記応答ノードの上位層は、アシンクロナス転送が行われている時間帯であるAsynchronous転送時間帯であるか否かを判定する判定手段を備え、前記判定手段がAsynchronous転送時間帯であると判定した場合に、前記上位層が前記ReadResponseパケットを送信バッファに蓄えることを特徴とする。

30

#### 【0034】

この発明によれば、前記応答ノードの上位層の判定手段が、アシンクロナス転送が行われている時間帯であるAsynchronous転送時間帯であるか否かを判定し、前記判定手段がAsynchronous転送時間帯であると判定した場合に、前記上位層は前記ReadResponseパケットを送信バッファ(TX\_FIFO)に蓄えることで、前記ReadResponseパケットは、送信バッファ長くとどまることなく、直ちに要求ノードに返送されるようにしている。

#### 【0035】

つぎの発明にかかるI E E E 1 3 9 4を用いた同期システムは、上記の発明において、前記応答ノードのリンク層は、パケットの送出直前に該パケットにデータを書き込む書き込み手段を備え、前記ReadResponseパケットがリンク層バッファから送出される直前に前記書き込み手段によって該ReadResponseパケットに当該応答ノードのサイクルタイム値を書き込むことを特徴とする。

#### 【0036】

この発明によれば、前記応答ノードのリンク層の書き込み手段が、前記ReadResponseパケットがリンク層バッファから送出される直前に該ReadResponseパケットに当該応答ノードのサイクルタイム値を書き込むようにしている。

40

#### 【0037】

つぎの発明にかかるI E E E 1 3 9 4を用いた同期システムは、上記の発明において、各ノードは、前記遅延ずれ量を記憶するサイクルタイム遅延記憶手段を備えたことを特徴とする。

#### 【0038】

この発明によれば、各ノードのサイクルタイム遅延記憶手段が、前記遅延ずれ量を記憶し、少なくとも他のノードからのアクセスによって遅延ずれ量を獲得できるようにしている。

#### 【0039】

50

つぎの発明にかかる I E E E 1 3 9 4 を用いた同期システムは、上記の発明において、前記サイクルタイマ遅延記憶手段は、全てのノード間の遅延ずれ量をデータテーブル形式で記憶することを特徴とする。

【 0 0 4 0 】

この発明によれば、前記サイクルタイマ遅延記憶手段が、全てのノード間の遅延ずれ量をデータテーブル形式で記憶するようにしている。

【 0 0 4 1 】

つぎの発明にかかる I E E E 1 3 9 4 を用いた同期システムは、上記の発明において、前記サイクルタイマ遅延記憶手段は、サイクルマスタとしてのノードに設けられたことを特徴とする。

10

【 0 0 4 2 】

この発明によれば、前記サイクルタイマ遅延記憶手段を、サイクルマスタとしてのノードに設けるようにしている。

【 0 0 4 3 】

つぎの発明にかかる I E E E 1 3 9 4 を用いた同期システムは、上記の発明において、前記ネットワークの構成の変化を判別するネットワーク構成変化判別手段をさらに備え、前記ネットワーク構成変化判別手段がネットワークの構成に変化があったと判別した場合、該ネットワークの再構成後、前記サイクルタイマ遅延計測手段がサイクルタイマ同士の遅延ずれ量を計測し、前記サイクルタイマ遅延補正手段が該遅延ずれ量をもとにサイクルタイマ同士の遅延ずれを補正する処理を行なうことを特徴とする。

20

【 0 0 4 4 】

この発明によれば、ネットワーク構成変化判別手段が、前記ネットワークの構成の変化を判別し、前記ネットワーク構成変化判別手段がネットワークの構成に変化があったと判別した場合、該ネットワークの再構成後、前記サイクルタイマ遅延計測手段がサイクルタイマ同士の遅延ずれ量を計測し、前記サイクルタイマ遅延補正手段が該遅延ずれ量をもとにサイクルタイマ同士の遅延ずれを補正する処理を行なうようにしている。

【 0 0 4 5 】

つぎの発明にかかる I E E E 1 3 9 4 を用いた同期システムは、上記の発明において、前記ネットワーク構成変化判別手段は、サイクルマスタとしてのノードに設けられたことを特徴とする。

30

【 0 0 4 6 】

この発明によれば、前記ネットワーク構成変化判別手段を、サイクルマスタとしてのノードに設けるようにしている。

【 0 0 4 7 】

つぎの発明にかかる I E E E 1 3 9 4 を用いた同期システムは、上記の発明において、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延補正手段は、ノード間の同期を用いる所定のノードに設けられたことを特徴とする。

【 0 0 4 8 】

この発明によれば、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延補正手段を、ノード間の同期を用いる所定のノードに設けるようにしている。

40

【 0 0 4 9 】

つぎの発明にかかる I E E E 1 3 9 4 を用いた同期システムは、上記の発明において、前記遅延ずれ量を伝送するサイクルタイマ遅延伝送手段をさらに備え、同期の基準となるサイクルタイマを有するサイクルマスタのノードは、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延伝送手段を有し、前記サイクルマスタのノード以外の所定のノードは、前記サイクルタイマ遅延補正手段を有し、前記サイクルマスタのノードが、該ノードが計測した遅延ずれ量を前記所定のノードに伝送し、あるいは該ノードが計測した遅延ずれ量をデータテーブルに記憶し、前記所定のノードが前記サイクルマスタのノードから該遅延ずれ量を取得し、その後所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに該ノードのサイクルタイマの遅延ずれを補正することを特徴とする。

50

**【0050】**

この発明によれば、同期の基準となるサイクルタイマを有するサイクルマスタのノードが、該ノードが計測した遅延ずれ量を前記サイクルタイマ遅延伝送手段によって前記所定のノードに伝送し、あるいは該ノードが計測した遅延ずれ量をデータテーブルに記憶し、前記所定のノードが前記サイクルマスタのノードから該遅延ずれ量を取得し、その後所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに該ノードのサイクルタイマの遅延ずれを補正するようにしている。

**【0051】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記サイクルタイマ遅延補正手段は、サイクルスタートパケットを受信した際に、遅延ずれ量をもとにサイクルタイマ値を設定することを特徴とする。 10

**【0052】**

この発明によれば、前記サイクルタイマ遅延補正手段が、サイクルスタートパケットを受信した際に、遅延ずれ量をもとにサイクルタイマ値を設定することを特徴とする。

**【0053】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記サイクルタイマ遅延補正手段は、上位層がサイクルタイマ値の使用時に、前記遅延ずれ量を用いて遅延ずれを補正することを特徴とする。

**【0054】**

この発明によれば、前記サイクルタイマ遅延補正手段が、上位層がサイクルタイマ値の使用時に、前記遅延ずれ量を用いて遅延ずれを補正することを特徴とする。 20

**【0055】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記所定のノードは、第 2 のサイクルタイマをさらに備え、前記サイクルタイマ遅延補正手段は、任意のタイミングで遅延ずれ量を用いて前記遅延ずれを補正したサイクルタイマ値を前記第 2 のサイクルタイマに設定することを特徴とする。

**【0056】**

この発明によれば、所定のノードの前記サイクルタイマ遅延補正手段が、任意のタイミングで遅延ずれ量を用いて前記遅延ずれを補正したサイクルタイマ値を第 2 のサイクルタイマに設定することを特徴とする。 30

**【0057】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記サイクルマスタのノードは、タイムスタンプを生成するタイムスタンプ生成手段を備え、前記所定のノードは、タイムスタンプが示す時刻を監視するタイムスタンプ時刻監視手段を備え、前記サイクルタイマ遅延補正手段は、前記遅延ずれ量をもとに、前記サイクルマスタのノードから送られた前記タイムスタンプのタイムスタンプ値を更新し、前記タイムスタンプ時刻監視手段は、前記更新されたタイムスタンプ値が示す時刻を監視することを特徴とする。

**【0058】**

この発明によれば、前記サイクルタイマ遅延補正手段が、前記遅延ずれ量をもとに、前記サイクルマスタのノードから送られた前記タイムスタンプのタイムスタンプ値を更新し、前記タイムスタンプ時刻監視手段が、前記更新されたタイムスタンプ値が示す時刻を監視することを特徴とする。

**【0059】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延補正手段は、サイクルマスタとしてのノードに設けられたことを特徴とする。

**【0060】**

この発明によれば、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延補正手段を、サイクルマスタとしてのノードに設けるようにしている。 50

**【0061】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記遅延ずれ量を転送するサイクルタイム遅延伝送手段をさらに備え、サイクルマスタのノードは、前記サイクルタイム遅延補正手段を有し、前記サイクルマスタのノード以外の所定のノードは、前記サイクルタイム遅延計測手段および前記サイクルタイム遅延伝送手段を有し、前記所定のノードが、該所定のノードで計測した遅延ずれ量を前記サイクルマスタのノードに伝送し、あるいは前記所定のノードから遅延ずれ量を取得し、その後該所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに前記サイクルマスタのノードのサイクルマスタの遅延ずれを補正することを特徴とする。

**【0062】**

10

この発明によれば、前記所定のノードが、該所定のノードで計測した遅延ずれ量を前記サイクルマスタのノードに伝送し、あるいは前記所定のノードから遅延ずれ量を取得し、その後該所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに前記サイクルマスタのノードのサイクルマスタの遅延ずれを補正するようにしている。

**【0063】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記サイクルマスタのノードは、タイムスタンプを生成するタイムスタンプ生成手段を備え、前記所定のノードは、タイムスタンプが示す時刻を監視するタイムスタンプ時刻監視手段を備え、前記サイクルタイム遅延補正手段は、前記遅延ずれ量をもとに、前記タイムスタンプ生成手段が生成したタイムスタンプのタイムスタンプ値を更新することを特徴とする。

20

**【0064】**

この発明によれば、前記サイクルタイム遅延補正手段が、前記遅延ずれ量をもとに、自サイクルマスタのノードの前記タイムスタンプ生成手段が生成したタイムスタンプのタイムスタンプ値を更新し、この更新したタイムスタンプ値を含むデータを所定のノードに伝送するようにしている。

**【0065】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、請求項 1 ~ 23 のいずれか一つに記載した IEE 1394 を用いた同期システムは、サーボドライブ装置とこれを制御するコントローラとからなる制御システムであることを特徴とする。

30

**【0066】**

この発明によれば、請求項 1 ~ 23 のいずれか一つに記載した IEE 1394 を用いた同期システムを、サーボドライブ装置とこれを制御するコントローラとからなる制御システムに適用している。

**【0067】**

つぎの発明にかかる IEE 1394 を用いた同期システムは、上記の発明において、前記コントローラは、サイクルマスタであることを特徴とする。

**【0068】**

この発明によれば、前記コントローラを、サイクルマスタとし、効率的な遅延ずれ量の計測および補正ができるようにしている。

40

**【0069】****【発明の実施の形態】**

以下、添付図面を参照して、この発明にかかる IEE 1394 を用いた同期システムの好適な実施の形態について説明する。

**【0070】**

実施の形態 1.

まず、この発明の実施の形態 1 について説明する。この実施の形態 1 では、ピングパケットを利用してサイクルタイム遅延を推定し補償するようにしている。P1394a では、最適な Gap\_Count 値を計算し設定するために、ピング (Ping) パケットが定義されている。Gap

50

(ギャップ)とは、例えば図24に示したデータパケットD2,D3間などの時間であり、バスがアイドル状態となっている時間をいい、このギャップが長くなれば、バスがアイドルとなっている時間が長くなり、実際にパケットが流れる時間が制限され、一方、ギャップを極端に短くすると、トポロジの構成で、物理層のホップ数が多い場合や接続されるノードが多い場合には通信が行えなくなってしまうため、ギャップは最適化される。

#### 【0071】

P1394aでは、あるノード(バスマネージャ)から他のノードにこのピングパケット送信すると、このピングパケットを受信した送り先のノードの物理層(Phyレイヤ)は、Self\_IDパケットを送り返す仕様になっており、ピングパケットが送出されてから、Self\_IDパケットが返送されて戻ってくるまでの時間を測ることによって、2つのノード間の遅延時間がわかるようになっている。そして、上述したように、P1394aでは、この遅延時間をもとに、最適なGap\_Count値を計算し設定することができるようになった。ルート以外は、すべてリンク層(Linkレイヤ)がなくても、このPingパケットに応答できるため、物理層だけで構成されるリピータでも遅延時間を知ることができ、トポロジが変わっても最適なGap\_Count値を計算することができる。なお、このPingパケットは、IEEE1394-1995規格にはないが、P1394a規格で検討中である。

10

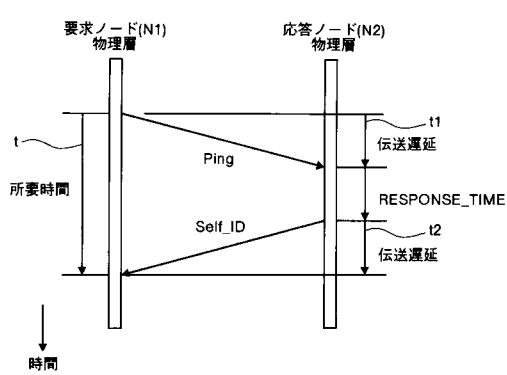

#### 【0072】

さて、この実施の形態1では、Pingパケットを利用してサイクルタイム遅延を推定し、補償する。IEEE1394の物理層のパケットリピート回路は、対称なため、図1に示すように、要求ノードN1の物理層から送られたPingパケットが応答ノードN2の物理層に到達するまでの伝送遅延t1は、応答ノードN2の物理層から返送されたSelf\_IDパケットが要求ノードN1の物理層に到達するまでの伝送遅延t2とほぼ等しい。すなわち、

伝送遅延t1 伝送遅延t2

20

とみなすことができる。この結果、図1に示すように、要求ノードN1の物理層がPingパケットを送出してからSelf\_IDパケットを受信するまでの時間を所要時間tとするとき、伝送遅延t1は、

$$t_1 \text{ (伝送遅延)} = (t \text{ (所要時間)} - \text{RESPONSE\_TIME}) / 2$$

として求めることができる。この伝送遅延t1がそのまま、要求ノードN1が保持するサイクルタイムと応答ノードN2が保有するサイクルタイムとの間の遅延として考えることができる。なお、「RESPONSE\_TIME」に実際どのくらいの時間がかかったのかは、この手法では分からぬが、「RESPONSE\_TIME」の最小値および最大値は、パラメータで指定されており(Cable interface timing constants)、既知である。したがって、たとえば、

RESPONSE\_TIME (最大値 + 最小値) / 2

30

として「RESPONSE\_TIME」を求めてよい。実験的に、「RESPONSE\_TIME」に実際どのくらいの時間がかかっているのかがわかっているれば、最大値と最小値の平均の代わりに適当な重み付き平均、たとえば、係数wを用いて

$$\text{RESPONSE\_TIME} = (w \times \text{最大値} + (1 - w) \times \text{最小値}) / 2$$

とし、これによって一層精度の良い「RESPONSE\_TIME」を求めることができる。

#### 【0073】

また、Pingパケットを送信し、Self\_IDパケットが返ってくるまでの所要時間tを計測する代わりに、RemoteAccessパケットを送信し、RemoteReplyパケットが返ってくるまでの時間を計測し、この時間を所要時間tとしてもよい。また、RemoteCommandパケットを送信し、RemoteConfirmationパケットが返ってくるまでの時間を計測し、この時間を所要時間tとしてもよい。これらパケットは、ほぼ同じ振る舞い、すなわち物理層が返送するので、これらのどのパケットを用いてもよい。これらのパケットは、サイクルマスター、サイクルスレーブに関わらず、全てのノードが任意にノードに対して送信することができるので、任意のノード間の遅延を任意のノードが必要に応じて計測することができる。

40

#### 【0074】

このノード間の遅延(タイム遅延)は各ノード間で各々異なるので、各ノード間の全ての場合についてタイム遅延の補償を行うのが望ましい。しかしながら、タイム遅延計測を頻

50

繁に行えば、タイマ遅延計測のためのパケットが増えることになり、その分だけネットワークのトラフィックが増えることになり、重要なパケットの伝送の妨げになりかねない。

【0075】

タイマ遅延は、ネットワークの構成（トポロジ）が変わらない限り同じであるから、タイマ遅延補償は、基本的にネットワークの構成（再構成）が行われた後の最初の1回だけ行えば良いので、バスリセットなどのネットワークの再構成を含むネットワークの構成が行われたことを検出し、かつサイクルスタートパケットによるサイクルタイマ設定が行われた後に、最初に1回だけタイマ遅延計測のためのパケットを流してタイマ遅延補償を行う。

【0076】

このため、ネットワーク上のある1つノード、たとえばサイクルマスタ、制御システムの場合はコントローラが、ネットワーク構成変化判別手段を保有する必要がある。ネットワーク構成変化判別手段は、ネットワークが再構成を判別した場合、タイマ遅延補償を行う指令を他のノードへ伝える。あるいは、ネットワーク構成変化判別手段を、必ずサイクルマスタ（制御システムの場合はコントローラ）が保有するようにし、サイクルマスタ自体が保有するデータテーブルにタイマ遅延を記憶するなどの一連のタイマ遅延に関する作業をすべてサイクルマスタによって管理するようにしても良い。

【0077】

この実施の形態1によれば、IEEE 1394の仕様（P1394a既存の仕様）の範囲内で、各ノードが有するサイクルタイマのタイマ遅延を補償することで、IEEE 1394を任意の用途に利用する場合でも、高精度な同期を実現することが可能となる。さらには、IEEE 1394をコントローラとサーボドライバと間のオーブンなインターフェースとして使用した場合でも、コントローラとサーボドライバとの間、あるいはサーボドライバ間同士のタイマ遅延を補償することが可能となり、高速高精度な制御を実現することができる。また、タイマ遅延計測に使用されるパケットは、サイクルマスタのみが使用できるものではなく、全てのノードが等しく使用できるため、任意のノード間のタイマ遅延を計測することが可能である。

【0078】

実施の形態2。

つぎに、この発明の実施の形態2について説明する。上述した実施の形態1では、RESPONSE\_TIMEに、実際どのくらいの時間がかかったのかが分からなかったため、およそのタイマ遅延を推定するようになっていたが、この実施の形態2では、真に正確なタイマ遅延を測定できるようにし、特にタイマ遅延の誤差が大きな影響を及ぼす、コントローラとサーボドライバとを有する制御システムにIEEE 1394を用いる場合であっても、支障のないようにしている。

【0079】

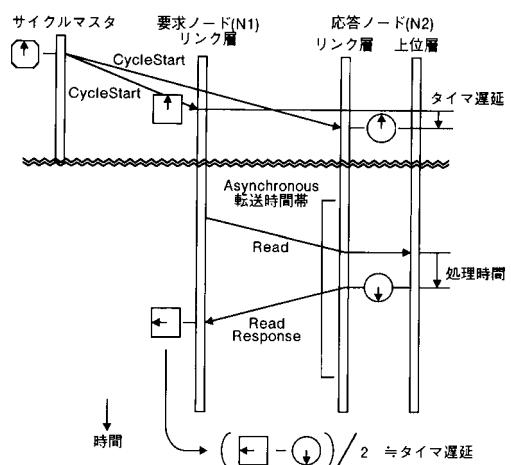

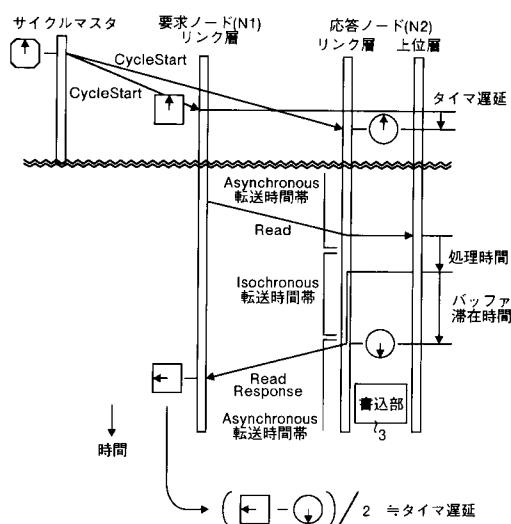

IEEE 1394では、リード（Read）パケットを使って、応答ノードが有するサイクルタイマのサイクルタイマ値を読み込むことができる。この読み込みによって取得されたサイクルタイマ値と要求ノードが有するサイクルタイマのサイクルタイマ値との差から、タイマ遅延を計測すれば、実際のタイマ遅延を測定することができるようと思われる。

【0080】

しかし、実際には、Readパケットに対するレスポンス（ReadResponse）パケットは、応答ノードの上位層（トランザクション層およびそれより上位の層）がReadResponseパケットを送信バッファ（TX\_FIFO）に蓄える際、ReadResponseパケットにサイクルタイマ値を書き込むため、その後、実際に応答ノードのリンク層から送信されるまでの時間は一定値ではなく、Readパケットとこれに対するReadResponseパケットとを用いても、正確なタイマ遅延を測定することはできない。

【0081】

送信バッファに蓄えられる時間が長くなる理由は、このリード処理が非同期（ASYNC）処理であり、ReadパケットおよびReadResponseパケットが非同期（ASYNC）パケットである

10

20

30

40

50

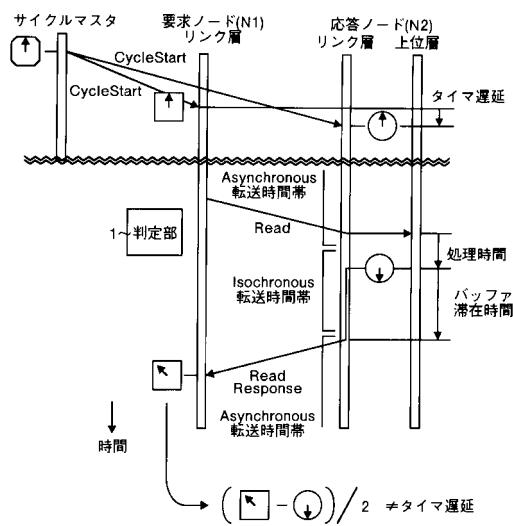

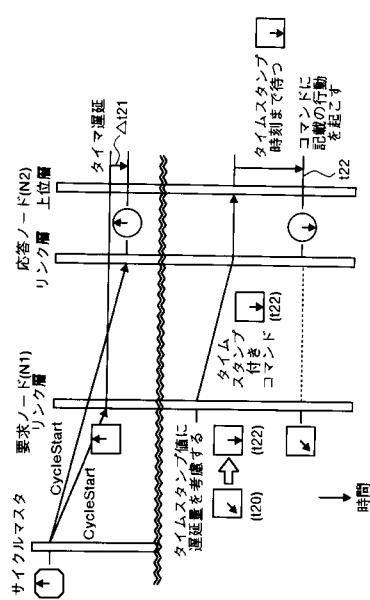

から、Asynchronous転送時間帯でしか送信することができないために、ReadResponseパケットが送信バッファに蓄える時がAsynchronous転送時間帯であれば、図2に示すように、送信バッファに滞留する時間は一瞬であって、直ちに送信されるのに対し、図3に示すように、ReadResponseパケットが送信バッファに送られた時がIsochronous転送時間帯であれば、Isochronous転送時間帯が終了してAsynchronous転送時間帯になって送信可能となるまで、ReadResponseパケットが送信バッファに滞留するからである。

#### 【0082】

この送信バッファに滞留する時間の差異を解消するには、いくつかの方策がある。その第1の方策は、応答ノードN2がReadパケットを受け付けてReadResponseパケットを送出するまでの一連の動作が、常に図2に示すように、同一のAsynchronous転送時間帯中に行わればよいのであるから、要求ノードN1が予め、Readパケットを送信してReadResponseパケットが返送されるまでの一連の動作が、同一のAsynchronous転送時間帯中に行われるかどうかを判定部1が判定し、同一のAsynchronous転送時間帯中に行われると判断した場合に、要求ノードがReadパケットを応答ノードに送信すればよい。

10

#### 【0083】

基本的に、タイマ遅延計測のためのパケットは、ネットワーク構築後の初期の段階で行われるので、ネットワーク構築後の初期の段階においては、制御システムが制御するためのデータ転送はなく、すなわちトラフィックは少なく、また、応答ノードN2の上位層でも特別なアプリケーションが作動していないので、タイマ遅延計測のためのパケットの要求に対してすばやく応答するであろう。

20

#### 【0084】

したがって、同一のAsynchronous転送時間帯中に上述した一連の動作が行われるネットワーク構築後の初期の段階などに、タイマ遅延計測のためのパケットを要求ノードN1が応答ノードN2に送出すれば、Readパケットを受け付けてからReadResponseパケットを送出するまでの処理時間は、容易に推定することができる。この場合、上位層における処理時間の推定は、上述した実施の形態1による遅延計測を用いることができる。また、この場合、上述した一連の動作が他のトラフィックに邪魔される可能性は少ないため、信頼度の高い測定が可能となる。

#### 【0085】

この第1の方策によれば、既存のプロトコルをそのまま使用し、送信側である要求ノードN1の上位層に、Readパケットを送信してReadResponseパケットが返送されるまでの一連の動作が同一のAsynchronous転送時間帯中に行われるかどうかを判定する判定部1を設けるのみで、この一連の動作が同一のAsynchronous転送時間帯内で行われるので、正確なタイマ遅延補償が可能となる。

30

#### 【0086】

第2の方策としては、図4に示すように、応答ノードN1の上位層が、ReadResponseパケットを送信バッファに蓄えるタイミングをAsynchronous転送時間帯の間に行えば良い。すなわち、応答ノードN2の上位層が、Asynchronous転送時間帯となるまで待って、ReadResponseパケットをリンク層に送出するようにする。なお、上位層は、下位のリンク層からの割り込み信号によって現在の通信伝送路の状態がIsochronous転送時間帯であるかAsynchronous転送時間帯であるかを知ることができる。これによって、Asynchronous転送時間帯待ちの既知の時間を上位層の処理時間に加えるのであるので、要求ノードN1と応答ノードN2との間のタイマ遅延を確実に測定することができる。

40

#### 【0087】

第2の方策によれば、既存のプロトコルをそのまま使用し、受信側ノードである応答ノードN2の上位層に、現在の通信伝送路の状態がIsochronous転送時間帯であるかAsynchronous転送時間帯であるかを判定する判定部を設けるだけで、ReadパケットとReadResponseパケットとが同一のAsynchronous転送時間帯内であろうとなかろうとに関わらず、正確なタイマ遅延補償を行うことができる。

#### 【0088】

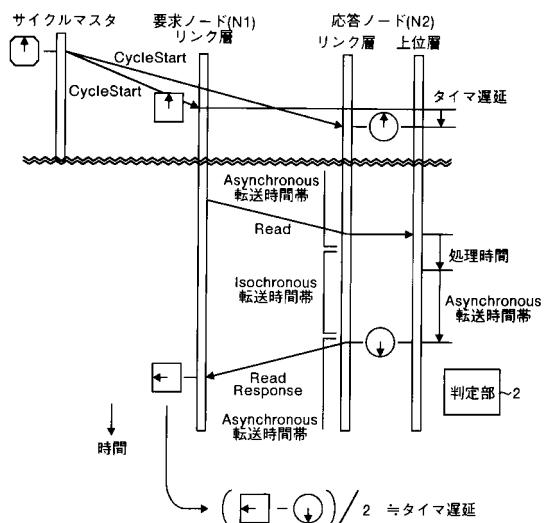

50

第3の方策としては、図5に示すように、ReadResponseパケットをリンク層から送出する時に、書込部3がこのReadResponseパケットにサイクルタイム値を書き込むようにする。すなわち、上位層からリンク層にReadResponseパケットが送られたときにサイクルタイム値を書き込むのではなく、ReadResponseパケットがリンク層から送出される瞬間に、このReadResponseパケットにサイクルタイム値を書き込むようにする。

【0089】

I E E E 1 3 9 4において、サイクルスタートパケットによるサイクルタイム設定では、サイクルマスターから送られてくるサイクルスタートパケットを応答ノードN2がリンク層で受け取った瞬間に、該サイクルスタートパケットに記述されているサイクルタイム値を自ノードのサイクルタイム値として設定する機構を既に備えている。

10

【0090】

しかしながら、この機構は、サイクルスタートパケットに固有の機構であって、第3の方策を行う機構は、I E E E 1 3 9 4には定義されておらず、新規にこの機構を追加するものである。なお、第1の方策あるいは第2の方策のように、送信バッファに蓄えられてから直ちに送信されると言っても若干の時間はかかるものであるが、この第3の方策によれば、この若干の時間の誤差すら発生せず、一層、正確な遅延測定が可能になる。

【0091】

第3の方策によれば、既存のプロトコルをそのまま使用し、受信側ノードである応答ノードのリンク層に、ReadResponseパケットがリンク層から送出される瞬間にこのReadResponseパケットにサイクルタイム値を書き込む書込部3を設けるだけで、ReadパケットとRead Responseパケットとが同一のAsynchronous転送時間帯内であろうとなかろうとに関わらず、正確なタイム遅延補償が可能となる。

20

【0092】

この実施の形態2によれば、I E E E 1 3 9 4の仕様(I E E E 1 3 9 4 - 1 9 9 5既存の仕様)の範囲内で、各ノードが有するサイクルタイムのタイム遅延を補償することで、I E E E 1 3 9 4を任意の用途に利用する場合でも、高精度な同期を実現することが可能である。さらには、I E E E 1 3 9 4をコントローラとサーボドライバとの間のオープンなインターフェースとして使用した場合でも、コントローラとサーボドライブとの間あるいはサーボドライブ間同士のタイム遅延を補償することが可能となり、高速高精度な制御を実現できる。また、タイム遅延計測に使用されるパケットは、サイクルマスターのみが使用できるものではなく、全てのノードが等しく使用できるため、任意のノード間のタイム遅延を計測することが可能である。

30

【0093】

実施の形態3。

つぎに、この発明の実施の形態3について説明する。この実施の形態3では、上述した実施の形態1または実施の形態2によって測定されたタイム遅延をもとに、タイム遅延の補償を行うものである。なお、この実施の形態3では、サイクルスレーブ側がサイクルスタートパケット受信時にタイム遅延を補償する場合について説明する。

【0094】

まず、サイクルスレーブは、サイクルスレーブ自身が有するサイクルタイム値と、サイクルマスターが有するサイクルタイム値との遅延ずれを知っている必要がある。この遅延ずれを取得するためのいくつかの態様としては、たとえば、つぎの9つの遅延ずれ取得態様がある。

40

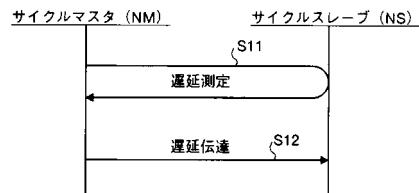

【0095】

第1の遅延ずれ取得態様は、図6に示すように、サイクルマスターNMが任意のサイクルスレーブNSとの間の遅延ずれを測定し(S11)、この遅延ずれを当該サイクルスレーブNSに伝える(S12)ことによって当該サイクルスレーブNSが遅延ずれを取得する態様である。

【0096】

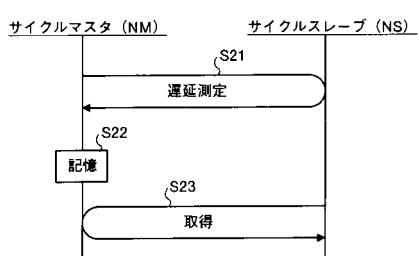

第2の遅延ずれ取得態様は、図7に示すように、サイクルマスターNMが任意のサイクルス

50

レープNSとの間の遅延ずれを測定し(S21)、この遅延ずれをサイクルマスタNMが有する遅延記憶手段に記憶し(S22)、任意のサイクルスレープNSがサイクルマスタNMに対してこの遅延記憶手段をアクセスし、遅延ずれを読み取り(S23)、当該サイクルスレープNSが遅延ずれを取得する態様である。

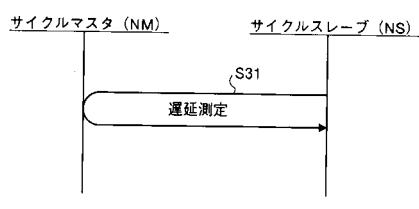

#### 【0097】

第3の遅延ずれ取得態様は、図8に示すように、任意のサイクルスレープNSがサイクルマスタNMとの間の遅延ずれを測定し(S31)、これによって遅延ずれを取得する態様である。

#### 【0098】

この第1～第3の遅延ずれ取得態様によれば、サイクルスレープNSは、サイクルマスタNMのタイマ値に厳密に一致するように補償することができる。 10

#### 【0099】

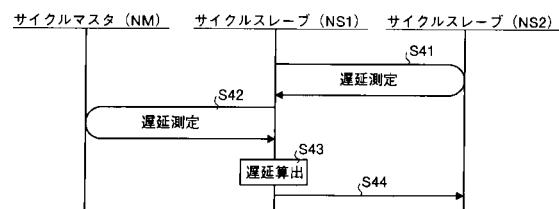

第4の遅延ずれ取得態様は、図9に示すように、ある特定のサイクルスレープNS1が、他の任意のサイクルスレープNS2との間の遅延ずれを測定し(S41)、かつ、サイクルマスタNMとの間の遅延ずれを測定し(S42)、サイクルマスタNMと任意のサイクルスレープNS2との間の遅延を算出し(S43)、この遅延を任意のサイクルスレープNS2に伝える(S44)ことによって、当該任意のサイクルスレープNS2が遅延ずれを取得する態様である。

#### 【0100】

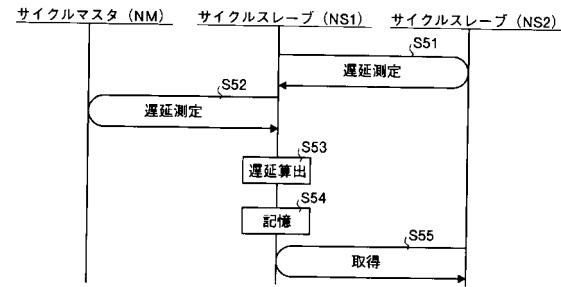

第5の遅延ずれ取得態様は、図10に示すように、ある特定のサイクルスレープNS1が、他の任意のサイクルスレープNS2との間の遅延ずれを測定し(S51)、かつ、サイクルマスタNMとの間の遅延ずれを測定し(S52)、サイクルマスタNMと任意のサイクルスレープNS2との間の遅延を算出し(S53)、この算出した遅延を、特定のサイクルスレープ自身が有する遅延記憶手段に記憶し(S54)、任意のサイクルスレープNS2がこの遅延記憶手段をアクセスしてこの遅延を読み取り(S55)、これによって任意のサイクルスレープNS2が遅延ずれを取得する態様である。 20

#### 【0101】

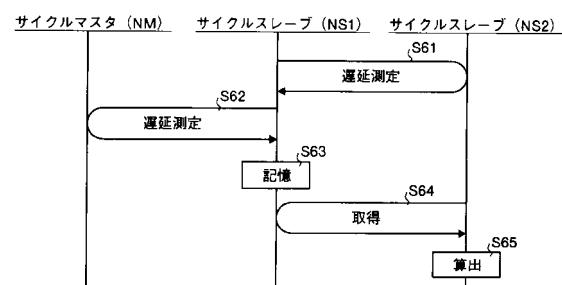

第6の遅延ずれ取得態様は、図11に示すように、ある特定のサイクルスレープNS1が、他の任意のサイクルスレープNS2との間の遅延ずれを測定し(S61)、かつ、サイクルマスタNMとの間の各遅延ずれを測定し(S62)、これらの各遅延を特定のサイクルスレープNS1自身が有する遅延記憶手段に記憶し(S63)、任意のサイクルスレープNS2が特定のサイクルスレープNS1をアクセスしてこれらの遅延を読み取り(S64)、その後サイクルマスタNMとの間の遅延を算出する(S65)態様である。 30

#### 【0102】

上述した第4～第6の遅延ずれ取得態様は、第1～第3の遅延ずれ取得態様と同じ作用効果を有するが、やや複雑な取得態様となっている。

#### 【0103】

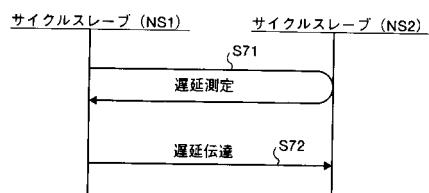

第7の遅延ずれ取得態様は、図12に示すように、ある特定のサイクルスレープNS1が他の任意のサイクルスレープNS2との間の遅延ずれを測定し(S71)、この遅延ずれを当該任意のサイクルスレープNS2に伝送し(S72)、任意のサイクルスレープNS2が遅延ずれを取得する態様である。 40

#### 【0104】

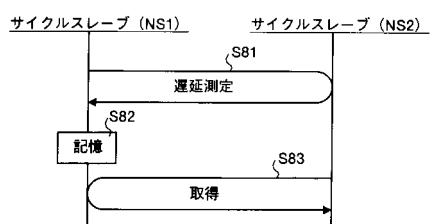

第8の遅延ずれ取得態様は、図13に示すように、ある特定のサイクルスレープNS1が他の任意のサイクルスレープNS2との間の遅延ずれを測定し(S81)、この遅延ずれを特定のサイクルスレープNS1自身が有する遅延記憶手段に記憶し(S82)、任意のサイクルスレープNS2がこの遅延記憶手段にアクセスして遅延ずれを読み取る(S83)ことによって、任意のサイクルスレープが遅延ずれを取得する態様である。

#### 【0105】

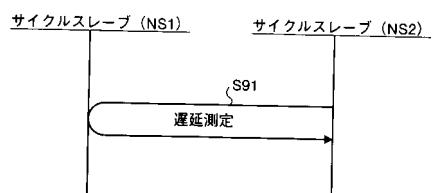

第9の遅延ずれ取得態様は、図14に示すように、任意のサイクルスレープNS2が、ある特定のサイクルスレープNS1との間の遅延ずれを測定し(S91)、これによって任 50

意のサイクルスレープNS2が遅延ずれを取得する態様である。

【0106】

上述した第7～第9の遅延ずれ取得態様によれば、ある特定のサイクルスレープのタイマ値に厳密に一致するように他の任意のサイクルスレープのタイマ値を補償することが可能となる。この場合、同じタイマ値を有していないのはネットワーク上ではサイクルマスターのみとなる。

【0107】

サイクルスレープが自信の有するサイクルタイマ値と、基準となるノード（サイクルマスターの場合もあればサイクルスレープの場合もある）が有するサイクルタイマ値の遅延ずれを、サイクルスレープ自身で知ることができたならば、サイクルスレープ側自身でタイマ遅延を補償することができる。このタイマ遅延補償態様には、つぎの3つの態様がある。以下に説明する3つの態様では、基準となるノードがサイクルマスターの場合について説明しているが、基準となるノードがサイクルスレープの場合でも同様に実施できる。

10

【0108】

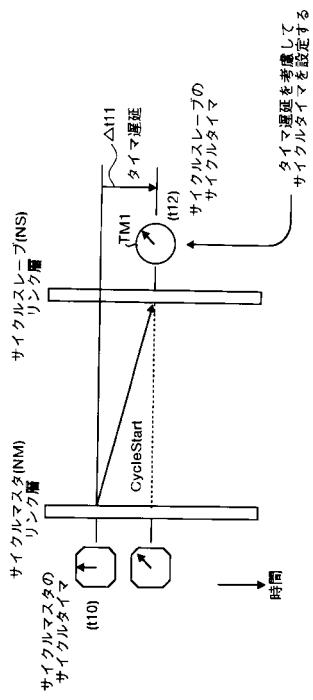

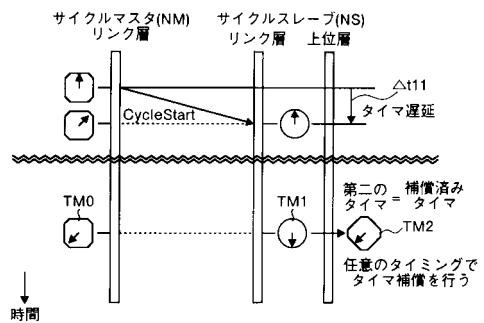

第1のタイマ遅延補償態様は、図15に示されるように、タイマ遅延量  $t_{11}$  を考慮してサイクルタイマTM1のサイクルタイマ値を設定するものである。サイクルマスターNMが、サイクルスレープNSに対し、サイクルスタートパケットによってサイクルマスターNMが有するサイクルタイマ値  $t_{10}$  を伝送した際に、サイクルスレープNS側がこのサイクルスタートパケットを受け取った時にサイクルタイマ値  $t_{10}$  をそのままサイクルスレープNS自身が有するサイクルタイマTM1のサイクルタイマ値  $t_{10}$  と設定せずに、遅延ずれ量  $t_{11}$  を考慮してサイクルタイマ値  $t_{12}$  を設定する。すなわち、

20

$t_{12}$  (設定すべきサイクルタイマ値)

$= t_{10} + t_{11}$  (タイマ遅延量)

となる。

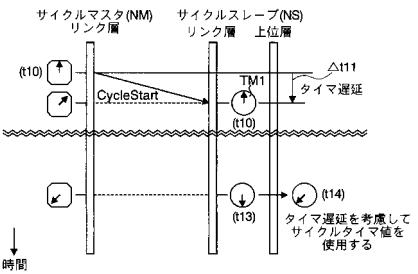

【0109】

第2のタイマ遅延補償態様は、図16に示すように、サイクルスレープNS側がサイクルスタートパケットを受け取った時にサイクルタイマ値  $t_{10}$  をそのまま自サイクルスレープNSが有するサイクルタイマ値  $t_{10}$  として設定する点は、従来のタイマ設定と同じであるが、サイクルスレープNS側の上位層（サイクルスレープ側のアプリケーション）がサイクルタイマ値を使用する、すなわち読みにきた際ににおけるサイクルタイマ値  $t_{13}$  に、遅延ずれ量を補正し、この補正したサイクルタイマ値  $t_{14}$  を上位層が用いるようにする。この場合、遅延ずれ量が予め知っていれば、基本的にいつでもサイクルタイマ値を補償でき、この補正したサイクルタイマ値を用いることができる。すなわち、

30

$t_{14}$  (使用すべきサイクルタイマ値)

$= t_{13} + t_{11}$  (タイマ遅延量)

となる。

【0110】

第3のタイマ遅延補償態様は、図17に示すように、サイクルスレープNSは、サイクルタイマTM1とは別個に第2のサイクルタイマTM2を有する。サイクルタイマTM1には、受け付けたサイクルタイマ値をそのまま設定し、第2のサイクルタイマTM2には、任意のタイミング、たとえば時間的にクリティカルでないときに、タイマ遅延量  $t_{11}$  を加味したタイマ遅延補償されたサイクルタイマ値が設定され、上位層は、このサイクルタイマ値を用いるようにしている。

40

【0111】

この実施の形態3によれば、IEEE1394の仕様（IEEE1394-1995既存の仕様）の範囲内で、各ノードが有するサイクルタイマのタイマ遅延を補償することで、IEEE1394を任意の用途に利用する場合でも、高精度な同期を実現することができる。また、すべてのノードがタイマ補償を必要としている訳ではないので、必要なノードだけが必要に応じて遅延計測補償を行えば良い。さらには、IEEE1394をコントローラとサーボドライバとの間のオープンなインターフェースとして使用した場合でも、

50

コントローラとサーボドライブとの間、あるいはサーボドライブ間同士のタイマ遅延を補償することが可能となり、高速高精度な制御を実現できる。また、タイマ遅延補償はサーボ側で行うので、コントローラ部分に何の変更も必要ない。さらには、すべての被制御機器がタイマ補償を必要としている訳ではないので、必要なサーボノードだけが必要に応じて遅延計測補償を行えば良い。

#### 【0112】

ところで、上述した第1のタイマ遅延補償態様は、単純であり、また、タイマを用いた割込は遅延を補償した時刻における割込となることから、正確である。しかし、IEEEE1394の基幹に関わる部分であるリンク層を変更しなければならない。さらに、IEEEE1394ではサイクルスタートパケットを受け取ってタイマ値を更新する際にタイマ値を戻してはならない、という規約がある。この実施の形態で、サイクルスレーブのサイクルタイマを基準としたならば、遅延ずれが負の値を持ち、タイマ遅延補償をする際にタイマ値を戻すノードが存在する事があるので、このような場合には、IEEEE1394のこの規約を無視するか、あるいは、「基準となるサイクルスレーブのサイクルタイマ値 + 一定時間」をネットワーク上で基準時間として、タイマ遅延補償をする際にタイマ値を戻すノードがないようにして、IEEEE1394のこの規約を守るようにする、などの処置を行う必要がある。また、タイマ遅延補償を行うサイクルスレーブの上位層からみて、タイマがいつ更新されるかがわからない、すなわちサイクルスタートパケットがいつ送られてくるのかわからないため、タイマ遅延補償を行うサイクルスレーブの上位層において、時間を計測している最中など、時間に対してクリティカルな最中にタイマの更新が行われる可能性があり、クリティカルな最中にタイマの更新が行われた場合とそうでない場合とで誤差が生じてしまう。

#### 【0113】

もともと、サイクルマスターが有するサイクルタイマとサイクルスレーブが有するサイクルタイマとは完全に特性が一致するとは限らないので、お互いのサイクルタイマの間に精度の差が存在し、サイクルスタートパケットによってサイクルスレーブのサイクルタイマを、サイクルマスターのサイクルタイマ値に合わせるのは、このサイクルタイマ間の精度差をなくすためである。しかしながら、たとえば、タイマ遅延補償を行うサイクルスレーブの上位層（の任意のアプリケーション）が、何か別の目的で時間計測などを、自身のサイクルタイマを使って行う場合、サイクルタイマの更新が起こらなければ、自身のサイクルタイマの精度の範囲内で、その時間計測の精度は保証されるが、その時間計測の途中でサイクルタイマの更新が起こってしまったら、その時間計測の精度は全く保証されないものになってしまふ。もちろん、この誤差が問題のない範囲でシステムにIEEEE1394を用いるのであれば、この第1のタイマ遅延補償態様はこのシステムに十分である。

#### 【0114】

一方、第2のタイマ遅延補償態様では、IEEEE1394に関わる変更は全くなく、上位層（アプリケーション）のみ変更すれば良いので、容易に実現が可能である。しかしながら、このタイマを使った割込は、遅延を補償したタイマが発生する割込とはならない。この代替手段としてアプリケーションからタイマをポーリングして正確な時刻の割込を実現することも可能である。ただし、ポーリングによる負荷が生じることになる。さらに、第1のタイマ遅延補償態様と同様に、サイクルタイマ値の更新がいつ起こるか判らないことによる、タイマの精度の保証の問題が残る。ポーリングによる負荷や、タイマ更新に関わる誤差が問題ない範囲で用いるシステムに適用するのであれば、この第2のタイマ遅延補償態様は、十分用いることができる。

#### 【0115】

また、第3のタイマ遅延補償態様では、第1および第2のタイマ遅延補償態様で問題となっていたタイマ更新に関わる誤差の保証問題を解決することができる。この第3のタイマ遅延保証態様では、サイクルタイマ値にタイマ遅延量を考慮したサイクルタイマ値を、第2のサイクルタイマに第2のサイクルタイマ値として設定するタイミングを任意とすることができるため、タイマ遅延量  $t$  を計測している最中など、時間にクリティカルな時間

10

20

30

40

50

帶を避けたタイミングでタイマ値を設定することができる。また、このタイマを使った割込は、遅延を補償した時刻における割込であるから、正確である。したがって、この第3のタイマ遅延補償態様によるタイマ遅延補償が最も好ましいといえる。

【0116】

実施の形態4.

つぎに、この発明の実施の形態4について説明する。この実施の形態4では、上述した実施の形態1, 2に示したタイマ遅延の測定などを用いてタイマ遅延を測定しておき、このタイマ遅延およびタイムスタンプを用いてタイマ遅延補償を行うようにしている。

【0117】

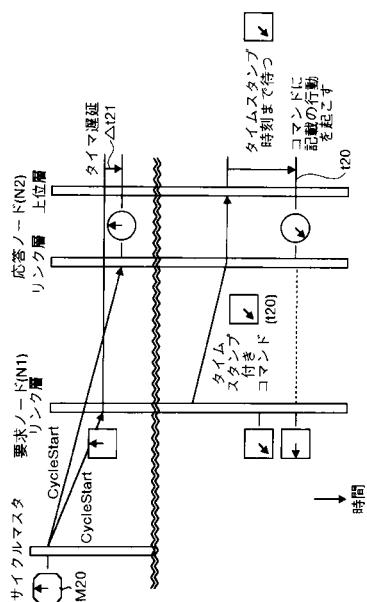

図18は、タイムスタンプを用いて制御を行う同期システムの概要を示す図である。図18において、要求ノードN1と応答ノードN2とによる同期をとる場合、たとえばコントローラと各サーボドライバによる同期制御を行う場合、ある時刻において同期を取る、すなわち同期制御を行う必要があるが、このような場合には、コマンド内容(制御内容)とともに、このコマンド内容(制御内容)が行われるべき時刻をタイムスタンプとして、要求ノードN1から応答ノードN2に対して送られる。要求ノードN1がコントローラであり、応答ノードN2が各サーボドライバである場合には、コントローラから各サーボドライバに対してタイムスタンプが送られる。応答ノードN2は、受け取った時刻、すなわちタイムスタンプの時刻(タイムスタンプ値)  $t_{20}$ になると、受け取ったコマンド内容(制御内容)を実行する。

【0118】

しかしながら、応答ノードN2の時刻は、応答ノードN2自身が有するサイクルタイマによるものであるから、応答ノードN2と要求ノードN1との間に遅延が存在する。応答ノードN2が要求ノードN1からタイムスタンプ値を受け付けると、応答ノードN2は、遅延ずれを補償する。なお、この場合、各応答ノードN2は、各応答ノードN2が有するサイクルタイマ値と、要求ノードN1が有するサイクルタイマ値との遅延ずれを予め知っている必要がある。この遅延ずれを、タイムスタンプを用いて補償する態様には、つぎの2つの態様がある。

【0119】

第1のタイムスタンプによるタイマ遅延補償態様は、まず要求ノードN1が、任意の応答ノードN2との間の遅延ずれを測定し、この遅延を任意の応答ノードN2に伝達する。応答ノードN2が遅延ずれ量を予め取得する態様には、つぎの3つの態様がある。

【0120】

第1の取得態様は、図6に示した第1の遅延ずれ取得態様と同様に、要求ノードN1が任意の応答ノードN2との間の遅延ずれを測定し、この遅延ずれを当該任意の応答ノードN2に伝える態様である。

【0121】

第2の取得態様は、図7に示した第2の遅延ずれ取得態様と同様に、要求ノードN1が任意の応答ノードN2との間の遅延ずれを測定し、要求ノードN1自身が有する遅延記憶手段に記憶し、任意の応答ノードN2が要求ノードN1の遅延記憶手段にアクセスし、この遅延ずれを読み取り、当該任意の応答ノードN2が遅延ずれを取得する態様である。

【0122】

第3の取得態様は、図8に示した第3の遅延ずれ取得態様と同様に、任意の応答ノードN2が要求ノードN1との間の遅延ずれを測定し、これによって、遅延ずれを取得する態様である。

【0123】

その後、図19に示すように、要求ノードN1から応答ノードN2に対して、コマンド内容(制御内容)とともに、このコマンド内容(制御内容)が行われるべき時刻であるタイムスタンプ値  $t_{20}$  が応答ノードに送られてくると、応答ノードN2は、受け取った時刻、すなわちタイムスタンプ値  $t_{20}$  に対して遅延ずれ量  $T_{21}$  を補償し、この補償したタイムスタンプ値  $t_{22}$  が示す時刻になると、受け取ったコマンド内容(制御内容)を実

10

20

30

40

50

行する。

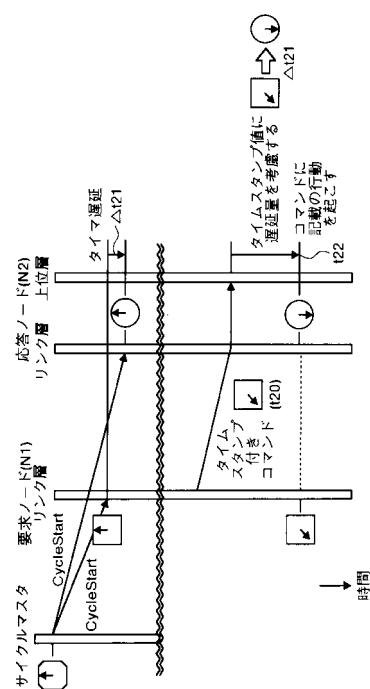

【0124】

一方、第2のタイムスタンプによるタイマ遅延補償態様では、要求ノードN1が各応答ノードN2の遅延ずれ量  $t_{21}$ をそれぞれ考慮したタイムスタンプを発行する。この場合は、要求ノードN1は、要求ノードN1自身が有するサイクルタイマ値と各応答ノードが有するサイクルタイマ値との遅延ずれ量  $t_{21}$ を予め知っている必要がある。この遅延ずれ量を取得する態様としては、つきの3つの態様がある。

【0125】

その第1の取得態様は、要求ノードN1が各応答ノードN2との間の遅延を測定し、要求ノードN1自身が有するデータテーブル形式の遅延量記憶手段に記憶しておく。

10

【0126】

第2の取得態様は、各応答ノードN2が、要求ノードN1との間の遅延ずれ量  $t_{21}$ を測定し、この遅延ずれ量  $t_{21}$ を応答ノードN2自身の遅延量記憶手段に記憶しておく、要求ノードN1が、応答ノードN2の遅延量記憶手段に記憶された遅延ずれ量を読み取る。

【0127】

第3の取得態様は、各応答ノードN2が、要求ノードN1との間の遅延ずれ量を測定し、この遅延ずれ量を要求ノードN1に伝える。

【0128】

その後、図20に示すように、要求ノードN1は、制御内容とともに、この制御内容が行われるべき時刻であるタイムスタンプ値  $t_{20}$ を、各応答ノードN2の遅延ずれ量を考慮して、遅延ずれ量  $t_{21}$ 分だけ時刻を戻して設定し、要求ノードN1から各応答ノードN2に対して送る。これに対し、応答ノードN2側は、受け取ったタイムスタンプ値  $t_{22}$ が示す時刻になると、受け取った制御内容を実行する。この場合、受け取ったタイムスタンプ値  $t_{22}$ は、既に遅延ずれ量を考慮した値となっているので、そのまま制御内容を実行すればよい。

20

【0129】

この実施の形態4によれば、IEEE1394の仕様(IEEE1394-1995既存の仕様)の範囲内で、各ノードが有するサイクルタイマのタイマ遅延を補償することで、IEEE1394を任意の用途に利用する場合でも、高精度な同期を実現することが可能である。また、すべてのノードがタイマ補償を必要としている訳ではないので、必要なノードだけが必要に応じて遅延計測補償を行えば良い。さらには、IEEE1394をコントローラとサーボドライバとの間のオープンなインタフェースとして使用した場合でも、コントローラとサーボドライブとの間、あるいはサーボドライブ間同士のタイマ遅延を補償することが可能となり、高速高精度な制御を実現できる。また、タイマ遅延補償はサーボ側で行うので、コントローラ部分に何の変更も必要ない。さらには、すべての被制御機器がタイマ補償を必要としている訳ではないので、必要なサーボノードだけが必要に応じて遅延計測補償を行えば良い。

30

【0130】

実施の形態5。

40

つぎに、この発明の実施の形態5について説明する。この実施の形態5では、上述した実施の形態1~4で示したIEEE1394を、コントローラとサーボドライバとの間のオープンなインタフェースとして使用した場合について説明する。

【0131】

ここで、コントローラをサイクルスレーブとし、被制御対象機器であるサーボドライバをサイクルスレーブとし、被制御対象機器のサーボドライバの1つを、サイクルマスターとしてもよいが、コントローラをサイクルマスターとし、被制御対象機器のサーボドライバの全てをサイクルスレーブとすることが好ましい。

【0132】

コントローラは、サーボドライバに対してIsochronousパケットによるサーボデータなど

50

のデータを送出し、サーボドライバは、コントローラに対してIsochronousパケットによるフィードバックデータなどを返送する。この場合、コントローラがサイクルマスタであれば、Isochronous転送時間帯の中で、コントローラの制御パケットを先に優先し、すなわちIsochronousパケットの先頭に位置させて送出することができる。

#### 【0133】

上述した実施の形態1～4を適宜組み合わせ、コントローラとサーボドライバとのタイム遅延計測補償を行ってもよいが、ここでは、タイム遅延の計測に関する一連の動作をコントローラが管理し、タイム遅延の補償をサーボドライバ側が行う場合のタイム遅延補償処理シーケンスについて説明する。

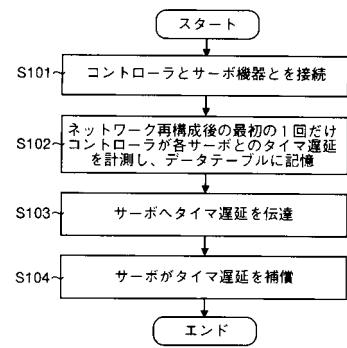

#### 【0134】

図21は、タイム遅延の補償をサーボドライバ側が行う場合におけるタイム遅延補償処理手順を示すフローチャートである。図21において、まず、サーボドライバをコントローラに接続する(ステップS101)。その後、コントローラが有するネットワーク構成変化判別手段が、ネットワークの構成が変化したことを検出し、ネットワーク再構成後に1回だけ、コントローラが各サーボドライバとの間のタイム遅延を計測し、このタイム遅延量を、コントローラ自身が有するデータテーブルに記憶する(ステップS102)。

#### 【0135】

その後、コントローラは、各サーボドライバにタイム遅延量を伝達し(ステップS103)、このタイム遅延量を受けたサーボドライバは、このタイム遅延量をもとにタイム遅延を補償し(ステップS104)、本処理を終了する。

#### 【0136】

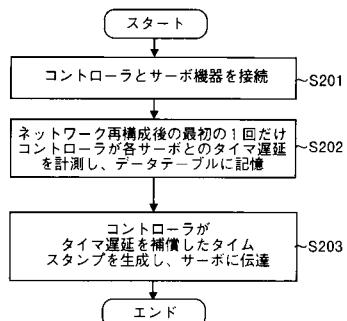

つぎに、コントローラが遅延補償したタイムスタンプを生成する場合のタイム遅延補償処理シーケンスについて説明する。図22は、コントローラが遅延補償したタイムスタンプを生成する場合の遅延補償処理手順を示すフローチャートである。図22において、まず、ステップS101と同様に、サーボドライバをコントローラに接続する(ステップS201)。その後、コントローラが有するネットワーク構成変化判別手段が、ネットワークの構成が変化したことを検出し、ネットワーク再構成後に1回だけ、コントローラが各サーボドライバとの間のタイム遅延を計測し、このタイム遅延量を、コントローラ自身が有するデータテーブルに記憶する(ステップS202)。その後、コントローラは、タイム遅延量を補償したタイムスタンプを生成してサーボドライバ側に伝達し(ステップS203)、本処理を終了する。

#### 【0137】

この実施の形態5では、コントローラとサーボドライバとからなる制御システムのように、高速高精度の同期を必要とするシステムであっても、コントローラとサーボドライバとの間にオープンなインターフェースであるIEEE1394を使用して、コントローラとサーボドライバとの間のタイム遅延補償を確実かつ精度良く行うことができる。

#### 【0138】

##### 【発明の効果】

以上説明したように、この発明によれば、IEEE1394を用いて接続されたネットワーク内の各ノード間の同期をとる際、サイクルタイム遅延計測手段が、前記各ノードが有する各サイクルタイム同士の遅延ずれ量を計測し、サイクルタイム遅延補正手段が、前記サイクルタイム遅延計測手段が計測した遅延ずれ量をもとに前記各サイクルタイム同士の遅延ずれを補正するようにしているので、IEEE1394の仕様の範囲内で、各ノードが有するサイクルタイムのサイクルタイム同士のタイム遅延が補償され、高速高精度な同期制御が可能なシステムを実現することができるという効果を奏する。また、前記サイクルタイム遅延計測手段が、要求ノードから応答ノードに対してReadパケットを送信し、該応答ノードのサイクルタイム値を読み取り、この読み取ったサイクルタイム値を含むReadResponseパケットを前記要求ノードが受信し、この受信したサイクルタイム値と要求ノードのサイクルタイム値との差をもとに前記遅延ずれ量を算出するようにしているので、サイクルタイム値を読み取ることによって容易にサイクルタイム同士の遅延ずれ量を得る

10

20

30

40

50

ことができるという効果を奏する。

【0144】

つぎの発明によれば、前記要求ノードの判定手段が、前記Readパケットを送信し、前記ReadResponseパケットが返送される一連のシーケンスが、同一のアシンクロナス転送が行われている時間帯である同一のAsynchronous転送時間帯で完了するか否かを判定し、前記要求ノードが、前記判定手段が同一のAsynchronous転送時間帯で完了すると判定した場合に、Readパケットを前記応答ノードに送出するようにし、ReadResponseパケットが同一のAsynchronous転送時間帯内で返送されるようにしているので、信頼度の高い遅延ずれ量を計測することができるという効果を奏する。

【0145】

10

つぎの発明によれば、前記応答ノードの上位層の判定手段が、アシンクロナス転送が行われている時間帯であるAsynchronous転送時間帯であるか否かを判定し、前記判定手段がAsynchronous転送時間帯であると判定した場合に、前記上位層は前記ReadResponseパケットを送信バッファ (TX\_FIFO) に蓄えることで、前記ReadResponseパケットは、送信バッファ長くとどまることなく、直ちに要求ノードに返送されるようにしているので、信頼度の高い遅延ずれ量を計測することができるという効果を奏する。

【0146】

つぎの発明によれば、前記応答ノードのリンク層の書き込み手段が、前記ReadResponseパケットがリンク層バッファから送出される直前に該ReadResponseパケットに当該応答ノードのサイクルタイム値を書き込むようにしているので、信頼度の高い遅延ずれ量を計測することができるという効果を奏する。

20

【0147】

つぎの発明によれば、各ノードのサイクルタイム遅延記憶手段が、前記遅延ずれ量を記憶し、少なくとも他のノードからのアクセスによって遅延ずれ量を獲得できるようにしているので、効率的な遅延ずれ量の取得を可能にするという効果を奏する。

【0148】

つぎの発明によれば、前記サイクルタイム遅延記憶手段が、全てのノード間の遅延ずれ量をデータテーブル形式で記憶するようにしているので、遅延ずれ量の取得を迅速に行うことができるという効果を奏する。

【0149】

30

つぎの発明によれば、前記サイクルタイム遅延記憶手段を、サイクルマスタとしてのノードに設けるようにしているので、効率的な遅延ずれ量の管理を行うことができるという効果を奏する。

【0150】

つぎの発明によれば、ネットワーク構成変化判別手段が、前記ネットワークの構成の変化を判別し、前記ネットワーク構成変化判別手段がネットワークの構成に変化があったと判別した場合、該ネットワークの再構成後、前記サイクルタイム遅延計測手段がサイクルタイム同士の遅延ずれ量を計測し、前記サイクルタイム遅延補正手段が該遅延ずれ量をもとにサイクルタイム同士の遅延ずれを補正する処理を行なうようにしているので、ネットワークのトラヒックに影響を与えることなく、しかも正確かつ確実な遅延ずれ量の計測および補正を行うことができるという効果を奏する。

40

【0151】

つぎの発明によれば、前記ネットワーク構成変化判別手段を、サイクルマスタとしてのノードに設けるようにしているので、迅速かつ効率的な遅延ずれの計測および補正を行うことができるという効果を奏する。

【0152】

つぎの発明によれば、前記サイクルタイム遅延計測手段および前記サイクルタイム遅延補正手段を、ノード間の同期を用いる所定のノードに設けるようにしているので、ノード間の同期を必要とするノードが確実に遅延ずれ量を計測し、補正することができるという効果を奏する。

50

**【 0 1 5 3 】**

つぎの発明によれば、同期の基準となるサイクルタイマを有するサイクルマスタのノードが、該ノードが計測した遅延ずれ量を前記サイクルタイマ遅延伝送手段によって前記所定のノードに伝送し、あるいは該ノードが計測した遅延ずれ量をデータテーブルに記憶し、前記所定のノードが前記サイクルマスタのノードから該遅延ずれ量を取得し、その後所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに該ノードのサイクルタイマの遅延ずれを補正するようにしているので、遅延ずれ量およびその補正を確実に行うことができるという効果を奏する。

**【 0 1 5 4 】**

つぎの発明によれば、前記サイクルタイマ遅延補正手段が、サイクルスタートパケットを受信した際に、遅延ずれ量をもとにサイクルタイマ値を設定するようにしているので、同期がとれた制御処理を確実に行うことができるという効果を奏する。 10

**【 0 1 5 5 】**

つぎの発明によれば、前記サイクルタイマ遅延補正手段が、上位層がサイクルタイマ値の使用時に、前記遅延ずれ量を用いて遅延ずれを補正するようにしているので、適時に、遅延ずれ量が補正された時刻を用いて制御処理を行うことができ、遅延ずれ量の補正時期の不一致による不具合を解消することができるという効果を奏する。

**【 0 1 5 6 】**

つぎの発明によれば、所定のノードの前記サイクルタイマ遅延補正手段が、任意のタイミングで遅延ずれ量を用いて前記遅延ずれを補正したサイクルタイマ値を第2のサイクルタイマに設定するようにしているので、適時に、遅延ずれ量が補正された時刻を用いて制御処理を行うことができ、遅延ずれ量の補正時期の不一致による不具合を解消することができるという効果を奏する。 20

**【 0 1 5 7 】**

つぎの発明によれば、前記サイクルタイマ遅延補正手段が、前記遅延ずれ量をもとに、前記サイクルマスタのノードから送られた前記タイムスタンプのタイムスタンプ値を更新し、前記タイムスタンプ時刻監視手段が、前記更新されたタイムスタンプ値が示す時刻を監視するようにしているので、タイムスタンプを用いた遅延ずれ量の補正を確実に行うことができるという効果を奏する。

**【 0 1 5 8 】**

つぎの発明によれば、前記サイクルタイマ遅延計測手段および前記サイクルタイマ遅延補正手段を、サイクルマスタとしてのノードに設けるようにしているので、効率的なサイクルタイマ同士の遅延ずれ量の計測および補正を行うことができるという効果を奏する。 30

**【 0 1 5 9 】**

つぎの発明によれば、前記所定のノードが、該所定のノードで計測した遅延ずれ量を前記サイクルマスタのノードに伝送し、あるいは前記所定のノードから遅延ずれ量を取得し、その後該所定のノードに伝送された遅延ずれ量あるいは取得した遅延ずれ量をもとに前記サイクルマスタのノードのサイクルマスタの遅延ずれを補正するようにしているので、遅延ずれ量およびその補正を確実に行うことができるという効果を奏する。

**【 0 1 6 0 】**

つぎの発明によれば、前記サイクルタイマ遅延補正手段が、前記遅延ずれ量をもとに、自サイクルマスタのノードの前記タイムスタンプ生成手段が生成したタイムスタンプのタイムスタンプ値を更新し、この更新したタイムスタンプ値を含むデータを所定のノードに伝送するようにしているので、タイムスタンプを用いた遅延ずれ量の計測および補正を効率的かつ確実に行うことができるという効果を奏する。 40

**【 0 1 6 1 】**

つぎの発明によれば、請求項1～23のいずれか一つに記載したIEEE1394を用いた同期システムを、サーボドライブ装置とこれを制御するコントローラとからなる制御システムに適用しているので、高速高精度の同期制御を確実に行うことができるという効果を奏する。 50

## 【0162】

つきの発明によれば、前記コントローラを、サイクルマスタとし、効率的な遅延ずれ量の計測および補正ができるようにしているので、高速高精度の同期制御が可能な制御システムを実現することができるという効果を奏する。

## 【図面の簡単な説明】

【図1】 この発明の実施の形態1であるI E E E 1 3 9 4を用いた同期システムにおける伝送遅延測定の処理シーケンスを示す図である。

【図2】 I E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの概要を示す図である。

【図3】 この発明の実施の形態2であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。 10

【図4】 この発明の実施の形態2であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図5】 この発明の実施の形態2であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図6】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図7】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図8】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図9】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図10】 遅延ずれの取得処理シーケンスの一例を示す図である。 20

【図11】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図12】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図13】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図14】 遅延ずれの取得処理シーケンスの一例を示す図である。

【図15】 この発明の実施の形態3であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図16】 この発明の実施の形態3であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図17】 この発明の実施の形態3であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。 30

【図18】 この発明の実施の形態4であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図19】 この発明の実施の形態4であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図20】 この発明の実施の形態4であるI E E E 1 3 9 4を用いた同期システムにおけるタイマ遅延補償の処理シーケンスの一例を示す図である。

【図21】 この発明の実施の形態5であるI E E E 1 3 9 4を用いた同期システムを、コントローラと1以上のサーボドライブとからなる制御システムに適用した場合における遅延ずれ補正処理手順の一例を示すフローチャートである。

【図22】 この発明の実施の形態5であるI E E E 1 3 9 4を用いた同期システムを、コントローラと1以上のサーボドライブとからなる制御システムに適用した場合における遅延ずれ補正処理手順の一例を示すフローチャートである。 40

【図23】 I E E E 1 3 9 4の通信レイヤの構成を示す図である。

【図24】 Isochronous通信とAsynchronous通信とが混在する場合を示す図である。

【図25】 サイクルスタートパケットを用いたサイクルマスタとサイクルスレーブとの間におけるタイマ同期処理を示すシーケンス図である。

【図26】 サイクルスタートパケットを用いたサイクルスレーブ間のタイマ同期処理を示すシーケンス図である。

## 【符号の説明】

1, 2 判定部、3 書込部、N1 要求ノード、N2 応答ノード、NM サイクルマ 50

スタ、NS, NS1, NS2 サイクルスレーブ、TM2 第2のサイクルタイマ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 10】

【図 9】

【図 11】

【図 12】

【図 14】

【図 13】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【 図 25 】

【図26】

---

フロントページの続き

(72)発明者 牛尾 裕介

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 羽岡 さやか

(56)参考文献 特開2000-078170 (JP, A)

特表平09-502851 (JP, A)

特開平09-046390 (JP, A)

特開平09-233098 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 12/28-12/46

H04L 7/00