(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-516301

(P2016-516301A)

(43) 公表日 平成28年6月2日(2016.6.2)

| (51) Int.Cl.                  | F 1        | テーマコード (参考) |       |

|-------------------------------|------------|-------------|-------|

| <b>H01L 21/8238 (2006.01)</b> | H01L 27/08 | 321D        | 5F048 |

| <b>H01L 27/092 (2006.01)</b>  | H01L 29/78 | 301R        | 5F140 |

| <b>H01L 21/336 (2006.01)</b>  | H01L 29/78 | 301X        |       |

| <b>H01L 29/78 (2006.01)</b>   | H01L 27/08 | 331A        |       |

| <b>H01L 27/08 (2006.01)</b>   |            |             |       |

審査請求 未請求 予備審査請求 有 (全 23 頁)

|               |                              |          |                                                                                        |

|---------------|------------------------------|----------|----------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2016-500931 (P2016-500931) | (71) 出願人 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン デイエゴ モアハウス ドラ<br>イブ 5775 |

| (86) (22) 出願日 | 平成26年3月10日 (2014.3.10)       | (74) 代理人 | 100108453<br>弁理士 村山 靖彦                                                                 |

| (85) 翻訳文提出日   | 平成27年9月2日 (2015.9.2)         | (74) 代理人 | 100163522<br>弁理士 黒田 晋平                                                                 |

| (86) 國際出願番号   | PCT/US2014/022263            | (72) 発明者 | ビン・ヤン<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775                         |

| (87) 國際公開番号   | W02014/159160                |          |                                                                                        |

| (87) 國際公開日    | 平成26年10月2日 (2014.10.2)       |          |                                                                                        |

| (31) 優先権主張番号  | 13/799,955                   |          |                                                                                        |

| (32) 優先日      | 平成25年3月13日 (2013.3.13)       |          |                                                                                        |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                        |

最終頁に続く

(54) 【発明の名称】ダミーゲートで分割された連続活性領域を有する金属酸化物半導体(MOS)分離方式および関連する方法

## (57) 【要約】

詳細な説明に開示された実施形態は、ダミーゲートで区切られた連続活性領域を有する金属酸化物半導体(MOS)分離方式を含む。MOSデバイスは、n型金属またはp型金属のいずれかとして記載される仕事関数を有する材料から形成された活性領域を備える。能動部品は、同じ仕事関数を有する材料を使用し、この活性領域上に形成される。能動部品の間にダミーゲートを配置することによって、分離がなされる。ダミーゲートは、活性領域の材料に対して逆の仕事関数を有する材料から作られる。たとえば、活性領域がp型金属材料の場合、ダミーゲートは、n型金属から作られ、逆もまた同様に可能である。

FIG. 5

**【特許請求の範囲】****【請求項 1】**

第1のn型金属またはp型金属の仕事関数を有する第1の材料と、

前記第1の材料を含む第1のゲートと、

前記第1の材料を含む第2のゲートと、

前記第1のゲートと前記第2のゲートとの間に位置し、前記第1の材料とは逆の仕事関数を有する第2の材料を含むダミーゲートと、

各ゲートの下に位置し、約18よりも大きい誘電率(k)を有するゲート誘電体と

を備える、金属酸化物半導体(MOS)デバイス。

**【請求項 2】**

10

前記第1の材料が、n型金属の仕事関数を有する材料を含む、請求項1に記載のMOSデバイス。

**【請求項 3】**

前記第2の材料が、p型金属の仕事関数を有する材料を含む、請求項2に記載のMOSデバイス。

**【請求項 4】**

前記第1の材料が、p型金属の仕事関数を有する材料を含む、請求項1に記載のMOSデバイス。

**【請求項 5】**

20

前記第2の材料が、n型金属の仕事関数を有する材料を含む、請求項4に記載のMOSデバイス。

**【請求項 6】**

相補型MOSデバイス(CMOS)を形成するための第2のMOSデバイスをさらに備え、前記第2のMOSデバイスが、

前記第2の材料を含む第3のゲートと、

前記第2の材料を含む第4のゲートと、

前記第3のゲートと前記第4のゲートとの間に位置し、前記第2の材料を含む第2のダミーゲートと

を備える、請求項1に記載のMOSデバイス。

**【請求項 7】**

30

前記第1のMOSデバイスと前記第2のMOSデバイスとの間に浅溝分離構造(STI)をさらに含む、請求項6に記載のMOSデバイス。

**【請求項 8】**

前記ダミーゲートは、前記ゲート誘電体上に配置され、前記ダミーゲート下に分離埋込ゾーンがない、請求項1に記載のMOSデバイス。

**【請求項 9】**

前記MOSデバイスは、実質的に平面状のデバイスである、請求項1に記載のMOSデバイス。

**【請求項 10】**

40

前記MOSデバイスは、フィンベースの電界効果トランジスタ(FinFET)デバイスである、請求項1に記載のMOSデバイス。

**【請求項 11】**

前記MOSデバイスは、半導体ダイに集積される、請求項1に記載のMOSデバイス。

**【請求項 12】**

前記MOSデバイスが組み込まれた、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定位置データユニット、モバイルロケーションデータユニット、移動電話、携帯電話、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、パーソナルデジタルアシスタント(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、携帯音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビ

50

デオディスク( D V D )プレーヤ、携帯デジタルビデオプレーヤからなる群から選択されたデバイスをさらに含む、請求項 1 に記載の M O S デバイス。

**【請求項 1 3】**

第 1 の n 型金属または p 型金属の仕事関数を有するための第 1 の手段と、

前記第 1 の手段を含む第 1 のゲート手段と、

前記第 1 の手段を含む第 2 のゲート手段と、

前記第 1 のゲート手段と前記第 2 のゲート手段との間に位置し、前記第 1 の手段とは逆の仕事関数を有するための第 2 の手段を含むダミーゲート手段と、

各ゲート手段の下に位置し、約 18 よりも大きい誘電率( k )を有するゲート誘電体と

を備える、金属酸化物半導体( M O S )デバイス。

10

**【請求項 1 4】**

第 1 の n 型金属または p 型金属の仕事関数を有する第 1 の材料を提供するステップと、

活性領域上に、約 18 よりも大きい誘電率( k )を有するゲート誘電体を形成するステ

ップと、

前記ゲート誘電体上に前記第 1 の材料を含む第 1 のゲートを形成するステップと、

前記ゲート誘電体上に前記第 1 の材料を含む第 2 のゲートを形成するステップと、

前記ゲート誘電体上に、前記第 1 の材料とは逆の仕事関数を有する第 2 の材料を含むダ

ミーゲートを形成するステップと、

前記第 1 のゲートと前記第 2 のゲートとの間に、前記第 1 の材料とは逆の仕事関数を有

する第 2 の材料を含む前記ダミーゲートを配置するステップと

20

**【請求項 1 5】**

前記ダミーゲートを形成するステップは、分離埋込ゾーンが存在しない位置に前記ダミ

ーゲートを形成するステップを含む、請求項 1 4 に記載の方法。

**【請求項 1 6】**

前記ゲート誘電体を形成するステップは、約 20 ~ 25 の誘電率を有する前記ゲート誘

電体を形成するステップを含む、請求項 1 4 に記載の方法。

**【請求項 1 7】**

前記第 1 の材料は n 型金属の仕事関数を有する材料を含み、前記第 2 の材料は p 型金属

の仕事関数を有する材料を含む、請求項 1 4 に記載の方法。

30

**【請求項 1 8】**

前記第 2 のゲートを接地するステップをさらに含む、請求項 1 7 に記載の方法。

**【請求項 1 9】**

前記第 2 のゲートの近くにソースを形成するステップをさらに含む、請求項 1 7 に記載

の方法。

**【請求項 2 0】**

前記第 1 の材料が p 型金属の仕事関数を有する材料を含み、前記第 2 の材料が n 型金属

の仕事関数を有する材料を含む、請求項 1 4 に記載の方法。

**【請求項 2 1】**

電圧ソースに前記第 2 のゲートを接続するステップをさらに含む、請求項 2 0 に記載の

方法。

40

**【請求項 2 2】**

前記第 2 のゲートの近くにソースを形成するステップをさらに含む、請求項 2 0 に記載

の方法。

**【請求項 2 3】**

C M O S デバイスを形成するために、前記第 1 の M O S デバイスとともに第 2 の M O S

デバイスを形成するステップをさらに含む、請求項 1 4 に記載の方法。

**【請求項 2 4】**

前記第 2 の M O S デバイスを形成するステップは、前記第 2 の M O S デバイス内にダミ

ーゲートを形成するステップを含む、請求項 2 3 に記載の方法。

50

**【発明の詳細な説明】****【技術分野】****【0001】****優先権出願**

本願は、2013年3月13日に出願された米国特許出願第13/799,955号、名称「METAL OXIDE SEMICONDUCTOR (MOS) ISOLATION SCHEMES WITH CONTINUOUS ACTIVE AREA S SEPARATED BY DUMMY GATES AND RELATED METHODS」の優先権を主張するものであり、その全体は参照により本明細書に組み込まれる。

10

**【0002】**

本開示の技術は、金属酸化物半導体(MOS)に関する。

**【背景技術】****【0003】**

モバイル通信デバイスは、現在の社会において一般的になっている。これらのモバイルデバイスの普及は、1つには現在このようなデバイスで可能な多くの機能のためである。このような機能に対しての需要のため、処理能力の要求が増え、より強力な電池の必要性が生じている。電池は、モバイル通信デバイスの筐体の限られた空間内で、処理回路と競合する状態にある。これらの要因、およびその他の要因が、継続的な回路内の部品の小型化および電力消費の低減の一因となっている。部品の小型化は、金属酸化物半導体(MOS)を含む処理回路のトランジスタやその他のリアクタンス素子を含む処理回路のすべての面に影響を与える。

20

**【0004】**

歴史的に、MOSデバイスは、小型化の努力の恩恵を受けている。たとえば、0.25マイクロメートル( $\mu\text{m}$ )スケールから、0.13 $\mu\text{m}$ から28ナノメートル(nm)のスケールまで縮小し、現在の取り組みでは20nmスケールに挑んでいる。このような半導体の小型化により、集積回路(IC)内のMOSデバイスによる占有設置面積が縮小されただけでなく、このようなICを作動するために必要な電力を低減し、同時に作動速度も改善された。MOSデバイスが、ナノメートルスケール、たとえば、90nmのスケールに縮小されると、IC内のMOSデバイスによる占有設置面積が予想どおり減少した。しかし、移動度は電流機構の有効質量の関数であるので、電流機構(すなわち、電子または孔)の移動度は、直線的に改善しなかったため、また、有効質量は小型化に伴って変化しなかったため、MOSデバイスは、目に見えて速い速度では動作できなかった。

30

**【0005】**

さらに、既存のMOSデバイスは、望むデバイス間の分離を得るために、能動素子間の浅溝分離構造(STI)に依存していた。しかし、小型化がナノメートルスケールに達するとSTIがIC内の貴重なスペースを占有してしまう。

**【0006】**

ナノメートルスケールでMOSデバイスが動作する速度を改善しようと、様々な技術が実施してきた。一例は、電流機構の移動度を向上させるためにMOSチャネル素子上に応力を導入する工程を含む。応力誘導要素は、ストレスを与えるストレッサの物理的大きさに依存する。つまり、移動度を向上させる大きい応力を導入するために、物理的に大きいストレッサが使用されているが、これは小型化の目的と矛盾する。さらに、STIはストレッサの形成に障害となり、所望のストレスを与えるのに利用可能なストレッサの物理的寸法を低減する。

40

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

少なくとも、ストレス誘導要素の縮小に伴う性能の低下を回避するために提案されている解決策の1つは、連続活性領域でのSTI遮断をなくすことである。STI遮断の代わ

50

りに、ダミーゲートが部品の間に挿入されている。しかし、このようなダミーゲートによる分離はSTIによる分離よりも悪く、加えて/あるいは、より高いゲートバイアスを必要とするため、今度は、パワーレールを必要とするといった独自の問題点があり、コストが増大し、デバイスの設置面積を増大させる。このように、隣接するMOSデバイスが劣化することなく動作することができるような効果的な分離技術が必要である。

#### 【課題を解決するための手段】

##### 【0008】

詳細な説明に開示された実施形態は、ダミーゲートで分割された連続活性領域を有する金属酸化物半導体(MOS)分離方式を含む。関連する方法も開示されている。例示的な実施形態では、MOSデバイスは、n型金属またはp型金属のいずれかとして記載されている仕事関数を有する材料から形成されたゲートを有する活性領域を含む。能動部品は、同じ仕事関数を有するゲート材料を使用して、この活性領域上に形成されている。能動部品の間にダミーゲートを配置することによって、分離がなされる。ダミーゲートは、活性領域のゲート材料に対して逆の仕事関数を有する材料から作られる。たとえば、活性領域内のゲートがp型金属材料であった場合、ダミーゲートは、n型金属から作られ、逆もまた同様である。この構造によって達成される分離方式は、効果的にリーク電流の量を低減し、MOS素子の動作速度を向上させる。この分離方式はまた、MOSデバイスが、浅溝分離構造(STI)の幅とリーク電流に制限されることなく、MOSデバイスの技術のスケーリングから予想される対応速度の増加を実現しながら小型化を可能にする。ポリゲートMOS素子とは異なり、本明細書に開示された特定の実施形態のゲート絶縁膜は、比較的高い誘電率( $k$ )を有するため、ダミーゲート下に配置される分離埋込ゾーンの必要性を回避しつつ、逆仕事関数型ダミーゲートが所望の分離をするのを可能にする。

10

20

30

##### 【0009】

この点に関して、ある実施形態で、1つのMOSデバイスが開示されている。MOSデバイスは、第1のn型金属またはp型金属の仕事関数を有する第1の材料を備える。MOSデバイスは、第1の材料を含む第1のゲートを備える。MOSデバイスは、第1の材料を含む第2のゲートを備える。MOSデバイスは、第1のゲートと第2ゲートとの間に位置し、第1の材料とは逆の仕事関数を有する第2の材料を含むダミーゲートを備える。MOSデバイスは、各ゲートの下に位置し約18よりも大きい誘電率( $k$ )を有するゲート誘電体を備える。

##### 【0010】

別の例示的な実施形態で、1つのMOSデバイスが開示されている。MOSデバイスは、第1のn型金属またはp型金属の仕事関数を有するための第1の手段を備える。MOSデバイスは、第1の手段を含む第1のゲート手段を備える。MOSデバイスは、第1の手段を含む第2のゲート手段を備える。MOSデバイスは、第1のゲート手段と第2のゲート手段との間に位置し、第1の手段とは逆の仕事関数を有するための第2の手段を含むダミーゲート手段を備える。MOSデバイスは、各ゲート手段の下に位置し約18よりも大きい誘電率( $k$ )を有するゲート誘電体を備える。

##### 【0011】

別の例示的な実施形態で、1つのMOSデバイスを形成する方法が開示されている。この方法は、第1のn型金属またはp型金属の仕事関数を有する第1の材料を提供するステップを含む。この方法はまた、活性領域上に、約18よりも大きい誘電率( $k$ )を有するゲート誘電体を形成するステップを含む。この方法はまた、ゲート誘電体上に第1の材料を含む第1のゲートを形成するステップを含む。この方法はまた、ゲート誘電体上に第1の材料を含む第2のゲートを形成するステップを含む。この方法はまた、ゲート誘電体上に、第1の材料とは逆の仕事関数を有する第2の材料を含むダミーゲートを形成するステップを含む。この方法はまた、第1のゲートと第2のゲートとの間に、第1の材料とは逆の仕事関数を有する第2の材料を含むダミーゲートを配置するステップを含む。

40

##### 【図面の簡単な説明】

##### 【0012】

50

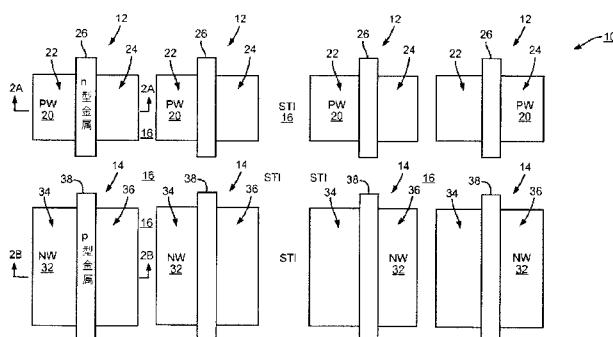

【図1】能動半導体部品を分離する浅溝分離構造（STI）を有する例示的な従来の相補型金属酸化物半導体（MOS）（CMOS）の簡略平面図である。

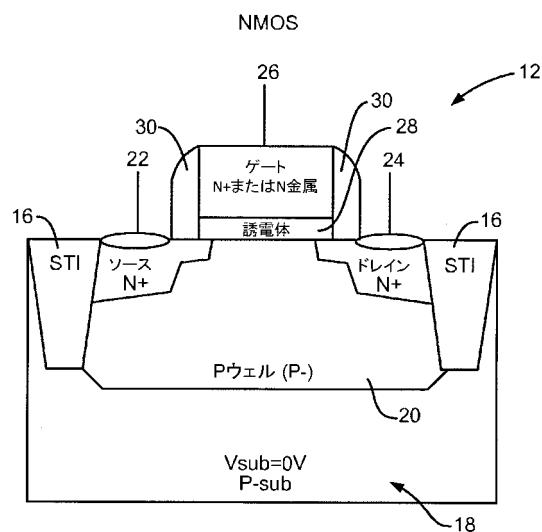

【図2A】n型MOS（nMOS）の、図1の2A-2A線による断面図である。

【図2B】p型MOS（pMOS）の、図1の2B-2B線による断面図である。

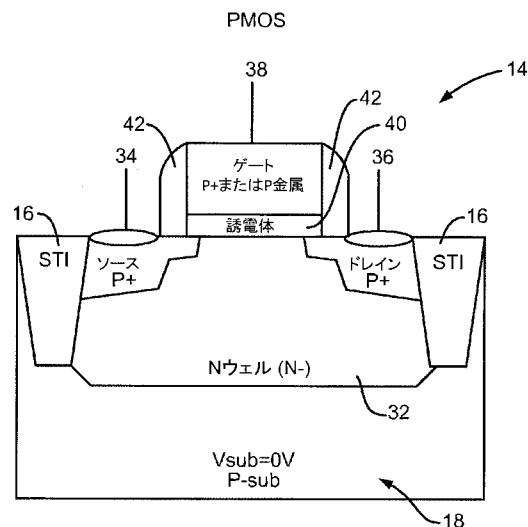

【図3】電界効果トランジスタ（FET）の分離に使用されるSTI遮断およびダミーゲートを有する連続活性領域が形成された例示的な従来のCMOSの簡略平面図である。

【図4】FETの分離に使用されるダミーゲートを有する連続活性領域が形成された例示的な従来のCMOSの簡略平面図である。

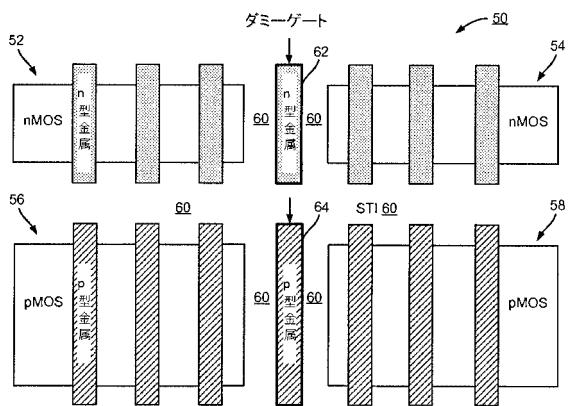

【図5】本開示の例示的な一実施形態に係る連続活性領域から形成された逆の仕事関数のダミーゲートを有する例示的なCMOSデバイスの簡略平面図である。 10

【図6】ほぼ平坦な構成を有する図4のCMOSデバイス内のnMOSデバイスの一実施形態の断面図である。

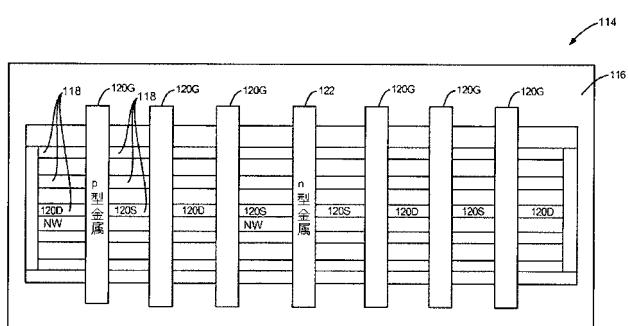

【図7A】本開示の例示的な一実施形態に係るダミーゲートを有する、フィンベース電界効果トランジスタ（FinFET）MOSデバイスの簡略平面図である。

【図7B】本開示の例示的な一実施形態に係るダミーゲートを有する、フィンベース電界効果トランジスタ（FinFET）MOSデバイスの簡略平面図である。

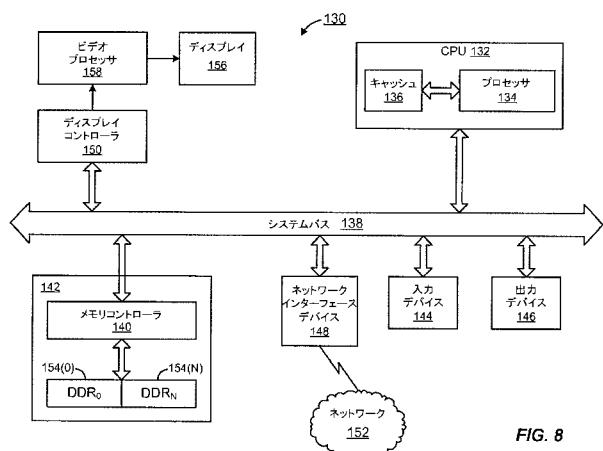

【図8】図5のCMOSデバイスを備えることができる、例示的なプロセッサ搭載システムのブロック図である。

#### 【発明を実施するための形態】

##### 【0013】

ここから、本開示のいくつかの例示的な実施形態を、図面を参照しつつ説明する。「例示的」という語は、本明細書で「例、事例、または描写の役割を果たす」ことを意味して用いられる。「例示的」として本明細書に記載されるいかなる実施形態も、必ずしも他の実施形態よりも好ましいまたは有利であるように解釈されるべきではない。 20

##### 【0014】

詳細な説明に開示される実施形態は、ダミーゲートで分割された連続活性領域を有する金属酸化物半導体（MOS）分離方式を含む。関連する方法もまた開示される。例示的な一実施形態では、MOSデバイスは、n型金属またはp型金属のいずれかとして記載されている仕事関数を有する材料から形成されたゲートを有する活性領域を含む。能動部品は、同じ仕事関数を有するゲート材料を使用して、この活性領域上に形成されている。能動部品の間にダミーゲートを配置することによって、分離がなされる。ダミーゲートは、活性領域のゲート材料に対して逆の仕事関数を有する材料から作られる。たとえば、活性領域内のゲートがp型金属材料であった場合、ダミーゲートは、n型金属から作られ、逆もまた同様である。この構造によって達成される分離方式は、効果的にリーク電流の量を低減し、MOS素子の動作速度を向上させる。この分離方式はまた、MOSデバイスが、浅溝分離構造（STI）の幅とリーク電流に制限されることなく、MOSデバイスの技術のスケーリングから予想される対応速度の増加を実現しながら小型化を可能にする。ポリゲートMOS素子とは異なり、本明細書に開示された特定の実施形態のゲート絶縁膜は、比較的高い誘電率（k）を有するため、ダミーゲート下に配置される分離埋込ゾーンの必要性を回避しつつ、逆仕事関数型ダミーゲートが所望の分離をするのを可能にする。 30

##### 【0015】

本開示による1つまたは複数のダミーゲートを用いたMOSデバイスの例示的な実施形態を論ずる前に、相補型MOS（CMOS）デバイス内の従来の分離プロセスの概要を、以下の図1～図4を参照して述べる。図1～図4はCMOSデバイスを示しているが、CMOSデバイスは、n型金属の仕事関数を有するMOSデバイス（すなわち、nMOS）およびp型金属の仕事関数を有するMOSデバイス（すなわち、pMOS）から形成されることを理解されたい。ダミーゲートを使用する実施形態の説明の一助とするために、これらの従来の分離プロセスを述べ、図5～図7Bに関連して以下に説明する。 40

##### 【0016】

この点に関し、図1は、従来のCMOSデバイス10のブロック図である。CMOSデ

バイス 10 は、1つまたは複数の n MOS 電界効果トランジスタ (FET) 12 および1つまたは複数の p MOS FET 14 が形成されている。各 FET 12、14 は、STI 16 によって他の FET 12、14 から分離される。

#### 【0017】

図 2A によりわかりやすく示すように、n MOS FET 12 は基板 18 上に形成されており、基板 18 は例示的な実施形態ではシリコン基板である。ウェル 20 は、基板 18 に形成されており、ウェル 20 は、例示的な実施形態では、p - 型フェルミエネルギー準位を有し（ここで、フェルミ準位を、シリコン内で P 型または N 型ドーパントによって誘導されるシリコンバンドギャップ内部の欠陥エネルギー帯と呼ぶ）、また、ここで p ウェル（または p w）と呼ぶことができる。n MOS FET 12 は、ソース 22、ドレイン 24 およびゲート 26 を備える。ソース 22 およびドレイン 24 は、ウェル 20 内に形成されており、n + 型フェルミエネルギー準位（すなわち、導電帯に非常に近いフェルミエネルギー準位）を有してもよい。ゲート 26 は、ウェル 20 上に形成され、ゲート誘電体 28 によってそこから分離され、ゲート誘電体 28 は酸化物層等であってもよい。ゲート 26 は、n 型金属の仕事関数を有する材料から形成される。また、ゲート 26 は、ゲート 26 の両側にスペーサ 30 を有していてもよい。n MOS FET 12 は、電源 22、ドレイン 24、およびゲート 26 との電気的接点（図示せず）を備える。

10

#### 【0018】

同様に、図 2B に示すように、p MOS FET 14 は基板 18 上に形成されており、基板 18 は例示的な実施形態ではシリコン基板である。ウェル 32 は、基板 18 に形成されており、ウェル 32 は、例示的な実施形態では、n - 型フェルミエネルギー準位を有し、ここで、N ウェル（または n w）と呼ぶことができる。p MOS FET 14 は、ソース 34、ドレイン 36 およびゲート 38 を備える。ソース 34 およびドレイン 36 は、ウェル 32 内に形成されており、p + 型のフェルミエネルギー準位を有してもよい。ゲート 38 は、ウェル 32 上に形成され、ゲート誘電体 40 によってそこから分離され、ゲート誘電体 38 は酸化物層等であってもよい。ゲート 38 は、p 型金属の仕事関数を有する材料から形成される。また、ゲート 38 は、ゲート 38 の両側にスペーサ 42 を有していてもよい。p MOS FET 14 は、ソース 34、ドレイン 36、およびゲート 38 との電気的接点（図示せず）を備える。

20

#### 【0019】

図 1 に戻り、上述したように、FET 12、14 は、STI 16 によって互いから分離されている。STI 16 は FET 12、14 のそれぞれに効果的な電気的絶縁の役割を果たす。典型的な構成では、STI 16 などの STI 遮断による分離は、先端スケーリング技術のため 10 pA / μm の範囲にある。STI 16 などの STI 遮断は、多くの例で許容可能な分離を提供するが、STI 遮断を使用すると、連続的な製造プロセスに影響を及ぼし、要素間の遮断が生じ、そのことが、チップサイズを増大させ、駆動電流を低減し、それが今度は速度を減少させ、電力消費を増加させる。

30

#### 【0020】

図 1 ~ 図 2B は CMOS デバイス 10 に焦点を当てているが、厳密な n MOS デバイスまたは厳密な p MOS デバイスのような、他のタイプの MOS デバイスに、同一の概念および欠点があてはまることを理解されたい。さらに、CMOS デバイス 10 は、平面デバイスとして示されているが、同じ技術は FinFET デバイスにもまた使用される。FinFET は、非平面で、シリコン基板または絶縁体 (SOI) 基板のシリコン上に構築されたダブルまたはトリプルゲートトランジスタの説明に使用される用語である。FinFET の際立った特徴は、導電チャネルが、デバイスのチャネルを形成する薄いシリコン「フィン」の周りにあるということである。フィンの長さ（ソースからドレインへの方向で測定される）が、デバイスの実効チャネル長を決定する。

40

#### 【0021】

図 3 に示す別の従来の手法では、ダミーゲートを STI に組み合わせている。この点に関して、図 3 に示すように、CMOS デバイス 50 は、基板（図示せず）上に形成されて

50

いる。CMOSデバイス50は、第1のnMOSFET52と第2のnMOSFET54、また、第1のpMOSFET56と第2のpMOSFET58を備える。FET52、54、56、58は、STI60によって互いから分離されている。また、ダミーゲート62は、nMOSFET52、54の間に配置される。ダミーゲート62はn型金属の仕事関数を有する。同様に、ダミーゲート64は、pMOSFET56、58の間に配置される。ダミーゲート64は、p型金属の仕事関数を有する。このように、ダミーゲート62、64の仕事関数はダミーゲートが分離するFET(52、54または56、58のいずれか)の仕事関数に相当する。ここでも、STI60とダミーゲート62、64を使用すると(たとえば、約10pA/μmの範囲の)許容可能な分離がなされるが、STI60を使用すると、連続活性領域が中断される。上述のように、STI60は電流機構の所望の移動度を達成するのに十分な大きさのストレッサを作成する能力に影響を与え、CMOSデバイス50の性能はより小さいサイズ(たとえば、28ナノメートル(nm)以下のスケール)では改善されない。

### 【0022】

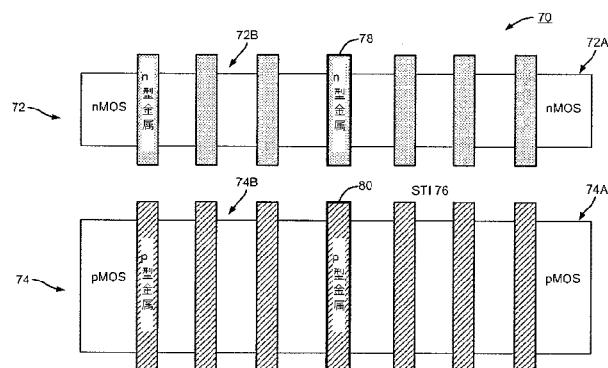

図4に、また別の従来の手法を示す。図4は、連続活性領域方式により形成されたCMOSデバイス70を示す。特に、CMOSデバイス70は、nMOSFET72A、72B(総称して72)およびpMOSFET74A、74B(総称して74)を備える。nMOSFET72は、STI76によりpMOSFET74から分離される。図3のCMOSデバイス50とは異なり、nMOSFET72Aは、STI76によりnMOSFET72Bから分離されていない。むしろ、nMOSFET72AとnMOSFET72Bは、連続的な活性領域から形成され、ダミーゲート78のみで分離されている。ダミーゲート78はn型金属の仕事関数を有する。同様に、pMOSFET74Aは、STI76によってpMOSFET74Bから分離されていない。むしろ、pMOSFET74AとpMOSFET74Bは、連続活性領域から形成され、ダミーゲート80のみで分離されている。ダミーゲート80は、p型金属の仕事関数を有する。この例示的な実施形態には、連続的な活性領域方式から形成されるという利点があるが、ダミーゲート78、80は、対になったFET72A、72Bまたは対になったFET74A、74Bの間では十分に絶縁しないことがよくある。たとえば、20nmスケールの典型的なnMOS構造では、デバイスは、極端な低閾値デバイスとして10nA/μmを有するが、これはSTIスタイルのデバイスのリーケよりも約千倍大きい。同様に、類似のデバイスは、標準閾値デバイスとして約350pA/μmを有するが、これはSTIスタイルのデバイスのリーケより約35倍大きい。このように、(pMOSFET74AからpMOSFET74Bへと同様に)1つのnMOSFET72AからnMOSFET72Bへダミーゲート78をわたって電流がリーケし、CMOSデバイス70の性能を低下させる。リーケ電流に対処するための1つの解決策は、ダミーゲート78、80上のゲートバイアスを増加させることである。nMOSFET72の例では、通常、ゲートバイアスが0Vであるが、リーケ電流を低減するために、ダミーゲート78に-0.5Vを印加するかもしれない。このようなゲートバイアスを使用すると、余分に外部電源が必要となるので、今度は、デバイスの設置面積が増大し、回路が複雑になる。同様に、-0.5Vのゲートバイアスで、V<sub>gs</sub>はV<sub>dd</sub>(たとえば、0.5V)に到達するかもしれないが、これは薄いゲート酸化膜には高すぎ、ゲートに不必要的摩耗を引き起こす可能性がある。同様に、pMOSFET74において、通常、分離なしだとV<sub>g</sub>=0Vであるが、リーケ電流を低減するために、V<sub>g</sub>はV<sub>dd</sub>または0.5Vに設定されるかもしれない。このゲートバイアスは、ここでも余分に外部電源を必要とし同時に/あるいはゲート酸化膜の信頼性の問題を生みだす。いずれの場合も、CMOSデバイス70は、より小さい設計スケールにおいては、最適にはならない。

### 【0023】

従来のデバイスの性能(たとえば、速度、リーケ電流など)が最適にならぬことへの解決策は、ダミーゲート78、80を逆の仕事関数を有する材料から作られた分離ダミーゲートと交換することにある。すなわち、FETがn型金属の仕事関数を有する場合、

ダミーゲートは p 型金属の仕事関数を有する。逆に、FET が p 型金属の仕事関数を有する場合、ダミーゲートは、n 金属の仕事関数を有する。ダミーゲートの材料を選択することにより、余分な外部電源を必要とせずに分離の改善を可能とし、回路内の領域を温存できる。同様に、これらの半導体デバイスを作成するプロセスは、従来の、高誘電率 / メタルゲートプロセス (high-k / metal gate process) に対しての余分な変更を必要としない。むしろ、新たなダミーゲートには、(CMOSで使用されている) 逆型ゲートマスクを、ダミーゲートを配置するために使用する。ダミーゲートの仕事関数を反転させることにより、連続活性領域方式を用いた CMOS デバイスを形成する能力をいまだ保持しながら、許容レベルの分離が達成されることを試験結果は示している。すなわち、この例では、 $10 \text{ pA} / \mu\text{m}$  の範囲で分離がなされている。ストレッサ要素を形成するための領域が維持されるため、ON 状態で利用可能な電流も増大し、そのため FET の内の電流機構の移動度が増大する。改善した分離を伴って結合された連続活性領域方式を使用することにより、さらなる小型化および柔軟な設計が可能になる。

#### 【0024】

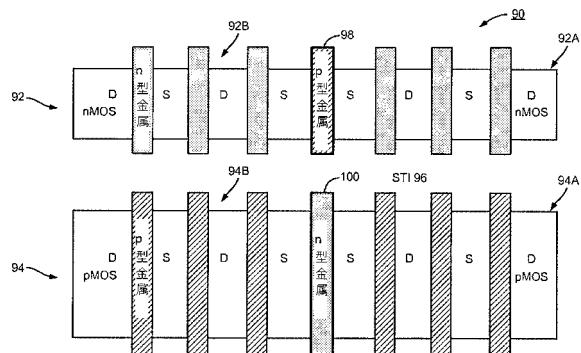

この点に関し、反転した仕事関数を有するダミーゲートを採用した CMOS デバイス 90 の第 1 の実施形態を図 5 に示す。図に示すように、CMOS デバイス 90 は、連続活性領域方式により形成されている。具体的には、CMOS デバイス 90 は、nMOS FET 92A、92B (総称して 92) と pMOS FET 94A、94B (総称して 94) とを備える。nMOS FET 92 は、STI 96 によって pMOS FET 94 から分離される。図 4 の CMOS デバイス 70 と同様に、nMOS FET 92A は、STI 96 によって nMOS FET 92B から分離されていない。むしろ、nMOS FET 92A と nMOS FET 92B は、連続活性領域から形成され、ダミーゲート 98 のみによって分離されている。ダミーゲート 98 は、p 型金属の仕事関数を有し、したがって、それが使用される MOS デバイスとは逆の仕事関数を有する。言い換えれば、ダミーゲート 98 は反転した仕事関数を有する。同様に、pMOS FET 94A は、STI 96 によって pMOS FET 94B から分離されていない。むしろ、pMOS FET 94A と pMOS FET 94B は、連続的な活性領域から形成され、ダミーゲート 100 のみによって分離されている。ダミーゲート 100 は、n 型金属の仕事関数を有し、したがって、それが使用される MOS デバイスとは逆の仕事関数を有する。言い換えれば、ダミーゲート 100 は、反転仕事関数を有する。図示されていないが、ダミーゲート 98、100 のそれぞれは、ゲート誘電体 28、40 に類似のゲート誘電体上に配置されることを理解されたい。例示的な実施形態では、CMOS デバイス 90 のゲート誘電体は、高誘電率 ( $k$ ) を有する。例示的な実施形態では、 $k$  は 18 より大きく、また別例示的な実施形態では、 $k$  は約 20 ~ 25 の間にある。

#### 【0025】

引き続き図 5 を参照すると、例示的な実施形態では、ダミーゲート 98 は  $V_{ss}$  に接続され、ダミーゲート 100 は  $V_{dd}$  に接続される。既に述べたように、仕事関数の反転により、CMOS デバイス 90 の製造において、製造者が連続能動領域方式を使用するのを可能にしつつ、許容レベルの分離が得られる。ダミーゲート 98、100 の近くに電源を配置することにより、分離リードをさらに低減することができる。

#### 【0026】

図 5 は、nMOS FET 92 と pMOS FET 94 の両方を有する CMOS デバイス 90 を示しているが、本開示の概念は、nMOS デバイスのみ、および / または pMOS デバイスのみを備える MOS デバイスに用いることができるることを理解されたい。

#### 【0027】

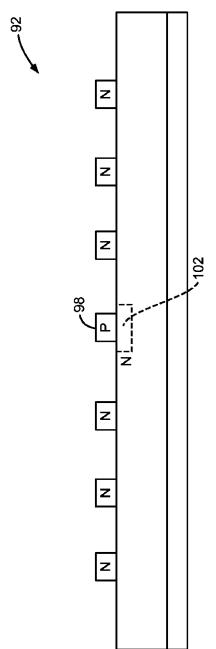

さらに注意したい点は、ダミーゲート 98、100 の下に分離埋込ゾーンが存在しないことである。特に、ポリゲートの技術のような従来技術は、ダミーゲートによる分離を改善するために、そのような分離埋込ゾーン (すなわち、特定のタイプのドーピングが埋め込まれたゾーン) をダミーゲートの下に用いる。そのような分離埋込ゾーンは、分離サイズを増大させ、一般的には、同じレベルの分離に至らない。図 6 に nMOS デバイス 92

10

20

30

40

50

の断面図を示すが、それは分離埋込ゾーンのないダミーゲート98の下にゾーン102を備える。pMOSデバイス94も、ダミーゲート100下に分離埋込ゾーンが存在しないことを理解されたい。

#### 【0028】

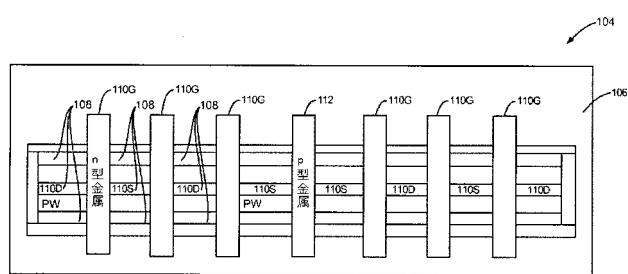

図5のCMOSデバイス90は、周知のように、一般的に平坦な構成だが、本発明の概念はそれに限定されず、FinFETの設計に拡張することができる。図7Aおよび図7Bは、FinFETにおける反転型の金属ダミーゲートの2つの種類を示している。特に、図7Aは、フィン108がゲート110Gに沿って垂直に配置される活性領域106を持つ、FinFET nMOSデバイス104を示している。FinFET nMOSデバイス104は、さらに、ソース110Sおよびドレイン110Dを備える。FinFET nMOSデバイス104においては、能動素子のゲートの仕事関数は、n型金属のものであり、対応するダミーゲート112は、p型金属の仕事関数を有する。ダミーゲート112の近くにソースを配置することにより、分離リーケをさらに低減することができる。

10

#### 【0029】

図7AのFinFET nMOSデバイス104と対比して、FinFET pMOSデバイス114が、図7Bに示される。FinFET pMOSデバイス114は、活性領域116およびフィン118を備える。同様に、FinFET pMOSデバイス114はドレイン120D、ソース120S、およびゲート120Gを備える。FinFET pMOSデバイス114の活性領域116は、p型金属の仕事関数を有し、対応するダミーゲート122は、n金属の仕事関数を有する。ダミーゲート122の近くにソースを配置することにより、分離リーケをさらに低減することができる。

20

#### 【0030】

nMOSデバイス104およびpMOSデバイス114は、必要に応じCMOSデバイスに組み込むことができる。ここでも、高いゲート誘電体、および注入分離領域が存在しないことにより、ますます小さいサイズにおいても、速度の改善が可能になる。

#### 【0031】

本明細書において開示する実施形態に係る連続活性領域を有するCMOS分離方式は任意のプロセッサ搭載デバイスに備え、または統合することができる。例としては、以下に限定するものではないが、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定位置データユニット、移動位置データユニット、移動電話、携帯電話、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、パーソナルデジタルアシスタント(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、携帯音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、携帯型デジタルビデオプレーヤ、が挙げられる。

30

#### 【0032】

この点に関し、図8は、CMOSデバイス90またはMOSデバイス92、94、104、114のようなCMOSデバイスを使用することができるプロセッサ搭載システム130の一例を示す。この例では、プロセッサ搭載システム130は、各々が1つまたは複数のプロセッサ134を含む1つまたは複数の中央処理装置(CPU)132を備える。CPU132は、一時的に格納されたデータへの迅速なアクセスのためにプロセッサ134に結合されたキャッシュメモリ136を備えてもよい。CPU132は、システムバス138に係合され、プロセッサ搭載システム130に含まれるマスタデバイスとスレーブデバイスを相互に連結することができる。周知のように、CPU132は、システムバス138を介してアドレス、制御、およびデータ情報を交換することにより、これらの他のデバイスと通信する。たとえば、CPU132は、メモリコントローラ140へバストラ nsザクションリクエストを通信することができる。図8に示されていないが、複数のシステムバス138を設けてもよく、それぞれのシステムバス138は、別な構成である。

40

#### 【0033】

他のデバイスをシステムバス 138 に接続することもできる。図 8 に示すように、これらのデバイスは、例として、メモリシステム 142、1つまたは複数の入力デバイス 144、1つまたは複数の出力デバイス 146、1つまたは複数のネットワークインターフェースデバイス 148、および 1つまたは複数のディスプレイコントローラ 150 を含み得る。入力デバイス 144 は、任意のタイプの入力デバイスも含み、入力キー、スイッチ、音声プロセッサ、等を含むが、これらに限定されない。出力デバイス 146 は、任意のタイプの出力デバイスも含み、オーディオ、ビデオ、その他視覚的インジケータ等を含むが、これらに限定されない。ネットワークインターフェースデバイス 148 は、ネットワーク 152 とのデータ交換が可能なように構成された任意のデバイスである。ネットワーク 152 は、任意のタイプのネットワークで、有線またはワイヤレスのネットワーク、プライベートまたはパブリックネットワーク、ローカルエリアネットワーク (LAN)、ワイドローカルエリアネットワーク (WLAN)、およびインターネットを含むが、これらに限定されない。ネットワークインターフェースデバイス 148 は、任意のタイプの所望の通信プロトコルをサポートするように構成することができる。メモリシステム 142 は、1つまたは複数のメモリユニット 154 (0 - N) を備えることができる。

10

## 【0034】

CPU 132 は、1つまたは複数のディスプレイ 156 に送信される情報を制御するためのシステムバス 138 を介してディスプレイコントローラ 150 にアクセスするように構成されてもよい。ディスプレイコントローラ 150 は、1つまたは複数のビデオプロセッサ 158 を介して表示するディスプレイ 156 に情報を送信し、1つまたは複数のビデオプロセッサ 158 は表示される情報をディスプレイ 156 に適した形式に処理する。ディスプレイ 156 は、任意のタイプのディスプレイ、たとえば陰極線管 (CRT)、液晶ディスプレイ (LCD)、プラズマディスプレイ、等を含み得るが、これに限定されない。

20

## 【0035】

当業者は、本明細書に開示された実施形態に関連して説明される様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムは、電子ハードウェアとして、メモリまたは他のコンピュータ可読媒体に格納された命令として実装され、プロセッサまたは他の処理デバイス、またはその両方の組合せにより実行され得ることを、さらに理解するであろう。本明細書に記載のアービタ、マスタデバイス、スレーブデバイスは、例として、任意の回路、ハードウェア・コンポーネント、集積回路 (IC)、または IC チップで使用してもよい。本明細書に開示されたメモリは、任意のタイプおよびサイズのメモリであってもよく、所望の任意のタイプの情報を格納するように構成されてもよい。この互換性を明瞭に示すために、様々な例示的なコンポーネント、ブロック、モジュール、回路、およびステップが、それらの機能の観点から一般的に上記に記載されている。そのような機能がどのように実装されているかは、特定のアプリケーション、設計選択、および / またはシステム全体に課される設計制約次第である。当業者は、各特定のアプリケーションのために様々な方法で上記に説明した機能を実施するかもしれないが、そのような実施方法を判断することは、本開示の範囲からの逸脱と解釈されるべきではない。

30

## 【0036】

本明細書に開示された実施形態に関連して説明される様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ (DSP)、特定用途向け集積回路 (ASIC)、フィールドプログラマブルゲートアレイ (FPGA) または他のプログラマブル論理デバイス、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェアコンポーネント、または本明細書に記載の機能を実行するように設計された任意の組合せを用いて実装または実施できる。プロセッサは、マイクロプロセッサであってもよいが、代わりに、プロセッサは任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであってもよい。また、プロセッサは、たとえば、DSP とマイクロプロセッサ、複数のマイクロプロセッサ、DSP コアと連動した 1つまたは複数のマイクロプロセッサ、または任意の他のそのような構成の組合せ

40

50

といった、コンピューティングデバイスの組合せで実施されてもよい。

【0037】

本明細書に開示された実施形態は、ハードウェアおよびハードウェア内に記憶された命令で実施することができ、たとえば、ランダムアクセスメモリ( RAM )、フラッシュメモリ、読み取り専用メモリ( ROM )、電気的プログラマブル ROM ( EEPROM )、電気的消去可能プログラマブル ROM ( EEPROM )、レジスタ、ハードディスク、リムーバブルディスク、CD - ROM、または当技術分野で知られているコンピュータ可読媒体の他の任意の形態で実現してもよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるようプロセッサに結合される。代わりに、記憶媒体はプロセッサと一体であってもよい。プロセッサおよび記憶媒体は ASIC 中に常駐することができる。ASICは、遠隔局に常駐することができる。代わりに、プロセッサおよび記憶媒体は、遠隔局、基地局、またはサーバにおいてディスクリート部品として常駐してもよい。

10

【0038】

また、本明細書の任意の例示的な実施形態に記載の動作ステップが例と説明を提示するために記載されていることに留意されたい。説明の動作は、図示の順番以外の多数の異なる順番で実行されてもよい。さらに、単一の動作ステップで説明した動作は実際には多数の異なるステップで行ってもよい。さらに、例示的な実施形態で説明した1つまたは複数の動作ステップは組み合わされてもよい。なお、フローチャート図に示す動作ステップは、当業者に容易に明らかのように、多数の様々な改変を受けるであろうことが理解されるべきである。任意の様々な異なる技術および技法を用いて情報および信号を表し得ることを当業者は理解するであろう。たとえば、上記の説明を通じ参照されるかもしれないデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界または磁性粒子、光場または光粒子、または任意のこれらの組合せによって表されるかもしれない。

20

【0039】

本開示の上記説明は、当業者が本開示を作成あるいは使用することを可能にするために提示される。本開示に対する様々な改変は、当業者には容易に明らかであり、本明細書中で定義された一般的な原理は、本開示の精神または範囲から逸脱することなく他の応用に適用されるかもしれない。したがって、本開示は、本明細書に記載の例および設計に限定されるものではなく、ここに開示された原理および新規な特徴と一致する最も広い範囲を与えるべきである。

30

【符号の説明】

【0040】

- 2 A 線

- 2 B 線

- 1 0 C M O S デバイス

- 1 2 n M O S F E T

- 1 4 p M O S F E T

- 1 6 S T I

- 1 8 基板

- 2 0 ウエル

- 2 2 ソース

- 2 4 ドレイン

- 2 6 ゲート

- 2 8 ゲート誘電体

- 3 0 スペーサ

- 3 2 ウエル

- 3 4 ソース

- 3 6 ドレイン

40

50

|         |                       |    |

|---------|-----------------------|----|

| 3 8     | ゲート                   |    |

| 4 0     | ゲート誘電体                |    |

| 4 2     | スペーサ                  |    |

| 5 0     | C M O S デバイス          |    |

| 5 2     | 第1のnMOS FET           |    |

| 5 4     | 第2のnMOS FET           |    |

| 5 6     | 第1のpMOS FET           |    |

| 5 8     | 第2のpMOS FET           |    |

| 6 0     | S T I                 |    |

| 6 2     | ダミーゲート                | 10 |

| 6 4     | ダミーゲート                |    |

| 7 0     | C M O S デバイス          |    |

| 7 2     | nMOS FET              |    |

| 7 2 A   | nMOS FET              |    |

| 7 2 B   | nMOS FET              |    |

| 7 4     | pMOS FET              |    |

| 7 4 A   | pMOS FET              |    |

| 7 4 B   | pMOS FET              |    |

| 7 6     | S T I                 |    |

| 7 8     | ダミーゲート                | 20 |

| 8 0     | ダミーゲート                |    |

| 9 0     | C M O S デバイス          |    |

| 9 2     | nMOS FET              |    |

| 9 2 A   | nMOS FET              |    |

| 9 2 B   | nMOS FET              |    |

| 9 4     | pMOS FET              |    |

| 9 4 A   | pMOS FET              |    |

| 9 4 B   | pMOS FET              |    |

| 9 6     | S T I                 |    |

| 9 8     | ダミーゲート                | 30 |

| 1 0 0   | ダミーゲート                |    |

| 1 0 2   | ゾーン                   |    |

| 1 0 4   | F i n F E T nMOS デバイス |    |

| 1 0 6   | 活性領域                  |    |

| 1 0 8   | フィン                   |    |

| 1 1 0 G | ゲート                   |    |

| 1 1 0 D | ドレイン                  |    |

| 1 1 0 S | ソース                   |    |

| 1 1 2   | ダミーゲート                |    |

| 1 1 4   | F i n F E T pMOS デバイス | 40 |

| 1 1 6   | 活性領域                  |    |

| 1 1 8   | フィン                   |    |

| 1 2 0 G | ゲート                   |    |

| 1 2 0 D | ドレイン                  |    |

| 1 2 0 S | ソース                   |    |

| 1 2 2   | ダミーゲート                |    |

| 1 3 0   | プロセッサ搭載システム           |    |

| 1 3 2   | C P U                 |    |

| 1 3 4   | プロセッサ                 |    |

| 1 3 6   | キャッシュメモリ              | 50 |

- 1 3 8 システムバス

1 4 0 メモリコントローラ

1 4 2 メモリシステム

1 4 4 入力デバイス

1 4 6 出力デバイス

1 4 8 ネットワークインターフェースデバイス

1 5 0 ディスプレイコントローラ

1 5 2 ネットワーク

1 5 4 メモリユニット

1 5 6 ディスプレイ

1 5 8 ビデオプロセッサ

10

【図 1】

FIG. 1

(先行技術)

【図 2 A】

FIG. 2A

(先行技術)

【図 2B】

FIG. 2B

(先行技術)

【図 3】

FIG. 3

(先行技術)

【図 4】

FIG. 4

(先行技術)

【図 5】

FIG. 5

(先行技術)

【図6】

FIG. 6

【図7A】

FIG. 7A

【図7B】

FIG. 7B

【図8】

FIG. 8

**【手続補正書】**

【提出日】平成26年12月5日(2014.12.5)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

第1のn型金属またはp型金属の仕事関数を有する第1の材料と、

前記第1の材料を含む第1の複数のゲートと、

前記第1の材料を含む第2の複数のゲートと、

前記第1の複数のゲートと前記第2の複数のゲートとの間に位置し、前記第1の材料とは逆の仕事関数を有する第2の材料を含むダミーゲートと

を備える、金属酸化物半導体(MOS)デバイス。

**【請求項2】**

前記第1の材料が、n型金属の仕事関数を有する材料を含む、請求項1に記載のMOSデバイス。

**【請求項3】**

前記第2の材料が、p型金属の仕事関数を有する材料を含む、請求項2に記載のMOSデバイス。

**【請求項4】**

前記第1の材料が、p型金属の仕事関数を有する材料を含む、請求項1に記載のMOSデバイス。

**【請求項5】**

前記第2の材料が、n型金属の仕事関数を有する材料を含む、請求項4に記載のMOSデバイス。

**【請求項6】**

相補型MOSデバイス(CMOS)を形成するための第2のMOSデバイスをさらに備え、前記第2のMOSデバイスが、

前記第2の材料を含む第3のゲートと、

前記第2の材料を含む第4のゲートと、

前記第3のゲートと前記第4のゲートとの間に位置し、前記第1の材料を含む第2のダミーゲートと

を備える、請求項1に記載のMOSデバイス。

**【請求項7】**

前記第1のMOSデバイスと前記第2のMOSデバイスとの間に浅溝分離構造(STI)をさらに含む、請求項6に記載のMOSデバイス。

**【請求項8】**

前記ダミーゲートは、ゲート誘電体上に配置され、前記ダミーゲート下に分離埋込ゾーンがない、請求項1に記載のMOSデバイス。

**【請求項9】**

前記MOSデバイスは、実質的に平面状のデバイスである、請求項1に記載のMOSデバイス。

**【請求項10】**

前記MOSデバイスは、フィンベースの電界効果トランジスタ(FinFET)デバイスである、請求項1に記載のMOSデバイス。

**【請求項11】**

前記MOSデバイスは、半導体ダイに集積される、請求項1に記載のMOSデバイス。

**【請求項12】**

前記MOSデバイスが組み込まれた、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定位置データユニット、モバイルロケーションデータユニット、移動電話、携帯電話、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、パーソナルデジタルアシスタント(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、携帯音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、携帯デジタルビデオプレーヤからなる群から選択されたデバイスをさらに含む、請求項1に記載のMOSデバイス。

#### 【請求項13】

第1のn型金属またはp型金属の仕事関数を有するための第1の手段と、

前記第1の手段から形成される第1の複数のゲートを含む第1のゲート手段と、

前記第1の手段から形成される第2の複数のゲートを含む第2のゲート手段と、

前記第1のゲート手段と前記第2のゲート手段との間に位置し、前記第1の手段とは逆の仕事関数を有するための第2の手段を含むダミーゲート手段と

を備える、金属酸化物半導体(MOS)デバイス。

#### 【請求項14】

第1のn型金属またはp型金属の仕事関数を有する第1の材料を提供するステップと、

活性領域上に、約18よりも大きい誘電率(k)を有するゲート誘電体を形成するステップと、

前記ゲート誘電体上に前記第1の材料を含む第1の複数のゲートを形成するステップと、

前記ゲート誘電体上に前記第1の材料を含む第2の複数のゲートを形成するステップと、

前記ゲート誘電体上に、前記第1の材料とは逆の仕事関数を有する第2の材料を含むダミーゲートを形成するステップと、

前記第1の複数のゲートと前記第2の複数のゲートとの間に、前記第1の材料とは逆の仕事関数を有する第2の材料を含む前記ダミーゲートを配置するステップと

を含む、金属酸化物半導体(MOS)デバイスを形成する方法。

#### 【請求項15】

前記ダミーゲートを形成するステップは、分離埋込ゾーンが存在しない位置に前記ダミーゲートを形成するステップを含む、請求項14に記載の方法。

#### 【請求項16】

前記ゲート誘電体を形成するステップは、約20～25の誘電率を有する前記ゲート誘電体を形成するステップを含む、請求項14に記載の方法。

#### 【請求項17】

前記第1の材料はn型金属の仕事関数を有する材料を含み、前記第2の材料はp型金属の仕事関数を有する材料を含む、請求項14に記載の方法。

#### 【請求項18】

前記ダミーゲートを接地するステップをさらに含む、請求項17に記載の方法。

#### 【請求項19】

前記第2のゲートの近くにソースを形成するステップをさらに含む、請求項17に記載の方法。

#### 【請求項20】

前記第1の材料がp型金属の仕事関数を有する材料を含み、前記第2の材料がn型金属の仕事関数を有する材料を含む、請求項14に記載の方法。

#### 【請求項21】

電圧ソースに前記ダミーゲートを接続するステップをさらに含む、請求項20に記載の方法。

#### 【請求項22】

前記第2のゲートの近くにソースを形成するステップをさらに含む、請求項20に記載

の方法。

【請求項 2 3】

C M O S デバイスを形成するために、前記第 1 の M O S デバイスとともに第 2 の M O S デバイスを形成するステップをさらに含む、請求項 1 4 に記載の方法。

【請求項 2 4】

前記第 2 の M O S デバイスを形成するステップは、前記第 2 の M O S デバイス内にダミーゲートを形成するステップを含む、請求項 2 3 に記載の方法。

【請求項 2 5】

各ゲートの下に位置し、約 1/8 よりも大きい誘電率 ( k ) を有するゲート誘電体をさらに備える、請求項 1 に記載の M O S デバイス。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2014/022263

A. CLASSIFICATION OF SUBJECT MATTER

INV. H01L21/8238 H01L21/765 H01L27/02

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                            | Relevant to claim No.      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| X         | US 2011/147765 A1 (HUANG LI-PING [TW] ET AL) 23 June 2011 (2011-06-23)<br>paragraphs [0010], [0026] - [0028], [0034], [0035], [0041]; figures 1-4<br>-----                    | 1-9,<br>11-24              |

| X         | US 2011/215404 A1 (ZHU MING [SG] ET AL ZHU MING [TW] ET AL)<br>8 September 2011 (2011-09-08)<br>paragraphs [0012], [0017], [0019], [0035] - [0037], [0043]; figure 8<br>----- | 1-9,<br>11-17,<br>20,23,24 |

| X         | US 2012/126336 A1 (ANDERSON BRENT A [US] ET AL) 24 May 2012 (2012-05-24)<br>paragraphs [0013], [0015], [0016];<br>figure 2<br>-----<br>-/-                                    | 1-5,8-22                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

17 June 2014

25/06/2014

Name and mailing address of the ISA/

European Patent Office, P.B. 5816 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Seck, Martin

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/022263 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                    | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | GANG HE; ZHAOQI SUN; GUANG LI; LIDE ZHANG:<br>"Review and Perspective of Hf-based High-k<br>gate Dielectrics on Silicon",<br>CRITICAL REVIEWS IN SOLID STATE AND<br>MATERIAL SCIENCES,<br>vol. 37, no. 3,<br>12 September 2012 (2012-09-12), pages<br>131-157, XP009178565,<br>ISSN: 1040-8436, DOI:<br>10.1080/10408436.2011.602136<br>Section "1. Introduction";<br>page 132 - page 134; figure 1; table 1<br>----- | 1,13,14,<br>16        |

| A         | US 2012/001232 A1 (LIAW JHON JHY [TW])<br>5 January 2012 (2012-01-05)<br>paragraphs [0036], [0048], [0049];<br>figures 5,9<br>-----                                                                                                                                                                                                                                                                                   | 10,18,21              |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2014/022263

| Patent document cited in search report | Publication date | Patent family member(s) |  | Publication date |

|----------------------------------------|------------------|-------------------------|--|------------------|

| US 2011147765                          | A1 23-06-2011    | CN 102104041 A          |  | 22-06-2011       |

|                                        |                  | KR 20110069689 A        |  | 23-06-2011       |

|                                        |                  | TW 201123419 A          |  | 01-07-2011       |

|                                        |                  | US 2011147765 A1        |  | 23-06-2011       |

| US 2011215404                          | A1 08-09-2011    | CN 102194874 A          |  | 21-09-2011       |

|                                        |                  | US 2011215404 A1        |  | 08-09-2011       |

|                                        |                  | US 2014038376 A1        |  | 06-02-2014       |

| US 2012126336                          | A1 24-05-2012    | NONE                    |  |                  |

| US 2012001232                          | A1 05-01-2012    | CN 102314931 A          |  | 11-01-2012       |

|                                        |                  | KR 20120002401 A        |  | 05-01-2012       |

|                                        |                  | SG 177041 A1            |  | 30-01-2012       |

|                                        |                  | US 2012001232 A1        |  | 05-01-2012       |

|                                        |                  | US 2012223395 A1        |  | 06-09-2012       |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 シア・リ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ブル・チダムバラム

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

F ターム(参考) 5F048 AA04 AC03 BA01 BB09 BB10 BB14 BD06 BE03 BG00 BG13

5F140 AA24 AA39 AB03 BB05 CB06